JP6329843B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6329843B2 JP6329843B2 JP2014160945A JP2014160945A JP6329843B2 JP 6329843 B2 JP6329843 B2 JP 6329843B2 JP 2014160945 A JP2014160945 A JP 2014160945A JP 2014160945 A JP2014160945 A JP 2014160945A JP 6329843 B2 JP6329843 B2 JP 6329843B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- node

- potential

- semiconductor device

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

- H10B99/22—Subject matter not provided for in other groups of this subclass including field-effect components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/481—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D87/00—Integrated devices comprising both bulk components and either SOI or SOS components on the same substrate

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

- Electrodes Of Semiconductors (AREA)

- Static Random-Access Memory (AREA)

- Thin Film Transistor (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

Description

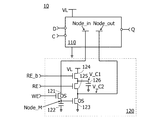

本実施の形態では、半導体装置の回路構成、及びその動作について説明する。

本実施の形態では、実施の形態1で説明した半導体装置10における変形例について説明する。また以下では、図6乃至図12を参照して変形例1乃至7について説明する。

図6は、図1で説明した半導体装置10において、トランジスタ123のソース及びドレインにバイポーラトランジスタ141(第5のトランジスタともいう)を接続した、半導体装置30の構成例を示す回路図である。

図7は、図1で説明した半導体装置10において、トランジスタ123のソース及びドレインにSiトランジスタであるトランジスタ142を接続した、半導体装置40の構成例を示す回路図である。

図8は、図1で説明した半導体装置10において、ノードV_C2に該ノードの電位を初期化するためのトランジスタ143を接続した、半導体装置50の構成例を示す回路図である。なおトランジスタ143はOSトランジスタとして図示しているが、Siトランジスタでもよい。なお図8では、トランジスタ143に接続されたノードV_C2を初期化するための電位として、グラウンド線の電位を与える構成を一例として示している。

図9は、図1で説明した半導体装置10において、トランジスタ124をpチャネル型トランジスタであるトランジスタ124_pとし、トランジスタ125をnチャネル型トランジスタとした、半導体装置60の構成例を示す回路図である。

図10は、図1で説明した半導体装置10において、トランジスタ121及びトランジスタ123のバックゲートに閾値電圧を制御するためのバックゲート信号OS_BGを与える構成とした、半導体装置70の構成例を示す回路図である。

図11は、図1で説明した半導体装置10において、トランジスタ121及びトランジスタ123のバックゲートに閾値電圧をプラスシフトさせるためのLレベルの電位であるグラウンド電位を与える構成とした、半導体装置80の構成例を示す回路図である。

図12は、図1で説明した半導体装置10において、トランジスタ124及びトランジスタ125をSiトランジスタでなく、OSトランジスタとした、半導体装置90の構成例を示す回路図である。なお図12では図示していないが、インバータ回路128を構成するトランジスタも同様に、OSトランジスタとすることもできる。

本実施の形態では、上記実施の形態で説明したオフ電流の低いトランジスタの、チャネル形成領域となる半導体層に用いることのできる酸化物半導体層について説明する。

本実施の形態では、開示する発明の一態様に係る半導体装置が有するトランジスタの断面の構造について、図面を参照して説明する。

本実施の形態では、上述の実施の形態で説明した半導体装置を電子部品に適用する例、及び該電子部品を具備する電子機器に適用する例について、図14、図15を用いて説明する。

V_C2 ノード

Node_in ノード

Node_out ノード

Node_M ノード

P1 期間

P2 期間

P3 期間

P4 期間

t1 時刻

t5 時刻

t6 時刻

t7 時刻

t9 時刻

t11 時刻

t14 時刻

T1 時刻

T5 時刻

T6 時刻

T7 時刻

T9 時刻

T11 時刻

T13 時刻

T14 時刻

10 半導体装置

30 半導体装置

40 半導体装置

50 半導体装置

60 半導体装置

70 半導体装置

80 半導体装置

90 半導体装置

110 記憶回路

111 スイッチ

112 インバータ回路

113 インバータ回路

114 スイッチ

115 インバータ回路

120 記憶回路

121 トランジスタ

122 容量素子

123 トランジスタ

124 トランジスタ

125 トランジスタ

124_p トランジスタ

126 容量素子

127 容量素子

128 インバータ回路

128_n トランジスタ

128_p トランジスタ

130 セレクタ

131 インバータ回路

141 バイポーラトランジスタ

142 トランジスタ

143 トランジスタ

700 電子部品

701 リード

702 プリント基板

703 半導体装置

704 実装基板

810 半導体基板

812 素子分離用絶縁膜

814 不純物領域

816 不純物領域

818 導電膜

820 ゲート絶縁膜

822 絶縁膜

824 導電膜

826 導電膜

828 導電膜

830 導電膜

832 導電膜

834 絶縁膜

836 導電膜

838 導電膜

840 半導体層

842 半導体層

844 導電膜

846 導電膜

848 導電膜

850 導電膜

852 ゲート絶縁膜

854 導電膜

856 導電膜

858 導電膜

860 絶縁膜

862 導電膜

901 筐体

902 筐体

903a 表示部

903b 表示部

904 選択ボタン

905 キーボード

911 筐体

912 筐体

913 表示部

914 表示部

915 軸部

916 電源

917 操作キー

918 スピーカー

921 筐体

922 表示部

923 スタンド

924 リモコン操作機

930 本体

931 表示部

932 スピーカー

933 マイク

934 操作ボタン

941 本体

942 表示部

943 操作スイッチ

Claims (8)

- 第1のノード及び第2のノードにデータを記憶する第1の記憶回路と、

前記データを記憶する第3のノードを有する第2の記憶回路と、を有し、

前記第2の記憶回路は、

前記データの書き込み時において、前記データの電位を前記第3のノードに与える第1のトランジスタと、

ゲートに前記第3のノードに保持される電位が与えられる第2のトランジスタと、

前記データの非読み出し時において、ソース及びドレインの一方に設けられた第1の容量素子への電荷の充電を行う第3のトランジスタと、

前記データの読み出し時において、前記第1の容量素子に充電された電荷を第2の容量素子に分配する第4のトランジスタと、

を有し、

前記データの読み出し時において、前記第2のトランジスタは、前記第3のノードの電位に従って、前記第2の容量素子の保持される電位を前記データの論理が反転した電位とし、

前記第1のトランジスタ及び前記第2のトランジスタは、酸化物半導体をチャネル形成領域となる半導体層に用いたトランジスタである半導体装置。 - 請求項1において、

前記第3のトランジスタ及び前記第4のトランジスタは、シリコンをチャネル形成領域となる半導体層に用いたトランジスタである半導体装置。 - 請求項2において、

前記第1のトランジスタ及び前記第2のトランジスタと、前記第3のトランジスタ及び前記第4のトランジスタとは、積層して設けられた半導体装置。 - 請求項1乃至3のいずれか一において、

前記第1のトランジスタ及び第2のトランジスタは、バックゲート電極が設けられたトランジスタである半導体装置。 - 請求項1乃至4のいずれか一において、

前記第2の容量素子に保持される電位を初期化するための電位を与えるトランジスタが、前記第2の容量素子の一方の電極に電気的に接続して設けられた半導体装置。 - 請求項1乃至5のいずれか一において、

前記第1の容量素子の静電容量は、前記第2の容量素子の静電容量よりも大きい半導体装置。 - 請求項1乃至6のいずれか一において、

前記第2のトランジスタのゲート絶縁膜の膜厚は、前記第3のトランジスタ及び前記第4のトランジスタのゲート絶縁膜の膜厚よりも大きい半導体装置。 - 請求項1乃至7のいずれか一において、

前記半導体装置は、前記第2の容量素子に保持される電位を反転し、前記第2のノードに与えるインバータ回路を有する、半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014160945A JP6329843B2 (ja) | 2013-08-19 | 2014-08-07 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013169830 | 2013-08-19 | ||

| JP2013169830 | 2013-08-19 | ||

| JP2014160945A JP6329843B2 (ja) | 2013-08-19 | 2014-08-07 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015062218A JP2015062218A (ja) | 2015-04-02 |

| JP6329843B2 true JP6329843B2 (ja) | 2018-05-23 |

Family

ID=52466200

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014160945A Expired - Fee Related JP6329843B2 (ja) | 2013-08-19 | 2014-08-07 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9608005B2 (ja) |

| JP (1) | JP6329843B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI791952B (zh) | 2014-12-18 | 2023-02-11 | 日商半導體能源研究所股份有限公司 | 半導體裝置、感測裝置和電子裝置 |

| JP2017041877A (ja) * | 2015-08-21 | 2017-02-23 | 株式会社半導体エネルギー研究所 | 半導体装置、電子部品、および電子機器 |

| US9998119B2 (en) * | 2016-05-20 | 2018-06-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, electronic component, and electronic device |

| US9992442B2 (en) * | 2016-10-13 | 2018-06-05 | Semiconductor Energy Laboratory Co., Ltd. | Decoder, receiver, and electronic device |

| KR20180099974A (ko) * | 2017-02-27 | 2018-09-06 | 삼성디스플레이 주식회사 | 반도체 장치 |

| WO2020254914A1 (ja) * | 2019-06-21 | 2020-12-24 | 株式会社半導体エネルギー研究所 | 酸化物半導体を用いる記憶回路 |

| WO2021048669A1 (ja) * | 2019-09-11 | 2021-03-18 | 株式会社半導体エネルギー研究所 | 撮像装置 |

Family Cites Families (183)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58205226A (ja) | 1982-05-25 | 1983-11-30 | Fujitsu Ltd | スタンバイ機能を内蔵したマイクロコンピユ−タ |

| JPS6025269A (ja) | 1983-07-21 | 1985-02-08 | Hitachi Ltd | 半導体記憶素子 |

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPS62177794A (ja) | 1986-01-31 | 1987-08-04 | Hitachi Ltd | 半導体メモリセル |

| JP2689416B2 (ja) | 1986-08-18 | 1997-12-10 | 日本電気株式会社 | フリツプフロツプ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| US4809225A (en) | 1987-07-02 | 1989-02-28 | Ramtron Corporation | Memory cell with volatile and non-volatile portions having ferroelectric capacitors |

| JPH0327419A (ja) | 1989-06-23 | 1991-02-05 | Toshiba Corp | パーソナルコンピュータ |

| US5218607A (en) | 1989-06-23 | 1993-06-08 | Kabushiki Kaisha Toshiba | Computer having a resume function and operable on an internal power source |

| JPH03192915A (ja) | 1989-12-22 | 1991-08-22 | Nec Corp | フリップフロップ |

| JPH05110392A (ja) | 1991-10-16 | 1993-04-30 | Hitachi Ltd | 状態保持回路を具備する集積回路 |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JPH07147530A (ja) | 1993-11-24 | 1995-06-06 | Mitsubishi Electric Corp | ラッチ回路及びマスタースレーブ型フリップフロップ回路 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| DE69635107D1 (de) | 1995-08-03 | 2005-09-29 | Koninkl Philips Electronics Nv | Halbleiteranordnung mit einem transparenten schaltungselement |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| GB9614800D0 (en) | 1996-07-13 | 1996-09-04 | Plessey Semiconductors Ltd | Programmable logic arrays |

| JPH1078836A (ja) | 1996-09-05 | 1998-03-24 | Hitachi Ltd | データ処理装置 |

| JP4103968B2 (ja) | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| US6046606A (en) | 1998-01-21 | 2000-04-04 | International Business Machines Corporation | Soft error protected dynamic circuit |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000077982A (ja) | 1998-08-27 | 2000-03-14 | Kobe Steel Ltd | 半導体集積回路 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP3955409B2 (ja) | 1999-03-17 | 2007-08-08 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| US6570801B2 (en) | 2000-10-27 | 2003-05-27 | Kabushiki Kaisha Toshiba | Semiconductor memory having refresh function |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| US6385120B1 (en) | 2000-12-22 | 2002-05-07 | Texas Instruments Incorporated | Power-off state storage apparatus and method |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| WO2003040441A1 (fr) | 2001-11-05 | 2003-05-15 | Japan Science And Technology Agency | Film mince monocristallin homologue a super-reseau naturel, procede de preparation et dispositif dans lequel est utilise ledit film mince monocristallin |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| US6944045B2 (en) | 2001-11-19 | 2005-09-13 | Rohm Co., Ltd. | Data holding apparatus and data read out method |

| JP4091301B2 (ja) | 2001-12-28 | 2008-05-28 | 富士通株式会社 | 半導体集積回路および半導体メモリ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| WO2003073429A1 (en) | 2002-02-28 | 2003-09-04 | Renesas Technology Corp. | Nonvolatile semiconductor storage device |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| JP3940014B2 (ja) | 2002-03-29 | 2007-07-04 | 富士通株式会社 | 半導体集積回路、無線タグ、および非接触型icカード |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| JP4141767B2 (ja) | 2002-08-27 | 2008-08-27 | 富士通株式会社 | 強誘電体キャパシタを使用した不揮発性データ記憶回路 |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| US6788567B2 (en) | 2002-12-02 | 2004-09-07 | Rohm Co., Ltd. | Data holding device and data holding method |

| WO2004059838A1 (ja) | 2002-12-25 | 2004-07-15 | Matsushita Electric Industrial Co., Ltd. | 不揮発性ラッチ回路及びその駆動方法 |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7064973B2 (en) | 2004-02-03 | 2006-06-20 | Klp International, Ltd. | Combination field programmable gate array allowing dynamic reprogrammability |

| US6972986B2 (en) | 2004-02-03 | 2005-12-06 | Kilopass Technologies, Inc. | Combination field programmable gate array allowing dynamic reprogrammability and non-votatile programmability based upon transistor gate oxide breakdown |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| CN102867855B (zh) | 2004-03-12 | 2015-07-15 | 独立行政法人科学技术振兴机构 | 薄膜晶体管及其制造方法 |

| JP2005323295A (ja) | 2004-05-11 | 2005-11-17 | Asahi Kasei Microsystems Kk | ラッチ回路及びフリップフロップ回路 |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006050208A (ja) | 2004-08-04 | 2006-02-16 | Denso Corp | 電源瞬断対応論理回路 |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US20060095975A1 (en) | 2004-09-03 | 2006-05-04 | Takayoshi Yamada | Semiconductor device |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7374984B2 (en) | 2004-10-29 | 2008-05-20 | Randy Hoffman | Method of forming a thin film component |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| JP5053537B2 (ja) | 2004-11-10 | 2012-10-17 | キヤノン株式会社 | 非晶質酸化物を利用した半導体デバイス |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| RU2358355C2 (ru) | 2004-11-10 | 2009-06-10 | Кэнон Кабусики Кайся | Полевой транзистор |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| CA2585190A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Amorphous oxide and field effect transistor |

| CN101057333B (zh) | 2004-11-10 | 2011-11-16 | 佳能株式会社 | 发光器件 |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI569441B (zh) | 2005-01-28 | 2017-02-01 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI505473B (zh) | 2005-01-28 | 2015-10-21 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100702310B1 (ko) | 2005-07-21 | 2007-03-30 | 주식회사 하이닉스반도체 | 비휘발성 래치 회로 및 이를 포함하는 시스템 온 칩 |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4560502B2 (ja) | 2005-09-06 | 2010-10-13 | キヤノン株式会社 | 電界効果型トランジスタ |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| EP1998373A3 (en) | 2005-09-29 | 2012-10-31 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| JP2007125823A (ja) | 2005-11-04 | 2007-05-24 | Seiko Epson Corp | 液体吐出装置及び液体吐出部の駆動方法 |

| KR20090130089A (ko) | 2005-11-15 | 2009-12-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 다이오드 및 액티브 매트릭스 표시장치 |

| US8004481B2 (en) | 2005-12-02 | 2011-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| JP5364235B2 (ja) | 2005-12-02 | 2013-12-11 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US7915619B2 (en) | 2005-12-22 | 2011-03-29 | Showa Denko K.K. | Light-emitting diode and method for fabrication thereof |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4954639B2 (ja) | 2006-08-25 | 2012-06-20 | パナソニック株式会社 | ラッチ回路及びこれを備えた半導体集積回路 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| JP4297159B2 (ja) | 2006-12-08 | 2009-07-15 | ソニー株式会社 | フリップフロップおよび半導体集積回路 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| JP5508662B2 (ja) | 2007-01-12 | 2014-06-04 | 株式会社半導体エネルギー研究所 | 表示装置 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| WO2008133345A1 (en) | 2007-04-25 | 2008-11-06 | Canon Kabushiki Kaisha | Oxynitride semiconductor |

| JP5294651B2 (ja) | 2007-05-18 | 2013-09-18 | キヤノン株式会社 | インバータの作製方法及びインバータ |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| US8354674B2 (en) | 2007-06-29 | 2013-01-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device wherein a property of a first semiconductor layer is different from a property of a second semiconductor layer |

| US20090002044A1 (en) | 2007-06-29 | 2009-01-01 | Seiko Epson Corporation | Master-slave type flip-flop circuit |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP5178492B2 (ja) | 2007-12-27 | 2013-04-10 | 株式会社半導体エネルギー研究所 | 表示装置および当該表示装置を具備する電子機器 |

| JP5140459B2 (ja) | 2008-02-28 | 2013-02-06 | ローム株式会社 | 不揮発性記憶ゲートおよびその動作方法、および不揮発性記憶ゲート組込み型論理回路およびその動作方法 |

| JP5305696B2 (ja) | 2008-03-06 | 2013-10-02 | キヤノン株式会社 | 半導体素子の処理方法 |

| KR101490112B1 (ko) | 2008-03-28 | 2015-02-05 | 삼성전자주식회사 | 인버터 및 그를 포함하는 논리회로 |

| US8085076B2 (en) | 2008-07-03 | 2011-12-27 | Broadcom Corporation | Data retention flip flop for low power applications |

| JP2010034710A (ja) | 2008-07-25 | 2010-02-12 | Nec Electronics Corp | 半導体集積回路及びその誤動作防止方法 |

| TWI508282B (zh) | 2008-08-08 | 2015-11-11 | Semiconductor Energy Lab | 半導體裝置及其製造方法 |

| JP5537787B2 (ja) | 2008-09-01 | 2014-07-02 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| KR101623958B1 (ko) | 2008-10-01 | 2016-05-25 | 삼성전자주식회사 | 인버터 및 그의 동작방법과 인버터를 포함하는 논리회로 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| JP5781720B2 (ja) | 2008-12-15 | 2015-09-24 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| US8174021B2 (en) | 2009-02-06 | 2012-05-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the semiconductor device |

| TWI489628B (zh) | 2009-04-02 | 2015-06-21 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| TWI476917B (zh) | 2009-04-16 | 2015-03-11 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| WO2011048929A1 (en) | 2009-10-21 | 2011-04-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR20240042253A (ko) | 2009-10-29 | 2024-04-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN102668077B (zh) | 2009-11-20 | 2015-05-13 | 株式会社半导体能源研究所 | 非易失性锁存电路和逻辑电路,以及使用其的半导体器件 |

| CN102714180B (zh) | 2009-12-11 | 2015-03-25 | 株式会社半导体能源研究所 | 非易失性锁存电路和逻辑电路以及使用它们的半导体器件 |

| KR101729933B1 (ko) | 2009-12-18 | 2017-04-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 불휘발성 래치 회로와 논리 회로, 및 이를 사용한 반도체 장치 |

| WO2011078373A1 (en) | 2009-12-25 | 2011-06-30 | Semiconductor Energy Laboratory Co., Ltd. | Memory device, semiconductor device, and electronic device |

| WO2011089847A1 (en) | 2010-01-20 | 2011-07-28 | Semiconductor Energy Laboratory Co., Ltd. | Signal processing circuit and method for driving the same |

| JP2013009285A (ja) | 2010-08-26 | 2013-01-10 | Semiconductor Energy Lab Co Ltd | 信号処理回路及びその駆動方法 |

| US9024317B2 (en) * | 2010-12-24 | 2015-05-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor circuit, method for driving the same, storage device, register circuit, display device, and electronic device |

| TWI621121B (zh) * | 2011-01-05 | 2018-04-11 | Semiconductor Energy Laboratory Co., Ltd. | 儲存元件、儲存裝置、及信號處理電路 |

| TWI525619B (zh) | 2011-01-27 | 2016-03-11 | 半導體能源研究所股份有限公司 | 記憶體電路 |

| KR101899375B1 (ko) | 2011-01-28 | 2018-09-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP5827145B2 (ja) * | 2011-03-08 | 2015-12-02 | 株式会社半導体エネルギー研究所 | 信号処理回路 |

| TWI567735B (zh) | 2011-03-31 | 2017-01-21 | 半導體能源研究所股份有限公司 | 記憶體電路,記憶體單元,及訊號處理電路 |

| US8681533B2 (en) | 2011-04-28 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Memory circuit, signal processing circuit, and electronic device |

| KR101874144B1 (ko) * | 2011-05-06 | 2018-07-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기억 장치 |

| US9257422B2 (en) * | 2011-12-06 | 2016-02-09 | Semiconductor Energy Laboratory Co., Ltd. | Signal processing circuit and method for driving signal processing circuit |

| US9372694B2 (en) | 2012-03-29 | 2016-06-21 | Semiconductor Energy Laboratory Co., Ltd. | Reducing data backup and recovery periods in processors |

| US8873308B2 (en) | 2012-06-29 | 2014-10-28 | Semiconductor Energy Laboratory Co., Ltd. | Signal processing circuit |

| US9054678B2 (en) | 2012-07-06 | 2015-06-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| JP5807076B2 (ja) | 2013-01-24 | 2015-11-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9786350B2 (en) | 2013-03-18 | 2017-10-10 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

| JP6316630B2 (ja) | 2013-03-26 | 2018-04-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6396671B2 (ja) | 2013-04-26 | 2018-09-26 | 株式会社半導体エネルギー研究所 | 半導体装置 |

-

2014

- 2014-08-07 JP JP2014160945A patent/JP6329843B2/ja not_active Expired - Fee Related

- 2014-08-18 US US14/461,564 patent/US9608005B2/en active Active

-

2017

- 2017-03-27 US US15/469,721 patent/US20170263609A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20170263609A1 (en) | 2017-09-14 |

| JP2015062218A (ja) | 2015-04-02 |

| US9608005B2 (en) | 2017-03-28 |

| US20150048362A1 (en) | 2015-02-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6290722B2 (ja) | プログラマブルロジックデバイス | |

| JP6329843B2 (ja) | 半導体装置 | |

| JP6368155B2 (ja) | プログラマブルロジックデバイス | |

| US9225336B2 (en) | Programmable logic device and semiconductor device | |

| JP6457239B2 (ja) | 半導体装置 | |

| JP6405097B2 (ja) | 半導体装置 | |

| JP6408245B2 (ja) | 半導体装置 | |

| US9305630B2 (en) | Semiconductor device and method for driving the same | |

| US20160217848A1 (en) | Semiconductor device, electronic component, and electronic device | |

| US9647665B2 (en) | Semiconductor device and electronic device | |

| JP2014199707A (ja) | 半導体装置の駆動方法 | |

| JP2014199708A (ja) | 半導体装置の駆動方法 | |

| JP2016115386A (ja) | 半導体装置、及び電子機器 | |

| JP6392603B2 (ja) | 半導体装置 | |

| JP6396671B2 (ja) | 半導体装置 | |

| JP6262574B2 (ja) | プログラマブルロジックデバイス | |

| JP6280794B2 (ja) | 半導体装置及びその駆動方法 | |

| JP2015118724A (ja) | 半導体装置及び半導体装置の駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170706 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180327 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180329 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180423 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6329843 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |