JP3950988B2 - アクティブマトリックス電界発光素子の駆動回路 - Google Patents

アクティブマトリックス電界発光素子の駆動回路 Download PDFInfo

- Publication number

- JP3950988B2 JP3950988B2 JP2001381400A JP2001381400A JP3950988B2 JP 3950988 B2 JP3950988 B2 JP 3950988B2 JP 2001381400 A JP2001381400 A JP 2001381400A JP 2001381400 A JP2001381400 A JP 2001381400A JP 3950988 B2 JP3950988 B2 JP 3950988B2

- Authority

- JP

- Japan

- Prior art keywords

- reference current

- transistor

- voltage terminal

- unit

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

Description

【発明の属する技術分野】

本発明はディスプレイ素子の駆動回路に関し、特に、デジタル信号で駆動可能なアクティブマトリックス電界発光素子(AMELD:Active Matrix Electroluminescence Device)の駆動回路に関する。

【0002】

【従来の技術】

前記AMELDは、板状の発光層の両面に電極をマトリックス状に形成された電界発光を用いた発光体であり、大きく画面表示部と駆動回路部とに区分される。AMELDは、広い視野角、高速応答性、高コントラスト、低電圧駆動、低電力消費などの優れた特徴を有しており、薄くて軽く、色感が優れているため、最近の大型化の傾向に対応することができる次世代の平面表示素子である。

【0003】

一方、ディスプレイ素子は、カラー表示のような膨大な量の情報を表示するために、白と黒状態の間に幾つかの中間段階を更に有するが、これを実現するためには、液晶に印加される電圧の強度を調節する方法と電流の強度を調節する方法とがある。

2つの方法の内、電圧を調節する方法は、電圧によって光透過量が変化する特性を用いて階調を調節するものであって、外部から印加された電圧を調節して、データ電圧による画面の明るさの変化を液晶のしきい値電圧に対するパラメータとして抽出する。ここで、前記しきい値電圧は、電圧を漸増させた場合に透過率の変化が本格的に起こり始める電圧を云い、前記しきい値電圧が大きいと、液晶に印加すべき電圧も大きくなり、結局、電力消耗を増加させる要因になり得る。

【0004】

さらに、電圧に対する透過度の関係は非線形なので、所望の透過度を得るための電圧調節には困難が伴なう。

即ち、実際の画像を実現する際には、何段階かの印加電圧によって透過率の階調を制御することになるが、電圧を一定間隔の段階に分ける場合、透過率の非線形性のため、透過率にむらを生じる。つまり、印加電圧を一定刻みの段階にしても、透過率の刻み幅は不均一になるので、繊細な階調表示が難しくなり、結果的に、画像の繊細さが失われる。

【0005】

反面、電流の強度に対する透過度の関係は線形性を有するので、電流の調節方法は電圧の調節方法よりはるかに正確且つ容易である。

【0006】

以下に、添付の図面を参照して一般的なAMELD駆動回路の構造を概略的に説明する。

【0007】

図1は一般的なAMELD駆動回路の構造を示す概略図である。

一般的なAMELD駆動回路は、図1に示すように、ディスプレイに電源を供給する電源供給部10と、信号源の外部のマイクで制御部と映像信号をインタフェースするインタフェース部11と、該インタフェース部11を介して伝送された映像信号を格納するメモリ部12と、該メモリ部12に格納した映像信号を入力され、前記電源供給部10から入力される電源をディスプレイパネル18のデータ信号で出力するソースドライバ15と、ディスプレイパネル18の各画素にデータ信号が印加され得るようにTFTをオンさせる走査信号を出力するゲートドライバ16と、前記ソースドライバ及びゲートドライバで必要な各種のタイミング信号を発生し、制御するタイミング制御部17とから構成されている。

前記信号源としてはコンピュータや動画像ディスプレイのためのレーザディスクプレイヤーなどがある。

【0008】

【発明が解決しようとする課題】

本発明は電流駆動用ICで集積化が可能であり、nビットのデジタル信号を受けて、各RGBチャネル別の出力電流値の調節の可能なAMELDの駆動回路を提供することを目的とする。

【0009】

【課題を解決するための手段】

上記の目的を達成するために、本発明のAMELDの駆動回路は、データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、前記データドライバは仮格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号に出力する複数のデジタル−アナログコンバータとを備えて構成されることを特徴とする。

【0010】

即ち、n個の基準電流値を仮に選定して、nビットのデジタル入力信号に従って選択/非選択して所望のグレーを表現し、電圧が一定に保持された電圧端と各RGBチャネル別に電圧が変化する電圧端を備えて各カラー別の出力電流値を調節することを技術的特徴としている。

【0011】

【発明の実施の形態】

以下、本発明の実施形態によるAMELDの駆動回路を添付の図面に沿って詳細に説明する。

【0012】

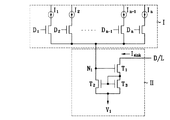

図2は一般的なAMELDのデータドライバの構成図である。

図2を参考にしてAMELDのデータドライバに対して説明すると、データクロック(Data Clock)により外部から入力されたRGBのデジタル信号を仮に格納するシフトレジスタ部と、前記シフトレジスタ部から印加されたRGBのデジタル信号を制御信号によりラッチするラッチ部と、前記ラッチ部からラッチしたRGBのデジタル信号(D1〜Dn)を受けて、RGBのアナログ信号に変換させるデジタル−アナログコンバータ(以下、DAC)部から構成されている。

この場合、前記DAC部は複数個の電流DACから構成され、それぞれの電流DACはリファレンスブロックからのリファレンス電流源(I1〜In)を複数個のスイッチ素子の制御信号にして、前記RGBのデジタル信号(D1〜Dn)を仮に組み合わせて特定のレベルの電流を出力することにより、各画素に接続されるデータラインに特定のシンク電流を送り出す。

【0013】

第1,第2実施形態

図3は本発明の第1実施形態による駆動回路図であり、図4は本発明の第2実施形態による駆動回路図である。

本発明の第1実施形態によるAMELDの駆動回路は複数個のリファレンス電流源(I1,I2,...,In)を仮に組み合わせて特定のレベルのリファレンス電流を出力するリファレンス電流出力部Iと、リファレンス電流出力部から出力される特定のレベルのリファレンス電流を受けてシンク電流のレベルを調整するシンク電流調節部(II)とから構成されている。

この場合、前記リファレンス電流出力部(I)は入力端にそれぞれ互いに異なるレベルの電流(I1,I2,...,In)が印加され、その出力端は共通に接続され制御信号(D1,D2,...,Dn)によってその出力レベルが決定される複数個のスイッチ素子から構成されている。ここで、前記スイッチ素子は薄膜トランジスタである。

【0014】

つぎに、前記シンク電流調節部(II)は第1,第2電圧端(V1,V2)と、カレントミラー型を成す多数のトランジスタとから構成されている。前記トランジスタには前記リファレンス電流出力部(I)の出力端と第1電圧端(V1)との間に接続された第1トランジスタ(T1)と、第2電圧端(V2)とデータラインに接続される第2トランジスタ(T2)があり、前記第1トランジスタ(T1)のゲートと第2トランジスタ(T2)のゲートは共通に前記リファレンス電流の出力端と接続される。

【0015】

前記デジタル駆動回路で第1電圧端(V1)は一定に保持された電圧の一例として主に接地電圧を用いることができるが、ポジティブ電圧又はネガティブ電圧を用いることもできる。つぎに、第2電圧端(V2)はRGB別に他のレベルの特定の電圧を印加するが、このような方法で電圧レベルを調節すると、シンク電流のレベルが増加又は減少することにより、データライン(D/L)に特定の電圧レベルが伝達される。

ここで、基準電流I1,I2,....In−1,Inのレベルは仮に設定可能であり、最も簡単な例としてバイナリウェートを与える。即ち、「In=2 In―1=22 In―2 … =2n−2I2=2n−1I1」式を満足するように電流のレベルを設定する。

その他にランマコレクション(ramma correction)でリファレンス電流のレベルを設定することも可能である。

制御信号のD1,D2,....,Dnは入力されるアナログ信号に対して変換されたnビットを構成するデジタル入力信号である。

【0016】

一方、第2実施形態は、図4に示すように、前記第1実施形態におけるリファレンス電流出力端(I)と第1トランジスタ(T1)の入力端との間に電流遮断スイッチ(SI)を更に設けることを特徴とする。

【0017】

第3,第4実施形態

図5は本発明の第3実施形態による駆動回路図であり、図6は本発明の第4実施形態による駆動回路図である。

本発明の第3実施形態によるAMELD駆動回路図もリファレンス電流出力部(I)とシンク電流調節部(II)とから構成されている。

前記リファレンス電流出力部(I)は入力端にそれぞれ互いに異なるレベルの電流(I1,I2,...,In)が印加され、その出力端は共通に接続され、制御信号(D1,D2,....,Dn)によってその出力レベルが決定される複数個のスイッチ素子から構成されている。ここで、前記スイッチ素子は薄膜トランジスタである。

【0018】

前記シンク電流調節部(II)は第1電圧端と、前記リファレンス電流出力部の出両端と前記第1電圧端(V1)との間に直列に接続された第1トランジスタ(T1)と固定抵抗(Rs)と、前記第1電圧端(V1)とデータライン(D/L)との間に接続された第2トランジスタとから構成され、前記第1トランジスタと第2トランジスタのゲートは共通に前記リファレンス電流出力端と接続されている。

【0019】

より詳細に説明すると、前記複数個の制御信号、即ち、デジタル入力信号(D1,D2,....,Dn)によってリファレンス電流源(I1,I2,...,In)のレベルが選択的に制御、組み合わせられて前記リファレンス電流出力部に出力される特定のレベルのリファレンス電流が第1,第2トランジスタのゲートに入力され、第1電圧端から印加される電圧を制御して、データラインから流れ込むシンク電流値を調節する。この場合、前記第1電圧端から印加される電圧は接地電圧、ポジティブ電圧又はネガティブ電圧のうち何れかから設定する。

【0020】

固定抵抗はR,G,B別に違うレベルの電圧に設定して各R,G,Bチャネルを駆動する。

即ち、リファレンス電流出力部(I)から出力される同一な特定レベルのリファレンス電流で各カラー別の出力シンク電流値を調節できるので、AMELD駆動回路の集積化が可能である。

以上で前記リファレンス電流源のレベルは仮設定し、例えば、「In=2In―1= … =2n−2I2=2n−1I1」式を満足するように定められる。

【0021】

一方、第4実施形態は、図6に示すように、前記第3実施形態におけるリファレンス電流出力端(I)と第1トランジスタ(T1)の入力端との間に電流遮断スイッチ(S1)を更に設けることを特徴とする。

【0022】

第5,第8実施形態

図7は本発明の第5実施形態による駆動回路図である。

本発明の第5実施形態によるAMELD駆動回路図もリファレンス電流出力部(I)とシンク電流調節部(II)とから構成されている。

前記リファレンス電流出力部(I)は入力端にそれぞれ互いに違うレベルのリファレンス電流(I1,I2,...,In)が印加され、その出力端は共通に接続され、制御信号(D1,D2,....,Dn)によってその出力レベルが決定される複数個のスイッチ素子から構成されている。ここで、前記スイッチ素子は薄膜トランジスタである。

【0023】

前記シンク電流調節部(II)は第1電圧端(V1)と、前記リファレンス電流出力部の出力端と前記第1電圧端(V1)との間に直列に接続された可変抵抗(Rr),第1トランジスタ(T1),及び固定抵抗(Rs)と、前記第1電圧端(V1)とデータライン(D/L)との間に接続された第2トランジスタ(T2)及び第3トランジスタ(T3)とから構成され、前記第3トランジスタのゲートは、前記可変抵抗(Rr)と第1トランジスタのドレインが接続された第1ノード(N1)との間に接続され、前記第1,第2トランジスタのゲートは、第2トランジスタのソースと第3トランジスタのドレインが接続された第2ノード(N2)に共通に接続される。

【0024】

前記可変抵抗(Rr)はリファレンス電流出力部からデータ電圧が印加されるときパネル内に全てのTFTが同一な特性を有し得るようにその抵抗値が調整される。

【0025】

前記第1,第3トランジスタはカレントリピーター(current repeater)を構成して、データライン(D/L)から第1電圧端の側に流れる電流量が第1ノードに供給される電流量に従って変化する。すなわち、データラインから第3,第2トランジスタを経由して、第1電圧端の側に流れる逆方向電流がリファレンス電流出力端の電圧に従って変化する。

【0026】

前記第1,第2トランジスタはカレントミラーを形成するため、データラインから第1電圧端の側に供給される電流量は第3トランジスタに流れる電流量により定められる。

【0027】

前記固定抵抗の抵抗値はR,G,Bによって異なるように設定される。すなわち、同一な画素電圧が印加されたとき、データラインから第1電圧端の側に流れる電流量は固定抵抗の抵抗値により定められる。

【0028】

かかる固定抵抗は第8実施形態を示す図10のように、第2トランジスタと第1電圧端との間に接続することもできる。

前記固定抵抗により、第1,第2トランジスタのゲートに入力され、第1電圧端から印加される電圧を制御して、データラインから流れるシンク電流値を調節する。

この場合、前記第1電圧端に印加される電圧は接地電圧、ポジティブ電圧又はネガティブ電圧のうち何れかから設定される。

すなわち、リファレンス電流出力部(I)から出力される同一な特定のレベルのリファレンス電流で各カラー別の出力シンク電流値を調節できるので、AMELD駆動回路の集積化が可能である。また、可変抵抗値を調節して全体パネルの明るさを調節することができる。

【0029】

第6,第7実施形態

図8は本発明の第6実施形態による駆動回路図であり、図9は本発明の第7実施形態による駆動回路図である。

本発明の実施形態によるAMELDは、図8に示すように、複数のリファレンス電流源を仮に組み合わせて特定のレベルのリファレンス電流を出力するリファレンス電流出力部(I)と、そのリファレンス電流出力部(I)から出力されるリファレンス電流を受けてシンク電流のレベルを調整するシンク電流調節部(II)とから構成されている。

前記リファレンス電流出力部(I)は、入力端にそれぞれ互いに異なるレベルのリファレンス電流(I1,I2,...,In)が印加され、その出力端が共通に接続されてnビットの制御信号(D1,D2,....,Dn)によってその出力レベルが決定される複数のスイッチ素子から構成されている。ここで、前記スイッチ素子は薄膜トランジスタである。

【0030】

前記シンク電流調節部(II)は第1電圧端(V1)と、固定抵抗(Rs)と、前記リファレンス電流出力部(I)の出力端と前記第1電圧端(V1)との間に接続された第1トランジスタ(T1)及び前記固定抵抗(Rs)と直列に接続され、データラインと前記第1電圧端(V1)に接続された第2トランジスタ(T2)を含むカレントミラー構造から構成されている。但し、前記第1トランジスタ(T1)と第2トランジスタ(T2)のゲートは共通に前記リファレンス電流出力部の出力端と接続される。

【0031】

前記固定抵抗(Rs)は第1電圧端(V1)と直接に接続されるが、前記第1電圧端(V1)を一定の電圧で固定させ、各RGB別に抵抗値が変化する固定抵抗(Rs)を使用して、各RGBチャネル別の出力シンク電流を調節する。

【0032】

つぎに、前記リファレンス電流出力部(I)からnビットの制御信号(D1,D2,....,Dn)によってn個のリファレンス電流源が選択又は非選択され、リファレンス電流出力部から統合的に出力されるので、R,G,Bの間の所望の中間階調を表現することができる。

例えば、6ビットの駆動回路を使用すると64階調を作ることができる。フルカラーを要求するモニターでは256階調になると1600万色以上が実現可能である。

【0033】

一方、第7実施形態は、図9に示すように、前記第6実施形態におけるリファレンス電流出力端(I)と第1トランジスタ(T1)の入力端との間に電流遮断スイッチ(S1)を更に設けたことを特徴とする。

【0034】

第9,第10,第11,第12,第13実施形態

図11は本発明の第9実施形態による駆動回路図であり、図12は本発明の第10実施形態による駆動回路図である。

本発明の実施形態によるAMELDは、図11に示すように、特定のレベルのリファレンス電流を出力するリファレンス電流出力部(I)と、シンク電流のレベルを調整するシンク電流調節部(II)とから構成されている。

前記リファレンス電流出力部(I)は、入力端にそれぞれ互いに異なるレベルのリファレンス電流(I1,I2,...,In)が印加され、その出力端が共通に接続されてnビットの制御信号(D1,D2,....,Dn)によってリファレンス電流が組み合わされ特定の出力レベルが決定されるn個のスイッチ素子から構成されている。この場合、前記スイッチ素子は薄膜トランジスタである。

【0035】

前記シンク電流調節部(II)は第1電圧端(V1)と、第1,第2トランジスタ(T1,T2)と、前記リファレンス電流出力部(I)の出力端と前記第1電圧端(V1)との間に直列に接続された第1,第3トランジスタ(T1,T3)及び前記第1電圧端(V1)とデータラインとの間に直列に接続される第2,第4トランジスタ(T2,T4)から構成され、前記第3トランジスタと第4トランジスタのゲートは共通に前記リファレンス電流出力部(I)の出力端の第1ノード(N1)に接続され、前記第1トランジスタのゲートと第2トランジスタのゲートは外部から一定の電圧で制御する特定の電圧Vbiasに共通に接続される。前記Vbiasは通常3.3Vにする。

前記第1電圧端はRGB別に出力されるシンク電流のレベルを調節するために外部から制御して印加する電圧である。

【0036】

一方、第10実施形態は、図12に示すように、前記第9実施形態におけるリファレンス電流出力端(I)と第1ノード(N1)との間に電流遮断スイッチ(S1)を更に設けたことを特徴とする。

【0037】

第11実施形態は、図13に示すように、前記第9実施形態におけるリファレンス電流出力端(I)と第1ノード(N1)との間に可変抵抗(Rr)を更に設け、第3,第4トランジスタに共通に接続された第1電圧端を分割して第3トランジスタには第1電圧端を接続し、第4トランジスタには第2電圧端を接続する。ここで、前記第1電圧端(V1)は一定の固定値として主に接地電圧を用いるが、ポジティブ電圧又はネガティブ電圧を用いることもでき、前記第2電圧端(V2)はRGB別に違うレベルの特定の電圧を印加するが、このような方法で電圧レベルを調節すると、シンク電流(Isink)のレベルが増加又は減少することによりデータラインに特定の電圧レベルが伝達される。

【0038】

第12実施形態は、図14に示すように、前記第9実施形態におけるリファレンス電流出力端(I)と第1ノード(N1)との間に可変抵抗(Rr)を更に設け、第3トランジスタ(T3)と第1電圧端(V1)との間に固定抵抗(Rs)を更に設けた。ここで、固定抵抗の抵抗値はR,G,Bにより異なるように設定される。すなわち、同一な画素電圧が印加されたとき、データラインから第1電圧端の側に流れる電流量は固定抵抗の抵抗値により決定される。これにより同一なデジタル入力信号を各カラー別のシンク電流値で調節することができる。

【0039】

前記第12実施形態における固定抵抗は第13実施形態を示す図15のように、第4トランジスタと第1電圧端との間に接続することもできる。

【0040】

第14,第15実施形態

図16は本発明の第14実施形態による駆動回路図であり、図17は本発明の第15実施形態による駆動回路図である。

本発明の実施形態によるAMELDは、図14に示すように、リファレンス電流出力部(I)と、リファレンス電流出力部から出力されるリファレンス電流を受けてシンク電流のレベルを調整するシンク電流調節部(II)とから構成されている。

【0041】

前記リファレンス電流出力部(I)は、入力端にそれぞれ互いに異なるレベルのn個のリファレンス電流(I1,I2,...,In)が印加され、その出力端が共通に接続されて制御信号(D1,D2,....,Dn)によって前記リファレンス電流が組み合わされ出力レベルが決定されるn個のスイッチ素子から構成されている。

ここで、前記スイッチ素子は薄膜トランジスタである。

【0042】

前記シンク電流調節部(II)は第1電圧端(V1)と、データラインと接続された第1トランジスタ(T1)と、前記リファレンス電流出力部(I)の出力端と前記第1電圧端(V1)との間に接続された第2トランジスタ(T2)と、前記第1電圧端(V1)とデータラインとの間に直列に接続される第1,第3トランジスタ(T1,T3)とから構成され、前記第2トランジスタ(T2)と第3トランジスタ(T3)のゲートは共通に第1トランジスタ(T1)のドレインと接続され、前記第1トランジスタのゲートはリファレンス電流出力部(I)の出力端と第1トランジスタ(T1)の入力端との間の第1ノード(N1)に接続される。

【0043】

前記構造で、同一なデジタル入力信号下で第1電圧端にRGB別に互いに異なる電圧を印加することだけで各RGB別のシンク電流値を調節できるので、電流駆動用ICで集積化が可能となる。

【0044】

一方、第15実施形態は、図17に示すように、前記第14実施形態におけるリファレンス電流出力端(I)と第1ノード(N1)との間に電流遮断スイッチ(S1)を更に設けたことを特徴とする。

【0045】

以上の第2,4,7,10,15実施形態における電流遮断スイッチ(S1)はリファレンス電流出力部(I)とシンク電流調節部(II)とを電気的に分離するために構成したもので、D1,D2,....,Dnの制御信号によってスイッチ素子がオン又はオフ時に発生するノイズを減少させ、電流の消費を防止するためのものである(図4,6,9,12,17参照)。

【0046】

ところが、本発明でnビットのデジタル入力信号、即ち、制御信号によってスイッチ素子(S1)がオン又はオフ時に生じるスイッチノイズは極く小さいので、これを無視した構造も可能である。前記スイッチ素子を無視した構造を説明したのが第1,3,6,9,14実施形態である。

【0047】

【発明の効果】

以上説明したように、本発明によるAMELDの駆動回路によれば、同一なデジタル入力信号で各RGB別に駆動が可能なので、電流駆動用ドライバICで集積化が可能である。

また、デジタル入力信号がオン又はオフする時に発生するノイズが小さいので、スイッチノイズ減少のために導入されるスイッチ素子を排除することが可能である。

【図面の簡単な説明】

【図1】 一般的なAMELD駆動回路の構造を示す概略図である。

【図2】 一般的なAMELDのデータ駆動回路の構成図である。

【図3】 本発明の第1実施形態による駆動回路図である。

【図4】 本発明の第2実施形態による駆動回路図である。

【図5】 本発明の第3実施形態による駆動回路図である。

【図6】 本発明の第4実施形態による駆動回路図である。

【図7】 本発明の第5実施形態による駆動回路図である。

【図8】 本発明の第6実施形態による駆動回路図である。

【図9】 本発明の第7実施形態による駆動回路図である。

【図10】 本発明の第8実施形態による駆動回路図である。

【図11】 本発明の第9実施形態による駆動回路図である。

【図12】 本発明の第10実施形態による駆動回路図である。

【図13】 本発明の第11実施形態による駆動回路図である。

【図14】 本発明の第12実施形態による駆動回路図である。

【図15】 本発明の第13実施形態による駆動回路図である。

【図16】 本発明の第14実施形態による駆動回路図である。

【図17】 本発明の第15実施形態による駆動回路図である。

【符号の説明】

I1,I2,...,In:リファレンス電流源

D1,D2,...,Dn:デジタル入力信号

V1,V2:第1,第2電圧端

Rs:固定抵抗

Rr:可変抵抗

S1:電流遮断スイッチ

Isink:シンク電流

T1,T2:第1,第2トランジスタ

Claims (26)

- データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は第1電圧端と、第2電圧端と、前記リファレンス電流出力部の出力端により共通に制御される前記リファレンス電流出力部の出力端と前記第1電圧端との間に接続された第1トランジスタ及び、前記第2電圧端とデータ配線との間に接続される第2トランジスタが成すカレントミラー構造であり、第1トランジスタと第2トランジスタのゲートはリファレンス電流の出力端と接続されて構成され、

前記第1電圧端は一定の電圧に保持され、第2電圧端はRGB別に特定の電圧を外部から印加されて、RGB別にシンク電流のレベルを調節することを特徴とするAMELDの駆動回路。 - データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は第1電圧端と、第2電圧端と、前記リファレンス電流出力部の出力端により共通に制御される前記リファレンス電流出力部の出力端と前記第1電圧端との間に接続された第1トランジスタ及び、前記第2電圧端とデータ配線との間に接続される第2トランジスタが成すカレントミラー構造であり、第1トランジスタと第2トランジスタのゲートはリファレンス電流の出力端と接続され、前記リファレンス電流出力端と第1トランジスタとの間に電流遮断スイッチが更に設けられた構成であることを特徴とするAMELDの駆動回路。 - データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

該デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流の調節部は第1電圧端と、可変抵抗と、前記リファレンス電流出力部の出力端によって共通に制御される前記リファレンス電流出力部の出力端と前記第1電圧端との間で前記可変抵抗と直列に接続された第1トランジスタ及び、前記第1電圧端とデータ配線との間に接続された第2トランジスタが成すカレントミラー構造から構成され、第1トランジスタと第2トランジスタのゲートはリファレンス電流の出力端と接続され、さらに前記可変抵抗は前記第1電圧端と前記第1トランジスタとの間に接続され、特定のリファレンス電流下でRGB別にその抵抗値が変化するものであることを特徴とするAMELDの駆動回路。 - データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

該デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流の調節部は第1電圧端と、固定抵抗と、前記リファレンス電流出力部の出力端によって共通に制御される前記リファレンス電流出力部の出力端と前記第1電圧端との間で前記固定抵抗と直列に接続された第1トランジスタ及び、前記第1電圧端とデータ配線との間に接続された第2トランジスタが成すカレントミラー構造から構成され、第1トランジスタと第2トランジスタのゲートはリファレンス電流の出力端と接続され、前記リファレンス電流出力端と第1トランジスタとの間に電流遮断スイッチが更に構成されることを特徴とするAMELDの駆動回路。 - データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は第1電圧端と、可変抵抗と、リファレンス電流出力部の出力端に共通に制御されるリファレンス電流出力部の出力端と前記第1電圧端との間に接続された第1トランジスタ及び、前記第1電圧端とデータ配線との間で前記可変抵抗と直列に接続された第2トランジスタが成すカレントミラー構造から構成され、第1トランジスタと第2トランジスタのゲートはリファレンス電流の出力端と接続され、さらに前記可変抵抗は前記第1電圧端と前記第2トランジスタとの間に接続され、特定のリファレンス電流下でRGB別にその抵抗値が変化するものであることを特徴とするAMELDの駆動回路。 - データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は第1電圧端と、固定抵抗と、リファレンス電流出力部の出力端に共通に制御されるリファレンス電流出力部の出力端と前記第1電圧端との間に接続された第1トランジスタ及び、前記第1電圧端とデータ配線との間で前記固定抵抗と直列に接続された第2トランジスタが成すカレントミラー構造から構成され、第1トランジスタと第2トランジスタのゲートはリファレンス電流の出力端と接続され、前記リファレンス電流の出力端と第1トランジスタとの間に電流遮断スイッチが更に構成されることを特徴とするAMELDの駆動回路。 - データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は第1電圧端と、第1,第2トランジスタと、前記リファレンス電流出力部の出力端に共通に制御される前記リファレンス電流出力部の出力端と前記第1電圧端との間で第1トランジスタと直列に接続された第3トランジスタ及び、前記第1電圧端とデータ配線との間で第2トランジスタと直列に接続された第4トランジスタが成すカレントミラー構造から構成され、第1トランジスタと第2トランジスタのゲートはVbiasに接続されることを特徴とするAMELDの駆動回路。 - 前記第1トランジスタのゲートと第2トランジスタのゲートは、共通にVbiasに接続されることを特徴とする請求項7記載のAMELDの駆動回路。

- 前記第1電圧端はRGB別にシンク電流を調節するために、外部から制御して印加される電圧であることを特徴とする請求項7記載のAMELDの駆動回路。

- 前記Vbiasは一定に外部から印加される電圧であることを特徴とする請求項8に記載のAMELDの駆動回路。

- 前記リファレンス電流の出力端と第1トランジスタとの間に電流遮断スイッチが更に構成されることを特徴とする請求項7記載のAMELDの駆動回路。

- データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は第1電圧端と、第1トランジスタと、前記第1トランジスタのドレインの出力値によって共通に制御されるリファレンス電流出力部の出力端と前記第1電圧端との間に接続された第2トランジスタ及び、前記第1電圧端とデータ配線との間で前記第1トランジスタと直列に接続された第3トランジスタが成すカレントミラー構造から構成され、第1トランジスタのゲートはリファレンス電流出力部の出力端に接続されることを特徴とするAMELDの駆動回路。 - 前記第1トランジスタのゲートはリファレンス電流出力部の出力端に接続されることを特徴とする請求項12記載のAMELDの駆動回路。

- 前記第1電圧端は各RGB別に外部から特定の電圧を印加されることを特徴とする請求項12記載のAMELDの駆動回路。

- 前記リファレンス電流の出力端と第1トランジスタとの間に電流遮断スイッチが更に構成されることを特徴とする請求項10記載のAMELDの駆動回路。

- データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は、

第1電圧端と、

前記リファレンス電流出力部の出力端と前記第1電圧端との間に直列に接続された可変抵抗及び第1トランジスタと、

前記データラインと前記第1電圧端との間に直列に接続され、そのゲートが前記可変抵抗と第1トランジスタとの間に接続される第3トランジスタと、

前記第3トランジスタと前記第1電圧端との間に直列に接続され、そのゲートが前記第1トランジスタのゲートと共通に前記第3トランジスタのドレインに接続される第2トランジスタと、

を含むことを特徴とするAMELDの駆動回路。 - 前記第1電圧端は各R,G,B別に外部から特定の電圧を印加されることを特徴とする請求項16記載のAMELDの駆動回路。

- 前記第1トランジスタと第1電圧端との間にR,G,B別に特定の抵抗値で設定された固定抵抗が更に接続されていることを特徴とする請求項16記載のAMELDの駆動回路。

- 前記第2トランジスタと第1電圧端との間にR,G,B別に特定の抵抗値で設定された固定抵抗が更に接続されていることを特徴とする請求項16記載のAMELDの駆動回路。

- データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は、

第1、第2電圧端と、

前記リファレンス電流出力部の出力端と前記第1電圧端との間に直列に接続された可変抵抗、第1トランジスタ、及び第3トランジスタと、

前記データラインと前記第2電圧端との間に直列に接続され、そのゲートが前記第1トランジスタのゲートと共通にVbiasに接続される第2トランジスタと、

前記第2トランジスタと前記第2電圧端との間に直列に接続され、そのゲートが前記第3トランジスタのゲートと共通に前記可変抵抗と第1トランジスタとの間に接続される第4トランジスタと、

を含むことを特徴とするAMELDの駆動回路。 - 前記Vbiasは一定に外部から印加される電圧であることを特徴とする請求項20記載のAMELDの駆動回路。

- 前記第1電圧端は仮電圧に保持され、第2電圧端はR,G,B別に特定の電圧を外部から印加され、R,G,B別にシンク電流のレベルを調節することを特徴とする請求項20記載のAMELDの駆動回路。

- データ信号と走査信号をパネルの各画素に伝送するデータドライバとゲートドライバを含むAMELDの駆動回路において、

前記データドライバはシフトレジスタに格納された制御信号をラッチするラッチ部と、ラッチした制御信号によって特定のレベルのリファレンス電流をRGB別のデータ信号線に出力する複数のデジタル−アナログコンバータとを備えており、

前記デジタル−アナログコンバータは、特定のレベルのリファレンス電流を出力するリファレンス電流出力部と、該リファレンス電流出力部から出力される特定のリファレンス電流を受けて、RGB別にデータラインへ流れるシンク電流のレベルを調節するシンク電流調節部とから構成され、

前記シンク電流調節部は、

第1電圧端と、

前記リファレンス電流出力部の出力端と前記第1電圧端との間に直列に接続された可変抵抗、第1トランジスタ、及び第3トランジスタと、

前記データラインと前記第1電圧端との間に直列に接続され、そのゲートが前記第1トランジスタのゲートと共通にVbiasに接続される第2トランジスタと、

前記第2トランジスタと前記第1電圧端との間に直列に接続され、そのゲートが前記第3トランジスタのゲートと共通に前記可変抵抗と第1トランジスタとの間に接続される第4トランジスタと、

を含むことを特徴とするAMELDの駆動回路。 - 前記第3トランジスタと第1電圧端との間にR,G,B別に特定の抵抗値で設定された固定抵抗が更に接続されていることを特徴とする請求項23記載のAMELDの駆動回路。

- 前記第4トランジスタと第1電圧端との間にR,G,B別に特定の抵抗値で設定された固定抵抗が更に接続されていることを特徴とする請求項23記載のAMELDの駆動回路。

- 前記第1電圧端は、R,G,B別にシンク電流を調節するために外部から制御して印加される電圧であることを特徴とする請求項23記載のAMELDの駆動回路。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR2000-77083 | 2000-12-15 | ||

| KR1020000077083A KR100796480B1 (ko) | 2000-12-15 | 2000-12-15 | 액티브 매트릭스 전계발광소자의 구동회로 |

| KR2000-81415 | 2000-12-23 | ||

| KR1020000081415A KR100675318B1 (ko) | 2000-12-23 | 2000-12-23 | 일렉트로 루미네센스 패널의 구동회로 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002244618A JP2002244618A (ja) | 2002-08-30 |

| JP3950988B2 true JP3950988B2 (ja) | 2007-08-01 |

Family

ID=26638627

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001381400A Expired - Lifetime JP3950988B2 (ja) | 2000-12-15 | 2001-12-14 | アクティブマトリックス電界発光素子の駆動回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6943760B2 (ja) |

| JP (1) | JP3950988B2 (ja) |

Families Citing this family (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100382130C (zh) * | 2001-08-29 | 2008-04-16 | 日本电气株式会社 | 用于驱动电流负载器件的半导体器件及提供的电流负载器件 |

| US7180479B2 (en) | 2001-10-30 | 2007-02-20 | Semiconductor Energy Laboratory Co., Ltd. | Signal line drive circuit and light emitting device and driving method therefor |

| US7576734B2 (en) * | 2001-10-30 | 2009-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Signal line driving circuit, light emitting device, and method for driving the same |

| US6933527B2 (en) * | 2001-12-28 | 2005-08-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and semiconductor device production system |

| JP2003195810A (ja) * | 2001-12-28 | 2003-07-09 | Casio Comput Co Ltd | 駆動回路、駆動装置及び光学要素の駆動方法 |

| JP4011344B2 (ja) * | 2001-12-28 | 2007-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| EP1326273B1 (en) * | 2001-12-28 | 2012-01-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2003204067A (ja) * | 2001-12-28 | 2003-07-18 | Semiconductor Energy Lab Co Ltd | 表示装置およびそれを用いた電子機器 |

| US6841797B2 (en) | 2002-01-17 | 2005-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device formed over a surface with a drepession portion and a projection portion |

| JP2003255900A (ja) * | 2002-02-27 | 2003-09-10 | Sanyo Electric Co Ltd | カラー有機el表示装置 |

| JP3923341B2 (ja) | 2002-03-06 | 2007-05-30 | 株式会社半導体エネルギー研究所 | 半導体集積回路およびその駆動方法 |

| US6847050B2 (en) * | 2002-03-15 | 2005-01-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor element and semiconductor device comprising the same |

| US6930326B2 (en) * | 2002-03-26 | 2005-08-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor circuit and method of fabricating the same |

| JP2003308042A (ja) * | 2002-04-17 | 2003-10-31 | Hitachi Ltd | 画像表示装置 |

| JP3918642B2 (ja) * | 2002-06-07 | 2007-05-23 | カシオ計算機株式会社 | 表示装置及びその駆動方法 |

| KR100507551B1 (ko) * | 2002-06-20 | 2005-08-26 | 로무 가부시키가이샤 | 능동 매트릭스형 유기 el 패널의 구동 회로 및 이 구동회로를 이용한 유기 el 디스플레이 장치 |

| JP4610843B2 (ja) * | 2002-06-20 | 2011-01-12 | カシオ計算機株式会社 | 表示装置及び表示装置の駆動方法 |

| JP3970110B2 (ja) * | 2002-06-27 | 2007-09-05 | カシオ計算機株式会社 | 電流駆動装置及びその駆動方法並びに電流駆動装置を用いた表示装置 |

| JP4103500B2 (ja) * | 2002-08-26 | 2008-06-18 | カシオ計算機株式会社 | 表示装置及び表示パネルの駆動方法 |

| KR100511788B1 (ko) * | 2002-08-28 | 2005-09-02 | 엘지.필립스 엘시디 주식회사 | 일렉트로-루미네센스 표시패널의 데이터 구동장치 |

| EP1547194A1 (en) | 2002-09-10 | 2005-06-29 | Fractus, S.A. | Coupled multiband antennas |

| JP3875173B2 (ja) | 2002-10-17 | 2007-01-31 | ローム株式会社 | 有機el駆動回路およびこれを用いる有機el表示装置 |

| JP4241144B2 (ja) * | 2002-10-31 | 2009-03-18 | カシオ計算機株式会社 | 駆動制御装置及びその制御方法並びに駆動制御装置を備えた表示装置 |

| TWI470607B (zh) | 2002-11-29 | 2015-01-21 | Semiconductor Energy Lab | A current driving circuit and a display device using the same |

| JP4566528B2 (ja) * | 2002-12-05 | 2010-10-20 | シャープ株式会社 | 表示装置 |

| JP4397811B2 (ja) | 2002-12-27 | 2010-01-13 | 株式会社半導体エネルギー研究所 | 半導体装置、el表示装置、及び電子機器 |

| JP2004226835A (ja) | 2003-01-24 | 2004-08-12 | Pioneer Electronic Corp | 表示装置及び方法 |

| JP4563692B2 (ja) * | 2003-02-06 | 2010-10-13 | ルネサスエレクトロニクス株式会社 | 表示パネルの電流駆動回路及び電流駆動装置 |

| US7944411B2 (en) | 2003-02-06 | 2011-05-17 | Nec Electronics | Current-drive circuit and apparatus for display panel |

| JP3952965B2 (ja) | 2003-02-25 | 2007-08-01 | カシオ計算機株式会社 | 表示装置及び表示装置の駆動方法 |

| CN1754316B (zh) * | 2003-02-28 | 2011-07-13 | 株式会社半导体能源研究所 | 半导体装置及其驱动方法 |

| JP2004294752A (ja) * | 2003-03-27 | 2004-10-21 | Toshiba Matsushita Display Technology Co Ltd | El表示装置 |

| CN1323382C (zh) * | 2003-04-01 | 2007-06-27 | 友达光电股份有限公司 | 用于一电流驱动的显示元件的组合式数据驱动电路结构 |

| JP3991003B2 (ja) | 2003-04-09 | 2007-10-17 | 松下電器産業株式会社 | 表示装置およびソース駆動回路 |

| TW591586B (en) * | 2003-04-10 | 2004-06-11 | Toppoly Optoelectronics Corp | Data-line driver circuits for current-programmed electro-luminescence display device |

| WO2004097781A1 (en) * | 2003-04-25 | 2004-11-11 | Koninklijke Philips Electronics N.V. | Method and device for driving an active matrix display panel |

| KR100520827B1 (ko) * | 2003-06-21 | 2005-10-12 | 엘지.필립스 엘시디 주식회사 | 일렉트로 루미네센스 표시패널의 구동장치 및 구동방법과일렉트로 루미네센스 표시장치의 제조방법 |

| JP2005037915A (ja) * | 2003-06-25 | 2005-02-10 | Rohm Co Ltd | 有機el駆動回路およびこれを用いる有機el表示装置 |

| JP4841812B2 (ja) * | 2003-06-27 | 2011-12-21 | ローム株式会社 | 有機el駆動回路 |

| JP4826056B2 (ja) * | 2003-11-25 | 2011-11-30 | セイコーエプソン株式会社 | 電流生成回路、電気光学装置及び電子機器 |

| JP4111128B2 (ja) * | 2003-11-28 | 2008-07-02 | カシオ計算機株式会社 | 表示駆動装置及び表示装置並びにその駆動制御方法 |

| US7889157B2 (en) * | 2003-12-30 | 2011-02-15 | Lg Display Co., Ltd. | Electro-luminescence display device and driving apparatus thereof |

| JP2005222030A (ja) * | 2004-01-05 | 2005-08-18 | Seiko Epson Corp | データ線駆動回路、電気光学装置および電子機器 |

| JP4203656B2 (ja) * | 2004-01-16 | 2009-01-07 | カシオ計算機株式会社 | 表示装置及び表示パネルの駆動方法 |

| EP1562167B1 (en) * | 2004-02-04 | 2018-04-11 | LG Display Co., Ltd. | Electro-luminescence display |

| US7298368B2 (en) * | 2004-03-17 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Display device having a DAC per pixel |

| JP4665419B2 (ja) * | 2004-03-30 | 2011-04-06 | カシオ計算機株式会社 | 画素回路基板の検査方法及び検査装置 |

| KR100600314B1 (ko) * | 2004-11-17 | 2006-07-18 | 삼성에스디아이 주식회사 | 발광 표시 장치 및 그것의 데이터 구동 칩 |

| KR100635950B1 (ko) * | 2005-06-15 | 2006-10-18 | 삼성전자주식회사 | Oled 데이터 구동 회로 및 디스플레이 시스템 |

| JP4475187B2 (ja) * | 2005-07-04 | 2010-06-09 | セイコーエプソン株式会社 | 電気光学装置、その駆動回路および電子機器 |

| JP4702061B2 (ja) * | 2006-01-06 | 2011-06-15 | セイコーエプソン株式会社 | 電気光学装置 |

| TWI323871B (en) * | 2006-02-17 | 2010-04-21 | Himax Tech Inc | Current mirror for oled |

| TWI342006B (en) * | 2006-05-09 | 2011-05-11 | Himax Tech Inc | Amole panel |

| WO2008018196A1 (fr) * | 2006-08-07 | 2008-02-14 | Panasonic Corporation | Convertisseur analogique - numérique à sommation de courants |

| KR100893482B1 (ko) * | 2007-08-23 | 2009-04-17 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시장치 및 그의 구동방법 |

| TWI391891B (zh) * | 2008-06-06 | 2013-04-01 | Holtek Semiconductor Inc | 顯示器面板驅動器 |

| JP4941426B2 (ja) * | 2008-07-24 | 2012-05-30 | カシオ計算機株式会社 | 表示装置 |

| JP5399198B2 (ja) * | 2009-10-08 | 2014-01-29 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | 画素回路および表示装置 |

| CN109213253B (zh) * | 2018-09-28 | 2020-10-30 | 聚辰半导体股份有限公司 | 一种快速的高精度低温漂强下拉电流产生电路 |

| CN111077937A (zh) * | 2019-12-27 | 2020-04-28 | 苏州易美新思新能源科技有限公司 | 一种适用于电池管理系统的单片机电源电路 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4996523A (en) * | 1988-10-20 | 1991-02-26 | Eastman Kodak Company | Electroluminescent storage display with improved intensity driver circuits |

| JPH06314977A (ja) * | 1993-04-28 | 1994-11-08 | Nec Ic Microcomput Syst Ltd | 電流出力型デジタル/アナログ変換回路 |

| JPH08106075A (ja) * | 1994-10-06 | 1996-04-23 | Sharp Corp | 表示駆動回路 |

| JP3091173B2 (ja) * | 1997-10-22 | 2000-09-25 | ローム株式会社 | デジタル/アナログ変換器 |

| JP3252897B2 (ja) * | 1998-03-31 | 2002-02-04 | 日本電気株式会社 | 素子駆動装置および方法、画像表示装置 |

| JP2000056732A (ja) * | 1998-08-12 | 2000-02-25 | Tdk Corp | 有機el表示装置 |

| JP2000105574A (ja) * | 1998-09-29 | 2000-04-11 | Matsushita Electric Ind Co Ltd | 電流制御型発光装置 |

| JP4138102B2 (ja) * | 1998-10-13 | 2008-08-20 | セイコーエプソン株式会社 | 表示装置及び電子機器 |

| JP2000276108A (ja) * | 1999-03-24 | 2000-10-06 | Sanyo Electric Co Ltd | アクティブ型el表示装置 |

| JP3485175B2 (ja) * | 2000-08-10 | 2004-01-13 | 日本電気株式会社 | エレクトロルミネセンスディスプレイ |

-

2001

- 2001-12-14 JP JP2001381400A patent/JP3950988B2/ja not_active Expired - Lifetime

- 2001-12-17 US US10/015,767 patent/US6943760B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002244618A (ja) | 2002-08-30 |

| US6943760B2 (en) | 2005-09-13 |

| US20020075208A1 (en) | 2002-06-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3950988B2 (ja) | アクティブマトリックス電界発光素子の駆動回路 | |

| CN100440277C (zh) | 显示装置及显示用驱动电路 | |

| US7006114B2 (en) | Display driving apparatus and display apparatus using same | |

| US7486303B2 (en) | Circuit for adjusting gray-scale voltages of a self-emitting display device | |

| TWI395183B (zh) | 液晶顯示器之源極驅動器 | |

| JP3661650B2 (ja) | 基準電圧発生回路、表示駆動回路及び表示装置 | |

| KR100443214B1 (ko) | 다중 포맷 샘플링 레지스터, 다중 포맷 디지털/아날로그 컨버터, 및 액티브 매트릭스 표시 장치용 다중 포맷 데이터 드라이버 | |

| US20080252665A1 (en) | Current driver and display device | |

| TWI235988B (en) | Driving circuit of liquid crystal display | |

| US20050012700A1 (en) | Gamma correction circuit, liquid crystal driving circuit, display and power supply circuit | |

| JP4290627B2 (ja) | 表示素子駆動装置及びその表示素子駆動装置を備えた表示装置並びに表示素子駆動方法 | |

| KR100569471B1 (ko) | 디스플레이 제어 회로와 디스플레이 장치 | |

| US7880692B2 (en) | Driver circuit of AMOLED with gamma correction | |

| KR20080102726A (ko) | 소스 드라이버 및 이를 포함하는 표시 장치 | |

| JP2001166751A (ja) | 階調表示基準電圧発生回路およびそれを用いた液晶駆動装置 | |

| KR20040018932A (ko) | 표시 패널 드라이버 | |

| KR100796480B1 (ko) | 액티브 매트릭스 전계발광소자의 구동회로 | |

| WO2008042545A2 (en) | Reducing power consumption associated with high bias currents in systems that drive or otherwise control displays | |

| US7508363B2 (en) | Data driver circuit for display device and drive method thereof | |

| WO2004054114A1 (ja) | 半導体装置、デジタル・アナログ変換回路及びそれらを用いた表示装置 | |

| JP4216558B2 (ja) | 表示装置およびその駆動方法 | |

| KR100626262B1 (ko) | 표시 장치의 구동 회로, 표시 장치 및 표시 장치의 구동방법 | |

| CN100409304C (zh) | 阻抗变换电路、驱动电路及控制方法 | |

| JP7433377B2 (ja) | 表示装置及びその駆動方法{Display device and driving method for the same} | |

| US7982650B2 (en) | Digital-to-analog converter (DAC) and an associated method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050607 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20050907 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20050912 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051207 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060214 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060515 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20060926 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061225 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20070131 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070313 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070403 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3950988 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100511 Year of fee payment: 3 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100511 Year of fee payment: 3 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100511 Year of fee payment: 3 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110511 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120511 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130511 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130511 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |