JP5821828B2 - Soiウェーハの製造方法 - Google Patents

Soiウェーハの製造方法 Download PDFInfo

- Publication number

- JP5821828B2 JP5821828B2 JP2012255719A JP2012255719A JP5821828B2 JP 5821828 B2 JP5821828 B2 JP 5821828B2 JP 2012255719 A JP2012255719 A JP 2012255719A JP 2012255719 A JP2012255719 A JP 2012255719A JP 5821828 B2 JP5821828 B2 JP 5821828B2

- Authority

- JP

- Japan

- Prior art keywords

- wafer

- oxide film

- soi

- bond

- bond wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 30

- 238000000034 method Methods 0.000 claims description 37

- 238000005468 ion implantation Methods 0.000 claims description 35

- 239000001307 helium Substances 0.000 claims description 29

- 229910052734 helium Inorganic materials 0.000 claims description 29

- -1 helium ion Chemical class 0.000 claims description 28

- 239000001257 hydrogen Substances 0.000 claims description 21

- 229910052739 hydrogen Inorganic materials 0.000 claims description 21

- 239000013078 crystal Substances 0.000 claims description 14

- 238000002513 implantation Methods 0.000 claims description 14

- 239000007789 gas Substances 0.000 claims description 11

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 claims description 10

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 9

- 150000002500 ions Chemical class 0.000 claims description 6

- 230000003647 oxidation Effects 0.000 claims description 5

- 238000007254 oxidation reaction Methods 0.000 claims description 5

- 238000005498 polishing Methods 0.000 claims description 5

- 239000004065 semiconductor Substances 0.000 claims description 5

- 239000000758 substrate Substances 0.000 claims description 4

- 230000001172 regenerating effect Effects 0.000 claims description 3

- 235000012431 wafers Nutrition 0.000 description 236

- 239000010408 film Substances 0.000 description 136

- 230000005856 abnormality Effects 0.000 description 15

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 11

- 238000010438 heat treatment Methods 0.000 description 11

- 229910052710 silicon Inorganic materials 0.000 description 11

- 239000010703 silicon Substances 0.000 description 11

- 238000005530 etching Methods 0.000 description 10

- 239000000243 solution Substances 0.000 description 9

- 230000000052 comparative effect Effects 0.000 description 7

- 230000032798 delamination Effects 0.000 description 7

- 238000000926 separation method Methods 0.000 description 7

- 238000012545 processing Methods 0.000 description 4

- 230000002159 abnormal effect Effects 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000007598 dipping method Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 238000012958 reprocessing Methods 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 239000007864 aqueous solution Substances 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000004299 exfoliation Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 230000008929 regeneration Effects 0.000 description 1

- 238000011069 regeneration method Methods 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02236—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor

- H01L21/02238—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor silicon in uncombined form, i.e. pure silicon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/02255—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by thermal treatment

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- High Energy & Nuclear Physics (AREA)

- Chemical & Material Sciences (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Inorganic Chemistry (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Element Separation (AREA)

Description

半導体単結晶基板からなるボンドウェーハに酸化膜を形成し、該酸化膜を通して水素および希ガスのうち少なくとも1種類のガスイオンをイオン注入して前記ボンドウェーハにイオン注入層を形成し、該ボンドウェーハのイオン注入した表面とベースウェーハ表面とを前記酸化膜を介して貼り合わせた後、前記イオン注入層で前記ボンドウェーハを剥離することによりSOIウェーハを作製するSOIウェーハの製造方法において、

貼り合わせ前に前記ボンドウェーハに形成する酸化膜を、貼り合わせ面の酸化膜よりも背面の酸化膜を厚くし、該背面の酸化膜を厚くしたボンドウェーハにイオン注入した後、ベースウェーハと貼り合わせることを特徴とするSOIウェーハの製造方法を提供する。

半導体単結晶基板からなるボンドウェーハに酸化膜を形成し、該酸化膜を通して水素および希ガスのうち少なくとも1種類のガスイオンをイオン注入して前記ボンドウェーハにイオン注入層を形成し、該ボンドウェーハのイオン注入した表面とベースウェーハ表面とを前記酸化膜を介して貼り合わせた後、前記イオン注入層で前記ボンドウェーハを剥離することによりSOIウェーハを作製するSOIウェーハの製造方法において、

前記ボンドウェーハに形成する酸化膜を、貼り合わせ面の酸化膜よりも背面の酸化膜を厚くするSOIウェーハの製造方法である。

図1は、本発明のSOIウェーハの製造方法のフロー図である。

尚、ベースウェーハとしては、シリコン単結晶ウェーハ、又は、表面に絶縁膜を形成したシリコン単結晶ウェーハなどを用いることができる。

直径300mmの両面が鏡面研磨されたシリコン単結晶ウェーハからなるボンドウェーハに熱酸化を行って150nmの熱酸化膜(初期酸化膜)を全面に形成し、ボンドウェーハの背面の酸化膜をオーリングで保護した状態でHF水溶液に浸漬して貼り合わせ面側の酸化膜を除去し、その後、CMP加工により表面の再加工を行った後、再度、熱酸化を行い貼り合わせ面側に30nm熱酸化膜(埋め込み酸化膜)を形成し、水素のイオン注入を行った後、直径300mmのシリコン単結晶ウェーハからなるベースウェーハと貼り合わせ、横型熱処理炉で剥離熱処理して剥離してSOIウェーハを10枚作製した。

実施例1で得られた剥離後のボンドウェーハ(背面の酸化膜155nm付き)を、背面の酸化膜(初期酸化膜)をオーリングで保護した状態でHF水溶液に浸漬して貼り合わせ面側の酸化膜を除去し、その後、CMP加工により再生加工を行った後、熱酸化を行い貼り合わせ面側に30nm熱酸化膜(埋め込み酸化膜)を形成し、水素のイオン注入を行った後、直径300mmのシリコン単結晶ウェーハからなるベースウェーハと貼り合わせ、横型熱処理炉で剥離熱処理して剥離してSOIウェーハを10枚作製した。

直径300mmの両面が鏡面研磨されたシリコン単結晶ウェーハからなるボンドウェーハに熱酸化を行って150nmの熱酸化膜(初期酸化膜)を全面に形成し、ボンドウェーハの背面の酸化膜をオーリングで保護した状態でHF水溶液に浸漬して貼り合わせ面側の酸化膜を除去し、その後、CMP加工により表面の再加工を行った後、再度、熱酸化を行い貼り合わせ面側に30nm熱酸化膜(埋め込み酸化膜)を形成し、水素及びヘリウムのイオン注入(共注入)を行った後、直径300mmのシリコン単結晶ウェーハからなるベースウェーハと貼り合わせ、横型熱処理炉で剥離熱処理して剥離してSOIウェーハを10枚作製した。

尚、水素及びヘリウムの共注入では、注入エネルギーがそれぞれ30keV、50keVであるため、ヘリウムイオンの方が深い位置に注入される。

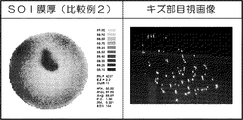

直径300mmの両面が鏡面研磨されたシリコン単結晶ウェーハからなるボンドウェーハの全面に30nmの熱酸化膜(埋め込み酸化膜)を形成し、その後、HF処理及び再度の熱酸化膜形成を行わずに水素のイオン注入を行った後、ベースウェーハに貼り合わせ、剥離熱処理して剥離してSOIウェーハを10枚作製した。

直径300mmの両面が鏡面研磨されたシリコン単結晶ウェーハからなるボンドウェーハの全面に30nmの熱酸化膜(埋め込み酸化膜)を形成し、その後、HF処理及び再度の熱酸化膜形成を行わずに水素及びヘリウムのイオン注入(共注入)を行った後、ベースウェーハに貼り合わせ、剥離熱処理して剥離してSOIウェーハを10枚作製した。

尚、水素及びヘリウムの共注入では、注入エネルギーがそれぞれ30keV、50keVであるため、ヘリウムイオンの方が深い位置に注入される。

尚、反りの形状(凹凸)は、剥離面を基準とした形状のことを示す。

2’…背面の酸化膜、 3…水素イオン注入層、4…ヘリウムイオン注入層、

5…ベースウェーハ、 6…SOI層、 10…貼り合わせウェーハ、

20…SOIウェーハ。

Claims (6)

- 半導体単結晶基板からなるボンドウェーハに酸化膜を形成し、該酸化膜を通して水素および希ガスのうち少なくとも1種類のガスイオンをイオン注入して前記ボンドウェーハにイオン注入層を形成し、該ボンドウェーハのイオン注入した表面とベースウェーハ表面とを前記酸化膜を介して貼り合わせた後、前記イオン注入層で前記ボンドウェーハを剥離することによりSOIウェーハを作製するSOIウェーハの製造方法において、

貼り合わせ前に前記ボンドウェーハに形成する酸化膜を、貼り合わせ面の酸化膜よりも背面の酸化膜を厚くし、該背面の酸化膜を厚くしたボンドウェーハにイオン注入した後、ベースウェーハと貼り合わせるものとし、その際、剥離直後の前記SOIウェーハの凸形状の大きさと剥離直後の前記ボンドウェーハの凹形状の大きさが同等になるように前記背面の酸化膜を設定することを特徴とするSOIウェーハの製造方法。 - 前記ボンドウェーハの酸化膜の形成は、ボンドウェーハの全面に熱酸化膜を形成した後、該ボンドウェーハの貼り合わせ面側の熱酸化膜を除去することによって背面のみに熱酸化膜を有するボンドウェーハを作製し、該背面のみに熱酸化膜を有するボンドウェーハの全面を熱酸化することによって行うことを特徴とする請求項1に記載のSOIウェーハの製造方法。

- 前記ボンドウェーハの貼り合わせ面側の熱酸化膜を除去した後に、該貼り合わせ面側を研磨する工程を含み、その後全面の熱酸化を行うことを特徴とする請求項2に記載のSOIウェーハの製造方法。

- 前記ボンドウェーハとして、イオン注入層で剥離後のボンドウェーハを再生加工して作製したウェーハを用いることを特徴とする請求項1乃至請求項3のいずれか一項に記載のSOIウェーハの製造方法。

- 前記再生加工において、前記剥離後のボンドウェーハの背面酸化膜を除去しないことを特徴とする請求項4に記載のSOIウェーハの製造方法。

- 前記イオン注入として、水素イオンとヘリウムイオンの共注入を行い、該共注入においてヘリウムイオンを水素イオンよりも深い位置に注入することを特徴とする請求項1乃至請求項5のいずれか一項に記載のSOIウェーハの製造方法。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012255719A JP5821828B2 (ja) | 2012-11-21 | 2012-11-21 | Soiウェーハの製造方法 |

| CN201380047666.6A CN104620384B (zh) | 2012-11-21 | 2013-10-11 | Soi晶圆的制造方法 |

| KR1020157005866A KR101910100B1 (ko) | 2012-11-21 | 2013-10-11 | Soi 웨이퍼의 제조방법 |

| EP13856571.8A EP2924736B1 (en) | 2012-11-21 | 2013-10-11 | Method for manufacturing soi wafer |

| US14/427,151 US9378999B2 (en) | 2012-11-21 | 2013-10-11 | Method for manufacturing SOI wafer |

| PCT/JP2013/006072 WO2014080563A1 (ja) | 2012-11-21 | 2013-10-11 | Soiウェーハの製造方法 |

| SG11201501873QA SG11201501873QA (en) | 2012-11-21 | 2013-10-11 | Method for manufacturing soi wafer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012255719A JP5821828B2 (ja) | 2012-11-21 | 2012-11-21 | Soiウェーハの製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014103329A JP2014103329A (ja) | 2014-06-05 |

| JP2014103329A5 JP2014103329A5 (ja) | 2015-04-30 |

| JP5821828B2 true JP5821828B2 (ja) | 2015-11-24 |

Family

ID=50775761

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012255719A Active JP5821828B2 (ja) | 2012-11-21 | 2012-11-21 | Soiウェーハの製造方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9378999B2 (ja) |

| EP (1) | EP2924736B1 (ja) |

| JP (1) | JP5821828B2 (ja) |

| KR (1) | KR101910100B1 (ja) |

| CN (1) | CN104620384B (ja) |

| SG (1) | SG11201501873QA (ja) |

| WO (1) | WO2014080563A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6353814B2 (ja) * | 2015-06-09 | 2018-07-04 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

| JP6556511B2 (ja) * | 2015-06-17 | 2019-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN110085549B (zh) * | 2018-01-26 | 2021-06-04 | 沈阳硅基科技有限公司 | 一种双面注入得到soi的方法 |

| CN110544668B (zh) | 2018-05-28 | 2022-03-25 | 沈阳硅基科技有限公司 | 一种通过贴膜改变soi边缘stir的方法 |

| CN109360805A (zh) * | 2018-09-28 | 2019-02-19 | 沈阳硅基科技有限公司 | 一种图形soi硅片的制备方法 |

| FR3146019A1 (fr) * | 2023-02-16 | 2024-08-23 | Soitec | Procédé de formation d’une zone de fragisilation dans un substrat semi-conducteur |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0355822A (ja) | 1989-07-25 | 1991-03-11 | Shin Etsu Handotai Co Ltd | 半導体素子形成用基板の製造方法 |

| JPH0680624B2 (ja) | 1990-02-28 | 1994-10-12 | 信越半導体株式会社 | 接合ウエーハの製造方法 |

| JP3422225B2 (ja) | 1997-07-08 | 2003-06-30 | 三菱住友シリコン株式会社 | 貼り合わせ半導体基板及びその製造方法 |

| JP3500063B2 (ja) * | 1998-04-23 | 2004-02-23 | 信越半導体株式会社 | 剥離ウエーハを再利用する方法および再利用に供されるシリコンウエーハ |

| FR2811807B1 (fr) | 2000-07-12 | 2003-07-04 | Commissariat Energie Atomique | Procede de decoupage d'un bloc de materiau et de formation d'un film mince |

| US20070069335A1 (en) * | 2003-09-08 | 2007-03-29 | Akihiko Endo | Bonded wafer and its manufacturing method |

| KR101151458B1 (ko) * | 2005-02-28 | 2012-06-01 | 신에쯔 한도타이 가부시키가이샤 | 접합 웨이퍼의 제조방법 및 접합 웨이퍼 |

| JP4398934B2 (ja) * | 2005-02-28 | 2010-01-13 | 信越半導体株式会社 | Soiウエーハの製造方法 |

| JP5233111B2 (ja) | 2006-11-30 | 2013-07-10 | 株式会社Sumco | 貼り合わせsoiウェーハの製造方法 |

| US7902039B2 (en) | 2006-11-30 | 2011-03-08 | Sumco Corporation | Method for manufacturing silicon wafer |

| JP2011187502A (ja) | 2010-03-04 | 2011-09-22 | Seiko Epson Corp | 半導体装置の製造方法 |

| US20130089968A1 (en) | 2010-06-30 | 2013-04-11 | Alex Usenko | Method for finishing silicon on insulator substrates |

-

2012

- 2012-11-21 JP JP2012255719A patent/JP5821828B2/ja active Active

-

2013

- 2013-10-11 KR KR1020157005866A patent/KR101910100B1/ko active IP Right Grant

- 2013-10-11 SG SG11201501873QA patent/SG11201501873QA/en unknown

- 2013-10-11 CN CN201380047666.6A patent/CN104620384B/zh active Active

- 2013-10-11 US US14/427,151 patent/US9378999B2/en active Active

- 2013-10-11 EP EP13856571.8A patent/EP2924736B1/en active Active

- 2013-10-11 WO PCT/JP2013/006072 patent/WO2014080563A1/ja active Application Filing

Also Published As

| Publication number | Publication date |

|---|---|

| EP2924736A1 (en) | 2015-09-30 |

| EP2924736B1 (en) | 2017-08-30 |

| WO2014080563A1 (ja) | 2014-05-30 |

| KR20150087181A (ko) | 2015-07-29 |

| CN104620384B (zh) | 2017-06-06 |

| US9378999B2 (en) | 2016-06-28 |

| EP2924736A4 (en) | 2016-06-29 |

| US20150243550A1 (en) | 2015-08-27 |

| JP2014103329A (ja) | 2014-06-05 |

| CN104620384A (zh) | 2015-05-13 |

| SG11201501873QA (en) | 2015-05-28 |

| KR101910100B1 (ko) | 2018-10-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5780234B2 (ja) | Soiウェーハの製造方法 | |

| JP5821828B2 (ja) | Soiウェーハの製造方法 | |

| WO2013102968A1 (ja) | 貼り合わせsoiウェーハの製造方法 | |

| WO2015136834A1 (ja) | 貼り合わせsoiウェーハの製造方法 | |

| JP6056516B2 (ja) | Soiウェーハの製造方法及びsoiウェーハ | |

| JP6380245B2 (ja) | Soiウェーハの製造方法 | |

| KR102095383B1 (ko) | 접합 웨이퍼의 제조방법 | |

| KR102019658B1 (ko) | Soi 웨이퍼의 제조방법 | |

| CN104364880B (zh) | Soi晶片的制造方法 | |

| WO2014080565A1 (ja) | Soiウェーハの製造方法 | |

| JP2005079389A (ja) | 貼り合わせウェーハの分離方法及びその分離用ボート | |

| JP6607207B2 (ja) | 貼り合わせsoiウェーハの製造方法 | |

| JP6136786B2 (ja) | 貼り合わせウェーハの製造方法 | |

| JP2009252948A (ja) | 貼り合わせウェーハの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20141015 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150312 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20150312 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20150507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150512 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150608 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150908 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150921 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5821828 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R154 | Certificate of patent or utility model (reissue) |

Free format text: JAPANESE INTERMEDIATE CODE: R154 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5821828 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |