CN113016090A - 半导体装置 - Google Patents

半导体装置 Download PDFInfo

- Publication number

- CN113016090A CN113016090A CN201980072751.5A CN201980072751A CN113016090A CN 113016090 A CN113016090 A CN 113016090A CN 201980072751 A CN201980072751 A CN 201980072751A CN 113016090 A CN113016090 A CN 113016090A

- Authority

- CN

- China

- Prior art keywords

- insulating layer

- layer

- film

- region

- metal oxide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B33/00—Electroluminescent light sources

- H05B33/12—Light sources with substantially two-dimensional radiating surfaces

- H05B33/14—Light sources with substantially two-dimensional radiating surfaces characterised by the chemical or physical composition or the arrangement of the electroluminescent material, or by the simultaneous addition of the electroluminescent material in or onto the light source

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/6737—Thin-film transistors [TFT] characterised by the electrodes characterised by the electrode materials

- H10D30/6739—Conductor-insulator-semiconductor electrodes

-

- H10D64/011—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/129—Chiplets

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

- H10D30/6715—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes characterised by the doping profiles, e.g. having lightly-doped source or drain extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

- H10D30/6736—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes characterised by the shape of gate insulators

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Thin Film Transistor (AREA)

Abstract

提供一种电特性的良好的半导体装置。提供一种可靠性高的半导体装置。该半导体装置包括半导体层、第一绝缘层、第二绝缘层、第三绝缘层、金属氧化物层及导电层。半导体层、第二绝缘层、金属氧化物层及导电层依次层叠在第一绝缘层上。第二绝缘层的端部位于半导体层的端部的内侧,导电层及金属氧化物层的端部位于第二绝缘层的端部的内侧。第三绝缘层与第一绝缘层的顶面、半导体层的顶面及侧面、第二绝缘层的顶面及侧面、金属氧化物层的侧面以及导电层的顶面及侧面接触。半导体层具有第一区域、一对第二区域以及一对第三区域。第一区域与第一绝缘层及金属氧化物层重叠。第二区域夹持第一区域且与第二绝缘层重叠而不与金属氧化物层重叠。第三区域夹持第一区域及一对第二区域且不与第二绝缘层重叠。第三区域与第三绝缘层接触并具有其电阻低于第一区域的部分。第二区域具有其电阻高于第三区域的部分。

Description

技术领域

本发明的一个方式涉及一种半导体装置。本发明的一个方式涉及一种显示装置。本发明的一个方式涉及一种半导体装置或显示装置的制造方法。

注意,本发明的一个方式不限定于上述技术领域。作为本说明书等所公开的本发明的一个方式的技术领域的一个例子,可以举出半导体装置、显示装置、发光装置、蓄电装置、存储装置、电子设备、照明装置、输入装置、输入输出装置、其驱动方法或者其制造方法。半导体装置是指能够通过利用半导体特性而工作的所有装置。

背景技术

作为可用于晶体管的半导体材料,使用金属氧化物的氧化物半导体受到瞩目。例如,专利文献1公开了如下半导体装置:层叠有多个氧化物半导体层,在该多个氧化物半导体层中,被用作沟道的氧化物半导体层包含铟及镓,并且铟的比例高于镓的比例,由此场效应迁移率(有时,简称为迁移率或μFE)得到提高的半导体装置。

由于能够用于半导体层的金属氧化物可以利用溅射法等形成,所以可以被用于构成大型显示装置的晶体管的半导体层。此外,因为可以将使用多晶硅或非晶硅的晶体管的生产设备的一部分改良而利用,所以还可以抑制设备投资。此外,与使用非晶硅的晶体管相比,使用金属氧化物的晶体管具有高场效应迁移率,所以可以实现设置有驱动电路的高性能的显示装置。

此外,在由显示装置中的屏幕尺寸有大型化的趋势,于是,显示装置的研制甚至针对对角线60英寸以上,进而为对角线120英寸以上的屏幕。并且,屏幕也有走向高分辨率的趋势,如全高清(像素数为1920×1080,也被称为“2K”等)、Ultra High-Definition(像素数为3840×2160,也被称为“4K”等)、Super High-Definition(像素数为7680×4320,也被称为“8K”等)。

屏幕尺寸的大型化或分辨率的提高趋于导致显示部内的布线电阻的增大。专利文献2中公开了在使用非晶硅晶体管的液晶显示装置中为了抑制布线电阻的增大使用铜(Cu)形成低电阻布线层的技术。

[先行技术文献]

[专利文献]

[专利文献1]日本专利申请公开第2014-7399号公报

[专利文献2]日本专利申请公开第2004-163901号公报

发明内容

发明所要解决的技术问题

本发明的一个方式的目的之一是提供一种电特性良好的半导体装置。此外,本发明的一个方式的目的之一是提供一种可靠性高的半导体装置。此外,本发明的一个方式的目的之一是提供一种新颖的半导体装置。

注意,这些目的的记载不妨碍其他目的的存在。并且,本发明的一个方式不需要实现所有上述目的。此外,可以从说明书、附图、权利要求书等的记载抽出上述以外的目的。

解决技术问题的手段

本发明的一个方式是包括半导体层、第一绝缘层、第二绝缘层、第三绝缘层、金属氧化物层及导电层的半导体装置。半导体层、第二绝缘层、金属氧化物层及导电层依次层叠在第一绝缘层上。在沟道长度方向的截面上,第二绝缘层的端部位于半导体层的端部的内侧,导电层及金属氧化物层的端部都位于第二绝缘层的端部的内侧。第三绝缘层与第一绝缘层的顶面、半导体层的顶面及侧面、第二绝缘层的顶面及侧面、金属氧化物层的侧面以及导电层的顶面及侧面接触。半导体层具有第一区域、一对第二区域以及一对第三区域。第一区域与第一绝缘层及金属氧化物层重叠。第二区域夹持第一区域且与第二绝缘层重叠而不与金属氧化物层重叠。第三区域夹持第一区域及一对第二区域且不与第二绝缘层重叠。第三区域与第三绝缘层接触并具有其电阻低于第一区域的部分。第二区域具有其电阻高于第三区域的部分。

在上述半导体装置中,第二绝缘层优选具有不与金属氧化物层重叠的区域的厚度比与金属氧化物层重叠的区域的厚度薄的部分。

在上述半导体装置中,第二区域优选具有其薄层电阻为1×103Ω/□以上且1×109Ω/□以下的部分。

在上述半导体装置中,第一区域的电阻优选为第二区域的电阻的1×100倍以上且1×109倍以下。

在上述半导体装置中,第二区域的电阻优选为第三区域的电阻的1×100倍以上且1×109倍以下。

在上述半导体装置中,沟道长度方向的截面上的第二区域的宽度优选为100nm以上且2μm以下。

在上述半导体装置中,第一绝缘层优选包含氮化物,并且第三绝缘层优选包含氮化物。

上述半导体装置优选还包括第四绝缘层,该第四绝缘层与第三绝缘层的顶面接触并包含氮化物。

在上述半导体装置中,第三绝缘层优选具有其氢浓度低于第四绝缘层的氢浓度的区域。

在上述半导体装置中,第三绝缘层优选具有其膜密度高于第四绝缘层的膜密度的区域。

在上述半导体装置中,优选的是:导电层与金属氧化物层的顶面形状大致一致;导电层的端部位于金属氧化物层的端部的内侧。

在上述半导体装置中,第二绝缘层的端部及金属氧化物层的端部优选都具有锥形形状。

在上述半导体装置中,半导体层及金属氧化物层优选都包含同一金属元素。

在上述半导体装置中,金属元素优选为铟和锌中的任一个以上。

发明效果

根据本发明的一个方式,可以提供一种电特性良好的半导体装置。此外,可以提供一种可靠性高的半导体装置。此外,可以提供一种新颖的半导体装置。

注意,上述效果的记载并不妨碍其他效果的存在。此外,本发明的一个方式并不需要具有所有上述效果。此外,可以从说明书、附图、权利要求书等的记载抽出上述以外的效果。

附图简要说明

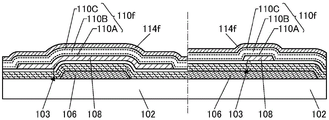

图1A是半导体装置的俯视图。图1B、图1C是半导体装置的截面图。

图2A、图2B、图2C是半导体装置的截面图。

图3A、图3B、图3C是半导体装置的截面图。

图4A、图4B、图4C是半导体装置的截面图。

图5A是半导体装置的俯视图。图5B、图5C是半导体装置的截面图。

图6A、图6B是半导体装置的截面图。

图7A是半导体装置的俯视图。图7B、图7C是半导体装置的截面图。

图8A、图8B、图8C是半导体装置的截面图。

图9A是半导体装置的俯视图。图9B、图9C是半导体装置的截面图。

图10A、图10B、图10C、图10D是说明半导体装置的制造方法的截面图。

图11A、图11B、图11C是说明半导体装置的制造方法的截面图。

图12A、图12B、图12C是说明半导体装置的制造方法的截面图。

图13A、图13B、图13C是说明半导体装置的制造方法的截面图。

图14A、图14B是说明半导体装置的制造方法的图。

图15A、图15B、图15C是显示装置的俯视图。

图16是显示装置的截面图。

图17是显示装置的截面图。

图18是显示装置的截面图。

图19是显示装置的截面图。

图20A是显示装置的方框图。图20B、图20C是显示装置的电路图。

图21A、图21C、图21D是显示装置的电路图。图21B是显示装置的时序图。

图22A示出显示模块的结构例子。图22B是显示模块的截面示意图。

图23A示出电子设备的结构例子。图23B是电子设备的截面示意图。

图24A、图24B、图24C、图24D、图24E示出电子设备的结构例子。

图25A、图25B、图25C、图25D、图25E、图25F、图25G示出电子设备的结构例子。

图26A、图26B、图26C、图26D示出电子设备的结构例子。

图27是示出晶体管的Id-Vd特性的图。

图28是示出晶体管的Id-Vd特性的图。

图29是示出金属氧化物膜的电阻的图。

图30A、图30B是截面STEM图像。

图31是示出晶体管的Id-Vg特性的图。

图32是示出晶体管的Id-Vg特性的图。

图33是示出晶体管的Id-Vg特性的图。

图34是示出晶体管的Id-Vg特性的图。

图35是示出晶体管的可靠性测试结果的图。

图36是示出金属氧化物膜的电阻的图。

图37是示出晶体管的Id-Vd特性的图。

图38是示出栅极驱动器的工作结果的图。

图39A、图39B、图39C、图39D、图39E是示出样品结构的截面图。

图40A、图40B是示出样品结构的截面图。

图41是示出样品结构的截面图。

图42是示出TDS测试结果的图。

图43是示出TDS测试结果的图。

图44是示出TDS测试结果的图。

图45是示出TDS测试结果的图。

图46是示出TDS测试结果的图。

图47是示出晶体管的Id-Vg特性的图。

图48是示出晶体管的Id-Vg特性的图。

图49是示出晶体管的Id-Vg特性的图。

图50是示出晶体管的Id-Vg特性的图。

图51是示出晶体管的Id-Vg特性的图。

图52是示出晶体管的Id-Vg特性的图。

图53是示出晶体管的Id-Vg特性的图。

图54A、图54B是示出晶体管的可靠性测试结果的图。

图55A、图55B是晶体管的截面TEM图像。

实施发明的方式

下面,参照附图对实施方式进行说明。注意,实施方式可以以多个不同方式来实施,所属技术领域的普通技术人员可以很容易地理解一个事实,就是其方式和详细内容可以被变换为各种各样的形式而不脱离本发明的宗旨及其范围。因此,本发明不应该被解释为仅局限在以下实施方式所记载的内容中。

在本说明书所说明的附图中,为便于清楚地说明,有时夸大表示各构成要素的大小、层的厚度或区域。

本说明书等所使用的“第一”、“第二”、“第三”等序数词是为了避免构成要素的混淆而附加的,而不是为了在数目方面上进行限定的。

在本说明书等中,为了方便起见,使用“上”、“下”等表示配置的词句以参照附图说明构成要素的位置关系。此外,构成要素的位置关系根据描述各结构的方向适当地改变。因此,不局限于本说明书中所说明的词句,可以根据情况适当地更换。

此外,在本说明书等中,在采用极性不同的晶体管或电路工作中的电流方向变化的情况等下,晶体管所包括的源极及漏极的功能有时相互调换。因此,“源极”和“漏极”可以相互调换。

注意,在本说明书等中,晶体管的沟道长度方向是指与以最短距离连接源区域和漏区域的直线平行的方向中的一个。也就是说,沟道长度方向相当于在晶体管处于开启状态时流过半导体层中的电流的方向之一。此外,沟道宽度方向是指与该沟道长度方向正交的方向。此外,根据晶体管的结构及形状,沟道长度方向及沟道宽度方向有时不限于一个方向。

在本说明书等中,“电连接”包括通过“具有某种电作用的元件”连接的情况。在此,“具有某种电作用的元件”只要可以进行连接对象间的电信号的授受,就对其没有特别的限制。例如,“具有某种电作用的元件”不仅包括电极和布线,而且还包括晶体管等的开关元件、电阻元件、电感器、电容器、其他具有各种功能的元件等。

此外,在本说明书等中,可以将“膜”和“层”相互调换。例如,有时可以将“导电层”、“绝缘层”等的词句换为“导电膜”、“绝缘膜”。

在本说明书等中,“顶面形状大致一致”是指叠层中的每一个层的轮廓的至少一部分重叠。例如,也是指上层及下层的一部分或全部通过同一的掩模图案被加工的情况。但是,严格地说,有时轮廓不重叠而上层的端部位于下层的端部的内侧或者上层的端部位于下层的端部的外侧,这些情况也包括在“顶面形状大致一致”的情况中。

此外,在本说明书等中,在没有特别的说明的情况下,关态电流(off-statecurrent)是指晶体管处于关闭状态(也称为非导通状态、遮断状态)时的漏极电流。在没有特别的说明的情况下,在n沟道晶体管中,关闭状态是指栅极与源极间的电压Vgs低于阈值电压Vth(p沟道型晶体管中Vgs高于Vth)的状态。

在本说明书等中,显示装置的一个方式的显示面板是指能够在显示面显示(输出)图像等的面板。因此,显示面板是输出装置的一个方式。

此外,在本说明书等中,有时将在显示面板的衬底上安装有例如FPC(FlexiblePrinted Circuit:柔性印刷电路)或TCP(Tape Carrier Package:载带封装)等连接器的结构或在衬底上以COG(Chip On Glass:玻璃覆晶封装)方式等直接安装IC的结构称为显示面板模块或显示模块,或者也简称为显示面板等。

注意,在本说明书等中,显示装置的一个方式的触摸面板具有如下功能:在显示面显示图像等的功能;以及检测出手指或触屏笔等被检测体接触、点击或靠近显示面的作为触摸传感器的功能。因此触摸面板是输入/输出装置的一个方式。

触摸面板例如也可以称为具有触摸传感器的显示面板(或显示装置)、具有触摸传感器功能的显示面板(或显示装置)。触摸面板也可以包括显示面板及触摸传感器面板。或者,也可以具有在显示面板内部或表面具有触摸传感器的功能的结构。

此外,在本说明书等中,有时将在触摸面板的衬底上安装有连接器或IC的结构称为触摸面板模块、显示模块,或者简称为触摸面板等。

(实施方式1)

在本实施方式中,说明本发明的一个方式的半导体装置。作为半导体装置的一个例子,以下说明晶体管的结构例子及其制造方法例子。

本发明的一个方式是一种半导体装置,该半导体装置在第一绝缘层上包括形成沟道的半导体层、被用作栅极绝缘层的第二绝缘层以及被用作栅电极的导电层。半导体层优选包含呈现半导体特性的金属氧化物(以下也称为氧化物半导体)。

半导体装置在第二绝缘层与导电层之间包括金属氧化物层。金属氧化物层优选具有导电性,此时该金属氧化物层被用作栅电极的一部分。

在沟道长度方向的截面上,第二绝缘层的端部(轮廓)优选位于半导体层的端部(轮廓)的内侧。此外,在沟道长度方向的截面上,导电层及金属氧化物层的端部(轮廓)优选位于第二绝缘层的端部(轮廓)的内侧。

本发明的一个方式的半导体装置还包括第三绝缘层。第三绝缘层优选与第一绝缘层的顶面、半导体层的顶面及侧面、第二绝缘层的顶面及侧面、金属氧化物层的侧面、导电层的顶面及侧面接触而设置。第一绝缘层及第三绝缘层优选都使用抑制杂质扩散的材料。例如,第一绝缘层及第三绝缘层优选都使用氮化物。此外,通过设置第一绝缘层与第三绝缘层接触的区域,可以抑制杂质扩散到晶体管,由此得到高可靠性晶体管。

半导体层包括形成沟道的第一区域、夹持第一区域的一对第二区域、夹持第一区域及第二区域并被用作源区域及漏区域的一对第三区域。第一区域是与第一绝缘层及金属氧化物层重叠的区域。第二区域是与第二绝缘层重叠而不与金属氧化物层重叠的区域。第三区域是不与第二绝缘层重叠的区域。此外,第三区域优选具有与第三绝缘层接触且其电阻低于第一区域的电阻的部分。第二区域优选具有其电阻高于第三区域的电阻的部分。

第二区域被用作LDD(轻掺杂漏极:Lightly Doped Drain)区域。通过具有第二区域,可以缓和漏极电场,在以高电压驱动的情况下也可以得到高可靠性晶体管。

以下,参照附图说明更具体的例子。

<结构例子1>

图1A是晶体管100的俯视图,图1B是沿着图1A所示的点划线A1-A2的截面图,图1C是沿着图1A所示的点划线B1-B2的截面图。在图1A中,省略了晶体管100的构成要素的一部分(保护层等)。点划线A1-A2方向相当于沟道长度方向,点划线B1-B2方向相当于沟道宽度方向。在后面的晶体管的俯视图中也与图1A同样地省略构成要素的一部分。

晶体管100设置在衬底102上,并包括绝缘层103、半导体层108、绝缘层110、金属氧化物层114、导电层112、绝缘层116及绝缘层118等。岛状半导体层108设置在绝缘层103上。绝缘层110以覆盖绝缘层103的顶面的一部分及半导体层108的顶面的一部分的方式设置。金属氧化物层114及导电层112依次设置在绝缘层110上,并具有与半导体层108重叠的部分。图2A是图1B中的以点划线围绕的区域P的放大图。

导电层112及金属氧化物层114的端部位于绝缘层110的端部的内侧。换言之,绝缘层110至少在半导体层108上具有突出到导电层112及金属氧化物层114的端部的外侧的部分。

半导体层108具有被用作沟道形成区域的区域108C、夹持区域108C的一对区域10gL及其外侧的一对区域108N。区域108L是半导体层108中的与绝缘层110重叠且不与导电层112重叠的区域。在图2A中,将晶体管100的沟道长度方向上的区域108C的宽度记为L1,将区域108L的宽度记为L2。

区域108C被用作沟道形成区域。在此,金属氧化物层114在具有导电性时被用作栅电极的一部分,因此电场隔着被用作栅极绝缘层的绝缘层110施加到区域108C而形成沟道。

区域108L具有用来缓和漏极电场的缓冲区域的功能。由于区域108L不与导电层112及金属氧化物层114重叠,因此在对导电层112施加栅电压时也几乎不形成沟道。区域108L的载流子浓度优选比区域108C高。由此可以使区域108L用作LDD区域。

区域108L也可以说是:与区域108C相比,其电阻与它大致相等或较低的区域;其载流子浓度与它大致相等或较高的区域;其氧缺陷密度与它大致相等或较高的区域;其杂质浓度与它大致相等或较高的区域。

区域108L也可以说是:与区域108N相比,其电阻与它大致相等或较高的区域;其载流子浓度与它大致相等或较低的区域;其氧缺陷密度与它大致相等或较低的区域;其杂质浓度与它大致相等或较低的区域。

像这样,通过在作为沟道形成区域的区域108C和作为源区域或漏区域的区域108N之间设置被用作LDD区域的区域108L,可以实现兼具高漏极耐压及高通态电流的高可靠性晶体管。

区域108N被用作源区域或漏区域,其电阻低于半导体层108的其他区域。或者,区域108N也可以说是:与半导体层108的其他区域相比,其载流子浓度最高的区域;其氧缺陷密度最高的区域;或者其杂质浓度最高的区域。

区域108N的电阻越低越好,例如区域108N的薄层电阻值优选为1Ω/□以上且低于1×103Ω/□,更优选1Ω/□以上且8×102Ω/□以下。

此外,未形成沟道的状态下的区域108C的电阻越高越好。例如,区域108C的薄层电阻值为1×109Ω/□以上,优选为5×109Ω/□以上,更优选为1×1010Ω/□以上。

由于未形成沟道的状态下的区域108C的电阻越高越好,因此对其上限值没有特别的限制。但是,如果设定上限值,则区域108C的薄层电阻值例如为1×109Ω/□以上且1×1012Ω/□以下,优选为5×109Ω/□以上且1×1012Ω/□以下,更优选为1×1010Ω/口以上且1×1012Ω/□以下。

区域108L的薄层电阻值例如可以为1×103Ω/□以上且1×109Ω/□以下,优选为1×103Ω/□以上且1×108Ω/□以下,更优选为1×103Ω/□以上且1×107Ω/□以下。通过将电阻值设定为上述范围,可以实现电特性良好且可靠性高的晶体管。此外,可以根据电阻值算出薄层电阻。通过在区域108N和区域108C之间设置上述区域108L,可以提高晶体管100的源极-漏极耐压。

此外,未形成沟道的状态下的区域108C的电阻可以为区域108N的电阻的1×106倍以上且1×1012倍以下,优选为1×106倍以上且1×1011倍以下,更优选为1×106倍以上且1×1010倍以下。

未形成沟道的状态下的区域108C的电阻可以为区域108L的电阻的1×100倍以上且1×109倍以下,优选为1×101倍以上且1×108倍以下,更优选为1×102倍以上且1×107倍以下。

区域108L的电阻可以为区域108N的电阻的1×100倍以上且1×109倍以下,优选为1×101倍以上且1×108倍以下,更优选为1×101倍以上且1×107倍以下。

通过将具有上述电阻的区域108L设置在区域108N和沟道形成区域之间,可以提高晶体管100的源极-漏极耐压。

此外,半导体层108中的载流子浓度具有按区域108C、区域108L、区域108N的顺序依次增高的分布。通过在区域108C和区域108N之间设置区域108L,例如即使在制造工序中氢等杂质从区域108N扩散,也可以将区域108C的载流子浓度保持为极低。

被用作沟道形成区域的区域108C中的载流子浓度越低越好,优选为1×1018cm-3以下,更优选为1×1017cm-3以下,进一步优选为1×1016cm-3以下,进一步优选为1×1013cm-3以下,进一步优选为1×1012cm-3以下。注意,对区域108C的载流子浓度的下限值没有特别的限制,例如可以为1×10-9cm-3。

另一方面,区域108N中的载流子浓度例如可以为5×1018cm-3以上,优选为1×1019cm-3以上,更优选为5×1019cm-3以上。对区域108N中的载流子浓度的上限值没有特别的限制,例如可以为5×1021cm-3或1×1022cm-3等。

区域108L中的载流子浓度可以为区域108C和区域108N之间的值。例如,可以在1×1014cm-3以上且低于1×1020cm-3的范围内。

区域108L中的载流子浓度也可以不均匀,有时具有从区域108N一侧越靠近沟道形成区域一侧越低的梯度。例如,也可以具有区域108L中的氢浓度和氧空位浓度中的一方或双方从区域108N一侧越靠近沟道形成区域一侧越低的梯度。

半导体层108优选包含金属氧化物。与半导体层108的沟道形成区域接触的绝缘层103和绝缘层110优选使用氧化物膜。例如,可以使用氧化硅膜、氧氮化硅膜、氧化铝膜等氧化物膜。由此,通过晶体管100的制造工序中的热处理等,可以使氧从绝缘层103或绝缘层110脱离来供应到半导体层108的沟道形成区域,从而减少半导体层108中的氧空位。

绝缘层110的端部的一部分位于半导体层108上。绝缘层110包括与导电层112重叠而被用作栅极绝缘层的部分及不与导电层112及金属氧化物层114重叠的部分(即,与区域108L重叠的部分)。

绝缘层110也可以具有两层以上的叠层结构。图1B、图1C及图2A示出绝缘层110具有绝缘层110a、绝缘层110a上的绝缘层110b以及绝缘层110b上的绝缘层110c的三层结构的例子。此外,由于绝缘层110a、绝缘层110b及绝缘层110c可以使用由相同种类的材料构成的绝缘膜,因此有时不能够明确地确认到绝缘层110a、绝缘层110b及绝缘层110c的界面。因此,在本实施方式中,由虚线图示绝缘层110a、绝缘层110b及绝缘层110c的界面。

绝缘层110a包括与半导体层108的沟道形成区域接触的区域。绝缘层110c包括与金属氧化物层114接触的区域。绝缘层110b位于绝缘层110a和绝缘层110c之间。

绝缘层110a、绝缘层110b及绝缘层110c优选都是包含氧化物的绝缘膜。此时,绝缘层110a、绝缘层110b及绝缘层110c优选都使用相同的成膜装置连续地形成。

例如,作为绝缘层110a、绝缘层110b及绝缘层110c,可以使用包含氧化硅膜、氧氮化硅膜、氮氧化硅膜、氧化铝膜、氧化铪膜、氧化钇膜、氧化锆膜、氧化镓膜、氧化钽膜、氧化镁膜、氧化镧膜、氧化铈膜及氧化钕膜中的一种以上的绝缘层。

此外,与半导体层108接触的绝缘层110优选采用氧化物绝缘膜的叠层结构,更优选具有氧含量超过化学计量组成的区域。换言之,绝缘层110具有能够释放氧的绝缘膜。例如,通过在氧气氛下形成绝缘层110,对形成后的绝缘层110在氧气氛下进行热处理、等离子体处理等或者在绝缘层110上在氧气氛下形成氧化物膜等,可以将氧供应到绝缘层110中。

例如,绝缘层110a、绝缘层110b及绝缘层110c可以利用溅射法、化学气相沉积(CVD)法、真空蒸镀法、脉冲激光沉积(PLD)法、原子层沉积(ALD)法等形成。作为CVD法有等离子体增强化学气相沉积(PECVD)法、热CVD法等。

特别是,绝缘层110a、绝缘层110b及绝缘层110c优选通过等离子体CVD法形成。

绝缘层110a由于形成于半导体层108上,所以优选为尽可能在不给半导体层108带来损伤的条件下形成的膜。例如,可以在成膜速度(也称为成膜速率)充分低的条件下形成。

例如,在利用等离子体CVD法形成绝缘层110a时,通过在低功率的条件下形成,可以使给半导体层108带来的损伤极小。

在使用氧氮化硅膜作为绝缘层110a、绝缘层110b及绝缘层110c的情况下,作为用于形成氧氮化硅膜的成膜气体例如可以使用包含硅烷、乙硅烷等含硅的沉积气体以及氧、臭氧、一氧化二氮、二氧化氮等氧化气体的源气体。此外,除了源气体以外也可以包含氩、氦或氮等稀释气体。

例如,通过减小相对于成膜气体的总流量的沉积气体的流量的比例(以下,简称为流量比),可以降低成膜速度,因此可以形成致密且缺陷少的膜。

绝缘层110b优选为在其成膜速度高于绝缘层110a的条件下形成的膜。由此,可以提高生产率。

例如,当采用与绝缘层110a相比增加沉积气体的流量比的条件时,绝缘层110b可以在提高成膜速度的条件下形成。

绝缘层110c优选为其表面缺陷得到降低、不容易附着水等包含在大气中的杂质、极为致密的膜。例如,与绝缘层110a同样地,可以在成膜速度充分低的条件下形成。

由于绝缘层110c形成于绝缘层110b上,所以与绝缘层110a相比在形成绝缘层110c时给半导体层108带来的影响很小。因此,绝缘层110c可以与绝缘层110a相比在高功率的条件下形成。通过降低沉积气体的流量比且在较高的功率下形成,可以实现致密且其表面缺陷得到降低的膜。

换言之,可以将在成膜速度由高到低的顺序依次为绝缘层110b、绝缘层110a、绝缘层110c的条件下形成的叠层用于绝缘层110。此外,在绝缘层110中,对于湿蚀刻或干蚀刻的同一条件下的蚀刻速度由高到低的顺序依次为绝缘层110b、绝缘层110a、绝缘层110c。

绝缘层110b的厚度优选比绝缘层110a及绝缘层110c厚。通过使成膜速度最高的绝缘层110b形成得厚,可以缩短绝缘层110的形成工序所需要的时间。

这里,由于绝缘层110a与绝缘层110b的边界及绝缘层110b与绝缘层110c的边界有时不清楚,所以在图1A等中以虚线表示这些边界。注意,由于绝缘层110a与绝缘层110b的膜密度不同,所以有时在绝缘层110的截面的透射电子显微镜(TEM:Transmission ElectronMicroscopy)图像等中,可以以对比度的不同观察到这些边界。同样地,有时可以观察到绝缘层110b和绝缘层110c的边界。

在形成导电层112及金属氧化物层114时,不与导电层112重叠的区域的绝缘层110的厚度可能会变薄。图1B、图1C及图2A示出不与导电层112重叠的区域的绝缘层110c被去除,而残留有绝缘层110a及绝缘层110b的结构。此外,与导电层112重叠的区域的绝缘层110b相比,有时不与导电层112重叠的区域的绝缘层110b的厚度较薄。

通过减薄不与导电层112重叠的区域的绝缘层110的厚度,可以增加从绝缘层116供应的氢来降低区域108L的电阻。此外,通过调整不与导电层112重叠的区域的绝缘层110的厚度,可以调整绝缘层116的氢供给量来控制区域108L的电阻。

通过减薄不与导电层112重叠的区域的绝缘层110的厚度,绝缘层110端部的台阶减小,形成在绝缘层110上的层(例如,绝缘层116)的台阶覆盖性得到提高,由此可以抑制该层中出现如断开或空洞等的不良现象。

图2B示出在不与导电层112重叠的区域中残留有绝缘层110a、绝缘层110b及绝缘层110c的结构。此外,有时不与导电层112重叠的区域的绝缘层110c的厚度比与导电层112重叠的区域的绝缘层110c薄。如图2B所示,特别优选在不与导电层112重叠的区域中残留绝缘层110c。通过采用绝缘层110c残留在不与导电层112重叠的区域中的结构,可以抑制水吸附到绝缘层110。与导电层112重叠的区域的绝缘层110c的厚度为1nm以上且50nm以下,优选为2nm以上且40nm以下,更优选为3nm以上且30nm以下。

图2C示出绝缘层110a、绝缘层110b及绝缘层110c残留在不与导电层112重叠的区域中的例子,其中与导电层112重叠的区域的绝缘层110c的厚度大致等于不与导电层112重叠的区域的绝缘层110c的厚度。

此外,绝缘层110也可以采用绝缘层110a和绝缘层110a上的绝缘层110c的两层结构。或者,绝缘层110也可以采用单层结构。作为绝缘层110,可以根据目的适当地选择上述绝缘层110a、绝缘层110b和绝缘层110c中的任一个。

绝缘层116以覆盖导电层112的顶面及侧面、金属氧化物层114的侧面、绝缘层110的顶面及侧面、半导体层108的顶面及侧面以及绝缘层103的顶面的方式设置。绝缘层118以覆盖绝缘层116的方式设置。绝缘层116及绝缘层118被用作保护层,能够抑制杂质元素从外部扩散。

绝缘层116具有抑制来自绝缘层116上方的杂质扩散到半导体层108的功能。此外,绝缘层116具有在成膜时降低与绝缘层116接触的半导体层108的电阻的功能。绝缘层116接触区域108N的顶面及侧面而设置。绝缘层116可以使用通过在绝缘层116形成时或形成之后对区域108N中供应杂质的绝缘膜形成。或者,可以使用通过在绝缘层116形成时或形成之后进行加热,能够在区域108N中产生氧空位的绝缘膜形成。

绝缘层116优选为使用包含氢等杂质元素的成膜气体形成的膜。例如,作为包含氢的气体,可以使用硅烷、氨等。此外,通过降低绝缘层116的成膜温度,可以有效地对半导体层108供应很多杂质元素。绝缘层116的成膜温度例如优选为200℃以上且500℃以下,更优选为220℃以上且450℃以下,进一步优选为230℃以上且430℃以下,更进一步优选为250℃以上且400℃以下。

当在进行加热的同时在减压下形成绝缘层116时,可以促进从半导体层108中的成为区域108N的区域脱离氧。当对形成很多氧空位的半导体层108供应氢等杂质时,提高区域108N中的载流子浓度,可以进一步有效地使区域108N低电阻化。

作为绝缘层116,例如可以适当地使用氮化硅、氮氧化硅、氧氮化硅、氮化铝、氮氧化铝等含氮化物的绝缘膜。尤其是,氮化硅具有对氢及氧的阻挡性,因此可以防止从外部向半导体层108的氢的扩散及从半导体层108向外部的氧的脱离的双方,由此可以实现可靠性高的晶体管。

绝缘层116可以为具有吸收半导体层108中的氧且产生氧空位的功能的绝缘膜。尤其是,作为绝缘层116例如优选使用氮化铝等金属氮化物。

此外,在绝缘层116使用金属氮化物的情况下,优选使用铝、钛、钽、钨、铬或钌的氮化物。例如,特别优选包含铝或钛。例如,关于利用使用铝作为溅射靶材且使用包含氮的气体作为成膜气体的反应性溅射法形成的氮化铝膜,通过适当地控制相对于成膜气体的总流量的氮气的流量比,可以形成兼具极高绝缘性及对氢或氧的极高阻挡性的膜。因此,通过与半导体层108接触地设置包含这种金属氮化物的绝缘膜,不但可以实现半导体层108的低电阻化而且还可以有效地防止氧从半导体层108脱离或者氢扩散到半导体层108。

在使用氮化铝作为金属氮化物的情况下,包含该氮化铝的绝缘层的厚度优选为5nm以上。就算是这么薄的膜,也可以兼具对氢及氧的高阻挡性及使半导体层低电阻化的功能。此外,对该绝缘层的厚度没有特别的上限,但是考虑到生产率,优选为500nm以下,更优选为200nm以下,进一步优选为50nm以下。

在使用氮化铝膜作为绝缘层116的情况下,优选使用其组成式满足A1Nx(x为大于0且2以下的实数,x优选为大于0.5且1.5以下的实数)的膜。因此,可以形成具有高绝缘性及高热传导率的膜,由此可以提高在驱动晶体管100时产生的热的散热性。

或者,作为绝缘层116,可以使用氮化铝钛膜、氮化钛膜等。

由于这种绝缘层116以与区域108N接触的方式设置,因此绝缘层116吸收区域108N中的氧,可以在区域108N中产生氧空位。此外,当形成这种绝缘层116之后进行加热处理时,可以在区域108N中形成更多的氧空位,可以进一步降低电阻。在作为绝缘层116使用包含金属氧化物的膜的情况下,绝缘层116吸收半导体层108中的氧,由此有时在绝缘层116与区域108N之间形成包括包含在绝缘层116中的金属元素(例如铝)的氧化物的层。

区域108L不与绝缘层116接触而其间夹着绝缘层110,因此从绝缘层116供应的氢少于区域108N。此外,杂质浓度也低于区域108N,所以可以使区域108L处于其电阻高于区域108N的状态。

如后面说明,由于可以自对准地形成区域108L,所以不需要用来形成区域108L的光掩模,可以降低制造成本。此外,当自对准地形成区域108L时,不发生区域108L与导电层112的相对错位,由此可以使半导体层108中的区域108L的宽度大致一致。

可以在半导体层108中的沟道形成区域与低电阻的区域108N间均匀且稳定地形成不被施加(或与沟道形成区域相比不容易被施加)栅极电场的被用作偏置区域的区域108L。其结果是,可以提高晶体管的源极-漏极耐压而可以实现可靠性高的晶体管。

区域108L的宽度L2优选为100nm以上且2μm以下,更优选为150nm以上且1μm以下,进一步优选为200nm以上且1μm以下。通过设置区域108L,可以缓和电场集中在漏极附近,因此可以抑制尤其漏电压高的状态下的晶体管的劣化。此外,尤其是,通过使区域108L的宽度L2大于绝缘层110的厚度,可以有效地抑制电场集中在漏极附近。另一方面,在宽度L2大于2μm时源极-漏极电阻增高而有时晶体管的驱动速度变低。通过将宽度L2设定为上述范围,可以制造可靠性高且驱动速度高的晶体管、半导体装置。此外,区域108L的宽度L2可以根据半导体层108的厚度、绝缘层110的厚度、在驱动晶体管100时对源极-漏极间施加的电压的大小决定。

通过在沟道形成区域与低电阻的区域108N间设置区域108L,可以减少沟道形成区域与区域108N边界的电流密度,抑制沟道与源极或漏极边界产生的发热,由此可以制造可靠性高的晶体管、半导体装置。

绝缘层103可以具有叠层结构。图1A至图1C示出绝缘层103具有从衬底102一侧层叠有绝缘层103a、绝缘层103b、绝缘层103c及绝缘层103d的叠层结构的例子。绝缘层103a与衬底102接触。绝缘层103d与半导体层108接触。

绝缘层103优选满足如下特征中的一个,更优选满足如下特征的全部:耐压高,低应力,不容易释放氢及水,缺陷少,抑制包含在衬底102中的杂质的扩散。

在绝缘层103所包括的四个绝缘膜中,位于衬底102一侧的绝缘层103a、绝缘层103b及绝缘层103c优选使用含氮的绝缘膜。另一方面,与半导体层108接触的绝缘层103d优选使用含氧的绝缘膜。绝缘层103所包括的四个绝缘膜优选利用等离子体CVD装置以不接触于大气的方式连续地形成。

作为绝缘层103a、绝缘层103b及绝缘层103c的每一个,例如可以使用氮化硅膜、氮氧化硅膜、氮化铝膜、氮化铪膜等含氮的绝缘膜。此外,绝缘层103d可以参照有关能够用于上述绝缘层110的绝缘膜的记载。

绝缘层103a及绝缘层103c优选为防止从这些膜的下方扩散杂质的致密膜。优选的是,绝缘层103a能够阻挡包含在衬底102中的杂质,绝缘层103c能够阻挡包含在绝缘层103b中的氢及水。因此,绝缘层103a及绝缘层103c的每一个可以使用在与绝缘层103b相比成膜速度更低的条件下形成的绝缘膜。

另一方面,绝缘层103b优选使用具有低应力且在高成膜速度的条件下形成的绝缘膜形成。绝缘层103b优选形成为比绝缘层103a及绝缘层103c厚。

例如,在作为绝缘层103a、绝缘层103b及绝缘层103c使用利用等离子体CVD法形成的氮化硅膜的情况下,绝缘层103b的膜密度也比其他两个绝缘膜小。因此,在绝缘层103的截面的透射电子显微镜图像中,有时以对比度的不同观察到这些膜。由于绝缘层103a和绝缘层103b的边界及绝缘层103b和绝缘层103c的边界有时不清楚,所以在图1A至图1C等中以虚线示出这些边界。

作为与半导体层108接触的绝缘层103d,优选使用其表面上不容易吸附水等杂质的致密的绝缘膜。此外,优选的是使用缺陷尽可能少且水及氢等杂质减少的绝缘膜。例如,作为绝缘层103d可以使用与上述绝缘层110所包括的绝缘层110c同样的绝缘膜。

通过采用具有这种叠层结构的绝缘层103,晶体管可以具有极高的可靠性。

如图1B及图1C所示,晶体管100优选具有绝缘层103c与绝缘层116接触的区域。图3A是图1B中的以点划线围绕的区域Q的放大图,图3B是图1C中的以点划线围绕的区域R的放大图。

如图1B及图3A所示,在沟道长度方向上,不与半导体层108重叠的区域的绝缘层116与绝缘层103c接触。此外,绝缘层103d的端部与半导体层108的端部大致整齐。

如图3B所示,在沟道宽度方向上,不与绝缘层110重叠的区域的绝缘层116与绝缘层103c接触。此外,绝缘层103d的端部与绝缘层110的端部大致整齐。例如,当形成绝缘层110时,通过去除不与绝缘层110重叠的区域的成为绝缘层103d的绝缘膜,可以使绝缘层103d的端部与绝缘层110的端部大致整齐。

通过具有绝缘层103c与绝缘层116接触的区域,可以抑制杂质从外部扩散到晶体管100。尤其是,作为绝缘层116及绝缘层103c,优选使用包含氮的绝缘膜。

如图3C所示,绝缘层103d的端部也可以与半导体层108的端部大致整齐。例如,当形成半导体层108时,通过去除不与半导体层108重叠的区域的成为绝缘层103d的绝缘膜,可以使绝缘层103d的端部与半导体层108的端部大致整齐。

在沟道长度方向上,有时不与半导体层108重叠的区域的绝缘层103c的厚度比与半导体层108重叠的区域的绝缘层103c的厚度薄。图4A是图1B中的以点划线围绕的区域Q的放大图。图4A示出如下例子:不与半导体层108重叠的区域的绝缘层103c的厚度比与半导体层108重叠的区域的绝缘层103c的厚度薄;在绝缘层103c的厚度薄的区域中,绝缘层103c与绝缘层116接触。

在沟道宽度方向上,有时不与绝缘层110重叠的区域的绝缘层103c的厚度比与绝缘层110重叠的区域的绝缘层103c的厚度薄。图4B及图4C是图1C中的以点划线围绕的区域R的放大图。图4B及图4C示出如下例子:不与绝缘层110重叠的区域的绝缘层103c的厚度比与绝缘层110重叠的区域的绝缘层103c的厚度薄;在绝缘层103c的厚度薄的区域中,绝缘层103c与绝缘层116接触。此外,在图4B中,绝缘层103d的端部与绝缘层110的端部大致整齐。在图4C中,绝缘层103d的端部与半导体层108的端部大致整齐。

此外,图4A、图4B及图4C示出绝缘层103c与绝缘层116接触的例子,但是本发明的一个方式不局限于此,也可以暴露绝缘层103b,使得绝缘层103b与绝缘层116接触。此外,也可以暴露绝缘层103a,使得绝缘层103a与绝缘层116接触。

绝缘层110的端部及金属氧化物层114的端部优选都具有锥形形状。通过采用上述结构,形成在绝缘层110及金属氧化物层114上的层(例如,绝缘层116)的覆盖性提高而可以抑制在该层中发生断开或空洞等不良。

导电层112的一部分被用作栅电极。绝缘层110的一部分被用作栅极绝缘层。晶体管100是在半导体层108上设置有栅电极的所谓的顶栅型晶体管。

如图1A及图1B所示,晶体管100也可以在绝缘层118上包括导电层120a及导电层120b。导电层120a及导电层120b被用作源电极或漏电极。导电层120a及导电层120b分别通过设置在绝缘层118及绝缘层116中的开口部141a及开口部141b电连接于区域108N。

半导体层108优选包含金属氧化物。

例如,半导体层108优选包含铟、元素M(M为选自镓、铝、硅、硼、钇、锡、铜、钒、铍、钛、铁、镍、锗、锆、钼、镧、铈、钕、铪、钽、钨和镁中的一种或多种)和锌。尤其是,M优选为选自铝、镓、钇和锡中的一种或多种。

尤其是,作为半导体层108,优选使用包含铟、镓及锌的氧化物。

半导体层108也可以采用层叠有组成不同的层、结晶性不同的层或杂质浓度不同的层的叠层结构。

导电层112优选使用低电阻材料。通过作为导电层112使用低电阻材料,可以降低寄生电阻而使晶体管具有高通态电流,由此可以实现通态电流高的半导体装置。此外,通过在大型显示装置、高清晰的显示装置中降低布线电阻,可以抑制信号延迟而实现高速驱动。例如,作为导电层112,可以使用铜、银、金或铝等。尤其是,优选使用铜,因为其电阻低,而且量产性良好。

导电层112可以具有叠层结构。当导电层112具有叠层结构时,在低电阻的第一导电层的上方和/或下方设置第二导电层。作为第二导电层,优选使用与第一导电层相比不容易氧化(具有耐氧化性)的导电材料。此外,作为第二导电层,优选使用抑制第一导电层的成分扩散的材料。作为第二导电层,例如适合使用氧化铟、铟锌氧化物、铟锡氧化物(ITO)、含有硅的铟锡氧化物(ITSO)、氧化锌等金属氧化物或氮化钛、氮化钽、氮化钼、氮化钨等金属氮化物。

位于绝缘层110与导电层112之间的金属氧化物层114被用作防止绝缘层110所包含的氧扩散到导电层112一侧的阻挡膜。再者,金属氧化物层114还被用作防止导电层112所包含的氢或水扩散到绝缘层110一侧的阻挡膜。金属氧化物层114例如可以使用至少与绝缘层110相比不容易使氧及氢透过的材料。

借助于金属氧化物层114,在导电层112使用如铝或铜等容易抽吸氧的金属材料的情况下,也可以防止氧从绝缘层110扩散到导电层112。此外,在导电层112包含氢的情况下,也可以防止氢从导电层112通过绝缘层110扩散到半导体层108。其结果是,半导体层108的沟道形成区域中的载流子浓度可以为极低。

作为金属氧化物层114,可以使用绝缘材料或导电材料。当金属氧化物层114具有绝缘性时,该金属氧化物层114被用作栅极绝缘层的一部分。另一方面,当金属氧化物层114具有导电性时,该金属氧化物层114被用作栅电极的一部分。

作为金属氧化物层114,优选使用其介电常数比氧化硅高的绝缘材料。尤其是,优选使用氧化铝膜、氧化铪膜或铝酸铪膜等,因为可以降低驱动电压。

作为金属氧化物层114可以使用金属氧化物。例如,可以使用氧化铟、铟锌氧化物、铟锡氧化物(ITO)、含有硅的铟锡氧化物(ITSO)等含有铟的氧化物。优选使用包含铟的导电氧化物,因为其导电性高。此外,ITSO在包含硅时不容易结晶化,具有高平坦性,由此ITSO与在其上形成的膜的紧密性得到提高。作为金属氧化物层114,能够使用氧化锌、含有镓的氧化锌等金属氧化物。此外,金属氧化物层114也可以具有上述材料的叠层结构。

作为金属氧化物层114,优选使用包含一个以上的与半导体层108相同的元素的氧化物材料。尤其是,优选使用可应用于上述半导体层108的氧化物半导体材料。此时,通过使用利用与半导体层108相同的溅射靶材而形成的金属氧化物膜作为金属氧化物层114,可以共用设备,所以这是优选的。

此外,在半导体层108和金属氧化物层114的双方都使用包含铟及镓的金属氧化物材料的情况下,通过将其镓组成(含有比例)高于半导体层108的材料用于金属氧化物层114,可以提高对氧的阻挡性,所以这是优选的。此时,通过将其铟组成高于金属氧化物层114的材料用于半导体层108,可以提高晶体管100的场效应迁移率。

金属氧化物层114优选利用溅射装置形成。例如,在利用溅射装置形成氧化物膜时,通过在包含氧气体的气氛下形成该氧化物膜,可以适当地对绝缘层110或半导体层108中添加氧。

半导体层108具有隔着绝缘层110与导电层112重叠的沟道形成区域。此外,半导体层108具有夹持该沟道形成区域的一对区域108N。区域108N是半导体层108中的不与导电层112和绝缘层110重叠的区域且与绝缘层116接触的区域。

此外,区域108N也可以说是与沟道形成区域相比电阻更低的区域、载流子浓度更高的区域、氧缺陷密度更高的区域、杂质浓度更高的区域或呈现n型的区域。

区域108N是包含杂质元素(第一元素)的区域。作为该杂质元素,例如可以举出氢、硼、碳、氮、氟、磷、硫、砷、铝、镁或稀有气体等。作为稀有气体的典型例子,有氦、氖、氩、氪以及氙等。特别是,优选包含硼、磷、镁或铝。此外,也可以包含这些元素中的两种以上。

在此,区域108N的杂质的浓度优选具有越接近绝缘层116浓度越高的浓度梯度。因此,与整个区域108N具有均匀的浓度的情况相比,可以进一步降低区域108N的杂质元素的总量,由此可以将因制造工序中加热等而有可能扩散到沟道形成区域的杂质量保持为少量水平。由此,越靠近区域108N的上部,电阻越低,从而可以更有效地降低与导电层120a(或导电层120b)之间的接触电阻。

如后面所述,对区域108N添加杂质元素的处理可以使用绝缘层110作为掩模进行。由此,可以自对准地形成区域108N。

区域108N优选具有杂质的浓度为1×1019atoms/cm3以上且1×1023atoms/cm3以下,优选为5×1019atoms/cm3以上且5×1022atoms/cm3以下,更优选为1×1020atoms/cm3以上且1×1022atoms/cm3以下的区域。

例如,可以利用二次离子质谱分析(SIMS:Secondary Ion Mass Spectrometry)、X射线光电子能谱(XPS:X-ray Photoelectron Spectroscopy)等分析法分析出区域108N所包含的杂质的浓度。在利用XPS分析技术的情况下,通过组合来自表面一侧或背面一侧的离子溅射和XPS分析,可以得知深度方向上的浓度分布。

区域108N中的杂质元素优选在被氧化的状态下存在。例如,作为杂质元素,优选使用硼、磷、镁、铝、硅等容易被氧化的元素。这种容易被氧化的元素可以在与半导体层108中的氧键合而被氧化了的状态下稳定地存在,因此,即使在后面的工序中被施加高温(例如为400℃以上、600℃以上、800℃以上),也可以抑制脱离。此外,杂质元素夺取半导体层108中的氧,由此在区域108N中产生很多氧空位(Vo)。膜中的氢进入该氧空位(Vo)而成的缺陷(以下称为VoH)成为载流子供给源,使得区域108N成为极低电阻状态。

此外,当在后面的工序中进行施加高温度的处理时,有时多量的氧从外部或区域108N附近的膜被供应到区域108N而导致电阻上升。因此,在进行施加高温度的处理时优选以使用氧阻挡性高的绝缘层116覆盖半导体层108的状态进行处理。

绝缘层116以与半导体层108的区域108N接触的方式设置。

绝缘层116被用作向区域108N的氢供应源。例如,绝缘层116优选为通过加热释放氢的膜。通过以与区域108N接触的方式设置上述绝缘层116而在形成绝缘层116后进行加热处理,可以向区域108N供应氢而降低电阻。

绝缘层116优选为通过作为进行成膜时使用的成膜气体使用包含氢的气体而形成的膜。由此,也可以在形成绝缘层116时也可以有效地向区域108N供应氢。

作为绝缘层116,例如可以使用氮化硅、氮氧化硅、氧氮化硅、氮化铝、氮氧化铝等绝缘膜。

通过如上所述那样地被添加杂质元素,区域108N处于包括多个氧空位的状态。因此,除了由于半导体层108中的氢以外,还由于从绝缘层116被供应的氧可以进一步提高载流子浓度。

绝缘层118被用作保护晶体管100的保护层。绝缘层118例如可以使用氧化物或氮化物等无机绝缘材料。更具体而言,可以使用氮化硅、氮氧化硅、氧氮化硅、氧化铝、氧氮化铝、氮化铝、氧化铪、铝酸铪等无机绝缘材料。此外,也可以使用绝缘层118作为平坦化层。此时,作为绝缘层118可以使用有机树脂材料。

注意,在此示出保护层具有绝缘层116与绝缘层118的叠层结构的例子,但是如果不需要则可以不设置绝缘层118。此外,绝缘层118也可以具有两层以上的叠层结构。

在此,对半导体层108以及有可能形成在半导体层108中的氧空位进行说明。

形成在半导体层108的沟道形成区域中的氧空位对晶体管特性造成影响而引起问题。例如,当在半导体层108中形成氧空位时,有时氢进入该氧空位而成为载流子供应源。当在沟道形成区域中产生载流子供应源时,晶体管100的电特性发生变动,典型为阈值电压的漂移。因此,在沟道形成区域中,氧空位越少越好。

于是,在本发明的一个方式中,半导体层108的沟道形成区域附近的绝缘膜,具体而言,位于沟道形成区域上方的绝缘层110及位于沟道形成区域下方的绝缘层103包含氧化物膜。通过利用制造工序中的加热等将氧从绝缘层103及绝缘层110移动到沟道形成区域,可以减少沟道形成区域中的氧空位。

半导体层108优选具有相对于元素M的In的原子个数比大于1的区域。In的含有率越高,越可以提高晶体管的场效应迁移率。

在此,在包含In、Ga及Zn的金属氧化物中,In与氧的键合力比Ga与氧的键合力弱,因此在In的含有率高的情况下,氧空位容易形成在金属氧化物膜中。此外,在使用上述以元素M表示的金属元素代替Ga的情况下,也有同样的倾向。当在金属氧化物膜中存在较多的氧空位时,晶体管的电特性及可靠性下降。

但是,在本发明的一个方式中,能够对包含金属氧化物的半导体层108的沟道形成区域中供应极多的氧,由此可以使用In的含有率高的金属氧化物材料。因此,可以实现具有极高的场效应迁移率、稳定的电特性以及高可靠性的晶体管。

例如,可以适当地使用相对于元素M的In的原子个数比为1.5以上、2以上、3以上、3.5以上或4以上的金属氧化物。

尤其是,半导体层108的In、M及Zn的原子个数的比例优选为In∶M∶Zn=4∶2∶3或其附近。或者,半导体层108的In、M及Zn的原子个数的比例优选为In∶M∶Zn=5∶1∶6或其附近。此外,在半导体层108的组成中,半导体层108的In、M及Zn的原子个数的比例也可以大致相等。也就是说,半导体层108可以包含In、元素M及Zn的原子个数的比例为In∶M∶Zn=1∶1∶1或其附近的材料。

例如,通过将上述场效应迁移率高的晶体管用于生成栅极信号的栅极驱动器,可以提供边框宽度窄(也称为窄边框)的显示装置。此外,通过将上述场效应迁移率高的晶体管用于源极驱动器(尤其是,与源极驱动器所包括的移位寄存器的输出端子连接的解复用器),可以提供一种与显示装置连接的布线数较少的显示装置。

注意,即使半导体层108包括相对于元素M的In的原子个数比大于1的区域,也在半导体层108的结晶性较高时,有时场效应迁移率降低。半导体层108的结晶性例如可以通过X射线衍射(XRD:X-Ray Diffraction)或透射电子显微镜(TEM)进行分析。

这里,通过降低半导体层108的沟道形成区域的杂质浓度及缺陷态密度(减少氧空位),可以降低膜中的载流子浓度。将该金属氧化物膜用于半导体层的沟道形成区域的晶体管很少具有负阈值电压的电特性(也称为常开启特性)。此外,使用该金属氧化物膜的晶体管具有关态电流极小的特性。

通过将结晶性高的金属氧化物膜用于半导体层108,可以抑制在加工半导体层108时或在形成绝缘层110时的损伤,由此可以实现高可靠性的晶体管。另一方面,通过将结晶性较低的金属氧化物膜用于半导体层108,可以提高导电性,由此可以实现场效应迁移率高的晶体管。

例如,半导体层108优选使用具有后面所述的CAAC(c-axis aligned crystal)结构的金属氧化物膜、具有nc(nano crystal)结构的金属氧化物膜或混有CAAC结构和nc结构的金属氧化物膜。

此外,半导体层108也可以具有两层以上的叠层结构。

例如,可以使用层叠其组成彼此不同的两个以上的金属氧化物膜而成的半导体层108。例如,当使用In-M-Zn氧化物时,优选层叠利用如下溅射靶材形成的膜中的两个以上而使用,该溅射靶材的In、元素M及Zn的原子个数的比例为In∶M∶Zn=5∶1∶6、In∶M∶Zn=4∶2∶3、In∶M∶Zn=1∶1∶1、In∶M∶Zn=2∶2∶1、In∶M∶Zn=1∶3∶4、In∶M∶Zn=1∶3∶2或其附近。

此外,可以使用层叠其结晶性彼此不同的两个以上的金属氧化物膜而成的半导体层108。在此情况下,优选使用相同的氧化物靶材在不同的成膜条件下以不暴露于大气的方式连续地形成该金属氧化物膜。

此时,作为半导体层108可以采用具有nc结构的金属氧化物膜与具有CAAC结构的金属氧化物膜的叠层结构。或者,可以采用具有nc结构的金属氧化物膜与具有nc结构的金属氧化物膜的叠层结构。此外,适用于这些金属氧化物膜的金属氧化物的功能或材料结构可以援用后面所述的CAC(Cloud-Aligned Composite)的记载。

例如,将先形成的第一金属氧化物膜的成膜时的氧流量比设定为比后形成的第二金属氧化物膜的成膜时的氧流量比小。或者,采用在第一金属氧化物膜的成膜时不引入氧的条件。由此,可以在第二金属氧化物膜的成膜时有效地供应氧。此外,第一金属氧化物膜可以具有比第二金属氧化物膜低的结晶性以及比第二金属氧化物膜高的导电性。另一方面,通过使设置在上部的第二金属氧化物膜的结晶性高于第一金属氧化物膜的结晶性,可以抑制在半导体层108的加工时或绝缘层110的成膜时造成的损伤。

更具体而言,第一金属氧化物膜的成膜时的氧流量比为0%以上且低于50%,优选为0%以上且30%以下,更优选为0%以上且20%以下,典型为10%。第二金属氧化物膜的成膜时的氧流量比为50%以上且100%以下,优选为60%以上且100%以下,更优选为80%以上且100%以下,进一步优选为90%以上且100%以下,典型为100%。此外,虽然可以使第一金属氧化物膜与第二金属氧化物膜的成膜时的压力、温度、电力等的条件不同,但是通过使氧流量比以外的条件相同,可以缩短成膜工序所需要的时间,所以是优选的。

通过采用上述结构,可以实现电特性良好且可靠性高的晶体管100。

以下,说明部分结构与上述结构例子1不同的晶体管的结构例子。注意,以下有时省略与上述结构例子1重复的部分的说明。此外,在以下所示的附图中,具有与上述结构例子1同样的功能的部分使用相同的阴影线而有时不附加附图标记。

<结构例子2>

图5A是晶体管100A的俯视图,图5B是晶体管100A的沟道长度方向的截面图,图5C是晶体管100A的沟道宽度方向的截面图。图6A示出图5B中的以点划线围绕的区域P的放大图。图6B示出图5C中的以点划线围绕的区域R的放大图。

晶体管100A具有导电层112的端部位于金属氧化物层114的端部的内侧,主要在这一点上与晶体管100不同。此外,绝缘层116与金属氧化物层的顶面及侧面接触地设置。

在晶体管100A中,导电层112的端部位于金属氧化物层114的端部的内侧。换言之,金属氧化物层114至少在绝缘层110上包括突出到导电层112的端部的外侧的部分。

在导电层112的端部位于金属氧化物层114的端部的内侧时,导电层112及金属氧化物层114的侧面的台阶平缓,形成在导电层112及金属氧化物层114上的层(例如,绝缘层116)的台阶覆盖性得到提高,由此可以抑制该层中出现如断开或空洞等不良现象。

在形成导电层112及金属氧化物层114时,可以适当地采用湿蚀刻法。此外,通过在金属氧化物层114中使用其蚀刻速度比导电层112低的材料,可以使导电层112的端部位于金属氧化物层114的端部的内侧。再者,可以以同一工序形成金属氧化物层114及导电层112来提高生产率。

以上是结构例子2的说明。

<结构例子3>

图7A是晶体管100B的俯视图,图7B是晶体管100B的沟道长度方向的截面图,图7C是晶体管100B的沟道宽度方向的截面图。图8A示出图7B中的以点划线围绕的区域P的放大图。图8B示出图7B中的以点划线围绕的区域Q的放大图。图8C示出图7C中的以点划线围绕的区域R的放大图。

晶体管100B与晶体管100A不同之处主要在于绝缘层116具有叠层结构。绝缘层116也可以具有两层以上的叠层结构。在绝缘层116具有叠层结构的情况下,不局限于由相同材料构成的叠层结构,也可以具有由不同材料构成的叠层结构。

图7B、图7C、图8A、图8B及图8C示出绝缘层116具有绝缘层116a与绝缘层116a上的绝缘层116b的两层结构的例子。作为绝缘层116a及绝缘层116b,可以使用可用于绝缘层116的材料。绝缘层116a及绝缘层116b可以使用相同材料也可以使用不同材料。绝缘层116a及绝缘层116b可以使用相同种类的材料的绝缘膜,所以有时不能明确地确认到绝缘层116a与绝缘层116b的界面。因此,在本实施方式中以虚线表示绝缘层116a与绝缘层116b的界面。

如图8A及图8B所示,绝缘层116与区域108N接触,并被用作对区域108N的氢供给源。例如,绝缘层116优选为通过加热而释放氢的膜。

绝缘层116可以在包含氢的气氛下形成。例如,绝缘层116优选使用包含氢的成膜气体通过等离子体CVD法而形成。例如,作为绝缘层116,可以使用包含硅烷气体和氨气体的成膜气体形成氮化硅膜。除了硅烷气体之外还使用氨气体,由此可以增加绝缘层116的含氢量。此外,当形成绝缘层116时,也可以将氢供应到半导体层108的露出部分。

但是,当在包含氢的气氛下形成绝缘层116的情况下,有时在形成绝缘层116时半导体层108的露出区域还原。如果半导体层108的表面还原,半导体层108表面的粗糙度就增高,有时形成在半导体层108上方的层(例如,绝缘层116等)中发生断开或空洞等不良。

于是,用来形成位于半导体层108一侧的绝缘层116a的气氛的含氢量优选比用来形成绝缘层116b的气氛的含氢量少。例如,当形成绝缘层116a及绝缘层116b时,可以使用硅烷、氮及氨的混合气体,其中用来形成绝缘层116a的氨的流量少于用来形成绝缘层116b的氨的流量。此外,当形成绝缘层116a时,可以使用硅烷及氮的混合气体,当形成绝缘层116b时可以使用硅烷、氮及氨的混合气体。再者,与绝缘层116b相比,绝缘层116a优选具有氢浓度低的区域。通过具有这种结构,可以抑制半导体层108表面的还原。

例如,在绝缘层116a及绝缘层116b使用通过等离子体CVD法而形成的氮化硅膜的情况下,也有时因两者的膜密度不同而从绝缘层110的截面上的透射电子显微镜(TEM)图像等观察到两者的对比度的不同,即两者的边界。例如,与绝缘层116b相比,绝缘层116a有时具有膜密度高的区域。在TEM观察中,膜密度高则透射电子(TE)图像浓(暗),膜密度低则透射电子(TE)图像淡(明)。因此,在透射电子(TE)图像中,有时与绝缘层116b相比绝缘层116a呈浓(暗)图像。此外,有时与绝缘层116b相比绝缘层116a具有氢浓度低的区域。绝缘层116a和绝缘层116b的氢浓度的差异例如可以通过二次离子质谱分析(SIMS)评测。

绝缘层116b优选使用能够阻挡氢、水及氧的材料。此外,绝缘层116b的对氢、水及氧的阻挡性优选高于绝缘层116a的对氢、水及氧的阻挡性。通过设置在绝缘层116a上的绝缘层116b能够阻挡氢、水及氧,可以在抑制氢及水从外部扩散到半导体层108的同时抑制氧从半导体层108向外部脱离,由此可以实现高可靠性晶体管。

优选的是,与半导体层108接触的绝缘层116的缺陷少。例如,在将氮化硅用于绝缘层116的情况下,氮化硅膜中的缺陷典型为Kcenter等。K center起因于硅的悬空键,可以通过电子自旋共振法(ESR:Electron Spin Resonance)评测。

当用来形成绝缘层116a的气氛的含氢量少于用来形成绝缘层116b的气氛的含氢量时,有时绝缘层116a中的缺陷多于绝缘层116b中的缺陷。因此,在绝缘层116只有绝缘层116a的单层结构的情况下,整个绝缘层116中的缺陷增多。为此,通过使绝缘层116具有绝缘层116a及绝缘层116b的叠层结构,可以减少整个绝缘层116中的缺陷。

绝缘层116b的厚度优选为绝缘层116a的厚度的0.5倍以上且30倍以下,更优选为1倍以上且25倍以下,进一步优选为2倍以上且20倍以下,更进一步优选为3倍以上且10倍以下,还进一步优选为4倍以上且5倍以下。通过使绝缘层116具有叠层结构,可以使绝缘层116阻挡氢、水及氧并抑制在形成绝缘层116时半导体层108表面还原,还可以减少绝缘层116的含缺陷量。

此外,绝缘层116a及绝缘层116b优选都以不接触于大气的方式使用等离子体CVD装置连续地形成。通过连续地形成,可以抑制杂质附着于绝缘层116a与绝缘层116b的界面。此外,绝缘层116a、绝缘层116b及绝缘层118优选都以不接触于大气的方式使用等离子体CVD装置连续地形成。通过连续地形成,可以抑制杂质附着于绝缘层116a与绝缘层116b的界面及绝缘层116b与绝缘层118的界面。

以上是结构例子3的说明。

<结构例子4>

图9A是晶体管100C的俯视图,图9B是晶体管100C的沟道宽度方向的截面图,图9C是晶体管100C的沟道宽度方向的截面图。

晶体管100C在衬底102与绝缘层103间包括导电层106,主要在这一点上与晶体管100不同。导电层106具有与半导体层108的沟道形成区域、金属氧化物层114及导电层112重叠的区域。

在晶体管100C中,导电层106被用作第一栅电极(也称为底栅电极),导电层112被用作第二栅电极(也称为顶栅电极)。此外,绝缘层103的一部分被用作第一栅极绝缘层,绝缘层110的一部分被用作第二栅极绝缘层。

半导体层108的与导电层112和导电层106中的至少一个重叠的部分被用作沟道形成区域。注意,以下为了容易说明,有时将半导体层108的与导电层112重叠的部分称为沟道形成区域,但是实际上沟道也有可能形成在不与导电层112重叠而与导电层106重叠的部分(包括区域108N的部分)。

如图9A及图9C所示,导电层106也可以通过设置在金属氧化物层114、绝缘层110及绝缘层103中的开口142电连接于导电层112。由此,可以对导电层106及导电层112供应相同电位。

导电层106可以使用与导电层112、导电层120a或导电层120b同样的材料。尤其是,导电层106优选使用包含铜的材料,此时可以降低布线电阻。此外,在导电层106使用包含钨、钼等的高熔点金属的材料时,可以在后面的工序中以高温度进行处理。

如图9A及图9C所示,导电层112及导电层106优选在沟道宽度方向上突出到半导体层108的端部的外侧。此时,如图9C所示,形成沟道宽度方向的半导体层108整体隔着绝缘层110及绝缘层103被导电层112、导电层106覆盖的结构。

通过采用上述结构,可以由通过一对栅电极产生的电场电围绕半导体层108。此时,尤其优选对导电层106及导电层112供应相同电位。由此,可以有效地对半导体层108施加用来引起沟道的电场,所以可以增大晶体管100C的通态电流。因此,也可以使晶体管100C微型化。

此外,也可以采用不连接导电层112及导电层106的结构。此时,也可以对一对栅电极中的一方供应恒电位且对另一方供应用来驱动晶体管100C的信号。在此情况下,可以通过对一方的栅电极供应的电位控制利用另一方的栅电极驱动晶体管100C时的阈值电压。

绝缘层103也可以具有叠层结构。图9B及图9C示出绝缘层103具有从导电层106一侧依次层叠有绝缘层103a、绝缘层103b、绝缘层103c及绝缘层103d的结构的例子。绝缘层103a与导电层106接触。绝缘层103a优选能够阻挡包含在导电层106中的金属元素。关于绝缘层103a、绝缘层103b、绝缘层103c及绝缘层103d可以参照上面记载,所以省略详细的说明。

此外,例如在作为导电层106使用不容易扩散到绝缘层103的金属膜或合金膜的情况下,可以采用不设置绝缘层103a而层叠绝缘层103b、绝缘层103c及绝缘层103d这三个绝缘膜的结构。

通过采用具有这种叠层结构的绝缘层103,晶体管可以具有极高的可靠性。

以上是结构例子4的说明。

<制造方法例子1>

以下,参照附图说明本发明的一个方式的半导体装置的制造方法。在此,以在上述结构例子中示出的晶体管100C为例进行说明。

构成半导体装置的薄膜(绝缘膜、半导体膜、导电膜等)可以通过溅射法、化学气相沉积(CVD)法、真空蒸镀法、脉冲激光沉积(PLD)法、原子层沉积(ALD)法等形成。作为CVD法,可以举出等离子体增强化学气相沉积(PECVD)法、热CVD法等。此外,作为热CVD法的方法之一,可以举出有机金属化学气相沉积(MOCVD)法。

构成半导体装置的薄膜(绝缘膜、半导体膜、导电膜等)可以利用旋涂法、浸渍法、喷涂法、喷墨法、分配器法、丝网印刷法、胶版印刷法、刮刀(doctor knife)法、狭缝式涂布法、辊涂法、帘式涂布法、刮刀式涂布法等方法形成。

此外,当对构成半导体装置的薄膜进行加工时,可以利用光刻法等进行加工。除了上述方法以外,还可以利用纳米压印法、喷砂法、剥离法等对薄膜进行加工。此外,可以利用金属掩模等遮蔽掩模的成膜方法直接形成岛状薄膜。

光刻法典型地有如下两种方法。一个是在要进行加工的薄膜上形成抗蚀剂掩模,通过蚀刻等对该薄膜进行加工,并去除抗蚀剂掩模的方法。另一个是在形成感光性薄膜之后,进行曝光及显影来将该薄膜加工为所希望的形状的方法。

在光刻法中,作为用于曝光的光,例如可以使用i线(波长365nm)、g线(波长436nm)、h线(波长405nm)或将这些光混合了的光。此外,还可以使用紫外线、KrF激光或ArF激光等。此外,也可以利用液浸曝光技术进行曝光。作为用于曝光的光,也可以使用极紫外光(EUV:Extreme Ultra-violet)或X射线。此外,也可以使用电子束代替用于曝光的光。当使用极紫外光、X射线或电子束时,可以进行极其精细的加工,所以是优选的。注意,在通过利用电子束等光束进行扫描而进行曝光时,不需要光掩模。

作为薄膜的蚀刻方法,可以利用干蚀刻法、湿蚀刻法及喷砂法等。

图10A至图14B的各图示出晶体管100C的制造工序的各阶段中的截面。在各图中,中央虚线左侧示出沟道长度方向的截面,中央虚线右侧示出沟道宽度方向的截面。

[导电层106的形成]

在衬底102上形成导电膜,对其进行蚀刻加工得到用作第一栅电极的导电层106(参照图10A)。

[绝缘层103的形成]

接着,以覆盖衬底102及导电层106的方式形成绝缘层103(参照图10B)。绝缘层103可以利用PECVD法、ALD法、溅射法等形成。

在此,作为绝缘层103,形成绝缘层103a、绝缘层103b、绝缘层103c及绝缘层103d的叠层。尤其是,构成绝缘层103的各绝缘层优选通过PECVD法而形成。

绝缘层103a优选具有阻挡杂质的功能。通过设置绝缘层103a,可以抑制来自绝缘层103的下层的杂质向绝缘层103的上层扩散。优选绝缘层103b的应力小且绝缘耐压性高。通过设置绝缘层103b,可以形成应力小且绝缘耐压性高的绝缘层103。优选的是,绝缘层103c很少释放包含氢的杂质并具有阻挡包含氢的杂质的功能。通过设置绝缘层103c,可以抑制氢扩散到沟道形成区域。优选的是,绝缘层103d的缺陷密度低且很少释放包含氢的杂质。

将说明绝缘层103a、绝缘层103b、绝缘层103c使用氮化硅膜且绝缘层103d使用氧氮化硅膜的情况。通过使用硅烷、氮及氨的混合气体的等离子体CVD法形成绝缘层103a。接着,使用氨流量多于绝缘层103a的混合气体形成应力小且绝缘耐压性高的绝缘层103b。接着,使用氨流量少于绝缘层103b的混合气体形成包含氢的杂质的释放量少且具有阻挡包含氢的杂质的功能的绝缘层103c。接着,使用硅烷及一氧化二氮的混合气体形成缺陷密度低且包含氢的杂质的释放量少的绝缘层103d,由此可以形成绝缘层103。此外,通过在同一处理室中切换成膜条件,可以在真空中连续地形成绝缘层103a、绝缘层103b、绝缘层103c及绝缘层103d,由此可以以高生产率形成绝缘层103。

此外,通过在形成绝缘层103c后在包含氧的气氛下进行等离子体处理来使绝缘层103c表面氧化,可以在绝缘层103c上形成绝缘层103d。

有时绝缘层103b的密度低于绝缘层103a及绝缘层103c。绝缘层103a、绝缘层103b及绝缘层103c的膜密度的不同例如可以通过TEM图像的浓度(亮度)评价。此外,有时绝缘层103b的氢浓度高于绝缘层103a及绝缘层103c。绝缘层103a、绝缘层103b及绝缘层103c的氢浓度的不同例如可以通过二次离子质谱分析(SIMS)评测。

也可以在形成绝缘层103后进行对绝缘层103供应氧的处理。例如,可以在氧气氛下进行等离子体处理或加热处理等。或者,也可以通过等离子体离子掺杂法或离子注入法等对绝缘层103供应氧。

[半导体层108的形成]

接着,通过在绝缘层103上形成用作半导体层108的金属氧化物膜108f(参照图10C)。

金属氧化物膜108f优选通过使用金属氧化物靶材的溅射法形成。

在形成金属氧化物膜108f时,也可以混合氧气体和惰性气体(例如,氦气体、氩气体、氙气体等)。注意,在形成金属氧化物膜时的成膜气体整体中所占的氧气体的比例(氧流量比)越高,金属氧化物膜的结晶性可以越高,可以实现具有高可靠性的晶体管。另一方面,氧流量比越低,金属氧化物膜的结晶性越低,可以实现通态电流高的晶体管。

在半导体层108具有叠层结构的情况下,优选使用相同的溅射靶材在相同的成膜室中连续形成膜,这是因为可以得到良好的界面。尤其是,虽然可以使各金属氧化物膜的成膜时的压力、温度、电力等的条件不同,但是通过使氧流量比以外的条件相同,可以缩短成膜工序所需要的时间,所以是优选的。此外,在层叠组成不同的金属氧化物膜的情况下,优选以不暴露于大气的方式连续形成膜。

在此,金属氧化物膜108f优选以成为具有CAAC结构的金属氧化物膜、具有nc结构的金属氧化物膜或者混有CAAC结构和nc结构的金属氧化物膜的方式设定成膜条件。注意,形成的金属氧化物膜为CAAC结构的成膜条件及成为nc结构的成膜条件根据所使用的溅射靶材的组成而不同,所以可以根据其组成适当地设定衬底温度、氧流量比、压力、电力等。

作为金属氧化物膜108f的成膜条件,衬底温度可以设定为室温以上且450℃以下,优选为室温以上且300℃以下,更优选为室温以上且200℃以下,进一步优选为室温以上且140℃以下。例如,在使用大型玻璃衬底或树脂衬底作为衬底102的情况下,衬底温度优选为室温以上且低于140℃,这是因为可以提高生产率的缘故。此外,通过在衬底温度为室温或者没进行加热的状态下形成金属氧化物膜,可以降低结晶性。

此外,优选在形成金属氧化物膜108f之前进行用来使附着于绝缘层103表面的水、氢、有机物等脱离的处理或者进行将氧供应到绝缘层103中的处理。例如,可以在减压气氛下以70℃以上且200℃以下的温度进行加热处理。或者,也可以在含氧气氛下进行等离子体处理。此外,当在包含一氧化二氮气体的气氛下进行等离子体处理时,可以适当地去除绝缘层103的表面的有机物。优选的是,在这种处理之后,以不使绝缘层103的表面暴露于大气的方式连续地形成金属氧化物膜。

接着,对金属氧化物膜108f进行加工,来形成岛状半导体层108(参照图10D)。

当对金属氧化物膜进行加工时,可以使用湿蚀刻法和干蚀刻法中的一个或两个。此时,也可以对不与半导体层108重叠的绝缘层103d的一部分进行蚀刻来去除。通过去除绝缘层103d的一部分,半导体层108与绝缘层103d的顶面形状大致一致。此外,通过去除绝缘层103d的一部分,绝缘层103c的一部分露出而后面形成的绝缘层116与绝缘层103c接触。

此外,也可以在形成金属氧化物膜后或者将金属氧化物膜加工为半导体层108后进行加热处理,以去除金属氧化物或半导体层108中的氢或水。典型地,可以将加热处理的温度设定为150℃以上且低于衬底的应变点、250℃以上且450℃以下、或者300℃以上且450℃以下。此外,也可以在形成金属氧化物膜之后或将金属氧化物膜加工为半导体层108之后不进行加热处理。此外,加热处理也可以在形成金属氧化物膜之后的任意阶段进行。此外,也可以兼作后面的加热处理或施加热的工序。

可以在包含稀有气体或氮的气氛中进行加热处理。或者,也可以在该气氛中进行加热之后在包含氧的气氛中进行加热。作为含氮气氛或含氧气氛,也可以使用超干燥空气(CDA:Clean Dry Air)。此外,上述加热处理的气氛优选不包含氢、水等。此外,通过使用露点为-60℃以下,优选为-100℃以下的高纯度气体,可以尽可能地防止氢、水等混入半导体层108中。此外,该加热处理可以使用电炉、快速热退火(RTA:Rapid Thermal Annealing)装置等。通过使用RTA装置,可以缩短加热处理时间。

此外,优选在形成半导体层108之后立刻形成绝缘膜110f。在半导体层108的表面被露出的状态中,有时水附着于半导体层108的表面上。在水附着于半导体层108的表面上时,通过后面的加热处理等氢扩散到半导体层108中而有时形成VOH。VOH有可能成为载流子的发生源,所以附着于半导体层108的水越少越好。

[绝缘膜110f的形成]

接着,以覆盖绝缘层103及半导体层108的方式形成绝缘膜110f(图11A)。

绝缘膜110f是后面成为绝缘层110的膜。作为绝缘膜110f例如优选通过使用等离子体增强化学气相沉积装置(被称为PECVD装置或简称为等离子体CVD装置)形成氧化硅膜或氧氮化硅膜等氧化物膜。此外,也可以通过利用微波的PECVD法形成。

在此,依次层叠后面分别成为绝缘层110a、绝缘层110b及绝缘层110c的绝缘膜110A、绝缘膜110B及绝缘膜110C。尤其是,构成绝缘膜110f的各绝缘膜优选利用PECVD法形成。

将说明使用氧氮化硅膜作为绝缘膜110A、绝缘膜110B及绝缘膜110C的情况。例如,通过使用硅烷及一氧化二氮的混合气体的等离子体CVD法形成绝缘膜110A。接着,在使用与绝缘膜110A相比相对于一氧化二氮的流量的硅烷流量比高的混合气体且功率高的条件下形成绝缘膜110B。接着,在使用与绝缘膜110B相比相对于一氧化二氮流量的硅烷的流量比低的混合气体且压力低的条件下形成绝缘膜110C,由此可以形成绝缘膜110f。此外,通过在同一处理室中切换成膜条件,可以在真空中连续地形成绝缘膜110A、绝缘膜110B以及绝缘膜110C,由此可以以高生产率形成绝缘膜110f。

也可以在形成绝缘膜110f之后进行加热处理。通过进行加热处理,可以去除绝缘膜110f中的杂质及绝缘膜110f表面上的水。加热处理可以在含氮、氧、稀有气体中的一个以上的气氛下以200℃以上且400℃以下的温度进行。此外,也可以在形成绝缘膜110f之后不进行加热处理。此外,加热处理也可以在形成绝缘膜110f之后的任意阶段进行。此外,也可以兼作后面的加热处理或施加热的工序。

优选在绝缘膜110f的成膜之前对半导体层108的表面进行等离子体处理。通过该等离子体处理,可以减少附着于半导体层108的表面的水等的杂质。因此,可以减少半导体层108与绝缘膜110f的界面中的杂质,所以可以实现可靠性高的晶体管。尤其是,从半导体层108的形成到绝缘膜110f的成膜之间半导体层108的表面暴露于大气的情况下,进行等离子体处理是优选的。等离子体处理例如可以在包含氧、臭氧、氮、一氧化二氮、氩等的气氛下进行。此外,等离子体处理及绝缘膜110f的成膜优选以不暴露于大气的方式连续地进行。

在此,优选在形成绝缘膜110f之后进行加热处理。通过加热处理,可以去除含在绝缘膜110f中的或附着于表面的氢或水。此外,可以减少绝缘膜110f中的缺陷。

加热处理的条件可以参照上述条件。

也可以在形成绝缘膜110f之后或者进行去除上述氢或水的加热处理之后进行对绝缘膜110f供应氧的处理。例如,可以在含氧气氛下进行等离子体处理或加热处理等。或者,也可以通过等离子体离子掺杂法、离子注入法等对绝缘膜110f供应氧。在等离子体处理中,例如适当地利用PECVD装置。在利用PECVD装置形成绝缘膜110f时,优选在形成绝缘膜110f之后在真空中连续进行等离子体处理。通过在真空中连续进行绝缘膜110f的形成和等离子体处理,可以提高生产率。

在进行对绝缘膜110f供应氧的处理之后进行加热处理的情况下,优选在绝缘膜110f上形成膜(例如,金属氧化物膜114f)之后进行加热处理。在以绝缘膜110f被露出的状态进行加热处理时,有时供应到绝缘膜110f的氧脱离到绝缘膜110f之外。通过在绝缘膜110f上形成膜(例如,金属氧化物膜114f)之后进行加热处理,可以抑制供应到绝缘膜110f的氧脱离到绝缘膜110f之外。

[金属氧化物膜114f的形成]

接着,以覆盖绝缘膜110f的方式形成金属氧化物膜114f(图11B)。

金属氧化物膜114f是后面成为金属氧化物层114的膜。尤其是,金属氧化物膜114f例如优选在包含氧的气氛下利用溅射法形成。由此,可以在形成金属氧化物膜114f时对绝缘膜110f供应氧。

在与上述半导体层108同样通过使用包含金属氧化物的氧化物靶材的溅射法形成金属氧化物膜114f的情况下,可以援用上述记载。

例如,金属氧化物膜114f可以通过作为成膜气体使用氧且使用金属靶材的反应性溅射法来形成。在作为金属靶材使用铝的情况下,可以形成氧化铝膜。

当形成金属氧化物膜114f时,引入到成膜装置的成膜室内的成膜气体的总流量中的氧流量的比例(氧流量比)或成膜室内的氧分压越高,越可以增大供应给绝缘膜110中的氧量。氧流量比或氧分压例如大于0%且为100%以下,优选为10%以上且100%以下,更优选为20%以上且100%以下,进一步优选为30%以上且100%以下,进一步优选为40%以上且100%以下。尤其是,优选将氧流量比设定为100%,来使氧分压尽量接近于100%。

如此,通过在包含氧的气氛下利用溅射法形成金属氧化物膜114f,可以当形成金属氧化物膜114f时在对绝缘膜110f供应氧的同时防止氧从绝缘膜110f脱离。其结果是,可以将极多的氧封闭在绝缘膜110f中。并且,通过后面的加热处理对半导体层108的沟道形成区域供应多量氧而可以降低沟道形成区域中的氧空位,由此可以实现可靠性高的晶体管。

作为金属氧化物膜114f的成膜条件,将衬底温度设定为室温以上且450℃以下,优选为室温以上且300℃以下,更优选为室温以上且200℃以下,进一步优选为室温以上且140℃以下即可。例如,在作为衬底102使用大型玻璃衬底或树脂衬底的情况下,在衬底温度为室温以上且低于140℃时生产率提高,所以是优选的。此外,在形成金属氧化物膜114f时的温度高时,金属氧化物膜114f的结晶性提高而有时蚀刻速度变低。在金属氧化物膜114f的成膜温度低时,金属氧化物膜114f的结晶性变低而有时蚀刻速度变高。此外,也可以适当地选择金属氧化物膜114f的成膜温度,以便对加工金属氧化物膜114f时使用的蚀刻剂来说很适合的蚀刻速度。

此外,也可以在形成金属氧化物膜114f之后进行加热处理,以将氧从绝缘膜110f供应到半导体层108。加热处理可以在含氮、氧、稀有气体中的一个以上的气氛下以200℃以上且400℃以下的温度进行。此外,也可以在形成金属氧化物膜114f之后不进行加热处理。此外,加热处理在形成金属氧化物膜114f之后的任意阶段进行。此外,也可以兼作后面的加热处理或施加热的工序。

[导电膜112f的形成]

接着,通过对金属氧化物膜114f、绝缘膜110f及绝缘层103的一部分进行蚀刻来形成到达导电层106的开口142。由此,可以使后面形成的导电层112与导电层106通过开口142电连接。

接着,在金属氧化物膜114f上形成将成为导电层112的导电膜112f(图11C)。导电膜112f优选通过使用金属或合金的溅射靶材的溅射法形成。

[绝缘层110、金属氧化物层114、导电层112的形成]

接着,在导电膜112f上形成抗蚀剂掩模115(参照图12A)。然后,去除不被该抗蚀剂掩模115覆盖的区域的导电膜112f及金属氧化物膜114f,来形成导电层112及金属氧化物层114(参照图12B)。

在形成导电层112及金属氧化物层114时,可以适当地使用湿蚀刻法。作为湿蚀刻法,例如可以使用包含过氧化氢的蚀刻剂。例如,可以使用包含磷酸、醋酸、硝酸、盐酸、硫酸中的一个以上的蚀刻剂。尤其是,在作为导电层112使用包含铜的材料时,可以适当地使用包含磷酸、醋酸及硝酸的蚀刻剂。

以导电层112及金属氧化物层114的端部位于抗蚀剂掩模115的轮廓的内侧的方式进行加工。导电层112及金属氧化物层114优选通过湿蚀刻法形成。通过调节蚀刻时间,可以控制区域108L的宽度L2。

在形成导电层112及金属氧化物层114时,也可以在使用各向异性蚀刻法对导电膜112f及金属氧化物膜114f进行蚀刻,然后利用各向同性蚀刻法对导电膜112f及金属氧化物膜114f的侧面进行蚀刻来使端面缩退(也称为侧面蚀刻)。由此,可以形成在俯视时其端部位于绝缘层110的内侧的导电层112及金属氧化物层114。

如图12B所示,在形成导电层112及金属氧化物层114时,有时不与导电层112重叠的区域的绝缘膜110f的厚度比与导电层112重叠的区域的绝缘膜110f的厚度薄。

此外,在形成导电层112及金属氧化物层114时,可以使用不同蚀刻条件或方法至少分为两次进行蚀刻。例如,也可以先对导电膜112f进行蚀刻,接着以不同蚀刻条件对金属氧化物膜114f进行蚀刻。

接着,在不被抗蚀剂掩模115覆盖的区域中去除绝缘膜110f来形成绝缘层110(参照图12C)。在形成绝缘层110时,可以使用湿蚀刻法及干蚀刻法中的任一方或双方。注意,可以以抗蚀剂掩模115被去除的状态形成绝缘层110,但是通过不去除抗蚀剂掩模115可以抑制导电层112的膜厚度减薄。此外,在形成绝缘层110时,也可以去除不被抗蚀剂掩模115覆盖的区域的绝缘层103d。

通过调整绝缘层110的形成条件,可以控制区域108L的宽度L2。例如,通过使用在形成绝缘层110时抗蚀剂掩模115缩退的条件,可以减少抗蚀剂掩模115的宽度。通过减少抗蚀剂掩模115的宽度,减少抗蚀剂掩模115与导电层112的端部的距离,其结果是,可以减少区域108L的宽度L2。

在形成绝缘层110后去除抗蚀剂掩模115。

在此,也可以进行去除杂质的洗涤。通过进行洗涤,可以去除附着于绝缘层110及半导体层108的被露出的区域的杂质而抑制晶体管的电特性及可靠性降低。作为杂质,例如可以举出蚀刻绝缘膜110f时附着的蚀刻气体或蚀刻剂的成分或者导电膜112f的成分、金属氧化物膜114f的成分等。

作为洗涤方法,可以使用利用洗涤液等的湿式洗涤或等离子体处理等。此外,也可以适当地组合上述洗涤而进行。湿式洗涤可以使用包含草酸、磷酸、氨水或氢氟酸等的洗涤液。

[绝缘层116、区域108N的形成(供应氢的处理)]

接着,进行对半导体层108被露出的区域供应氢的处理。在此,通过以与半导体层108被露出的区域接触的方式形成包含氢的绝缘层116,来供应氢(图13A)。

绝缘层116优选通过使用含氢的成膜气体的等离子体CVD法形成。例如,通过使用包含硅烷气体及氨气体的成膜气体形成氮化硅膜。通过除了硅烷气体以外还使用氨气体,可以在膜中包含多量氢。此外,在成膜时也可以对半导体层108的被露出的部分中供应氢。

优选的是,通过在形成绝缘层116后进行加热处理而将从绝缘层116释放的氢的一部分供应到半导体层108的一部分。加热处理优选在包含氮、氧和稀有气体中的一个以上的气氛下以150℃以上且450℃以下,优选以200℃以上且400℃以下的温度进行。

通过如上所述那样地供应氢,可以在半导体层108中形成电阻非常低的区域108N。

通过进行加热处理,可以将氧从绝缘层110供应到半导体层108的沟道形成区域。

[绝缘层118的形成]

接着,在绝缘层116上形成绝缘层118(图13B)。

在使用等离子体CVD法形成绝缘层118的情况下,当成膜温度过高时,包含在区域108N等中的杂质有可能扩散到包括半导体层108的沟道形成区域的周围部。其结果是,有沟道形成区域的电阻下降或者区域108N的电阻上升等担忧。绝缘层116或绝缘层118的成膜温度例如优选为150℃以上且400℃以下,更优选为180℃以上且360℃以下,进一步优选为200℃以上且250℃以下。通过在低温下形成绝缘层118,即使是沟道长度短的晶体管,也可以得到良好的电特性。

此外,也可以在形成绝缘层118之后进行加热处理。

[开口部141a、开口部141b的形成]

接着,通过光刻法在绝缘层118的所希望的位置形成掩模,然后对绝缘层118及绝缘层116部分地进行蚀刻,由此形成到达区域108N的开口部141a及开口部141b。

[导电层120a、导电层120b的形成]

接着,以覆盖开口部141a及开口部141b的方式在绝缘层118上形成导电膜,对该导电膜进行加工为所希望的形状,来形成导电层120a及导电层120b(图13C)。

通过上述工序,可以制造晶体管100C。

<制造方法例子2>

以下举出作为上述结构例子的晶体管100A所示的导电层112的端部位于金属氧化物层114的端部的内侧的结构例子进行说明。

到在导电膜112f上形成抗蚀剂掩模115的步骤与上述<制造方法例子1>相同(参照图12A)。

[绝缘层110、金属氧化物层114、导电层112的形成]

接着,去除不被该抗蚀剂掩模115覆盖的区域的导电膜112f及金属氧化物膜114f,来形成导电层112及金属氧化物层114(参照图14A)。

在形成导电层112及金属氧化物层114时,可以适当地使用湿蚀刻法。以导电层112及金属氧化物层114的端部位于抗蚀剂掩模115的轮廓的内侧的方式进行加工。通过调节蚀刻时间,可以控制区域108L的宽度L2。

在形成导电层112及金属氧化物层114时,也可以在使用各向异性蚀刻法对导电膜112f及金属氧化物膜114f进行蚀刻,然后利用各向同性蚀刻法对导电膜112f及金属氧化物膜114f的侧面进行蚀刻来使端面缩退。

如图14A所示,在形成导电层112及金属氧化物层114时,有时不与金属氧化物层114重叠的区域的绝缘膜110f的厚度比与金属氧化物层114重叠的区域的绝缘膜110f的厚度薄。

在形成导电层112及金属氧化物层114时,有时导电层112的端部相比于金属氧化物层114的端部缩退,不与导电层112重叠的区域的金属氧化物层114的厚度比与导电层112重叠的区域的金属氧化物层114的厚度薄。

接着,在不被抗蚀剂掩模115覆盖的区域中去除绝缘膜110f来形成绝缘层110(参照图14B)。在形成绝缘层110时,可以使用湿蚀刻法及干蚀刻法中的任一方或双方。注意,可以以抗蚀剂掩模115被去除的状态形成绝缘层110,但是通过不去除抗蚀剂掩模115可以抑制导电层112的膜厚度减薄。

在形成绝缘层110之后,去除抗蚀剂掩模115。

以下,形成绝缘层116之后的工序可以参照<制造方法例子1>的记载,所以省略其详细说明。

<半导体装置的构成要素>

接着,对本实施方式的半导体装置所包括的构成要素进行详细的说明。

[衬底]

虽然对衬底102的材料等没有特别的限制,但是至少需要具有能够承受后续的加热处理的耐热性。例如,可以使用以硅或碳化硅为材料的单晶半导体衬底或多晶半导体衬底、硅锗等化合物半导体衬底、SOI衬底、玻璃衬底、陶瓷衬底、石英衬底、蓝宝石衬底等作为衬底102。此外,也可以将在上述衬底上设置有半导体元件的衬底用作衬底102。

此外,作为衬底102,也可以使用柔性衬底,并且在柔性衬底上直接形成晶体管100等。或者,也可以在衬底102与晶体管100等之间设置剥离层。当剥离层上制造半导体装置的一部分或全部,然后将其从衬底102分离并转置到其他衬底上时可以使用剥离层。此时,也可以将晶体管100等转置到耐热性低的衬底或柔性衬底上。

[绝缘层103]

绝缘层103可以适当地使用溅射法、CVD法、蒸镀法、脉冲激光沉积(PLD)法等而形成。此外,绝缘层103例如可以使用氧化物绝缘膜或氮化物绝缘膜的单层或叠层。注意,为了提高绝缘层103与半导体层108的界面特性,绝缘层103中的至少与半导体层108接触的区域优选使用氧化物绝缘膜形成。此外,绝缘层103优选使用通过加热释放氧的膜。

绝缘层103例如可以使用氧化硅、氧氮化硅、氮氧化硅、氮化硅、氧化铝、氧化铪、氧化镓或者Ga-Zn氧化物等,并且以叠层或单层设置。

此外,当在绝缘层103的与半导体层108接触的一侧使用氮化硅膜等氧化物膜以外的膜时,优选对与半导体层108接触的表面进行氧等离子体处理等预处理使该表面或表面附近氧化。

[导电膜]

作为导电层106、用作源电极的导电层120a、用作漏电极的导电层120b,可以使用选自铬、铜、铝、金、银、锌、钼、钽、钛、钨、锰、镍、铁、钴的金属元素或以上述金属元素为成分的合金或者组合上述金属元素的合金等来分别形成。

此外,作为导电层106、导电层120a以及导电层120b,可以使用In-Sn氧化物、In-W氧化物、In-W-Zn氧化物、In-Ti氧化物、In-Ti-Sn氧化物、In-Zn氧化物、In-Sn-Si氧化物、In-Ga-Zn氧化物等的氧化物导电体或者金属氧化物膜。

这里,对氧化物导电体(OC:Oxide Conductor)进行说明。例如,氧化物导电体是通过如下步骤而得到的:在具有半导体特性的金属氧化物中形成氧空位,对该氧空位添加氢而在导带附近形成施主能级。其结果是,金属氧化物的导电性增高,而成为导电体。可以将成为导电体的金属氧化物称为氧化物导电体。

此外,作为导电层106等,也可以采用含有上述氧化物导电体(金属氧化物)的导电膜、含有金属或合金的导电膜的叠层结构。通过使用包含金属或合金的导电膜,可以降低布线电阻。此时,优选作为与被用作栅极绝缘膜的绝缘层接触的部分,使用包含氧化物导电体的导电膜。

此外,导电层106、导电层120a、导电层120b尤其优选包含选自上述金属元素中的钛、钨、钽和钼中的任一个或多个。尤其是,优选使用氮化钽膜。该氮化钽膜具有导电性,并对铜、氧或氢具有高阻挡性,且从氮化钽膜本身释放的氢少,由此可以作为与半导体层108接触的导电膜或半导体层108附近的导电膜适当地使用氮化钽膜。

[绝缘层110]

用作晶体管100等的栅极绝缘膜的绝缘层110可以使用PECVD法、溅射法等而形成。作为绝缘层110,可以使用包含氧化硅膜、氧氮化硅膜、氮氧化硅膜、氮化硅膜、氧化铝膜、氧化铪膜、氧化钇膜、氧化锆膜、氧化镓膜、氧化钽膜、氧化镁膜、氧化镧膜、氧化铈膜和氧化钕膜中的一种以上的绝缘层。此外,绝缘层110也可以具有两层的叠层结构或三层以上的叠层结构。

此外,与半导体层108接触的绝缘层110优选为氧化物绝缘膜,更优选具有氧含量超过化学计量组成的区域。换言之,绝缘层110是能够释放氧的绝缘层。例如,通过在氧气氛下形成绝缘层110;通过对形成后的绝缘层110在氧气氛下进行热处理、等离子体处理等;或者通过在绝缘层110上在氧气氛下形成氧化物膜等,可以将氧供应到绝缘层110中。

作为绝缘层110,也可以使用相对介电常数比氧化硅或氧氮化硅高的氧化铪等材料。由此,可以增加绝缘层110的厚度以抑制由隧道电流导致的泄漏电流。尤其是,优选使用具有结晶性的氧化铪,因为其相对介电常数比非晶氧化铪高。

[半导体层]

当半导体层108为In-M-Zn氧化物时,优选用来形成In-M-Zn氧化物的溅射靶材中的相对于元素M的In的原子个数比为1以上。作为这种溅射靶材的金属元素的原子个数比,可以举出In∶M∶Zn=1∶1∶1、In∶M∶Zn=1∶1∶1.2、In∶M∶Zn=2∶1∶3、In∶M∶Zn=3∶1∶2、In∶M∶Zn=4∶2∶3、In∶M∶Zn=4∶2∶4.1、In∶M∶Zn=5∶1∶6、In∶M∶Zn=5∶1∶7、In∶M∶Zn=5∶1∶8、In∶M∶Zn=6∶1∶6、In∶M∶Zn=5∶2∶5等。

此外,作为溅射靶材优选使用含有多晶氧化物的靶材,由此可以易于形成具有结晶性的半导体层108,所以是优选的。注意,所形成的半导体层108的原子个数比分别包含上述溅射靶材中的金属元素的原子个数比的±40%的范围内。例如,在被用于半导体层108的溅射靶材的组成为In∶Ga∶Zn=4∶2∶4.1[原子个数比]时,所形成的半导体层108的组成有时为In∶Ga∶Zn=4∶2∶3[原子个数比]或其附近。

注意,当记载为原子个数比为In∶Ga∶Zn=4∶2∶3或其附近时包括如下情况:In为4时,Ga为1以上且3以下,Zn为2以上且4以下。此外,当记载为原子个数比为In∶Ga∶Zn=5∶1∶6或其附近时包括如下情况:In比为5时,Ga大于0.1且为2以下,Zn为5以上且7以下。此外,当记载为原子个数比为In∶Ga∶Zn=1∶1∶1或其附近时包括如下情况:In为1时,Ga大于0.1且为2以下,Zn大于0.1且为2以下。

半导体层108的能隙为2eV以上,优选为2.5eV以上。如此,通过使用能隙比硅宽的金属氧化物,可以减少晶体管的关态电流。

优选将载流子浓度低的金属氧化物用于半导体层108。为了降低金属氧化物的载流子浓度,降低金属氧化物中的杂质浓度以降低缺陷态密度。在本说明书等中,将杂质浓度低且缺陷态密度低的状态称为“高纯度本征”或“实质上高纯度本征”。此外,作为金属氧化物中的杂质,例如有氢、氮、碱金属、碱土金属、铁、镍、硅等。

特别是,由于包含在金属氧化物中的氢与键合到金属原子的氧起反应而成为水,因此有时在金属氧化物中形成氧空位。当金属氧化物中的沟道形成区域中包括氧空位时,晶体管有时具有常开启特性。再者,有时氢进入氧空位中而成的缺陷被用作供体而生成作为载流子的电子。此外,有时氢的一部分键合到与金属原子键合的氧而生成作为载流子的电子。因此,使用包含多量氢的金属氧化物的晶体管容易具有常开启特性。

氢进入了氧空位的缺陷可能被用作金属氧化物的供体。然而,定量地评价该缺陷是困难的。于是,在金属氧化物中,有时不以供体浓度而以载流子浓度进行评价。因此,在本说明书等中,有时作为金属氧化物的参数,不采用供体浓度而采用假定不施加电场的状态的载流子浓度。也就是说,本说明书等所记载的“载流子浓度”有时可以称为“供体浓度”。

由此,优选尽可能减少金属氧化物中的氢。具体而言,在金属氧化物中,利用二次离子质谱分析(SIMS)测得的氢浓度低于1×1020atoms/cm3,优选低于1×1019atoms/cm3,更优选低于5×1018atoms/cm3,进一步优选低于1×1018atoms/cm3。通过将氢等杂质被充分降低的金属氧化物用于晶体管的沟道形成区域,可以使晶体管具有稳定的电特性。

沟道形成区域的金属氧化物的载流子浓度优选为1×1018cm-3以下,更优选低于1×1017cm-3,进一步优选低于1×1016cm-3,更进一步优选低于1×1013cm-3,还进一步优选低于1×1012cm-3。注意,对沟道形成区域的金属氧化物的载流子浓度的下限值没有特别的限制,例如可以为1×10-9cm-3。

半导体层108优选具有非单晶结构。非单晶结构例如包括后述的CAAC结构、多晶结构、微晶结构或非晶结构。在非单晶结构中,非晶结构的缺陷态密度最高,CAAC结构的缺陷态密度最低。

下面对CAAC(c-axis aligned crystal)进行说明。CAAC表示结晶结构的一个例子。

CAAC结构是指包括多个纳米晶(最大直径小于10nm的结晶区域)的薄膜等的结晶结构之一,具有如下特征:各纳米晶的c轴在特定方向上取向,其a轴及b轴不具有取向性,纳米晶彼此不形成晶界而连续地连接。尤其是,在具有CAAC结构的薄膜中,各纳米晶的c轴容易在薄膜的厚度方向、被形成面的法线方向或者薄膜表面的法线方向上取向。

CAAC-OS(Oxide Semiconductor)是结晶性高的氧化物半导体。另一方面,在CAAC-OS中观察不到明确的晶界,因此不容易发生起因于晶界的电子迁移率的下降。此外,氧化物半导体的结晶性有时因杂质的混入或缺陷的生成等而降低,因此可以说CAAC-OS是杂质或缺陷(氧空位等)少的氧化物半导体。因此,包含CAAC-OS的氧化物半导体的物理性质稳定。因此,包含CAAC-OS的氧化物半导体具有高耐热性及高可靠性。

在晶体学的单位晶格中,一般以构成单位晶格的a轴、b轴、c轴这三个轴(晶轴)中较特殊的轴为c轴。尤其是,在具有层状结构的结晶中,一般来说,与层的面方向平行的两个轴为a轴及b轴,与层交叉的轴为c轴。作为这种具有层状结构的结晶的典型例子,有分类为六方晶系的石墨,其单位晶格的a轴及b轴平行于劈开面,c轴正交于劈开面。例如,为层状结构的具有YbFe2O4型结晶结构的InGaZnO4的结晶可分类为六方晶系,其单位晶格的a轴及b轴平行于层的面方向,c轴正交于层(即,a轴及b轴)。

具有微晶结构的氧化物半导体膜(微晶氧化物半导体膜)在利用TEM观察到的图像中有时不能明确地确认到结晶部。微晶氧化物半导体膜中含有的结晶部的尺寸大多为1nm以上且100nm以下或1nm以上且10nm以下。尤其是,将具有尺寸为1nm以上且10nm以下或1nm以上且3nm以下的微晶的纳米晶体(nc:nanocrystal)的氧化物半导体膜称为nc-OS(nanocrystalline Oxide Semiconductor)膜。例如,在使用TEM观察nc-OS膜时,有时不能明确地确认到晶界。

在nc-OS膜中,微小的区域(例如1nm以上且10nm以下的区域,特别是1nm以上且3nm以下的区域)中的原子排列具有周期性。此外,nc-OS膜在不同的结晶部之间观察不到晶体取向的规律性。因此,在膜整体中观察不到取向性。所以,有时nc-OS膜在某些分析方法中与非晶氧化物半导体膜没有差别。例如,在通过其中利用使用其束径比结晶部大的X射线的XRD装置的out-of-plane法对nc-OS膜进行结构分析时,检测不出表示结晶面的峰值。此外,在使用其束径比结晶部大(例如,50nm以上)的电子射线获得的nc-OS膜的电子衍射图案(也称为选区电子衍射图案)中,观察到光晕图案。另一方面,在对nc-OS膜进行使用其电子束径接近结晶部的大小或者比结晶部小(例如,1nm以上且30nm以下)的电子射线的电子衍射(也称为纳米束电子衍射)时,观察到呈圈状(环状)的亮度高的区域,有时该环状区域内观察到多个斑点。

nc-OS膜比非晶氧化物半导体膜的缺陷态密度低。但是,nc-OS膜在不同的结晶部之间观察不到晶体取向的规律性。所以,nc-OS膜的缺陷态密度比CAAC-OS膜高。因此,nc-OS膜有时具有比CAAC-OS膜高的载流子浓度及电子迁移率。由此,使用nc-OS膜的晶体管有时具有较高的场效应迁移率。

nc-OS膜可以以比CAAC-OS膜成膜时更小的氧流量比形成。此外,nc-OS膜可以以比CAAC-OS膜形成时更低的衬底温度形成。例如,nc-OS膜可以在衬底温度为较低的低温(例如130℃以下的温度)的状态或不对衬底进行加热的状态下形成,因此适用于大型玻璃衬底、树脂衬底等,可以提高生产率。

下面,对金属氧化物的结晶结构的一个例子进行说明。注意,以使用In-Ga-Zn氧化物靶材(In∶Ga∶Zn=4∶2∶4.1[原子个数比])且通过溅射法形成的金属氧化物为一个例子进行说明。使用上述靶材在衬底温度为100℃以上且130℃以下的条件下利用溅射法形成的金属氧化物易于具有nc(nano crystal)结构和CAAC结构中的任一方的结晶结构或其混在的结构。在衬底温度为室温(R.T.)的条件下利用溅射法形成的金属氧化物易于具有nc结晶结构。注意,这里的室温(R.T.)是指包括对衬底不进行加热时的温度。

<金属氧化物的构成>

以下,对可用于本发明的一个方式所公开的晶体管的CAC(Cloud-AlignedComposite)-OS的构成进行说明。

在本说明书等中,有时记载CAAC(c-axis aligned crystal)或CAC(Cloud-Aligned Composite)。注意,CAAC是指结晶结构的一个例子,CAC是指功能或材料构成的一个例子。

CAC-OS或CAC-metal oxide在材料的一部分中具有导电性的功能,在材料的另一部分中具有绝缘性的功能,作为材料的整体具有半导体的功能。此外,在将CAC-OS或CAC-metal oxide用于晶体管的活性层的情况下,导电性的功能是使被用作载流子的电子(或空穴)流过的功能,绝缘性的功能是不使被用作载流子的电子流过的功能。通过导电性的功能和绝缘性的功能的互补作用,可以使CAC-OS或CAC-metal oxide具有开关功能(控制开启/关闭的功能)。通过在CAC-OS或CAC-metal oxide中使各功能分离,可以最大限度地提高各功能。

此外,CAC-OS或CAC-metal oxide包括导电性区域及绝缘性区域。导电性区域具有上述导电性的功能,绝缘性区域具有上述绝缘性的功能。此外,在材料中,导电性区域和绝缘性区域有时以纳米粒子级分离。此外,导电性区域和绝缘性区域有时在材料中不均匀地分布。此外,有时观察到其边缘模糊而以云状连接的导电性区域。

此外,在CAC-OS或CAC-metal oxide中,导电性区域和绝缘性区域有时以0.5nm以上且10nm以下,优选为0.5nm以上且3nm以下的尺寸分散在材料中。

此外,CAC-OS或CAC-metal oxide由具有不同带隙的成分构成。例如,CAC-OS或CAC-metal oxide由具有起因于绝缘性区域的宽隙的成分及具有起因于导电性区域的窄隙的成分构成。在该结构中,当使载流子流过时,载流子主要在具有窄隙的成分中流过。此外,具有窄隙的成分与具有宽隙的成分互补作用,与具有窄隙的成分联动地在具有宽隙的成分中载流子流过。因此,在将上述CAC-OS或CAC-metal oxide用于晶体管的沟道形成区域时,在晶体管的开启状态中可以得到高电流驱动力,即大通态电流及高场效应迁移率。

就是说,也可以将CAC-OS或CAC-metal oxide称为基质复合材料(matrixcomposite)或金属基质复合材料(metal matrix composite)。

以上是构成要素的说明。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

(实施方式2)

在本实施方式中对具有上述实施方式例示的晶体管的显示装置的一个例子进行说明。

<结构例子>

图15A是显示装置700的俯视图。显示装置700包括利用密封剂712贴合在一起的第一衬底701和第二衬底705。在被第一衬底701、第二衬底705及密封剂712密封的区域中,第一衬底701上设置有像素部702、源极驱动电路部704及栅极驱动电路部706。像素部702设置有多个显示元件。

此外,第一衬底701的不与第二衬底705重叠的部分中设置有与FPC716(FPC:Flexible printed circuit柔性印刷电路)连接的FPC端子部708。利用FPC716通过FPC端子部708及信号线710分别对像素部702、源极驱动电路部704及栅极驱动电路部706提供各种信号等。

可以设置多个栅极驱动电路部706。此外,栅极驱动电路部706及源极驱动电路部704分别另行形成在半导体衬底等上,也可以采用被封装的IC芯片的方式。该IC芯片可以安装在第一衬底701上或安装到FPC716。

像素部702、源极驱动电路部704及栅极驱动电路部706包括的晶体管可以使用本发明的一个方式的半导体装置的晶体管。

作为设置在像素部702中的显示元件,可以举出液晶元件、发光元件等。作为液晶元件,可以采用透射型液晶元件、反射型液晶元件、半透射型液晶元件等。此外,作为发光元件可以举出LED(LightEmitting Diode:发光二极管)、OLED(Organic LED:有机LED)、QLED(Quantum-dot LED:量子点LED)、半导体激光器等自发光性的发光元件。此外,可以使用快门方式或光干涉方式的MEMS(Micro Electro Mechanical Systems:微电子机械系统)元件或采用微囊方式、电泳方式、电润湿方式或电子粉流体(注册商标)方式等的显示元件等。

图15B所示的显示装置700A是使用具有柔性的树脂层743代替第一衬底701的能够用作柔性显示器的显示装置的例子。

显示装置700A的像素部702不是矩形而是角部具有圆弧形的形状。此外,如图15B中的区域P1所示,像素部702及树脂层743的一部分具有切断的缺口部。一对栅极驱动电路部706夹着像素部702设置在两侧。栅极驱动电路部706在像素部702的角部沿着圆弧形的轮廓内侧设置。

树脂层743的设置有FPC端子部708的部分突出。树脂层743的包括FPC端子部708的一部分可以沿着图15B中的区域P2折到背面。通过将树脂层743的一部分折到背面,可以在FPC716与像素部702的背面重叠配置的状态下将显示装置700A安装到电子设备,由此可以节省电子设备的空间。

此外,与显示装置700A连接的FPC716安装有IC717。IC717例如具有源极驱动电路的功能。这里,显示装置700A中的源极驱动电路部704可以采用至少包括保护电路、缓冲器电路、解复用器电路等中的一种的结构。

图15C所示的显示装置700B是适用于具有大屏幕的电子设备的显示装置。例如,显示装置700B可以适用于电视装置、显示器装置、个人计算机(包括笔记本型或台式)、平板终端、数字标牌等。

显示装置700B包括多个源极驱动器IC721和一对栅极驱动电路部722。

多个源极驱动器IC721分别安装在FPC723上。此外,多个FPC723的一个端子与第一衬底701连接,另一个端子与印刷电路板724连接。通过使FPC723弯曲,可以将印刷电路板724配置在像素部702的背面,安装在电子设备中,而可以减小用来设置电子设备的空间。

另一方面,栅极驱动电路部722形成在第一衬底701上。由此,可以实现窄边框的电子设备。

通过采用上述结构,可以实现大型且高分辨率的显示装置。例如,可以实现屏幕尺寸为对角线30英寸以上、40英寸以上、50英寸以上或60英寸以上的显示装置。此外,可以实现4K2K、8K4K等极为高分辨率的显示装置。

<截面结构例子>

下面参照图16至图19对作为显示元件使用液晶元件的结构及使用EL元件的结构进行说明。图16至图18是分别沿着图15A所示的点划线Q-R的截面图。图19是沿着图15B所示的显示装置700A中的点划线S-T的截面图。图16及图17是作为显示元件使用液晶元件的结构,图18及图19是使用EL元件的结构。

[显示装置的共同部分的说明]

图16至图19所示的显示装置包括引绕布线部711、像素部702、源极驱动电路部704及FPC端子部708。引绕布线部711包括信号线710。像素部702包括晶体管750及电容器790。源极驱动电路部704包括晶体管752。图17示出不包括电容器790的情况。

晶体管750及晶体管752可以使用实施方式1所示的晶体管。

本实施方式使用的晶体管包括高度纯化且氧空位的形成被抑制的氧化物半导体膜。该晶体管可以具有低关态电流。因此,可以延长图像信号等电信号的保持时间,可以延长图像信号等的写入间隔。因此,可以降低刷新工作的频度,由此可以发挥降低功耗的效果。

此外,在本实施方式中使用的晶体管能够得到较高的场效应迁移率,因此能够进行高速驱动。例如,通过将这种能够进行高速驱动的晶体管用于显示装置,可以在同一衬底上形成像素部的开关晶体管及用于驱动电路部的驱动晶体管。即,可以采用不采用由硅片等形成的驱动电路的结构,由此可以减少显示装置的构件数。此外,通过在像素部中也使用能够进行高速驱动的晶体管,可以提供高品质的图像。

图16、图18及图19所示的电容器790包括通过对与晶体管750包括的第一栅电极相同的膜进行加工形成的下部电极以及通过对与半导体层相同的金属氧化物进行加工形成的上部电极。上部电极与晶体管750的源区域及漏区域同样地被低电阻化。此外,在下部电极与上部电极之间设置有用作晶体管750的第一栅极绝缘层的绝缘膜的一部分。也就是说,电容器790具有在一对电极间夹有用作电介质膜的绝缘膜的叠层结构。此外,上部电极连接有通过对与晶体管的源电极及漏电极为同一膜进行加工形成的布线。

此外,晶体管750、晶体管752及电容器790上设置有平坦化绝缘膜770。

此外,像素部702所包括的晶体管750与源极驱动电路部704所包括的晶体管752也可以使用不同结构的晶体管。例如,可以采用其中一方使用顶栅极型晶体管而另一方使用底栅极型晶体管的结构。此外,上述栅极驱动电路部706也与源极驱动电路部704同样。

信号线710由与晶体管750、752的源电极及漏电极等相同的导电膜形成。这里,优选使用含有铜元素的材料等低电阻材料,由此可以减少起因于布线电阻的信号延迟等,从而可以实现大屏幕显示。

FPC端子部708包括其一部分用作连接电极的布线760、各向异性导电膜780及FPC716。布线760通过各向异性导电膜780与FPC716的端子电连接。在此,布线760是由与晶体管750、752的源电极及漏电极等相同的导电膜形成。

作为第一衬底701及第二衬底705,例如可以使用玻璃衬底或塑料衬底等具有柔性的衬底。当作为第一衬底701使用具有柔性的衬底时,优选在第一衬底701与晶体管750等之间设置对水或氢具有阻挡性的绝缘层。

第二衬底705一侧设置有遮光膜738、着色膜736以及与它们接触的绝缘膜734。

[使用液晶元件的显示装置的结构例子]

图16所示的显示装置700包括液晶元件775及间隔物778。液晶元件775包括导电层772、导电层774以及导电层772与导电层774之间的液晶层776。导电层774设置在第二衬底705一侧,用作公共电极。此外,导电层772与晶体管750所包括的源电极或漏电极电连接。导电层772形成在平坦化绝缘膜770上用作像素电极。

导电层772可以使用对可见光具有透光性的材料或具有反射性的材料。作为透光性材料,例如,可以使用含有铟、锌、锡等的氧化物材料。作为反射性材料,例如,可以使用含有铝、银等材料。

当作为导电层772使用反射性材料时,显示装置700为反射型液晶显示装置。另一方面,当作为导电层772使用透光性材料时,显示装置700为透射型液晶显示装置。当为反射型液晶显示装置的情况下,在观看侧设置偏振片。另一方面,当为透射型液晶显示装置的情况下,以夹着液晶元件的方式设置一对偏振片。

图17所示的显示装置700示出使用横向电场方式(例如,FFS模式)的液晶元件775的例子。导电层772上隔着绝缘层773设置有用作公共电极的导电层774。可以通过导电层772与导电层774间产生的电场控制液晶层776的取向状态。

在图17中,可以以导电层774、绝缘层773、导电层772的叠层结构构成存储电容器。因此,不需要另外设置电容器,可以提高开口率。

此外,虽然图16及图17中没有示出,也可以采用设置与液晶层776接触的取向膜。此外,可以适当地设置偏振构件、相位差构件、抗反射构件等的光学构件(光学衬底)及背光、侧光等光源。

液晶层776可以使用热致液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLC:Polymer Dispersed Liquid Crystal)、高分子网络型液晶(PNLC:Polymer NetworkLiquid Crystal)、铁电液晶、反铁电液晶等。此外,在采用横向电场方式的情况下,也可以使用不需要取向膜的呈现蓝相的液晶。

作为液晶元件的模式,可以采用TN(Twisted Nematic:扭曲向列)模式、VA(Vertical Alignment:垂直取向)模式、IPS(In-Plane-Switching:平面内转换)模式、FFS(Fringe Field Switching:边缘电场转换)模式、ASM(Axially Symmetric alignedMicro-cell:轴对称排列微单元)模式、OCB(Optically Compensated Birefringence:光学补偿弯曲)模式、ECB(Electrically Controlled Birefringence:电控双折射)模式、宾主模式等。

此外,液晶层776可以采用使用高分子分散型液晶、高分子网络型液晶等的散乱型液晶。此时,可以采用不设置着色膜736进行黑白色显示的结构,也可以采用使用着色膜736进行彩色显示的结构。

此外,作为液晶元件的驱动方法,可以应用利用继时加法混色法进行彩色显示的分时显示方式(也称为场序制列驱动方式)。在该情况下,可以采用不设置着色膜736的结构。当采用分时显示方式的情况下,例如无需设置分别呈现R(红色)、G(绿色)、B(蓝色)的子像素,因此具有可以提高像素的开口率、分辨率等优点。

[使用发光元件的显示装置]

图18所示的显示装置700包括发光元件782。发光元件782包括导电层772、EL层786及导电膜788。EL层786具有有机化合物或量子点等的无机化合物。

作为可用于有机化合物的材料,可以举出荧光性材料或磷光性材料等。此外,可用于量子点的材料,可以举出胶状量子点材料、合金型量子点材料、核壳(Core Shell)型量子点材料、核型量子点材料等。

图18所示的显示装置700在平坦化绝缘膜770上设置有覆盖导电层772的一部分的绝缘膜730。在此,发光元件782包括透光性导电膜788为顶部发射型发光元件。此外,发光元件782也可以采用使光射出到导电层772侧的底部发射结构或者使光射出到导电层772一侧及导电膜788一侧的双方的双面发射结构。

着色膜736设置在与发光元件782重叠的位置,遮光膜738设置在与绝缘膜730重叠的位置、引绕布线部711及源极驱动电路部704中。此外,着色膜736及遮光膜738由绝缘膜734覆盖。此外,发光元件782与绝缘膜734之间由密封膜732充填。此外,当通过在各像素中将EL层786形成为岛状或者在各像素列中将EL层786形成为条状,也就是说,通过分开涂布来形成EL层786时,也可以采用不设置着色膜736的结构。

图19示出适用于柔性显示器的显示装置的结构。图19是沿着图15B所示的显示装置700A中的点划线S-T的截面图。

图19所示的显示装置700A采用支撑衬底745、粘合层742、树脂层743及绝缘层744的叠层结构代替图18所示的第一衬底701。晶体管750、电容器790等设置于形成在树脂层743上的绝缘层744上。

支撑衬底745是包含有机树脂、玻璃等的具有柔性的薄衬底。树脂层743是包含聚酰亚胺、丙烯酸树脂等的有机树脂的层。绝缘层744包含氧化硅、氧氮化硅、氮化硅等的无机绝缘膜。树脂层743与支撑衬底745通过粘合层742贴合在一起。树脂层743优选比支撑衬底745薄。

图19所示的显示装置700包括保护层740代替图18所示的衬底705。保护层740与密封膜732贴合在一起。保护层740可以使用玻璃衬底、树脂薄膜等。此外,保护层740也可以使用偏振片、散射板等光学构件、触摸传感器面板等输入装置或上述两个以上的叠层结构。

发光元件782包括的EL层786在绝缘膜730及导电层772上以岛状设置。通过以各子像素中的发光颜色都不同的方式分开形成EL层786,可以在不使用着色膜736的情况下实现彩色显示。此外,覆盖发光元件782设置有保护层741。保护层741可以防止水等杂质扩散到发光元件782中。保护层741优选使用无机绝缘膜。此外,更优选的是采用无机绝缘膜和有机绝缘膜各为一个以上的叠层结构。

图19中示出能够折叠的区域P2。区域P2中包括不设置有支撑衬底745、粘合层742以及绝缘层744等无机绝缘膜的部分。此外,在区域P2中,覆盖布线760设置有树脂层746。通过尽量不在能够折叠的区域P2中设置无机绝缘膜而采用仅层叠含有金属或合金的导电层、含有有机材料的层的结构,可以防止在使其弯曲时产生裂缝。此外,通过不在区域P2设置支撑衬底745,可以使显示装置700A的一部分以极小的曲率半径弯曲。

[在显示装置中设置输入装置的结构例子]

此外,也可以对图16至图19所示的显示装置设置输入装置。作为该输入装置,例如,可以举出触摸传感器等。

例如,作为传感器的方式,可以利用静电电容式、电阻膜式、表面声波式、红外线式、光学式、压敏式等各种方式。此外,可以组合使用上述方式中的两个以上。

此外,触摸面板有如下结构:输入装置形成在一对衬底之间的所谓的In-Cell型触摸面板;输入装置形成在显示装置上的所谓的On-Cell型触摸面板;与显示装置贴合的所谓的Out-Cell型触摸面板;等等。

本实施方式所示的结构例子及对应于这些例子的附图等的至少一部分可以与其他结构例子或附图等适当地组合而实施。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

(实施方式3)

在本实施方式中参照图20A至图20C对包括本发明的一个方式的半导体装置的显示装置进行说明。

图20A所示的显示装置包括像素部502、驱动电路部504、保护电路506及端子部507。注意,也可以采用不设置保护电路506的结构。

对像素部502或驱动电路部504所包括的晶体管可以使用本发明的一个方式的晶体管。此外,也可以对保护电路506使用本发明的一个方式的晶体管。

像素部502包括使配置为X行Y列(X、Y为分别独立的2以上的自然数)的多个显示元件驱动的多个像素电路501。

驱动电路部504包括对扫描线GL_1至GL_X输出扫描信号的栅极驱动器504a、对数据线DL_1至DL_Y供应数据信号的源极驱动器504b等的驱动电路。栅极驱动器504a采用至少包括移位寄存器的结构即可。此外,源极驱动器504b例如由多个模拟开关等构成。此外,也可以由移位寄存器等构成源极驱动器504b。

端子部507是指设置有用来从外部的电路对显示装置输入电源、控制信号及图像信号等的端子的部分。

保护电路506是在自身所连接的布线被供应一定的范围之外的电位时使该布线与其他布线之间处于导通状态的电路。图20A所示的保护电路506例如与栅极驱动器504a和像素电路501之间的布线的扫描线GL_1至GL_X或者与源极驱动器504b和像素电路501之间的布线的数据线DL_1至DL_Y等的各种布线连接。

此外,既可以采用栅极驱动器504a及源极驱动器504b各自设置在与像素部502相同的衬底上的结构,又可以采用形成有栅极驱动电路或源极驱动电路的另一衬底(例如,使用单晶半导体、多晶半导体形成的驱动电路板)以COG或TAB(Tape Automated Bonding:卷带自动结合)安装于衬底上的结构。

此外,图20A所示的多个像素电路501例如可以采用与图20B、图20C所示的结构。

图20B所示的像素电路501包括液晶元件570、晶体管550及电容器560。此外,与像素电路501连接有数据线DL_n、扫描线GL_m及电位供应线VL等。

根据像素电路501的规格适当地设定液晶元件570的一对电极中的一个电极的电位。根据被写入的数据设定液晶元件570的取向状态。此外,也可以对多个像素电路501的每一个所具有的液晶元件570的一对电极中的一个电极供应公共电位。此外,也可以对各行的像素电路501的每一个所具有的液晶元件570的一对电极中的一个电极供应不同的电位。

图20C所示的像素电路501包括晶体管552、554、电容器562以及发光元件572。此外,与像素电路501连接有数据线DL_n、扫描线GL_m、电位供应线VL_a及电位供应线VL_b等。

此外,电位供应线VL_a和电位供应线VL_b中的一个被施加高电源电位VDD,另一个被施加低电源电位VSS。根据晶体管554的栅极被施加的电位,流过发光元件572中的电流被控制,从而来自发光元件572的发光亮度被控制。

本实施方式所示的结构例子及对应于这些例子的附图等的至少一部分可以与其他结构例子或附图等适当地组合而实施。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

(实施方式4)

下面对备有用来校正像素所显示的灰度的存储器的像素电路以及具有该像素电路的显示装置进行说明。实施方式1中例示出的晶体管可以用于下文中例示出的像素电路所使用的晶体管。

<电路结构>

图21A示出像素电路400的电路图。像素电路400包括晶体管M1、晶体管M2、电容器C1及电路401。此外,像素电路400连接有布线S1、布线S2、布线G1及布线G2。

晶体管M1的栅极与布线G1连接,源极和漏极中的一个与布线S1连接,源极和漏极中的另一个与电容器C1的一个电极连接。晶体管M2的栅极与布线G2连接,源极和漏极中的一个与布线S2连接,源极和漏极中的另一个与电容器C1的另一个电极及电路401连接。

电路401至少包括一个显示元件。显示元件可以使用各种各样的元件,典型地可以使用有机EL元件或LED元件等发光元件、液晶元件或MEMS(Micro Electro MechanicalSystems)元件等。

将连接晶体管M1与电容器C1的节点记作节点N1,将连接晶体管M2与电路401的节点记作节点N2。

像素电路400通过使晶体管M1变为关闭状态可以保持节点N1的电位。此外,通过使晶体管M2变为关闭状态可以保持节点N2的电位。此外,当在晶体管M2处于关闭状态的状态下通过晶体管M1对节点N1写入规定的电位时,由于通过电容器C1的电容耦合,可以使节点N2的电位对应节点N1的电位变化而发生改变。

在此,作为晶体管M1、晶体管M2中的一方或双方可以使用实施方式1中例示出的使用氧化物半导体的晶体管。由于该晶体管具有极低的关态电流,因此可以长时间地保持节点N1及节点N2的电位。此外,当各节点的电位保持期间较短时(具体而言,帧频为30Hz以上时等)也可以采用使用硅等半导体的晶体管。

<驱动方法例子>

接着,参照图21B对像素电路400的工作方法的一个例子进行说明。图21B是像素电路400的工作的时序图。注意,这里为了便于说明,不考虑布线电阻等各种电阻、晶体管或布线等的寄生电容及晶体管的阈值电压等的影响。

在图21B所示的工作中,将1个帧期间分为期间T1和期间T2。期间T1是对节点N2写入电位的期间,期间T2是对节点N1写入电位的期间。

[期间T1]

在期间T1,对布线G1和布线G2的双方供给使晶体管变为开启状态的电位。此外,对布线S1提供为固定电位的电位Vref,对布线S2提供第一数据电位Vw。

节点N1通过晶体管M1从布线S1被供给电位Vref。此外,节点N2从布线S2通过晶体管M2被供给第一数据电位Vw。因此,电容器C1变为保持电位差Vw-Vref的状态。

[期间T2]

接着,在期间T2,布线G1被供应使晶体管M1变为开启状态的电位,布线G2被供应使晶体管M2变为关闭状态的电位。布线S1被供应第二数据电位Vdata。此外,布线S2也可以被供应预定的恒电位或成为浮动状态。

节点N1从布线S1通过晶体管M1被供应第二数据电位Vdata。此时,由于通过电容器C1的电容耦合,对应第二数据电位Vdata节点N2的电位发生变化,其变化量为电位dV。也就是说,电路401被输入将第一数据电位Vw和电位dV加在一起的电位。注意,虽然图21B示出电位dV为正的值,但是其也可以为负的值。也就是说,电位Vdata也可以比第二数据电位Vref低。

这里,电位dV基本由电容器C1的电容值及电路401的电容值决定。当电容器C1的电容值充分大于电路401的电容值时,电位dV成为接近第二数据电位Vdata的电位。

如上所述,由于像素电路400可以组合两种数据信号生成供应给包括显示元件的电路401的电位,所以可以在像素电路400内进行灰度校正。

此外,像素电路400可以生成超过可对布线S1及布线S2供给的最大电位的电位。例如,在使用发光元件的情况下,可以进行高动态范围(HDR)显示等。此外,在使用液晶元件的情况下,可以实现过驱动等。

<应用例子>

[使用液晶元件的例子]

图21C所示的像素电路400LC包括电路401LC。电路401LC包括液晶元件LC及电容器C2。

液晶元件LC的一个电极与电容器C1的另一个电极、晶体管M2的源极和漏极中的另一个及电容器C2的一个电极连接,另一个电极与被供应电位Vcom2的布线连接。电容器C2的另一个电极与被供应电位Vcom1的布线连接。

电容器C2用作存储电容器。此外,当不需要时可以省略电容器C2。

由于像素电路400LC可以对液晶元件LC提供高电压,所以例如可以通过过驱动实现高速显示,可以采用驱动电压高的液晶材料等。此外,通过对布线S1或布线S2提供校正信号,可以根据使用温度或液晶元件LC的劣化状态等进行灰度校正。

[使用发光元件的例子]

图21D所示的像素电路400EL包括电路401EL。电路401EL包括发光元件EL、晶体管M3及电容器C2。

晶体管M3的栅极与电容器C2的一个电极连接,源极和漏极中的一个与被供应电位VH的布线连接,源极和漏极中的另一个与发光元件EL的一个电极连接。电容器C2的另一个电极与被供应电位Vcom的布线连接。发光元件EL的另一个电极与被供应电位VL的布线连接。

晶体管M3具有控制对发光元件EL供应的电流的功能。电容器C2用作存储电容器。不需要时也可以省略电容器C2。

此外,虽然这里示出发光元件EL的阳极一侧与晶体管M3连接的结构,但是也可以采用阴极一侧与晶体管M3连接的结构。此时,可以适当地改变电位VH与电位VL的值。

在像素电路400EL中,可以通过对晶体管M3的栅极施加高电位使大电流流过发光元件EL,所以可以实现HDR显示等。此外,通过对布线S1或布线S2提供校正信号可以对晶体管M3及发光元件EL的电特性偏差进行校正。

此外,不局限于图21C及图21D所示的电路,也可以采用另外附加晶体管或电容器等的结构。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

(实施方式5)

在本实施方式中,对可以使用本发明的一个方式制造的显示模块进行说明。

图22A所示的显示模块6000在上盖6001与下盖6002之间包括与FPC6005连接的显示装置6006、框架6009、印刷电路板6010及电池6011。

例如,可以将使用本发明的一个方式制造的显示装置用作显示装置6006。通过利用显示装置6006,可以实现功耗极低的显示模块。

上盖6001及下盖6002可以根据显示装置6006的尺寸适当地改变其形状或尺寸。

显示装置6006也可以具有作为触摸面板的功能。

框架6009具有保护显示装置6006的功能、遮断因印刷电路板6010的工作而产生的电磁波的功能以及散热板的功能等。

印刷电路板6010具有电源电路以及用来输出视频信号及时钟信号的信号处理电路、电池控制电路等。

图22B是具备光学触摸传感器的显示模块6000的截面示意图。

显示模块6000包括设置在印刷电路板6010上的发光部6015及受光部6016。此外,由上盖6001与下盖6002围绕的区域设置有一对导光部(导光部6017a、导光部6017b)。

显示装置6006隔着框架6009与印刷电路板6010、电池6011重叠。显示装置6006及框架6009固定在导光部6017a、导光部6017b。

从发光部6015发射的光6018经过导光部6017a、显示装置6006的上部及导光部6017b到达受光部6016。例如,当光6018被指头或触屏笔等被检测体阻挡时,可以检测触摸操作。

例如,多个发光部6015沿着显示装置6006的相邻的两个边设置。多个受光部6016配置在与发光部6015对置的位置。由此,可以取得触摸操作的位置的信息。

作为发光部6015例如可以使用LED元件等光源,尤其是,优选使用发射红外线的光源。作为受光部6016可以使用接收发光部6015所发射的光且将其转换为电信号的光电元件。优选使用能够接收红外线的光电二极管。

通过使用使光6018透过的导光部6017a及导光部6017b,可以将发光部6015及受光部6016配置在显示装置6006中的下侧,可以抑制外光到达受光部6016而导致触摸传感器的错误工作。尤其优选使用吸收可见光且透过红外线的树脂,由此可以更有效地抑制触摸传感器的错误工作。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

(实施方式6)

在本实施方式中对能够使用本发明的一个方式的显示装置的电子设备的例子进行说明。

图23A所示的电子设备6500是可以用作智能手机的便携式信息终端设备。

电子设备6500包括外壳6501、显示部6502、电源按钮6503、按钮6504、扬声器6505、麦克风6506、照相机6507及光源6508等。显示部6502具有触摸面板功能。

显示部6502可以使用本发明的一个方式的显示装置。

图23B是包括外壳6501的麦克风6506一侧的端部的截面示意图。

外壳6501的显示面一侧设置有具有透光性的保护构件6510,被外壳6501及保护构件6510包围的空间内设置有显示面板6511、光学构件6512、触摸传感器面板6513、印刷电路板6517、电池6518等。

保护构件6510通过没有图示的粘合层固定到显示面板6511、光学构件6512及触摸传感器面板6513。

在显示部6502外侧的区域中,显示面板6511的一部分被折叠。此外,该被折叠的部分与FPC6515连接。FPC6515安装有IC6516。此外,FPC6515与设置于印刷电路板6517的端子连接。

显示面板6511可以使用本发明的一个方式的柔性显示器面板。由此,可以实现极轻量的电子设备。此外,由于显示面板6511极薄,所以可以在抑制电子设备的厚度的情况下搭载大容量的电池6518。此外,通过折叠显示面板6511的一部分以在像素部的背面设置与FPC6515的连接部,可以实现窄边框的电子设备。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

(实施方式7)

在本实施方式中对包括使用本发明的一个方式制造的显示装置的电子设备进行说明。

以下所例示的电子设备是在显示部中包括本发明的一个方式的显示装置的电子设备。因此,以下所例示的电子设备是可以实现高分辨率的电子设备。此外,可以同时实现高分辨率及大屏幕的电子设备。

在本发明的一个方式的电子设备的显示部上例如可以显示具有全高清、4K2K、8K4K、16K8K或更高的分辨率的影像。

作为电子设备,例如除了电视装置、笔记本型个人计算机、显示器装置、数字标牌、弹珠机、游戏机等具有比较大的屏幕的电子设备之外,还可以举出数码相机、数码摄像机、数码相框、移动电话机、便携式游戏机、便携式信息终端、声音再现装置等。

使用了本发明的一个方式的电子设备可以沿着房屋或楼的内壁或外壁、汽车等的内部装饰或外部装饰等的平面或曲面组装。

图24A是示出安装有取景器8100的照相机8000的外观的图。

照相机8000包括外壳8001、显示部8002、操作按钮8003、快门按钮8004等。此外,照相机8000安装有可装卸的透镜8006。

在照相机8000中,透镜8006和外壳也可以被形成为一体。

照相机8000通过按下快门按钮8004或者触摸用作触摸面板的显示部8002,可以进行成像。

外壳8001包括具有电极的嵌入器,除了可以与取景器8100连接以外,还可以与闪光灯装置等连接。

取景器8100包括外壳8101、显示部8102以及按钮8103等。

外壳8101通过嵌合到照相机8000的嵌入器装到照相机8000。取景器8100可以将从照相机8000接收的图像等显示到显示部8102上。

按钮8103被用作电源按钮等。

本发明的一个方式的显示装置可以用于照相机8000的显示部8002及取景器8100的显示部8102。此外,也可以在照相机8000中内置有取景器。

图24B是示出头戴显示器8200的外观的图。

头戴显示器8200包括安装部8201、透镜8202、主体8203、显示部8204以及电缆8205等。此外,在安装部8201中内置有电池8206。

通过电缆8205,将电力从电池8206供应到主体8203。主体8203具备无线接收器等,能够将所接收的图像信息等显示到显示部8204上。此外,主体8203具有照相机,由此可以利用使用者的眼球及眼睑的动作作为输入方法。

此外,也可以对安装部8201的被使用者接触的位置设置多个电极,以检测出根据使用者的眼球的动作而流过电极的电流,由此实现识别使用者的视线的功能。此外,还可以具有根据流过该电极的电流监视使用者的脉搏的功能。此外,安装部8201可以具有温度传感器、压力传感器、加速度传感器等各种传感器,也可以具有将使用者的生物信息显示在显示部8204上的功能或与使用者的头部的动作同步地使显示在显示部8204上的图像变化的功能。

可以将本发明的一个方式的显示装置用于显示部8204。

图24C、图24D及图24E是示出头戴显示器8300的外观的图。头戴显示器8300包括外壳8301、显示部8302、带状固定工具8304以及一对透镜8305。

使用者可以通过透镜8305看到显示部8302上的显示。优选的是,弯曲配置显示部8302,因为使用者可以感受高真实感。此外,通过透镜8305分别看到显示在显示部8302的不同区域上的图像,来可以进行利用视差的三维显示等。此外,本发明的一个方式不局限于设置有一个显示部8302的结构,也可以设置两个显示部8302以对使用者的一对眼睛分别配置一个显示部。

可以将本发明的一个方式的显示装置用于显示部8302。因为包括本发明的一个方式的半导体装置的显示装置具有极高的分辨率,所以即使如图24E那样地使用透镜8305放大,也可以不使使用者看到像素而可以显示现实感更高的影像。

图25A至图25G所示的电子设备包括外壳9000、显示部9001、扬声器9003、操作键9005(包括电源开关或操作开关)、连接端子9006、传感器9007(该传感器具有测量如下因素的功能:力、位移、位置、速度、加速度、角速度、转速、距离、光、液、磁、温度、化学物质、声音、时间、硬度、电场、电流、电压、电力、辐射线、流量、湿度、倾斜度、振动、气味或红外线)、麦克风9008等。

图25A至图25G所示的电子设备具有各种功能。例如,可以具有如下功能:将各种信息(静态图像、动态图像、文字图像等)显示在显示部上的功能;触摸面板的功能;显示日历、日期或时间等的功能;通过利用各种软件(程序)控制处理的功能;进行无线通信的功能;读出储存在存储介质中的程序或数据来处理的功能;等。注意,电子设备的功能不局限于上述功能,而可以具有各种功能。电子设备可以包括多个显示部。此外,也可以在该电子设备中设置照相机等而使其具有如下功能:拍摄静态图像或动态图像来储存在存储介质(外部存储介质或内置于照相机的存储介质)中的功能;将所拍摄的图像显示在显示部上的功能;等。

下面,详细地说明图25A至图25G所示的电子设备。

图25A是示出电视装置9100的立体图。可以将例如是50英寸以上或100英寸以上的大型显示部9001组装到电视装置9100。

图25B是示出便携式信息终端9101的立体图。便携式信息终端9101例如可以用作智能手机。便携式信息终端9101也可以设置有扬声器9003、连接端子9006、传感器9007等。此外,便携式信息终端9101可以将文字或图像信息显示在其多个面上。图25B示出显示三个图标9050的例子。此外,也可以将由虚线矩形表示的信息9051显示在显示部9001的另一个面上。作为信息9051的一个例子,可以举出提示收到电子邮件、SNS或电话等的信息;电子邮件或SNS等的标题;发送者姓名;日期;时间;电池余量;以及天线接收信号强度等。或者,可以在显示有信息9051的位置上显示图标9050等。

图25C是示出便携式信息终端9102的立体图。便携式信息终端9102具有将信息显示在显示部9001的三个以上的面上的功能。在此,示出信息9052、信息9053、信息9054分别显示于不同的面上的例子。例如,使用者也可以在将便携式信息终端9102放在上衣口袋里的状态下确认显示在能够从便携式信息终端9102的上方观察到的位置上的信息9053。使用者可以确认到该显示而无需从口袋里拿出便携式信息终端9102,由此能够判断例如是否接电话。

图25D是示出手表型便携式信息终端9200的立体图。便携式信息终端9200例如可以用作智能手表(注册商标)。此外,显示部9001的显示面被弯曲,能够在所弯曲的显示面上进行显示。例如,通过与可进行无线通信的耳麦相互通信,便携式信息终端9200可以进行免提通话。此外,便携式信息终端9200包括连接端子9006,可以与其他信息终端进行数据的交换或者进行充电。此外,充电工作也可以利用无线供电进行。

图25E、图25F及图25G是示出能够折叠的便携式信息终端9201的立体图。此外,图25E是便携式信息终端9201为展开状态的立体图,图25G是便携式信息终端9201为折叠状态的立体图,并且图25F是便携式信息终端9201为从图25E和图25G中的一个状态变为另一个状态的中途的状态的立体图。便携式信息终端9201在折叠状态下可携带性好,在展开状态下因为具有无缝拼接的较大的显示区域而其显示的一览性优异。便携式信息终端9201所包括的显示部9001由铰链9055所连接的三个外壳9000来支撑。例如,可以以1mm以上且150mm以下的曲率半径使显示部9001弯曲。

图26A示出电视装置的一个例子。电视装置7100的显示部7500被组装在外壳7101中。在此示出利用支架7103支撑外壳7101的结构。

可以通过利用外壳7101所具备的操作开关或另外提供的遥控操作机7111进行图26A所示的电视装置7100的操作。此外,也可以将触摸面板应用于显示部7500,通过用手指等触摸显示部7500可以进行电视装置7100的操作。此外,遥控操作机7111也可以除了具备操作按钮以外还具备显示部。

此外,电视装置7100也可以具备电视广播的接收机或用来连接到通信网络的通信设备。

图26B示出笔记型个人计算机7200。笔记型个人计算机7200包括外壳7211、键盘7212、指向装置7213、外部连接端口7214等。在外壳7211中组装有显示部7500。

图26C及图26D示出数字标牌(Digital Signage)的一个例子。

图26C所示的数字标牌7300包括外壳7301、显示部7500及扬声器7303等。此外,还可以包括LED灯、操作键(包括电源开关或操作开关)、连接端子、各种传感器以及麦克风等。

图26D示出设置于圆柱状柱子7401上的数字标牌7400。数字标牌7400包括沿着柱子7401的曲面设置的显示部7500。

显示部7500越大,一次能够提供的信息量越多,并且容易吸引人的注意,由此例如可以提高广告宣传效果。

优选将触摸面板用于显示部7500,使得使用者能够操作。由此,不仅可以用于广告,还可以用于提供路线信息或交通信息、商用设施的指南等使用者需要的信息。

如图26C和图26D所示,数字标牌7300或数字标牌7400优选通过无线通信可以与使用者所携带的智能手机等信息终端设备7311联动。例如,显示在显示部7500上的广告的信息可以显示在信息终端设备7311的屏幕,并且通过操作信息终端设备7311,可以切换显示部7500的显示。

此外,可以在数字标牌7300或数字标牌7400上以信息终端设备7311为操作单元(控制器)执行游戏。由此,不特定多个使用者可以同时参加游戏,享受游戏的乐趣。

本发明的一个方式的显示装置可以应用于图26A至图26D所示的显示部7500。

虽然本实施方式的电子设备采用具有显示部的结构,但是本发明的一个方式也可以用于不具有显示部的电子设备。

本实施方式的至少一部分可以与本说明书所记载的其他实施方式适当地组合而实施。

[实施例1]

在本实施例中,制造相当于图9A至图9C所示的晶体管100C的样品(样品A1至样品A6)而对晶体管的漏电流-漏电压特性(Id-Vd特性)进行评价。

<样品的制造>

首先,通过溅射法在玻璃衬底上依次形成厚度为30nm的钛膜与厚度为100nm的铜膜,对其进行加工来得到第一栅电极(底栅极)。

接着,作为第一栅极绝缘层依次形成厚度为50nm的第一氮化硅膜、厚度为150nm的第二氮化硅膜、厚度为100nm的第三氮化硅膜及厚度为3nm的第一氧氮化硅膜。

第一氮化硅膜及第三氮化硅膜都通过使用流量为200sccm的硅烷气体、流量为2000sccm的氮气体及流量为100sccm的氨气体的混合气体的PECVD法形成。在成膜中,压力为100Pa,功率为2000W,衬底温度为350℃。此外,第一氮化硅膜相当于实施方式1所示的绝缘层103a,第三氮化硅膜相当于实施方式1所示的绝缘层103c。

第二氮化硅膜通过使用流量为290sccm的硅烷气体、流量为2000sccm的氮气体及流量为2000sccm的氨气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为3000W,衬底温度为350℃。此外,第二氮化硅膜相当于实施方式1所示的绝缘层103b。

第一氧氮化硅膜通过使用流量为20sccm的硅烷气体及流量为3000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为40Pa,功率为3000W,衬底温度为350℃。此外,第一氧氮化硅膜相当于实施方式1所示的绝缘层103d。

接着,在第一氧氮化硅膜上形成厚度为25nm的第一金属氧化物膜。第一金属氧化物膜通过使用In-Ga-Zn氧化物靶材(In∶Ga∶Zn=4∶2∶4.1[原子个数比])的溅射法形成。在成膜中,压力为0.3Pa,电源功率为4.5kW,衬底温度为室温。作为成膜气体使用氧气体和氩气体的混合气体,氧流量占成膜气体的总流量的比例(氧流量比)为10%。注意,通过使用In∶Ga∶Zn=4∶2∶4.1[原子个数比]的组成的靶材形成的样品的膜组成大致为In∶Ga∶Zn=4∶2∶3[原子个数比]。

接着,将第一金属氧化物膜加工为岛状而形成第一金属氧化物层。

接着,在氮气氛下以370℃进行1小时的加热处理,然后在氮和氧的混合气体(氮气体流量∶氧气体流量=4∶1)气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,作为第二栅极绝缘层依次形成厚度为5nm的第二氧氮化硅膜、厚度为130nm的第三氧氮化硅膜及厚度为5nm的第四氧氮化硅膜。

第二氧氮化硅膜通过使用流量为24sccm的硅烷气体及流量为18000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为130W,衬底温度为350℃。注意,第二氧氮化硅膜相当于实施方式1所示的绝缘层110a。

第三氧氮化硅膜通过使用流量为200sccm的硅烷气体及流量为10000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为300Pa,功率为750W,衬底温度为350℃。注意,第三氧氮化硅膜相当于实施方式1所示的绝缘层110b。

第四氧氮化硅膜通过使用流量为20sccm的硅烷气体及流量为3000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为40Pa,功率为500W,衬底温度为350℃。注意,第四氧氮化硅膜相当于实施方式1所示的绝缘层110c。

接着,在氮气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,在第四氧氮化硅膜上形成厚度为20nm的第二金属氧化物膜。第二金属氧化物膜通过使用In-Ga-Zn氧化物靶材(In∶Ga∶Zn=4∶2∶4.1[原子个数比])的溅射法形成。在成膜中,压力为0.8Pa,电源功率为3.5kW,衬底温度为室温。作为成膜气体,使用氧气体(氧流量比为100%)。

接着,在氮和氧的混合气体(氮气体流量∶氧气体流量=4∶1)气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,在第二金属氧化物膜上依次形成厚度为10nm的ITSO膜及厚度为100nm的铜膜。ITSO膜及铜膜通过溅射法形成。ITSO膜使用ITSO靶材(In2O3∶SnO2∶SiO2=85∶10∶5[重量比])形成。铜膜使用Cu靶材形成。

接着,在铜膜上形成抗蚀剂掩模,加工第二金属氧化物膜、ITSO膜及铜膜,由此形成第二金属氧化物层、ITSO层及铜层。在进行加工时使用湿蚀刻法。作为蚀刻剂,使用在使用之前以5∶1[体积比]混合药液A及药液B的两个药液而得的药液。作为药液A使用磷酸(低于5wt.%)、氢氟酸(低于1wt.%)、硝酸(低于10wt.%)、添加剂(低于22wt.%)的水溶液。作为药液B使用过氧化氢(31wt.%)的水溶液。蚀刻时的蚀刻剂温度为30℃。

使样品A1至样品A6的每一个的湿蚀刻处理时间不同而使样品A1至样品A6的每一个的区域108L的沟道长度方向的宽度L2不同。样品A1的湿蚀刻处理时间为60sec,样品A2的湿蚀刻处理时间为75sec,样品A3的湿蚀刻处理时间为90sec,样品A4的湿蚀刻处理时间为105sec,样品A5的湿蚀刻处理时间为120sec,并且样品A6的湿蚀刻处理时间为135sec。

接着,进行了洗涤。在洗涤中,使用将85wt.%的磷酸稀释到500倍的水溶液。蚀刻时的蚀刻剂温度为室温,处理时间为15sec。

接着,以上述抗蚀剂掩模为掩模对第二氧氮化硅膜至第四氧氮化硅膜进行加工来形成第二栅极绝缘层。此外,当形成第二栅极绝缘层时,去除不与该抗蚀剂掩模重叠的区域的第一氧氮化硅膜,以暴露第三氮化硅膜的一部分。在进行加工时使用干蚀刻法。然后,去除抗蚀剂掩模。

接着,作为覆盖晶体管的保护层依次形成厚度为100nm的第四氮化硅膜及厚度为300nm的第五氧氮化硅膜。

第四氮化硅膜通过使用流量为150sccm的硅烷气体及流量为5000sccm的氮气体及流量为100sccm的氨气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为2000W,衬底温度为350℃。

第五氧氮化硅膜通过使用流量为290sccm的硅烷气体及流量为4000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为133Pa,功率为1000W,衬底温度为350℃。

接着,在覆盖晶体管的保护层的一部分形成开口且通过溅射法依次形成厚度为30nm的钛膜、厚度为100nm的铜膜及厚度为50nm的钛膜,然后加工该膜来得到源电极及漏电极。然后,作为平坦化层形成厚度为1.5μm左右的丙烯酸树脂膜,在氮气氛下以250℃的温度进行1小时的加热处理。

通过上述工序,得到形成在玻璃衬底上的晶体管(样品A1至样品A6)。

<Id-Vd特性的评价>

接着,测量所制造的上述晶体管的Id-Vd特性。

晶体管的Id-Vd特性的测量条件为如下:源极电位设定为接地电位(GND)且在0V至30V的范围内每隔0.25V扫描漏电压(Vd)。在栅电压(Vg)为0V、2V、4V及6V的四个条件下使用相同晶体管连续地进行Id-Vd测量。作为晶体管的尺寸,沟道长度为3μm,并且沟道宽度为10μm。

图27及图28示出样品A1至样品A6的Id-Vd特性。在图27及图28的每一个中,横轴表示漏电压(Vd)且纵轴表示漏电流(Id)。

在图27中,在横向上示出样品A1至样品A3的结果。在图28中,在横向上示出样品A4至样品A6的结果。此外,样品A1的宽度L2为200nm左右,样品A2的宽度L2为300nm左右,样品A3的宽度L2为400nm左右,样品A4的宽度L2为500nm左右,样品A5的宽度L2为600nm左右,样品A6的宽度L2为700nm左右。

在图27及图28中,在纵向上示出晶体管的结构不同的条件。Single Gate表示在不包括导电层106的晶体管中对导电层112施加栅电压(Vg)而进行Id-Vd测量的结果。SourceSync.表示在包括导电层106的晶体管中以导电层106(底栅电极)与源电极(GND)电连接的状态对导电层112(顶栅电极)施加栅电压(Vg)而进行Id-Vd测量的结果。Top Gate Sync.表示在包括导电层106的晶体管中以导电层106(底栅电极)与导电层112(顶栅电极)电连接的状态对导电层112(顶栅电极)施加栅电压(Vg)而进行Id-Vd测量的结果。

如图27及图28所示,在Single Gate中,在任何条件下都呈现良好的Id-Vd特性。在Source Sync.及Top Gate Sync.中,在宽度L2为200nm左右、300nm左右及400nm左右时确认到通态电流的下降,但是在宽度L2为500nm以上时确认不到通态电流的下降而呈现良好的Id-Vd特性。由此可知,通过增大宽度L2,可以抑制施加高漏电压时的通态电流的下降。

[实施例2]

在本实施例中,制造分别相当于图2A至图2C所示的区域108C、区域108L及区域108N的样品(样品B1至样品B3)而对区域108C、区域108L及区域108N的电阻进行评价。样品B1相当于区域108C,样品B2相当于区域108L,并且样品B3相当于区域108N。

<样品B1的制造>

首先,在玻璃衬底上形成厚度为25nm的第一金属氧化物膜。第一金属氧化物膜通过使用In-Ga-Zn氧化物靶材(In∶Ga∶Zn=4∶2∶4.1[原子个数比])的溅射法形成。在成膜中,压力为0.6Pa,电源功率为2.5kW,衬底温度为室温。作为成膜气体使用氧气体和氩气体的混合气体,氧流量比为10%。

接着,在氮气氛下以370℃进行1小时的加热处理,然后在氮和氧的混合气体(氮气体流量∶氧气体流量=4∶1)气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,依次形成厚度为5nm的第一氧氮化硅膜、厚度为130nm的第二氧氮化硅膜及厚度为5nm的第三氧氮化硅膜。

第一氧氮化硅膜通过使用流量为24sccm的硅烷气体及流量为18000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为130W,衬底温度为350℃。

第二氧氮化硅膜通过使用流量为200sccm的硅烷气体及流量为10000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为300Pa,功率为750W,衬底温度为350℃。

第三氧氮化硅膜通过使用流量为20sccm的硅烷气体及流量为3000sccm的一氧化二氮气体的混合气体的PECVD法形成。在成膜中,压力为40Pa,功率为500W,衬底温度为350℃。

接着,在氮气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,在第三氧氮化硅膜上形成厚度为20nm的第二金属氧化物膜。第二金属氧化物膜通过使用In-Ga-Zn氧化物靶材(In∶Ga∶Zn=4∶2∶4.1[原子个数比])的溅射法形成。在成膜中,压力为0.8Pa,电源功率为3.5kW,衬底温度为室温。作为成膜气体,使用氧气体(氧流量比为100%)。

接着,在氮和氧的混合气体(氮气体流量∶氧气体流量=4∶1)气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,在第二金属氧化物膜上依次形成厚度为10nm的ITSO膜及厚度为100nm的铜膜。ITSO膜及铜膜通过溅射法形成。ITSO膜使用ITSO靶材(In2O3∶SnO2∶SiO2=85∶10∶5[重量比])形成。铜膜使用Cu靶材形成。

接着,形成厚度为100nm的氮化硅膜。

氮化硅膜通过使用流量为150sccm的硅烷气体及流量为5000sccm的氮气体及流量为100sccm的氨气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为2000W,衬底温度为350℃。

接着,去除氮化硅膜、铜膜、ITSO膜及第二金属氧化物膜,以暴露第三氧氮化硅膜。

接着,在第一氧氮化硅膜、第二氧氮化硅膜及第三氧氮化硅膜中形成到达第一金属氧化物膜的开口,以设置端子。

<样品B2的制造>

首先,在玻璃衬底上形成第一金属氧化物膜、第一氧氮化硅膜、第二氧氮化硅膜、第三氧氮化硅膜、第二金属氧化物膜、ITSO膜及铜膜。关于直到形成铜膜的步骤可以参照<样品B1的制造>的记载,由此不详细说明。

接着,去除铜膜、ITSO膜及第二金属氧化物膜,以暴露第三氧氮化硅膜。

接着,形成厚度为100nm的氮化硅膜。

氮化硅膜通过使用流量为150sccm的硅烷气体及流量为5000sccm的氮气体及流量为100sccm的氨气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为2000W,衬底温度为350℃。

接着,在第一氧氮化硅膜、第二氧氮化硅膜、第三氧氮化硅膜及氮化硅膜中形成到达第一金属氧化物膜的开口,以设置端子。

<样品B3的制造>

首先,在玻璃衬底上形成第一金属氧化物膜、第一氧氮化硅膜、第二氧氮化硅膜、第三氧氮化硅膜、第二金属氧化物膜、ITSO膜及铜膜。关于直到形成铜膜的步骤可以参照<样品B1的制造>的记载,由此不详细说明。

接着,去除铜膜、ITSO膜、第二金属氧化物膜、第一氧氮化硅膜、第二氧氮化硅膜、第三氧氮化硅膜,以暴露第一金属氧化物膜。

接着,形成厚度为100nm的氮化硅膜。

氮化硅膜通过使用流量为150sccm的硅烷气体及流量为5000sccm的氮气体及流量为100sccm的氨气体的混合气体的PECVD法形成。在成膜中,压力为200Pa,功率为2000W,衬底温度为350℃。

接着,在氮化硅膜中形成到达第一金属氧化物膜的开口,以设置端子。

<薄层电阻测量>

接着,测量所制造的上述样品的薄层电阻而评价第一金属氧化物膜的电阻。

图29示出样品B1至样品B3的薄层电阻值。在图29中,横轴表示样品名称,纵轴表示薄层电阻Rs。

如图29所示,相当于区域108C的样品B1的薄层电阻为1.5×1011Ω/□左右。相当于区域108L的样品B2的薄层电阻为4.6×105Ω/□左右。相当于区域108N的样品B3的薄层电阻为8.0×102Ω/口左右。

[实施例3]

在本实施例中,制造相当于图5A至图5C所示的晶体管100A的样品(样品C1及样品C2)而对截面形状进行评价。

<样品的制造>

首先,通过溅射法在玻璃衬底上依次形成厚度为30nm的钛膜与厚度为100nm的铜膜,对其进行加工来得到第一栅电极(底栅极)。

接着,作为第一栅极绝缘层依次形成厚度为50nm的第一氮化硅膜、厚度为150nm的第二氮化硅膜、厚度为100nm的第三氮化硅膜及厚度为3nm的第一氧氮化硅膜。关于第一至第三氮化硅膜及第一氧氮化硅膜可以参照实施例1的记载,由此不详细说明。

接着,在第一氧氮化硅膜上形成厚度为25nm的第一金属氧化物膜。关于第一金属氧化物膜可以参照实施例1的记载,由此不详细说明。

接着,将第一金属氧化物膜加工为岛状而形成第一金属氧化物层。

接着,在氮气氛下以370℃进行1小时的加热处理,然后在氮和氧的混合气体(氮气体流量∶氧气体流量=4∶1)气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,作为第二栅极绝缘层依次形成厚度为5nm的第二氧氮化硅膜、厚度为130nm的第三氧氮化硅膜及厚度为5nm的第四氧氮化硅膜。关于第二氧氮化硅膜至第四氧氮化硅膜可以参照实施例1的记载,由此不详细说明。

接着,在氮气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,在第四氧氮化硅膜上形成厚度为20nm的第二金属氧化物膜。关于第二金属氧化物膜可以参照实施例1的记载,由此不详细说明。

接着,在氮和氧的混合气体(氮气体流量:氧气体流量=4:1)气氛下以370℃进行1小时的加热处理。加热处理中利用烘箱装置。

接着,在第二金属氧化物膜上依次形成厚度为10nm的ITSO膜及厚度为100nm的铜膜。关于ITSO膜及铜膜可以参照实施例1的记载,由此不详细说明。

接着,在铜膜上形成抗蚀剂掩模,加工第二金属氧化物膜、ITSO膜及铜膜,由此形成第二金属氧化物层、ITSO层及铜层。在进行加工时使用湿蚀刻法。关于蚀刻剂可以参照实施例1的记载,由此不详细说明。湿蚀刻时间为60sec。

接着,以上述抗蚀剂掩模为掩模对第二氧氮化硅膜至第四氧氮化硅膜进行加工来形成第二栅极绝缘层。在进行加工时使用干蚀刻法。在此,样品C1和样品C2的干蚀刻条件不相同。

样品C1的蚀刻气体使用C4F8。ICP高频功率为6000W,Bias高频功率为1000W,压力为0.67Pa,C4F8气体流量为100sccm,蚀刻时间为140sec,并且下部电极温度为10℃。

样品C2的蚀刻气体使用CF4。ICP高频功率为6000W,Bias高频功率为750W,压力为0.67Pa,CF4气体流量为100sccm,蚀刻时间为112sec,并且下部电极温度为10℃。

接着,去除抗蚀剂掩模。

接着,作为覆盖晶体管的保护层依次形成厚度为100nm的第四氮化硅膜及厚度为300nm的第五氧氮化硅膜。关于第四氮化硅膜及第五氧氮化硅膜可以参照实施例1的记载,由此不详细说明。

接着,在覆盖晶体管的保护层的一部分形成开口且通过溅射法依次形成厚度为30nm的钛膜、厚度为100nm的铜膜及厚度为50nm的钛膜,然后加工该膜来得到源电极及漏电极。然后,作为平坦化层涂上厚度为1.5μm左右的丙烯酸树脂膜,在氮气氛下以250℃的温度进行1小时的加热处理。

通过上述工序,得到形成在玻璃衬底上的晶体管(样品C1及样品C2)。

<截面观察>

接着,通过聚焦离子束(FIB:Focused Ion Beam)使样品C1及样品C2薄片化,通过STEM观察样品C1及样品C2的截面。

<蚀刻速度评价>

关于在样品C1及样品C2的制造中用于第二氧氮化硅膜至第四氧氮化硅膜的蚀刻的干蚀刻条件,评价了蚀刻速度。

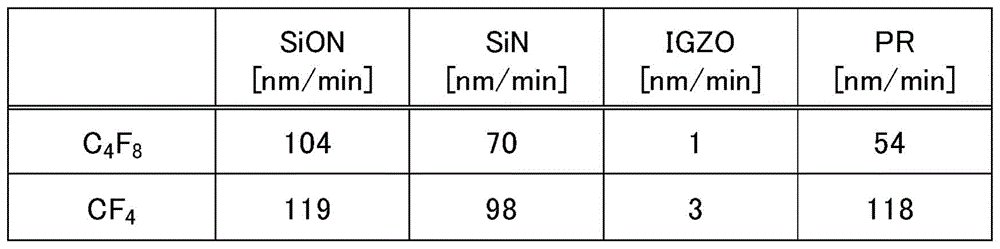

表1示出蚀刻速度。表1的上段表示在样品C1的制造中使用C4F8气体时的蚀刻速度,下段表示在样品C2的制造中使用CF4气体时的蚀刻速度。此外,表1在横向上表示被蚀刻膜的种类。SiON表示氧氮化硅膜,SiN表示氮化硅膜,IGZO表示金属氧化物膜,并且PR表示抗蚀剂膜。

[表1]