JP5627163B2 - 動作モード及びスリープモードでのデータ保持方法および回路 - Google Patents

動作モード及びスリープモードでのデータ保持方法および回路 Download PDFInfo

- Publication number

- JP5627163B2 JP5627163B2 JP2006278533A JP2006278533A JP5627163B2 JP 5627163 B2 JP5627163 B2 JP 5627163B2 JP 2006278533 A JP2006278533 A JP 2006278533A JP 2006278533 A JP2006278533 A JP 2006278533A JP 5627163 B2 JP5627163 B2 JP 5627163B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- signal

- latch

- sleep

- tri

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 11

- 230000004044 response Effects 0.000 claims description 28

- 230000005540 biological transmission Effects 0.000 claims description 27

- 230000014759 maintenance of location Effects 0.000 claims description 23

- 230000002457 bidirectional effect Effects 0.000 claims description 10

- 230000001360 synchronised effect Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 14

- 230000003068 static effect Effects 0.000 description 8

- 238000013461 design Methods 0.000 description 7

- 230000007704 transition Effects 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 230000000717 retained effect Effects 0.000 description 4

- 238000009434 installation Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000008859 change Effects 0.000 description 1

- 230000001351 cycling effect Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 235000014347 soups Nutrition 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Landscapes

- Logic Circuits (AREA)

Description

本願は2005年10月13日提出の共通に所有される米国特願第11/249135号の一部継続出願(IP)である。

12 第1スリープ信号分配論理

30 マスタースレーブ保持フロップ

31 データ入力

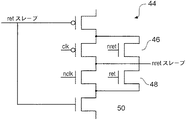

32、34、50 トランスミッションゲート

33 進行データ路

36 マスターラッチ

39 データ出力

40 スレーブラッチ

42 インバータ

44、47 トライステート・インバータ

50 トライステート可能素子

60 保持ラッチ

63 NANDゲート

64 トライステート・インバータ

65、67 スリープ・トランジスタ

66 ゲート

Claims (24)

- 回路の部分を電力ダウンしつつスリープモード時に信号値を保持する回路において、

クロック信号を受取るように動作するクロック信号入力と、

前記クロック信号によりクロックされる少なくとも1個のラッチと、

データ入力、データ出力及びその間の進行データ路であって、信号値は前記データ入力で受取られるよう動作し、前記データ入力で受取られた信号値が前記ラッチに供給されるクロック信号に同期して前記少なくとも1個のラッチへラッチされ、前記進行データ路に沿って前記データ出力へ渡される前記データ入力、データ出力及びその間の進行データ路と、を含み、

前記少なくとも1個のラッチの少なくとも1個は、前記スリープモードの間信号値を保持するように動作する保持ラッチを含み、前記回路はさらに、

トライステート可能素子であって、前記進行データ路と前記保持ラッチとの間に配置され、第1スリープ信号がアサートされている時に前記進行データ路から前記保持ラッチを分離するよう動作する前記トライステート可能素子を含み、

前記第1スリープ信号アサートの後に第2スリープ信号がアサートされると、前記保持ラッチと前記トライステート可能素子上の電圧差が保持され、前記回路の前記部分上の電圧差が減少されるように、前記回路の前記部分が電力ダウンして、前記回路がスリープモードに入るよう動作し、

第2スリープ信号がアサート解除されると前記回路の前記部分が前記回路がスリープモードから抜け出して前記回路の前記部分に電力が供給され、

前記回路はさらに前記保持ラッチと前記出力との間に存在する出力素子と、前記出力素子の入力と接続された駆動素子とを含み、

前記出力素子と前記駆動素子は第2スリープ信号がアサートされると前記スリープモードに入るよう動作し、

前記駆動素子は、前記第2スリープ信号がアサートされていない時に前記出力素子を駆動するよう動作する、

回路。 - 請求項1記載の回路において、前記クロック信号によりクロックされる複数個のラッチを含み、前記信号値は前記複数個のラッチの内の1個から前記進行データ路に沿って前記複数個のラッチの以後のものへ渡され、前記複数個のラッチの少なくとも1個は前記保持ラッチを含む、回路。

- 請求項1記載の回路において、前記トライステート可能素子は双方向トライステート可能素子を含む回路。

- 請求項3記載の回路において、前記トライステート可能素子は、前記第1スリープ信号を受取るよう動作する2個のトランジスタを含み、前記2個のトランジスタは、前記第1スリープ信号がアサートされている時に前記2個のトランジスタは高インピーダンス路を形成し、前記第1スリープ信号がアサートされていない時に前記2個のトランジスタは低インピーダンス路を形成するよう配置されている回路。

- 請求項1記載の回路において、前記トライステート可能素子は4個のトランジスタを含み、前記4個のトランジスタの内の2個は前記トライステート可能素子を形成し、前記4個のトランジスタの内の2個は、前記2個のトランジスタの一方へ入力する前に前記第1スリープ信号を反転するよう動作するインバータを形成する、回路。

- 請求項5記載の回路において、前記トライステート可能素子はトランスミッションゲートを含む回路。

- 請求項1記載の回路において、前記保持ラッチは前記クロック信号を受取るよう動作する回路。

- 請求項7記載の回路において、前記回路はさらに、

前記クロック信号を前記保持ラッチへ分配するよう動作するクロック信号分配装置と、を含む回路。 - 請求項8記載の回路において、前記クロック信号分配装置は第1スリープ信号を受け取るように動作する第1信号スリープ信号入力を含み、

前記第1スリープ信号がアサートされている時に前記クロック分配装置は、前記保持ラッチがステートを保持するように前記クロック信号を所定の値に保持するよう動作する、回路。 - 請求項8記載の回路において、前記クロック信号分配装置は、クロック信号入力と第1スリープ信号入力とを有する論理ゲートを含む、回路。

- 請求項7記載の回路において、前記保持ラッチはクロックされたトライステート・インバータと、前記クロックされたトライステート・インバータの一部と並列に配置されて前記第1スリープ信号を入力するトランジスタとを含み、前記保持ラッチは、前記第1スリープ信号がアサートされている時に前記クロックの値に係わらずステートを保持するよう動作する回路。

- 請求項11記載の回路において、前記トランジスタは前記トライステート・インバータの前記2個のクロックされたトランジスタと並列の2個のトランジスタを含み、前記2個のトランジスタは前記第1スリープ信号と反転第1スリープ信号を各々受取る、回路。

- 請求項1記載の回路において、前記回路は少なくとも1個の別なラッチを含み、前記ラッチの少なくとも2個はマスターラッチとスレーブラッチとを含むマスタースレーブ・フリップフロップを含み、前記保持ラッチは前記スレーブラッチを含む、回路。

- 請求項13記載の回路において、前記マスタースレーブ・フリップフロップはリセット・マスタースレーブ・フリップフロップを含み、前記保持ラッチは、前記第1スリープ信号とリセット信号とを受取るよう動作し、前記第1スリープ信号がアサートされている時に前記リセット信号を阻止して前記保持ラッチのステートをリセットすることを防止するよう動作する2個のトランジスタを含む、回路。

- 請求項13記載の回路において、前記マスタースレーブ・フリップフロップはセット・マスタースレーブ・フリップフロップを含み、前記保持ラッチは、前記第1スリープ信号とセット信号とを受取るよう動作し、前記第1スリープ信号がアサートされている時に前記セット信号を阻止して前記保持ラッチのステートをセットすることを防止するよう動作する2個のトランジスタを含む、回路。

- 請求項1記載の回路において、前記回路は前記回路の部分へ供給される電圧レベルを制御するよう動作する電圧制御器を含み、前記電圧制御器は前記第2スリープ信号を受取るよう動作し、前記第2スリープ信号がアサートされると前記回路の前記部分が電力ダウンするよう前記回路の前記部分上の電圧差を減少し、前記保持ラッチと前記トライステート可能素子上の電圧差を保持するよう動作する、回路。

- 請求項1記載の回路において、前記保持ラッチと前記トライステート可能素子は低漏れ電流素子を含む回路。

- 請求項1記載の回路において、複数個の保持ラッチを含む回路。

- 請求項1記載の回路において、前記保持ラッチは循環ループを含み、前記駆動素子は前記ループの出力から遠隔の前記循環ループの部分と接続された入力を有するトライステート・インバータである、回路。

- 請求項19記載の回路において、前記回路は、前記クロック信号を前記保持ラッチと前記トライステート・インバータへ分配するクロック信号分配装置をさらに含み、前記クロック信号分配装置は第1スリープ信号を受取るように動作する第1スリープ信号入力と第2スリープ信号を受取るように動作する第2スリープ信号入力とを含み、前記クロック分配装置は、前記第1スリープ信号がアサートされ前記第2スリープ信号がアサートされていない時に、所定のレベルの信号を出力し、前記第1スリープ信号と前記第2スリープ信号の双方がアサートされている時に電力ダウンされ、どちらもアサートされていない場合に前記クロック信号を出力するよう動作し、

前記トライステート・インバータは、前記第2スリープ信号がアサートされていない時に前記所定レベルである前記クロック信号に応答して前記出力インバータを駆動する、回路。 - 請求項1記載の回路において、前記駆動素子はトライステート可能素子を含み、前記トライステート可能素子は、前記進行データ路に配置された別の前記トライステート可能素子とは反対にクロックされ、前記双方のトライステート可能素子の一つが所定のレベルを有するクロック信号に応答して前記出力素子を駆動するよう動作する、回路。

- 請求項21記載の回路において、前記回路は少なくとも1個の別なラッチを含み、前記ラッチの少なくとも2個はマスターラッチとスレーブラッチ、及び2個のリセット入力を含む、リセット・マスタースレーブ・フリップフロップを含み、前記2個のリセット入力の各々は前記2個の反対にクロックされたトライステート可能素子の各々を介して前記保持ラッチと接続しており、前記保持ラッチは前記スレーブラッチを含み、前記保持ラッチは循環ループとトライステート可能素子を含み、前記トライステート可能素子は前記第1スリープ信号がアサートされると前記リセット入力から前記循環ループを分離するよう動作する、回路。

- 回路の部分を電力ダウンしつつスリープモード時に回路内の信号値を記憶する方法において、前記方法は、

クロック信号を少なくとも1個のラッチのクロック入力に分配する段階であって、前記少なくとも1個のラッチはデータ入力とデータ出力との間に配置され、前記データ入力で受取った信号値が前記少なくとも1個のラッチにクロック入力され、進行データ路に沿って前記データ出力に渡され、前記少なくとも1個のラッチの内の少なくとも1個は前記スリープモード時に信号値を保持するよう動作する保持ラッチである、前記分配する段階と、を含み、

第1スリープ信号がアサートされると、

前記進行データ路と前記保持ラッチとの間に配置したトライステート可能素子を使用して前記進行データ路から前記保持ラッチを分離する段階と、

第2スリープ信号がアサートされると、

前記回路の前記部分が電力ダウンするように、前記回路の前記部分上の電圧差を減少する段階と、

前記保持ラッチと前記トライステート可能素子上の電圧差を保持する段階と、

出力素子と該出力素子の駆動素子とを電力ダウンする段階と、を含み、

前記第2スリープ信号がアサートされていないとき、前記駆動素子は前記出力素子の入力を駆動する、

回路の一部を電力ダウンしつつスリープモード時に回路内の信号値を記憶する方法。 - 回路の部分を電力ダウンしつつ信号値を保持する回路において、

クロック信号を受取るよう動作するクロック信号入力と、

前記クロック信号によりクロックされるデータを保持する装置と、を含み、

前記装置は、

信号値がデータ入力から通過し、保持装置にクロックされ、前記進行データ路に沿ってデータ出力へ通過するような進行データ路と、

スリープモード時に信号値を保持するよう動作する前記保持装置と、

第1スリープ信号がアサートされている時に、前記進行データ路から前記保持装置を分離するトライステート可能装置であって、前記進行データ路と前記保持装置との間に配置されている前記トライステート可能素子と、を含み、

前記第1スリープ信号のアサートされた後に第2スリープ信号がアサートされると、前記回路の前記部分が電力ダウンされ、前記保持装置と前記トライステート可能装置上の電圧差を保持するよう前記回路の前記部分上の電圧差が減少されるように前記回路が前記スリープモードに入るよう動作し、

前記回路はさらに前記保持ラッチと前記データ出力との間の出力素子と、前記出力素子の入力と接続する駆動素子とを含み、

前記出力素子と前記駆動素子は前記第2スリープ信号がアサートされると前記スリープモードに入るよう動作し、

前記駆動素子は、前記第2スリープ信号がアサートされていない時に前記出力素子の入力を駆動するよう動作する、

回路の一部を電力ダウンしつつ信号値を保持する回路。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/249,135 | 2005-10-13 | ||

| US11/249,135 US20070085585A1 (en) | 2005-10-13 | 2005-10-13 | Data retention in operational and sleep modes |

| US11/415,436 US7514975B2 (en) | 2005-10-13 | 2006-05-02 | Data retention in operational and sleep modes |

| US11/415,436 | 2006-05-02 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007110728A JP2007110728A (ja) | 2007-04-26 |

| JP5627163B2 true JP5627163B2 (ja) | 2014-11-19 |

Family

ID=38036159

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006278533A Active JP5627163B2 (ja) | 2005-10-13 | 2006-10-12 | 動作モード及びスリープモードでのデータ保持方法および回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5627163B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101777643B1 (ko) | 2009-12-11 | 2017-09-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 논리 회로, 및 cpu |

| JP5704600B2 (ja) * | 2010-11-26 | 2015-04-22 | ルネサスエレクトロニクス株式会社 | 半導体集積回路 |

| TWI567735B (zh) | 2011-03-31 | 2017-01-21 | 半導體能源研究所股份有限公司 | 記憶體電路,記憶體單元,及訊號處理電路 |

| KR102501754B1 (ko) * | 2016-03-28 | 2023-02-20 | 삼성전자주식회사 | 불균형 멀티플렉서 및 이를 적용하는 스캔 플립플롭 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07154228A (ja) * | 1993-09-30 | 1995-06-16 | Nippon Telegr & Teleph Corp <Ntt> | 論理回路装置 |

| JPH08256044A (ja) * | 1995-03-16 | 1996-10-01 | Nippon Telegr & Teleph Corp <Ntt> | 記憶回路およびフリップフロップ回路 |

| JPH11330918A (ja) * | 1998-05-20 | 1999-11-30 | Nec Corp | 順序回路 |

| JP3183260B2 (ja) * | 1998-06-17 | 2001-07-09 | 日本電気株式会社 | スキャンフリップフロップ回路 |

-

2006

- 2006-10-12 JP JP2006278533A patent/JP5627163B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007110728A (ja) | 2007-04-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7514975B2 (en) | Data retention in operational and sleep modes | |

| JP3080062B2 (ja) | 半導体集積回路 | |

| US7391250B1 (en) | Data retention cell and data retention method based on clock-gating and feedback mechanism | |

| US8242826B2 (en) | Retention flip-flop | |

| JP3727838B2 (ja) | 半導体集積回路 | |

| JP4245413B2 (ja) | 相補型バッファ回路及びその制御方法 | |

| US7180348B2 (en) | Circuit and method for storing data in operational and sleep modes | |

| CN103684355B (zh) | 门控时钟锁存器、其操作方法和采用其的集成电路 | |

| US6989702B2 (en) | Retention register with normal functionality independent of retention power supply | |

| JP2005527166A (ja) | リーク電流制御を用いた非揮発性多しきい値cmosラッチ | |

| JP3912960B2 (ja) | 半導体集積回路、論理演算回路およびフリップフロップ | |

| KR101729004B1 (ko) | 상태 리텐션 회로 및 그 회로의 작동방법 | |

| US7154317B2 (en) | Latch circuit including a data retention latch | |

| JP2008219785A (ja) | 半導体集積回路 | |

| JP4138521B2 (ja) | 半導体装置 | |

| JP2006025400A (ja) | 信号値の記憶回路と方法 | |

| JP2003249843A (ja) | フリップフロップおよび動作方法 | |

| US6836175B2 (en) | Semiconductor integrated circuit with sleep memory | |

| JP5627163B2 (ja) | 動作モード及びスリープモードでのデータ保持方法および回路 | |

| US7091766B2 (en) | Retention register for system-transparent state retention | |

| JP4220326B2 (ja) | Mtcmos用クロックド・スキャン・フリップフロップ | |

| Liu et al. | New MTCMOS flip-flops with simple control circuitry and low leakage data retention capability | |

| US7224197B2 (en) | Flip-flop implemented with metal-oxide semiconductors using a single low-voltage power supply and control method thereof | |

| US20070171731A1 (en) | Leakage mitigation logic | |

| JP2001127595A (ja) | フリップフロップ回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111014 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120116 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120207 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120907 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121207 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140716 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140930 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5627163 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |