JP3584893B2 - フィルタ回路 - Google Patents

フィルタ回路 Download PDFInfo

- Publication number

- JP3584893B2 JP3584893B2 JP2001072572A JP2001072572A JP3584893B2 JP 3584893 B2 JP3584893 B2 JP 3584893B2 JP 2001072572 A JP2001072572 A JP 2001072572A JP 2001072572 A JP2001072572 A JP 2001072572A JP 3584893 B2 JP3584893 B2 JP 3584893B2

- Authority

- JP

- Japan

- Prior art keywords

- transconductance

- output

- filter

- transconductors

- common

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000010586 diagram Methods 0.000 description 12

- 230000008859 change Effects 0.000 description 10

- 239000003990 capacitor Substances 0.000 description 9

- 238000000034 method Methods 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 6

- 238000013461 design Methods 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 4

- 238000012546 transfer Methods 0.000 description 3

- 239000000470 constituent Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000007476 Maximum Likelihood Methods 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/34—DC amplifiers in which all stages are DC-coupled

- H03F3/343—DC amplifiers in which all stages are DC-coupled with semiconductor devices only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Networks Using Active Elements (AREA)

- Amplifiers (AREA)

Description

【発明の属する技術分野】

本発明は、フィルタ回路、特にGm−C(トランスコンダクタ−C)フィルタと呼ばれるアクティブフィルタ回路及びこのようなフィルタ回路の構成要素となるトランスコンダクタに関するものである。

【0002】

【従来の技術】

アクティブフィルタ、例えば、Gm−Cフィルタを構成要素とする集積化フィルタ回路に関し、フィルタのQ値を保ったまま、カットオフ周波数fC を容易にしかもリニア(線形的)に調整できるものが望まれる。

【0003】

磁気あるいは光ディスクなどの情報記録媒体からの記録情報を再生する記録データ再生系(リードチャネル)に、PRML(Pertial Response−Maximum Likelihood )に代表される波形等化手法が一般的に取り入れられている。通常、記録媒体から光ピックアップまたは磁気ヘッドを介して再生される信号波形は隣接するビットデータ間の信号漏れ込み、即ち、ISI(Inter−Symbol Interference)が大きく、当該サンプル時刻の信号レベルのみによるデータの再生が困難である。PR(Pertial Response)等化手法は、隣接する2〜5サンプル時刻に限りISIを許容する一方、それ以外のサンプル時刻への信号の漏れをなくすことで、後段のビタビ(Viterbi )復号アルゴリズムなどと合わせて高密度記録と再生を可能にする方法である。

【0004】

再生信号が本質的に微分系である磁気媒体を例にとると、等化法としてPR4(書き込み符号1を隣接する3サンプル列1,0,−1に等化)、EPR4(同じく、1,1,−1,−1に等化)、EEPR4(同じく1,2,0,−2,−1)に等化などの微分系列が用いられ、具体的には高域強調したアナログ−ローパスフィルタが等化器として用いられる。例えば、Geert A. De Veirman 及びRichard G. Yamasaki は、文献“Design of a Bipolar 10−MHz Programmable Continuous−Time 0.05°Equiripple Linear Phase Filter”, IEEE Journal of Solid−State Circuits, vol.27, no.3, March 1992において、Gm−Cバイクワッドフィルタ(Biquadratic Filter、双2次状態変数フィルタ、以下、便宜上単に2次状態変数フィルタという)を構成要素とする7極2零点(7−Pole, 2−Zero)フィルタを提案している。このフィルタ構成はディジタルリードチャネルに要求される位相特性のリニアリティ、即ち、良好で一定な群遅延特性を有しており、アナログ等化フィルタとして一般的に用いられている。

【0005】

図5には、このフィルタの構成を示すブロック図である。

図示のように、このフィルタは、縦続接続されている2次状態変数フィルタ/イコライザ101(Biquad1/Equalizer )、102(Biquad2 )、103(Biquad3 )及びローパスフィルタ(LPF)104によって構成されている。なお、2次状態変数フィルタ/イコライザ101は、等化のためのイコライジング機能を有する。図5に示すフィルタ構成において、再生信号Sinは、所望のゲインコントロール(利得制御)を施されたあと、まず、初段の2次状態変数フィルタ/イコライザ101に入力され、ここでは高周波ブースト量が調整され、さらに等化のためのイコライジングが行われる。そして、後続の2次状態変数フィルタ102、103及びローパスフィルタ104とあわせて群遅延が一定の位相特性が達成される。上述したVeirman 及び Yamasaki によると、各フィルタの構成要素の極周波数及びそのQ値は、図6に示す通りである。

【0006】

図6における極周波数は、等化フィルタのカットオフ周波数で規格化されており、例えば、400Mbpsのデータレートのリードチャネルでは、等化フィルタのカットオフ周波数は100MHz程度となる。これにより等化フィルタのカットオフ周波数が100MHzとすると、図6により、例えば、3段目の2次状態変数フィルタ103の極周波数、即ち、カットオフ周波数は231.74MHzとなる。なお、図6の極周波数/Q値の組み合わせ、即ち極の配置は、フィルタ設計において良く知られている「0.05°等リップル誤差を持つ線形位相フィルタ」であるが、他の極周波数/Q値においても適用可能で、ここでの極配置は一例に過ぎない。

【0007】

ディスク媒体の再生データレートは、内周、外周で約2.5倍の開きがあり、また、最適なカットオフ周波数に外部コントロール手段によって調整可能であることが要求される。このとき、フィルタの構成要素となる各2次状態変数フィルタ及びローパスフィルタでは、そのQ値が常に図6に示す値を保持し、また、各2次状態変数フィルタ及びローパスフィルタの極周波数の比は等化フィルタ全体のカットオフ周波数にかかわらず、常に図6に示される比であることが必要である。言い換えれば、再生データレートの変化に応じて等化フィルタ全体のカットオフ周波数を調整するに当たり、構成要素となる各2次状態変数フィルタ及びローパスフィルタはそれぞれのQ値を一定に保ったまま、各極周波数が単調に増加または減少する必要がある。

【0008】

次に、等化フィルタをGm−Cフィルタで構成する場合の各構成要素の回路例を示し、上記カットオフ周波数及びQ値の設計法について述べる。

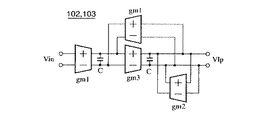

図7に2次状態変数フィルタ102、103の基本構成を示し、図8に2次状態変数フィルタ/イコライザ101に使われるフィードフォワードパルススリミング構成を示している。さらに、図9には、1次のローパスフィルタ104の構成を示している。

【0009】

図7は、差動構成を有する2次状態変数の一構成例を示している。図示のように、Gm−Cで構成される積分器が2段カスケード接続され、さらに出力端子に別のGmセルで構成された負帰還ループが接続されている。なお、図7において、負荷容量Cを差動容量として表現しているが、一般的には寄生容量分を考慮した容量設定のし易さや、同相帰還ループにおける位相補償容量の機能を併せ持たせるなどの理由から正相、逆相信号線と接地電位との間にそれぞれ2Cの容量を接続する。

【0010】

図7に示す構成を有し、等化フィルタとして用いられる2次状態変数フィルタ102及び103の伝達関数は、次式によって与えられる。

【0011】

【数1】

【0012】

従って、極周波数ω0 及びフィルタのQ(Quality Factor)は、それぞれ次式によって表される。

【0013】

【数2】

【0014】

図8は、フィードフォワード増幅器Kにより、高域ブースト量を調整可能なイコライザ部を含む等化フィルタの一構成例を示している。この等化フィルタの伝達関数は、次式によって与えられる。

【0015】

【数3】

【0016】

同様に、このフィルタの極周波数及びQは、それぞれ次式によって表される。

【0017】

【数4】

【0018】

ここで、高域ブーストを2次状態変数フィルタ/イコライザ101で実現する理由は、図6から分かるように、相対的に小さいKで高域ブーストができるためである。このため、高域ブーストの実現は、2次状態変数フィルタ/イコライザ101に限られず、他の2次状態変数によって実現することも可能である。

【0019】

図9は、ローパスフィルタ104の一構成例を示している。図示のように、このフィルタの伝達関数は、次式によって与えられる。

【0020】

【数5】

【0021】

その極周波数ω0 は、次のように求められる。

【0022】

【数6】

【0023】

群遅延特性が一定で、カットオフ周波数可変の等化フィルタの実現は、図6に示される極周波数の比とQ値を満たすべく、各2次状態変数フィルタの極周波数ω0 及びQを設定することで行われる。これは通常各2次状態変数フィルタを構成するgm を制御することで実現できる。式(1)〜(5)によれば、容量Cを変化させることで、それぞれのフィルタのカットオフ周波数を可変とすることも原理的は可能だが、バリキャップなどの可変容量素子を標準CMOS製造プロセスに集積化することは、製造プロセスの工程数を増やし、コストの上昇を招くので、通常避けるべきである。ただし、この場合においても各Gm−C積分器に接続する容量値をC,2C,3CのようにC単位、あるいは0.5C単位で段階的に変えることによってフィルタのカットオフ周波数を比較的に広範囲に粗く変化させ、さらにgm 値を制御してフィルタのカットオフ周波数を連続的にしかも精度良く調整することは一般的に行われる。

【0024】

容量Cを固定とした場合、ω0 及びQの二つの値を決定するのにgm1,gm2,gm3のパラメータ(自由度)を調整することができる。通常、gm2=gm3、またはgm1=gm3とするのが一般的である。gm2=gm3とすることによって式(2)あるいは式(4)は、次の式に書き改められる。

【0025】

【数7】

【0026】

一方、gm1=gm3とすると、式(2)あるいは式(4)は、次のように書き改められる。

【0027】

【数8】

【0028】

上記いずれの場合でも、2次状態変数フィルタのを構成するgm がすべてリニアに変化することによって、Qを一定に保ちつつ、ω0 をやはりリニアに変化させることができる。例えば、一例として、gm1とgm2をともに2倍にすれば、Qを不変に保ちつつ、カットオフ周波数ω0 を2倍に変化させることができる。

【0029】

以上の説明から分かるように、Gm−C構成の2次状態変数フィルタ及び一次ローパスフィルタを設計する場合、回路レベルのGm−C積分器として、そのgm の値が外的手段によって制御でき、しかもリニアに制御できることが好都合となる。

【0030】

従来よりこのような高周波フィルタ用途には、シリコンバイポーラ素子が利用されてきた。バイポーラ素子においては、周知のように、そのgm (以下、MOSトランジスタのgm と区別するために、gm,bip と表記する)は次の式によって示される。

【0031】

【数9】

【0032】

式(9)によれば、バイポーラトランジスタのgm,bip が、そのコレクタ電流IC に比例することを示し、比較的簡単にgm,bip をリニアに変化させることが可能である。

【0033】

一方で、PRMLリードチャネル機能は前述のビタビ復号処理、あるいはエラー訂正アルゴリズムであるリード・ソロモンなどに代表される次段論理処理と不可分であり、これらの純ディジタル処理ブロックと親和性の高いCMOS製造プロセスでアナログPR等化処理を行いたいという要望は強い。

【0034】

MOS素子のgm (以下、明確するために、gm,MOS と表記する)は、周知のように、次式によって示される。

【0035】

【数10】

【0036】

ここで、VthはMOSトランジスタのしきい値電圧(閾値電圧)であり、K=μCoxW/2L、且つVeff =VGS−Vthである。

【0037】

式(10)と式(9)とを比較すると、バイポーラ素子のgm はコレクタ電流IC に対しリニアである一方、CMOS素子のgm はドレイン電流ID のルートに対してリニアであるため、CMOS素子の場合、何らかの外的手段によってドレイン電流ID を変化させることによってそのgm を制御する場合は、通常、各トランスコンダクタ毎に上記ルート特性を補償するための変換機構を設け、変化範囲内における最低のgm,min から、最大gm,max に至るまでリニアに変化した方が制御性の点において望ましい。

【0038】

【発明が解決しようとする課題】

ところで、上述した従来のCMOS素子で構成された等化フィルタにおいて、例えば、PR等化フィルタのカットオフ周波数調整は5〜6ビット幅程度の調整手段によって行われる。この場合、上記ルート特性を補正する変換機構は、例えば、ルックアップテーブルによるディジタル領域の処理によっても実現でき、また、別にアナログ領域でルート特性を補償することもできる。

しかし、いずれの場合も、付加回路による回路規模の増大、消費電力の増大を招き、またこれによるフィルタ特性そのものの劣化を引き起こしている。

【0039】

また、別の問題として、ドレイン電流ID でCMOS素子のgm をコントロールする場合、一般に何らかのリニアライズ手段が必要であり、その結果、CMOS素子本来のトランスコンダクタンスが回路gm として得られないという不利が生じるほか、回路規模の増加及びそれによる消費電力の増加が避けられない。

例えば、図10に示すMOSトランジスタからなる差動回路では、バイアス電流IB でMOSトランジスタのgm を制御できる、その関係は次式によって表される。

【0040】

【数11】

【0041】

式(11)に示すように、非線形項が含まれる。このため、様々なリニアライズ手法によって線形化する必要があり、この結果得られるgm は、式(10)に示されるMOS素子の本来のgm,MOS の値より大幅に小さいものとなってしまう。

【0042】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、回路規模の増加を抑制でき、回路設計が容易に行え、定電源電圧動作による消費電力の低減を実現でき、オフセット周波数を安定に制御できるフィルタ回路を提供することにある。

【0043】

【課題を解決するための手段】

上記目的を達成するため、本発明のフィルタ回路は、入力端子に入力信号が印加される第1のトランスコンダクタンスと、入力端子に出力信号が印加される第2のトランスコンダクタンスと、上記第1および第2のトランスコンダクタンスの出力側に接続され、当該トランスコンダクタンスによって駆動される負荷容量素子とを含むトランスコンダクタ−C(Gm−C)回路と、上記第1および第2のトランスコンダクタの出力信号と制御電圧に応じて、当該第1および第2のトランスコンダクタの差動出力信号の平均電圧と上記制御制御電圧とが一致するようにバイアス電圧を生成して上記第1および第2のトランスコンダクタに供給する同相電位制御回路と、を有し、上記第1および第2のトランスコンダクタの各々は、上記バイアス電圧によって出力電流が制御される第1および第2の電流源と、ゲートが正相入力端子に接続され、ソースが接地され、ドレインに上記第1の動作電流を供給する第1の電流源が接続されている第1のMOSトランジスタと、ゲートが逆相入力端子に接続され、ソースが接地され、ドレインに第2の動作電流を供給する上記第2の電流源が接続されている第2のMOSトランジスタと、を含む。

【0044】

また、本発明のフィルタ回路は、入力端子に入力信号が印加される第1のトランスコンダクタンスと、入力端子に出力信号が印加され、出力端子が上記第1のトランスコンダクタンスの出力端子に接続された第2のトランスコンダクタンスと、入力端子が上記第1および第2のトランスコンダクタンスの出力端子に接続された第3のトランスコンダクタンスと、入力端子に出力信号が印加され、出力端子が上記第3のトランスコンダクタンスの出力端子に接続された第4のトランスコンダクタンスと、上記第1および第2のトランスコンダクタンスの出力側に接続され、当該トランスコンダクタンスによって駆動される第1の負荷容量素子と、上記第3および第4のトランスコンダクタンスの出力側に接続され、当該トランスコンダクタンスによって駆動される第2の負荷容量素子とを含むトランスコンダクタ−C(Gm−C)回路と、上記第1および第2のトランスコンダクタの出力信号と制御電圧に応じて、当該第1および第2のトランスコンダクタの差動出力信号の平均電圧と上記制御電圧とが一致するようにバイアス電圧を生成して上記第1および第2のトランスコンダクタに供給する第1の同相電位制御回路と、を有し、上記第3および第4のトランスコンダクタの出力信号と制御電圧に応じて、当該第3および第4のトランスコンダクタの差動出力信号の平均電圧と上記制御電圧とが一致するようにバイアス電圧を生成して上記第3および第4のトランスコンダクタに供給する第2の同相電位制御回路と、を有し、上記第1、第2、第3、および第4のトランスコンダクタの各々は、上記バイアス電圧によって出力電流が制御される第1および第2の電流源と、ゲートが正相入力端子に接続され、ソースが接地され、ドレインに上記第1の動作電流を供給する第1の電流源が接続されている第1のMOSトランジスタと、ゲートが逆相入力端子に接続され、ソースが接地され、ドレインに第2の動作電流を供給する上記第2の電流源が接続されている第2のMOSトランジスタと、を含む。

【0045】

また、本発明では、好適には、上記同相電位制御回路は、上記第1と第2のMOSトランジスタからなる差動回路から出力される差動出力信号と所定の基準電位とに応じて、上記制御信号を生成する。

【0046】

また、本発明では、好適には、上記同相電位制御回路は、上記第1と第2のMOSトランジスタからなる差動回路から出力される差動出力信号の平均電位が上記基準電位と一致するように上記制御信号を生成する。

【0047】

また、本発明では、好適には、上記第1と第2のトランジスタのゲートに入力される同相電位が、所望のトランスコンダクタンス値になるように制御される。

【0048】

さらに、本発明では、好適には、上記第1と第2のトランジスタのチャネル幅とチャネル長との比を、所望のトランスコンダクタンス値になるように設定される。

【0049】

【発明の実施の形態】

図1は本発明に係るフィルタ回路の一実施形態を示す回路図である。

図示のように、本実施形態のフィルタ回路は、トランスコンダクタンスセル(以下、便利のためgm セルと称する)、キャパシタ、及びバイアス回路によって構成されている。なお、このフィルタ回路は、例えば、等化フィルタとして用いられる2次状態変数フィルタ、あるいはローパスフィルタである。

【0050】

図1は、gm セルによって構成されている2次状態変数フィルタの一実施形態を示している。図示のように、このフィルタ回路は、gm セル10(第2のトランスコンダクタンス),20(第1のトランスコンダクタンス),30(第4のトランスコンダクタンス),40(第3のトランスコンダクタンス)及びバイアス回路50(第1の同相電位制御回路),60(第2の同相電位制御回路)によって構成されている。

【0051】

gm セル10,20,30,40は、CMOSトランジスタによって構成されたトランスコンダクタンスセルであり、それぞれ予め設計されたgm 及びQを持つように形成されている。バイアス回路50と60は、それぞれgm セル10,20及び30,40に共通の同相フィードバック電圧を供給する同相フィードバック回路(CMFB)で構成されている。

キャパシタC1は、gm セル10と20によって駆動され、キャパシタC2は、gm セル30と40によって駆動される。

【0052】

図示のように、gm セル20とgm セル40は、直列接続されている。gm セル20の入力側に、入力信号Vi が印加される。gm セル20の出力端子にキャパシタC1が接続され、gm セル40の出力端子にキャパシタC2が接続されている。また、gm セル10は、gm セル20と並列に接続され、その入力端子にgm セル40の出力信号Vlpが印加されている。gm セル30は、gm セル40と並列に接続され、その入力側に、gm セル40の出力信号Vlpが印加される。即ち、図1に示すフィルタ回路において、キャパシタC1は、gm セル10と20の負荷容量であり、キャパシタC2は、gm セル30と40の負荷容量である。

【0053】

なお、図1に示す構成では、gm セルの負荷容量を形成するキャパシタC1とC2は、それぞれ差動容量として表現しているが、一般的に寄生容量分を考慮した場合、容量値の設定のし易さまたは同相帰還ループにおける位相補償容量の機能を併せ持たせるなどの理由から、例えば、負荷容量をCとすると、この負荷容量をそれぞれgm セルの正相、逆相出力端子と接地電位との間に接続されている2Cのキャパシタで構成することが望ましい。

【0054】

バイアス回路50は、gm セル20およびgm セル10の出力VO と外部から入力される同相電位設定端子電圧(制御電圧VC )に応じてバイアス電圧Vbs1を生成し、gm セル10と20にそれぞれ供給する。また、バイアス回路60は、gm セル40およびgm セル30の出力Vlpと外部から入力される制御電圧VC に応じてバイアス電圧Vbs2 を生成し、gm セル30と40にそれぞれ供給する。

なお、バイアス回路50と60は、gm セルから出力される差動出力信号の同相成分、即ち、差動出力信号の平均電圧と制御電圧VC とが一致するように、バイアス電圧Vbs1 バイアス電圧Vbs2 を生成する。

【0055】

上述した構成を有するフィルタ回路において、CMOS素子のgm がVeff =VGS−Vthに対してリニアに変化することを利用する、即ち、それぞれのgm セルのgm 値を決定するMOS素子の動作点におけるVGSを共通電位とし、フィルタを構成する各2次状態変数フィルタまたはローパスフィルタが図6に示す極周波数及びQ値を満たすように、そのgm 値を決定するMOS素子のK、具体的には、チャネル幅Wを各素子毎に予め設定し、レイアウトしておき、フィルタのカットオフ周波数調整は共通電位であるVGSを変化させることによって行われる。

【0056】

図1のフィルタ回路を構成するgm セルは、例えば、図2に示すMOSトランジスタからなる差動回路によって構成することができる。

図2に示すように、gm セルは、MOSトランジスタM1とM2及びこれらのトランジスタにそれぞれ動作電流を供給する電流源IS1とIS2によって構成されている。トランジスタM1とM2のゲートが、例えば、それぞれgm セルの正相入力端子と逆相入力端子に接続され、ソースがともに接地されている。トランジスタM1のドレインに電流源IS1が接続され、トランジスタM2のドレインに電流源IS2が接続されている。電流源IS1とIS2は、バイアス回路50または60から供給されるバイアス電圧Vbs(例えば、図1に示すVbs1 またはVbs2 )によって出力電流が制御される。図2に示すように、これらの電流源によって、トランジスタM1とM2にそれぞれ同相電流成分の変化分if が供給される。

【0057】

図示のgm セルにおいて、電流i1 ’及びi2 ’は、トランジスタM1とM2からなる差動対によって出力される差動電流である。このため、gm セルの出力差動電流iodは、次式によって与えられる。

【0058】

【数12】

【0059】

式(12)から分かるように、gm セルの出力差動電流iodは、同相入力電圧v1 −v2 に対してリニアに変化する。

【0060】

このように、図2に示すgm セルを用いて、2次状態変数フィルタ、またはローパスフィルタを構成し、さらに、これらのフィルタによって図1に示す本実施形態のフィルタ回路(等化フィルタ)を構成することがによって、等化フィルタのカットオフ周波数は各gm セルに共通に接続されているバイアス回路で供給されるバイアス電圧によって制御される。さらに、各gm セルのgm の比は不変に保たれることによって各2次状態変数フィルタ及びローパスフィルタのQ、及び群遅延特性などを保つため、各2次状態変数フィルタの極周波数の比が一定に保たれる。各gm セルのgm は外部から入力される制御電圧VC に対してリニアに変化するため、関数変換機構を必要としない。

さらに、図2に示すように、gm セルとしてソース接地MOSトランジスタからなる差動対を用いることで、入力振幅に対して原理的にリニアなgm を得ることが可能である。

【0061】

以下、上述したgm セルによって構成された本実施形態のフィルタ回路の動作について説明する。

容量負荷C1を駆動するgm セル10と20は、共通のバイアス回路50によって、バイアス電圧Vbs1 が供給される。これによって、これらのgm セルにおいてそれぞれの同相出力電位がバイアス電圧Vbs1 によって設定された所望の値になるようにフィードバック制御が行われる。

【0062】

また、同様に、容量負荷C2を駆動するgm セル30と40は、共通のバイアス回路60によって、バイアス電圧Vbs2 が供給される。これによって、これらのgm セルにおいてそれぞれの同相出力電位がバイアス電圧Vbs2 によって設定された所望の値になるようにフィードバック制御が行われる。

【0063】

さらに、図1に示すように、各gm セルの出力端子がそれぞれ他のgm セル、あるいは場合によって自分自身の入力端子に接続されているため、その結果、すべてのgm セルの入出力端子が共通の同相電位で動作し、この電位は、各gm セルの同相電位設定端子に与えられたバイアス電圧Vbs1 またはVbs2 で共通に設定される。

【0064】

ここで、MOS素子、例えば、MOSトランジスタから構成された差動対のトランスコンダクタンスgm,MOS は、前述した式(10)によって与えられる。この式によれば、MOS素子のgm は、電圧Veff 即ち、MOSトランジスタのゲート−ソース間電圧VGSとそのしきい値電圧Vthとの差VGS−Vthに対して、リニアに変化することが分かる。本実施形態では、この特徴を利用して、バイアス回路50と60によって共通設定されたバイアス電圧を用いてそれぞれのgm セルのMOSトランジスタのゲート−ソース間に印加することによって、ソース接地MOSトランジスタをgm セルの入力トランジスタとすることで同相電位、即ちMOSトランジスタのゲート−ソース間電圧VGSにに対してリニアなgm を獲得する。

【0065】

ここでは、図2に示すgm セルによって構成された図5の2次状態変数フィルタ103について説明する。なお、図5における他の構成要素、例えば、2次状態変数フィルタ/イコライザ101、2次状態変数フィルタ102及びローパスフィルタ104についても同様の説明が当てはまる。

【0066】

図6に示すように、2次状態変数フィルタ103では正規化極周波数が2.3174Hz、Q値が2.0229で、Q>1である。このため、gm3=gm2よりもgm3=gm1とした方がgm1を提供するgm セルのカットオフ周波数を小さくでき、消費電力の観点から一般的に有利である。ここで、gm3=gm1として説明する。

【0067】

このとき、ω0 =gm1/C、Q=gm1/gm2であるから、例えば、等化フィルタ全体のカットオフ周波数を100MHz、C=1pFとすると、gm1=1.4553mS、gm2=719.4μSとなる。式(10)により、gm1=2K1 Veff 、またgm2=2K2 Veff として、K1 /K2 =1.4553/0.7194となるように、MOS素子のサイズを設定すれば、各gm セル共通の制御電圧Veff を変化させることによって、各gm 値の比、即ちQ値を変えることなく、フィルタ回路のカットオフ周波数fC を調整することができる。

【0068】

なお、各等化フィルタの極周波数を常に図6に示す比を保つ必要があるため、結局すべてのgm セルのgm 値は常に互いに固定の比を保つ必要がある。このため、本実施形態のフィルタ回路において、各gm セルのgm 値をきめるMOS素子のK、実際にはMOSトランジスタのチャネル幅Wを上記固定の比に設定する。このようにすることで、等化フィルタ全体のカットオフ周波数の制御はgm セルの共通の動作点電圧VGSまたは同相電位を変化させるだけで済み、取り立てて関数変換をする必要はない。

【0069】

また、gm 値を決める各MOS素子のKを予め決めるに当たり、チャネル長Lをパラメータにすることも可能であるが、一般的に大きなgm 値を獲得するために短チャネルになる傾向で、この場合短チャネル効果などによりチャネル長Lとgm 値が比例関係からずれる傾向がある。このため、各MOS素子のKはチャネル幅Wで決めることがもっとも望ましい。ただし、本発明では、これに限定されるものではなく、MOS素子のチャネル長Lまたはチャネル幅Wの何れかによってgm セルのKを決めることができ、それによってgm 値を決めることができる。

【0070】

図3は、本実施形態のフィルタ回路の利得特性を示すグラフであり、vc 端子電圧を変化させるときのフィルタの利得特性の変化を示す図である。

【0071】

また、図4は、本実施形態のフィルタ回路の群遅延特性を示すグラフであり、vc 端子電圧を変化させるときのフィルタの群遅延特性の変化を示す図である。

【0072】

【発明の効果】

以上説明したように、本発明のフィルタ回路によれば、フィルタを構成する各トランスコンダクタは共通の制御電圧によってそれぞれのトランスコンダクタンス(gm )が制御される。このため、フィルタ回路のカットオフ周波数の調整は容易に実現でき、ルックアップテーブルによる関数変換機構あるいは関数変換回路などは一切不要である。これにより回路規模の縮小、及びそれによる消費電力の低減と付加的外乱の排除を両立できる。

また、本発明において、トランスコンダクタからなる各2次状態変数フィルタのQ値を不変に保ちつつ、さらにフィルタの群遅延特性を達成するために重要となる各Gm−C積分器間のgm 値の比は、経年変化などの影響を受けないMOS素子の形状パラメータ、即ちチャネル幅Wとチャネル長Lの比で決定されるので、安定なカットオフ周波数の調整を実現できる。

さらに、本発明のトランスコンダクタによれば、出力同相電位は外部で設定された同相電位制御電圧と同電位となり、出力同相電位が次段のあるいはこの出力端子と接続された他のトランスコンダクタの入力同相電位となり、その結果フィルタ全体を構成するすべてのトランスコンダクタが同一の同相電位で動作する。これによって、フィルタ回路全体の動作点の設計を容易にでき、入出力におけるダイナミックレンジの拡大、さらに低消費電力化を実現できる利点がある。

【図面の簡単な説明】

【図1】本発明に係るフィルタ回路の一実施形態を示す回路図である。

【図2】本発明のフィルタ回路を構成するコンダクタンスセルの構成を示す回路図である。

【図3】本発明のフィルタ回路の利得特性を示すグラフである。

【図4】本発明のフィルタ回路の群遅延特性を示すグラフである。

【図5】等化フィルタの一構成例を示すブロック図である。

【図6】フィルタの構成要素の極周波数及びQ値を示す図である。

【図7】等化フィルタを構成する2次状態変数フィルタの構成を示す回路図である。

【図8】等化フィルタを構成する2次状態変数フィルタ/イコライザの構成を示す回路図である。

【図9】等化フィルタを構成するローパスフィルタの構成を示す回路図である。

【図10】従来のトランスコンダクタンスセルの一構成例を示す回路図である。

【符号の説明】

10,20,30,40…コンダクタンスセル(gm セル)、50,60…バイアス回路、101…2次状態変数フィルタ/イコライザ、102、103…2次状態変数フィルタ、104…ローパスフィルタ、VCC…電源電圧、GND…接地電位。

Claims (8)

- 入力端子に入力信号が印加される第1のトランスコンダクタンスと、入力端子に出力信号が印加される第2のトランスコンダクタンスと、

上記第1および第2のトランスコンダクタンスの出力側に接続され、当該トランスコンダクタンスによって駆動される負荷容量素子とを含むトランスコンダクタ−C(Gm−C)回路と、

上記第1および第2のトランスコンダクタの出力信号と制御電圧に応じて、当該第1および第2のトランスコンダクタの差動出力信号の平均電圧と上記制御電圧とが一致するようにバイアス電圧を生成して上記第1および第2のトランスコンダクタに供給する同相電位制御回路と、を有し、

上記第1および第2のトランスコンダクタの各々は、

上記バイアス電圧によって出力電流が制御される第1および第2の電流源と、

ゲートが正相入力端子に接続され、ソースが接地され、ドレインに上記第1の動作電流を供給する第1の電流源が接続されている第1のMOSトランジスタと、

ゲートが逆相入力端子に接続され、ソースが接地され、ドレインに第2の動作電流を供給する上記第2の電流源が接続されている第2のMOSトランジスタと、を含む、

フィルタ回路。 - 上記同相電位制御回路は、上記第1と第2のMOSトランジスタからなる差動回路から出力される差動出力信号と上記制御電圧とに応じて、上記制御信号を生成する

請求項1記載のフィルタ回路。 - 上記第1と第2のトランジスタのゲートに入力される同相電位が、所望のトランスコンダクタンス値になるように制御される

請求項1記載のフィルタ回路。 - 上記第1と第2のトランジスタのチャネル幅とチャネル長との比を、所望のトランスコンダクタンス値になるように設定される

請求項1記載のフィルタ回路。 - 入力端子に入力信号が印加される第1のトランスコンダクタンスと、入力端子に出力信号が印加され、出力端子が上記第1のトランスコンダクタンスの出力端子に接続された第2のトランスコンダクタンスと、入力端子が上記第1および第2のトランスコンダクタンスの出力端子に接続された第3のトランスコンダクタンスと、入力端子に出力信号が印加され、出力端子が上記第3のトランスコンダクタンスの出力端子に接続された第4のトランスコンダクタンスと、

上記第1および第2のトランスコンダクタンスの出力側に接続され、当該トランスコンダクタンスによって駆動される第1の負荷容量素子と、上記第3および第4のトランスコンダクタンスの出力側に接続され、当該トランスコンダクタンスによって駆動される第2の負荷容量素子とを含むトランスコンダクタ−C(Gm−C)回路と、

上記第1および第2のトランスコンダクタの出力信号と制御電圧に応じて、当該第1および第2のトランスコンダクタの差動出力信号の平均電圧と上記制御電圧とが一致するようにバイアス電圧を生成して上記第1および第2のトランスコンダクタに供給する第1の同相電位制御回路と、を有し、

上記第3および第4のトランスコンダクタの出力信号と制御電圧に応じて、当該第3および第4のトランスコンダクタの差動出力信号の平均電圧と上記制御電圧とが一致するようにバイアス電圧を生成して上記第3および第4のトランスコンダクタに供給する第2の同相電位制御回路と、を有し、

上記第1、第2、第3、および第4のトランスコンダクタの各々は、

上記バイアス電圧によって出力電流が制御される第1および第2の電流源と、

ゲートが正相入力端子に接続され、ソースが接地され、ドレインに上記第1の動作電流を供給する第1の電流源が接続されている第1のMOSトランジスタと、

ゲートが逆相入力端子に接続され、ソースが接地され、ドレインに第2の動作電流を供給する上記第2の電流源が接続されている第2のMOSトランジスタと、を含む、

フィルタ回路。 - 上記第1および第2の同相電位制御回路は、上記第1と第2のMOSトランジスタからなる差動回路から出力される差動出力信号と上記制御電圧とに応じて、上記制御信号を生成する

請求項5記載のフィルタ回路。 - 上記第1と第2のトランジスタのゲートに入力される同相電位、並びに上記第3と第4のトランジスタのゲートに入力される同相電位が、所望のトランスコンダクタンス値になるように制御される

請求項5記載のフィルタ回路。 - 上記第1と第2のトランジスタのチャネル幅とチャネル長との比、並びに上記第3と第4のトランジスタのチャネル幅とチャネル長との比を、所望のトランスコンダクタンス値になるように設定される

請求項5記載のフィルタ回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001072572A JP3584893B2 (ja) | 2001-03-14 | 2001-03-14 | フィルタ回路 |

| US10/092,541 US6677822B2 (en) | 2001-03-14 | 2002-03-08 | Transconductor and filter circuit using the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001072572A JP3584893B2 (ja) | 2001-03-14 | 2001-03-14 | フィルタ回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002280877A JP2002280877A (ja) | 2002-09-27 |

| JP3584893B2 true JP3584893B2 (ja) | 2004-11-04 |

Family

ID=18930138

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001072572A Expired - Fee Related JP3584893B2 (ja) | 2001-03-14 | 2001-03-14 | フィルタ回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6677822B2 (ja) |

| JP (1) | JP3584893B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9768993B2 (en) | 2015-12-11 | 2017-09-19 | Anritsu Corporation | Multiband equalizer, error rate measurement system using the same, error rate measurement device, and path selection method |

Families Citing this family (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7158772B1 (en) * | 2002-01-18 | 2007-01-02 | Lsi Logic Corporation | Filter for broadcast receiver tuner |

| US7266351B2 (en) * | 2002-09-13 | 2007-09-04 | Broadcom Corporation | Transconductance / C complex band-pass filter |

| US20040198287A1 (en) * | 2002-10-08 | 2004-10-07 | Kramer Bradley A. | Simultaneous Gm-C filter and variable gain amplifier circuit |

| JP4170786B2 (ja) * | 2003-02-04 | 2008-10-22 | 松下電器産業株式会社 | データ通信装置及びデータ通信方法 |

| JP2004328487A (ja) * | 2003-04-25 | 2004-11-18 | Renesas Technology Corp | 演算増幅器 |

| JP3917571B2 (ja) * | 2003-09-05 | 2007-05-23 | 株式会社東芝 | 差動回路とそれを用いたトランスコンダクタ |

| US7139544B2 (en) * | 2003-09-22 | 2006-11-21 | Intel Corporation | Direct down-conversion receiver with transconductance-capacitor filter and method |

| US7098718B2 (en) * | 2003-12-11 | 2006-08-29 | The Trustees Of Boston University | Tunable current-mode integrator for low-frequency filters |

| US7145395B2 (en) * | 2004-09-16 | 2006-12-05 | Qualcomm Incorporated | Linear transconductance cell with wide tuning range |

| JP2006121480A (ja) * | 2004-10-22 | 2006-05-11 | Sony Corp | サンプルホールド回路及びそれを用いたパイプラインad変換器 |

| US7498858B2 (en) * | 2004-11-01 | 2009-03-03 | Hewlett-Packard Development Company, L.P. | Interpolator systems with linearity adjustments and related methods |

| US7113016B2 (en) * | 2004-12-11 | 2006-09-26 | Muchip Co., Ltd | Device for DC offset cancellation |

| US7920017B2 (en) * | 2004-12-16 | 2011-04-05 | Analog Devices, Inc. | Programmable clock booster system |

| US7692489B2 (en) * | 2004-12-16 | 2010-04-06 | Analog Devices, Inc. | Differential two-stage miller compensated amplifier system with capacitive level shifting |

| KR100672987B1 (ko) * | 2004-12-20 | 2007-01-24 | 삼성전자주식회사 | 고속 아날로그 인벨롭 디텍터 |

| JP4804033B2 (ja) * | 2005-05-11 | 2011-10-26 | ローム株式会社 | 高周波イコライザ |

| US7271651B2 (en) * | 2005-06-17 | 2007-09-18 | Agere Systems Inc. | High performance differential amplifiers with thick oxide devices for high impedance nodes |

| US7253686B2 (en) * | 2005-07-27 | 2007-08-07 | Analog Devices, Inc. | Differential amplifiers with enhanced gain and dynamic range |

| JP4871590B2 (ja) * | 2005-12-28 | 2012-02-08 | パナソニック株式会社 | トランスコンダクタを用いた積分器及びフィルタ回路 |

| US7573326B2 (en) * | 2005-12-30 | 2009-08-11 | Intel Corporation | Forwarded clock filtering |

| US7417495B2 (en) * | 2006-06-14 | 2008-08-26 | Broadcom Corporation | Reconfigurable frequency filter |

| US7504879B2 (en) * | 2006-08-24 | 2009-03-17 | Itt Manufacturing Enterprises, Inc. | Transconductor and filter circuit |

| US7471148B2 (en) * | 2007-05-21 | 2008-12-30 | Sekio Epson Corporation | Differential low noise amplifier (LNA) with common mode feedback and gain control |

| KR100851528B1 (ko) | 2007-07-25 | 2008-08-11 | 전자부품연구원 | 무선통신 시스템에서의 차동 트랜스컨덕턴스 회로와 그를이용한 채널선택필터 |

| JP4977102B2 (ja) * | 2008-09-02 | 2012-07-18 | 株式会社東芝 | 差動増幅器 |

| US9867574B2 (en) * | 2016-02-22 | 2018-01-16 | National University Of Singapore | Multi-channel neural signal amplifier system providing high CMRR across an extended frequency range |

| KR101982209B1 (ko) * | 2018-06-14 | 2019-05-24 | 고려대학교 산학협력단 | 연속 시간 델타-시그마 변조기 |

| CN111064448A (zh) * | 2020-01-09 | 2020-04-24 | 宁波爱芯微电子有限公司 | 一种跨导电容滤波器 |

| KR102757342B1 (ko) | 2020-10-29 | 2025-01-20 | 삼성전자주식회사 | 아날로그 프론트 앤드 수신기 및 상기 수신기를 포함한 전자 장치 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IT1236787B (it) * | 1989-11-13 | 1993-04-02 | Italtel Spa | Circuito amplificatore di potenza cmos con struttura completamente differenziale. |

| US5489872A (en) * | 1994-01-25 | 1996-02-06 | Texas Instruments Incorporated | Transconductance-capacitor filter circuit with current sensor circuit |

| JPH0832406A (ja) * | 1994-05-12 | 1996-02-02 | Hitachi Ltd | 電圧制御フィルタ回路及び信号処理用半導体集積回路装置並びにそれを用いた信号読み取りシステム |

| JPH10126214A (ja) * | 1996-10-23 | 1998-05-15 | Toshiba Corp | フィルタ回路 |

| JP3442613B2 (ja) * | 1997-03-31 | 2003-09-02 | 株式会社東芝 | 可変利得増幅器 |

| JP3727777B2 (ja) * | 1997-04-28 | 2005-12-14 | 株式会社東芝 | 平衡型増幅器 |

| JPH10322143A (ja) * | 1997-05-21 | 1998-12-04 | Toshiba Corp | Ac結合回路 |

| JP4086371B2 (ja) * | 1998-08-18 | 2008-05-14 | 富士通株式会社 | 半導体増幅回路 |

| US6346856B1 (en) * | 2000-05-16 | 2002-02-12 | Intersil Americas Inc. | Ultra linear high frequency transconductor structure |

| US6420932B1 (en) * | 2001-06-29 | 2002-07-16 | Intel Corporation | Variable offset amplifier circuit |

-

2001

- 2001-03-14 JP JP2001072572A patent/JP3584893B2/ja not_active Expired - Fee Related

-

2002

- 2002-03-08 US US10/092,541 patent/US6677822B2/en not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9768993B2 (en) | 2015-12-11 | 2017-09-19 | Anritsu Corporation | Multiband equalizer, error rate measurement system using the same, error rate measurement device, and path selection method |

Also Published As

| Publication number | Publication date |

|---|---|

| US20020163384A1 (en) | 2002-11-07 |

| JP2002280877A (ja) | 2002-09-27 |

| US6677822B2 (en) | 2004-01-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3584893B2 (ja) | フィルタ回路 | |

| US5572163A (en) | Active filter control apparatus | |

| Mehr et al. | A CMOS continuous-time G/sub m/-C filter for PRML read channel applications at 150 Mb/s and beyond | |

| Silva-Martínez et al. | A 60-mW 200-MHz continuous-time seventh-order linear phase filter with on-chip automatic tuning system | |

| US5559470A (en) | Circuit technique that sets transconductance | |

| US5508570A (en) | Differential amplifier based integrator having a left-half plane pole | |

| US5283483A (en) | Slimmer circuit technique | |

| US20050248396A1 (en) | Novel VGA-CTF combination cell for 10 GB/S serial data receivers | |

| Dehaene et al. | A 50-MHz standard CMOS pulse equalizer for hard disk read channels | |

| Rezzi et al. | A 70-mW seventh-order filter with 7-50 MHz cutoff frequency and programmable boost and group delay equalization | |

| JP2001077666A (ja) | 連続時間リードチャネル・フィルタにおいて振幅及び群遅延を整形する回路 | |

| US20100091623A1 (en) | Frequency characteristic adjusting circuit, receiving interface circuit, and magnetic storage device | |

| JPH08274583A (ja) | ブースト型等化回路 | |

| JP4075369B2 (ja) | アナログフィルタ回路およびこれを用いたディスク装置 | |

| KR19980082771A (ko) | 트랜스컨덕턴스 가변방법 및 회로와 그를 이용한 가변 대역 필터 및 가변 이득 증폭기 | |

| JP4515720B2 (ja) | オフセット制御回路及び信号処理装置 | |

| JP4572481B2 (ja) | トランスコンダクタ回路 | |

| Gambhir et al. | A low power 1.3 GHz dual-path current mode Gm-C filter | |

| JP7567909B2 (ja) | 増幅回路、差動増幅回路、受信回路及び半導体集積回路 | |

| JPH0661791A (ja) | フィルタ回路およびその制御方法 | |

| JP2008533794A (ja) | 利得制御可能な入力増幅器を有するレシーバ | |

| JP3111838B2 (ja) | 波形等化装置 | |

| WO2000054259A1 (fr) | Dispositif electronique | |

| Pandey | A CMOS 500MHz continuous-time fourth order 0.05 degree equiripple linear phase filter with automatic tuning | |

| JPH10126214A (ja) | フィルタ回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040210 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040412 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040713 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040726 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080813 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090813 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100813 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |