JP2005031629A - 表示素子および表示装置 - Google Patents

表示素子および表示装置 Download PDFInfo

- Publication number

- JP2005031629A JP2005031629A JP2004059620A JP2004059620A JP2005031629A JP 2005031629 A JP2005031629 A JP 2005031629A JP 2004059620 A JP2004059620 A JP 2004059620A JP 2004059620 A JP2004059620 A JP 2004059620A JP 2005031629 A JP2005031629 A JP 2005031629A

- Authority

- JP

- Japan

- Prior art keywords

- current control

- display

- voltage

- electro

- organic

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 claims abstract description 19

- 238000005401 electroluminescence Methods 0.000 claims description 114

- 239000010409 thin film Substances 0.000 claims description 23

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 7

- 238000000034 method Methods 0.000 description 42

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 24

- 229910052710 silicon Inorganic materials 0.000 description 24

- 239000010703 silicon Substances 0.000 description 24

- 239000010408 film Substances 0.000 description 19

- 238000003780 insertion Methods 0.000 description 17

- 230000037431 insertion Effects 0.000 description 17

- 230000007423 decrease Effects 0.000 description 15

- 238000010586 diagram Methods 0.000 description 15

- 230000006866 deterioration Effects 0.000 description 14

- 239000010410 layer Substances 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 230000036961 partial effect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 239000011521 glass Substances 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 230000036962 time dependent Effects 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000011368 organic material Substances 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

- H10K59/1315—Interconnections, e.g. wiring lines or terminals comprising structures specially adapted for lowering the resistance

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

【課題】抵抗素子を挿入したり、レイアウト変更により開口率を低下させることなく、電気光学素子の表示寿命を延ばす表示素子および表示装置を提供する。

【解決手段】本表示素子は、電気光学素子である有機EL素子20と、電源線電極12と、走査信号線電極10と、データ信号線電極11と、共通電極Vcomと、補助容量30と、有機EL素子20に流す電流を制御する電流制御用TFT2と、有機EL素子20に電流を流すタイミングを制御するデータ電圧制御用TFT1とを備える。ここで、上記電流制御用TFT2の両端への印加電圧値Vrと有機EL素子20の両端への印加電圧値Velとの比率をβ(=Vr/Vel)とするとき、0.1≦β≦7.0となる電圧Vrを電流制御用TFT2の両端に印加してその導電率を制御する。このことにより、有機EL素子20の輝度の経時変化速度を遅くし、表示寿命をより長くする。

【選択図】図4

【解決手段】本表示素子は、電気光学素子である有機EL素子20と、電源線電極12と、走査信号線電極10と、データ信号線電極11と、共通電極Vcomと、補助容量30と、有機EL素子20に流す電流を制御する電流制御用TFT2と、有機EL素子20に電流を流すタイミングを制御するデータ電圧制御用TFT1とを備える。ここで、上記電流制御用TFT2の両端への印加電圧値Vrと有機EL素子20の両端への印加電圧値Velとの比率をβ(=Vr/Vel)とするとき、0.1≦β≦7.0となる電圧Vrを電流制御用TFT2の両端に印加してその導電率を制御する。このことにより、有機EL素子20の輝度の経時変化速度を遅くし、表示寿命をより長くする。

【選択図】図4

Description

本発明は、電気光学素子に流される電流量によって発光が制御される表示素子および当該該表示素子を含む表示装置に関する。

従来より、素子に流される電流量に応じてその発光量が制御される素子、例えば、無機EL(Electro Luminescence)素子や有機EL素子等に代表されるLED(Light Emitting Diode)を電気光学素子として利用した表示素子がある。ここで、本明細書において、電気光学素子とは、上記有機EL素子等の他、FED(Field Emission Display)、電荷駆動素子、液晶、Eインク(Electronic Ink)など、電気を与えることにより光学的な特性が変化する全ての素子をいうものとする。なお、以下では電気光学素子として有機EL素子を例示するが、電流量に応じて発光量が制御される発光素子であれば同様の説明が可能である。

また、上記表示素子により画素が形成されるように、複数の表示素子がマトリクス状に配置される表示装置がある。この表示素子は、電気光学素子に流す電流量を制御するスイッチング素子を含み、このスイッチング素子により、外部からの電気信号に基づき電気光学素子の電流量が制御される。このスイッチング素子は、例えばダイオードやMIM(Metal Insulator Metal )素子があるが、より好適にはスイッチ特性の優れたアモルファスシリコンや多結晶シリコン(Polycrystalline Silicon )、さらにはより結晶性の高い多結晶シリコンである連続粒界結晶シリコン(Continuous Grain Silicon:以下「CGシリコン」と略する)、またはシリコン膜とは別の導電性の有機材料膜を利用した薄膜トランジスタ(Thin Film Transistor:以下「TFT」と略する)である。このような電気光学素子の電流量を制御する電気信号の形態によって、その制御方法は、以下に示されるような定電圧型制御方式および定電流型制御方式と呼ばれる2つの方法に大別される。

まず、定電圧型制御方式につき説明する。図12は、1つの画素を形成する表示素子の等価回路を示す図である。この表示素子は、電気光学素子である有機EL素子920と、駆動電源Vrefからの電流を供給する電源線電極912と、走査信号線電極910と、データ信号線電極911と、共通電極Vcomと、補助容量930と、有機EL素子920に流す電流を制御するためのpチャネル型TFTである電流制御用TFT92と、有機EL素子920に電流を流すタイミングを制御するnチャネル型TFTであるデータ電圧制御用TFT91とを備える。図に示すように、電源線電極912には、電流制御用TFT92のソース端子と補助容量930の一端とが接続され、補助容量930の他端には電流制御用TFT92のゲート端子およびデータ電圧制御用TFT91のドレイン端子に接続される。また、データ電圧制御用TFT91のソース端子はデータ信号線電極911に接続され、そのゲート端子は走査信号線電極910に接続される。さらに、有機EL素子920の陽極は、電流制御用TFT92のドレイン端子に接続され、その陰極は共通電極Vcomに接続される。定電圧型制御方式では、走査信号線電極910に与えられる走査信号によりデータ電圧制御用TFT91が選択されている期間に、データ信号線電極911に対してデータ信号電圧が印加されることにより、補助容量930に該データ信号電圧に応じた電圧が保持される。その後、データ電圧制御用TFT91が選択されていない期間に、補助容量930で保持されている電圧に応じて電流制御用TFT92の導電率が制御されるため、この電流制御用TFT92に対して直列に接続される有機EL素子920に所定の電流が流され、その発光量が制御される。(例えば、非特許文献1参照。)

また、この発光量を制御し、表示装置の画質を良く見せるためには、従来より、上記データ信号がデジタル信号であることにより上記補助容量に保持される電位が離散的に変化することが好ましく、その際、上記電流制御用TFTのオン抵抗は、発光素子のオン抵抗に比べて、無視できるほど小さいほうが好ましいことが知られている。(例えば、特許文献1参照。)

このような定電圧型制御方式に対して、定電流型制御方式では、図12に示す表示素子のデータ信号線電極に流れるデータ信号電流により、有機EL素子920に流すべき電流が得られるような電圧が補助容量930に保持される。この補助容量930に保持された電圧に応じて、有機EL素子920の発光量が制御される。さらに、具体的に表示素子へ流すべき該電流を流すための構成について説明する。図13は、従来例における定電流型制御方式による表示素子の等価回路を示す図である。図13に示されるように、データ信号線電極911には定電流回路が接続されており、表示素子内にはさらにTFT93,94と、TFT94を制御するための信号線電極940とが配置される。なお、TFT93は、TFT91と同様に、走査信号線電極910により制御される。まず、TFT91,93がオンされるとともに、TFT94がオフされると、TFT92のソース・ドレイン間を流れる電流が所望の値になるまで、駆動電源Vrefからデータ信号線電極911に接続される定電流回路へTFT93を介して電流が流される。そのとき、TFT92のソース・ドレイン間を流れる電流が得られるような電圧が補助容量930に保持されるので、TFT91とTFT93のスイッチをオフした後、TFT94のスイッチをオンすることにより、有機EL素子920には所望の電流が流れる。(例えば、非特許文献2参照。)

ここで、有機EL素子920に流れる電流とその発光量との関係につき説明する。図14は、有機EL素子の発光輝度と発光時に流れる電流との関係を示す図である。図14に示されるように、有機EL素子の発光輝度は、有機EL素子に流れる電流、すなわち図12に示す電流制御用TFT92の駆動電流にほぼ比例する。このことは一般的に良く知られている。

そして、定電圧型制御方式では、時間の経過に伴って有機EL素子の内部抵抗が(水分や酸素との反応、材料の分解、膜層形状変化等の素子劣化が主な原因で)増加すると、電源負荷が相対的に増加することから、当該有機EL素子に流れる電流は相対的に減少する。そして、図14に示されるように発光輝度と発光時に流れる電流とは比例関係にあることから、当該有機EL素子の発光輝度も相対的に低下する。

これに対して、定電流型制御方式では、時間の経過(による内部抵抗の増加)とは無関係に、有機EL素子に一定の電流が流れるようデータ信号の電流値が制御される。そのため、流れる電流の減少による上記のような発光輝度の低下は生じない。しかし、一般的に有機EL素子は、時間経過とともに同一電流値に対する発光輝度が(素子の劣化により)低下する特性を有しているため、定電流型制御方式においても、時間の経過による発光輝度の低下は生じる。

図15は、定電圧型制御方式および定電流型制御方式による、上記有機EL素子の時間経過による発光輝度の低下を示す図である。なお、曲線Aは定電圧型制御方式の場合を示し、曲線Bは定電流型制御方式の場合を示している。また、図15に示す規格化時間は、定電圧型制御方式での規格化輝度が半減した(すなわち0.5となる)ときの時間を1としている。図15に示されるように、定電流型制御方式の方が定電圧型制御方式よりも表示装置の表示寿命を延ばすことができる。なお、この表示寿命とは、所定の輝度で発光する素子が、経時的な劣化により表示装置として使用できなくなる輝度に至る時間、すなわち上記所定の輝度がほぼ半減するまでの時間を意味する。

ところで、上述のような経時的な劣化による発光輝度の低下は、表示パネルに含まれるTFT素子の特性ばらつきを原因とする各有機EL素子毎の発光履歴の違いに基づきばらつきが生じる。そこで、有機EL素子に対して直列に抵抗素子を接続し、有機EL素子に加わる電圧を分圧することにより調節し、相対的に発光のばらつきを低減させる手法が知られている。(例えば、特許文献2、3参照。)

この構成では例えば、図12に示す表示素子の有機EL素子920に対し、電流制御用TFT92に加えてさらに所定の抵抗素子Rを直列に接続する。図16は、この従来例に係る表示素子の等価回路を示す図である。図16に示すように有機EL素子920の内部抵抗が増加することにより流れる電流が所定値から経時的に低下する場合であっても、電圧の分配法則に従い、当該有機EL素子920に加わる電圧を当該有機EL素子920の内部抵抗に応じて増加させることができる。そのため、電流値の経時的な低下による輝度の低下を抑制することができる。したがって、定電圧型制御方式による場合であっても、前述の定電流型制御方式による場合と同様に発光輝度の低下を抑制した表示装置を実現することができる。

特開平11−73158号公報

特開2001−272930号公報(第3−4頁、第1図)

特開2002−175029号公報(第6−8頁、第2、5−7図)

I.M.ハンター(I.M.Hunter)、他1名,「低温ポリシリコンTFTを用いたポリマー発光ダイオードのアクティブマトリクスアドレッシング(Active Matrix Addressing of Polymer Light Emitting Diodes Using Low Temperature Poly Silicon TFTs)」,AM−LCD2000,2000年,p.249−252

服部励治、他3名,「電流指定型ポリシリコンTFTアクティブマトリクス駆動有機LEDディスプレイの回路シミュレーション」,信学技報,2001年4月,ED2001−8 SDM2001−8 Vol.101,No.15,p.7−14

しかしながら、上記従来の構成のように、定電圧型制御方式においてデジタルデータ信号に基づき制御を行う構成(例えば特許文献1を参照)では、電流制御用TFT素子の抵抗は無視できるほど小さい方が好ましいとされるので、この構成で表示寿命を延ばすためには、表示素子内の有機EL素子に対して直列に抵抗素子を接続することにより、電圧の分配方式に従って有機EL素子に加わる電圧を該有機EL素子の内部抵抗に応じて増加させる前述の構成を必要とする。あるいは表示寿命を延ばす方法として、電圧の分配法則に関係なく常に一定の電流を有機EL素子に流すことができる定電流型制御方式による表示素子の構成が考えられる。しかし上記のような構成では、図12に示す表示素子に比べて、表示素子に含まれるスイッチ素子や抵抗が増える。そのため、これらによって占められる面積が大きくなるので、これらの面積が表示素子全体の面積に対して占める割合が大きくなる。その結果、発光素子の発光面積が減少することになるので、表示素子の開口率が低下する。

ここで、図12に示す回路構成の表示素子の表示輝度と同じ表示輝度を上記のような開口率が低下する構成において実現するためには、表示素子に含まれる有機EL素子の輝度を上げる必要がある。しかし、有機EL素子の輝度をより上昇させて駆動すると、当該有機EL素子の劣化を早めてしまうことが良く知られており、表示寿命がより短くなる。さらに、当該有機EL素子の発光効率は低下し、その消費電力も相対的に増加するため、表示特性の点からも有機EL素子の輝度をより上昇させて駆動することは好ましくない。

なお、ここでは電気光学素子としての有機EL素子を例示して説明しているが、有機EL素子に限らず、素子に流れる電流量に応じてその発光量が制御される発光素子には同様の問題点がある。

そこで本発明は、前述のように抵抗素子を直列に挿入したり、表示素子内部のTFT数を増加させて、表示素子のレイアウトを大幅に変更することにより開口率を低下させることなく、電気光学素子の経時的な輝度劣化を補償して表示寿命を延ばすことができる表示素子および表示装置を提供することを目的とする。

本発明は、電流により駆動される電気光学素子と、当該電気光学素子に対して直列に接続されることにより当該電気光学素子に流れるべき電流を与える電流制御用素子と、当該電流制御用素子を制御するためのデータ信号を当該電流制御用素子に与えるスイッチング素子と、当該スイッチング素子を制御するための走査信号を前記スイッチング素子に与える走査信号線電極と、前記データ信号を前記スイッチング素子に与えるデータ信号線電極と、前記電気光学素子を駆動するための電流を前記電流制御用素子に与える電源線電極とを備える表示素子であって、

前記電流制御用素子は、前記電気光学素子の発光時に、前記電気光学素子の両端に加わる電圧値Velに対する当該電流制御用素子の両端に加わる電圧値Vrの比率をβ(=Vr/Vel)とするとき、0.1≦β≦7.0を満たす、所定の導通抵抗値を有することを特徴とする。

前記電流制御用素子は、前記電気光学素子の発光時に、前記電気光学素子の両端に加わる電圧値Velに対する当該電流制御用素子の両端に加わる電圧値Vrの比率をβ(=Vr/Vel)とするとき、0.1≦β≦7.0を満たす、所定の導通抵抗値を有することを特徴とする。

また、本発明では、電流制御用素子の両端に加わる電圧に対する耐圧値が小さな値(例えば最大で8Vの値)をとるとき、前記比率β(=Vr/Vel)が、0.1≦β≦3.0となることが好ましい。

また、電流制御用素子は、ガラス基板上に形成可能である薄膜トランジスタであることが好適であり、さらに多結晶シリコンからなる薄膜トランジスタであることがより好適であり、pチャネル型またはnチャネル型の薄膜トランジスタであってもよい。さらにまた、電流制御用素子は、多結晶シリコンよりも電流を多く流すことができるCGシリコンであってもよい。また、電気光学素子は、有機エレクトロルミネッセンス素子であることが好適である。

ここで、本発明では、前記電流制御用素子が所定の導通抵抗値を有するように形成されてもよい。具体的には、電流制御用素子(例えば薄膜トランジスタ)は、当該電流制御用素子のゲート幅またはゲート長を所定の長さに形成されることにより、所定の導通抵抗値を有するように調整されてもよい。また、電流制御用素子は、所定の電圧値を有するデータ信号が与えられることにより、0.1≦β≦7.0を満たす所定の導電率を有するように制御されてもよい。

本発明の表示装置は、以上のような表示素子をマトリクス状に複数配列してなる表示部を備えており、当該電流制御用素子が、例えば薄膜トランジスタのように素子特性がばらつくことを考慮すると、アナログ的な制御方式では階調のばらつきが一般に大きくなるため、当該表示素子に含まれる電気光学素子は、発光または非発光のいずれかの発光状態となるように、例えばサブフィールド法(中間調を持つ動画像をそれぞれ重み付けられた複数の2値の画像に分け、時間的にそれらを重ね合わせることで中間調を表示する方式)や発光面積の異なる電気光学素子を2値のデジタルデータ信号で階調制御する方式(たとえば特許文献1を参照)のように、2値で階調制御されるのが好ましい。

このような本発明によれば、電気光学素子の発光時に、その両端に加わる電圧値Velに対する電流制御用素子の両端に加わる電圧値Vrの比率β(=Vr/Vel)が、0.1≦β≦7.0となるように電流制御用素子の導通抵抗値が設定される。そのため、新たに抵抗素子を挿入したり、定電流制御方式で表示素子や表示装置で用いた特別な補償回路等を組み込むことなく、電気光学素子の輝度の経時変化速度を遅くすることができるため、電気光学素子の表示寿命をより長くすることができる。

以下、本発明の一実施形態につき添付図面を参照して説明する。

<1.原理>

本発明の一実施形態の構成を説明する前提として、本発明において適用されるべき原理と得られる効果につき説明する。

本発明の一実施形態の構成を説明する前提として、本発明において適用されるべき原理と得られる効果につき説明する。

一般的に、時間経過等による素子特性の劣化は、指数(exponent)関数的な変化を示すことが知られている。よって、以下の説明において、電気光学素子単体の規格化された輝度の経時変化は、指数関数L(t)により近似するものとする。この指数関数L(t)は、指数係数をK、経過時間をtとするとき、次式(1)のように表される。

L(t)=exp(−K・t) …(1)

L(t)=exp(−K・t) …(1)

図1は、単体で発光させるときの電気光学素子を示す回路図である。図示される電気光学素子に対して電源から与えられる電圧をV、電気光学素子が所定の輝度となるときの抵抗値をRel(0)、そのときの電流値をI(0)としたとき、T時間後における電流値はI(T)、電気光学素子の抵抗値はRel(T)と表すことができる。ここでオームの法則より、上記電流、電圧、および抵抗の関係は次式(2)のように表される。

V=I(0)・Rel(0)

=I(T)・Rel(T) …(2)

V=I(0)・Rel(0)

=I(T)・Rel(T) …(2)

この電気光学素子の抵抗値Rel(T)は、発光履歴のない初期状態の時点近傍(以下「発光初期」という)における電気光学素子の抵抗値Rel(0)のα倍であるものとして、次式(3)のように表される。

Rel(T)=α・Rel(0) …(3)

Rel(T)=α・Rel(0) …(3)

また、電気光学素子の輝度と電流密度とは、ほぼ比例関係にあることから、上式(1)の指数関数L(t)をL1(t)、指数係数をK1とおくと、L1(t)を規格化された電流値I(t)/I(0)の式として、次式(4)のように表すことができる。

L1(t)=I(t)/I(0)

=exp(−K1・t) …(4)

L1(t)=I(t)/I(0)

=exp(−K1・t) …(4)

ところで、上式(3)により示されたαの値は、オームの法則と上式(4)により、以下のように規格化された輝度の逆数としても表すことができる。

α=Rel(T)/Rel(0)

=(V/I(T))/(V/I(0))

=1/(I(T)/I(0))

=1/L1(T) …(5)

α=Rel(T)/Rel(0)

=(V/I(T))/(V/I(0))

=1/(I(T)/I(0))

=1/L1(T) …(5)

また、上式(2)は、I(T)=V/Rel(T)、I(0)=V/Rel(0)と表され、上式(4)は、I(T)/I(0)=exp(−K1・T)と表されるので、これらの式から次式(6)が導かれる。

(V/Rel(T))/(V/Rel(0))=exp(−K1・T)…(6)

(V/Rel(T))/(V/Rel(0))=exp(−K1・T)…(6)

さらに、K1は上式(4)および上式(5)より、1/α=exp(−K1・T)であることから、次式(7)のように表される。

K1=(ln α)/T …(7)

K1=(ln α)/T …(7)

したがって、ある時間tにおける規格化電流値I(t)/I(0)は、上式(4)および上式(7)より、次式(8)のように表される。

L1(t)=I(t)/I(0)

=exp(−(ln α)/T・t) …(8)

L1(t)=I(t)/I(0)

=exp(−(ln α)/T・t) …(8)

また、上式(8)は、I(t)=V/Rel(t)、I(0)=V/Rel(0)より、(V/Rel(t))/(V/Rel(0))=exp(−(ln α)/T・t)と表すことができるので、上式(8)は、オームの法則から、経時的な電気光学素子における抵抗の劣化関数Rel(t)として次式(9)のようにも表すことができる。

Rel(t)=Rel(0)・exp(−(ln α)/T・t) …(9)

Rel(t)=Rel(0)・exp(−(ln α)/T・t) …(9)

次に、電気光学素子に対して抵抗素子を直列に接続する場合について説明する。図2は、図1に示す回路における電気光学素子に対して抵抗素子を直列に挿入したときのこれらの素子を示す回路図である。なお、電気光学素子の劣化特性は、接続される抵抗素子に関わらず同じものとする。この電気光学素子の発光初期における抵抗値をRel(0)とし、この電気光学素子に対して直列に挿入される抵抗素子(以下「挿入抵抗素子」という)の抵抗値(以下「挿入抵抗値」という)をRrとするとき、電気光学素子の発光初期における電流値I’(0)が電流値I(0)と等しくなるような電圧値V’を決定することができる。すなわち、図2に示す電気光学素子の発光輝度が、挿入抵抗素子を挿入しないときの(図1に示す)電気光学素子の発光初期における発光輝度に等しくなるような電圧値V’を決定することができる。

発光初期において電気光学素子に加わる電圧値をVel(0)、そのときの挿入抵抗素子(挿入抵抗値Rr)に加わる電圧値をVr(0)とするとき、オームの法則より、上記電流、電圧、および抵抗の関係は、次式(10)のように表される。

V’=Vel(0)+Vr(0)

=I’(0)・(Rr+Rel(0))

=I(0)・(Rr+Rel(0)) …(10)

V’=Vel(0)+Vr(0)

=I’(0)・(Rr+Rel(0))

=I(0)・(Rr+Rel(0)) …(10)

上式(10)に示すI(0)は、オームの法則より、I(0)=Vel(0)/Rel(0)と表されるので、これを上式(10)に代入すると、次式(11)のように表すことができる。

V’=Vel(0)・(Rr+Rel(0))/Rel(0) …(11)

V’=Vel(0)・(Rr+Rel(0))/Rel(0) …(11)

ここで、挿入抵抗値Rrと電気光学素子の発光初期における抵抗値Rel(0)との抵抗比率(すなわち抵抗値Rel(0)に対する挿入抵抗値Rrの割合)をβとするとき、βは分圧の比率に置き替えることにより、次式(12)のように表現することができる。

β=Rr/Rel(0)

=(Vr(0)/I’(0))/(Vel(0)/I’(0))

=Vr(0)/Vel(0) …(12)

β=Rr/Rel(0)

=(Vr(0)/I’(0))/(Vel(0)/I’(0))

=Vr(0)/Vel(0) …(12)

このとき、上式(11)は、上式(12)に示すβを用いて表すと、次式(13)のように表現できる。

V’=Vel(0)・(β+1) …(13)

V’=Vel(0)・(β+1) …(13)

ここで、t時間後における電気光学素子の抵抗値Rel(t)と挿入抵抗値Rrとの和をR(t)とするとき、上式(9)及び上式(12)をR(t)に代入すると、R(t)は、次式(14)のように表される。

R(t)=Rel(t)+Rr

=Rel(0)・exp((ln α)/T・t)+β・Rel(0)

=[exp((ln α)/T・t)+β]・Rel(0)…(14)

R(t)=Rel(t)+Rr

=Rel(0)・exp((ln α)/T・t)+β・Rel(0)

=[exp((ln α)/T・t)+β]・Rel(0)…(14)

同様に、t時間後における電流値I’(t)も、オームの法則と上式(13)および上式(14)より、次式(15)のように表される。

I’(t)=V’/R(t)

=Vel(0)/Rel(0)・(β+1)

/[ exp((ln α)/T・t)+β]

=I(0)・(β+1)

/[ exp((ln α)/T・t)+β] …(15)

I’(t)=V’/R(t)

=Vel(0)/Rel(0)・(β+1)

/[ exp((ln α)/T・t)+β]

=I(0)・(β+1)

/[ exp((ln α)/T・t)+β] …(15)

また、上式(15)から、抵抗素子を直列に挿入したときの電気光学素子の経時的な輝度変化、すなわち電流変化I’(t)/I(0)は、次式(16)のように表される。

I’(t)/I(0)

=(β+1)/[ exp((ln α)/T・t)+β]…(16)

I’(t)/I(0)

=(β+1)/[ exp((ln α)/T・t)+β]…(16)

ここで、抵抗素子を挿入しないときの(図1に示す)電気光学素子に流れる電流と、抵抗素子を直列に挿入したときの(図2に示す)電気光学素子に流れる電流とが同一となる時間について、抵抗素子を挿入しないときの上記時間をTとすると、抵抗素子を挿入したときの上記時間はTのX倍としてXTと表すことができる。したがって、I’(XT)/I(0)=I(T)/I(0)となる。この式に上式(8)および上式(16)を代入すると、次式(17)のように表すことができる。

(β+1)/[ exp((ln α)/T・XT)+β]

=exp(−(ln α)/T・T) …(17)

(β+1)/[ exp((ln α)/T・XT)+β]

=exp(−(ln α)/T・T) …(17)

上式(17)を整理すると、次式(18)のように表される。

β=(αx −α)/(α−1) …(18)

β=(αx −α)/(α−1) …(18)

上式(18)によれば、電気光学素子が劣化し、所定の輝度から輝度Lになる時間をTとし、この時間TをX倍に延ばすためのβの値(すなわち電気光学素子の発光輝度が所定の輝度になるときのその両端に加わる電圧値Velと、そのときの挿入抵抗素子の両端に加わる電圧値Vrとの比率Vr/Vel)は、T時間後における電気光学素子の電圧値Velの増加率(すなわちT時間後の規格化された輝度の逆数)αを求めることにより、求めることができる。逆に、上記αの値を求め、さらに電圧値Vrの値を求めることでβの値を求めることにより、所定の輝度からある輝度Lとなる時間Tが、X倍延びることを知ることもできる。

なお、上記の原理的な説明では省略したが、現実的には配線等の他の抵抗素子による影響、電気光学素子の内部構造のばらつき、またはスイッチング素子の経時的な劣化等により、上記指数関数から導かれる値には、ずれが生じる。例えば、上式(1)で近似した電気光学素子の輝度の経時変化モデルは発光初期のモデルであるため、後述する実際の測定結果を考慮すると、発光中期(例えば所定の輝度が半減する時刻近傍)では、上式(1)に補正式を加えた多項式の近似式となると考えられる。しかしながら、上記のずれに関わらず、基本的には上記原理の説明で示したように、挿入抵抗により電気光学素子の輝度の経時変化速度を遅くし、表示寿命をより長くする効果を得ることができるので、上記多項式に関する説明は省略する。

ここで、以下に説明する本発明の一実施形態に係る表示素子(ここでは画素を構成する画素回路)では、上記挿入抵抗素子を用いることなく、当該表示素子に含まれる電気光学素子に対して直列に接続される電流制御用TFTの導電率を調整する。具体的には、電流制御用TFTのゲート幅を調節し、またはデータ信号の電圧値を調節することにより、上記分圧Vrを調整する。本表示素子は、このことにより表示寿命を長くする構成である。以下、本発明の一実施形態に係る表示素子に含まれる電気光学素子を有機EL素子とし、スイッチング素子をTFT素子として、当該有機EL素子に対して直列に接続された電流制御用のTFTの導電率が調整される表示素子および当該表示素子を含む表示装置について説明する。

<2.表示素子および表示装置の構成>

図3は、本発明の一実施形態に係る表示装置の構成を示すブロック図である。この表示装置は、画像表示部100と、選択信号出力部101と、データ信号出力部102と、駆動信号発生部103と、電流供給部104とを含む。画像表示部100は、表示素子がm×nのマトリクス状に複数配置されることにより構成される。選択信号出力部(ゲートドライバ回路)101は、表示素子の走査信号線電極に繋がる複数の走査信号線に接続されており、所定の周期を有する走査信号を当該走査信号線に出力する。データ信号出力部(ソースドライバ回路)102は、表示素子のデータ信号線電極に繋がる複数のデータ信号線に接続されており、有機EL素子の発光または非発光を制御するためのデータ信号を出力する。駆動信号発生部103は、上記選択信号出力部101およびデータ信号出力部102に対して走査信号およびデータ信号を生成するための所定の制御信号を出力する。電流供給部104は、表示素子の電源線電極に繋がる複数の電源配線に接続されており、発光素子のための駆動電流を供給する駆動電源である。

図3は、本発明の一実施形態に係る表示装置の構成を示すブロック図である。この表示装置は、画像表示部100と、選択信号出力部101と、データ信号出力部102と、駆動信号発生部103と、電流供給部104とを含む。画像表示部100は、表示素子がm×nのマトリクス状に複数配置されることにより構成される。選択信号出力部(ゲートドライバ回路)101は、表示素子の走査信号線電極に繋がる複数の走査信号線に接続されており、所定の周期を有する走査信号を当該走査信号線に出力する。データ信号出力部(ソースドライバ回路)102は、表示素子のデータ信号線電極に繋がる複数のデータ信号線に接続されており、有機EL素子の発光または非発光を制御するためのデータ信号を出力する。駆動信号発生部103は、上記選択信号出力部101およびデータ信号出力部102に対して走査信号およびデータ信号を生成するための所定の制御信号を出力する。電流供給部104は、表示素子の電源線電極に繋がる複数の電源配線に接続されており、発光素子のための駆動電流を供給する駆動電源である。

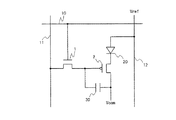

次に、上記画素表示部100に含まれる表示素子の構成につき説明する。図4は、本発明の一実施形態に係る表示素子の等価回路を示す図である。この表示素子は、電気光学素子である有機EL素子20と、駆動電源Vref(電流供給部104)からの電流を供給する電源線電極12と、選択信号出力部(ゲートドライバ回路)101に接続される走査信号線電極10と、データ信号出力部(ソースドライバ回路)102に接続されるデータ信号線電極11と、共通電極Vcomと、補助容量30と、有機EL素子20に流す電流を制御するためのpチャネル型TFTである電流制御用TFT2と、有機EL素子20に電流を流すタイミングを制御するnチャネル型TFTであるデータ電圧制御用TFT1とを備える。

ここで、データ電圧制御用TFT1および電流制御用TFT2のシリコン膜には、アモルファスシリコンや多結晶シリコン、またはシリコン膜とは別に導電性の有機材料膜であってもよいが、アモルファスや多結晶よりも結晶が大きく、有機EL素子により電流を多く流すことができる(すなわち発光輝度の上限がより大きくなるため、ディスプレイのさらなる高輝度化に対応できる)上述のCGシリコンが用いられるものとする。なお、これらのシリコン膜には、当該CGシリコンよりもさらに多く電流を流せるシリコン膜、例えば単結晶シリコンが用いられてもよい。また、上記表示素子では、電流制御用TFT2としてpチャネル型TFTが用いられるが、nチャネル型TFTが用いられる公知の画素回路の構成であってもよい。

図4に示されるように、電源線電極12には、電流制御用TFT2のソース端子と補助容量30の一端とが接続され、補助容量30の他端には電流制御用TFT2のゲート端子およびデータ電圧制御用TFT1のドレイン端子とが接続される。また、データ電圧制御用TFT1のソース端子にはデータ信号線電極11が接続され、そのゲート端子には走査信号線電極10が接続される。さらに、有機EL素子20の陽極は、電流制御用TFT2のドレイン端子に接続され、その陰極は共通電極Vcomに接続される。定電圧型制御方式では、走査信号線電極10に与えられる走査信号によりデータ電圧制御用TFT1が選択されている期間に、データ信号線電極11に対してデータ信号電圧が印加されることにより、当該データ信号電圧に応じた電圧が補助容量30に保持される。その後、データ電圧制御用TFT1が選択されていない期間に、補助容量30で保持されている電圧に応じて電流制御用TFT2の導電率が制御される。このように、電流制御用TFT2に対して直列に接続される有機EL素子20に所定の電流が流されることにより、その発光量が制御される。

ここで、上記構成では、前述した従来の表示素子のように電気光学素子に対して挿入抵抗素子を直列に接続するのではなく、電流制御用TFT2の導電率を制御することにより、当該電流制御用TFT2を(挿入抵抗素子に代わる)抵抗素子として機能させる。ただし、当該電流制御用TFT2のソース・ドレイン電流をアナログ量で制御するアナログ階調制御の構成では、前述した特開2001−272930号公報等で開示されているようなTFT素子の素子特性等による階調のばらつきが大きくなる。そのため、本実施形態の構成として採用可能ではあるが上記理由により必ずしも好ましくない。そこで、本実施形態では、有機EL素子20を所定の明輝度の発光状態または所定の暗輝度の非発光状態とする2値のデータ信号電圧により制御し、有機EL素子20の発光時間を制御することにより階調を表現するデジタル階調制御方式が用いられるものとする。

次に、この2値のデータ信号電圧につき説明する。図5は、上記電流制御用TFT2のゲートに対して電圧値Vgの電圧が印加されたときにソース・ドレイン間を流れる電流値をIdとしたときの、当該電圧値Vgと当該電流値Idとの関係を示す図である。図5では、有機EL素子20の発光時における上記電圧値Vgの範囲がaとして示され、非発光時における上記電圧値Vgの範囲がbとして示され、発光状態と非発光状態との境界となる上記電圧値Vgの範囲が閾値電圧値Vthとして示されている。図5を参照すると、発光状態と非発光状態とを区別可能な電圧値Vgであれば、閾値電圧値Vthを除くどの範囲の電圧値Vgが上記データ信号電圧の基準値とされてもよい。もっとも、例えば表示に必要なコントラスト比が1000以上であるとすると、非発光時の電流値に対する発光時の電流値の比率は、絶対値で103 以上となる電圧値Vgを基準値とすることが好ましい。なお、上記電源線電極12は、定電圧源回路である駆動電源Vref(電流供給部104)に接続されているため、この電源線電極12により、有機EL素子20が発光するために十分である電圧であって、かつ設定された輝度で発光状態を維持するのに十分である一定の電圧が、有機EL素子20と、当該有機EL素子20に直列に接続された電流制御用TFT2とに印加される。

ここで、有機EL素子20の表示寿命の延長効果を簡易に説明するため、以下のように条件を固定して説明する。すなわち、電流制御用TFT2と有機EL素子20とにより形成される直列回路には一定の電圧が印加されるものとし、有機EL素子20は常時発光しているものとする。この条件によれば、電流制御用TFT2のゲートに印加される電圧値Vgは、図5に示すaの範囲にあるため、補助容量30によって電流制御用TFT2の導電率は高い状態で保持される。すなわち、この条件によれば、データ電圧制御用TFT1を選択状態とする走査信号が走査信号線電極10に印加されており、かつ電流制御用TFT2を高い導電率状態に維持するため必要十分となる電圧のデータ信号がデータ信号線電極11に印加される。したがって、表示素子に含まれる走査信号線電極10、データ信号線電極11、データ電圧制御用TFT1、および補助容量30の抵抗成分および容量成分と、電流制御用TFT2および有機EL素子20の容量成分については無視することができる。その結果、上記表示素子は、有機EL素子20発光時の電流制御用TFT2の導通抵抗Rrと、有機EL素子20の抵抗Relとによる単純な直列回路として説明することができる。

図6は、この直列回路として表される表示素子の等価回路を示す図である。この図6を参照すれば明らかなように、電流制御用TFT2の導通抵抗Rrを所定の値とすれば、前述した従来の表示素子のように直列に抵抗素子を挿入することなく、有機EL素子20に加わる分圧値を所望の値にすることができる。

そこで、電流制御用TFT2のゲートに印加されるデータ信号電圧、すなわち上記電圧値Vgを適宜に設定することにより、電流制御用TFT2の導通抵抗Rrを所望の値に制御する。そうすれば直列に抵抗素子を挿入することなく、有機EL素子20に加わる分圧値を所望の値にすることにより、その表示寿命を延長させることができる。もっとも上述のように、当該電圧値Vgは、非発光時に有機EL素子20に流れる電流値に対する発光時に流れる電流値の比率が絶対値で103 以上となる値に設定されることが好ましい。

また、上記電流制御用TFT2の導通抵抗Rrは、上記のようにデータ信号電圧を適宜に設定することなく、当該電流制御用TFT2のゲート幅やゲート長の大きさなどを変更することにより所望の値にすることもできる。一般的には、ゲート幅を小さくし、またはゲート長を大きくすると、導電率は低くなり、ソース・ドレイン間の抵抗は増大する。そこで、電流制御用TFT2の構造(例えばゲート幅)を適宜に設計することにより、電流制御用TFT2の導通抵抗Rrを所望の値に設定する。そうすれば直列に抵抗素子を挿入することなく、有機EL素子20に加わる電圧の分圧値を所望の値にすることにより、その表示寿命を延長させることができる。以下、この電流制御用TFT2の構造につき説明する。

図7は、上記表示素子に含まれる電流制御用TFT2近傍の構造例を示す断面図である。図7に示すように ガラス基板60には活性層となるCGシリコン薄膜52が形成され、さらにゲート絶縁膜59を挟んでゲート電極51および層間絶縁膜58が形成される。その後、CGシリコン薄膜52が露出されるように2つの後述するコンタクト部が開口され、これらのコンタクト部には配線層56および電源線電極12が形成される。さらにその上に不動態化するためのパッシベーション膜57と表面を平坦にするための平坦化膜55とが形成された後、配線層56が露出されるようにさらなるコンタクト部が開口される。この上にITO(Indium Tin Oxide)からなる透明導電膜54が形成される。この透明導電膜54は有機EL素子20の陽極(アノード電極)となる。さらに、その上に蛍光材料である有機材料が塗布されてなる有機EL素子20が形成された後、共通電極Vcomとしての金属製導電層53が形成される。この金属製導電層53は、有機EL素子20の陰極(カソード電極)となる。

なお、上記表示素子(の有機EL素子20)は、上記CGシリコン薄膜52を含む薄膜トランジスタが形成されるガラス基板60方向へ発光する。このような構造はボトム・エミッション構造と呼ばれる。これに対して、アノード電極となる透明導電膜54とカソード電極となる金属製導電層53とを入れ替えることにより、上記方向とは逆の方向に発光させてもよい。この構造はトップ・エミッション構造と呼ばれる。図8は、このトップ・エミッション構造を実現する表示素子の等価回路を示す図である。図8に示されるように、このトップ・エミッション構造では、図4に示す表示素子の等価回路とは異なり、電気光学素子である有機EL素子20と電流制御用TFT2との配置関係が逆になっており、有機EL素子20の陽極は、電流制御用TFT2を介することなく電源線電極12に直接接続される。この構造は、TFTが形成されているガラス基板を光が通過しない構造となるため開口率を大きくすることができるという利点を有するが、金属製導電層上に有機膜を形成することが困難であるという欠点を有するため、通常はボトム・エミッション構造が好適である。しかし、本実施形態に係る表示素子の構成は、トップ・エミッション構造においても全く同様の効果を奏するため、本実施形態に係る表示装置(表示素子)はトップ・エミッション構造であってもよい。

図9は、上記電流制御用TFT2を含む表示素子の概略的な構造を示す平面図である。この表示素子は、図4に示す各構成要素である有機EL素子20と、電源線電極12と、走査信号線電極10と、データ信号線電極11と、補助容量30と、電流制御用TFT2と、データ電圧制御用TFT1とを備える。さらに、本表示素子には、有機EL素子20の下面にITOからなる透明導電膜54が形成される。なお、図9では見やすくするため、図7に示す金属製導電層53の記載を省略している。

また、図10は、上記電流制御用TFT2の概略的な構造を示す平面図である。図10に示されるように、CGシリコン薄膜52の一端は第1のコンタクト部61を介して透明導電膜54に接続され、その他端は第2のコンタクト部62を介して電源線電極12に接続される。また、ゲート電極51とCGシリコン薄膜52とは直交しており、CGシリコン薄膜52の長手方向に沿ったゲート電極51の長さはゲート長Lとして示され、ゲート電極51の長手方向に沿ったCGシリコン薄膜52の長さはゲート幅Wとして示されている。ここで、上記ゲート幅Wを小さくし、またはゲート長Lを大きくすると、導電率が低くなるため、有機EL素子20の表示寿命を相対的に延ばすことができる。以下、具体的に説明する。

表示素子に含まれる有機EL素子の所定の輝度における発光初期時の内部抵抗の値は、発光面積やその内部構造によって大きく変動するため、特に制限されるものではないが、通常は100Ω〜20MΩである。例えば、100PPI(Pixel Per Inch)の画素密度のときの上記内部抵抗の値は、1MΩ〜10MΩである。一般に、有機EL素子の内部抵抗の値は、その内部を流れる電流密度、輝度特性、および電流密度−電圧特性に基づき算出される。また、有機EL素子(の両端)に加わる電圧値によりその内部抵抗が変化することはよく知られている。この有機EL素子を発光させるときに当該素子に加わる電圧(以下「発光時のEL電圧」という)は、素子構造により異なるが、通常は約2V〜約10Vである。

また、本表示素子に含まれるCGシリコンからなる各TFT素子の耐圧は、ゲート長等によっても異なるが、最大で約16Vである。よって、発光時における電流制御用TFT2のソース・ドレイン間に印加しうる電圧の上限値は16Vとなる。さらに、電流制御用TFT2がOFF状態、すなわち有機EL素子20が非発光状態のとき、当該電流制御用TFT2に加わる分圧は、電源電圧から非発光状態の有機EL素子20に加わる分圧(以下「非発光時のEL電圧」という)を差し引いた電圧に等しくなる。この非発光時のEL電圧は、有機EL素子20を構成する材料やその素子電流値により異なるが、おおむね0V〜2V程度である。よって、有機EL素子20が発光状態であるときと非発光状態であるときとを考慮すると、電流制御用TFT2のソース・ドレイン間電圧とEL電圧値Velとの和である全体の電圧値V’の上限は16Vとなる。なお、消費電力の点からも、電圧値V’の上限としては16V程度が適当である。

ここで、図6に示す上述の本実施形態に係る表示素子の等価回路は、図2に示す抵抗素子を直列に挿入した従来の表示素子と同様に考えることができるので、従来の表示素子において挿入される挿入抵抗素子に加わる電圧値Vrは、電流制御用TFT2のソース・ドレイン間電圧と同視することができる。そこで、発光時の有機EL素子20に加わる電圧を電圧値Velとし、発光時の電流制御用TFT2のソース・ドレイン間電圧を電圧値Vrとし、β=Vr/Velとするとき、電圧値Velの最小値は有機EL素子20が発光するための最小電圧である2Vであるから、上式(13)より次式(19)に示す不等式が導かれる。

16≧2(β+1) …(19)

この式(19)より、β≦7となり、βの上限値は7であることがわかる。

16≧2(β+1) …(19)

この式(19)より、β≦7となり、βの上限値は7であることがわかる。

また、前述のように、挿入抵抗素子(挿入抵抗値Rr)がEL素子に対して直列に接続された表示素子の方が、接続されない表示素子(挿入抵抗値Rr=0)よりもEL素子の表示寿命を長くすることができるため、β>0と仮定することができる。実際的なβの下限値については後述する。

ここで、電流制御用TFT2の耐圧は大きければ大きいほど好ましいが、上述したようにCGシリコンのTFT耐圧はゲート長等によって異なる。一般的には、電流制御用TFT2には最大で耐圧8Vの素子が用いられる。このとき、有機EL素子20の発光するための最小電圧を2Vとすると、上述と同様に上式(13)より、β≦3となる。

次に、図6に示す等価回路をモデルとして用い、本表示素子に含まれる電流制御用TFT2に加わる(分圧された)電圧値を変化させることにより表示寿命がどのように延びるかにつき説明する。ここでは、電流制御用TFT2に加わる電圧値を素子の導通抵抗値により決定するものとし、この電流制御用TFT2のゲート幅Wを4μmとした場合を条件Aとし、ゲート幅Wを30μmとした場合を条件Bとする。また、条件Aおよび条件Bではいずれも、データ電圧制御用TFT1のゲートに印加される電圧が16V、電流制御用TFT2のゲートに印加される電圧が2V、駆動電源からの電圧が9Vに設定されるものとする。さらに、有機EL素子20の発光初期の輝度を条件Aおよび条件Bにおいて同一にするため、電流制御用TFT2に流れる電流値を条件Aおよび条件Bにおいて同一にするように駆動電源から与えられる電圧が調整されるものとする。このときの共通電極Vcomの電圧は、条件Aでは4.70Vとなり、条件Bでは5.02Vとなる。また、電流制御用TFT2のソース・ドレイン間の導通抵抗Rrは、条件Aでは約300kΩとなり、条件Bでは約5kΩとなる。

以上より、図6に示す等価回路全体の電圧V’は、駆動電源の電圧から共通電極Vcomの電圧を差し引いた電圧値となるので、条件Aでは4.30Vとなり、条件Bでは3.98Vとなる。また、測定環境により異なるが、本表示素子の配線抵抗等の抵抗値は、有機EL素子20の内部抵抗値に比べて約1/2000程度の非常に小さい値となるため、この抵抗値はほぼ無視してよい。したがって、電流制御用TFT2に加わる分圧Vrの有機EL素子20に加わる分圧Velに対する比率β(=Vr/Vel)は、条件Aでは0.131となり、条件Bでは0.002となる。

図11は、上記条件Aおよび条件Bにおいて、規格化された有機EL素子20の発光輝度の経時変化を示す図である。図では、規格化された有機EL素子20の発光輝度を縦軸に、条件Bの規格化輝度が0.5になる時間を1とした規格化時間を横軸にとり、条件Aおよび条件Bにおける発光輝度と時間との関係が示されている。ここで、上述のように条件Bにおけるβはほぼ0であることから、条件Bにおける電流制御用TFT2の導通抵抗Rrは0であるものとし、駆動電源からの電圧(電圧値V’)はすべて有機EL素子20に加わるものとしてよい。そこで、発光輝度が所定値まで低下する時間、例えば規格化輝度が0.9になるまでの経過時間に着目して図11を参照すると、上記所定値に低下するまでの経過時間は、条件Aにおける時間の方が条件Bにおける時間よりも約1.15倍に延びていることがわかる。また、このときのβの値に基づき、上式(18)より求められる条件Aの条件Bに対する上記経過時間は、約1.13倍の延長となる。逆に、上式(18)より求められるβは0.159となり、上記測定値から求められる値に近い値となる。

さらに、上記規格化輝度が0.5になるまでの経過時間、すなわち有機EL素子20の表示寿命は、条件Aの方が条件Bよりも1.76倍に延びている。この値は、上記βの値に基づき上式(18)より求めた条件Aの条件Bに対する上記経過時間の比率である1.09倍よりも大きくなっている。この原因は、理論上では上述のように時間経過による素子特性の劣化速度を指数関数で近似しているが、実際には時間経過に伴って素子特性の劣化速度が初期状態での劣化速度よりも低下していることにあると考えられる。したがって、理論上さらに正確な表示寿命の予測を行うためには、上述のような時間経過に伴う劣化速度の低下を考慮して素子特性の劣化関数を修正すればよい。

以上のことからわかるように、βがほぼ0に等しい場合、すなわち後述の条件Bにおけるβ=0.002のときには、電流制御用TFT2の導通抵抗Rrは有機EL素子の抵抗Relに対してほぼ0と考えられ、駆動電源からの電圧はほとんどすべて有機EL素子20に加わることになるため、表示寿命の延長効果はほとんど期待できない。それに対して、βが0.1近傍の値である場合、すなわち条件Aにおけるβ=0.131のときには、上述したように実際に表示寿命の延長効果を得ることができる。したがって、βの下限値は少なくとも0.1以上でなければならないと考えられる。

このように、本実施形態における有機EL素子20を含む表示素子は、当該有機EL素子20に対して直列に接続される電流制御用TFT2のゲート幅Wを小さくするように構成すれば、有機EL素子20の点灯時における電流制御用TFT2の導通抵抗を相対的に高くすることができるため、表示素子の表示寿命を相対的に延ばすことができることがわかる。

また上述のように、本実施形態に係る表示素子および当該表示素子を含む表示装置では、表示素子の発光時におけるβの範囲が0.1≦β≦7であるように設定されることが好適である。さらに、電流制御用TFT2の耐圧値が小さい値(例えば最大で8V)であるとき、βの範囲が0.1≦β≦3であるように設定されることがより好適である。

なお、ここでは、電流制御用TFT2の導通抵抗Rrを設定する方法として、当該電流制御用TFT2のゲート幅を適宜に調整する方法を例示したが、この方法に限定されるものではなく、ゲート長を適宜に調整する方法が用いられてもよい。また、電流制御用TFT2を作製するときにCGシリコン薄膜52のドーズ量を適宜に調整する方法が用いられてもよい。例えば、CGシリコン薄膜52にドープされた不純物(ここではp型)の注入量(ドーズ量)を少なくするほど上記導通抵抗Rrは増加する。もっとも、ドーズ量を極端に少なくすると、電流制御用TFT2のスイッチング機能が失われるため、その量には所定の下限値がある。さらに、電流制御用TFT2は、そのCGシリコン薄膜52に比較的低濃度の不純物がドープされた領域を有するLDD(Lightly Doped Drain )構造であるものとして、当該構造を適宜に調整することにより所望の導通抵抗Rrを設定する方法が用いられてもよい。

このように、本表示素子および本表示装置では、定電圧型制御方式である図4に示す表示素子にいかなる追加素子または付加回路を設ける必要がないため、発光素子を長寿命化しつつ、画素面積を広く(開口率を高く)することができる。また、周辺回路にも付加回路を設ける必要がないため、表示装置全体を小型化・簡素化することができる。なお、本実施形態の構成は、3つ以上のTFT素子を含む画素回路にも、容易に適用することができる。

以上のように本発明によれば、電気光学素子の発光時に、その両端に加わる電圧値Velに対する電流制御用素子の両端に加わる電圧値Vrの比率β(=Vr/Vel)が、0.1≦β≦7.0となるように電流制御素子の導通抵抗値が設定される。新たに抵抗素子を挿入したり、特別な補償回路等を組み込むことなく、電気光学素子の輝度の経時変化速度を遅くすることができるため、電気光学素子の表示寿命をより長くすることができる。さらに、TFTの特性ばらつきの影響を低減でき、制御性の良い階調表示を行うことができる、サブフィールド法や、発光面積の異なる電気光学素子を2値のデジタルデータ信号で階調制御する方式(たとえば特許文献1を参照)では、アナログ階調表示に比べて、常に高い発光輝度を必要とするため、有機EL素子の劣化を早め、表示寿命を短くしてしまう。本発明では、上記構成の表示素子における電気光学素子が2値で階調制御されることにより、従来の表示寿命をさらに延ばしながら、かつ制御性の良い階調表示を行える、優れた表示素子および表示装置を提供することができる。

1 …データ電圧制御用TFT

2 …電流制御用TFT

10 …走査信号線電極

11 …データ信号線電極

12 …電源線電極

20 …有機EL素子

30 …補助容量

51 …ゲート電極

52 …CGシリコン薄膜

54 …透明導電膜

60 …ガラス基板

100…画像表示部

101…選択信号出力部

102…画像信号出力部

103…駆動信号発生部

104…電流供給部

Vcom …共通電極

Vref …駆動電源

2 …電流制御用TFT

10 …走査信号線電極

11 …データ信号線電極

12 …電源線電極

20 …有機EL素子

30 …補助容量

51 …ゲート電極

52 …CGシリコン薄膜

54 …透明導電膜

60 …ガラス基板

100…画像表示部

101…選択信号出力部

102…画像信号出力部

103…駆動信号発生部

104…電流供給部

Vcom …共通電極

Vref …駆動電源

Claims (15)

- 電流により駆動される電気光学素子と、当該電気光学素子に対して直列に接続されることにより当該電気光学素子に流れるべき電流を与える電流制御用素子と、当該電流制御用素子を制御するためのデータ信号を当該電流制御用素子に与えるスイッチング素子と、当該スイッチング素子を制御するための走査信号を前記スイッチング素子に与える走査信号線電極と、前記データ信号を前記スイッチング素子に与えるデータ信号線電極と、前記電気光学素子を駆動するための電流を前記電流制御用素子に与える電源線電極とを備える表示素子であって、

前記電流制御用素子は、前記電気光学素子の発光時に、前記電気光学素子の両端に加わる電圧値Velに対する当該電流制御用素子の両端に加わる電圧値Vrの比率をβ(=Vr/Vel)とするとき0.1≦β≦7.0を満たす所定の導通抵抗値を有することを特徴とする表示素子。 - 前記電流制御用素子は、0.1≦β≦3.0を満たす所定の導通抵抗値を有することを特徴とする、請求項1に記載の表示素子。

- 前記電流制御用素子は、薄膜トランジスタであることを特徴とする、請求項1に記載の表示素子。

- 前記電流制御用素子は、多結晶シリコンからなる薄膜トランジスタであることを特徴とする、請求項3に記載の表示素子。

- 前記電流制御用素子は、pチャネル型の薄膜トランジスタであることを特徴とする、請求項3に記載の表示素子。

- 前記電流制御用素子は、nチャネル型の薄膜トランジスタであることを特徴とする、請求項3に記載の表示素子。

- 前記電流制御用素子は、前記所定の導通抵抗値を有するように形成されることを特徴とする、請求項3に記載の表示素子。

- 前記電流制御用素子は、当該電流制御用素子のゲート幅またはゲート長を所定の長さに形成されることにより、前記所定の導通抵抗値を有することを特徴とする、請求項7に記載の表示素子。

- 前記電気光学素子は、有機エレクトロルミネッセンス素子であることを特徴とする、請求項1に記載の表示素子。

- 前記データ信号の電圧に応じた電荷を蓄積することにより、当該蓄積された電荷に応じた電圧を、前記電流制御用素子を制御するための電圧として保持する容量部をさらに備えることを特徴とする、請求項1に記載の表示素子。

- 前記電流制御用素子は、表示されるべき所定の階調に応じてあらかじめ定められた所定の電圧を有する前記データ信号を受け取ることを特徴とする、請求項1に記載の表示素子。

- 前記電流制御用素子は、当該電流制御用素子をオンまたはオフするための2値信号である前記データ信号を受け取ることを特徴とする、請求項1に記載の表示素子。

- 請求項1から請求項12までのいずれか1項に記載の表示素子を複数配列してなる表示部と、

前記表示素子に所定の電圧値を有する前記データ信号を与える画像信号出力部と

を備える表示装置。 - 前記表示素子に含まれる電気光学素子は、発光または非発光のいずれかの発光状態となるように2値で階調制御されることを特徴とする、請求項13に記載の表示装置。

- 前記表示素子に含まれる電流制御用素子は、前記画像信号出力部からのデータ信号の電圧により、前記電気光学素子の発光時に0.1≦β≦7.0を満たす所定の導電率を有するように制御されることを特徴とする、請求項13または請求項14に記載の表示装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004059620A JP2005031629A (ja) | 2003-06-19 | 2004-03-03 | 表示素子および表示装置 |

| US10/872,093 US7301513B2 (en) | 2003-06-19 | 2004-06-17 | Display element and display device |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003175481 | 2003-06-19 | ||

| JP2004059620A JP2005031629A (ja) | 2003-06-19 | 2004-03-03 | 表示素子および表示装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005031629A true JP2005031629A (ja) | 2005-02-03 |

Family

ID=33518587

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004059620A Pending JP2005031629A (ja) | 2003-06-19 | 2004-03-03 | 表示素子および表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7301513B2 (ja) |

| JP (1) | JP2005031629A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006259374A (ja) * | 2005-03-17 | 2006-09-28 | Eastman Kodak Co | 表示装置 |

| JP2006259373A (ja) * | 2005-03-17 | 2006-09-28 | Eastman Kodak Co | 表示装置 |

| JP2006259714A (ja) * | 2006-02-17 | 2006-09-28 | Eastman Kodak Co | 表示装置 |

| WO2017221950A1 (ja) * | 2016-06-24 | 2017-12-28 | シャープ株式会社 | 光照射用基板 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1998040871A1 (fr) * | 1997-03-12 | 1998-09-17 | Seiko Epson Corporation | Circuit pixel, afficheur, et equipement electronique a dispositif photoemetteur commande par courant |

| CN102394049B (zh) * | 2005-05-02 | 2015-04-15 | 株式会社半导体能源研究所 | 显示装置的驱动方法 |

| EP1720149A3 (en) * | 2005-05-02 | 2007-06-27 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| US7636078B2 (en) * | 2005-05-20 | 2009-12-22 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| EP1724751B1 (en) * | 2005-05-20 | 2013-04-10 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic apparatus |

| US8059109B2 (en) * | 2005-05-20 | 2011-11-15 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic apparatus |

| GB2436391B (en) * | 2006-03-23 | 2011-03-16 | Cambridge Display Tech Ltd | Image processing systems |

| KR101594189B1 (ko) * | 2007-06-13 | 2016-02-15 | 가부시키가이샤 제이올레드 | 표시 장치, 영상 신호 처리 방법, 및 기록 매체 |

| KR101892307B1 (ko) * | 2011-11-24 | 2018-08-27 | 가부시키가이샤 제이올레드 | 표시 장치의 구동 방법 |

| KR102072403B1 (ko) * | 2013-12-31 | 2020-02-03 | 엘지디스플레이 주식회사 | 하이브리드 구동 방식 유기발광표시장치 |

| CN107767819A (zh) * | 2017-09-28 | 2018-03-06 | 京东方科技集团股份有限公司 | 像素驱动电路及方法、显示装置 |

| CN110364117B (zh) * | 2019-07-17 | 2021-10-01 | 京东方科技集团股份有限公司 | 像素电路及其驱动方法、显示面板和显示装置 |

| TWI855969B (zh) * | 2024-02-22 | 2024-09-11 | 友達光電股份有限公司 | 顯示面板 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1173158A (ja) | 1997-08-28 | 1999-03-16 | Seiko Epson Corp | 表示素子 |

| JP2001272930A (ja) | 2000-03-28 | 2001-10-05 | Sanyo Electric Co Ltd | エレクトロルミネッセンス表示装置 |

| JP4925528B2 (ja) | 2000-09-29 | 2012-04-25 | 三洋電機株式会社 | 表示装置 |

| US7456810B2 (en) * | 2001-10-26 | 2008-11-25 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and driving method thereof |

| TW558693B (en) * | 2002-04-17 | 2003-10-21 | Au Optronics Corp | Driving circuit design for display device |

-

2004

- 2004-03-03 JP JP2004059620A patent/JP2005031629A/ja active Pending

- 2004-06-17 US US10/872,093 patent/US7301513B2/en active Active

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006259374A (ja) * | 2005-03-17 | 2006-09-28 | Eastman Kodak Co | 表示装置 |

| JP2006259373A (ja) * | 2005-03-17 | 2006-09-28 | Eastman Kodak Co | 表示装置 |

| JP2006259714A (ja) * | 2006-02-17 | 2006-09-28 | Eastman Kodak Co | 表示装置 |

| WO2017221950A1 (ja) * | 2016-06-24 | 2017-12-28 | シャープ株式会社 | 光照射用基板 |

| CN109475751A (zh) * | 2016-06-24 | 2019-03-15 | 夏普株式会社 | 光照射用基板 |

| JPWO2017221950A1 (ja) * | 2016-06-24 | 2019-06-20 | シャープ株式会社 | 光照射用基板 |

| CN109475751B (zh) * | 2016-06-24 | 2020-10-20 | 夏普株式会社 | 光照射用基板 |

| US10974062B2 (en) | 2016-06-24 | 2021-04-13 | Sharp Kabushiki Kaisha | Photoirradiation substrate |

Also Published As

| Publication number | Publication date |

|---|---|

| US7301513B2 (en) | 2007-11-27 |

| US20040257359A1 (en) | 2004-12-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5538477B2 (ja) | 画像表示装置およびその駆動方法 | |

| US8243055B2 (en) | Light-emitting display device | |

| KR101282399B1 (ko) | 표시 장치 및 그 구동 방법 | |

| JP4737221B2 (ja) | 表示装置 | |

| TWI239500B (en) | Display device | |

| JP3989718B2 (ja) | メモリ一体型表示素子 | |

| CN102709478B (zh) | 发光装置 | |

| JP4168836B2 (ja) | 表示装置 | |

| US7551164B2 (en) | Active matrix oled display device with threshold voltage drift compensation | |

| US8605014B2 (en) | Method of driving image display apparatus | |

| JP2005031629A (ja) | 表示素子および表示装置 | |

| US8730134B2 (en) | Pixel circuit and display device | |

| WO2002075710A1 (fr) | Circuit de commande d'un element lumineux a matrice active | |

| CN100403377C (zh) | 图像显示装置 | |

| JP2005507505A (ja) | 有機elディスプレイパネルとこれを備えた有機elディスプレイ装置 | |

| KR102730411B1 (ko) | 표시 장치 및 그의 구동 방법 | |

| JP2006091089A (ja) | 画素駆動回路及び画像表示装置 | |

| TW200527378A (en) | Pixel circuit, display apparatus, and method for driving pixel circuit | |

| US20100001932A1 (en) | Display device and driving method thereof | |

| JPWO2002077958A1 (ja) | アクティブマトリクス型発光素子の駆動回路 | |

| CN101816036A (zh) | 电流驱动式el显示器的电源电压的动态自适应 | |

| JPWO2007040088A1 (ja) | 画像表示装置およびその駆動方法 | |

| JP2003150108A (ja) | アクティブマトリックス基板及びそれを用いた電流制御型発光素子の駆動方法 | |

| JP4838502B2 (ja) | 画像表示装置とその製造方法 | |

| JP2006106568A (ja) | 表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060125 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090220 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090317 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090707 |