CN101471133A - 半导体装置 - Google Patents

半导体装置 Download PDFInfo

- Publication number

- CN101471133A CN101471133A CNA2008101855938A CN200810185593A CN101471133A CN 101471133 A CN101471133 A CN 101471133A CN A2008101855938 A CNA2008101855938 A CN A2008101855938A CN 200810185593 A CN200810185593 A CN 200810185593A CN 101471133 A CN101471133 A CN 101471133A

- Authority

- CN

- China

- Prior art keywords

- layer

- memory

- memory cell

- current

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 75

- 230000015654 memory Effects 0.000 claims abstract description 398

- 230000008859 change Effects 0.000 claims abstract description 77

- 238000003860 storage Methods 0.000 claims description 162

- 238000006243 chemical reaction Methods 0.000 claims description 29

- 238000012546 transfer Methods 0.000 claims description 8

- 239000000463 material Substances 0.000 abstract description 24

- 150000004770 chalcogenides Chemical class 0.000 abstract description 23

- 230000007246 mechanism Effects 0.000 abstract description 2

- 210000004027 cell Anatomy 0.000 description 123

- 238000010586 diagram Methods 0.000 description 46

- 239000000872 buffer Substances 0.000 description 29

- 230000006870 function Effects 0.000 description 17

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 16

- 229910052721 tungsten Inorganic materials 0.000 description 16

- 239000010937 tungsten Substances 0.000 description 16

- 238000003491 array Methods 0.000 description 14

- 238000000034 method Methods 0.000 description 13

- 230000003213 activating effect Effects 0.000 description 11

- 230000000630 rising effect Effects 0.000 description 11

- 238000012360 testing method Methods 0.000 description 11

- 102100039496 Choline transporter-like protein 4 Human genes 0.000 description 9

- 101000889282 Homo sapiens Choline transporter-like protein 4 Proteins 0.000 description 9

- 230000000694 effects Effects 0.000 description 9

- 230000004913 activation Effects 0.000 description 7

- 101001095043 Homo sapiens Bone marrow proteoglycan Proteins 0.000 description 6

- 101001131990 Homo sapiens Peroxidasin homolog Proteins 0.000 description 6

- 101000582986 Homo sapiens Phospholipid phosphatase-related protein type 3 Proteins 0.000 description 6

- 101000999079 Homo sapiens Radiation-inducible immediate-early gene IEX-1 Proteins 0.000 description 6

- 101000879840 Homo sapiens Serglycin Proteins 0.000 description 6

- 102100030383 Phospholipid phosphatase-related protein type 3 Human genes 0.000 description 6

- 102100030368 Phospholipid phosphatase-related protein type 4 Human genes 0.000 description 6

- 238000012790 confirmation Methods 0.000 description 6

- 101100325974 Arabidopsis thaliana BHLH95 gene Proteins 0.000 description 5

- 230000009471 action Effects 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 5

- 101150103044 pcm3 gene Proteins 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 208000032414 susceptibility to 2 restless legs syndrome Diseases 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- 102100031699 Choline transporter-like protein 1 Human genes 0.000 description 3

- 101000940912 Homo sapiens Choline transporter-like protein 1 Proteins 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 239000012782 phase change material Substances 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 239000006185 dispersion Substances 0.000 description 2

- 230000016507 interphase Effects 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 238000010248 power generation Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 102100035954 Choline transporter-like protein 2 Human genes 0.000 description 1

- 102100039497 Choline transporter-like protein 3 Human genes 0.000 description 1

- 101000948115 Homo sapiens Choline transporter-like protein 2 Proteins 0.000 description 1

- 101000889279 Homo sapiens Choline transporter-like protein 3 Proteins 0.000 description 1

- 239000008186 active pharmaceutical agent Substances 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 230000002269 spontaneous effect Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 210000000352 storage cell Anatomy 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

- 238000003466 welding Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0004—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising amorphous/crystalline phase transition cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

- G11C13/0026—Bit-line or column circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0038—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0076—Write operation performed depending on read result

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0078—Write using current through the cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0083—Write to perform initialising, forming process, electro forming or conditioning

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

Landscapes

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Semiconductor Memories (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Abstract

本发明的课题是实现高可靠动作的相变存储器。本发明的半导体装置具有层叠了由使用硫族化合物材料的存储层和二极管构成的存储单元的结构的存储器阵列,根据所选择的存储单元所处的层变更初始化条件和改写条件。在根据动作选择电流镜电路的同时,利用电压选择电路和电流镜电路中的复位电流的控制机构,根据动作变更初始化条件和改写条件(在此是复位条件)。

Description

技术领域

本发明涉及半导体装置,涉及包含由与存储信息对应地在电阻值中产生差的元件构成的存储单元的存储装置,特别是涉及应用于包含使用了利用硫族化合物材料的状态变化来存储信息、检测由该信息产生的电阻值差来辨别信息的存储单元的相变存储器的存储装置的有效的技术。

背景技术

作为本发明者研究的技术,例如在包含相变存储器的半导体装置中可考虑以下的技术。存储元件将至少包含锑(Sb)和碲(Te)的Ge-Sb-Te系列、Ag-In-Sb-Te系列等的硫族化合物材料(或相变材料)用作记录层的材料。此外,选择元件使用了二极管。这样,例如在非专利文献1中叙述了使用了硫族化合物材料和二极管的相变存储器的特性。

图2是表示在使用了相变材料的电阻性存储元件的相变中必要的脉冲宽度和温度的关系的图。在该存储元件中写入存储信息“0”的情况下,如图2中所示,施加将元件加热到大于等于硫族化合物材料的熔点Ta之后急剧地冷却那样的复位脉冲。通过缩短冷却时间t1,例如设定为约1ns,硫族化合物材料成为高电阻的非晶质状态。

相反,在写入存储信息“1”的情况下,通过施加将存储元件保持为比熔点Ta低、比与玻璃转移点相同或比其高的结晶化温度Tx高的温度区域的那样的置位脉冲,硫族化合物材料成为低电阻的多晶状态。在结晶化中所需要的时间t2根据硫族化合物材料的组成而不同。图2中表示的元件的温度依赖于存储元件本身发出的焦耳热和对于周围的热扩散。

在专利文献1中记载了具有隔着绝缘层层叠了具有强电介质层的存储单元的阵列结构的半导体存储装置的存储单元特性和读出条件。具体地说,由于存储单元的热经历在每个层中不同,故根据所形成的层,在存储单元的电特性中产生差别。叙述了为了可靠地读出这样的存储单元根据所存取的存储单元包含的层改变参考电压的方式。在专利文献2中记载了具有层叠了由硫族化合物材料构成的存储单元的阵列结构的半导体存储装置的存储单元特性。即,将硫族化合物材料叙述为具有容易受到层叠排列的形成步骤的影响的特性。在专利文献3中记载了层叠型磁存储器的存储器阵列结构。具体地说,为了防止在每层中写入特性改变的情况,叙述了在每层中改变布线结构或接点结构等的方式。

【专利文献1】日本专利2003-060171号公报

【专利文献2】日本专利2007-501519号公报

【专利文献3】日本专利2004-266220号公报

【非专利文献1】「IEEE International Solid-State CircuitsConference,Digest of Technical Papers」(美国),2007年,p.472-473

发明内容

(发明要解决的问题)

本申请者等在本申请之前研究了使用由硫族化合物材料构成的记录层和二极管的相变存储器的高集成化。特别是在研究通过层叠存储器阵列得到的三维化时发现了下述的二个问题。

第一个问题是,由于存储单元的热经历在每个层中不同,故在存储单元的电特性中存在产生差别的危险。具体地说,下层的存储器阵列的热负载较大。因此,可预期下层的存储器阵列的制造后的电阻值较低。在相变存储器中,一般来说,进行施加比通常的改写动作高的电压或大的电流以降低电阻的所谓初始化动作。如果将该初始化动作中的偏压设定为与需要更高的电压或更大的电流的上层的存储器阵列一致的值,则对于电阻值低的下层的存储单元施加过度的应力,存在记录层的电特性劣化的危险。因而,希望根据形成了初始化的存储单元的层来调整初始化动作中的电压或电流。

第二个问题是,由于因与第一个问题同样的热经历产生的存储单元的电特性的差别的缘故,存在通常的改写动作后的电阻值产生离散(偏差)的危险。在前面叙述的专利文献1中记载的具有强电介质层的存储器、即强电介质存储器中,通过对强电介质施加电场以改变自发极化的方向来存储信息。作为补偿在所形成的层之间产生的存储单元的电特性差的方法,可考虑在每层中改变改写电压。但是,由于该方法有必要在每层中设置用于改变改写电压的电压控制电路,进而导致随着晶体管尺寸的增大而芯片面积增加,故是不理想的。因而,如专利文献1中叙述的那样,必须通过调整读出条件(在此,是参考电压)来补偿改写动作后的在存储单元中产生的电特性的差。

另一方面,在相变存储单元中,也可预期根据改写后的状态的差异导致干扰(disturb)或耐用性(endurance)等的特性劣化的情况。为了避免这样的问题,在用于成为高电阻状态的复位动作中,如果与需要较高的电压或大的电流的下层的存储器阵列一致地设定动作条件,则对电阻值相对高的位于上层的存储器阵列的存储单元施加过度的应力。其结果,复位后的电阻值提高到必要的程度以上,存在不能进行逆转改写动作的危险。与此相反,如果将复位动作中的偏压设定为对于上层的存储器阵列必要的值,则由于对电阻值相对低的位于下层的存储器单元供给的能量不足,故存在不变化为所希望的电阻值的危险。但是,在考虑抑制芯片面积而在硅衬底上形成在各层中共同的读出电路的情况下,为了实现可靠的读出动作,复位状态的单元电阻必须大于等于一定值。因而,希望对于位于存储器阵列的任意的位置上的存储单元都成为相同的电阻值那样的复位动作。

第三个问题是,由于迄今为止叙述的热负载的影响的缘故,存在根据形成存储单元的层在成品率上产生差别的危险。即,在迄今为止的芯片体系结构中,在存在成品率低的层的情况下,判断为芯片整体不合格而废弃该芯片。在这样的检查方法中,每个晶片的芯片取得个数就减少了,结果导致位成本的增加。为了减少位成本,希望有下述的体系结构:按层单位进行合格品判断,即使存在一个成品率高的层也能够将该芯片看作合格品而出厂。

因此,本发明的目的在于,鉴于这样的问题等,在具有层叠了存储单元的结构的存储器阵列的相变存储器中,通过根据形成了存储单元的层调整初始化动作或写入动作的驱动电压或驱动电流,将存储单元控制为所希望的电阻值而不损害硫族化合物材料的电特性。此外,本发明的目的在于作成下述的存储器阵列结构:按层单位评价存储单元的性能,即使存在一个成品率高的层,也能只使用该层。根据本说明书的记述和附图,本发明的上述的目的和新的特征会变得很明白。

(用于解决问题的方法)

如果简单地说明在本申请中公开的发明中的代表性的内容的概要,则如下所述。

其特征在于,具有:第1存储单元,设置在第1层中,具有并利用电流写入存储信息的第1存储元件;第2存储单元,设置在上述第1层的上方形成的第2层中,具有利用电流写入存储信息的第2存储元件;第1地址解码器,用于输出用来选择上述第1层的第1层选择信号或用来选择上述第2层的第2层选择信号;以及改写驱动器,用于在对上述第1存储单元写入第1存储信息时对上述第1存储单元供给第1电流、在对上述第2存储单元写入上述第1存储信息时对上述第2存储单元供给与上述第1电流不同的大小的第2电流,上述改写驱动器根据上述第1层选择信号和上述第2层选择信号控制上述第1电流和上述第2电流的大小。

或者,其特征在于,具有:第1位线,设置在第1层中;第2位线,设置在形成于上述第1层的上方的第2层中;第1字线和第2字线,与上述第1位线和上述第2位线交叉;第1存储单元,设置在上述第1位线与上述第1字线的交点处,具有利用电流写入存储信息的第1存储元件和用于在从上述第1字线经由上述第1存储元件到达上述第1位线的方向上流过电流的第1整流元件;第2存储单元,设置在上述第1位线与上述第2字线的交点处,具有利用电流写入存储信息的第2存储元件和用于在从上述第2字线经由上述第2存储元件到达上述第1位线的方向上流过电流的第2整流元件;第3存储单元,设置在上述第2位线与上述第1字线的交点处,具有利用电流写入存储信息的第3存储元件和用于在从上述第1字线经由上述第3存储元件到达上述第2位线的方向上流过电流的第3整流元件;以及第4存储单元,设置在上述第2位线与上述第2字线的交点处,具有利用电流写入存储信息的第4存储元件和用于在从上述第2字线经由上述第4存储元件到达上述第2位线的方向上流过电流的第4整流元件,在对上述第1或第2存储单元进行初始化的情况下,对上述第1或第2存储单元供给第1电压,在对上述第3或第4存储单元进行初始化的情况下,对上述第3或第4存储单元供给与上述第1电压不同的第2电压。

或者,其特征在于,具有:第1存储单元,设置在第1层中,具有利用电流写入存储信息的第1存储元件;第2存储单元,设置在形成于上述第1层的上方的第2层中,具有利用电流写入存储信息的第2存储元件;地址变换电路,用于将用来选择上述第1层或上述第2层的某一方的第1地址信号变换为用来选择上述第1层或上述第2层的另一方的第2地址信号;多路转换器,用于选择上述第1地址信号和从上述地址变换电路输出的上述第2地址信号中的某一方;以及第1地址解码器,用于根据上述多路转换器所选择的信号发生选择上述第1层的第1层选择信号或选择上述第2层的第2层选择信号。

(发明效果)

如果简单地说明由在本申请中公开的发明中的代表性的内容得到的效果,则可实现高可靠性动作的相变存储器。

附图说明

图1是表示在本发明的实施方式1的半导体装置中包含的相变存储器的主要部分电路块的结构例的图。

图2是表示在使用了相变材料的电阻元件的相变所需要的脉冲宽度和温度的关系的图。

图3是表示在本发明的实施方式1的半导体装置中图1中记载的电路块中的存储器阵列结构例的图。

图4是表示在本发明的实施方式1的半导体装置中图3中记载的存储器阵列中包含的层叠存储单元的剖面的图。

图5是表示在本发明的实施方式1的半导体装置中图1中记载的相变存储器的存储器映射图的图。

图6是表示在本发明的实施方式1的半导体装置中图5中记载的页结构的例子的图。

图7是表示在本发明的实施方式1的半导体装置中列地址的分配的例子的图。

图8是表示在本发明的实施方式1的半导体装置中行地址的分配的例子的图。

图9是表示在本发明的实施方式1的半导体装置中包含的图1中的读出放大器电路的详细的结构的例子的图。

图10是表示在本发明的实施方式1的半导体装置中包含的图1中的改写驱动器的详细的结构的例子的图。

图11是表示在本发明的实施方式1的半导体装置中图10中记载的改写驱动器中的复位的存储层与复位电流的关系的图。

图12是表示在本发明的实施方式1的半导体装置中阵列电压VARY的每个动作的设定的图。

图13是表示在本发明的实施方式1的半导体装置中包含的相变存储器的初始化动作的例子的图。

图14是表示在本发明的实施方式1的半导体装置中图13中记载的相变存储器的初始化动作中的内部动作的例子的图。

图15是表示在本发明的实施方式1的半导体装置中包含的相变存储器的写入动作的例子的图。

图16是表示在本发明的实施方式1的半导体装置中图15中记载的相变存储器的写入动作中的内部动作的例子的图。

图17是表示在本发明的实施方式1的半导体装置中包含的相变存储器的读出动作的例子的图。

图18是表示在本发明的实施方式1的半导体装置中图17中记载的相变存储器的读出动作中的内部动作的例子的图。

图19是表示在本发明的实施方式2的半导体装置中包含的图1中的改写驱动器的详细的结构的例子的图。

图20是表示在本发明的实施方式2的半导体装置中图19中记载的改写驱动器中的复位的存储层与复位电流的关系的图。

图21是表示在本发明的实施方式3的半导体装置中包含的相变存储器的主要部分电路块的结构例的图。

图22是表示在本发明的实施方式3的半导体装置中图21中记载的电路块中的地址变换电路的结构例的图。

图23是表示在本发明的实施方式3的半导体装置中图22中记载的地址变换电路中的地址变换表的图。

图24是表示在本发明的实施方式3的半导体装置中图22中记载的多路转换器的功能的图。

图25是表示在本发明的实施方式4的半导体装置中用于确认其中包含的相变存储器的各存储层的可否使用的读出动作中的流程的图。

图26是表示在本发明的实施方式4的半导体装置中包含的相变存储器的读出动作的变形例的图。

图27是表示在本发明的实施方式4的半导体装置中输入指令与芯片内部信号的对应的例子的图。

图28是表示在本发明的实施方式4的半导体装置中包含的相变存储器的器件ID读出动作的例子的图。

图29是表示在本发明的实施方式4的半导体装置中器件ID的内容的例子的图。

图30是表示在本发明的实施方式5的半导体装置中其主要部分块的结构的例子的图。

图31是表示在本发明的实施方式6的半导体装置中其主要部分块的结构的例子的图。

图32是表示在本发明的实施方式7的半导体装置中包含的图1中的改写驱动器的详细的结构的例子的图。

图33是表示在本发明的实施方式7的半导体装置中图32中记载的改写驱动器中的复位的存储层与复位电流的关系的图。

图34是表示在本发明的实施方式7的半导体装置中图22中记载的相变存储器的写入动作中的内部动作的例子的图。

图35是表示在本发明的实施方式8的半导体装置中包含的相变存储器的主要部分块的结构的例子的图。

图36是表示在本发明的实施方式8的半导体装置中阵列电压VARY的设定和图35中记载的电压选择电路的功能的图。

(符号说明)

PCM、PCM0~PCM3 相变存储器

PL0~PL3 存储器平面

MA 存储器阵列

YDEC 列解码器

XDEC1、XDEC2、XDEC3 行解码器

D[16895:0]、D0T/B~D16895T/B 数据线对

IA[30:0] 地址信号

PA0[28:27]、PA0[26:24]、PA0[23:21]、 内部地址信号

CA[28:27]、IA[28:27]

WL[4095:0] 字线

BS[7:0] 位线选择线

LS7T、LS7B)~(LS0T、LS0B) 选择线

CTL1~CTL4 控制信号组

INITV[3:0] 初始化电压

VARY、V0、V1、V2、V3 阵列电压

IO[7:0] 输入输出线

CLE 指令锁存起动信号

ALE 地址锁存起动信号

CEB 芯片起动信号

REB 读出起动信号

WEB 写入起动信号

WPB 写入保护信号

RBB 准备就绪/忙信号

PS[3:0] 存储器平面选择信号

SM0~SM16895 子存储器阵列

MUXB1、MUXB2、MB10~MB116895 多路转换器组

MB00~MB(212-1)7 层叠存储器单元组

R 相变电阻元件

D 存储器单元选择用二极管

MC1~MC4 存储器单元

MUX、MUX10~MUX17、 多路转换器

MUX20~MUX216895

LB001~LB004 局部位线

BL00~BL1168958 位

CD0~CD116895 共同数据线

RW0~RW16895 读写电路

SA 读出放大器

WD 改写驱动器

100 P型硅衬底

101 P阱区

103 多晶硅层

104 N+扩散层区域

105 元素分离用氧化物

201~204、211~214、500~501 钨层

600 相间绝缘膜

301、302、303、304 接点

400 PN二极管的P层

401 PN二极管的N层

402 硫族化合物材料层

SA 读出放大器

PCC 预充电电路

CCL 交叉耦合型锁存放大器

RG 传输门

DLEQ 数据线均衡信号

CSP、CSN 共同源线

RGE1、RGE2 传输门起动信号

VDD 电源电压

VPP 升压电压

VDR 基准电压

VSS 接地电压

VREF 参考电压

VBIAS0、VBIAS1 偏置电压

MN70、MN71、MN72、MN73 NMOS晶体管

MP700、MP701、MP710、MP711、MP710、 PMOS晶体管

MP722、MP723、MP724、MP725、MP726

INT_EN 初始化起动信号

IV700、IV730~733 倒相器电路

Ice11、Iint、Iset、Irst 存储单元电流

SET_EN 置位起动信号

ND70、ND71、ND720、ND721、 二输入NAND电路

ND730~ND733

INIT_EN 初始化起动信号

SET_EN 置位起动信号

RST_EN、RST_EN0~RST_EN3 置位起动信号

IN1、IN2 初始化指令信号

CA1、CA2 列地址

RA1、RA2、RA3 行地址

PRG1、PRG2 写入指令信号

RD1、RD2 读出指令信号

IV720、IV721 倒相器电路

AE 地址变换电路

AEL 地址变换逻辑电路

INIT 初始化模式信号

TEST 测试模式信号

NORM 通常动作模式信号

RLS1、RLS2 存储层可否使用确认指令

信号

RLS 存储层确认模式信号

RID 器件ID读出指令信号

NVCTL 非易失存储器控制芯片

SBUS 系统总线

NR730 四输入NOR电路

PAD_V0~PAD_V3 焊区

VGEN 芯片内部电源发生电路

VSEL 电压选择电路

具体实施方式

以下,根据附图详细地说明本发明的实施方式。再有,在用于说明实施方式的全部的图中,对于同一构件原则上附加同一符号,省略其重复的说明。此外,构成实施方式的各功能块的电路元件不作特别限定,可利用众所周知的CMOS(互补型MOS晶体管)等的集成电路技术在单晶硅那样的半导体衬底上形成。

再有,在实施方式中,作为MISFET(金属绝缘体半导体场效应晶体管)的一例,使用MOS(金属氧化物半导体)晶体管。在附图中,通过在P沟道型MOS晶体管(PMOS晶体管)中对栅极附加箭头的记号,与N沟道型MOS晶体管(NMOS晶体管)加以区别。在附图中未特别明确地记述MOS晶体管的衬底电位的连接,但只要是MOS晶体管可正常地动作的范围,其连接方法就不作特别限定。

(实施方式1)

本实施例提供可根据所选择的存储单元所处的层来变更初始化条件和改写条件的相变存储器。

首先,按照图1至图4,说明本发明的相变存储器。本发明的相变存储器是隔着绝缘层层叠了由硫族化合物材料构成的记录层和单元选择用的二极管构成的存储单元的结构。

《层叠相变存储器的整体结构》

图1是表示在本发明的实施方式1的半导体装置中相变存储器的主要部分结构例的电路框图。在该图中,作为一例,表示了由2Gbit的存储器平面PL0~PL3构成的8Gbit的情况的结构。各存储器平面由存储器阵列MA、读出放大器及改写驱动器(S/A & Write Driver)、列选择门(Y-Gating)、列解码器YDEC、第一行解码器XDEC1、第二行解码器XDEC2和第三行解码器XDEC3构成。存储器阵列MA如前面所述那样,是将由硫族化合物材料构成的记录层和单元选择的二极管构成的存储单元配置成三维矩阵状的结构。读出放大器及改写驱动器是进行来自存储器阵列的存储信息的读出和对存储器阵列的存储信息的写入动作的电路块。列选择门(Y-Gating)是经16896{=(214+29)-1}条数据线对D[16895:0]连接到读出放大器及改写驱动器上、同时经平面数据总线PDBUS连接到输入输出线缓冲器组和锁存器电路组(I/O Buffers & Latches)上以进行存储信息的收发的电路块。

以下着眼于存储器平面PL0说明各解码器的动作。列解码器YDEC是在连接上述的读出放大器及改写驱动器与输入输出线缓冲器组和锁存器电路组的列选择门中用于选择激活的门的电路块。第一至第三行解码器XDEC1~XDEC3是进行激活的存储单元的选择的电路块。第一行解码器是根据分配给存储器平面PL0用的内部地址PA0[23:12]从4095(212-1)条字线WL[4095:0]选择一条并将其激活的电路块。第二行解码器是根据分配给存储器平面PL0用的内部地址PA0[26:24]从8条位线选择线BS[7:0]选择一条并将其激活的电路块。第三行解码器是根据分配给存储器平面PL0用的内部地址PA0[28:27]从4对层选择线(LS7T、LS7B)~(LS0T、LS0B)选择一对并将其激活的电路块。

阵列电压VARY是从相变存储器PCM的外部供给第一行解码器XDEC1和改写驱动器WD的电压。此处,如后述的图12中表示的那样来控制阵列电压。即,在进行初始化动作的情况下,在设定为V0~V3的某一个以使在各自的层中成为最佳的电压之后,进行读出或改写动作的情况下,在无论哪个层都常时设定为VDD,然后供给第一行解码器XDEC1和改写驱动器。

在此,阵列电压VARY具有在初始化动作中对每层供给最佳的初始化电压的这一特征。

这样,利用对第一行解码器XDEC1供给在每层中进行了控制的阵列电压VARY的结构,按照因电特性的差异在每层中具有离散的电阻值,可在每层以最佳的电压进行存储单元的初始化动作。在此,如后述的实施方式7中所示,也可在内部设置电源发生电路来生成为了初始化使用的电压。但是,由于用出厂时的测试等进行一次初始化动作就足够了,故可不在内部设置电源发生电路,而是从外部供给。通过从外部供给电源,可防止因内部电源电路导致的芯片面积的增大。

此外,利用对改写驱动器WD供给对每层进行了控制的阵列电压VARY的结构,可将在初始化动作时流过存储单元的电流量Iint控制为适当的值,能以更高的精度进行初始化动作。

其次,说明周边电路块。用本发明的相变存储器处理的存储信息、指令信号、地址信号分别从输入输出线IO[7:0]经全局缓冲器(GlobalBuffer)或输出驱动器(Output Driver)来收发。利用控制信号组CTL1控制全局缓冲器(Global Buffer)。进而经对应的全局总线GBUS1或全局总线GBUS2在全局缓冲器(Global Buffer)或输出驱动器(Output Driver)与输入输出线缓冲器组和锁存器电路组(I/OBuffers&Latches)之间传送存储信息。利用控制信号组CTL2控制输入输出线缓冲器组和锁存器电路组(I/O Buffers & Latches)。从全局缓冲器(Global Buffer)经芯片内部总线IBUS对指令寄存器和控制逻辑电路(Command Resister & Control Logic)传送指令信号。同样经IBUS对地址缓冲器组和锁存器组传送地址信号IA[30:0]。具体地说,将地址信号IA[11:0]传送给列地址缓冲器组和锁存器组(Y-Buffers & Latches)。将地址信号IA[30:12]传送给行地址缓冲器组和锁存器组(X-Buffers & Latches)。

指令寄存器和控制逻辑电路(Command Resister & ControlLogic)进而按照从行地址缓冲器组和锁存器组(X-Buffers & Latches)输出的存储器平面选择信号PS[3:0]和多个控制信号,将控制信号组CTL1~CTL4分配给相变存储器的各块。多个控制信号具体地说是指令锁存起动信号CLE、地址锁存起动信号ALE、芯片起动信号CEB、读出起动信号REB、写入起动信号WEB、写入保护信号WPB、准备就绪/忙信号RBB。指令锁存起动信号CLE是用于激活暂时地存储指令信号的上述的指令寄存器的信号。地址锁存起动信号ALE是用于激活暂时地存储地址信号的上述的地址缓冲器组和锁存器组的信号。芯片起动信号CEB是用于选择相变存储器芯片的信号。读出起动信号REB是用于一边在芯片内部发生列地址一边激活上述的输出驱动器来输出存储信息的信号。写入起动信号WEB是用于接收存储信息、指令信号、地址信号的信号。写入保护信号WPB是用于防止电源启动时的未考虑的写入动作的信号。准备就绪/忙信号RBB是通知芯片内部的状态是否在读出动作或写入动作之中的信号。

列地址缓冲器组和锁存器组(Y-Buffers & Latches)是用于按照控制信号组CTL3和存储器平面选择信号PS[3:0]将地址信号IA[11:0]传送给存储器平面PL0~PL3的电路块。例如,在激活了存储器平面控制信号PS0的情况下,内部地址信号PA0[11:0]被激活。通过将内部地址信号有选择地分配给激活的存储器平面,可抑制信号线的驱动中需要的功耗。

行地址缓冲器组和锁存器组(X-Buffers & Latches)是用于按照存储器平面选择信号PS[3:0]将地址信号IA[30:12]传送给存储器平面PL0~PL3的电路块。利用与内部地址信号PA0[11:0]同样地按照内部地址信号PA[30:29]发生的存储器平面控制信号PS0~PS3来选择传送目的地的存储器平面。

《存储器阵列的结构》

图3是表示图1中表示的存储器阵列MA的详细的结构例的图通过如该图那样构成存储器阵列MA,利用层叠了由使用硫族化合物材料的存储层和二极管构成的存储单元的结构,可提高存储单元的集成度。以下说明其详细的情况。

以下将用一次读出动作或写入动作进行存取的存储单元的单位称为页。图3的存储器阵列MA具有131072(=217)个页。各自的页由2k字节的主区和64字节的备用区构成,若将其合计,则是2112k字节的规模。以下详细地说明这样的特征的存储器阵列MA。

存储器阵列MA由16896(=214+29)个子存储器阵列SM0~SM16895和第一多路转换器组MUXB1、第二多路转换器组MUXB2构成。子存储器阵列SM0~SM16895分别例如像子存储器阵列SM0那样由在4096=(212)条字线WL0~WL4095(=WL(212-1))和8组局部位线对(LB001~LB004)~(LB071~LB074)的各交点处配置的层叠存储单元组MB00~MB(212-1)7构成。层叠存储单元组MB00~MB(212-1)7分别用在对应的位线与字线之间串联连接了使用硫族化合物材料的具有记录层的功能的相变电阻元件R与存储单元选择用的二极管D的存储单元MC1~MC4构成。

第一多路转换器组MUXB1由与16896(=214+29)个子存储器阵列SM0~SM16895对应的多路转换器组MB10~MB116895构成。多路转换器组MB10~MB116895分别是例如像多路转换器组MB10内的多路转换器MUX10那样,按照存储层选择信号LS[3:0]从4条局部位线LB001~LB004选择一条连接到位BL00上的电路。

第二多路转换器组MUXB2由与16896(=214+29)个子存储器阵列SM0~SM16895对应的多路转换器MUX20~MUX216895构成。多路转换器MUX20~MUX216895分别是例如像多路转换器MUX20那样,按照位线选择信号BS[7:0]从8条局部位线BL00~BL07选择一条连接到共同数据线CD0上的电路。

在图3中也记载了读出放大器及改写驱动器(S/A & WriteDriver)。读出放大器及改写驱动器(S/A & Write Driver)由与16896(=214+29)个子存储器阵列SM0~SM16895对应的读写电路RW0~RW16895构成。读写电路RW0~RW16895分别例如像读写电路RW0那样,配置在共同数据线CD0与数据线对D0T/B之间。读写电路RW0由读出放大器SA和改写驱动器WD构成。

在图3中,在层叠存储单元组MB00~MB(212-1)7内,关于第1层的存储单元MC1至第4层的存储单元MC4,在各自的每个存储单元中设置了位线,字线从存储单元MC1至MC4汇总地利用同一布线进行短路。该结构与本实施例相反,即使在各自的每个存储单元中设置了字线并汇总地利用同一布线设置位线也能实现同样的结构。但是,由于多条字线分别与行解码器XDEC1内的选择电路连接,故关于其每一个分别连接面积大的PMOS。因此,通过将多条字线汇总而可抑制PMOS的数量的本实施例在能抑制电路面积的增大这一点上是更有效的。

图4表示图3中表示的层叠存储单元组和第一多路转换器组的剖面结构。在该图中,作为一例,表示了连接到局部位线对LB001~LB004上的层叠存储单元组MB00~MB(212-1)0和多路转换器MUX10。本实施方式的层叠存储单元组的特征在于堆叠了四个图3中表示的存储单元MC1~MC4。

在P型硅衬底100上形成的P阱区101内形成层叠存储单元组MB00~MB(212-1)0和多路转换器MUX10。103是多路转换器MUX10具有的NMOS晶体管的成为栅电极的多晶硅层。括号内的记号是存储层选择信号LS[3:0]。104是NMOS晶体管的成为源电极或漏电极的N+扩散层区域。105是用于隔断晶体管间的通电的元件分离用的氧化物。

201~204是成为局部位线LB001~LB004的第一~第四钨层。211~214是成为字线的第五~第八钨层。字线如WL0那样,在层叠存储单元组内共有,第五~第八钨层在纸面上未呈现的位置上短路。用相间绝缘膜600使这些第一~第八钨层互相分离。

301是用于连接第一钨层与N+扩散层的第一接点。302是用于连接第二钨层与第一钨层的第二接点。303是用于连接第三钨层与第二钨层的第三接点。304是用于连接第四钨层与第三钨层的第四接点。

例如像层叠存储单元组MB00内的存储单元MC1那样,在成为局部位线LB001的钨层(在此是201)与成为字线WL0的钨层(在此是211)之间将存储单元形成为柱状。400是PN二极管的P层,401是PN二极管的N层,402是硫族化合物材料层。此外,500是PN二极管与硫族化合物材料层之间的成为缓冲层的第九钨层,501是硫族化合物材料层与局部位线之间的成为缓冲层的第十钨层。在此,存储单元也可以是具有选择晶体管和硫族化合物材料层并将字线连接到选择晶体管的栅上的结构。但是,利用如本实施例那样具有二极管和硫族化合物材料层的结构,可进一步提高存储单元的集成度。

《存储器映射图》

其次,说明本实施方式的相变存储器的存储器映射图。图5是表示本存储器映射图的概略的图。存储器平面PL0~PL3分别具有以下特征,如存储器平面PL0那样由4个主块(Main block0、Main block4、Main block8、Main block12)构成。这些主块与层叠了的存储器阵列对应,例如,主块0是第一层的存储器阵列,主块4是第二层的存储器阵列,主块8是第三层的存储器阵列,主块12是第四层的存储器阵列。主块(Main block0~Main block12)分别例如像主块0那样,由512个块(block0~block511)构成。再者,块(block0~block511)分别像block0那样,由64个页(Page0~Page63)构成。

图6是表示图5中记载的页结构的图。页由2048(=211)字节的主区和64(=28)字节的备用区构成。主区进而用由512字节构成的4个区域(A区~D区或第一扇区~第四扇区)构成。此外,备用区用由16字节构成的4个区域(E区~H区或第五扇区~第八扇区)构成。在主区中写入存储信息,在备用区中写入1位纠错码。按照这样的页结构,图3中表示的存储器阵列由16896(=214+29)个子存储器阵列构成。此外,读出放大器及改写驱动器(S/A & Write Driver)由16896(=214+29)对读出放大器和改写驱动器构成。

图7是表示列地址的分配的图。用列地址0~2047来指定主区。此外,用列地址2048~2111来指定备用区。由图1中表示的地址信号IA[11:0]发生这些列地址。因而,虽然详细的情况在后面叙述,但将从存储器阵列MA一度读出的16896(=214+29)位的存储信息一次性地存储在读出放大器中,按照数据线选择线DS[2111:0]从列门(Y-Gating)一个字节一个字节地输出。相反,经列门(Y-Gating)将存储信息一个字节一个字节地存储在改写驱动器中,在16896(=214+29)位备齐时一举写入到存储器阵列MA中。

图8是表示行地址的分配的图。由图1中表示的地址信号IA[30:12]发生行地址。利用地址信号IA[30:29]发生存储器平面选择信号PS[3:0]。利用地址信号IA[28:27]发生存储层选择信号LS[3:0]。利用地址信号IA[26:12]发生用于选择页的字线WL0~WL(212-1)和位线选择线BS[7:0]。

《读出放大器和改写驱动器的结构》

以下说明读出放大器及改写驱动器(S/A & Write Driver)的具体的结构例。图9作为一例表示了读写电路RW0。首先,读出放大器SA是由预充电电路PCC、交叉耦合型锁存放大器CCL、传输门RG构成的众所周知的电路结构。

预充电电路PCC由3个NMOS晶体管构成,通过在待机时将数据线均衡信号DLEQ驱动为比电源电压VDD高的升压电压VPP而被激活,将数据线对D0T、D0B驱动为基准电压VDR(在此,例如是VDD/2)。

交叉耦合型锁存放大器CCL由2个PMOS晶体管和2个NMOS晶体管构成。在待机时将共同源线CSP、CSN驱动为与数据线对D0T、D0B相同的预充电电压(在此,是基准电压VDR)。另一方面,在读出动作中,如果在数据线对D0T中发生与所选择的存储单元存储的信息对应的信号,则通过将共同源线CSP驱动为电源电压VDD,将共同源线CSN驱动为接地电压VSS而被激活,放大在数据线对D0T、D0B中发生了的微小信号。

传输门RG由在交叉耦合型锁存放大器与存储单元阵列之间插入的2个NMOS晶体管构成。在读出动作中,通过将传输门起动信号RGE1、RGE2驱动为升压电压VPP而被激活,连接共同数据线CD0和参考电压VREF(在此,例如是VDD/2)与交叉耦合型锁存放大器,将从选择存储单元读出的信号传送给交叉耦合型锁存放大器。再有,数据线均衡信号DLEQ、共同源线CSP、CSN、传输门起动信号RGE1、RGE2是控制信号组CTL4的构成要素。

图10表示了改写驱动器WD0的结构。该改写驱动器的特征在于:按照存储层选择信号LS1B~LS3B控制在复位时流过存储单元的电流Irst并在每层中使改写条件变化。利用该结构,在使存储单元成为高电阻状态的复位动作中,可按照每层的电特性的差异,在每层中将电阻值控制为所希望的值,可实现高可靠性的相变存储器。

该改写驱动器的基本结构是由NMOS晶体管MN70、MN71、MN72、MN73构成的三个电流镜电路,具有以下的二个特征。第一个特征在于按照动作来激活电流镜电路。第二个特征在于按照动作模式来控制所供给的阵列电压VARY的电压值。

首先,说明电流镜电路的结构。第一电流镜电路由晶体管MN70和MN73的组合来构成。在晶体管MN70与阵列电压VARY之间串联地插入PMOS晶体管MP700、MP701。对晶体管MP700的栅输入偏置电压VBIAS0。此外,对晶体管MP701的栅输入用倒相器电路IV700使初始化起动信号INT_EN反相了的信号。利用这样的结构,将经共同数据线CD0施加的存储单元电流Icell设定为在初始化动作中必要的值Iint。

这样,第一电流镜电路的特征在于:不依赖于存储层选择信号LS1B~LS3B地控制存储单元的初始化电流。这是由于,在初始化中通过控制阵列电压VARY而在每层中控制初始化电压,可用最佳的条件进行初始化动作。因此,因不设置按照存储层选择信号进行每层的控制的电路,故可减少电路面积。

第二电流镜电路由晶体管MN71和MN73的组合来构成。在晶体管MN71与阵列电压VARY之间串联地插入PMOS晶体管MP710、MP711。对晶体管MP710的栅输入偏置电压VBIAS1。此外,对晶体管MP711的栅输入被输入了置位起动信号SET_EN和数据线D0T的二输入NAND电路ND70的输出信号。利用这样的结构,在使存储单元成为低电阻状态即写入存储信息“1”的情况下,将经共同数据线CD0施加的存储单元电流Icell控制为在置位动作中必要的值Iset。

这样,第二电流镜电路的特征也在于:与第一电流镜电路同样地不依赖于存储层选择信号LS1B~LS3B地控制存储单元的置位电流Iset的。这是由于,利用后述的第三电流镜电路将复位电阻控制为适当的值,因此,没有必要在置位动作中按照存储层选择信号进行每层的控制。因此,可简化电路结构,可减少电路面积。

但是,在上述第一电流镜电路和第二电流镜电路中,也可设置进行每层的控制的电路。

第三电流镜电路由晶体管MN72和MN73的组合来构成。在晶体管MN72与阵列电压VARY之间串并联地插入PMOS晶体管MP720、MP722、MP723、MP724、MP721。在此,并联的晶体管的栅宽度设定为按晶体管MP720、MP722、MP723、MP724的顺序逐步变宽。对晶体管MP720的栅输入接地电压VSS。此外,分别对晶体管MP722、MP723、MP724的栅输入存储层选择信号LS1T~LS3T的反相信号LS1B~LS3B。再者,对晶体管MP721的栅输入被输入了复位起动信号RST_EN和数据线D0B的二输入NAND电路ND71的输出信号。利用这样的结构,在使存储单元成为高电阻状态、即写入存储信息“0”的情况下,将经共同数据线CD0施加的存储单元电流Icell控制为如图11中所示那样与所选择的存储层对应的值Irst。具体地说,在对第一存储层(最下层)的存储单元进行写入动作的情况下,通过使晶体管MP720导通,将复位电流Irst设定为Irst0。在对第二存储层的存储单元进行写入动作的情况下,通过晶体管MP720、MP722分别导通,将复位电流Irst设定为(m+1)×Irst0。在对第三存储层的存储单元进行写入动作的情况下,通过晶体管MP720、MP723分别导通,将复位电流Irst设定为(k+1)×Irst0。在对第四存储层的(最上层)存储单元进行写入动作的情况下,通过使晶体管MP720、MP724分别导通,将复位电流Irst设定为(j+1)×Irst0。在此,将系数m、k、j设定为m<k<j的关系。于是,通过对越往上的层的存储阵列施加越大的电流以进行复位动作,能可靠地将各层的存储单元的电阻值控制为所希望的电阻值。再有,将复位电流Irst设定为比置位电流Iset大的值。此外,初始化起动信号INIT_EN、置位起动信号SET_EN、复位起动信号RST_EN分别是控制信号组CTL4的构成要素。

如以上所述,第三电流镜电路的特征在于:使栅宽度不同的晶体管MP720、MP722、MP723、MP724并联,按照存储层选择信号选择导通的晶体管。利用这样的结构,可对各自的层供给最佳的复位电流。

再有,由于晶体管MP720为导通状态,故可将其去掉。但是,因设置晶体管MP720,具有能设计成为进行第一存储层的复位动作时的基础的电流这样的优点。

其次,说明对改写驱动器WD和第一行解码器XDEC供给的阵列电压VARY的电压值。图12表示了各个动作的阵列电压VARY的设定。在初始化动作的情况下,施加与选择单元所处的存储层对应的值的阵列电压VARY。

具体地说,在对第一存储层(最下层)的存储单元进行初始化的情况下,供给的阵列电压VARY为第一电压V0。以下同样地,在对第二存储层的存储单元进行初始化的情况下,供给的阵列电压VARY为比第一电压V0高的第二电压V1。在对第三存储层的存储单元进行初始化的情况下,供给的阵列电压VARY为比第二电压V1高的第三电压V2。在对第四存储层(最高层)的存储单元进行初始化的情况下,供给的阵列电压VARY为比第三电压V2高的第四电压V3。以上的电压具有以下那样的关系。

VDD≧V3>V2>V1>V0...(式1)

这样,通过供给对每层为最佳的电压来进行初始化动作,可防止因对存储层的过度的应力的施加引起的电特性的劣化,可实现高可靠的相变存储器。

再有,在读出动作或改写动作中,将阵列电压VARY设定为电源电压VDD。这是由于,从相变存储器PCM的外部供给阵列电压,在内部未设置电压发生电路。但是,在读出动作中,由于存储单元的状态不会改写,故不需要阵列电压VARY的控制。此外,在改写动作中,由于可利用图10中表示的改写驱动器进行最佳的条件下的复位动作和置位动作,故利用图12中表示的阵列电压的控制可在所有的动作中对每层提供最佳的条件。

《初始化动作》

以下说明迄今为止说明的本实施方式的相变存储器中的动作。图13表示了初始化动作的例子。将成为接地电压VSS的指令锁存起动信号CLE驱动为高电平,将成为高电平的芯片起动信号CEB和地址锁存起动信号ALE驱动为低电平。其后,如果经输入输出线I/Ox(x=0~7)输入第一初始化指令信号IN1,则利用写入起动信号WEB的上升边,在相变存储器芯片中取入第一初始化指令信号IN1。其次,将成为高电平的指令锁存起动信号CLE驱动为低电平,将成为低电平的地址锁存起动信号ALE驱动为高电平,输入列地址和行地址。在此,由于列地址如图7中所示有0~2111个地址,故需要12位。另一方面,输入地址的I/O引脚如图7中所示只有8条,故将12位的列地址分成2次(CA1,CA2)按顺序输入。同样,由于行地址如图8中所示需要19位,故分成3次(RA1,RA2,RA3)按顺序输入。利用写入起动信号WEB的上升边将这些地址取入到相变存储器芯片中,在芯片内部依次进行地址的解码。再者,将成为高电平的地址锁存起动信号ALE驱动为低电平,将成为低电平的指令锁存起动信号CLE驱动为高电平,对输入输出线I/Ox(x=0~7)输入第二初始化指令信号IN2。利用写入起动信号WEB的上升边,在相变存储器芯片中取入该第二初始化指令信号IN2,进行初始化动作。再有,在初始化动作中,将成为高电平的准备就绪/忙信号RBB驱动为低电平。

图14是表示在本实施方式的相变存储器的初始化动作中的芯片内部动作的例子的图。在该图中,表示了在图3中表示的存储器阵列MA中包含的子存储器阵列SMA0~SMA16895中对处于层叠存储单元组MB00的最下层的存储单元MC1进行初始化的情况的动作波形。为了简化说明,省略了第一多路转换器组MUXB1和第二多路转换器组MUXB2的动作波形,但通过按照如图13所示的第二初始化指令信号IN2激活存储层选择信号LS0和位线选择信号BS0,分别连接局部位线LS001、LS101、...、LS1689501与共同数据线CD0、CD1、...、CD16895。其次,如果将成为接地电压VSS的初始化起动信号INIT_EN驱动为电源电压VDD,将成为接地电压VSS的字线WL0驱动为第一阵列电压V0,则对于对应的局部位线LB001、LB101、...、LB1689501施加初始化电流Iint,进行初始化动作。再有,根据上述的图12,可容易地理解对字线施加的阵列电压按照所选择的存储单元所属的存储层成为V0~V3中的某一个电压值。

《写入动作》

图15表示了写入动作的例子。将成为低电平的指令锁存起动信号CLE驱动为高电平,将成为高电平的芯片起动信号CEB和地址锁存起动信号ALE驱动为低电平。其后,如果经输入输出线I/Ox(x=0~7)输入第一写入指令信号PRG1,则利用写入起动信号WEB的上升边,在相变存储器芯片中取入第一写入指令信号PRG1。其次,将成为高电平的指令锁存起动信号CLE驱动为低电平,将成为低电平的地址锁存起动信号ALE驱动为高电平,分成2次(CA1,CA2)按顺序输入列地址,分成3次(RA1,RA2,RA3)按顺序输入行地址。利用写入起动信号WEB的上升边将这些地址取入到相变存储器芯片中,在芯片内部依次进行地址的解码。再者,将成为高电平的地址锁存起动信号ALE驱动为低电平,经输入输出线I/Ox(x=0~7)输入存储信息Din(N)~Din(M)。接着,将成为低电平的指令锁存起动信号CLE驱动为高电平,对输入输出线I/Ox(x=0~7)输入第二改写指令信号PRG2。利用写入起动信号WEB的上升边,在相变存储器芯片中取入该第二改写指令信号PRG2,进行改写动作。再有,在改写动作中,将成为高电平的准备就绪/忙信号RBB驱动为低电平。在结束改写动作将成为低电平的准备就绪/忙信号RBB驱动为高电平之后,输入状态读出指令信号RDS。利用写入起动信号WEB的上升边,在芯片内部取入状态读出指令信号RDS。再者,与读出起动信号RDB同步地从输入输出线I/Ox(x=0~7)输出写入后的状态RIO0。

图16是表示在本实施方式的相变存储器的改写动作中的芯片内部动作的例子的图。在该图中,表示了在图3表示的存储器阵列MA中包含的子存储器阵列SMA0~SMA16895中对处于层叠存储单元组MB00的最下层的存储单元MC1写入存储信息的情况的动作波形。通过按照图15表示的第二改写指令信号PRG2将成为升压电压VPP的数据线均衡信号DLEQ驱动为接地电压VSS,将成为基准电压VDR的共同源线CSP、CSN分别驱动为电源电压VDD、接地电压VSS,在读写电路RW0~RW16895内的读出放大器SA中暂时地存储经数据线D0T~D16895T输入了的存储信息。此外,为了简化说明,省略了第一多路转换器组MUXB1和第二多路转换器组MUXB2的动作波形,但通过激活存储层选择信号LS0和位线选择信号BS0,分别连接局部位线LS001、LS101、...LS1689501与共同数据线CD0、CD1、...CD16895。接着,如果将复位起动信号RST_EN、置位起动信号SET_EN分别驱动为电源电压VDD,将成为接地电压VSS的字线WL0驱动为阵列电压VARY(在此是电源电压VDD),则按照对应的读出放大器中存储了的存储信息对局部位线LB001、LB101、...LB1689501施加复位电流Irst或置位电流Iset,进行改写动作。再有,将置位起动信号SET_EN的脉冲宽度设定为比复位起动信号RST_EN充分地大,以使存储层充分地结晶化,降低其电阻值。最后,通过将成为电源电压VDD的共同源线CSP、成为接地电压VSS的共同源线CSN分别驱动为基准电压VDR,将成为接地电压VSS的数据线均衡信号DLEQ驱动为升压电压VPP,回复到待机状态。

《读出动作》

图17表示了读出动作的例子。将成为低电平的指令锁存起动信号CLE驱动为高电平,将成为高电平的芯片起动信号CEB和地址锁存起动信号ALE驱动为低电平。其后,如果经输入输出线I/Ox(x=0~7)输入第一读出指令信号RD1,则利用写入起动信号WEB的上升边,在相变存储器芯片中取入第一读出指令信号RD1。其次,将成为高电平的指令锁存起动信号CLE驱动为低电平,将成为低电平的地址锁存起动信号ALE驱动为高电平,分成2次(CA1,CA2)按顺序输入列地址,分成3次(RA1,RA2,RA3)按顺序输入行地址。利用写入起动信号WEB的上升边将这些地址取入到相变存储器芯片中,在芯片内部依次进行地址的解码。再者,将成为高电平的地址锁存起动信号ALE驱动为低电平,将成为低电平的指令锁存起动信号CLE驱动为高电平,对输入输出线I/Ox(x=0~7)输入第二读出指令信号RD2。利用写入起动信号WEB的上升边,在相变存储器芯片中取入该第二读出指令信号RD2,进行读出动作。再有,在读出动作中,将成为高电平的准备就绪/忙信号RBB驱动为低电平,将从存储器阵列读出的存储信息传送到芯片内部,将成为低电平的准备就绪/忙信号RBB驱动为高电平之后,与读出起动信号REB的上升边同步地按Dout(N)~Dout(M)的顺序输出。

图18是表示在本实施方式的相变存储器的读出动作中的芯片内部动作的例子的图。在该图中,表示了在图3表示的存储器阵列MA中包含的子存储器阵列SMA0~SMA16895中从处于层叠存储单元组MB00的最下层的存储单元MC1读出存储信息的情况的动作波形。为了简化说明,省略了第一多路转换器组MUXB1和第二多路转换器组MUXB2的动作波形,但通过按照图13中表示的第二读出指令信号RD2激活存储层选择信号LS0和位线选择信号BS0,分别连接局部位线LS001、LS101、...、LS1689501与共同数据线CD0、CD1、...、CD16895。其次,将成为接地电压VSS的传输门起动信号RGE1驱动为升压电压VPP,分别将局部位线LS001、LS101、...、LS1689501驱动为接地电压VSS。此外,将成为升压电压VPP的数据线均衡信号DLEQ驱动为接地电压VSS,将成为接地电压VSS的传输门起动信号RGE2驱动为升压电压VPP,将数据线D0B、D1B、D16895B驱动为参考电压VREF。接着,通过将成为接地电压VSS的字线驱动为阵列电压VARY(在此是电源电压VDD),将局部位线和数据线驱动为与存储信息对应的电压。例如,在局部位线LB001上的存储单元存储了信息“1”而处于低电阻状态的情况下,对局部位线LB001和数据线D0T进行充电。另一方面,在如局部位线LB101上的存储单元那样存储了信息“0”而处于高电阻状态的情况下,将局部位线LB101和数据线D1T大致保持为接地电压VSS。其后,如读出了存储信息“1”的局部位线LB001和数据线D0T那样,在这些电压高于参考电压VREF的时刻,分别将成为基准电压VDR的共同源线CSP、CSN驱动为电源电压VDD、接地电压VSS,放大读出了的信号。再者,将成为电源电压VDD的字线WL0驱动为接地电压VSS,将成为升压电压VPP的传输门起动信号RGE1、RGE2驱动为接地电压VSS,通过隔断共同数据线CD0、CD1、...、CD16895与数据线D0T、D1T、...、D16895T,避免因过度的电压施加引起的数据破坏。最后,通过将成为电源电压VDD的共同源线CSP、成为接地电压VSS的共同源线CSN分别驱动为基准电压VDR,将成为升压电压VPP的数据线均衡信号DLEQ驱动为接地电压VSS,回复到待机状态。

根据以上的结构和动作,可得到以下两个效果。第一个效果在于,如图4中所示,通过作成层叠了由使用硫族化合物材料的存储层和二极管的存储单元的结构,可提高相变存储器芯片的集成度。第二个效果在于,按照所选择的存储单元所处的层来变更初始化条件和改写条件。具体地说,如图10中所示,按照动作来选择电流镜电路,同时利用图12中表示的电压设定和电流镜电路中的复位电流Irst的控制机构,可按照动作来变更初始化条件和改写条件(在此是复位条件)。利用这样的机构,可防止在初始化动作中因对存储层的过度的应力的施加引起的电特性的劣化。此外,在使存储单元成为高电阻状态的复位动作中,可将电阻值控制为所希望的值。于是,可实现高可靠动作的相变存储器。

再有,在本实施方式中,说明了堆叠4层存储单元的情况,但层叠的层数不限于此,可以是2层,也可以是8层。即使在这样的情况下,通过按照所选择的存储层控制动作条件,也可得到同样的效果。

(实施方式2)

在本实施方式2中,说明图10中表示的改写驱动器WD的另外的结构。图19表示了本实施方式中的改写驱动器WD的结构例。该改写电路与图10中表示的改写电路的不同点在于,将PMOS晶体管MP722、MP723、MP724置换为晶体管MP725、MP726。这些晶体管的栅宽度按晶体管MP720、MP725、MP726的顺序为1:1:2的尺寸。

对晶体管MP725的栅输入用倒相电路IV720使被输入存储层选择信号LS1B、LS3B的二输入NAND电路ND720的输出信号的信号LS13B反相。对晶体管MP726的栅输入用倒相电路IV721使被输入存储层选择信号LS2B、LS3B的二输入NAND电路ND721的输出信号的信号LS23B反相。利用这样的结构,使用三个晶体管发生图20中表示的那样的4阶段的复位电流Irst。如果用多个改写电路共有逻辑电路部,则可削减改写驱动器内的晶体管个数,因此可以抑制改写驱动器WD的面积。

(实施方式3)

在本实施方式3中,说明图1中表示的相变存储器PCM的另外的结构例。图21表示了本实施方式中的相变存储器PCM的结构例。本相变存储器PCM的特征在于,对每个存储层判断是合格品还是不合格品,只使用判断为合格品的存储层。为了实现这样的功能,具有在图1中表示的结构中附加地址变换电路AE的这一特征。该地址变换电路AE将内部地址IA[28:27]变换为内部地址CA[28:27],传送给行地址缓冲器组和锁存器组(X-Buffers & Latches).

图22表示了图21中表示的地址变换电路AE的结构例。该地址变换电路AE由地址变换逻辑电路AEL和多路转换器MUX构成。地址变换电路使用熔断器等设定为任意的逻辑。该逻辑根据判断为合格品的存储层的组合而不同,实现例如图23中表示的那样的功能。以下说明该功能。

第一个功能在于,判断为合格品的存储层为一层,发生用于选择第一层~第四层中的某一层的地址。在该情况下,将应输入的内部地址IA[28:27]定义为00。地址变换逻辑电路AEL按照判断为合格品的存储层将该内部地址IA[28:27]变换为00、01、10、11。

第二个功能在于,判断为合格品的存储层为两层,发生用于从第一层~第四层选择某两层的地址。在该情况下,将应输入的内部地址IA[28:27]定义为00或01。地址变换逻辑电路AEL按照判断为合格品的存储层将该内部地址IA[28:27]变换为6种组合。

第三个功能在于,判断为合格品的存储层为三层,发生用于从第一层~第四层选择某三层的地址。在该情况下,将应输入的内部地址IA[28:27]定义为00、01、10。地址变换逻辑电路AEL按照判断为合格品的存储层将该内部地址IA[28:27]变换为4种组合。

第四个功能在于,判断为合格品的存储层为四层,发生用于选择第一层~第四层的某一层的地址。在该情况下,将应输入的内部地址IA[28:27]定义为00、01、10、11的某一个。将该内部地址IA[28:27]按原样作为内部地址EA[28:27]输出。

多路转换器MUX按照控制信号组CTL4将内部地址IA[28:27]或内部地址EA[28:27]的某一方作为内部地址CA[28:27]输出。控制信号组CTL4如图24中所示,具有初始化模式信号INIT、测试模式信号TEST、通常动作模式信号NORM。初始化模式信号INIT,如图9中所示,被第一和第二初始化指令信号IN1、IN2激活。通常动作模式信号NORM,如图15或图17中所示,被第一和第二改写指令信号PRG1、PRG2或第一和第二读出指令信号RD1、RD2激活。测试模式信号TEST通过分别输入测试时的第一和第二改写指令信号TPRG1、TPRG2、第一和第二读出指令信号TRD1、TRD2代替图15或图17中表示的第一和第二改写指令信号PRG1、PRG2、第一和第二读出指令信号RD1、RD2而被激活。利用以上的动作模式信号,在初始化模式和测试模式中,选择内部地址IA[28:27],将其输出给内部地址CA[28:27]。此外,在通常动作模式中,选择由地址变换逻辑电路AEL进行了变换的内部地址EA[28:27],将其输出给内部地址CA[28:27]。。

利用以上那样的地址变换电路AE的结构和动作,可得到以下的效果。即,如图23中所示,通过将内部地址IA[28:27]变换为内部地址EA[28:27],在进行初始化动作、写入动作和读出动作的试验时,通过选择全部的存储层以进行所希望的动作,可按存储层单位进行合格品或不合格品的识别。此外,通过按照该每个存储层的特性判断对每个芯片进行地址变换逻辑电路AEL的设定,可实现能只选择特性良好的存储层进行存储器动作的所谓部分品芯片。利用这样的部分品,可提高每个晶片的芯片取得数,可减少位成本。

(实施方式4)

在本实施方式中,说明用于确认在实施方式3中说明了的部分品芯片中能使用的存储层的方法。本方法的特征在于,在图7中表示的页结构中,在任意的页的备用区域中在芯片出厂前预先写入适用的页包含的存储层是否可使用的信息。更具体地说,如图5中所示,在存储器平面PL0中Main block0、Main block4、Main block8、Mainblock12中的开头块block0、block2048、block4096、block6144的第一和第二页Page0、Page1的备用区中写入由列地址2049选择的存储单元中存储层是否可使用的信息。备用区不一定需要用与主块为同一的存储器来构成,可用其它的非易失性存储器来构成。

以下,假定在存储信息为“FFh”的情况下,适用的存储层可使用,在存储信息为“FFh”以外的情况下,不能使用。

图25表示用于确认存储层的可否使用的读出动作中的流程图。首先,输入存储层的可否使用确认指令信号RLS1。其次,输入与列地址2049对应的地址信号和选择图8中表示的页那样的行地址信号。再者,输入存储层的可否使用确认指令信号RLS2,读出所希望的备用区的存储信息。此处,在适用的存储层能使用的情况下,将存储信息“FFh”通知给连接到在相变存储器芯片的外部的存储器控制器或中央运算装置CPU等的所谓主机侧的装置。另一方面,在适用的存储层不能使用的情况下,将存储信息“FFh”以外的信息通知给连接到在相变存储器芯片的外部的存储器控制器或中央运算装置CPU等的所谓主机侧的装置。主机侧的装置在不能使用的存储层管理表(InvalidLayer Table)中记录这样通知了的信息。一边逐层地推进存储层地址,一边重复这样的动作,作成不能使用的存储层管理表。

图26表示了图25中表示的流程中的读出动作部分。动作原理与图17中表示的读出动作相同。将第一和第二指令信号从图17中表示的读出指令信号RD1、RD2置换为存储层可否使用确认指令信号RLS1、RLS2。此外,其特征在于:在只读出开头页或后续的页中的列地址2049的存储信息。

图27是表示图22中表示的多路转换器的另外的功能的图。本实施方式的多路转换器的功能通过从第一和第二存储层可否使用确认指令信号RLS1、RLS2发生的存储层确认模式信号RLS进行扩展。即,如果存储层确认模式信号RLS被激活,则选择内部地址IA[28:27],输出给内部地址CA[28:27]。再有,在本实施方式中新附加的存储层确认模式信号RLS是控制信号组CTL4的构成要素。

利用以上的结构和动作,可得到以下的效果。即,通过使用第一和第二存储层可否使用确认指令信号RLS1、RLS2读出各存储层的备用区的存储信息,主机侧的装置可掌握哪个存储层可使用。于是,组合各种各样的容量的相变存储器芯片来构筑系统或增设相变存储器芯片变得容易。

再有,确认存储层的可否使用的方法不限于此,有各种各样的方法。例如,也可在相变存储器芯片内设置器件ID表,存储与存储器平面容量有关的信息。图28表示了器件ID读出动作的时序图,图29表示了器件ID表。图28中表示的器件ID读出动作依据图17中表示的读出动作,利用器件ID读出指令信号RID,按顺序读出图29中表示的器件ID。芯片用户(在此,是主机侧的装置)可从存储器平面容量掌握相变存储器的有效芯片容量和应输入的地址信号。

(实施方式5)

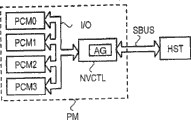

在本实施方式中,说明使用在实施方式3~实施方式4中说明了的多个相变存储器芯片形成的相变存储器模块。图30表示了本实施方式的相变存储器模块PM的结构。在该图中,作为一例,表示了使用4个相变存储器芯片PCM0~PCM3和非易失性存储器控制芯片NVCTL的结构。

非易失性存储器控制芯片NVCTL具有在实施方式3~实施方式4中叙述了的不能使用存储层管理表(Invalid Layer Table)。此外,具有用于使各存储单元中的改写次数均衡化的磨损均衡(WearLevelling)功能及用于将在存储器空间中散布的空闲区域汇总在一起的无用单元收集(Garbage Collection)功能。相变存储器芯片PCM0~PCM3具有图16和图17中表示的地址变换电路AE。利用该地址变换电路AE将所输入的地址信号变换为用于选择可使用的存储层的内部地址信号。用输入输出线I/O连接了非易失性存储器控制芯片NVCTL与相变存储器芯片PCM0~PCM3。此外,非易失性存储器控制芯片NVCTL经系统总线SBUS与主装置连接。利用这样的结构,可构筑组合了各种各样的容量的相变存储器芯片的大容量的存储装置。

(实施方式6)

在本实施方式中,说明使用已说明的多个相变存储器芯片形成的相变存储器模块的另外的结构。图31表示了本实施方式的相变存储器模块PM的结构。在该图中,作为一例,表示了使用4个相变存储器芯片PCM0~PCM3和非易失性存储器控制芯片NVCTL的结构。在此,假定4个相变存储器芯片PCM0~PCM3没有实施方式3~实施方式4中说明了的那样的地址变换电路。

与图30中表示的相变存储器模块的差别在于,非易失性存储器控制芯片NVCTL具有带有图23中表示的那样的地址变换功能的地址发生电路区AG。非易失性存储器控制芯片NVCTL每当电源接通时进行用于确认图18和图19中表示的存储层的可否使用的读出动作,构筑不能使用的存储层管理表(Invalid Layer Table)。通过在非易失性存储器控制芯片NVCTL中集约地址变换功能,可削减相变存储器芯片PCM0~PCM3的芯片面积。

(实施方式7)

在本实施方式中,说明实施方式1的半导体装置的另外的例子。在本实施方式中,具有下述特征:图1中表示的控制信号组CTL4还具有四种复位起动信号RST_EN0~RST_EN3,按照写入存储信息的存储层来选择这些复位起动信号。

图32表示了图1中的改写驱动器的另外的结构例。该图的特征在于,通过使用NAND电路ND730~ND733和倒相电路IV730~733进行复位起动信号RST_EN0~RST_EN3与存储层选择信号LS[3:0]的AND逻辑运算,选择与所激活的存储层选择信号对应的复位起动信号。将作为AND逻辑运算的结果的倒相电路IV730~733的输出信号分别输入到四输入NOR电路NR730中,将用倒相电路IV734使其输出信号反相而发生的复位起动信号输入到NAND电路ND71中。

图34是表示图23中表示的半导体装置中的相变存储器的改写动作中的芯片内部动作的例子的图。在该图中,表示了在图3中表示的存储器阵列MA中包含的子存储器阵列SMA0~SMA16895中对处于层叠存储单元组MB00的最下层的存储单元MC1写入存储信息的情况的动作波形。将复位起动信号RST_EN[3:0]的脉冲宽度设定为按复位起动信号RST_EN3至RST_EN0的顺序逐步变宽。在图23中表示的改写驱动器内选择这些脉冲。在此,由于写入存储信息的目的地的存储层是最下层,故通过激活存储层选择信号LS0,如图33中所示,选择脉冲宽度宽的复位起动信号RST_EN0。利用该复位起动信号RST_EN0按照存储信息进行复位动作。

利用以上的结构和动作,可得到以下的效果。即,通过对越是位于电阻相对低的下层的存储单元越加长复位动作中的电流驱动时间,可使记录层的电阻提高至所希望的值。此外,如图32中表示的改写驱动器那样,通过与施加电流的调整功能组合起来,能更可靠地进行复位动作。

(实施方式8)

在本实施方式中,说明迄今为止说明的相变存储器芯片的另外的结构。图35表示了基于图1中表示的相变存储器芯片的结构。该图的特征有以下的三个。

第一个特征在于,使用内部电压发生电路VGEN在芯片内部发生多个电压V[3:0]。内部电压发生电路VGEN从电源电压VDD和接地电压VSS发生这些多个电压。通过对逻辑电路供给电源电压VDD,对存储器阵列供给这些多个电压,可使逻辑电路的动作和多个电压的驱动变得稳定。

第二个特征在于,分别将所发生的电压V[3:0]的供电线引出到焊区PAD_V0~PAD_V3。利用这样的结构,在芯片内部测定是否发生了所希望的电压变得容易。

第三个特征在于,在存储器平面PL0~PL3中设置电压选择电路VSEL。该电压选择电路VSEL选择与作为控制信号组CTL4的构成要素的初始化起动信号INIT_EN和存储层选择信号LS[3:0]对应的值,作为阵列电压VARY输出。将被控制为适当的值的阵列电压VARY经由第一行解码器XDEC1供给字线WL,此外也供给改写驱动器WD。利用这样的电压控制,可按照因电特性的差异而在每层中具有离散的电阻值,在每层中用最佳的电压进行存储器单元的初始化动作。

具体地说,如图36中所示那样设定阵列电压VARY。在对第一存储层(最下层)的存储单元进行初始化的情况下,通过激活存储层选择信号LS0(在此,驱动为电源电压VDD),将阵列电压VARY驱动为第一电压V0。在对第二存储层的存储单元进行初始化的情况下,通过激活存储层选择信号LS1(在此,驱动为电源电压VDD),将阵列电压VARY驱动为比第一电压V0高的第二电压V1。在对第三存储层的存储单元进行初始化的情况下,通过激活存储层选择信号LS2(在此,驱动为电源电压VDD),将阵列电压VARY驱动为比第二电压V1高的第三电压V2。在对第四存储层(最高位)的存储单元进行初始化的情况下,通过激活存储层选择信号LS3(在此,驱动为电源电压VDD),将阵列电压VARY驱动为比第三电压V2高的第四电压V3。以上的电压满足上述的(式1)的关系。

这样,通过供给对每层为最佳的电压进行初始化动作可防止因对存储层的过度的应力的施加引起的电特性的劣化,可实现高可靠性的相变存储器。

再有,在初始化起动信号INIT_EN处于非激活状态(在此,驱动为接地电压VSS)的情况下,本发明的相变存储器进行读出动作或写入动作。在这样的情况下,不依赖于存储层选择信号LS[3:0]的状态,将阵列电压VARY设定为电源电压VDD。此外,可从外部供给阵列电压VARY。这是由于,在出厂时的测试等中进行一次初始化动作就足够了,只要用出厂时的测试等供给初始化中必要的电压也就足够了。也可设置阵列电压VARY专用的引脚,来供给与存储层对应的阵列电压。由于只调整电源电压VDD的值就可进行所希望的初始化动作,故通过调整对电源电压VDD引脚施加的电压,可实现本实施例的动作。在该情况下,由于可抑制引脚数,故可谋求存储器芯片的小面积化。

以上根据实施方式具体地说明了由本发明者进行的发明,但本发明不限定于上述实施方式,在不脱离其要旨的范围内当然可作各种变更。例如,层叠的存储单元不限于4层,可以小于等于或大于等于4层(例如,2层或8层)。另一方面,初始化动作中的阵列电压不限于越往上层越高那样的设定,可根据存储单元的特性进行其它的设定。例如,在因越往上层的存储单元加工尺寸的离散变得越大等的某种原因具有越往上层的存储单元电阻值越低的趋势的情况下,也可进行越往上层阵列电压越低那样的设定。同样,也可将复位动作中的复位电流Irst设定为越往上层越小。此外,也可将复位动作中的复位起动信号RST_EN的宽度设定为越往上层越小。再者,不限于复位动作,还可以根据存储单元的电特性,即使在置位动作中也可进行同样的改写条件的最佳化。再有,本发明不限于单体存储器芯片,也可将本发明适用于芯片上的存储器的接口。此外,本发明的概念不限于相变存储器,也可适用于闪速存储器或动态随机存取存储器、静态随机存取存储器、磁阻随机存取存储器等各种各样的半导体存储器。

本发明的半导体装置通过按照进行存取的存储单元所处的层调整初始化动作条件或复位动作条件,可防止对记录层的过度的应力,可避免电特性的劣化。如果半导体存储器的大容量化得到进展,则利用层叠使存储器阵列实现三维化。此外,如果存储单元的层叠数增加,则由于存储单元间的热经历的差别变大,故存储器阵列的电特性的差别增加。但是,按照本发明,由于可对每层使动作条件最佳化,故适合于将来的具有层叠存储器阵列的半导体装置的高可靠技术。

Claims (23)

1.一种半导体装置,其特征在于:

具有:

第1存储单元,设置在第1层中,具有利用电流写入存储信息的第1存储元件;

第2存储单元,设置在形成于上述第1层的上方的第2层中,具有利用电流写入存储信息的第2存储元件;

第1地址解码器,用于输出用来选择上述第1层的第1层选择信号或用来选择上述第2层的第2层选择信号;以及

改写驱动器,用于在对上述第1存储单元写入第1存储信息时对上述第1存储单元供给第1电流、在对上述第2存储单元写入上述第1存储信息时对上述第2存储单元供给与上述第1电流不同的大小的第2电流,

上述改写驱动器根据上述第1层选择信号和上述第2层选择信号控制上述第1电流和上述第2电流的大小。

2.如权利要求1中所述的半导体装置,其特征在于:

上述改写驱动器还具有用于对上述第1存储单元或上述第2存储单元写入第1存储信息的第1电流镜电路和用于对上述第1电流镜电路供给电压的第1晶体管及第2晶体管,

上述第2晶体管的栅宽度比上述第1晶体管的栅宽度宽,

上述第1晶体管在流过上述第1电流的情况和流过上述第2电流的情况这两种情况下与上述第1层选择信号和上述第2层选择信号无关地成为导通状态,

利用上述第2电流控制上述第2晶体管,以使其在流过上述第1电流的情况下成为截止状态、在流过上述第2电流的情况下成为导通状态。

3.如权利要求1中所述的半导体装置,其特征在于:

上述改写驱动器还具有用于对上述第1存储单元或上述第2存储单元写入第1存储信息的第1电流镜电路和用于对上述第1电流镜电路供给电压的第1晶体管及第2晶体管,

上述第2晶体管的栅宽度比上述第1晶体管的栅宽度宽,

利用上述第1层选择信号控制上述第1晶体管,使其在流过上述第1电流的情况下成为导通状态、在流过上述第2电流的情况下成为截止状态,

利用上述第2层选择信号控制上述第2晶体管,使其在流过上述第1电流的情况下成为截止状态、在流过上述第2电流的情况下成为导通状态。

4.如权利要求1中所述的半导体装置,其特征在于:

还具有第3存储单元,形成在上述第2层的上方,具有利用电流写入存储信息的第3存储元件,

上述第2电流比上述第1电流大,

在对上述第3存储单元写入上述第1存储信息时在上述第3存储单元中流过的第3电流比上述第2电流大。

5.如权利要求1中所述的半导体装置,其特征在于:

上述改写驱动器还具有用于对上述第1存储单元或上述第2存储单元写入与上述第1存储信息不同的第2存储信息的第2电流镜电路和用于对上述第1存储单元或上述第2存储单元进行初始化的第3电流镜电路,

上述第2电流镜电路在上述第1存储单元中流过的电流与在上述第2存储单元中流过的电流相等,

上述第3电流镜电路在上述第1存储单元中流过的电流与在上述第2存储单元中流过的电流相等。

6.如权利要求1中所述的半导体装置,其特征在于:

还具有:

第1位线,设置在上述第1层中,并连接到上述第1存储单元;

第2位线,设置在上述第2层中,并连接到上述第2存储单元;以及

第1字线,连接到上述第1存储单元和上述第2存储单元,

上述第1存储单元还具有用于在从上述第1字线经由上述第1存储元件到达上述第1位线的方向上流过电流的第1整流元件,

上述第2存储单元还具有用于在从上述第1字线经由上述第2存储元件到达上述第2位线的方向上流过电流的第2整流元件。

7.如权利要求1中所述的半导体装置,其特征在于:

还具有:

地址变换电路,用于将用来选择上述第1层或上述第2层的一方的第1地址信号变换为用来选择上述第1层或上述第2层的另一方的第2地址信号;以及

多路转换器,用于选择上述第1地址信号和从上述地址变换电路输出的上述第2地址信号中的某一方,

上述第1地址解码器根据上述多路转换器所选择的地址信号输出上述第1层选择信号或上述第2层选择信号。

8.如权利要求7中所述的半导体装置,其特征在于:

上述多路转换器在上述第1层或上述第2层的一方不能使用且上述第1层或上述第2层的另一方能使用的情况下选择上述第2地址信号。

9.如权利要求7中所述的半导体装置,其特征在于:

还具有非易失性的存储器,

在上述存储器中写入有上述第1层和上述第2层是否能使用的信息。

10.一种半导体装置,其特征在于:

具有:

第1位线,设置在第1层中;

第2位线,设置在形成于上述第1层的上方的第2层中;

第1字线和第2字线,与上述第1位线和上述第2位线交叉;

第1存储单元,设置在上述第1位线与上述第1字线的交点处,具有利用电流写入存储信息的第1存储元件和用于在从上述第1字线经由上述第1存储元件到达上述第1位线的方向上流过电流的第1整流元件;

第2存储单元,设置在上述第1位线与上述第2字线的交点处,具有利用电流写入存储信息的第2存储元件和用于在从上述第2字线经由上述第2存储元件到达上述第1位线的方向上流过电流的第2整流元件;

第3存储单元,设置在上述第2位线与上述第1字线的交点处,具有利用电流写入存储信息的第3存储元件和用于在从上述第1字线经由上述第3存储元件到达上述第2位线的方向上流过电流的第3整流元件;以及

第4存储单元,设置在上述第2位线与上述第2字线的交点处,具有利用电流写入存储信息的第4存储元件和用于在从上述第2字线经由上述第4存储元件到达上述第2位线的方向上流过电流的第4整流元件,

在对上述第1或第2存储单元进行初始化的情况下,对上述第1或第2存储单元供给第1电压,

在对上述第3或第4存储单元进行初始化的情况下,对上述第3或第4存储单元供给与上述第1电压不同的第2电压。

11.如权利要求10中所述的半导体装置,其特征在于:

从上述半导体装置的外部供给上述第1电压和上述第2电压。

12.如权利要求10中所述的半导体装置,其特征在于:

还具有:

第1地址解码器,用于输出用来选择上述第1层的第1层选择信号或用来选择上述第2层的第2层选择信号;以及

电源选择电路,用于根据上述第1层选择信号对上述第1存储单元或上述第2存储单元供给上述第1电压、根据上述第2层选择信号对上述第3存储单元或上述第4存储单元供给上述第2电压。

13.如权利要求10中所述的半导体装置,其特征在于:

还具有用于对上述第1、第2、第3或第4存储单元写入存储信息的改写驱动器,

对上述改写驱动器供给上述第1电压或上述第2电压。

14.如权利要求10中所述的半导体装置,其特征在于:

为了对上述第1或第2存储单元写入存储信息而对上述第1或第2存储单元供给的电压与为了对上述第3或第4存储单元写入存储信息而对上述第3或第4存储单元供给的电压相等,

为了从上述第1或第2存储单元读出存储信息而对上述第1或第2存储单元供给的电压与为了从上述第3或第4存储单元读出存储信息而对上述第3或第4存储单元供给的电压相等。

15.如权利要求10中所述的半导体装置,其特征在于:

还具有:

第3位线,设置在形成于上述第2层的上方的第3层中;

第5存储单元,设置在上述第3位线与上述第1字线的交点处,具有利用电流写入存储信息的第5存储元件和用于在从上述第1字线经由上述第5存储元件到达上述第5位线的方向上流过电流的第5整流元件;以及

第6存储单元,设置在上述第3位线与上述第2字线的交点处,具有利用电流写入存储信息的第6存储元件和用于在从上述第2字线经由上述第6存储元件到达上述第6位线的方向上流过电流的第6整流元件,

上述第2电压比上述第1电压大,

为了对上述第5或第6存储单元进行初始化而对上述第5或第6存储单元供给的第3电压比上述第2电压大。

16.如权利要求10中所述的半导体装置,其特征在于:

还具有:

地址变换电路,用于将用来选择上述第1层或上述第2层的一方的第1地址信号变换为用来选择上述第1层或上述第2层的另一方的第2地址信号;以及

多路转换器,用于选择上述第1地址信号和从上述地址变换电路输出的上述第2地址信号中的某一方,

上述第1地址解码器根据上述多路转换器所选择的地址信号输出上述第1层选择信号或上述第2层选择信号。

17.如权利要求16中所述的半导体装置,其特征在于:

上述多路转换器在上述第1层不能使用且上述第2层能使用的情况下选择上述第2地址信号。

18.如权利要求16中所述的半导体装置,其特征在于:

还具有非易失性的存储器,

在上述存储器中写入有上述第1层和上述第2层是否能使用的信息。

19.一种半导体装置,其特征在于,具有:

第1存储单元,设置在第1层中,具有利用电流写入存储信息的第1存储元件;

第2存储单元,设置在形成于上述第1层的上方的第2层中,具有利用电流写入存储信息的第2存储元件;

地址变换电路,用于将用来选择上述第1层或上述第2层的某一方的第1地址信号变换为用来选择上述第1层或上述第2层的另一方的第2地址信号;

多路转换器,用于选择上述第1地址信号和从上述地址变换电路输出的上述第2地址信号中的某一方;以及

第1地址解码器,用于根据上述多路转换器所选择的信号发生选择上述第1层的第1层选择信号或选择上述第2层的第2层选择信号。

20.如权利要求19中所述的半导体装置,其特征在于:

上述多路转换器在上述第1层或上述第2层的某一方不能使用且上述第1层或上述第2层的另一方能使用的情况下选择上述第2地址信号。

21.如权利要求19中所述的半导体装置,其特征在于:

还具有非易失性的存储器,

在上述存储器中写入有上述第1层和上述第2层是否能使用的信息。

22.如权利要求19中所述的半导体装置,其特征在于:

还具有:

第1位线,设置在上述第1层中,连接到上述第1存储单元;

第2位线,设置在上述第2层中,连接到上述第2存储单元;以及

第1字线,连接到上述第1存储单元和上述第2存储单元,

上述第1存储单元还具有用于在从上述第1字线经由上述第1存储元件到达上述第1位线的方向上流过电流的第1整流元件,

上述第2存储单元还具有用于在从上述第1字线经由上述第2存储元件到达上述第2位线的方向上流过电流的第2整流元件。

23.如权利要求1至22中任一项所述的半导体装置,其特征在于:

上述第1存储元件和上述第2存储元件是相变元件。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007335614 | 2007-12-27 | ||

| JP2007335614A JP5063337B2 (ja) | 2007-12-27 | 2007-12-27 | 半導体装置 |

| JP2007-335614 | 2007-12-27 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101471133A true CN101471133A (zh) | 2009-07-01 |

| CN101471133B CN101471133B (zh) | 2011-12-28 |

Family

ID=40798179

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2008101855938A Expired - Fee Related CN101471133B (zh) | 2007-12-27 | 2008-12-17 | 层叠有存储器阵列的半导体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US7830706B2 (zh) |

| JP (1) | JP5063337B2 (zh) |

| KR (2) | KR101031133B1 (zh) |

| CN (1) | CN101471133B (zh) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102725842A (zh) * | 2010-02-05 | 2012-10-10 | 株式会社半导体能源研究所 | 半导体器件 |

| CN101770807B (zh) * | 2009-12-29 | 2013-03-27 | 中国科学院上海微系统与信息技术研究所 | 相变存储器的写优化电路及其写优化方法 |

| CN103632710A (zh) * | 2012-08-24 | 2014-03-12 | 爱思开海力士有限公司 | 半导体存储器件 |

| CN104241526A (zh) * | 2013-06-21 | 2014-12-24 | 旺宏电子股份有限公司 | 相变化存储器、其写入方法及其读取方法 |

| CN107430889A (zh) * | 2015-03-27 | 2017-12-01 | 松下知识产权经营株式会社 | 半导体存储装置的改写方法以及半导体存储装置 |

| CN113129976A (zh) * | 2021-06-17 | 2021-07-16 | 中天弘宇集成电路有限责任公司 | 行译码电路及存储器 |

| CN114303153A (zh) * | 2019-09-02 | 2022-04-08 | 索尼集团公司 | 算术设备以及乘法累加算术系统 |

Families Citing this family (52)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI517156B (zh) * | 2008-02-29 | 2016-01-11 | Toshiba Kk | Semiconductor memory device |

| KR100998944B1 (ko) * | 2008-12-26 | 2010-12-09 | 주식회사 하이닉스반도체 | 피램의 라이트 드라이버 회로 |

| US7986572B2 (en) * | 2009-08-17 | 2011-07-26 | Magic Technologies, Inc. | Magnetic memory capable of minimizing gate voltage stress in unselected memory cells |

| JP5586915B2 (ja) * | 2009-10-09 | 2014-09-10 | ピーエスフォー ルクスコ エスエイアールエル | 半導体記憶装置及びこれを備える情報処理システム |

| JP2011258288A (ja) * | 2010-06-10 | 2011-12-22 | Toshiba Corp | 半導体記憶装置 |

| KR20110135299A (ko) | 2010-06-10 | 2011-12-16 | 삼성전자주식회사 | 반도체 메모리 장치 |

| US8860223B1 (en) * | 2010-07-15 | 2014-10-14 | Micron Technology, Inc. | Resistive random access memory |

| JP2012069216A (ja) | 2010-09-24 | 2012-04-05 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5756622B2 (ja) * | 2010-11-30 | 2015-07-29 | 株式会社日立製作所 | 半導体装置 |

| JP5416079B2 (ja) | 2010-12-16 | 2014-02-12 | 株式会社日立製作所 | 半導体記憶装置、およびメモリモジュール |

| KR20120097998A (ko) * | 2011-02-28 | 2012-09-05 | 에스케이하이닉스 주식회사 | 집적 회로 |

| JP5426596B2 (ja) * | 2011-03-24 | 2014-02-26 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2012243359A (ja) * | 2011-05-20 | 2012-12-10 | Sony Corp | 抵抗変化型メモリデバイスおよびその動作方法 |

| US8806171B2 (en) | 2011-05-24 | 2014-08-12 | Georgia Tech Research Corporation | Systems and methods providing wear leveling using dynamic randomization for non-volatile memory |

| US8932901B2 (en) | 2011-10-31 | 2015-01-13 | Macronix International Co., Ltd. | Stressed phase change materials |

| KR101321481B1 (ko) * | 2011-11-04 | 2013-10-28 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이를 위한 테스트 회로 |

| US9111612B2 (en) * | 2012-03-07 | 2015-08-18 | Rambus Inc. | Direct relative measurement of memory durability |

| KR101917192B1 (ko) | 2012-03-12 | 2018-11-12 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 불휘발성 메모리 장치의 읽기 방법 |

| KR101942275B1 (ko) * | 2012-04-18 | 2019-01-25 | 삼성전자주식회사 | 메모리 시스템 및 메모리 시스템의 동작 방법 |

| WO2014045372A1 (ja) | 2012-09-20 | 2014-03-27 | 株式会社日立製作所 | 半導体記憶装置 |

| US20140140124A1 (en) * | 2012-11-21 | 2014-05-22 | Dong-seok Kang | Resistive memory device having selective sensing operation and access control method thereof |

| US9224436B2 (en) | 2013-05-24 | 2015-12-29 | Micron Technology, Inc. | Apparatuses including a memory array with separate global read and write lines and/or sense amplifier region column select line and related methods |

| CN105531767B (zh) * | 2013-06-28 | 2018-01-26 | 英特尔公司 | 电阻式存储器的低功率写和读操作的装置 |

| US9001546B2 (en) * | 2013-08-22 | 2015-04-07 | Taiwan Semiconductor Manufacturing Company Limited | 3D structure for advanced SRAM design to avoid half-selected issue |

| KR102195893B1 (ko) | 2014-02-19 | 2020-12-29 | 에스케이하이닉스 주식회사 | 불휘발성 메모리 장치 및 그것의 동작 방법 |

| US9390770B2 (en) * | 2014-05-16 | 2016-07-12 | Micron Technology, Inc. | Apparatuses and methods for accessing memory including sense amplifier sections and coupled sources |

| US9646660B2 (en) * | 2014-09-23 | 2017-05-09 | Intel Corporation | Selectable memory access time |

| KR102217243B1 (ko) * | 2014-10-28 | 2021-02-18 | 삼성전자주식회사 | 저항성 메모리 장치, 저항성 메모리 시스템 및 저항성 메모리 장치의 동작방법 |

| US9361195B2 (en) | 2014-11-12 | 2016-06-07 | International Business Machines Corporation | Mirroring in three-dimensional stacked memory |

| KR102261817B1 (ko) | 2014-12-15 | 2021-06-07 | 삼성전자주식회사 | 다수의 레이어들을 포함하는 저항성 메모리 장치, 저항성 메모리 시스템 및 저항성 메모리 시스템의 동작방법 |

| US9575671B1 (en) | 2015-08-11 | 2017-02-21 | International Business Machines Corporation | Read distribution in a three-dimensional stacked memory based on thermal profiles |

| US9804793B2 (en) * | 2016-03-04 | 2017-10-31 | Intel Corporation | Techniques for a write zero operation |

| KR102423289B1 (ko) * | 2016-03-23 | 2022-07-20 | 삼성전자주식회사 | 동작 속도를 향상시키는 반도체 메모리 장치 |

| US10007462B1 (en) | 2016-03-31 | 2018-06-26 | EMC IP Holding Company LLC | Method and system for adaptive data migration in solid state memory |

| US10474370B1 (en) | 2016-05-20 | 2019-11-12 | EMC IP Holding Company LLC | Method and system for mitigating the effect of write and read disturbances in solid state memory regions |

| US10249351B2 (en) | 2016-11-06 | 2019-04-02 | Intel Corporation | Memory device with flexible internal data write control circuitry |

| US10490239B2 (en) | 2016-12-27 | 2019-11-26 | Intel Corporation | Programmable data pattern for repeated writes to memory |

| US10599342B2 (en) | 2016-12-30 | 2020-03-24 | EMC IP Holding Company LLC | Method and system for offset mirroring in a storage system |

| US10416904B1 (en) | 2016-12-30 | 2019-09-17 | EMC IP Holding Company LLC | Method and system for recovering storage object records in solid state memory |

| GB2561011B (en) * | 2017-03-31 | 2021-03-17 | Advanced Risc Mach Ltd | Initialisation of a storage device |

| US11037614B2 (en) | 2017-07-28 | 2021-06-15 | Intel Corporation | Imprint-free write driver for ferroelectric memory |

| US11334060B2 (en) | 2017-09-06 | 2022-05-17 | Siemens Healthcare Diagnostics Inc. | Alert-enabled passive application integration |

| US10454025B1 (en) | 2018-06-13 | 2019-10-22 | International Business Machines Corporation | Phase change memory with gradual resistance change |

| KR102487550B1 (ko) | 2018-06-29 | 2023-01-11 | 삼성전자주식회사 | 메모리 장치 및 그 동작 방법 |

| JP2020149736A (ja) * | 2019-03-11 | 2020-09-17 | キオクシア株式会社 | 半導体記憶装置 |

| KR102675350B1 (ko) * | 2019-05-29 | 2024-06-17 | 삼성전자주식회사 | 불휘발성 메모리 장치 |

| DE102019126107A1 (de) * | 2019-09-27 | 2021-04-01 | Infineon Technologies Ag | Speicheranordnungen, verfahren zum initiieren eines speichers und verfahren zum nutzen eines speichers |

| KR20210078232A (ko) * | 2019-12-18 | 2021-06-28 | 삼성전자주식회사 | 비휘발성 메모리 소자 및 이를 포함한 비휘발성 메모리 장치 |

| WO2022077318A1 (en) * | 2020-10-15 | 2022-04-21 | Yangtze Advanced Memory Industrial Innovation Center Co., Ltd | Array and contact architecture for four stack three dimensional cross point memory |

| US12216588B2 (en) * | 2020-12-11 | 2025-02-04 | SK Hynix Inc. | Semiconductor memory apparatus, memory module, and memory system including memory module |

| JP6999791B1 (ja) * | 2020-12-28 | 2022-01-19 | 華邦電子股▲ふん▼有限公司 | 半導体記憶装置 |

| GB202210806D0 (en) * | 2022-07-24 | 2022-09-07 | Advantec International Ltd | Sensor system |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7934074B2 (en) * | 1999-08-04 | 2011-04-26 | Super Talent Electronics | Flash module with plane-interleaved sequential writes to restricted-write flash chips |

| US20010037435A1 (en) * | 2000-05-31 | 2001-11-01 | Van Doren Stephen R. | Distributed address mapping and routing table mechanism that supports flexible configuration and partitioning in a modular switch-based, shared-memory multiprocessor computer system |

| JP3913014B2 (ja) * | 2000-08-31 | 2007-05-09 | 松下電器産業株式会社 | 情報記録媒体およびその製造方法ならびにその記録再生方法 |

| US6809401B2 (en) * | 2000-10-27 | 2004-10-26 | Matsushita Electric Industrial Co., Ltd. | Memory, writing apparatus, reading apparatus, writing method, and reading method |

| KR100382546B1 (ko) * | 2000-12-04 | 2003-05-09 | 주식회사 하이닉스반도체 | 불휘발성 강유전체 메모리 장치 및 그를 이용한 불량셀검출방법 |

| JP3591497B2 (ja) | 2001-08-16 | 2004-11-17 | ソニー株式会社 | 強誘電体型不揮発性半導体メモリ |

| JP2003067244A (ja) * | 2001-08-24 | 2003-03-07 | Matsushita Electric Ind Co Ltd | 不揮発性記憶装置及びその制御方法 |

| US6579760B1 (en) * | 2002-03-28 | 2003-06-17 | Macronix International Co., Ltd. | Self-aligned, programmable phase change memory |

| US7042749B2 (en) * | 2002-05-16 | 2006-05-09 | Micron Technology, Inc. | Stacked 1T-nmemory cell structure |

| JP3857658B2 (ja) | 2003-03-04 | 2006-12-13 | 株式会社東芝 | 磁気ランダムアクセスメモリ |

| JP4377817B2 (ja) * | 2003-03-18 | 2009-12-02 | 株式会社東芝 | プログラマブル抵抗メモリ装置 |

| US7394680B2 (en) * | 2003-03-18 | 2008-07-01 | Kabushiki Kaisha Toshiba | Resistance change memory device having a variable resistance element with a recording layer electrode served as a cation source in a write or erase mode |

| US6879505B2 (en) * | 2003-03-31 | 2005-04-12 | Matrix Semiconductor, Inc. | Word line arrangement having multi-layer word line segments for three-dimensional memory array |

| JP4445398B2 (ja) * | 2003-04-03 | 2010-04-07 | 株式会社東芝 | 相変化メモリ装置 |

| US7688621B2 (en) * | 2003-06-03 | 2010-03-30 | Samsung Electronics Co., Ltd. | Memory system, memory device and apparatus including writing driver circuit for a variable resistive memory |

| US7291878B2 (en) * | 2003-06-03 | 2007-11-06 | Hitachi Global Storage Technologies Netherlands B.V. | Ultra low-cost solid-state memory |

| US6914255B2 (en) | 2003-08-04 | 2005-07-05 | Ovonyx, Inc. | Phase change access device for memories |

| EP1884936A3 (en) | 2003-08-14 | 2009-04-29 | LG Electronics Inc. | Method and apparatus for recording control information on a recording medium having one or more recording layers and recording medium |

| KR100564602B1 (ko) * | 2003-12-30 | 2006-03-29 | 삼성전자주식회사 | 상 변화 메모리 어레이의 셋 프로그래밍 방법 및 기입드라이버 회로 |

| KR100520228B1 (ko) * | 2004-02-04 | 2005-10-11 | 삼성전자주식회사 | 상변화 메모리 장치 및 그에 따른 데이터 라이팅 방법 |

| KR100564636B1 (ko) * | 2004-10-26 | 2006-03-28 | 삼성전자주식회사 | 반도체 메모리 장치 |

| US7327600B2 (en) * | 2004-12-23 | 2008-02-05 | Unity Semiconductor Corporation | Storage controller for multiple configurations of vertical memory |

| US7307268B2 (en) * | 2005-01-19 | 2007-12-11 | Sandisk Corporation | Structure and method for biasing phase change memory array for reliable writing |

| US8111572B2 (en) * | 2007-12-12 | 2012-02-07 | Unity Semiconductor Corporation | Disturb control circuits and methods to control memory disturbs among multiple layers of memory |

| US7752381B2 (en) * | 2005-05-24 | 2010-07-06 | Micron Technology, Inc. | Version based non-volatile memory translation layer |

| JP4469319B2 (ja) * | 2005-06-17 | 2010-05-26 | シャープ株式会社 | 半導体記憶装置 |

| US8055833B2 (en) * | 2006-10-05 | 2011-11-08 | Google Inc. | System and method for increasing capacity, performance, and flexibility of flash storage |

| KR100773095B1 (ko) * | 2005-12-09 | 2007-11-02 | 삼성전자주식회사 | 상 변화 메모리 장치 및 그것의 프로그램 방법 |

| KR100655082B1 (ko) * | 2005-12-23 | 2006-12-08 | 삼성전자주식회사 | 상변화 메모리 소자 및 그 제조방법 |

| KR100855861B1 (ko) * | 2005-12-30 | 2008-09-01 | 주식회사 하이닉스반도체 | 비휘발성 반도체 메모리 장치 |

| US7292466B2 (en) * | 2006-01-03 | 2007-11-06 | Infineon Technologies Ag | Integrated circuit having a resistive memory |

| US7391664B2 (en) | 2006-04-27 | 2008-06-24 | Ovonyx, Inc. | Page mode access for non-volatile memory arrays |

| US7619945B2 (en) * | 2006-08-18 | 2009-11-17 | Unity Semiconductor Corporation | Memory power management |

| US7692951B2 (en) * | 2007-06-12 | 2010-04-06 | Kabushiki Kaisha Toshiba | Resistance change memory device with a variable resistance element formed of a first and a second composite compound |

| JP2009003991A (ja) * | 2007-06-19 | 2009-01-08 | Toshiba Corp | 半導体装置及び半導体メモリテスト装置 |

| US7715250B2 (en) * | 2007-08-16 | 2010-05-11 | Unity Semiconductor Corporation | Circuitry and method for indicating a memory |

| US7813210B2 (en) * | 2007-08-16 | 2010-10-12 | Unity Semiconductor Corporation | Multiple-type memory |

| JP4535117B2 (ja) * | 2007-11-06 | 2010-09-01 | ソニー株式会社 | メモリ装置、メモリ管理方法、およびプログラム |

| JP2009135131A (ja) * | 2007-11-28 | 2009-06-18 | Toshiba Corp | 半導体記憶装置 |

| US7663900B2 (en) * | 2007-12-31 | 2010-02-16 | Hitachi Global Storage Technologies Netherlands B.V. | Tree-structure memory device |

| KR101398633B1 (ko) * | 2008-01-28 | 2014-05-26 | 삼성전자주식회사 | 반도체 메모리 장치 및 이 장치의 칩 식별신호 발생방법 |

| JP2009211735A (ja) * | 2008-02-29 | 2009-09-17 | Toshiba Corp | 不揮発性記憶装置 |

| JP5188328B2 (ja) * | 2008-08-29 | 2013-04-24 | 株式会社日立製作所 | 半導体装置 |

| JP5127661B2 (ja) * | 2008-10-10 | 2013-01-23 | 株式会社東芝 | 半導体記憶装置 |

-

2007

- 2007-12-27 JP JP2007335614A patent/JP5063337B2/ja not_active Expired - Fee Related

-

2008

- 2008-12-15 US US12/335,418 patent/US7830706B2/en not_active Expired - Fee Related

- 2008-12-16 KR KR1020080127913A patent/KR101031133B1/ko not_active Expired - Fee Related

- 2008-12-17 CN CN2008101855938A patent/CN101471133B/zh not_active Expired - Fee Related

-

2010

- 2010-09-25 US US12/890,636 patent/US7983109B2/en not_active Expired - Fee Related

- 2010-10-25 KR KR1020100104109A patent/KR101050311B1/ko not_active Expired - Fee Related

-

2011

- 2011-05-20 US US13/112,567 patent/US8094489B2/en not_active Expired - Fee Related

- 2011-12-06 US US13/312,620 patent/US8456940B2/en not_active Expired - Fee Related

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101770807B (zh) * | 2009-12-29 | 2013-03-27 | 中国科学院上海微系统与信息技术研究所 | 相变存储器的写优化电路及其写优化方法 |

| US9190413B2 (en) | 2010-02-05 | 2015-11-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| CN102725842A (zh) * | 2010-02-05 | 2012-10-10 | 株式会社半导体能源研究所 | 半导体器件 |

| CN102725842B (zh) * | 2010-02-05 | 2014-12-03 | 株式会社半导体能源研究所 | 半导体器件 |

| US9793276B2 (en) | 2010-02-05 | 2017-10-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having transistor and capacitor |

| CN103632710B (zh) * | 2012-08-24 | 2018-01-02 | 爱思开海力士有限公司 | 半导体存储器件 |

| CN103632710A (zh) * | 2012-08-24 | 2014-03-12 | 爱思开海力士有限公司 | 半导体存储器件 |

| CN104241526B (zh) * | 2013-06-21 | 2017-01-11 | 旺宏电子股份有限公司 | 相变化存储器、其写入方法及其读取方法 |

| CN104241526A (zh) * | 2013-06-21 | 2014-12-24 | 旺宏电子股份有限公司 | 相变化存储器、其写入方法及其读取方法 |

| CN107430889A (zh) * | 2015-03-27 | 2017-12-01 | 松下知识产权经营株式会社 | 半导体存储装置的改写方法以及半导体存储装置 |

| CN107430889B (zh) * | 2015-03-27 | 2020-09-01 | 松下半导体解决方案株式会社 | 半导体存储装置的改写方法以及半导体存储装置 |

| CN114303153A (zh) * | 2019-09-02 | 2022-04-08 | 索尼集团公司 | 算术设备以及乘法累加算术系统 |

| CN113129976A (zh) * | 2021-06-17 | 2021-07-16 | 中天弘宇集成电路有限责任公司 | 行译码电路及存储器 |

| CN113129976B (zh) * | 2021-06-17 | 2021-09-03 | 中天弘宇集成电路有限责任公司 | 行译码电路及存储器 |

| US11410738B1 (en) | 2021-06-17 | 2022-08-09 | China Flash Co., Ltd. | Word line decoding circuit and memory |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101031133B1 (ko) | 2011-04-27 |

| US20120075926A1 (en) | 2012-03-29 |

| JP5063337B2 (ja) | 2012-10-31 |

| US20110013447A1 (en) | 2011-01-20 |

| US8094489B2 (en) | 2012-01-10 |

| JP2009158020A (ja) | 2009-07-16 |

| US20110216583A1 (en) | 2011-09-08 |

| US8456940B2 (en) | 2013-06-04 |

| US7830706B2 (en) | 2010-11-09 |

| US20090168505A1 (en) | 2009-07-02 |

| KR20090071396A (ko) | 2009-07-01 |

| KR101050311B1 (ko) | 2011-07-19 |

| US7983109B2 (en) | 2011-07-19 |

| CN101471133B (zh) | 2011-12-28 |

| KR20100119854A (ko) | 2010-11-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101471133B (zh) | 层叠有存储器阵列的半导体装置 | |

| JP5188328B2 (ja) | 半導体装置 | |

| JP5049334B2 (ja) | 半導体装置 | |

| US8750017B2 (en) | Resistance-change memory | |

| CN103106149B (zh) | 半导体器件 | |

| US20190267082A1 (en) | Resistance and gate control in decoder circuits for read and write optimization | |

| US8644072B2 (en) | Three dimensionally stacked memory and the isolation of memory cell layer | |

| EP2896045B1 (en) | Complementary decoding for non-volatile memory | |

| JPWO2007141865A1 (ja) | 半導体装置及びその製造方法 | |

| CN101833992B (zh) | 具有冗余存储单元的相变随机存储器系统 | |

| TW201409474A (zh) | 非揮發性半導體記憶裝置 | |

| US11417706B2 (en) | Semiconductor storage device | |

| JP2012185904A (ja) | 半導体装置 | |

| KR101771523B1 (ko) | 메모리 장치와 이의 동작 방법 | |

| JP5548789B2 (ja) | 半導体装置 | |

| WO2014061091A1 (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20111228 Termination date: 20181217 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |