WO2007142261A1 - パワー素子搭載用基板、その製造方法、パワー素子搭載用ユニット、その製造方法、およびパワーモジュール - Google Patents

パワー素子搭載用基板、その製造方法、パワー素子搭載用ユニット、その製造方法、およびパワーモジュール Download PDFInfo

- Publication number

- WO2007142261A1 WO2007142261A1 PCT/JP2007/061446 JP2007061446W WO2007142261A1 WO 2007142261 A1 WO2007142261 A1 WO 2007142261A1 JP 2007061446 W JP2007061446 W JP 2007061446W WO 2007142261 A1 WO2007142261 A1 WO 2007142261A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- circuit layer

- power element

- element mounting

- ceramic plate

- brazed

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Classifications

-

- H10W40/258—

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

-

- H10W40/255—

-

- H10W40/47—

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/09—Use of materials for the conductive, e.g. metallic pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/02—Fillers; Particles; Fibers; Reinforcement materials

- H05K2201/0203—Fillers and particles

- H05K2201/0263—Details about a collection of particles

- H05K2201/0269—Non-uniform distribution or concentration of particles

-

- H10W72/381—

-

- H10W90/734—

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

Definitions

- Power element mounting substrate manufacturing method thereof, power element mounting unit, manufacturing method thereof, and power module

- the present invention relates to a power element mounting substrate used in a semiconductor device that controls a large current and a high voltage, a manufacturing method thereof, a power element mounting unit, a manufacturing method thereof, and a power module.

- This type of power module generally has a power element mounting board in which a circuit layer is brazed to the surface of a ceramic plate and solder on the surface of the circuit layer, for example, as shown in Patent Document 1 below. And a joined power element.

- the circuit layer and the power element are soldered with a PbSn-based solder material.

- Pb-free solder materials that do not contain Pb are also widely used.

- this type of power module has a circuit layer on the surface of a ceramic plate as shown in Patent Documents 2 and 3 below, for example. It is equipped with a power element mounting unit that is brazed and brazed with a cooler having a cooling water channel formed inside. That is, the total thermal resistance of the power module is reduced by brazing the cooler directly to the back surface of the ceramic plate without interposing other members.

- the cooler in this case is made of an A1 alloy, and has a top plate portion having a brazing surface with a ceramic plate, and a hanging portion suspended from the top plate portion on the surface opposite to the brazing surface. And.

- a bottom plate portion connected to the hanging portion in a state of being arranged in parallel with the top plate portion is provided.

- a circuit layer is brazed to the surface of a ceramic plate as shown in Patent Document 4 below, for example.

- a power element mounting substrate in which a heat block made of pure Cu or Cu alloy solder is solder-bonded to the surface of the circuit layer, and a power element solder-bonded to the surface of the heat block.

- Patent Document 1 No. 03Z090277 gazette

- Patent Document 2 Japanese Patent Laid-Open No. 4-363052

- Patent Document 3 Japanese Patent Application Laid-Open No. 2004-115337

- Patent Document 4 Japanese Patent No. 3044952

- One object of the present invention is that even if a lead-free solder material is used for soldering the circuit layer and the power element, cracks are likely to develop in the solder layer during thermal cycling. It is to provide a power element mounting substrate capable of suppressing the above, a manufacturing method of the power element mounting substrate, and a power module.

- Another object of the present invention is that even when a cooler is directly brazed to the back surface of a ceramic plate, the occurrence of warpage during brazing can be suppressed, and deterioration in thermal cycle reliability can be suppressed. It is to provide a single element mounting unit, a method for manufacturing a power element mounting unit, and a power module.

- the high-purity A1 alloy or pure A1 has a lower bending stiffness than the A1 alloy, which is lower in purity than this material. Therefore, the ceramic plate can be used to braze the ceramic plate and the cooler. After the brazing material foil and the cooler are arranged in this order on the back surface of the laminate to form a laminate, when the laminate is pressurized in the lamination direction, the drooping portion of the cooler may buckle. In particular, in recent years, there is a demand for light weight of the power module, and the cooler tends to be thin. In such a thin cooler, the buckling is more likely to occur.

- Another object of the present invention is to provide a power module that does not reduce the buckling strength of the drooping portion of the cooler.

- a power element mounting unit capable of improving the thermal cycle reliability of the joule, a method of manufacturing the power element mounting unit, and a power module.

- Another object of the present invention is to suppress the occurrence of warpage during brazing and to suppress deterioration in thermal cycle reliability even when a cooler is directly brazed to the back surface of the ceramic plate. It is to provide a single element mounting unit and a power module.

- Another object of the present invention is to provide a power element mounting substrate, a power element mounting substrate manufacturing method, and a power module that can improve the bonding reliability when the power module is used in a thermal cycle. It is.

- the power element mounting substrate is for mounting a power element in which the circuit layer force S is brazed to the surface of the ceramic plate, and the power element is soldered to the surface of the circuit layer.

- the circuit layer is made of an Al alloy having an overall average purity of 98.Owt% or more and 99.9wt% or less, and is made of Fe contained in the brazing surface side with the ceramic plate. The concentration is less than 0.1 wt%, and the concentration of Fe contained on the surface side opposite to the brazing surface of the braces is 0. ⁇ % or more.

- the concentration of Fe contained in the opposite surface side of the circuit layer is 0.1 lwt% or more, so that the circuit layer repeatedly undergoes thermal deformation during the thermal cycle. This gradually makes it possible to cure this opposite surface side, this The amount of plastic deformation generated in the portion can be suppressed. This makes it possible to reduce the load acting on the solder layer that joins the opposite surface of the circuit layer and the power element due to plastic deformation of the circuit layer during the thermal cycle. Even if a crack occurs in this solder layer, its progress is suppressed, and even if a lead-free solder material is used to solder the circuit layer and the power element, the crack progresses in this solder layer during thermal cycling. It can suppress becoming easy to do.

- the concentration of Fe contained on the brazed surface side is less than 0.1 wt%, and therefore, due to the difference in thermal expansion coefficient between the ceramic plate and the circuit layer during the thermal cycle, Even when stress is about to occur at these joint interfaces, the stress can be absorbed by plastically deforming the brazing surface side of the circuit layer. Thereby, it is possible to suppress the stress acting on the joint interface, and the joint reliability between the ceramic plate and the circuit layer can be improved.

- the brazing surface side is a portion of the circuit layer that is located between 10% and 50% of the thickness of the circuit layer toward the opposite surface of the brazing surface force, and the remaining portion is the opposite It may be the surface side.

- a circuit layer is brazed to the surface of the ceramic plate, and the power element is soldered to the surface of the circuit layer.

- a method for producing a power element mounting substrate wherein the purity of the ceramic plate surface containing A1 brazing filler metal foil and Fe of 0.05 wt% or more and 1. Owt% or less is 98.5 wt% or more 99.

- circuit element mounting substrate is formed by brazing the circuit layer member to the surface of the plate.

- the laminate is pressed and brazed in the laminating direction, so that the surface of the ceramic plate and the circuit layer member can be satisfactorily brazed.

- Fe contained on the brazing surface side with the ceramic plate can be satisfactorily dissolved in the brazing material melted at the joining interface. Therefore, on the brazing side of the circuit layer A power device mounting substrate is reliably formed in which the concentration of Fe contained is less than 0.1 lwt% and the concentration of Fe contained on the surface opposite to the brazed surface is 0.1 lwt%. be able to.

- a power module includes a power element mounting substrate in which a circuit layer is brazed to the surface of a ceramic plate, and a power element solder-bonded to the surface of the circuit layer.

- the power element mounting board is a power element mounting board according to the above aspect of the present invention.

- the power element mounting unit includes a cooler in which a circuit layer is brazed on the surface of a ceramic plate and a cooling water channel is formed on the back surface of the ceramic plate.

- the circuit layer is formed of an A1 alloy having an overall average purity of 98. Owt% or more and 99.9 wt% or less, and a brazed surface to the ceramic plate.

- the concentration of Fe contained on the side is less than 0.1 wt%, and the concentration of Fe contained on the surface side opposite to the brazing surface is 0.1 wt% or more.

- the concentration of Fe contained in the opposite surface side in the circuit layer is 0.1 lwt% or more, the bending rigidity of the entire circuit layer is reduced. It is possible to reduce the difference between the bending rigidity of the cooler and reduce the amount of warping that occurs during brazing when forming this unit for mounting a noise element, resulting in cracks in the ceramic plate. It is possible to suppress a reduction in the reliability of the isothermal cycle, which becomes easier.

- the concentration of Fe contained on the brazed surface side is less than 0.1 wt%, and therefore, due to the difference in thermal expansion coefficient between the ceramic plate and the circuit layer during the thermal cycle, Even when stress is about to occur at these joint interfaces, the stress can be absorbed by plastically deforming the brazing surface side of the circuit layer. Thereby, it is possible to suppress the stress acting on the joint interface, and the joint reliability between the ceramic plate and the circuit layer can be improved.

- the concentration of Fe contained on the brazing surface side is preferably 0.05 wt% or less in view power of the separation progress rate at the interface between the ceramic plate and the circuit layer.

- the brazing surface side is directed toward the surface opposite to the brazing surface force in the circuit layer.

- the portion may be located between 10% and 50% of the thickness of the circuit layer, and the remaining portion may be the opposite surface side.

- a circuit layer is brazed on the surface of a ceramic board, and a cooling water channel is formed inside on the back surface.

- a method for manufacturing a power element mounting unit with a brazing device wherein the surface of the ceramic plate has an A1 brazing material foil and a purity of not less than 0.05 wt% and not more than 1. Owt%.

- the laminate After placing the circuit layer member that also has an A1 alloy strength of 5 wt% or more and 99.95 wt% or less in this order to form a laminate, the laminate is heated while being pressed in the laminating direction to melt the brazing material foil Then, the power element mounting unit according to the above aspect of the present invention is formed by brazing the circuit layer member to the surface of the ceramic plate.

- the laminate is pressurized and brazed in the laminating direction, so that the surface of the ceramic plate and the circuit layer member can be satisfactorily brazed.

- Fe contained on the brazing surface side with the ceramic plate can be satisfactorily dissolved in the brazing material melted at the joining interface. Therefore, the concentration of Fe contained on the brazing surface side of the circuit layer is less than 0.1 wt%, and the concentration of Fe contained on the surface side opposite to the brazing surface of the parenthesis is 0.

- the unit for use can be reliably formed.

- the power module according to another aspect of the present invention is a power module in which a circuit layer is brazed to the front surface of a ceramic plate and a cooler having a cooling water channel formed inside is brazed to the back surface.

- a power module comprising an element mounting unit and a power element solder-bonded to the surface of the circuit layer, wherein the power element mounting unit is the power element mounting unit according to the above aspect of the present invention.

- a power element mounting unit is for mounting a single element in which a circuit layer is brazed on the surface of a ceramic plate and a cooler is brazed on the back surface.

- the cooler includes a top plate portion having a brazing surface with the ceramic plate, and a hanging portion that is suspended from the top plate portion on a surface opposite to the brazing surface,

- the overall average purity is 98.Owt% or more and 99.9wt% or less. It is made of gold, and the Fe content in the surface layer portion on the brazed surface side is less than 0.1 wt%, and is included in the portion excluding the surface layer portion in the bracket cooler.

- the Fe concentration is 0.1% or more.

- the concentration of Fe in the surface layer on the brazed surface side of the top plate is less than 0.1 lwt%. Even when stress is generated at these joint interfaces due to the difference in thermal expansion coefficients, it is possible to absorb the stress by plastically deforming the surface layer portion. As a result, it is possible to suppress the stress generated at the joint interface, and the joint reliability between the ceramic plate and the cooler can be improved.

- the Fe concentration in the portion excluding the surface layer portion is 0.1 lwt% or more, and the bending rigidity of the portion excluding the surface layer portion can be maintained at the current level.

- the brazing material foil and the cooler are arranged in this order on the back surface of the ceramic plate to form a laminate, and then the laminate is pressed in the stacking direction. Even if the cooler is formed thin, it is possible to suppress the buckling of the hanging portion of the cooler.

- the concentration of Fe contained in the surface layer portion is preferably 0.05 wt% or less in view power of the separation progress rate at the bonding interface between the ceramic plate and the cooler.

- the cooler includes, for example, a bottom plate portion connected to the hanging portion in parallel with the top plate portion in addition to the top plate portion and the hanging portion.

- a method for manufacturing a power element mounting unit includes a power element in which a circuit layer is brazed on the surface of a ceramic board and a cooler is brazed on the back surface.

- a method for manufacturing a mounting unit wherein a brazing material foil and a cooler are arranged in this order on the back surface of a ceramic plate to form a laminated body, and then the laminated body is pressed in the laminating direction.

- the power element mounting unit according to the above aspect of the present invention is formed by heating in a heated state, melting the brazing material foil, and brazing a cooler to the back surface of the ceramic plate.

- a power module according to another aspect of the present invention includes a power element mounting unit in which a circuit layer is brazed to the surface of a ceramic plate and a cooler is brazed to the back surface, and a circuit layer.

- a power element mounting unit is a cooler in which a circuit layer is brazed to the front surface of a ceramic plate, and the material strength of the circuit layer is the same as that of the circuit layer.

- the thickness is C3, 0.75 -B3 ⁇ C3 ⁇ l. 5 ⁇ ⁇ 3 ⁇ 3 ⁇ ⁇ 3 is satisfied.

- the thickness of the circuit layer is A3, the thickness of the ceramic plate is ⁇ 3, and the thickness of the top plate of the cooler is C3, C3 Therefore, the difference between the bending rigidity of the cooler and the bending rigidity of the circuit layer can be reduced to reduce the amount of warping that occurs during brazing when forming a power element mounting unit.

- it is possible to suppress the generation of cracks in the solder layer that joins the power element to the surface of the circuit layer in the power module.

- 1.5 ⁇ ⁇ 3 ⁇ 3 ⁇ ⁇ 3 is satisfied, the expansion and contraction along the surface direction of the surface of the circuit layer when using the heat cycle of the power module can be restrained by the ceramic plate.

- the top plate of the cooler is more likely to be deformed due to the reduction in the difference between the flexural rigidity of the cooler and the bending rigidity of the circuit layer. This makes it possible to suppress the use of the power element mounting unit.

- a circuit layer is brazed to the surface of a ceramic plate, and a cooler having the same material force as the material of the circuit layer is provided on the back. Soldered to the surface of the circuit layer and the brazed power element mounting unit

- the power element mounting unit is the power element mounting unit according to the above aspect of the present invention.

- a circuit layer is brazed to the surface of the ceramic plate, and a heat block having pure Cu or Cu alloy power is soldered to the surface of the circuit layer.

- a power element mounting board in which a power element is soldered to the surface of this heat block, and the circuit layer has an overall average purity of 9 8. Owt% or more and 99.9 wt% or less. It is formed of an alloy, and the concentration of Fe contained in the surface side where the heat block is soldered is 0.1 lwt% or more, and the Fe block contained in the back side where the ceramic plate is brazed. The concentration is supposed to be less than 0. lwt%.

- the concentration of Fe contained on the back side of the circuit layer is less than 0.1 wt%. Even when a stress is about to be generated at these joint interfaces due to the difference, it is possible to absorb this stress by plastically deforming the back side of the circuit layer. As a result, it is possible to suppress the stress acting on the bonding interface, and to improve the bonding reliability between the ceramic plate and the circuit layer when the heat cycle is used.

- the Fe concentration in the surface side of the circuit layer is 0.1 lwt% or more, the surface side is gradually hardened as the circuit layer repeatedly undergoes thermal deformation during use of the heat cycle. And the amount of plastic deformation occurring in this portion can be suppressed.

- This makes it possible to reduce the load caused by the plastic deformation of the circuit layer when using the thermal cycle, which acts on the solder layer that joins the surface of the circuit layer and the heat block, and when using the thermal cycle, Even if cracks occur in this solder layer, the progress can be suppressed.

- the heat block is interposed between the circuit layer and the power element, it is conducted from the power element to the heat block via the solder layer.

- the thickness of the circuit layer is 0.4 mm or more, and the back surface side of the circuit layer is 0.04 mm or more from the back surface to the surface of the circuit layer and has a thickness of the circuit layer.

- the portion may be located up to half or less, and the remaining portion may be on the surface side of the circuit layer. In this case, the above-described effects are surely achieved.

- a circuit layer is brazed to the surface of a ceramic plate, and the surface of the circuit layer is made of pure Cu or a Cu alloy.

- the laminate is pressed and brazed in the laminating direction, so that the surface of the ceramic plate and the circuit layer member can be satisfactorily brazed.

- Fe contained on the brazing surface side with the ceramic plate can be dissolved well in the brazing material melted at the bonding interface. Therefore, the Fe concentration contained in the front side of the circuit layer is 0.1 lwt% or more, and the Fe concentration contained in the back side of the circuit layer is less than 0.1 lwt%.

- the substrate can be reliably formed.

- a circuit layer is brazed to the surface of the ceramic plate, and a heat block having pure Cu or Cu alloy power is soldered to the surface of the circuit layer.

- a power element mounting board and a power element soldered to the surface of the heat block, wherein the power element mounting board is the power element mounting board according to the aspect of the invention. is there.

- the circuit layer and the power element are soldered together. Even if a lead-free solder material is used for this purpose, it is possible to prevent cracks from being easily developed in this solder layer during the thermal cycle.

- the power element mounting unit of the present invention in which a cooler having a cooling water channel formed inside is brazed on the back surface, even if the cooler is brazed directly to the back surface of the ceramic plate, It is possible to suppress the occurrence of warping when the unit for mounting one element is formed, and to suppress deterioration in thermal cycle reliability.

- the thermal module reliability of the power module without reducing the buckling strength of the hanging portion of the cooler. Can be improved.

- the power element mounting unit of the present invention in which the circuit layer and the cooler having the same material strength are brazed, even if the cooler is brazed directly to the back surface of the ceramic plate, The generation of warp when forming a single element mounting unit can be suppressed, and the deterioration of thermal cycle reliability can be suppressed.

- the power element mounting substrate provided with the heat block of the present invention it is possible to improve the bonding reliability when using the power cycle of the power module.

- FIG. 1 is an overall view showing a power module to which a power element mounting substrate according to an embodiment of the present invention is applied.

- FIG. 2 is a diagram showing an example of Fe concentration distribution in the thickness direction of the circuit layer shown in FIG.

- FIG. 3 is an overall view showing a power module to which a power element mounting substrate according to another embodiment of the present invention is applied.

- FIG. 4 is an overall view showing a power module according to another embodiment of the present invention.

- FIG. 5 is an overall view showing a power module according to another embodiment of the present invention.

- FIG. 6 is a diagram showing an example of Fe concentration distribution in the thickness direction of the circuit layer shown in FIG.

- FIG. 7 is an overall view showing a power module according to another embodiment of the present invention.

- FIG. 8 is an overall view showing a power module according to another embodiment of the present invention.

- FIG. 9 is a diagram showing an example of Fe concentration distribution in the thickness direction of the top plate in the cooler shown in FIG.

- FIG. 10 is an overall view showing a power module according to another embodiment of the present invention.

- FIG. 11 is an overall view showing a power module according to another embodiment of the present invention.

- FIG. 12 is an overall view showing a power module to which a power element mounting substrate according to another embodiment of the present invention is applied.

- FIG. 13 is a diagram showing an example of Fe concentration distribution in the thickness direction of the circuit layer shown in FIG. 12.

- FIG. 1 is an overall view showing a power module to which a power element mounting substrate according to an embodiment of the present invention is applied.

- This power module 10 has a power element mounting substrate 14 having a circuit layer 12 brazed to a ceramic plate 11 and a metal layer 13 brazed to the front surface of the ceramic module 11; A semiconductor chip (power element) 16 soldered to the surface of the circuit layer 12 via a solder layer 15 and a heat sink 17 brazed or soldered to the surface of the metal layer 13 are provided.

- Examples of materials for forming these members include A1N and A1 in the ceramic plate 11, for example.

- solder layer 15 examples include lead-free solder materials such as Sn—Ag—Cu.

- brazing material for brazing the ceramic plate 11 to the circuit layer 12 and the metal layer 13 examples include an A1 type brazing material such as an A1—Si type.

- Si is 11.6 wt% or less, and is an Al—Si brazing material containing a concentration higher than the concentration of Si contained in a circuit layer member to be described later that forms the circuit layer 12.

- the circuit layer 12 is formed of an A1 alloy having an overall average purity of 98. Owt% or more and 99.9 wt% or less, and the brazing surface 12a side with the ceramic plate 11

- the Fe concentration is less than 0.1 wt%, and the Fe concentration on the surface 12b side opposite to the brazed surface 12a is not less than 0. ⁇ %.

- the brazing surface 12a side is located on the circuit layer 12! /, And is located from 10% to 50% of the thickness of the circuit layer 12 from the brazing surface 12a to the opposite surface 12b. The remaining portion is the opposite surface 12b side.

- the concentration of Fe contained on the brazing surface 12a side is preferably 0.05 wt% or less in view of the peeling progress rate at the interface between the ceramic plate 11 and the circuit layer 12.

- the concentration of Fe contained in the circuit layer 12 was set to 15 ⁇ V , an electric current value of 5 X 10 _8 A, and a spot size of 30 ⁇ m in an electron beam microanalyzer (EPMA) device. Then, in the circuit layer 12, the brazing surface 12a side and the opposite surface 12b side were measured at 10 arbitrary locations, and the average value of the obtained measurement values was calculated. In addition, the average purity of the entire circuit layer 12 is decomposed by first immersing the circuit layer 12 in a water bath (about 100 ° C.) in which water, hydrofluoric acid and nitric acid are mixed in the same amount. This decomposed sample was measured by using the ICP-AES method (inductively coupled plasma single emission spectrometry).

- ICP-AES method inductively coupled plasma single emission spectrometry

- a method for manufacturing the power element mounting substrate 14 configured as described above will be described.

- a circuit layer member having the same shape and size as the circuit layer 12 is formed.

- the circuit layer member has an average A1 alloy strength with a purity of 98.5 wt% or more and 99.9 wt% or less of Fe containing 0.05 wt% or more and 1. Owt% or less on average.

- the brazing material foil and the circuit layer member are arranged in this order on the surface of the ceramic plate 11.

- a metal layer member having the same shape and size as the metal layer 13 is disposed on the back surface of the ceramic plate 11 via a brazing material foil.

- the ceramic plate 11 forms a laminate in which the brazing material foil and the circuit layer member are arranged in this order on the front surface, and the brazing material foil and the metal layer member are arranged in this order on the back surface.

- the laminate is placed in an inert atmosphere, a reducing atmosphere, or in a vacuum (vacuum degree 1 X 10 " 5 Torr (l. 33 X 10 _3 Pa) or less).

- the circuit layer member is brazed onto the surface of the ceramic plate 11 by heating at 577 ° C or more and 660 ° C or less under pressure of 0.098MPa to 0.294MPa and melting the brazing foil.

- the circuit layer 12 is formed by bonding by brazing, and the back surface of the ceramic plate 11 and the metal layer member are bonded by brazing to form the metal layer 13 to form the power element mounting substrate 14.

- the concentration of Fe contained on the opposite surface 12 b side is not less than 0.0%. Therefore, as the circuit layer 12 repeatedly undergoes thermal deformation during the thermal cycle, the opposite surface 12b side can be gradually cured, and the amount of plastic deformation generated in this portion can be suppressed. This makes it possible to reduce the load acting on the solder layer 15 due to plastic deformation of the circuit layer 12 during the thermal cycle, and even if cracks occur in the solder layer 15 during the thermal cycle, Even if a lead-free solder material is used for soldering the circuit layer 12 and the semiconductor chip 16, the progress of cracks in the solder layer 15 during thermal cycling is suppressed. It can be done.

- the concentration of Fe contained on the brazing surface 12a side is less than 0.1 wt%, so that each thermal expansion coefficient of the ceramic plate 11 and the circuit layer 12 during the thermal cycle. Even when a stress is about to be generated at the joint interface due to the difference between the two, the stress can be absorbed by plastically deforming the brazing surface 12a side of the circuit layer 12. As a result, the stress acting on the joint interface can be suppressed, and the It is also possible to improve the bonding reliability between the lamix plate 11 and the circuit layer 12. In addition, if the concentration of Fe contained on the brazing surface 12a side is 0.05 wt% or less, such an effect is surely achieved.

- the laminate is pressed in the laminating direction, so that an oxide film is formed at the bonding interface between the surface of the ceramic plate 11 and the circuit layer member.

- Fe contained in the brazing surface side with the ceramic plate 11 can be well dissolved in the brazing material melted at the joining interface. . Therefore, the concentration of Fe contained on the brazing surface 12a side of the circuit layer 12 is less than 0.1 lw t%, and the concentration of Fe contained on the surface 12b side opposite to the brazing surface 12a is 0.1%.

- the power element mounting substrate 14 as described above can be reliably formed.

- the concentration of Si contained in the brazing material foil that joins the circuit layer member and the ceramic plate 11 is higher than the concentration of Si contained in the circuit layer member, Combined with the increase in the critical solid solution amount of Si in the circuit layer member, it becomes possible to diffuse the Si contained in the molten brazing material toward the inside of the circuit layer member by the force on the brazing surface side.

- the concentration of Si contained in the brazing surface side can be made higher than that on the opposite surface side.

- the limit solid solution amount of Fe on the brazing surface side becomes smaller than that on the opposite surface side, so that the concentration of Fe contained on the brazing surface side can be made lower than that on the opposite surface side. It becomes possible. Therefore, as described above, in the circuit layer member, Fe contained on the brazing surface side with the ceramic plate 11 can be satisfactorily dissolved in the brazing material melted at the joining interface. In combination with this, the power element mounting substrate 14 can be more reliably formed.

- the metal layer member or the circuit layer member may be formed by punching a base material or may be formed by a so-called etching method.

- the solder layer 15 is not limited to the solder material having a lead-free solder material such as Sn—Ag—Cu, for example, but also a solder material containing Pb, such as a PbSn material. The solder material may be used. Even in this case, the same effects as those of the above-described embodiment can be obtained.

- the power element mounting substrate 14 includes the circuit layer 12, the ceramics plate 11, and the metal layer 13, and the metal layer 13 and the heat sink 17 are brazed or soldered. Instead of this, for example, as shown in Fig.

- a power element mounting board 14 is used in which the back surface of the ceramic plate 11 and the heat sink 17 are brazed directly without providing the metal layer 13. May be. Even in such a configuration, it is possible to prevent cracks from being easily developed in the buried layer 15 during the thermal cycle.

- the structure of the heat sink 17 is not limited to the one provided with the heat radiation fins illustrated in FIG. 1.As shown in FIG. 3, a multi-hole tube type or other structure is applied. May be.

- the metal layer member and the circuit layer member will be joined to the ceramic plate 11 with the A1 alloy, the metal layer 13 and the circuit layer 12 having a purity of 99.5 wt% containing about 0.3 wt% of Fe.

- the material was Al—Si (A1 was 92.5 wt%, Si was 7.5 wt%), and the ceramic plate 11 was formed by AIN.

- the metal layer 13 and the circuit layer 12 were each about 0.6 mm

- the brazing material foil was about 30 / zm

- the ceramic plate 11 was about 0.635 mm.

- the metal layer 13 was a square in plan view, and the vertical and horizontal dimensions were about 30 mm. Then, the laminate is placed in a vacuum of 600 ° C.

- the power element mounting substrate 14 was formed by pressurizing at 098 MPa to 0.294 MPa.

- the region on the brazed surface 12a side and the region on the opposite surface 12b side were determined using an electronic microanalyzer (EPMA). Specifically, the circuit layer 12 is cut, and the acceleration voltage is 15 kV, the current value is 5 X 10 _8 A, the spot size is 1 ⁇ m, and one point measurement is performed from the brazed surface 12a of the cross section to the opposite surface 12b. EPMA line analysis was performed under conditions of a time of 5 seconds and a movement interval of 1 ⁇ m. The result is shown in Fig.2.

- the Fe concentration is lower in the region from the brazing surface 12a to the opposite surface 12b up to 0.15mm (equivalent to about 25% of the thickness of the circuit layer 12). On the surface 12b side, it is confirmed that the Fe concentration is high.

- each Fe concentration of the brazing surface 12a side of the circuit layer 12 and the opposite surface 12b side is Using ⁇ under the conditions of accelerating voltage 15kV, current value 5 X 10 _8 A, spot size 30 ⁇ m, measure the brazing surface 12a side and the opposite surface 12b side at any 10 locations, It calculated

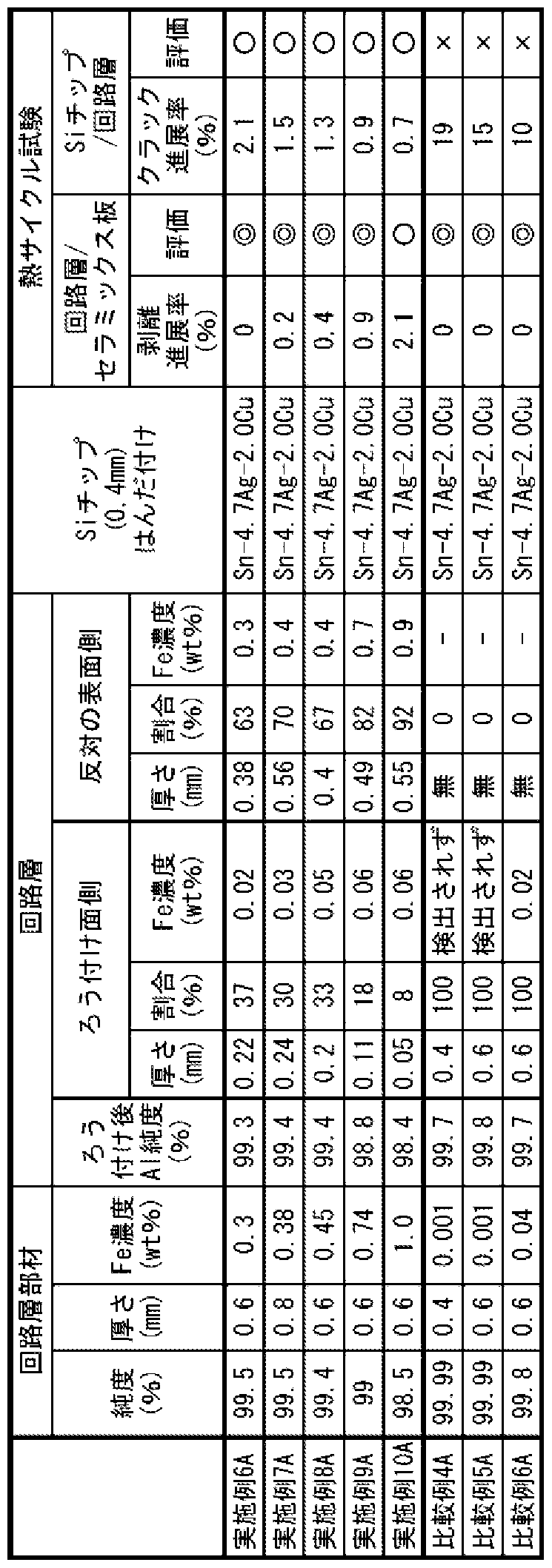

- the circuit layer member that forms the circuit layer eight types of power element mounting substrates are formed by varying at least one of the purity, thickness, and Fe concentration of A1, and the circuit layers of each power element mounting substrate The concentration of Fe contained in the brazing surface side, the concentration of Fe contained in the opposite surface side, the thickness of the brazing surface side, and the thickness of the opposite surface side are different from each other.

- the surface of the circuit layer of each of these power element mounting substrates was soldered with a Sn-Ag-Cu lead-free solder on the surface of the circuit layer from 40 ° C to 105 ° C. After heating up in about 3 minutes, 2000 thermal cycles were applied with a temperature history of 105 ° C and 40 ° C in 10 minutes as a temperature history.

- each power element mounting substrate was cut at five locations in the stacking direction, and each cut surface was polished, and then the cut surface was imaged using an optical microscope.

- the total length of the bonding interface of the circuit layer and the length of delamination progress were measured.

- the ratio of the peel progress length to the total length of the joint interface was calculated.

- the total length of the solder layer that solder-joins the circuit layer and the Si chip and the length of crack propagation generated in the solder layer were measured.

- the ratio of the crack progress length to the total length of the solder layer that is, the average value of the crack progress rate was calculated.

- the case where the peeling progress rate power was exceeded was evaluated as X, the case where it was 2% or more and 4% or less was rated as ⁇ , and the case where it was less than 2% was rated as ⁇ .

- the case where the crack growth rate exceeded 3% was evaluated as X, and the case where the crack growth rate was 3% or less was evaluated as ⁇ .

- the circuit layer 12 is formed of an A1 alloy having an overall average purity of 98. Owt% or more and 99.9 wt% or less, and Fe contained in the brazing surface 12a side with the ceramic plate 11 If the concentration of Fe is less than 0.1 lwt% and the concentration of Fe contained on the surface 12b side opposite to the brazed surface 12a is 0.1 lwt% or more, the above temperature cycle is 2000 cycles. Even if applied, it was confirmed that both the peeling progress rate and the crack progress rate were suppressed, and the above-mentioned effects were achieved.

- the ceramic plate 11 is made of Al 2 O 3.

- the circuit layer 12 is

- the ceramic plate 11 is made of SiN.

- A1 alloy with an average purity of 98.Owt% or more and 99.9wt% or less, and the concentration of Fe contained on the brazing surface 12a side with the ceramic plate 11 is less than 0.1 lwt%.

- the concentration of Fe contained on the surface 12b side opposite to the brazing surface 12a is 0.1 lwt% or more. In this case, it was confirmed that both the peeling progress rate and the crack progress rate could be suppressed even when the above-mentioned temperature cycle was applied 2000 times.

- FIG. 4 is an overall view showing a power module to which a power element mounting unit according to an embodiment of the present invention is applied.

- This power module 110 is a power element in which a ceramic layer 111 is brazed with a circuit layer 112 force S on the front surface thereof, and a cooler 113 having a cooling water channel 113a formed on the back surface thereof.

- a mounting unit 114 and a power element 116 soldered to the surface of the circuit layer 112 via a solder layer 115 are provided.

- Examples of materials for forming these members include A1N, Al in the ceramic plate 111, for example.

- cooler 113 includes pure Al or Al alloy

- solder layer 115 examples include lead-free solder materials such as Sn—Ag—Cu.

- solder material for brazing the ceramic plate 111, the circuit layer 112, and the cooler 113 for example, an A1-based brazing material such as an Al—Si based material can be cited.

- Si is an Al—Si brazing material containing not more than 11.6 wt% and containing a concentration higher than the concentration of Si contained in a circuit layer member described later that forms the circuit layer 112.

- the entire cooler 113 is integrally formed of pure A1 or A1 alloy or the like, and can be formed by, for example, forging or extrusion molding.

- the circuit layer 112 has an overall average purity of 98. Owt% or more 99.

- the brazing surface 112a side is a portion of the circuit layer 112 that is located from 10% to 50% of the thickness of the circuit layer 112 from the brazing surface 112a toward the opposite surface 112b, and the remaining portion. Is the opposite surface 112b side.

- the concentration of Fe contained in the circuit layer 112 was set to an acceleration voltage of 15 kV, a current value of 5 X 10 _8 A, and a spot size of 30 ⁇ m in an electron beam microanalyzer (EPMA) device. Then, the circuit layer 112 was measured at 10 arbitrary positions on the brazed surface 112a side and the opposite surface 112b side, and the average value of the obtained measured values was calculated. In addition, the average purity of the entire circuit layer 112 is decomposed by first immersing the circuit layer 112 in a water bath (approximately 100 ° C.) containing the same amount of water, hydrofluoric acid, and nitric acid. Thereafter, the decomposed sample was measured by using ICP-AES method (inductively coupled plasma-emission analysis method).

- ICP-AES method inductively coupled plasma-emission analysis method

- a circuit layer member having the same shape and size as the circuit layer 112 is formed.

- the average circuit layer member has an A1 alloy strength with an purity of 98.5 wt% or more and 99.95 wt% or less containing Fe in the range of 0.05 wt% to 1. Owt%.

- the brazing material foil and the circuit layer member are arranged in this order on the surface of the ceramic plate 111.

- a cooler 113 is disposed on the back surface of the ceramic plate 111 via a brazing filler metal foil.

- a laminated body is formed in which the brazing material foil and the circuit layer member are arranged in this order on the front surface, and the brazing material foil and the cooler 113 are arranged in this order on the back surface.

- the laminated body is placed in an inert atmosphere, a reducing atmosphere, or in a vacuum (vacuum degree 1 X 10 " 5 Torr (l. 33 X 10 _3 Pa) or less).

- the circuit layer member is brazed onto the surface of the ceramic plate 111 by heating at 577 ° C or more and 660 ° C or less by pressing at 0.098MPa to 0.294MPa and melting the brazing foil.

- the circuit layer 112 is formed by bonding by brazing, and the back surface of the ceramic plate 111 and the cooler 113 are bonded by brazing to form the power element mounting unit 114.

- the concentration of Fe contained on the opposite surface 112b side is 0.: ⁇ % or more. Therefore, it becomes possible to increase the bending rigidity of the entire circuit layer 112 and reduce the difference from the bending rigidity of the cooler 113, and at the time of brazing when forming the power element mounting unit 114 It is possible to reduce the amount of warpage that occurs, and it is possible to suppress a decrease in thermal cycle reliability, such as the ceramic plate 111 being easily cracked.

- the concentration of Fe contained on the brazing surface 112a side is less than 0.1 wt%. Even when stress is about to occur at these joint interfaces due to the difference in expansion coefficient

- the stress can be absorbed by plastically deforming the brazing surface 112a side of the circuit layer 112. Thereby, it is possible to suppress the stress acting on the joint interface, and the joint reliability between the ceramic plate 111 and the circuit layer 112 can be improved. If the concentration of Fe contained on the brazing surface 112a side is 0.05 wt% or less, such an effect is surely achieved.

- the laminate is pressed in the stacking direction, so that an oxide film is formed at the bonding interface between the surface of the ceramic plate 111 and the circuit layer member. It is possible to prevent Fe contained in the brazing surface side of the ceramic layer 111 in the circuit layer member in the brazing material melted at the joint interface. it can. Therefore, the concentration of Fe contained in the brazing surface 112a side of the circuit layer 112 is less than 0.1 wt%, and the concentration of Fe contained in the surface 112b side opposite to the brazing surface 112a is 0.1%.

- the power element mounting unit 114 as described above can be reliably formed.

- the concentration of Si contained in the brazing material foil joining the circuit layer member and the ceramic plate 111 is higher than the concentration of Si contained in the circuit layer member. Combined with the increase in the critical solid solution amount of Si in the circuit layer member, it is possible to diffuse the Si contained in the molten brazing material toward the inside of the circuit layer member.

- the concentration of Si contained on the brazing surface side can be increased more than that on the opposite surface side.

- the limit solid solution amount of Fe on the brazing surface side becomes smaller than that on the opposite surface side, so that the concentration of Fe contained on the brazing surface side can be made lower than that on the opposite surface side. It becomes possible.

- the power element mounting unit 114 can be formed more reliably.

- the entire cooler 113 is integrally formed of pure A1 or an A1 alloy or the like, the power element mounting unit that does not complicate the structure of the cooler 113. 114 can be formed, and the increase in manufacturing cost can be suppressed. In addition, the total thermal resistance in the stacking direction of the power module 110 including the power element mounting unit 114 can be reliably reduced.

- the circuit layer member may be formed by punching a base material, or may be formed by a so-called etching method.

- the force of the lead-free solder material such as Sn-Ag-Cu based on the solder material of the solder layer 115 is not limited to this.

- a solder material containing Pb such as a PbSn solder You can use the material.

- the power module 110 is a force showing a configuration in which the power element 116 is bonded to the surface of the circuit layer 112 via the solder layer 115.

- a heat spreader 117 having a composite material force such as pure Cu, Cu alloy, Cu—Mo alloy, or Cu—C may be provided between the circuit layer 112 and the power element 116.

- heat generated in the power element 116 can be conducted in the stacking direction while diffusing along the surface direction orthogonal to the stacking direction.

- the circuit layer member and the cooler 113 are made of Al alloy containing approximately 0.3 wt% of Fe and a purity of 99.5 wt%, and a brazing material for bonding the circuit layer 112 and the ceramic plate 111 to Al.

- the circuit layer 112 was about 0.8 mm

- the brazing material foil was about 30 / ⁇ ⁇

- the ceramic plate 111 was about 0.635 mm.

- the circuit layer 112 has a square shape in plan view, and the vertical and horizontal dimensions are each about 17 mm.

- the ceramic plate 111 is also a square in plan view, and the vertical and horizontal dimensions are each about 20 mm.

- the cooler 113 has an overall height, that is, a distance A1 between the surface to which the back surface of the ceramic plate 111 is brazed and the back surface opposite to this surface is about 2.5 mm.

- the overall width B1 was about 21.25 mm

- the overall length that is, the size in the direction in which the cooling water channel 113a extends (the depth direction of the paper in FIG. 4) was about 60 mm.

- the size C1 in the height direction of the cooler 113 is set to about 1.5 mm

- the size D1 in the width direction of the cooler 113 is set to about 1.25 mm.

- each of these cooling water channels 113a is formed at the center in the height direction, which is approximately 0.5 mm apart from the front and back surfaces of the cooler 113, and the distance E1 between adjacent cooling water channels 113a in the width direction of the cooler 113 is about 1 mm. 7

- the laminate is placed in a vacuum of 600 ° C. to 650 ° C. (vacuum degree: 1 ⁇ 10 ” 5 Torr (l. 33 X 1 0 _3 Pa) or less) and about 0. Pressurizing at 098 MPa to 0.294 MPa, the power element mounting unit 114 was formed.

- the region on the brazing surface 112a side and the region on the opposite surface 112b side were determined using an electronic microanalyzer (EPMA). Specifically, the circuit layer 112 is cut, and the acceleration voltage is 15 kV, the current value is 5 X 10 _8 A, the spot size is 1 ⁇ m, and the one-point measurement time from the brazed surface 112a of the cross section to the opposite surface 112b. EPMA line analysis was performed under the condition of 5 seconds and a movement interval of 1 ⁇ m. The result is shown in Fig. 6.

- EPMA electronic microanalyzer

- the Fe concentration in the region up to 0.15 mm (equivalent to about 25% of the thickness of the circuit layer 112) directed toward the surface 112b opposite to the force of the brazing surface 112a is low. Further, it is confirmed that the Fe concentration is higher in the opposite surface 112b side and becomes a region.

- the Fe concentration on the brazing surface 112a side of the circuit layer 112 and on the opposite surface 112b side is EPMA under the conditions of an acceleration voltage of 15 kV, a current value of 5 X 10 _8 A, and a spot size of 30 ⁇ m.

- Each of the affixing surface 112a side and the opposite surface 112b side was measured at an arbitrary 10 locations, and the average value was calculated.

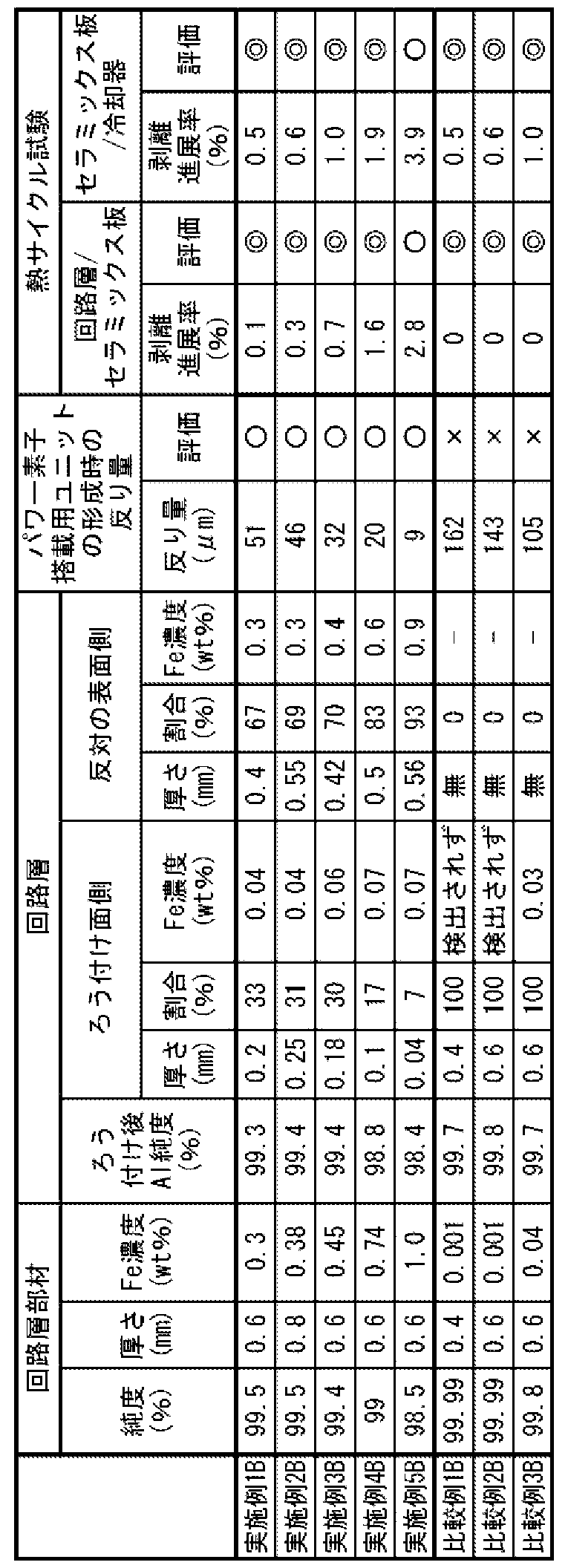

- At least one of the purity, thickness, and Fe concentration of A1 is varied to form eight types of power element mounting units, and the circuit of each power element mounting unit In the layer, at least one of the concentration of Fe contained on the brazing surface side, the concentration of Fe contained on the opposite surface side, the thickness on the brazing surface side, and the thickness on the opposite surface side is different.

- a Si chip with the same performance was soldered with Sn-Ag-Cu lead-free solder from 40 ° C to 105 ° C.

- each power element mounting unit was cut at five locations in the stacking direction, and each cut section was polished, and then the cut surface was imaged using an ultrasonic imaging device (140 MHz probe).

- the total length of the bonding interface between the ceramic plate and the circuit layer and the separation progress length were measured.

- the ratio of the peel progress length to the total length of the joint interface that is, the average value of the peel progress rates was calculated.

- the total length and the peeling progress length of the bonding interface of the ceramic plate and the cooler were respectively measured, and the average value of the peeling progress rate at the bonding interface was calculated.

- the amount of warpage generated in each power element mounting unit was measured in advance, and the amount of warpage was 100 ⁇ m or more.

- the product was evaluated as X, and less than 100 ⁇ m as ⁇ .

- the circuit layer 112 is formed of an A1 alloy having an overall average purity of 98.Owt% or more and 99.9wt% or less, and the concentration of Fe contained in the brazing surface 112a side with the ceramic plate 111 is reduced. If the concentration of Fe contained on the surface 112b side opposite to the brazing surface 112a of the bracket is less than 0.1 wt%, the brazing when forming the power element mounting unit 114 will be performed. It was confirmed that the amount of warpage generated at the time of application was suppressed, and even when the above-mentioned temperature cycle was applied for 2000 cycles, each of the above-described peeling progress rates was suppressed, and the above-mentioned effects were achieved. Although not described in Table 4, the power module of the example In Joule 110, it was also confirmed that cracks did not occur in ceramic plate 111 even when the temperature cycle was applied.

- FIG. 7 is an overall view showing a power module to which a power element mounting unit according to an embodiment of the present invention is applied.

- the power module 210 has a circuit layer 212 force S brazed to the front surface of the ceramic plate 211 and a power element mounting unit 214 with a cooler 213 brazed to the back surface, and a circuit layer.

- a power element 216 soldered to the surface of 212 via a solder layer 215 is provided.

- a lead-free solder material, or a solder material containing Pb such as PbSn, and the circuit layer 212 may be pure A1 or A1 alloy.

- an A1-based brazing material such as an Al—Si based material can be used.

- the cooler 213 is suspended from a top plate portion 219 having a brazing surface 218 with the ceramic plate 211 and a surface 220 opposite to the brazing surface 218 in the top plate portion 219. And a drooping portion 221.

- the cooler 213 has a bottom plate portion 222 disposed in parallel with the top plate portion 219 at a position facing the opposite surface 220 in addition to the top plate portion 219 and the hanging portion 221.

- a plurality of hanging parts 221 connect the top plate part 219 and the bottom plate part 222, and are provided with a plurality of predetermined intervals in a certain direction and extending in a direction orthogonal to the certain direction. It is considered to be a part.

- a plurality of refrigerant supply passages 213a are defined by the surface 220 opposite to the top plate portion 219, the bottom plate portion 222, and the plurality of hanging portions 221, and the cooler 213 includes a plurality of refrigerant supply passages 213a therein. It has a so-called multi-hole tube.

- the top plate portion 219, the bottom plate portion 222, and the hanging portion 221 are integrally formed of an A1 alloy having an overall average purity of 98.Owt% or more and 99.9wt% or less.

- the cooler 213 is formed by, for example, forging or extrusion molding.

- the concentration of Fe contained in the surface layer portion 219a on the brazing surface 218 side is less than 0.1 lwt%, and In this cooler 213, the concentration of Fe contained in the portion excluding the surface layer portion 219a is 0.1 wt% or more.

- the ceramic plate 211 whose brazing surface 218 is larger than the back surface of the ceramic plate 211 is brazed to a portion of the brazing surface 218 located inward of the outer peripheral edge.

- the surface layer portion 219a is formed only on the brazed surface 218 where the back surface of the ceramic plate 211 is brazed.

- the concentration of Fe contained in the cooler 213 was set to an acceleration voltage of 15 kV, an electric current value of 5 X 10 _8 A, and a spot size of 30 ⁇ m in an electron beam microanalyzer (EPMA) device.

- EPMA electron beam microanalyzer

- the average purity of A1 in the entire cooler 213 is decomposed by first immersing the cooler 213 in a water bath (approximately 100 ° C) containing the same amount of water, hydrofluoric acid and nitric acid. After that, this decomposed sample was determined to use the ICP-AES method (inductively coupled plasma-emission analysis method).

- the brazing material foil and the circuit layer 212 are arranged in this order on the surface of the ceramic plate 211, and the brazing material foil and the cooler 213 are arranged on the back surface of the ceramic plate 211 in this order.

- a brazing material foil and a circuit layer 212 are arranged in this order on the front surface, and a laminated body in which the brazing material foil and the cooler 213 are arranged in this order on the back surface is formed.

- the plan view shape of the brazing filler metal foil disposed between the ceramic plate 211 and the circuit layer 212 is substantially the same shape and size as the plan view shape of the circuit layer 212, and is between the ceramic plate 211 and the cooler 213.

- the shape of the brazing filler metal foil arranged in plan view is substantially the same shape and size as the plan view shape of the ceramic plate 211.

- the laminated body is placed in an inert atmosphere, a reducing atmosphere, or in a vacuum (vacuum degree 1 X 10 " 5 Torr (l. 33 X 10 _3 Pa) or less).

- a vacuum vacuum degree 1 X 10 " 5 Torr (l. 33 X 10 _3 Pa) or less.

- the circuit layer 12 is joined to the surface of the ceramic plate 11 by brazing, and the cooler 213 is joined to the back surface of the ceramic plate 211 by brazing to form the power element mounting unit 214.

- the Fe concentration in the surface layer portion 219a on the brazing surface 218 side of the top plate portion 219 is less than 0.1 lw t%. Therefore, even when a stress is about to be generated at the joint interface due to the difference in thermal expansion coefficient between the ceramic plate 211 and the cooler 213 during use in a thermal cycle, the surface layer This stress can be absorbed by plastically deforming the portion 219a. As a result, it is possible to suppress the stress generated at the bonding interface, and the bonding reliability between the ceramic plate 211 and the cooler 213 can be improved.

- the concentration of Fe contained in the portion excluding the surface layer portion 219a is set to 0.1 wt% or more, and the bending rigidity of the portion excluding the surface layer portion 219a is maintained at the current level.

- the cooler 213 is formed to be thin. It is possible to prevent the drooping portion 221 of the vessel 213 from buckling.

- the thermal cycle reliability of the power module 210 without reducing the buckling strength of the drooping portion 221 of the cooler 213 can be improved.

- the concentration of Fe contained in the surface layer portion 219a of the cooler 213 is 0.05 wt% or less, such an effect can be surely achieved.

- the entire cooler 213 is integrally formed of the A1 alloy, the power element mounting unit 214 that does not complicate the structure of the cooler 213 is formed. Therefore, the increase in manufacturing cost can be suppressed, and the total thermal resistance in the stacking direction of the power module 210 including the power element mounting unit 214 can be surely reduced.

- the circuit layer 212 formed of pure A1 or A1 alloy instead of the force shown for the circuit layer 212 formed of pure A1 or A1 alloy, for example, the circuit layer 212 formed of pure Cu or Cu alloy may be adopted.

- a cooler in which fins are brazed to the opposite surface 220 of the top plate 219 in the wide refrigerant supply path may be used.

- the cooler 213 does not have the bottom plate portion 222 but includes the top plate portion 219 and the hanging portion 221, and the opposite surface 220 of the top plate portion 219 has a pin on the opposite surface 220.

- a cooler in which a plurality of hanging portions 221 as fins are suspended may be employed.

- the power module 210 has been configured such that the power element 216 is bonded to the surface of the circuit layer 212 via the solder layer 215 as a power module 210, but instead, for example, As shown in FIG. 8, a heat spreader 217 having a composite material force such as pure Cu, Cu alloy, Cu-Mo alloy, or Cu-C may be provided between the circuit layer 212 and the power element 216. . In this case, heat generated in the power element 216 can be conducted in the stacking direction while diffusing along the surface direction orthogonal to the stacking direction.

- the back surface of the ceramic plate 211 and the brazing surface 218 may have the same shape and the same size, and the outer peripheral edges of the ceramic plates 211 may be brazed. .

- the surface layer portion 219a is formed over the entire brazing surface 218.

- the circuit layer 212 and the cooler 213 are made of Al alloy containing approximately 0.3 wt% of Fe and having a purity of 99.5 wt%, and a brazing material for bonding the circuit layer 212 and the ceramic plate 211 to Al.

- — Si-based (A1: 92.5wt%, Si: 7.5wt%) and ceramic plate 211 were formed of A1N.

- the circuit layer 212 was about 0.8 mm

- the brazing material foil was about 30 / ⁇ ⁇

- the ceramic plate 211 was about 0.635 mm.

- the circuit layer 212 has a square shape in plan view, and the vertical and horizontal dimensions are each about 17 mm.

- the ceramic plate 211 is also a square in plan view, and the vertical and horizontal dimensions are each about 20 mm.

- the cooler 213 has an overall height, that is, a distance A2 between the brazing surface 218 and the bottom surface of the bottom plate 222 is about 2.5 mm, and an overall width B2 is about 21.25 mm. Further, the overall length, that is, the size in the direction in which the refrigerant supply path 213a extends (the depth direction of the paper surface in FIGS. 7 and 8) is set to about 60 mm. Also, each refrigerant supply path 213a having a square shape in plan view Then, the size C2 in the height direction of the cooler 213 was set to about 1.5 mm, and the size D2 in the width direction of the cooler 213 was set to about 1.25 mm.

- Each of these refrigerant supply paths 213a is formed at the center in the height direction where the bottom surface forces of the brazing surface 218 and the bottom plate portion 222 are also separated by about 0.5 mm, respectively, and in the width direction of the cooler 213.

- the distance E2 between adjacent refrigerant supply paths 213a was set to about lmm. That is, the thickness of the top plate portion 219 and the bottom plate portion 222 was set to about 0.5 mm, and the thickness of the hanging portion 221 was set to about 1 mm.

- the laminate is placed in a vacuum of 600 ° C. to 650 ° C. (vacuum degree: 1 ⁇ 10 ” 5 Torr (l. 33 X 1 0 _3 Pa) or less) and about 0. Pressurizing at 098 MPa to 0.294 MPa, the power element mounting unit 214 was formed.

- an electronic microanalyzer (EPMA) was used to determine the surface layer portion 219a and other portions.

- the cooler 213 is cut, and the thickness of the top plate 219 from the brazing surface 218 of the cross section to the opposite surface 220 of the top plate 219 constituting the upper surface of the refrigerant supply path 213a.

- EPMA line analysis was performed for the entire direction (approx. 0.50 mm) under the conditions of accelerating voltage 15 kV, current value 5 X 10 _8 A, spot size 1 ⁇ m, single point measurement time 5 seconds, moving interval: m. . The results are shown in Fig. 9.

- the Fe concentration is low in the region from the brazing surface 218 to the opposite surface 220 to about 0.10 mm, and the top plate 219 is closer to the opposite surface 220 side than this region. It is confirmed that the Fe concentration is increasing in the part.

- each Fe concentration in the surface layer portion 219a and the portion other than the surface layer portion 219a is determined by using E PMA under the conditions of an acceleration voltage of 15 kV, a current value of 5 X 10 _8 A, and a spot size of 30 m.

- E PMA acceleration voltage of 15 kV

- a current value of 5 X 10 _8 A current value of 5 X 10 _8 A

- a spot size of 30 m For each of the part 219a and the part other than the surface layer part 219a, measurement was performed at 10 arbitrary positions, and the average value was calculated.

- each power element mounting unit was cut at five locations in the stacking direction, and each cut section was polished, and then the total length of the bonding interface between the ceramic plate and the cooler and the length of delamination progressed on this cut surface was measured respectively. Then, the ratio of the peel progress length to the total length of the joint interface, that is, the average value of the peel progress rate was calculated.

- the cooler 213 is formed of an A1 alloy having an overall average purity of 98. Owt% or more and 99.9 wt% or less, and the Fe concentration in the surface layer portion 219a is 0. ⁇ % If the concentration of Fe contained in the cooler 213 excluding the surface layer portion 219a is less than 0.0% in the cooler 213 of the parenthesis, the peeling will occur even if 2000 cycles of the temperature cycle are applied. It was confirmed that the progress rate was suppressed and the above-mentioned effects were achieved.

- a cooler made of A1 alloy or pure A1 with an overall average purity of more than 99.9 wt% It was also confirmed that even if an attempt was made to braze the ceramic plate to form a power element mounting unit, the drooping part could not be buckled.

- FIG. 10 is an overall view showing a power module to which the power element mounting unit according to one embodiment of the present invention is applied.

- the power module 310 includes a power element mounting unit 314 in which a circuit layer 312 is brazed on the surface of a ceramic plate 311 and a cooler 313 having a cooling water channel 313a formed on the back is brazed.

- a power element 316 soldered to the surface of the circuit layer 312 via a solder layer 315 is provided.

- the cooler 313 is made of the same material as that of the circuit layer 312.

- Examples of the material forming these members include A1N and A1 for the ceramic plate 311.

- solder layer 315 examples include lead-free solder materials such as Sn—Ag—Cu.

- the entire cooler 313 is integrally formed of pure A1 or A1 alloy or the like, and can be formed by, for example, forging or extrusion molding.

- the thickness of the circuit layer 312 is A3

- the thickness of the ceramic plate 311 is B3

- the cooler 313 has a top plate portion 319 having a brazing surface 318 with the ceramic plate 311.

- the thickness C3 of the top plate portion 319 is the distance between the brazing surface 318 and the upper surface of the cooling water channel 313a.

- the brazing material foil and the circuit layer 312 are arranged in this order on the surface of the ceramic plate 311, and the cooler 313 is arranged on the back surface of the ceramic plate 311 via the brazing material foil.

- the ceramic plate 311 forms a laminate in which the brazing material foil and the circuit layer 312 are arranged in this order on the front surface, and the brazing material foil and the cooler 313 are arranged in this order on the back surface.

- the laminated body is placed in an inert atmosphere, a reducing atmosphere, or in a vacuum (vacuum degree 1 X 10 " 5 Torr (l. 33 X 10 _3 Pa) or less).

- the circuit layer 312 is brazed onto the surface of the ceramic plate 311 by heating at 577 ° C or more and 660 ° C or less under pressure of 0.098MPa to 0.294MPa to melt the brazing foil.

- the power device mounting unit 314 is formed by bonding the cooler 313 to the back surface of the ceramic plate 311 by brazing.

- the thickness of the circuit layer 312 is A3, the thickness of the ceramic plate 311 is B3, and the top plate portion 319 of the cooler 313 is When the thickness is C3, it satisfies C3 1.5 A3. Therefore, the difference between the bending rigidity of the cooler 313 and the bending rigidity of the circuit layer 312 is reduced, and the power element mounting unit 314 It is possible to reduce the amount of warping that occurs during brazing when forming the solder, and in the power module 310, it is possible to suppress the occurrence of cracks in the solder layer 315 that joins the power element 316 to the surface of the circuit layer 312. It becomes possible.

- the ceramic plate 311 causes the elastic deformation along the surface direction of the circuit layer 312 when the thermal cycle of the power module 310 is used. It becomes possible to restrain, and even if a crack occurs in the solder layer 315, the progress can be suppressed. Furthermore, since 0.75 'B3 ⁇ C3 is satisfied, the top plate 3 19 of the cooler 313 is deformed due to the reduction in the difference between the flexural rigidity of the cooler 313 and the flexural rigidity of the circuit layer 312. Therefore, it is possible to prevent the use of the power element mounting unit 314 from being hindered.

- the entire cooler 313 is integrally formed of pure A1 or A1 alloy or the like, the power element mounting unit that does not complicate the structure of the cooler 313. 314 can be formed, and an increase in manufacturing cost thereof can be suppressed.

- the power module 310 has a force showing a configuration in which the power element 316 is bonded to the surface of the circuit layer 312 via the solder layer 315.

- a heat spreader 317 having a composite material force such as pure Cu, Cu alloy, Cu—Mo alloy, or Cu—C is provided between the circuit layer 312 and the power element 316. Also good.

- heat generated in the power element 316 can be conducted in the stacking direction while diffusing along the surface direction orthogonal to the stacking direction.

- the circuit layer 312 and the cooler 313 are connected to an A1 alloy having a purity of 99.5 wt%, and the brazing material joining the circuit layer 312 and the cooler 313 to the ceramic plate 311 is an A1-Si system (A1 92.5 wt% and Si 7.5 wt%), and the ceramic plate 311 was formed from A1N.

- the thickness A3 of the circuit layer 312 is about 400 m, 600 m or 800 m

- the brazing material box is about 30 ⁇ m

- the thickness B3 of the ceramic plate 311 is about 500 ⁇ m or about 635 ⁇ m. did.

- the circuit layer 312 has a square shape in plan view, and the vertical and horizontal dimensions are about 17 mm.

- the ceramic plate 311 is also a square in plan view, and the vertical and horizontal dimensions are about 20 mm.

- the cooler 313 has an overall height, that is, a distance D3 between the brazing surface 318 of the top plate portion 319 and the back surface opposite to the brazing surface 318 is about 2.5 mm.

- the overall width E 3 was about 21.25 mm, and the overall length, that is, the size in the direction in which the cooling water channel 313a extends (the depth direction of the paper surface in FIG. 10) was about 60 mm.

- each cooling water channel 313a having a square shape in plan view is formed in the central portion in the height direction, which is separated by an equal distance in the brazing surface 318 and the back surface force in the cooler 313, and has a thickness C3 of the top plate portion 319.

- the distance F3 between the cooling channels 313a adjacent in the width direction of the cooler 313 is about lmm.

- the power element mounting unit 314 was formed by pressurizing at 098 MPa to 0.294 MPa.

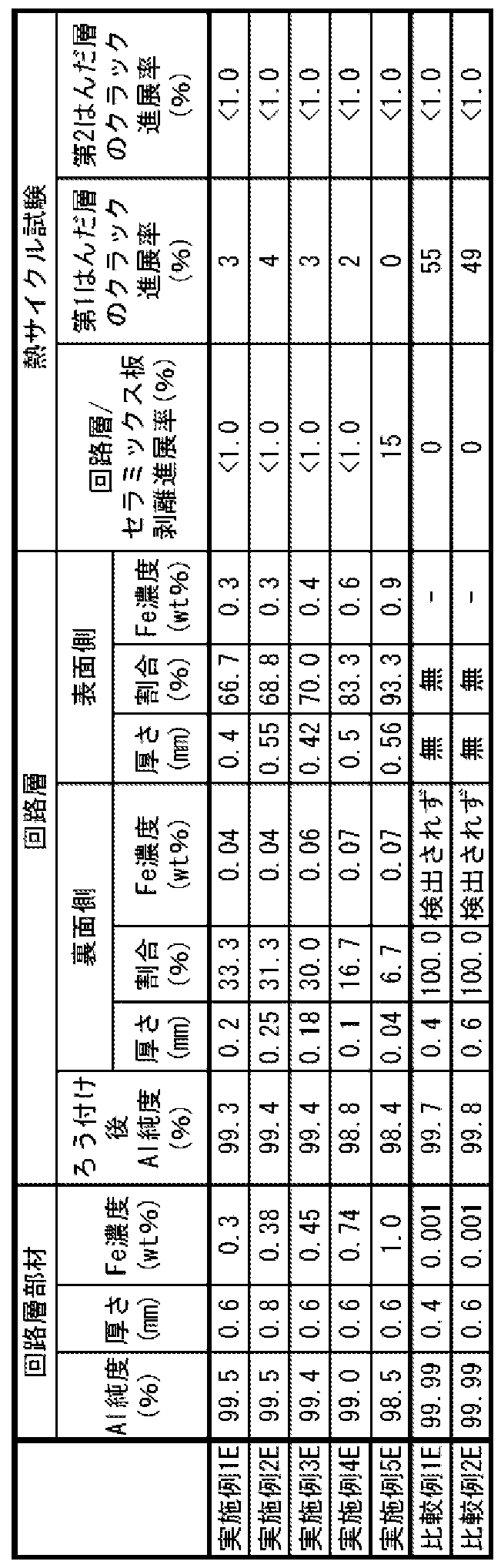

- At least one of the thicknesses of the circuit layer, ceramic plate, and top plate of the cooler is made different, and the other portions are for mounting six types of power elements in the same manner as the specific embodiment described above.

- a unit was formed. And each of these power element mounting units A Si chip with the same performance soldered to the surface of the circuit layer with Sn-Ag-Cu lead-free solder, heated from 40 ° C to 105 ° C in about 3 minutes, and then 105 ° From C to 2000 ° C, 2000 thermal cycles were applied, with the temperature history of cooling down to 40 ° C in 10 minutes as one cycle.

- each power element mounting unit was cut at five locations in the stacking direction, and each cut section was polished, and then the cut surface was imaged using an optical microscope. The total length of the solder layer that solder-bonds to the Si chip and the length of crack propagation that occurred in this solder layer were measured. Then, the ratio of the crack progress length to the total length of the solder layer, that is, the average value of the crack progress rate was calculated.

- the amount of warpage occurring in each power element mounting unit was measured in advance.

- the relationship between the thickness A3 of the circuit layer 12, the thickness B3 of the ceramic plate 11, and the thickness C3 of the top plate portion 19 of the cooler 13 is 0.75-B3 ⁇ C3 ⁇ l.5 If ⁇ 3 ⁇ 3 ⁇ 3 is satisfied, the amount of warpage generated during brazing when forming the element mounting unit 14 can be suppressed, and even if the force is applied to the above temperature cycle 2000 cycles Thus, it was confirmed that the crack progress rate was suppressed and the above-mentioned effects were achieved. Although not described in Table 6, in the power module 310 of the example, it was also confirmed that cracks were not generated in the ceramic plate 311 even when the temperature cycle was applied.

- FIG. 12 is an overall view showing a power module to which the power element mounting substrate according to one embodiment of the present invention is applied.

- a circuit layer 412 is brazed to the surface of the ceramic plate 411, and a heat block 413 made of pure Cu or Cu alloy is soldered to the surface 412b of the circuit layer 412 via the first solder layer 414.

- a power element mounting substrate 415 bonded and a semiconductor chip (power element) 417 solder-bonded to the surface of the heat block 413 via a second solder layer 416 are provided.

- the power element mounting substrate 415 further includes a cooler 418 brazed to the back surface of the ceramic plate 411.

- the cooler 418 is a so-called multi-hole tube having a plurality of refrigerant supply passages 418a therein.

- the heat block 413 is made of a Cu alloy having a purity of 50 wt% or more or pure Cu.

- Examples of the material forming these members include A1N and A1 in the ceramic plate 411, for example.

- brazing material for brazing the ceramic plate 411, the circuit layer 412, and the cooler 418, for example, an Al-based brazing material such as an Al—Si based material can be cited.

- this brazing material contains Si at a concentration of 11.6 wt% or less and higher than the concentration of Si contained in a circuit layer member described later that forms the circuit layer 412.

- the circuit layer 412 has an overall average purity of 98. Owt% or higher 99.

- the thickness of the circuit layer 412 is 0.4 mm or more, and the back surface 412a side of the circuit layer 412 is 0.04 mm or more in the circuit layer 412 from the back surface 412a toward the front surface 412b.

- the portion is located up to half or less the thickness of the circuit layer 412, and the remaining portion is on the surface 412 b side of the circuit layer 412.

- the concentration of Fe contained on the back surface 412a side is preferably 0.05 wt% or less from the viewpoint of reducing the peeling progress rate at the bonding interface between the ceramic plate 411 and the back surface 412a of the circuit layer 412. .

- the back surface 412a side and the front surface 412b side are specified by the circuit layer 41.

- Cross section obtained by cutting 2 and using an electronic microanalyzer (EPMA) device, accelerating voltage 15 kV, current value 5 X 10 _8 A, spot size 1 EPMA line analysis was performed under the conditions of ⁇ m, 1 point measurement time 5 seconds, and movement interval 1 ⁇ m. From the obtained data, the region where the Fe concentration is 0.1 lwt% or more and less than 0.1 lwt% This is done by specifying the boundary with the region.

- the acceleration voltage is set to 15 kV and the current value is set to 5 ⁇ 10 _8 A in the EPMA apparatus, and the spot size is set to 30 m. Then, the measurement was performed at any 10 points in the cross section, and the average value of the obtained measurement values was calculated to obtain the concentration of Fe contained in each of the back surface 412a side and the front surface 412b side.

- the average purity of the circuit layer 412 as a whole is first decomposed by immersing the circuit layer 412 in a water bath (approximately 100 ° C) containing the same amount of water, hydrofluoric acid and nitric acid. Thereafter, the decomposed sample was measured by using ICP-AES method (inductively coupled plasma-emission analysis method).

- a circuit layer member having the same shape and size as the circuit layer 412 is formed.

- the circuit layer member is made of an A1 alloy having a purity of 98.5 wt% or more and 99.95 wt% or less containing Fe in the range of 0.05 wt% to 1. Owt% on average.

- the brazing material foil and the circuit layer member are arranged in this order on the surface of the ceramic plate 411.

- a cooler 418 is disposed on the back surface of the ceramic plate 411 via a brazing filler metal foil.

- a laminated body is formed in which the brazing material foil and the circuit layer member are arranged in this order on the front surface, and the brazing material foil and the cooler 418 are arranged in this order on the back surface.

- the laminated body is placed in an inert atmosphere, a reducing atmosphere, or in a vacuum (vacuum degree 1 X 10 " 5 Torr (l. 33 X 10 _3 Pa) or less).