KR101838130B1 - 반도체 장치 및 그 제작방법 - Google Patents

반도체 장치 및 그 제작방법 Download PDFInfo

- Publication number

- KR101838130B1 KR101838130B1 KR1020127022955A KR20127022955A KR101838130B1 KR 101838130 B1 KR101838130 B1 KR 101838130B1 KR 1020127022955 A KR1020127022955 A KR 1020127022955A KR 20127022955 A KR20127022955 A KR 20127022955A KR 101838130 B1 KR101838130 B1 KR 101838130B1

- Authority

- KR

- South Korea

- Prior art keywords

- insulating layer

- transistor

- layer

- electrode

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D88/00—Three-dimensional [3D] integrated devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/20—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by three-dimensional arrangements, e.g. with cells on different height levels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/471—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having different architectures, e.g. having both top-gate and bottom-gate TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D87/00—Integrated devices comprising both bulk components and either SOI or SOS components on the same substrate

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0416—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a single floating gate transistor and no select transistor, e.g. UV EPROM

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0433—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a single floating gate transistor and one or more separate select transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

- G11C16/28—Sensing or reading circuits; Data output circuits using differential sensing or reference cells, e.g. dummy cells

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Dram (AREA)

- Electroluminescent Light Sources (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

본 발명의 반도체 장치는 제 1 트랜지스터와, 제 1 트랜지스터 위에 형성된 절연층과, 절연층 위에 형성된 제 2 트랜지스터를 가지며, 제 1 트랜지스터는 제 1 채널형성영역을 포함하고, 제 2 트랜지스터는 제 2 채널형성영역을 포함하며, 제 1 채널형성영역은 제 2 채널형성영역과 다른 반도체 재료를 포함하여 구성되고, 절연층은 제곱평균제곱근 거칠기가 1nm 이하인 표면을 갖는다.

Description

금속 산화물 중에는 반도체 특성을 나타내는 것이 있다. 반도체 특성을 나타내는 금속 산화물로서는 예를 들면 산화텅스텐, 산화주석, 산화인듐, 산화아연 등이 있으며, 이와 같은 금속 산화물을 채널형성영역에 사용한 박막 트랜지스터가 이미 알려져 있다(예를 들면, 특허문헌 1~특허문헌 4, 비특허문헌 1 등 참조).

그런데, 금속 산화물로는 일원계 산화물뿐만 아니라, 다원계 산화물도 알려져 있다. 예를 들면 호모로거스 상(homologous phase)을 갖는 InGaO3(ZnO)m(m: 자연수)은 In, Ga 및 Zn을 갖는 다원계 산화물 반도체로서 알려져 있다(예를 들면, 비특허문헌 2~비특허문헌 4 등 참조).

그리고, 상기와 같은 In-Ga-Zn계 산화물로 구성되는 산화물 반도체도 박막 트랜지스터의 채널형성영역에 적용가능한 것이 확인되고 있다(예를 들면, 특허문헌 5, 비특허문헌 5 및 비특허문헌 6 등 참조).

또한, 단결정 실리콘 등의 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터는 이동도가 높고, 충분한 고속 동작이 가능하지만, 오프 전류는 실질적으로 제로라 할 수 있을 정도로 작은 것이 아니다. 이 때문에, 반도체 장치의 동작상태에 상관없이 약간의 전류가 흐르게 되어, 기억장치나 액정표시장치 등의 전하홀딩형 반도체 장치를 구성할 경우에는 충분한 전하홀딩기간을 확보하는 것이 곤란하였다.

따라서, 개시하는 발명의 일 양태는 산화물 반도체를 사용한 트랜지스터와, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 적층하여, 새로운 구조의 반도체 장치를 제공하는 것을 목적 중 하나로 한다.

또한, 본 발명의 다른 일 양태는 평탄성이 양호한 표면 위에 산화물 반도체층을 형성함으로써 트랜지스터 특성을 향상시킨 트랜지스터를, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터에 적층한 반도체 장치이다. 예를 들면, 다음과 같은 구성을 채용할 수 있다.

본 발명의 일 양태는 제 1 트랜지스터와, 제 1 트랜지스터 위에 형성된 절연층과, 절연층 위에 형성된 제 2 트랜지스터를 가지며, 제 1 트랜지스터는 제 1 채널형성영역과, 제 1 채널형성영역 위에 형성된 제 1 게이트 절연층과, 제 1 채널형성영역과 중첩하여 제 1 게이트 절연층 위에 형성된 제 1 게이트 전극과, 제 1 채널형성영역과 전기적으로 접속하는 제 1 소스 전극 및 제 1 드레인 전극을 포함하고, 제 2 트랜지스터는 산화물 반도체를 포함하여 구성되는 제 2 채널형성영역과, 제 2 채널형성영역과 전기적으로 접속하는 제 2 소스 전극 및 제 2 드레인 전극과, 제 2 채널형성영역과 중첩하여 형성된 제 2 게이트 전극과, 제 2 채널형성영역과 제 2 게이트 전극 사이에 형성된 제 2 게이트 절연층을 포함하며, 제 1 채널형성영역은 제 2 채널형성영역과 다른 반도체 재료를 포함하여 구성되고, 절연층은 제곱평균제곱근 거칠기가 1nm 이하인 표면을 갖는 반도체 장치이다.

또한, 제 1 게이트 전극의 상면이 노출되어 절연층 표면과 동일면이 되고, 상기 제 1 게이트 전극의 상면에서 제 1 게이트 전극과 제 2 소스 전극 또는 제 2 드레인 전극이 서로 접하도록 하는 것이 바람직하다.

또한, 본 발명의 다른 일 양태는 제 1 채널형성영역과, 제 1 채널형성영역 위에 형성된 제 1 게이트 절연층과, 제 1 채널형성영역과 중첩하여 제 1 게이트 절연층 위에 형성된 제 1 게이트 전극과, 제 1 채널형성영역과 전기적으로 접속하는 제 1 소스 전극 및 제 1 드레인 전극을 포함하는 제 1 트랜지스터를 형성하고, 제 1 트랜지스터 위에 절연층을 형성하며, 절연층 표면의 제곱평균제곱근 거칠기가 1nm 이하가 되도록 절연층을 평탄화하고, 절연층 위에 접하게 산화물 반도체를 포함하여 구성되는 제 2 채널형성영역과, 제 2 채널형성영역과 전기적으로 접속하는 제 2 소스 전극 및 제 2 드레인 전극과, 제 2 채널형성영역과 중첩하여 형성된 제 2 게이트 전극과, 제 2 채널형성영역과 제 2 게이트 전극 사이에 형성된 제 2 게이트 절연층을 포함하는 제 2 트랜지스터를 형성하며, 제 1 채널형성영역은 제 2 채널형성영역과 다른 반도체 재료를 포함하는 반도체 장치의 제작방법이다.

또한, 본 발명의 다른 일 양태는 제 1 채널형성영역과, 제 1 채널형성영역 위에 형성된 제 1 게이트 절연층과, 제 1 채널형성영역과 중첩하여 제 1 게이트 절연층 위에 형성된 제 1 게이트 전극과, 제 1 채널형성영역과 전기적으로 접속하는 제 1 소스 전극 및 제 1 드레인 전극을 포함하는 제 1 트랜지스터를 형성하고, 제 1 트랜지스터 위에 절연층을 형성하며, 절연층 표면의 제곱평균제곱근 거칠기가 1nm 이하가 되고, 또한 제 1 게이트 전극의 상면이 노출되어 절연층 표면과 동일면이 되도록 절연층을 평탄화하며, 절연층 위에 접하게 산화물 반도체를 포함하여 구성되는 제 2 채널형성영역과, 제 2 채널형성영역과 전기적으로 접속하는 제 2 소스 전극 및 제 2 드레인 전극과, 제 2 채널형성영역과 중첩하여 형성된 제 2 게이트 전극과, 제 2 채널형성영역과 제 2 게이트 전극 사이에 형성된 제 2 게이트 절연층을 포함하는 제 2 트랜지스터를 형성하며, 제 2 소스 전극 또는 제 2 드레인 전극은 제 1 게이트 전극의 상면에 접하도록 형성되고, 제 1 채널형성영역은 제 2 채널형성영역과 다른 반도체 재료를 포함하는 반도체장치의 제작방법이다.

또한, 제 2 채널형성영역은 절연층의 표면에 형성되는 것이 바람직하다. 또한, 절연층의 표면은 화학적 기계적 연마(Chemical Mechanical Polishing : CMP) 처리에 의해 형성되는 것이 바람직하다. 또한, 제 1 트랜지스터는 제 1 채널형성영역을 사이에 끼우도록 형성된 불순물영역을 갖는 것이 바람직하다.

또한, 본 명세서 등에 있어, 용어 '위'나 '아래' 는 구성요소의 위치 관계가 '바로 위' 또는 '바로 아래'인 것을 한정하는 것이 아니다. 예를 들면 "게이트 절연층 위의 게이트 전극"이란 표현의 경우, 게이트 절연층과 게이트 전극 사이에 다른 구성요소를 포함하는 것을 제외하지 않는다.

또한, 본 명세서 등에 있어, 용어 '전극'이나 '배선'은 이들 구성요소를 기능적으로 한정하는 것이 아니다. 예를 들면, '전극'은 '배선'의 일부로서 사용될 수도 있으며, 그 반대도 또한 마찬가지이다. 그리고, 용어 '전극'이나 '배선'은 복수의 '전극'이나 '배선'이 일체로 형성되어 있는 경우 등도 포함한다.

또한, '소스'나 '드레인'의 기능은 서로 다른 극성의 트랜지스터를 채용하는 경우나 회로 동작에서 전류의 방향이 변화할 경우에는 서로 바뀔 수도 있다. 이 때문에, 본 명세서에서는 용어 '소스'나 '드레인'은 서로 바꿔 사용할 수 있는 것으로 한다.

또한, 본 명세서 등에 있어서, '전기적으로 접속'에는 '어떤 전기적 작용을 갖는 것'을 통해 접속되어 있는 경우가 포함된다. 여기서, '어떤 전기적 작용을 갖는 것'은 접속 대상들간의 전기신호의 주고 받음을 가능하게 하는 것이면 특별히 제한을 받지 않는다.

예를 들면, '어떤 전기적 작용을 갖는 것'에는 전극이나 배선을 비롯하여, 트랜지스터 등의 스위칭 소자, 저항 소자, 인덕터, 캐패시터, 기타 각종 기능을 갖는 소자 등이 포함된다.

이와 같이, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터와, 산화물 반도체를 사용한 트랜지스터를 일체로 구비하는 구성으로 함으로써, 각각의 특성의 이점을 살린 새로운 반도체 장치를 실현할 수 있다.

또한, 평탄성이 양호한 표면 위에 산화물 반도체를 형성함으로써 트랜지스터 특성을 향상시킨 트랜지스터를, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터에 적층한 반도체 장치를 제공할 수 있다.

도 2는 반도체 장치의 제작공정에 따른 단면도.

도 3은 반도체 장치의 제작공정에 따른 단면도.

도 4는 반도체 장치의 제작공정에 따른 단면도.

도 5는 반도체 장치의 제작공정에 따른 단면도.

도 6은 반도체 장치의 단면도 및 평면도.

도 7은 반도체 장치의 단면도 및 평면도.

도 8은 반도체 장치의 단면도 및 평면도.

도 9는 반도체 장치의 단면도 및 평면도.

도 10은 반도체 장치의 제작공정에 따른 단면도.

도 11은 반도체 장치의 제작공정에 따른 단면도.

도 12는 반도체 장치의 제작공정에 따른 단면도.

도 13은 반도체 장치의 제작공정에 따른 단면도.

도 14는 반도체 장치의 단면도 및 평면도.

도 15는 반도체 장치의 제작에 사용하는 반도체 기판의 제작공정에 따른 단면도.

도 16은 반도체 장치의 제작공정에 따른 단면도.

도 17은 반도체 장치의 회로도.

도 18은 반도체 장치의 회로도.

도 19는 반도체 장치의 회로도.

도 20은 반도체 장치를 사용한 전자기기를 설명하기 위한 도면,

도 21은 실시예 1의 AFM상을 나타낸 도면.

도 22는 실시예 1의 AFM상을 나타낸 도면.

또한, 도면 등에서 나타낸 각 구성의 위치, 크기, 범위 등은 이해를 쉽게 하기 위해, 실제의 위치, 크기, 범위 등을 나타내고 있지않은 경우가 있다. 이 때문에, 개시하는 발명은 반드시 도면 등에 개시된 위치, 크기, 범위 등에 한정되는 것이 아니다.

또한, 본 명세서 등에서 '제 1', '제 2', '제 3' 등의 서수는 구성요소의 혼동을 피하기 위해 붙인 것으로, 수적으로 한정하는 것이 아님을 밝힌다.

(실시형태 1)

본 실시형태에서는 개시하는 발명의 일 양태에 따른 반도체 장치의 구성 및 그 제작방법에 대해 도 1~도 5를 참조하여 설명한다.

<반도체 장치의 단면 구성>

도 1은 반도체 장치의 구성의 일 예이며, 반도체 장치의 단면을 나타낸다. 도 1에 도시된 반도체 장치는 하부에 제 1 반도체 재료를 사용한 트랜지스터(160)를 가지며, 상부에 제 2 반도체 재료를 사용한 트랜지스터(162)를 갖는 것이다. 여기서, 제 1 반도체 재료와 제 2 반도체 재료는 서로 다른 재료로 하는 것이 바람직하다. 예를 들면, 제 1 반도체 재료를 산화물 반도체 이외의 반도체 재료로 하고, 제 2 반도체 재료를 산화물 반도체로 할 수 있다. 산화물 반도체 이외의 반도체 재료로서는 예를 들면 실리콘, 게르마늄, 실리콘 게르마늄, 탄화실리콘, 또는 갈륨 비소 등을 사용할 수 있으며, 단결정 반도체를 사용하는 것이 바람직하다. 그 외에, 유기 반도체 재료 등을 사용하여도 좋다. 이와 같은 반도체 재료를 사용한 트랜지스터는 고속 동작이 용이하다. 한편, 산화물 반도체를 사용한 트랜지스터는 오프 전류를 충분히 저감하는 것을 가능하게 한다.

예를 들면, 산화물 반도체 이외의 반도체 재료를 사용한 하부 트랜지스터(160)로, 고속의 동작이 요구되는 논리회로나 구동회로를 형성할 수 있다. 또한, 산화물 반도체를 사용한 상부 트랜지스터(162)로, 충분한 전하홀딩기간이 요구되는 기억회로나 액정표시장치의 표시소자 등을 형성할 수 있다. 그리고, 이들을 일체로 구비하는 구성으로 함으로써, 각각의 특성의 이점을 살린 새로운 반도체 장치를 실현할 수 있다.

또한, 상기 트랜지스터는 모두 n채널형 트랜지스터인 것으로서 설명하지만, p채널형 트랜지스터를 사용할 수 있는 것은 말할 것까지도 없다. 또한, 개시하는 발명의 기술적인 본질은 오프 전류가 충분히 저감된, 산화물 반도체를 사용한 트랜지스터와, 충분한 고속 동작이 가능한, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 일체로 구비하는 점이기 때문에, 반도체 장치에 사용되는 재료나 반도체 장치의 구조 등, 반도체 장치의 구체적인 구성을 여기에서 나타내는 것으로 한정할 필요는 없다.

도 1의 트랜지스터(160)는 반도체 재료(예를 들면, 실리콘 등)를 포함하는 기판(100)에 형성된 채널형성영역(116)과, 채널형성영역(116)을 사이에 끼우도록 형성된 불순물영역(120)과, 불순물영역(120)에 접하는 금속화합물영역(124)과, 채널형성영역(116) 위에 형성된 게이트 절연층(108)과, 게이트 절연층(108) 위에 형성된 게이트 전극(110)을 갖는다. 또한, 도면에 있어, 명시적으로는 소스 전극이나 드레인 전극을 갖지 않는 경우가 있지만, 편의상, 이와 같은 상태를 포함하여 트랜지스터라 부르는 경우가 있다. 또한, 이 경우, 트랜지스터의 접속관계를 설명하기 위해, 소스 영역이나 드레인 영역을 포함하여 소스 전극이나 드레인 전극으로 표현하는 일이 있다. 즉, 본 명세서에 있어, 소스 전극의 기재에는 소스 영역이 포함되고, 드레인 전극의 기재에는 드레인 영역이 포함될 수 있다.

또한, 기판(100) 위에는 트랜지스터(160)를 둘러싸도록 소자분리절연층(106)이 형성되어 있으며, 트랜지스터(160) 위에 절연층(128) 및 절연층(130)이 형성되어 있다. 또한, 도시하고 있지는 않지만, 트랜지스터(160)의 금속화합물영역(124)의 일부는 소스 전극이나 드레인 전극으로서 기능하는 전극을 통해 배선에 접속되어 있다. 또한, 고집적화를 실현하기 위해서는 도 1에 나타낸 바와 같이 트랜지스터(160)가 측벽(side wall) 절연층을 갖지 않는 구성으로 하는 것이 바람직하다. 한편, 트랜지스터(160)의 특성을 중시하는 경우에는 게이트 전극(110)의 측면에 측벽 절연층을 형성하고, 그 측벽 절연층과 중첩하는 영역에 형성된 불순물 농도가 다른 영역을 포함하여 불순물영역(120)을 형성하여도 좋다.

도 1의 트랜지스터(162)는 절연층(130) 위에 형성된 소스 전극 또는 드레인 전극(142a) 및 소스 전극 또는 드레인 전극(142b)과, 소스 전극 또는 드레인 전극(142a) 및 소스 전극 또는 드레인 전극(142b)과 전기적으로 접속되어 있는 산화물 반도체층(144)와, 소스 전극 또는 드레인 전극(142a), 소스 전극 또는 드레인 전극(142b), 산화물 반도체층(144)을 덮는 게이트 절연층(146)과, 게이트 절연층(146) 위에 산화물 반도체층과 중첩하도록 형성된 게이트 전극(148a)과, 소스 전극 또는 드레인 전극(142a)과 산화물 반도체층(144) 사이의, 게이트 전극(148a)과 중첩하는 영역에 형성된 절연층(143a)과, 소스 전극 또는 드레인 전극(142b)과 산화물 반도체층(144) 사이의, 게이트 전극(148a)과 중첩하는 영역에 형성된 절연층(143b)을 갖는다. 또한, 소스 전극 또는 드레인 전극과 게이트 전극과의 사이의 용량을 저감하기 위해서는 절연층(143a) 및 절연층(143b)을 형성하는 것이 바람직하지만, 절연층(143a) 및 절연층(143b)을 형성하지 않는 구성으로 하는 것도 가능하다.

여기서, 산화물 반도체층(144)은 수소 등의 불순물이 충분히 제거됨으로써 또는 충분한 산소가 공급됨으로써 고순도화된 것인 것이 바람직하다. 구체적으로는 예를 들면 산화물 반도체층(144)의 수소 농도는 5×1019atoms/cm3 이하, 바람직하게는 5×1018atoms/cm3 이하, 보다 바람직하게는 5×1017atoms/cm3 이하로 한다. 또한, 상술한 산화물 반도체층(144) 중의 수소 농도는 이차이온 질량분석법(SIMS: Secondary Ion Mass Spectroscopy)으로 측정되는 것이다. 이와 같이 수소 농도가 충분히 저감되어 고순도화되고, 충분한 산소 공급에 의해, 산소 결핍에 기인하는 에너지 갭 중의 결함 준위가 저감된 산화물 반도체층(144)에서는, 수소나 산소 결함 등에서 유래하는 캐리어 농도가 1×1012atoms/cm3 미만, 바람직하게는 1×1011atoms/cm3 미만, 보다 바람직하게는 1.45×1010atoms/cm3 미만이 된다. 산화물 반도체층(144)을 갖는 트랜지스터에서는 오프 전류를 충분히 작게 하는 것이 가능하다. 예를 들면, 산화물 반도체층(144)의 막두께가 30nm이고 채널 길이가 2μm인 트랜지스터의, 실온(25℃)에서의 채널 길이 1μm 당 오프 전류(게이트 바이어스 -3V)는 100zA(1zA(zeptoampere)는 1×10-21A) 이하, 바람직하게는 10zA 이하가 된다. 이와 같이 고순도화된 산화물 반도체(이하, 본 명세서에서는 i형화(진성화) 또는 실질적으로 i형화된 산화물 반도체라고도 한다)를 사용함으로써, 매우 뛰어난 오프 전류 특성의 트랜지스터(162)를 얻을 수 있다.

여기서, 산화물 반도체층(144)은 제곱평균제곱근(RMS : Root Mean Square) 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하인 표면을 갖는 절연층(130) 위에 형성된다. 이와 같이 평탄성이 양호한 표면 위에 산화물 반도체층(144)을 형성함으로써, 산화물 반도체층(144)의 평탄성 및 균일성을 양호한 것으로 할 수 있다. 단, 산화물 반도체층의 평탄성 및 균일성은 적어도 산화물 반도체층의 채널형성영역이 포함되는 부분에 대해 양호한 것으로 할 수 있으면 된다. 또한, 평탄성 및 균일성이 양호한 산화물 반도체층(144)을 사용함으로써, 트랜지스터(162)의 트랜지스터 특성을 향상시킬 수 있다. 특히 산화물 반도체층(144)의 막두께를 10nm 정도 이하로 할 경우, 이와 같이 평탄성이 양호한 표면 위에 산화물 반도체층(144)을 형성함으로써, 산화물 반도체층(144)의 단 끊어짐 등을 방지할 수 있다.

평탄성 및 균일성이 양호한 산화물 반도체층(144)을 사용함으로써, 산화물 반도체층의 계면에서의 캐리어 산란 방지, 계면 준위 저감을 도모할 수 있다. 이로써, 트랜지스터(162)의 이동도의 향상, S값 및 오프 전류의 저감을 도모하며 트랜지스터 특성을 향상시킬 수 있다. 또한, 산화물 반도체층(144)의 평탄성을 향상시킴으로써, 트랜지스터(162)의 게이트 누설 전류를 저감할 수 있다.

또한, 본 명세서 등에 있어서, 제곱평균제곱근(RMS) 거칠기는 원자간력 현미경(AFM ; Atomic Force Microscope)을 사용하여 측정 면적 1μm×1μm로 측정하는 것으로 한다.

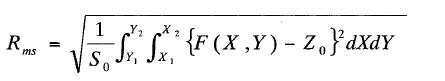

또한, 본 명세서 등에 있어서, 제곱평균제곱근(RMS) 거칠기란 단면 곡선에 대한 RMS 거칠기를 측정면에 대해 적용할 수 있도록 3차원으로 확장한 것이다. 기준면에서 지정면까지의 편차의 제곱을 평균한 값의 제곱근으로서 표현할 수 있으며, 다음과 같은 식으로 주어진다.

또한, 측정면이란 전체 측정 데이터가 나타내는 면이며, 하기의 식으로 표현한다.

또한, 지정면이란 거칠기 계측의 대상이 되는 면으로, 좌표 (X1,Y1)(X1,Y2)(X2,Y1)(X2,Y2)로 표시되는 4점에 의해 둘러싸이는 직사각형 영역으로 하고, 지정면이 이상적으로 평탄하다고 했을 때의 면적을 S0라 한다. 또한, S0는 하기의 식으로 구할 수 있다.

또한, 기준면이란 지정면의 평균 높이에서의, XY 평면과 평행한 면을 말한다. 즉, 지정면의 높이 평균값을 Z0라 할 때, 기준면의 높이도 Z0으로 표현된다. 또한, Z0은 하기의 식으로 구할 수 있다.

또한, 도 1의 트랜지스터(162)에서는 미세화에 기인하여 소자 사이에 발생하는 누설을 억제하기 위해, 섬형상으로 가공된 산화물 반도체층(144)을 사용하고 있는데, 섬형상으로 가공되지 않은 구성을 채용하여도 좋다. 산화물 반도체층을 섬형상으로 가공하지 않는 경우에는 가공시의 에칭으로 인한 산화물 반도체층(144)의 오염을 방지할 수 있다.

또한, 트랜지스터(162)에 있어서, 소스 전극 또는 드레인 전극(142a), 및 소스 전극 또는 드레인 전극(142b)의 단부는 테이퍼 형상인 것이 바람직하다. 소스 전극 또는 드레인 전극(142a), 소스 전극 또는 드레인 전극(142b)의 단부를 테이퍼 형상으로 함으로써, 산화물 반도체층(144)의 피복성이 향상되며 단 끊어짐을 방지할 수 있기 때문이다. 여기서, 테이퍼 각도는 예를 들면 30°이상 60°이하로 한다. 또한, 테이퍼 각도란, 테이퍼 형상을 갖는 층(예를 들면, 소스 전극 또는 드레인 전극(142a))을 그 단면(기판의 표면과 직교하는 면)에 수직인 방향에서 관찰했을 때에, 해당층의 측면과 저면이 이루는 경사각을 나타낸다.

트랜지스터(162) 위에는 절연층(150)이 형성되어 있으며, 절연층(150) 위에는 절연층(152)이 형성되어 있다. 그리고, 절연층(152) 위에는 트랜지스터(160) 또는 트랜지스터(162)와 접속하는 배선(156)이 형성된다.

<반도체 장치의 제작방법>

이어, 상기 반도체 장치의 제작방법의 일 예에 대해 설명한다. 이하에서는 먼저 하부 트랜지스터(160)의 제작방법에 대해 도 2 및 도 3을 참조하여 설명하고, 그 후, 상부 트랜지스터(162)의 제작방법에 대해 도 4 및 도 5를 참조하여 설명한다.

<하부 트랜지스터의 제작방법>

먼저, 반도체 재료를 포함하는 기판(100)을 준비한다(도 2(A) 참조). 반도체 재료를 포함하는 기판(100)으로서는 실리콘이나 탄화실리콘 등의 단결정 반도체기판, 다결정 반도체 기판, 실리콘 게르마늄 등의 화합물 반도체 기판, SOI 기판 등을 적용할 수 있다. 여기에서는 반도체 재료를 포함하는 기판(100)으로서, 단결정 실리콘 기판을 사용하는 경우의 일 예에 대해 나타낸 것으로 한다. 또한, 일반적으로 'SOI 기판'은 절연 표면 위에 실리콘 반도체층이 형성된 구성의 기판을 말하는데, 본 명세서 등에서는 절연 표면 위에 실리콘 이외의 재료로 이루어진 반도체층이 형성된 구성의 기판도 포함하는 것으로 한다. 즉, 'SOI 기판'이 갖는 반도체층은 실리콘 반도체층으로 한정되지 않는다. 또한, SOI 기판에는 유리 기판 등의 절연기판 위에 절연층을 통해 반도체층이 형성된 구성의 것이 포함되는 것으로 한다.

반도체 재료를 포함하는 기판(100)으로서, 특히 실리콘 등의 단결정 반도체 기판을 사용하는 경우에는 트랜지스터(160)의 동작을 고속화할 수 있기 때문에 바람직하다.

기판(100) 위에는 소자분리절연층을 형성하기 위한 마스크가 되는 보호층(102)을 형성한다(도 2(A) 참조). 보호층(102)으로서는 예를 들면 산화실리콘, 질화실리콘, 산화질화실리콘 또는 질화산화실리콘 등을 재료로 하는 절연층을 사용할 수 있다. 또한, 이 공정의 전후에, 트랜지스터의 문턱 전압을 제어하기 위해, n형의 도전성을 부여하는 불순물 원소나 p형 도전성을 부여하는 불순물 원소를 기판(100)에 첨가하여도 좋다. 반도체가 실리콘인 경우, n형의 도전성을 부여하는 불순물로서는 예를 들면 인이나 비소 등을 사용할 수 있다. 또한, p형 도전성을 부여하는 불순물로서는 예를 들면 비소, 알루미늄, 갈륨 등을 사용할 수 있다.

이어, 상기의 보호층(102)을 마스크로 하여 에칭을 하여, 보호층(102)으로 덮여있지 않은 영역(노출되어 있는 영역)의 기판(100) 일부를 제거한다. 이로써, 다른 반도체영역과 분리된 반도체영역(104)이 형성된다(도 2(B) 참조). 해당 에칭에는 건식 에칭을 사용하는 것이 바람직하지만, 습식 에칭을 사용하여도 좋다. 에칭가스나 에칭액에 대해서는 피에칭재료에 따라 적절히 선택할 수 있다.

그 후, 반도체영역(104)을 덮도록 절연층을 형성하고, 반도체영역(104)에 중첩하는 영역의 절연층을 선택적으로 제거함으로써, 소자분리절연층(106)을 형성한다(도 2(C) 참조). 해당 절연층은 산화실리콘, 질화실리콘, 산화질화실리콘 또는 질화산화실리콘 등을 사용하여 형성된다. 절연층의 제거방법으로서는 화학적 기계적 연마(Chemical Mechanical Polishing : CMP) 처리 등의 연마 처리나 에칭 처리 등이 있는데, 그 중 어느 것을 사용하여도 좋으며, 그들을 조합하여 사용하여도 좋다. 또한, 반도체영역(104)의 형성 후, 또는 소자분리절연층(106)의 형성 후에는 상기 보호층(102)을 제거한다.

또한, 소자분리절연층(106)의 형성방법으로서, 절연층을 선택적으로 제거하는 방법 외에, 산소를 주입함으로써 절연성의 영역을 형성하는 방법 등을 사용할 수도 있다.

이어, 반도체영역(104)의 표면에 절연층을 형성하고, 해당 절연층 위에 도전재료를 포함하는 층을 형성한다.

절연층은 이후 게이트 절연층이 되는 것으로, 예를 들면, 반도체영역(104) 표면의 열처리(열산화처리나 열질화처리 등)에 의해 형성할 수 있다. 열처리 대신에, 고밀도 플라즈마 처리를 적용하여도 좋다. 고밀도 플라즈마 처리는 예를 들면 He, Ar, Kr, Xe 등의 희가스, 산소, 산화질소, 암모니아, 질소, 수소 등 중 어느 한 혼합가스를 사용하여 수행할 수 있다. 물론, CVD법이나 스퍼터링법 등을 사용하여 절연층을 형성하여도 좋다. 해당 절연층은 산화실리콘, 산화질화실리콘, 질화산화실리콘, 질화실리콘, 산화하프늄, 산화알루미늄, 산화탄탈, 산화이트륨, 하프늄 실리게이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 실리게이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 알루미네이트(HfAlxOy(x>0, y>0)) 등을 포함하는 단층 구조 또는 적층 구조로 하는 것이 바람직하다. 또한, 절연층의 두께는 1nm 이상 100nm 이하, 바람직하게는 10nm 이상 50nm 이하로 할 수 있다.

도전재료를 포함하는 층은 알루미늄이나 구리, 티탄, 탄탈, 텅스텐 등의 금속재료를 사용하여 형성할 수 있다. 또한, 다결정 실리콘 등의 반도체 재료를 사용하여, 도전재료를 포함하는 층을 형성하여도 좋다. 형성방법도 특별히 한정되지 않으며, 증착법, CVD법, 스퍼터링법, 스핀 코팅법 등의 각종 성막방법을 사용할 수 있다. 또한, 본 실시형태에서는 도전재료를 포함하는 층을 금속재료를 사용하여 형성하는 경우의 일 예에 대해 나타낸 것으로 한다.

그 후, 절연층 및 도전재료를 포함하는 층을 선택적으로 에칭하여 게이트 절연층(108), 게이트 전극(110)을 형성한다(도 2(C) 참조).

이어, 반도체영역(104)에 인(P)이나 비소(As) 등을 첨가하여 채널형성영역(116) 및 불순물영역(120)을 형성한다(도 2(D) 참조). 또한, 여기에서는 n형 트랜지스터를 형성하기 위해 인이나 비소를 첨가하고 있는데, p형 트랜지스터를 형성하는 경우에는 붕소(B)나 알루미늄(Al) 등의 불순물 원소를 첨가하면 된다. 여기서, 첨가하는 불순물의 농도는 적절히 설정할 수 있지만, 반도체 소자가 고도로 미세화되는 경우에는 그 농도를 높게 하는 것이 바람직하다.

또한, 게이트 전극(110)의 주위에 측벽 절연층을 형성하여, 불순물 원소가 다른 농도로 첨가된 불순물영역을 형성하여도 좋다.

이어, 게이트 전극(110), 불순물영역(120) 등을 덮도록 금속층(122)을 형성한다(도 3(A) 참조). 해당 금속층(122)은 진공증착법이나 스퍼터링법, 스핀 코팅법 등의 각종 성막방법으로 형성할 수 있다. 금속층(122)은 반도체영역(104)을 구성하는 반도체 재료와 반응함으로써 저저항의 금속 화합물이 되는 금속재료를 사용하여 형성하는 것이 바람직하다. 이와 같은 금속재료로서는 예를 들면, 티탄, 탄탈, 텅스텐, 니켈, 코발트, 백금 등이 있다.

그 후, 열처리를 실시하여 상기 금속층(122)과 반도체 재료를 반응시킨다. 이로써, 불순물영역(120)에 접하는 금속화합물영역(124)이 형성된다(도 3(A) 참조). 또한, 게이트 전극(110)으로서 다결정 실리콘 등을 사용할 경우에는 게이트 전극(110)의 금속층(122)과 접촉하는 부분에도 금속화합물영역이 형성되게 된다.

상기 열처리로서는 예를 들면 플래시 램프의 조사에 의한 열처리를 사용할 수 있다. 물론, 기타의 열처리방법을 사용하여도 좋지만, 금속 화합물의 형성과 관련된 화학반응의 제어성을 향상시키기 위해서는 극히 단시간의 열처리를 실현할 수 있는 방법을 사용하는 것이 바람직하다. 또한, 상기의 금속화합물 영역은 금속재료와 반도체 재료의 반응에 의해 형성되는 것이며, 충분히 도전성이 높아진 영역이다. 해당 금속화합물영역을 형성함으로써, 전기 저항을 충분히 저감하고 소자 특성을 향상시킬 수 있다. 또한, 금속화합물영역(124)을 형성한 후에는 금속층(122)은 제거한다.

이어, 상술한 공정에 의해 형성된 각 구성을 덮도록 절연층(128), 절연층(130)을 형성한다(도 3(B) 참조). 절연층(128)이나 절연층(130)은 산화실리콘, 산화질화실리콘, 산화알루미늄 등의 무기절연재료를 포함하는 재료를 사용하여 형성할 수 있다. 특히, 절연층(128)이나 절연층(130)에 유전율이 낮은(low-k) 재료를 사용함으로써, 각종 전극이나 배선의 오버랩에 기인하는 용량을 충분히 저감하는 것이 가능해지기 때문에 바람직하다. 또한, 절연층(128)이나 절연층(130)에는 이들 재료를 사용한 다공성 절연층을 적용하여도 좋다. 다공성 절연층에서는 밀도가 높은 절연층에 비해 유전율이 저하되기 때문에, 전극이나 배선에 기인하는 용량을 더욱 저감하는 것이 가능하다.

또한, 절연층(128)이나 절연층(130) 중에, 질화산화실리콘, 질화실리콘 등의 질소를 많이 포함하는 무기절연재료로 이루어진 층을 포함하여도 좋다. 이로써, 하부 트랜지스터(160)를 구성하는 재료가 포함하는 물이나 수소 등의 불순물이 이후에 형성하는 상부 트랜지스터(162)의 산화물 반도체층(144)에 침입하는 것을 방지할 수 있다. 단, 이 경우, 이후의 공정에서 수행하는 CMP처리만으로는 질소를 많이 포함하는 무기절연재료로 이루어진 층의 제거가 곤란하므로, 에칭 처리 등을 병용하는 것이 바람직하다.

예를 들면, 절연층(128)으로서 산화질화실리콘을 형성하고, 절연층(130)으로서 산화실리콘을 형성할 수 있다. 이와 같이, 절연층(128) 및 절연층(130)을 산화질화실리콘이나 산화실리콘과 같은 산소를 많이 포함하는 무기절연재료만을 사용하여 형성함으로써, 이후의 공정에서 절연층(128) 및 절연층(130)에 용이하게 CMP처리를 실시할 수 있다.

또한, 여기에서는 절연층(128)과 절연층(130)의 적층 구조로 하고 있지만, 개시하는 발명의 일 양태는 이에 한정되지 않는다. 1층으로 하여도 좋고, 3층 이상의 적층 구조로 하여도 좋다. 예를 들면, 상기 절연층(128)으로서 산화질화실리콘을 형성하고 절연층(130)으로서 산화실리콘을 형성하는 구성에 있어, 추가로 절연층(128)과 절연층(130) 사이에 질화산화실리콘막을 형성하는 구성으로 하여도 좋다.

또한, 본 명세서 중에 있어서, '산화질화실리콘'이란 그 조성으로서 질소보다도 산소의 함유량이 많은 것을 가리키며, '질화산화실리콘'이란 그 조성으로서 산소보다도 질소의 함유량이 많은 것을 가리킨다.

이상에 따라, 반도체 재료를 포함하는 기판(100)을 사용한 트랜지스터(160)가 형성된다(도 3(B) 참조). 이와 같은 트랜지스터(160)는 고속 동작이 가능하다는 특징을 갖는다.

그 후, 트랜지스터(162) 형성 전의 처리로서, 절연층(128)이나 절연층(130)에 화학적 기계적 연마(Chemical Mechanical Polishing : CMP) 처리를 실시하여 절연층(128) 및 절연층(130)의 표면을 평탄화한다(도 3(C) 참조). 여기에서, CMP처리란 피가공물의 표면을 기준으로 하며, 이에 따라 표면을 화학적/기계적인 복합작용에 의해 평탄화하는 수법이다. 일반적으로 연마 스테이지 위에 연마포를 부착하고, 피가공물과 연마포 사이에 슬러리(연마제)를 공급하면서 연마 스테이지와 피가공물을 각각 회전 또는 요동시켜 피가공물의 표면을, 슬러리와 피가공물 표면 사이에서의 화학반응 및 연마포와 피가공물의 기계적 연마 작용에 의해 피가공물의 표면을 연마하는 방법이다.

CMP처리는 1회 실시하여도 좋고, 복수회 실시하여도 좋다. 복수회로 나눠 CMP처리를 실시할 경우에는 높은 연마율의 1차 연마를 수행한 후, 낮은 연마율의 마무리 연마를 수행하는 것이 바람직하다. 이와 같이 연마율이 다른 연마를 조합함으로써, 절연층(128) 및 절연층(130) 표면의 평탄성을 더욱 향상시킬 수 있다.

절연층(128) 및 절연층(130)을 평탄화시키는 처리로서는 CMP처리 외에 에칭 처리 등을 적용하는 것도 가능하지만, 산화물 반도체층(144)의 평탄성 및 균일성을 향상시키고 트랜지스터(162)의 특성을 향상시키기 위해, 절연층(128)이나 절연층(130)의 표면은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하가 되도록 평탄화해 두는 것이 바람직하다.

또한, 절연층(128) 및 절연층(130)의 적층 구조에, 질화실리콘이나 질화산화실리콘과 같은 질소를 많이 포함하는 무기절연재료가 포함될 경우, CMP처리만으로는 질소를 많이 포함하는 무기절연재료의 제거가 곤란하므로, 에칭 처리 등을 병용하는 것이 바람직하다. 질소를 많이 포함하는 무기절연재료의 에칭 처리에는 건식 에칭, 습식 에칭 중 어느 것을 사용하여도 좋지만, 소자의 미세화라는 관점에서는 건식 에칭을 사용하는 것이 바람직하다. 또한, 각 절연층의 에칭률이 균일해지도록 에칭 조건(에칭가스나 에칭액, 에칭시간, 온도 등)을 적절히 설정하는 것이 바람직하다. 또한, 건식 에칭에 사용하는 에칭가스에는 예를 들면, 불소를 포함하는 가스(트리플루오로메탄(CHF3))나, 추가로 헬륨(He)이나 아르곤(Ar) 등의 희가스를 첨가한 가스 등을 사용할 수 있다.

또한, 상기의 각 공정의 전후에는 추가로 전극이나 배선, 반도체층, 절연층 등을 형성하는 공정을 포함하고 있어도 좋다. 예를 들면, 배선 구조로서, 절연층 및 도전층의 적층 구조로 이루어진 다층 배선구조를 채용하여, 고도로 집적화된 반도체 장치를 실현하는 것도 가능하다.

<상부 트랜지스터의 제작방법>

이어, 게이트 전극(110), 절연층(128), 절연층(130) 등의 위에 도전층을 형성하고, 이 도전층을 선택적으로 에칭하여 소스 전극 또는 드레인 전극(142a), 소스 전극 또는 드레인 전극(142b)을 형성한다(도 4(A) 참조).

도전층은 스퍼터링법을 비롯한 PVD법이나, 플라즈마 CVD법 등의 CVD법을 사용하여 형성할 수 있다. 또한, 도전층의 재료로서는 알루미늄, 크롬, 구리, 탄탈, 티탄, 몰리브덴, 텅스텐 중에서 선택된 원소나, 상술한 원소를 성분으로 하는 합금 등을 사용할 수 있다. 망간, 마그네슘, 지르코늄, 베릴륨, 네오디뮴, 스칸듐 중 어느 하나 또는 이들을 복수 조합한 재료를 사용하여도 좋다.

도전층은 단층 구조이어도 좋고, 2층 이상의 적층 구조로 하여도 좋다. 예를 들면, 티탄막이나 질화티탄막의 단층 구조, 실리콘을 포함하는 알루미늄막의 단층 구조, 알루미늄막 위에 티탄막이 적층된 2층 구조, 질화티탄막 위에 티탄막이 적층된 2층 구조, 티탄막과 알루미늄막과 티탄막이 적층된 3층 구조 등을 들 수 있다. 또한, 도전층을 티탄막이나 질화티탄막의 단층 구조로 하는 경우에는 테이퍼 형상을 갖는 소스 전극 또는 드레인 전극(142a), 및 소스 전극 또는 드레인 전극(142b)으로의 가공이 용이하다는 이점이 있다.

또한, 도전층은 도전성 금속 산화물을 사용하여 형성하여도 좋다. 도전성 금속산화물로서는 산화인듐(In2O3), 산화주석(SnO2), 산화아연(ZnO), 산화인듐 산화주석 합금(In2O3-SnO2, ITO라 약칭하는 경우가 있다), 산화인듐 산화아연 합금(In2O3-ZnO), 또는 이들 금속 산화물 재료에 실리콘 또는 산화실리콘을 함유시킨 것을 사용할 수 있다.

도전층의 에칭은 형성되는 소스 전극 또는 드레인 전극(142a), 및 소스 전극 또는 드레인 전극(142b)의 단부가 테이퍼 형상이 되도록 수행하는 것이 바람직하다. 여기서, 테이퍼 각도은 예를 들면 30°이상 60°이하인 것이 바람직하다. 소스 전극 또는 드레인 전극(142a), 소스 전극 또는 드레인 전극(142b)의 단부를 테이퍼 형상이 되도록 에칭함으로써, 나중에 형성되는 게이트 절연층(146)의 피복성을 향상시키고 단 끊어짐을 방지할 수 있다.

상부 트랜지스터의 채널 길이(L)는 소스 전극 또는 드레인 전극(142a), 및 소스 전극 또는 드레인 전극(142b)의 하단부의 간격에 의해 결정된다. 또한, 채널 길이(L)가 25nm 미만인 트랜지스터를 형성하는 경우에 사용하는 마스크 형성의 노광을 수행할 때에는 수 nm~수 10nm과 파장이 짧은 초자외선(Extreme Ultraviolet)을 사용하는 것이 바람직하다. 초자외선에 의한 노광은 해상도가 높고 초점심도도 크다. 따라서, 나중에 형성되는 트랜지스터의 채널길이(L)를 10nm 이상 1000nm(1μm) 이하로 하는 것도 가능하며, 회로의 동작속도를 높이는 것이 가능하다. 또한, 미세화에 의해 반도체 장치의 소비 전력을 저감하는 것도 가능하다.

또한, 절연층(128)이나 절연층(130) 위에는 베이스로서 기능하는 절연층을 형성하여도 좋다. 해당 절연층은 PVD법이나 CVD법 등을 사용하여 형성할 수 있다. 이 경우, 형성한 절연층도 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하인 표면을 갖는 것이 바람직하다.

이어, 소스 전극 또는 드레인 전극(142a) 위에 절연층(143a)을, 소스 전극 또는 드레인 전극(142b) 위에 절연층(143b)을 각각 형성한다(도 4(B) 참조). 절연층(143a) 및 절연층(143b)은 소스 전극 또는 드레인 전극(142a)이나, 소스 전극 또는 드레인 전극(142b)을 덮는 절연층을 형성한 후, 해당 절연층을 선택적으로 에칭함으로써 형성할 수 있다. 또한, 절연층(143a) 및 절연층(143b)은 나중에 형성되는 게이트 전극의 일부와 중첩하도록 형성한다. 이와 같은 절연층을 형성함으로써, 게이트 전극과 소스 전극 또는 드레인 전극과의 사이의 용량을 저감하는 것이 가능하다.

절연층(143a)이나 절연층(143b)은 산화실리콘, 산화질화실리콘, 질화산화실리콘, 질화실리콘, 산화알루미늄 등의 무기절연재료를 포함하는 재료를 사용하여 형성할 수 있다. 특히, 절연층(143a)이나 절연층(143b)에 유전율이 낮은(low-k) 재료를 사용함으로써, 게이트 전극과 소스 전극 또는 드레인 전극과의 사이의 용량을 충분히 저감하는 것이 가능하게 되기 때문에 바람직하다. 또한, 절연층(143a)이나 절연층(143b)에는 이들 재료를 사용한 다공성 절연층을 적용하여도 좋다. 다공성 절연층에서는 밀도가 높은 절연층에 비해 유전율이 저하되기 때문에, 게이트 전극과 소스 전극 또는 드레인 전극과의 사이의 용량을 더욱 저감하는 것이 가능하다.

또한, 게이트 전극과 소스 전극 또는 드레인 전극과의 사이의 용량을 저감시킨다는 점에서는 절연층(143a) 및 절연층(143b)을 형성하는 것이 바람직하지만, 해당 절연층을 형성하지 않는 구성으로 하는 것도 가능하다.

이어, 소스 전극 또는 드레인 전극(142a), 및 소스 전극 또는 드레인 전극(142b)을 덮도록 산화물 반도체층을 형성한 후, 해당 산화물 반도체층을 선택적으로 에칭하여 산화물 반도체층(144)을 형성한다(도 4(C) 참조).

산화물 반도체층은 4원계 금속 산화물인 In-Sn-Ga-Zn-O계나, 3원계 금속 산화물인 In-Ga-Zn-O계, In-Sn-Zn-O계, In-Al-Zn-O계, Sn-Ga-Zn-O계, Al-Ga-Zn-O계, Sn-Al-Zn-O계나, 2원계 금속 산화물인 In-Zn-O계, Sn-Zn-O계, Al-Zn-O계, Zn-Mg-O계, Sn-Mg-O계, In-Mg-O계나, In-O계, Sn-O계, Zn-O계 등을 사용하여 형성할 수 있다.

그 중에서도, In-Ga-Zn-O계의 산화물 반도체 재료는 무전계시의 저항이 충분히 높아 오프 전류를 충분히 작게 하는 것이 가능하며, 또한, 전계효과이동도도 높기 때문에, 반도체 장치에 사용하는 반도체 재료로서는 바람직하다.

In-Ga-Zn-O계 산화물 반도체 재료의 대표예로서는 InGaO3(ZnO)m(m>0)으로 표기되는 것이 있다. 또한, Ga 대신에 M을 사용하고, InMO3(ZnO)m(m>0)과 같이 표기되는 산화물 반도체 재료가 있다. 여기서, M은 갈륨(Ga), 알루미늄(Al), 철(Fe), 니켈(Ni), 망간(Mn), 코발트(Co) 등에서 선택된 하나의 금속원소 또는 복수의 금속원소를 나타낸다. 예를 들면, M으로서는 Ga, Ga 및 Al, Ga 및 Fe, Ga 및 Ni, Ga 및 Mn, Ga 및 Co 등을 적용할 수 있다. 또한, 상술한 조성은 결정구조로부터 도출되는 것으로, 어디까지나 일 예에 지나지 않음을 밝힌다.

산화물 반도체층을 스퍼터링법으로 제작하기 위한 타겟으로서는 In:Ga:Zn=1:x:y(x는 0이상, y는 0.5이상 5이하)의 조성식으로 표시되는 것을 사용하는 것이 바람직하다. 예를 들면, In2O3:Ga2O3:ZnO=1:1:2[mol수 비]의 조성비를 갖는 타겟 등을 사용할 수 있다. 또한, In2O3:Ga2O3:ZnO=1:1:1[mol수 비]의 조성비를 갖는 타겟이나, In2O3:Ga2O3:ZnO=1:1:4[mol수 비]의 조성비를 갖는 타겟이나, In2O3:Ga2O3:ZnO=1:0:2[mol수 비]의 조성비를 갖는 타겟을 사용할 수도 있다.

본 실시형태에서는 산화물 반도체층을 In-Ga-Zn-O계 금속 산화물 타겟을 사용하는 스퍼터링법에 의해 형성하는 것으로 한다.

금속 산화물 타겟 중의 금속 산화물의 상대밀도는 80% 이상, 바람직하게는 95% 이상, 더욱 바람직하게는 99.9% 이상이다. 상대밀도가 높은 금속 산화물 타겟을 사용함으로써, 치밀한 구조의 산화물 반도체층을 형성하는 것이 가능하다.

산화물 반도체층의 형성 분위기는 희가스(대표적으로는 아르곤) 분위기, 산소 분위기, 또는 희가스(대표적으로는 아르곤)와 산소의 혼합 분위기로 하는 것이 바람직하다. 구체적으로는 예를 들면 수소, 물, 수산기, 수소화물 등의 불순물이 농도 1ppm 이하(바람직하게는 농도 10ppb 이하)로까지 제거된 고순도 가스 분위기를 사용하는 것이 바람직하다.

산화물 반도체층의 형성시에는 예를 들면, 감압 상태로 유지된 처리실 내에 피처리물을 홀딩하고, 피처리물의 온도가 100℃ 이상 550℃ 미만, 바람직하게는 200℃ 이상 400℃ 이하가 되도록 피처리물을 가열한다. 혹은, 산화물 반도체층의 형성시 피처리물의 온도는 실온(25℃±10℃)으로 하여도 좋다. 그리고, 처리실 내의 수분을 제거하면서, 수소나 물 등이 제거된 스퍼터링 가스를 도입하고, 상기 타겟을 사용하여 산화물 반도체층을 형성한다. 피처리물을 가열하면서 산화물 반도체층을 형성함으로써, 산화물 반도체층에 포함되는 불순물을 저감할 수 있다. 또한, 스퍼터링에 의한 손상을 경감할 수 있다. 처리실 내의 수분을 제거하기 위해서는 흡착형 진공 펌프를 사용하는 것이 바람직하다. 예를 들면, 크라이오펌프, 이온펌프, 티타늄 서블리메이션 펌프(titanium sublimation pump) 등을 사용할 수 있다. 또한, 터보 펌프에 콜드 트랩을 조합한 것을 사용하여도 좋다. 크라이오 펌프를 사용하여 배기함으로써, 처리실로부터 수소나 물 등을 제거할 수 있기 때문에, 산화물 반도체층 중의 불순물 농도를 저감할 수 있다.

산화물 반도체층의 형성조건으로서는 예를 들면, 피처리물과 타겟간의 거리가 170mm, 압력이 0.4Pa, 직류(DC) 전력이 0.5kW, 분위기가 산소(산소 100%) 분위기, 또는 아르곤(아르곤 100%) 분위기, 또는 산소와 아르곤의 혼합 분위기라는 조건을 적용할 수 있다. 또한, 펄스 직류(DC) 전원을 사용하면, 먼지(성막시에 형성되는 가루형태의 물질 등)를 저감할 수 있으며, 막두께 분포도 균일해지기 때문에 바람직하다. 산화물 반도체층의 두께는 1nm 이상 50nm 이하, 바람직하게는 1nm 이상 30nm 이하, 보다 바람직하게는 1nm 이상 10nm 이하로 한다. 이와 같은 두께의 산화물 반도체층을 사용함으로써, 미세화에 수반되는 쇼트채널효과를 억제하는 것이 가능하다. 단, 적용하는 산화물 반도체 재료나 반도체 장치의 용도 등에 따라 적절한 두께는 다르기 때문에, 그 두께는 사용하는 재료나 용도 등에 따라 선택할 수도 있다.

여기서, 산화물 반도체층(144)은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하인 표면을 갖는 절연층(130) 위에 형성된다. 이와 같이, 평탄성이 양호한 표면 위에 산화물 반도체층(144)을 형성함으로써, 산화물 반도체층(144)의 평탄성 및 균일성을 양호한 것으로 할 수 있다. 추가로, 평탄성 및 균일성이 양호한 산화물 반도체층(144)을 사용함으로써, 트랜지스터(162)의 트랜지스터 특성을 향상시킬 수 있다.

또한, 산화물 반도체층을 스퍼터링법에 의해 형성하기 전에는 아르곤 가스를 도입하여 플라즈마를 발생시키는 역스퍼터링을 수행하여, 형성 표면(예를 들면 절연층(130)의 표면)의 부착물을 제거하는 것이 바람직하다. 여기서, 역스퍼터링이란 통상의 스퍼터링에서는 스퍼터링 타겟에 이온을 충돌시키는 바를, 역으로 기판의 처리 표면에 이온을 충돌시킴으로써 그 표면을 개질하는 방법을 말한다. 처리 표면에 이온을 충돌시키는 방법으로서는 아르곤 분위기하에서 처리 표면측에 고주파 전압을 인가하여 피처리물 부근에 플라즈마를 생성하는 방법 등이 있다. 또한, 아르곤 분위기를 대신하여 질소, 헬륨, 산소 등의 분위기를 적용하여도 좋다.

그 후, 산화물 반도체층에 대해, 열처리(제 1 열처리)를 실시하는 것이 바람직하다. 이 제 1 열처리에 의해 산화물 반도체층 중의 과잉 수소(물이나 수산기를 포함함)를 제거하고 산화물 반도체층의 구조를 조정하여, 에너지 갭 중의 결함 준위를 저감할 수 있다. 제 1 열처리의 온도는 예를 들면 300℃ 이상 550℃ 미만, 또는 400℃ 이상 500℃ 이하로 한다.

열처리는 예를 들면 저항 발열체 등을 사용한 전기로에 피처리물을 도입하고, 질소 분위기 하, 450℃, 1시간의 조건에서 수행할 수 있다. 그동안, 산화물 반도체층은 물이나 수소의 혼입이 발생하지 않도록 대기에 노출시키지 않는다.

열처리장치는 전기로에 한정되지 않고, 가열된 가스 등의 매체로부터의 열전도 또는 열복사에 의해 피처리물을 가열하는 장치를 사용하여도 좋다. 예를 들면, GRTA(Gas Rapid Thermal Anneal) 장치, LRTA(Lamp Rapid Thermal Anneal) 장치 등의 RTA(Rapid Thermal Anneal) 장치를 사용할 수 있다. LRTA 장치는 할로겐 램프, 메탈 할라이드 램프, 크세논 아크 램프, 카본 아크 램프, 고압 나트륨 램프, 고압 수은 램프 등의 램프에서 발하는 광(전자파)의 복사에 의해 피처리물을 가열하는 장치이다. GRTA 장치는 고온의 가스를 사용하여 열처리를 수행하는 장치이다. 가스로서는 아르곤 등의 희가스, 또는 질소와 같은 열처리에 의해 피처리물과 반응하지 않는 비활성 기체가 사용된다.

예를 들면, 제 1 열처리로서, 가열된 비활성 가스 분위기 중에 피처리물을 투입하고, 수분 동안 가열한 후, 해당 비활성 가스 분위기로부터 피처리물을 꺼내는 GRTA 처리를 실시하여도 좋다. GRTA 처리를 사용하면 단시간으로 고온 열처리가 가능하게 된다. 또한, 피처리물의 내열 온도를 초과하는 온도 조건이더라도 적용이 가능하게 된다. 또한, 처리 중에, 비활성 가스를, 산소를 포함하는 가스로 전환하여도 좋다. 산소를 포함하는 분위기에서 제 1 열처리를 실시함으로써, 산소 결손에 기인하는 에너지 갭 중의 결함 준위를 저감할 수 있기 때문이다.

또한, 비활성 가스 분위기로서는 질소, 또는 희가스(헬륨, 네온, 아르곤 등)를 주성분으로 하는 분위기이면서 물, 수소 등이 포함되지 않는 분위기를 적용하는 것이 바람직하다. 예를 들면, 열처리 장치에 도입하는 질소나 헬륨, 네온, 아르곤 등의 희가스의 순도를 6N(99.9999%) 이상, 바람직하게는 7N(99.99999%) 이상(즉, 불순물 농도가 1ppm 이하, 바람직하게는 0.1ppm 이하)으로 한다.

어느 것으로 하든, 제 1 열처리에 의해 불순물을 저감하고 i형(진성 반도체) 또는 i형에 매우 가까운 산화물 반도체층을 형성함으로써, 매우 우수한 특성의 트랜지스터를 실현할 수 있다.

그런데, 상술한 열처리(제 1 열처리)에는 수소나 물 등을 제거하는 효과가 있으므로, 해당 열처리를 탈수화처리나 탈수소화처리 등으로 부를 수도 있다. 해당 탈수화처리나 탈수소화처리는 산화물 반도체층의 형성 후나 게이트 절연층의 형성 후, 게이트 전극의 형성 후 등의 타이밍에서 수행하는 것도 가능하다. 또한, 이와 같은 탈수화처리, 탈수소화처리는 1회에 국한되지 않고 복수회 실시하여도 좋다.

산화물 반도체층의 에칭은 상기 열처리 전, 또는 상기 열처리 후 중 어느 쪽에서든 실시하여도 좋다. 또한, 소자의 미세화라는 관점에서는 건식 에칭을 사용하는 것이 바람직하지만, 습식 에칭을 사용하여도 좋다. 에칭가스나 에칭액에 대해서는 피에칭재료에 따라 적절히 선택할 수 있다. 또한, 소자에서의 누설 등이 문제가 되지 않을 경우에는 산화물 반도체층을 섬형상으로 가공하지 않고 사용하여도 좋다.

이어, 산화물 반도체층(144)에 접하는 게이트 절연층(146)을 형성하고, 그 후, 게이트 절연층(146) 위에서 산화물 반도체층(144)과 중첩하는 영역에 게이트 전극(148a)을 형성한다(도 5(A) 참조).

게이트 절연층(146)은 CVD법이나 스퍼터링법 등을 사용하여 형성할 수 있다. 또한, 게이트 절연층(146)은 산화실리콘, 질화실리콘, 산화질화실리콘, 질화산화실리콘, 산화알루미늄, 산화탄탈, 산화하프늄, 산화이트륨, 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 실리게이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 알루미네이트(HfAlxOy(x>0, y>0)) 등을 포함하도록 형성하는 것이 바람직하다. 게이트 절연층(146)은 단층 구조로 하여도 좋고 적층 구조로 하여도 좋다. 또한, 그 두께는 특별히 한정되지 않지만, 반도체 장치를 미세화할 경우에는 트랜지스터의 동작을 확보하기 위해 얇게 하는 것이 바람직하다. 예를 들면, 산화실리콘을 사용하는 경우에는 1nm 이상 100nm 이하, 바람직하게는 10nm 이상 50nm 이하로 할 수 있다.

상술한 바와 같이, 게이트 절연층을 얇게 하면, 터널효과 등에 기인하는 게이트 누설이 문제가 된다. 게이트 누설의 문제를 해소하기 위해서는 게이트 절연층(146)에 산화하프늄, 산화탄탈, 산화이트륨, 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 실리게이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 알루미네이트(HfAlxOy(x>0, y>0)) 등의 고유전율(high-k) 재료를 사용하면 된다. high-k 재료를 게이트 절연층(146)에 사용함으로써, 전기적 특성을 확보하면서 게이트 누설을 억제하기 위해 막두께를 크게 하는 것이 가능하게 된다. 또한, high-k 재료를 포함하는 막과, 산화실리콘, 질화실리콘, 산화질화실리콘, 질화산화실리콘, 산화알루미늄 등 중 어느 하나를 포함하는 막과의 적층구조로 하여도 좋다.

게이트 절연층(146)의 형성 후에는 비활성 가스 분위기, 또는 산소 분위기 하에서 제 2 열처리를 실시하는 것이 바람직하다. 열처리의 온도는 200℃ 이상 450℃ 이하, 바람직하게는 250℃ 이상 350℃ 이하이다. 예를 들면, 질소 분위기하에 250℃에서 1시간 동안 열처리를 실시하면 된다. 제 2 열처리를 실시함으로써, 트랜지스터의 전기적 특성의 편차를 경감할 수 있다. 또한, 게이트 절연층(146)이 산소를 포함하는 경우, 산화물 반도체층(144)에 산소를 공급하고 이 산화물 반도체층(144)의 산소 결손을 보충하여, i형(진성 반도체) 또는 i형에 매우 가까운 산화물 반도체층을 형성할 수도 있다.

또한, 본 실시형태에서는 게이트 절연층(146)의 형성 후에 제 2 열처리를 실시하고 있는데, 제 2 열처리의 타이밍은 이에 한정되지 않는다. 예를 들면, 게이트 전극의 형성 후에 제 2 열처리를 실시하여도 좋다. 또한, 제 1 열처리에 이어 제 2 열처리를 실시하여도 좋고, 제 1 열처리에 제 2 열처리를 겸하게 하여도 좋으며, 제 2 열처리에 제 1 열처리를 겸하게 하여도 좋다.

상술한 바와 같이, 제 1 열처리와 제 2 열처리 중 적어도 한쪽을 적용함으로써, 산화물 반도체층(144)을 그 주성분 이외의 불순물이 가능한 포함되지 않도록 고순도화할 수 있다.

게이트 전극(148a)은 게이트 절연층(146) 위에 도전층을 형성한 후에, 해당 도전층을 선택적으로 에칭함으로써 형성할 수 있다. 게이트 전극(148a)이 되는 도전층은 스퍼터링법을 비롯한 PVD법이나, 플라즈마 CVD법 등의 CVD법을 사용하여 형성할 수 있다. 상세 사항은 소스 전극 또는 드레인 전극(142a) 등인 경우와 마찬가지이며, 이들 기재를 참작할 수 있다.

이어, 게이트 절연층(146), 게이트 전극(148a) 위에 절연층(150) 및 절연층(152)을 형성한다(도 5(B) 참조). 절연층(150) 및 절연층(152)은 PVD법이나 CVD법 등을 사용하여 형성할 수 있다. 또한, 산화실리콘, 산화질화실리콘, 질화산화실리콘, 질화실리콘, 산화하프늄, 산화알루미늄 등의 무기절연재료를 포함하는 재료를 사용하여 형성할 수 있다.

또한, 절연층(150)이나 절연층(152)에는 유전율이 낮은 재료나, 유전율이 낮은 구조(다공성 구조 등)를 사용하는 것이 바람직하다. 절연층(150)이나 절연층(152)의 유전율을 낮게 함으로써, 배선이나 전극 등의 사이에 발생하는 용량을 저감하여 동작의 고속화를 도모할 수 있기 때문이다.

또한, 본 실시형태에서는 절연층(150)과 절연층(152)의 적층 구조로 하고 있는데, 개시하는 발명의 일 양태는 이에 한정되지 않는다. 1층으로 하여도 좋으며, 3층 이상의 적층 구조로 하여도 좋다. 또한, 절연층을 형성하지 않는 구성으로 하는 것도 가능하다.

또한, 상기 절연층(152)은 그 표면이 평탄하게 되도록 형성하는 것이 바람직하다. 표면이 평탄해지도록 절연층(152)을 형성함으로써, 반도체 장치를 미세화한 경우 등에서도, 절연층(152) 위에 전극이나 배선 등을 적절하게 형성할 수 있기 때문이다. 또한, 절연층(152)의 평탄화는 CMP 등의 방법을 사용하여 수행할 수 있다.

그리고, 트랜지스터(160) 또는 트랜지스터(162)와 배선(156)을 전기적으로 접속하기 위한 전극(미도시)을 형성한 후, 절연층(152) 위에 배선(156)을 형성한다(도 5(C) 참조). 물론, 이들 요소가 모두 전기적으로 접속될 필요는 없다. 다른 요소로부터 독립된 요소를 갖고 있어도 좋다.

배선(156)은 스퍼터링을 비롯한 PVD법이나, 플라즈마 CVD법 등의 CVD법을 사용하여 도전층을 형성한 후, 해당 도전층을 패터닝함으로써 형성된다. 또한, 도전층 재료로서는 알루미늄, 크롬, 구리, 탄탈, 티탄, 몰리브덴, 텅스텐 중에서 선택된 원소나, 상술한 원소를 성분으로 하는 합금 등을 사용할 수 있다. 망간, 마그네슘, 지르코늄, 베릴륨, 네오디뮴, 스칸듐 중 어느 하나, 또는 이들을 복수 조합한 재료를 사용하여도 좋다. 상세 사항은 소스 전극 또는 드레인 전극(142a) 등과 마찬가지이다.

이상에 따라, 고순도화된 산화물 반도체층(144)을 사용한 트랜지스터(162)가 완성된다(도 5(C) 참조).

이와 같이 고순도화되며 진성화된 산화물 반도체층(144)을 사용함으로써, 트랜지스터(162)의 오프 전류를 충분히 저감할 수 있다.

이상에 따라, 하부에 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 가지며, 상부에 산화물 반도체를 사용한 트랜지스터를 갖는 반도체 장치를 제공할 수 있다.

이와 같이, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터와, 산화물 반도체를 사용한 트랜지스터를 일체로 구비하는 구성으로 함으로써, 각각의 특성의 이점을 살린 새로운 반도체 장치를 실현할 수 있다.

또한, 평탄성이 양호한 표면 위에 산화물 반도체층을 형성함으로써 트랜지스터 특성을 향상시킨 트랜지스터를, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터에 적층한 반도체 장치를 제공할 수 있다.

이상, 본 실시형태에 나타낸 구성, 방법 등은 다른 실시형태에 나타낸 구성, 방법 등과 적절히 조합하여 사용할 수 있다.

(실시형태 2)

본 실시형태에서는 개시하는 발명의 다른 일 양태에 따른 반도체 장치의 구성 및 그 제작방법에 대해, 도 6~도 13을 참조하여 설명한다. 또한, 본 실시형태에서는 특별히 기억장치로서 사용할 수 있는 반도체 장치의 구성예에 대해 설명한다.

<반도체 장치의 단면 구성 및 평면 구성>

도 6은 반도체 장치의 구성의 일 예이다. 도 6(A)에서는 반도체 장치의 단면을, 도 6(B)에는 반도체 장치의 평면을 각각 나타낸다. 여기서, 도 6(A)는 도 6(B)의 A1-A2 및 B1-B2에 따른 단면에 상당한다. 도 6(A) 및 도 6(B)에 나타나는 반도체 장치는 하부에 제 1 반도체 재료를 사용한 트랜지스터(260)를 가지며, 상부에 제 2 반도체 재료를 사용한 트랜지스터(262)를 갖는 것으로, 트랜지스터(260)의 게이트 전극(210)과, 트랜지스터(262)의 소스 전극 또는 드레인 전극(242a)은 서로 직접 접속되어 있다. 여기서, 제 1 반도체 재료와 제 2 반도체 재료는 서로 다른 재료로 하는 것이 바람직하다. 예를 들면, 제 1 반도체 재료를 산화물 반도체 이외의 반도체 재료로 하고, 제 2 반도체 재료를 산화물 반도체로 할 수 있다. 산화물 반도체 이외의 반도체 재료로서는 예를 들면 실리콘, 게르마늄, 실리콘 게르마늄, 탄화실리콘, 또는 갈륨 비소 등을 사용할 수 있으며, 단결정 반도체를 사용하는 것이 바람직하다. 그 외에, 유기 반도체 재료 등을 사용하여도 좋다. 이와 같은 반도체 재료를 사용한 트랜지스터(260)는 고속 동작이 용이하다. 한편, 산화물 반도체를 사용한 트랜지스터(262)는 오프 전류를 충분히 저감함으로써 장시간의 전하 홀딩을 가능하게 한다.

이 때문에, 트랜지스터(262)를 오프 상태로 함으로써, 트랜지스터(260)의 게이트 전극(210)의 전위를 매우 장시간에 걸쳐 홀딩하는 것이 가능하다. 그리고, 용량소자(264)를 가짐으로써, 트랜지스터(260)의 게이트 전극(210)에 주어진 전하의 홀딩이 용이하게 되며, 또한 홀딩된 정보의 읽기가 용이하게 된다. 또한, 상술한 바와 같은 반도체 재료를 사용한 트랜지스터(260)는 충분한 고속 동작이 가능하므로, 정보의 읽기 속도를 향상시킬 수 있다.

또한, 상기 트랜지스터는 모두 n채널형 트랜지스터인 것으로 설명하지만, p채널형 트랜지스터를 사용할 수 있음은 말할 것까지도 없다. 또한, 개시하는 발명의 기술적인 본질은 오프 전류가 충분히 저감된, 산화물 반도체를 사용한 트랜지스터와, 충분한 고속동작이 가능한, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 일체로 구비하는 점이기 때문에, 반도체 장치에 사용되는 재료나 반도체 장치의 구조 등, 반도체 장치의 구체적인 구성을 여기에서 나타내는 것으로 한정할 필요는 없다.

도 6의 트랜지스터(260)는 반도체 재료(예를 들면, 실리콘 등)를 포함하는 기판(200)에 형성된 채널형성영역(216)과, 채널형성영역(216)을 사이에 끼우도록 형성된 불순물영역(220)과, 불순물영역(220)에 접하는 금속화합물영역(224)과, 채널형성영역(216) 위에 형성된 게이트 절연층(208)과, 게이트 절연층(208) 위에 형성된 게이트 전극(210)을 갖는다. 즉, 트랜지스터(260)는 실시형태 1에서 나타낸 트랜지스터(160)와 마찬가지 구성이다. 또한, 도면에 있어서, 명시적으로는 소스 전극이나 드레인 전극을 갖지 않는 경우가 있지만, 편의상, 이와 같은 상태를 포함하여 트랜지스터라 부르는 경우가 있다.

또한, 기판(200) 위에는 트랜지스터(260)를 둘러싸도록 소자분리절연층(206)이 형성되어 있으며, 트랜지스터(260) 위에 절연층(228) 및 절연층(230)이 형성되어 있다. 또한, 도시하지는 않았지만, 트랜지스터(260)의 금속화합물영역(224)의 일부는 소스 전극이나 드레인 전극으로서 기능하는 전극을 통해 배선(256) 또는 다른 배선에 접속되어 있다. 또한, 고집적화를 실현하기 위해서는 도 6에 나타낸 바와 같이 트랜지스터(260)가 측벽 절연층을 갖지 않는 구성으로 하는 것이 바람직하다. 한편, 트랜지스터(260)의 특성을 중시하는 경우에는 게이트 전극(210)의 측면에 측벽 절연층을 형성하고, 그 측벽 절연층과 중첩하는 영역에 형성된 불순물 농도가 다른 영역을 포함하여 불순물영역(220)을 형성하여도 좋다.

도 6의 트랜지스터(262)는 절연층(230) 위에 형성된 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)과, 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)과 전기적으로 접속되어 있는 산화물 반도체층(244)과, 소스 전극 또는 드레인 전극(242a), 소스 전극 또는 드레인 전극(242b), 산화물 반도체층(244)을 덮는 게이트 절연층(246)과, 게이트 절연층(246) 위에 산화물 반도체층(244)과 중첩하도록 형성된 게이트 전극(248a)과, 소스 전극 또는 드레인 전극(242a)과 산화물 반도체층(244) 사이의, 게이트 전극(248a)과 중첩하는 영역에 형성된 절연층(243a)과, 소스 전극 또는 드레인 전극(242b)과 산화물 반도체층(244) 사이의, 게이트 전극(248a)과 중첩하는 영역에 형성된 절연층(243b)을 갖는다. 또한, 소스 전극 또는 드레인 전극과 게이트 전극과의 사이의 용량을 저감하기 위해서는 절연층(243a) 및 절연층(243b)을 형성하는 것이 바람직하지만, 절연층(243a) 및 절연층(243b)을 형성하지 않는 구성으로 하는 것도 가능하다. 즉, 트랜지스터(262)는 실시형태 1에서 나타낸 트랜지스터(162)와 마찬가지 구성이다.

여기서, 실시형태 1에서 나타낸 산화물 반도체층(144)과 마찬가지로, 산화물 반도체층(244)은 수소 등의 불순물이 충분히 제거됨으로써 또는 충분한 산소가 공급됨으로써 고순도화된 것인 것이 바람직하다. 이와 같이, 고순도화된 산화물 반도체를 사용함으로써, 매우 우수한 오프 전류 특성의 트랜지스터(262)를 얻을 수 있다. 산화물 반도체층(244)의 상세 사항에 대해서는 실시형태 1을 참작할수 있다.

여기서, 산화물 반도체층(244)은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하인 표면을 갖는 절연층(230) 위에 형성된다. 이와 같이, 평탄성이 양호한 표면 위에 산화물 반도체층(244)을 형성함으로써, 산화물 반도체층(244)의 평탄성 및 균일성을 양호한 것으로 할 수 있다.

평탄성 및 균일성이 양호한 산화물 반도체층(244)을 사용함으로써, 산화물 반도체층의 계면에서의 캐리어 산란방지, 계면 준위 저감을 도모할 수 있다. 이로써, 트랜지스터(262)의 이동도 향상, S값 및 오프 전류의 저감을 도모하고, 트랜지스터 특성을 향상시킬 수 있다. 또한, 산화물 반도체층(244)의 평탄성을 향상시킴으로써, 트랜지스터(262)의 게이트 누설 전류를 저감할 수 있다.

또한, 도 6의 트랜지스터(262)에서는 미세화에 기인하여 소자 사이에 발생하는 누설을 억제하기 위해, 섬형상으로 가공된 산화물 반도체층(244)을 사용하고 있는데, 섬형상으로 가공되지 않은 구성을 채용하여도 좋다. 산화물 반도체층을 섬형상으로 가공하지 않는 경우에는 가공시의 에칭으로 인한 산화물 반도체층(244)의 오염을 방지할 수 있다.

또한, 도 1에서 나타낸 반도체 장치와 도 6에 나타낸 반도체 장치의 차이점 중 하나는 하부 트랜지스터의 게이트 전극과, 상부 트랜지스터의 소스 전극 또는 드레인 전극이 서로 직접 접속되어 있는지 아닌 지에 있다. 도 6에 나타낸 반도체 장치와 같이, 절연층(230)으로부터 상면이 노출된 게이트 전극(210)과, 소스 전극 또는 드레인 전극(242a)을 서로 직접 접속함으로써, 게이트 전극(210)과 소스 전극 또는 드레인 전극(242a)을 콘택을 위한 개구 및 전극을 별도로 형성하여 서로 접속하는 경우보다, 콘택 면적을 축소할 수 있으므로, 반도체 장치의 고집적화를 도모할 수 있다. 또한, 콘택을 위해 별도로 형성하는 개구 및 전극에 필요한 공정을 생략할 수 있으므로, 반도체 장치 제작의 공정을 간략화할 수 있다.

또한, 도 1에서 나타낸 반도체 장치와 도 6에 나타낸 반도체 장치의 차이점 중 하나는 용량소자(264)의 유무이다. 도 6의 용량소자(264)는 소스 전극 또는 드레인 전극(242a), 산화물 반도체층(244), 게이트 절연층(246), 및 전극(248b)으로 구성된다. 즉, 소스 전극 또는 드레인 전극(242a)은 용량소자(264)의 일측 전극으로서 기능하며, 전극(248b)의 타측 전극으로서 기능하게 된다.

또한, 도 6의 용량소자(264)에서는 산화물 반도체층(244)과 게이트 절연층(246)을 적층시킴으로써, 소스 전극 또는 드레인 전극(242a)과 전극(248b) 사이의 절연성을 충분히 확보할 수 있다. 물론, 충분한 용량을 확보하기 위해, 산화물 반도체층(244)을 갖지 않는 구성의 용량소자(264)를 채용하여도 좋다. 또한, 절연층(243a)과 마찬가지로 형성되는 절연층을 갖는 구성의 용량소자(264)를 채용하여도 좋다. 그리고, 용량이 불필요한 경우에는 용량소자(264)를 마련하지 않는 구성으로 하는 것도 가능하다.

또한, 트랜지스터(262) 및 용량소자(264)에 있어서, 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)의 단부는 테이퍼 형상인 것이 바람직하다. 소스 전극 또는 드레인 전극(242a), 소스 전극 또는 드레인 전극(242b)의 단부를 테이퍼 형상으로 함으로써, 산화물 반도체층(244)의 피복성이 향상되며 단 끊어짐을 방지할 수 있기 때문이다. 여기서, 테이퍼 각도는 예를 들면 30°이상 60°이하로 한다. 또한, 테이퍼 각도란, 테이퍼 형상을 갖는 층(예를 들면, 소스 전극 또는 드레인 전극(242a))을 그 단면(기판의 표면과 직교하는 면)에 수직인 방향에서 관찰했을 때, 해당층의 측면과 저면이 이루는 경사각을 나타낸다.

본 실시형태에서는 트랜지스터(262) 및 용량소자(264)가 트랜지스터(260)와 중첩하도록 형성되어 있다. 이와 같은 평면 레이아웃을 채용함으로써, 고집적화가 가능하다. 예를 들면, 배선이나 전극과의 접속관계를 고안함으로써, 최소 가공 치수를 F로 하여, 메모리 셀이 차지하는 면적을 15F2~25F2로 하는 것도 가능하다.

트랜지스터(262) 및 용량소자(264) 위에는 절연층(250)이 형성되어 있으며, 절연층(250) 위에는 절연층(252)이 형성되어 있다. 그리고, 게이트 절연층(246), 절연층(250), 절연층(252) 등에 형성된 개구에는 전극(254)이 형성되고, 절연층(252) 위에는 전극(254)과 접속하는 배선(256)이 형성된다. 여기서, 도 1에서 나타낸 반도체 장치와 도 6에 나타낸 반도체 장치의 차이점 중 하나는 전극(254)의 유무이다. 또한, 도 6에서는 전극(254)을 사용하여, 소스 전극 또는 드레인 전극(242b)과 배선(256)을 접속하고 있는데, 개시하는 발명은 이에 한정되지 않는다. 예를 들면, 배선(256)을 직접, 소스 전극 또는 드레인 전극(242b)에 접촉시켜도 좋다.

또한, 금속화합물영역(224)과 접속되는 전극(미도시)과, 소스 전극 또는 드레인 전극(242b)을 서로 접속하여도 좋다. 이 경우, 금속화합물영역(224)과 접속되는 전극과, 소스 전극 및 드레인 전극(242b)과 배선(256)을 접속하는 전극(254)을 서로 중첩하여 배치하는 것이 바람직하다. 이와 같은 레이아웃을 채용함으로써, 반도체 장치의 고집적화를 도모할 수 있다.

또한, 도 6에 나타낸 반도체 장치는, 트랜지스터(262)로서, 소스 전극 및 드레인 전극 위에 산화물 반도체층을 형성한 상부 게이트형(top-gate) 트랜지스터를 사용하였지만, 본 실시형태에 따른 반도체 장치의 구성은 이에 한정되는 것이 아니다. 예를 들면, 도 7~도 9에 나타낸 바와 같은 반도체 장치의 구성으로 하여도 좋다.

도 7은 반도체 장치의 구성의 일 예이며, 도 7(A)에는 반도체 장치의 단면을, 도 7(B)에는 반도체 장치의 평면을 각각 나타낸다. 여기서, 도 7(A)는 도 7(B)의 A1-A2 및 B1-B2에 따른 단면에 상당한다.

도 7에 나타낸 반도체 장치와 도 6에 나타낸 반도체 장치의 차이점 중 하나는 산화물 반도체층(244) 위에 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)이 형성되어 있는 것이다. 이로써, 도 7에 나타낸 반도체 장치의 트랜지스터(272) 및 용량소자(274)의 구성은 도 6에 나타낸 반도체 장치의 트랜지스터(262) 및 용량소자(264)의 구성과는 다르다.

도 7에 나타낸 트랜지스터(272)는 절연층(230) 위에 형성된 산화물 반도체층(244)과, 산화물 반도체층(244) 위에 형성되며, 이 산화물 반도체층(244)과 전기적으로 접속되어 있는 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)과, 소스 전극 또는 드레인 전극(242a), 소스 전극 또는 드레인 전극(242b), 산화물 반도체층(244)을 덮는 게이트 절연층(246)과, 게이트 절연층(246) 위에 산화물 반도체층(244)과 중첩하도록 형성된 게이트 전극(248a)과, 소스 전극 또는 드레인 전극(242a)과 게이트 절연층(246) 사이의, 게이트 전극(248a)과 중첩하는 영역에 형성된 절연층(243a)과, 소스 전극 또는 드레인 전극(242b)과 게이트 절연층(246) 사이의, 게이트 전극(248a)과 중첩하는 영역에 형성된 절연층(243b)을 갖는다.

도 7에 나타낸 용량소자(274)는 소스 전극 또는 드레인 전극(242a), 게이트 절연층(246), 및 전극(248b)으로 구성된다. 즉, 소스 전극 또는 드레인 전극(242a)은 용량소자(274)의 일측 전극으로서 기능하며, 전극(248b)은 용량소자(274)의 타측 전극으로서 기능하게 된다.

또한, 도 7에 나타낸 반도체 장치의 다른 구성에 대해서는 도 6에 나타낸 반도체 장치와 마찬가지이므로, 도 6에 나타낸 반도체 장치를 참작할 수 있다.

도 8은 반도체 장치의 구성의 일 예이며, 도 8(A)에는 반도체 장치의 단면을, 도 8(B)에는 반도체 장치의 평면을 각각 나타낸다. 여기서, 도 8(A)는 도 8(B)의 A1-A2 및 B1-B2에 따른 단면에 상당한다.

도 8에 나타낸 반도체 장치와 도 6에 나타낸 반도체 장치의 차이점 중 하나는 게이트 절연층(246), 산화물 반도체층(244), 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)이 형성되어 있는 것이다. 즉, 도 8에 나타낸 반도체 장치의 트랜지스터(282)는 하부 게이트형(bottom-gate)이다. 이로써, 도 8에 나타낸 반도체 장치의 트랜지스터(282) 및 용량소자(284)의 구성은 도 6에 나타낸 반도체 장치의 트랜지스터(262) 및 용량소자(264)의 구성과는 다르다.

도 8에 나타낸 트랜지스터(282)는 절연층(230) 위에 형성된 게이트 전극(248a)과, 게이트 전극(248a)을 덮는 게이트 절연층(246)과, 게이트 절연층(246) 위에 형성된 소스 전극 또는 드레인 전극(242a) 및 소스 전극 또는 드레인 전극(242b)과, 소스 전극 또는 드레인 전극(242a) 및 소스 전극 또는 드레인 전극(242b) 위에 형성되며, 소스 전극 또는 드레인 전극(242a) 및 소스 전극 또는 드레인 전극(242b)과 전기적으로 접속되어 있는 산화물 반도체층(244)을 갖는다. 또한, 트랜지스터(282)는 절연층(243a) 및 절연층(243b)이 형성되어 있지 않다.

도 8에 나타낸 용량소자(284)는 소스 전극 또는 드레인 전극(242a), 게이트 절연층(246), 및 전극(248b)으로 구성된다. 즉, 소스 전극 또는 드레인 전극(242a)은 용량소자(284)의 일측 전극으로서 기능하며, 전극(248b)은 용량소자(284)의 타측 전극으로서 기능하게 된다.

또한, 도 8에 나타낸 반도체 장치의 다른 구성에 대해서는 도 6에 나타낸 반도체 장치와 마찬가지이므로, 도 6에 나타낸 반도체 장치를 참작할 수 있다.

도 9는 반도체 장치의 일 예이며, 도 9(A)에는 반도체 장치의 단면을, 도 9(B)에는 반도체 장치의 평면을 각각 나타낸다. 여기서, 도 9(A)는 도 9(B)의 A1-A2 및 B1-B2에 따른 단면에 상당한다.

도 9에 나타낸 반도체 장치와 도 6에 나타낸 반도체 장치의 차이점 중 하나는 게이트 전극(248a) 위에 게이트 절연층(246), 산화물 반도체층(244), 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)이 형성되어 있는 것이다. 즉, 도 9에 나타낸 반도체 장치의 트랜지스터(292)는 하부 게이트형이다. 이로써, 도 9에 나타낸 반도체 장치의 트랜지스터(292) 및 용량소자(294)의 구성은 도 6에 나타낸 반도체 장치의 트랜지스터(262) 및 용량소자(264)의 구성과는 다르다. 또한, 도 9에 나타낸 반도체 장치와 도 8에 나타낸 반도체 장치의 차이점 중 하나는 산화물 반도체층(244) 위에 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)이 형성되어 있는 것이다.

도 9에 나타낸 트랜지스터(292)는 절연층(230) 위에 형성된 게이트 전극(248a)과, 게이트 전극(248a)을 덮는 게이트 절연층(246)과, 게이트 절연층(246) 위에 형성된 산화물 반도체층(244)과, 산화물 반도체층 위에 형성되며 산화물 반도체층(244)과 전기적으로 접속되어 있는 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)을 갖는다. 또한, 트랜지스터(292)는 절연층(243a) 및 절연층(243b)이 형성되어 있지 않다.

도 9에 나타낸 용량소자(294)는 소스 전극 또는 드레인 전극(242a), 게이트 절연층(246), 및 전극(248b)으로 구성된다. 즉, 소스 전극 또는 드레인 전극(242a)은 용량소자(294)의 일측 전극으로서 기능하며, 전극(248b)은 용량소자(294)의 타측 전극으로서 기능하게 된다.

또한, 도 9에 나타낸 반도체 장치의 다른 구성에 대해서는 도 6에 나타낸 반도체 장치와 마찬가지이므로, 도 6에 나타낸 반도체 장치를 참작할 수 있다.

<반도체 장치의 제작방법>

이어, 상기 반도체 장치의 제작방법의 일 예에 대해 설명한다. 이하에서는 먼저 하부 트랜지스터(260)의 제작방법에 대해 도 10 및 도 11을 참조하여 설명하고, 그 후, 상부 트랜지스터(262) 및 용량소자(264)의 제작방법에 대해 도 12 및 도 13을 참조하여 설명한다.

<하부 트랜지스터의 제작방법>

먼저, 반도체 재료를 포함하는 기판(200)을 준비하고, 기판(200) 위에 소자분리절연층을 형성하기 위한 마스크가 되는 보호층(202)을 형성한다(도 10(A) 참조)

여기서, 기판(200)은 실시형태 1에서 나타낸 기판(100)과 마찬가지의 재료를 사용할 수 있다. 또한, 보호층(202)도 실시형태 1에서 나타낸 보호층(102)과 마찬가지의 재료를 사용할 수 있다. 이상의 상세사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

또한, 반도체 재료를 포함하는 기판(200)으로서, 특히 실리콘 등의 단결정 반도체 기판을 사용할 경우에는 반도체 장치의 읽기 동작을 고속화할 수 있기 때문에 바람직하다.

이어, 상기 보호층(202)을 마스크로 하여 에칭을 하여, 보호층(202)으로 덮여있지 않은 영역(노출되어 있는 영역)의 기판(200) 일부를 제거한다. 이로써, 다른 반도체영역과 분리된 반도체 장치(204)가 형성된다(도 10(B) 참조). 해당 에칭에는 건식 에칭을 사용하는 것이 바람직하지만, 습식 에칭을 사용하여도 좋다. 에칭 가스나 에칭액에 대해서는 피에칭재료에 따라 적절히 선택할 수 있다.

이어, 반도체영역(204)을 덮도록 절연층을 형성하고, 반도체영역(204)에 중첩하는 영역의 절연층을 선택적으로 제거함으로써, 소자분리절연층(206)을 형성한다(도 10(C) 참조). 소자분리절연층(206)은 실시형태 1에서 나타낸 소자분리절연층(106)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다. 따라서, 상세사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

그 후, 반도체영역(204)의 표면에 절연층을 형성하고, 해당 절연층 위에 도전재료를 포함하는 층을 형성한다. 그 후, 절연층 및 도전재료를 포함하는 층을 선택적으로 에칭하여 게이트 절연층(208), 게이트 전극(210)을 형성한다(도 10(C) 참조). 게이트 절연층(208) 및 게이트 전극(210)은 실시형태 1에서 나타낸 게이트 절연층(108) 및 게이트 전극(110)과 마간가지의 재료, 방법을 이용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

이어, 반도체영역(204)에 인(P)이나 비소(As) 등을 첨가하여 채널형성영역(216) 및 불순물영역(220)을 형성한다(도 10(D) 참조). 또한, 여기에서는 n형 트랜지스터를 형성하기 위해 인이나 비소를 첨가하고 있는데, p형 트랜지스터를 형성할 경우에는 붕소(B)나 알루미늄(Al) 등의 불순물 원소를 첨가하면 된다. 여기서, 첨가하는 불순물의 농도는 적절히 설정할 수 있지만, 반도체 소자가 고도로 미세화될 경우에는 그 농도를 높게 하는 것이 바람직하다.

또한, 게이트 전극(210)의 주위에 측벽 절연층을 형성하여, 불순물 원소가 다른 농도로 첨가된 불순물영역을 형성하여도 좋다.

이어, 게이트 전극(210), 불순물영역(220) 등을 덮도록 금속층(222)을 형성한다. 그리고나서, 열처리를 실시하여, 해당 금속층(222)과 반도체 재료를 반응시켜, 불순물영역(220)에 접하는 금속화합물영역(224)을 형성한다(도 11(A) 참조). 금속층(222) 및 금속화합물영역(224)은 실시형태 1에서 나타낸 금속층(122) 및 금속화합물영역(124)과 마찬가지의 재료, 방법을 이용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다. 해당 금속화합물영역을 형성함으로써, 전기 저항을 충분히 저감하고 소자 특성을 향상시킬 수 있다.

이어, 상술한 공정에 의해 형성된 각 구성을 덮도록 절연층(228), 절연층(230)을 형성한다(도 11(B) 참조). 절연층(228)이나 절연층(230)은 산화실리콘, 산화질화실리콘, 산화알루미늄 등의 무기절연재료를 포함하는 재료를 사용하여 형성할 수 있다. 특히, 절연층(228)이나 절연층(230)에 유전율이 낮은(low-k) 재료를 사용함으로써, 각종 전극이나 배선의 오버랩에 기인하는 용량을 충분히 저감하는 것이 가능해지기 때문에 바람직하다. 또한, 절연층(228)이나 절연층(230)에는 이들 재료를 사용한 다공성 절연층을 적용하여도 좋다. 다공성 절연층에서는 밀도가 높은 절연층에 비해 유전율이 저하되기 때문에, 전극이나 배선에 기인하는 용량을 더욱 저감하는 것이 가능하다.

또한, 절연층(228)이나 절연층(230) 중에, 질화산화실리콘, 질화실리콘 등의 질소를 많이 포함하는 무기절연재료로 이루어진 층을 포함하여도 좋다. 이로써, 하부 트랜지스터(260)를 구성하는 재료가 포함하는 물이나 수소 등의 불순물이 나중에 형성하는 상부 트랜지스터(262)의 산화물 반도체층(244)에 침입하는 것을 방지할 수 있다. 단, 이 경우, 이후의 공정에서 수행하는 CMP처리만으로는 질소를 많이 포함하는 무기절연재료로 이루어진 층의 제거가 곤란하므로, 에칭 처리 등을 병용하는 것이 바람직하다.

예를 들면, 절연층(228)으로서 산화질화실리콘을, 절연층(230)으로서 산화실리콘을 형성할 수 있다. 이와 같이, 절연층(228) 및 절연층(230)을 산화질화실리콘이나 산화실리콘과 같은 질소를 많이 포함하는 무기절연재료만을 이용하여 형성함으로써, 이후의 공정에서 절연층(228) 및 절연층(230)에 용이하게 CMP처리를 실시할 수 있다.

또한, 여기에서는 절연층(228)과 절연층(230)의 적층구조로 하고 있는데, 개시하는 발명의 일 양태는 이에 한정되지 않는다. 1층으로 하여도 좋고, 3층 이상의 적층 구조로 하여도 좋다. 예를 들면, 상기의 절연층(228)으로서 산화질화실리콘을 형성하고 절연층(230)으로서 산화실리콘을 형성하는 구성에 있어서, 추가로 절연층(228)과 절연층(230) 사이에 질화산화실리콘막을 형성하는 구성으로 하여도 좋다.

이상에 따라, 반도체 재료를 포함하는 기판(200)을 사용한 트랜지스터(260)가 형성된다(도 11(B) 참조). 이와 같은 트랜지스터(260)는 고속동작이 가능하다는 특징을 갖는다. 이 때문에, 해당 트랜지스터(260)를 읽기용 트랜지스터로서 사용함으로써, 정보의 읽기를 고속으로 수행할 수 있다.

그 후, 트랜지스터(262) 형성 전의 처리로서, 절연층(228)이나 절연층(230)에 CMP처리를 실시하여, 절연층(228) 및 절연층(230)의 표면을 평탄화함과 동시에 게이트 전극(210)의 상면을 노출시킨다(도 11(C) 참조).

CMP처리는 1회 실시하여도 좋고, 복수회 실시하여도 좋다. 복수회로 나눠 CMP처리를 실시할 경우에는 높은 연마율의 1차 연마를 실시한 후, 낮은 연마율의 마무리 연마를 수행하는 것이 바람직하다. 이와 같이 연마율이 다른 연마를 조합함으로써, 절연층(228) 및 절연층(230)의 표면 평탄성을 더욱 향상시킬 수 있다.

절연층(228) 및 절연층(230)을 평탄화시키는 처리로서는 CMP처리 외에 에칭처리 등을 적용하는 것도 가능하지만, 산화물 반도체층(244)의 평탄성 및 균일성을 향상시키고 트랜지스터(262)의 특성을 향상시키기 위해, 절연층(228)이나 절연층(230)의 표면은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하가 되도록 평탄화해 두는 것이 바람직하다.

또한, 절연층(228) 및 절연층(230)의 적층 구조에 질화실리콘이나 질화산화실리콘과 같은 질소를 많이 포함하는 무기절연재료가 포함될 경우, CMP처리만으로는 질소를 많이 포함하는 무기절연재료의 제거가 곤란하므로, 에칭처리 등을 병용하는 것이 바람직하다. 질소를 많이 포함하는 무기절연재료의 에칭처리에는 건식 에칭, 습식 에칭 중 어느 것을 사용하여도 좋지만, 소자의 미세화라는 관점에서는 건식 에칭을 사용하는 것이 바람직하다. 또한, 각 절연층의 에칭률이 균일해지며 또한 게이트 전극(210)과는 에칭의 선택비가 취해지도록, 에칭 조건(에칭가스나 에칭액, 에칭시간, 온도 등)을 적절히 설정하는 것이 바람직하다. 또한, 건식 에칭에 사용하는 에칭가스에는 예를 들면, 불소를 포함하는 가스(트리플루오로메탄(CHF3) 등)이나, 추가로 헬륨(He)이나 아르곤(Ar) 등의 희가스를 첨가한 가스 등을 사용할 수 있다.

또한, 게이트 전극(210)의 상면을 절연층(230)으로부터 노출시켰을 때, 게이트 전극(210)과 절연층(230)은 동일면을 형성하는 것이 바람직하다.

또한, 상기의 각 공정의 전후에는 추가로 전극이나 배선, 반도체층, 절연층 등을 형성하는 공정을 포함하고 있어도 좋다. 예를 들면, 금속화합물영역(224)의 일부와 접속되는, 트랜지스터(260)의 소스 전극 또는 드레인 전극으로서 기능하는 전극을 형성하여도 좋다. 또한, 배선의 구조로서, 절연층 및 도전층의 적층 구조로 된 다층배선구조를 채용하여, 고도로 집적화된 반도체 장치를 실현하는 것도 가능하다.

<상부 트랜지스터의 제작방법>

이어, 게이트 전극(210), 절연층(228), 절연층(230) 등의 위에 도전층을 형성하고, 이 도전층을 선택적으로 에칭하여, 소스 전극 또는 드레인 전극(242a), 소스 전극 또는 드레인 전극(242b)을 형성한다(도 12(A) 참조). 소스 전극 또는 드레인 전극(242a), 소스 전극 또는 드레인 전극(242b)은 실시형태 1에서 나타낸 소스 전극 또는 드레인 전극(142a), 소스 전극 또는 드레인 전극(142b)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

여기서, 소스 전극 또는 드레인 전극(242a), 소스 전극 또는 드레인 전극(242b)의 단부를 테이퍼 형상이 되도록 에칭함으로써, 나중에 형성되는 게이트 절연층(246)의 피복성을 향상시키고 단 끊어짐을 방지할 수 있다.

또한, 상부 트랜지스터의 채널 길이(L)는 소스 전극 또는 드레인 전극(242a), 및 소스 전극 또는 드레인 전극(242b)의 하단부의 간격에 의해 결정된다. 또한, 채널 길이(L)가 25nm 미만인 트랜지스터를 형성하는 경우에 사용하는 마스크 형성의 노광을 수행할 때에는 수 nm~수 10nm과 파장이 짧은 초자외선(Extreme Ultraviolet)을 사용하는 것이 바람직하다. 초자외선에 의한 노광은 해상도가 높고 초점심도도 크다. 따라서, 나중에 형성되는 트랜지스터의 채널 길이(L)를 10nm 이상 1000nm(1μm) 이하로 하는 것도 가능하며, 회로의 동작속도를 높이는 것이 가능하다. 또한, 미세화에 의해, 반도체 장치의 소비 전력을 저감하는 것도 가능하다.

여기서, 트랜지스터(262)의 소스 전극 또는 드레인 전극(242a)과 트랜지스터(260)의 게이트 전극(210)이 서로 직접 접속된다(도 12(A) 참조). 이와 같이, 게이트 전극(210)과 소스 전극 또는 드레인 전극(242a)을 서로 직접 접속함으로써, 게이트 전극(210)과 소스 전극 또는 드레인 전극(242a)을 콘택을 위한 개구 및 전극을 별도로 형성하여 서로 접속하는 경우보다, 콘택 면적을 축소할 수 있으므로, 반도체 장치의 고집적화를 도모할 수 있다. 따라서, 기억장치로서 사용할 수 있는 반도체 장치의 단위 면적당 기억용량을 증가시킬 수 있다. 또한, 콘택을 위해 별도로 형성하는 개구 및 전극에 필요한 공정을 생략할 수 있으므로, 반도체 장치 제작의 공정을 간략화할 수 있다.

이어, 소스 전극 또는 드레인 전극(242a) 위에 절연층(243a)을, 소스 전극 또는 드레인 전극(242b) 위에 절연층(243b)을 각각 형성한다(도 12(B) 참조). 절연층(243a) 및 절연층(243b)은 실시형태 1에서 나타낸 절연층(143a) 및 절연층(143b)과 마찬가지의 재료, 방법을 이용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다. 절연층(243a) 및 절연층(243b)을 마련함으로써, 게이트 전극과 소스 전극 또는 드레인 전극과의 사이의 용량을 저감하는 것이 가능하다.

또한, 게이트 전극과, 소스 전극 또는 드레인 전극과의 사이의 용량을 저감시킨다는 점에서는 절연층(243a) 및 절연층(243b)을 형성하는 것이 바람직하지만, 해당 절연층을 마련하지 않는 구성으로 하는 것도 가능하다.

이어, 소스 전극 또는 드레인 전극(242a) 및 소스 전극 또는 드레인 전극(242b)을 덮도록 산화물 반도체층을 형성한 후, 해당 산화물 반도체층을 선택적으로 에칭하여 산화물 반도체층(244)을 형성한다(도 12(C) 참조). 산화물 반도체층(244)은 실시형태 1에서 나타낸 산화물 반도체층(144)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

여기서, 산화물 반도체층(244)은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하인 표면을 갖는 절연층(230) 위에 형성된다. 이와 같이, 평탄성이 양호한 표면 위에 산화물 반도체층(244)을 형성함으로써, 산화물 반도체층(244)의 평탄성 및 균일성을 양호한 것으로 할 수 있다. 게다가, 평탄성 및 균일성이 양호한 산화물 반도체층(244)을 사용함으로써, 트랜지스터(262)의 트랜지스터 특성을 향상시킬 수 있다.

또한, 실시형태 1에서 나타낸 바와 같이, 산화물 반도체층을 스퍼터링법에 의해 형성하기 전에는, 아르곤 가스를 도입하여 플라즈마를 발생시키는 역스퍼터링을 수행하여, 형성 표면(예를 들면 절연층(230)의 표면)의 부착물을 제거하는 것이 바람직하다.

그리고나서, 산화물 반도체층에 대해 열처리(제 1 열처리)을 실시하는 것이 바람직하다. 열처리(제 1 열처리)와 관련해서는 실시형태 1에서 나타낸 것과 마찬가지의 방법으로 수행할 수 있다.

제 1 열처리에 의해 불순물을 저감하고 i형(진성 반도체) 또는 i형에 매우 가까운 산화물 반도체층을 형성함으로써, 매우 우수한 특성의 트랜지스터를 실현할 수 있다.

또한, 산화물 반도체층의 에칭은 상기 열처리 전, 또는 상기 열처리 후 중 어느 쪽에서든 수행하여도 좋다. 또한, 소자의 미세화라는 관점에서는 건식 에칭을 사용하는 것이 바람직하지만, 습식 에칭을 실시하여도 좋다. 에칭가스나 에칭액에 대해서는 피에칭재료에 따라 적절히 선택할 수 있다. 또한, 소자에서의 누설 등이 문제가 되지 않을 경우에는 산화물 반도체층을 섬형상으로 가공하지 않고 사용하여도 좋다.

이어, 산화물 반도체층(244)에 접하는 게이트 절연층(246)을 형성하고, 그 후, 게이트 절연층(246)에서 산화물 반도체층(244)과 중첩하는 영역에 게이트 전극(248a)을 형성하며, 소스 전극 또는 드레인 전극(242a)과 중첩하는 영역에 전극(248b)을 형성한다(도 12(D) 참조). 게이트 절연층(246)은 실시형태 1에서 나타낸 게이트 절연층(146)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다.

게이트 절연층(246)의 형성 후에는 비활성 가스 분위기 또는 산소 분위기하에서 제 2 열처리를 실시하는 것이 바람직하다. 제 2 열처리와 관련해서는 실시형태 1에서 나타낸 것과 마찬가지의 방법으로 수행할 수 있다. 제 2 열처리를 수행함으로써, 트랜지스터의 전기적 특성의 편차를 경감할 수 있다. 또한, 게이트 절연층(246)이 산소를 포함할 경우, 산화물 반도체층(244)에 산소를 공급하고, 이 산화물 반도체층(244)의 산소 결손을 보충하여, i형(진성 반도체) 또는 i형에 매우 가까운 산화물 반도체층을 형성할 수도 있다.

또한, 본 실시형태에서는 게이트 절연층(246)의 형성 후에 제 2 열처리를 실시하고 있는데, 제 2 열처리의 타이밍은 이에 한정되지 않는다. 예를 들면, 게이트 전극의 형성 후에 제 2 열처리를 실시하여도 좋다. 또한, 제 1 열처리에 이어서 제 2 열처리를 수행하여도 좋으며, 제 1 열처리에 제 2 열처리를 겸하게 하여도 좋고, 제 2 열처리에 제 1 열처리를 겸하게 하여도 좋다.

상술한 바와 같이, 제 1 열처리와 제 2 열처리 중 적어도 한쪽을 적용함으로써, 산화물 반도체층(244)을 그 주성분 이외의 불순물이 가능한 포함되지 않도록 고순도화할 수 있다.

게이트 전극(248a)은 실시형태 1에서 나타낸 게이트 전극(148a)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다. 또한, 게이트 전극(248a)을 형성할 때, 해당 도전층을 선택적으로 에칭함으로써 전극(248b)을 형성할 수 있다. 이상의 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

이어, 게이트 절연층(246), 게이트 전극(248a), 및 전극(248b) 위에 절연층(250) 및 절연층(252)을 형성한다(도 13(A) 참조). 절연층(250) 및 절연층(252)은 실시형태 1에서 나타낸 절연층(150) 및 절연층(152)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

이어, 게이트 절연층(246), 절연층(250), 절연층(252)에 소스 전극 또는 드레인 전극(242b)에까지 달하는 개구를 형성한다(도 13(B) 참조). 해당 개구의 형성은 마스크 등을 사용한 선택적인 에칭에 의해 수행된다.

그 후, 상기 개구에 전극(254)을 형성하고, 절연층(252) 위에 전극(254)에 접하는 배선(256)을 형성한다(도 13(C) 참조).

전극(254)은 예를 들면 개구를 포함하는 영역에 PVD법이나 CVD법 등을 사용하여 도전층을 형성한 후, 에칭처리나 CMP라는 방법을 사용하여, 상기 도전층의 일부를 제거함으로써 형성할 수 있다.

보다 구체적으로는 예를 들면, 개구를 포함하는 영역에 PVD법에 의해 티탄막을 얇게 형성하고, CVD법에 의해 질화티탄막을 얇게 형성한 후에, 개구에 메워 넣도록 텅스텐막을 형성하는 방법을 적용할 수 있다. 여기서, PVD법에 의해 형성되는 티탄막은 피형성면의 산화막(자연산화막 등)을 환원하여, 하부 전극 등(여기에서는 소스 전극 또는 드레인 전극(242b))과의 접촉 저항을 저감시키는 기능을 갖는다. 또한, 그 후에 형성되는 질화티탄막은 도전성 재료의 확산을 억제하는 배리어 기능을 구비한다. 또한, 티탄이나 질화티탄 등에 의한 배리어막을 형성한 후에, 도금법에 의해 구리막을 형성하여도 좋다.

또한, 상기 도전층의 일부를 제거하여 전극(254)을 형성할 때에는 그 표면이 평탄해지도록 가공하는 것이 바람직하다. 예를 들면, 개구를 포함하는 영역에 티탄막이나 질화티탄막을 얇게 형성한 후에, 개구에 메워 넣도록 텅스텐막을 형성할 경우에는 그 후의 CMP처리에 의해, 불필요한 텅스텐, 티탄, 질화티탄 등을 제거함과 아울러, 그 표면의 평탄성을 향상시킬 수 있다. 이와 같이, 전극(254)을 포함하는 표면을 평탄화함으로써, 이후의 공정에서, 양호한 전극, 배선, 절연층, 반도체층 등을 형성하는 것이 가능하게 된다.

배선(256)은 실시형태 1에서 나타낸 배선(156)과 마찬가지의 재료, 방법을 사용하여 형성할 수 있다. 따라서, 상세 사항에 대해서는 실시형태 1의 기재를 참작할 수 있다.

이상에 따라, 고순도화된 산화물 반도체층(244)을 사용한 트랜지스터(262), 및 용량소자(264)가 완성된다(도 13(C) 참조).

이와 같이 고순도화되고 진성화된 산화물 반도체층(244)을 사용함으로써, 트랜지스터의 오프 전류를 충분히 저감할 수 있다. 그리고, 이와 같은 트랜지스터를 사용함으로써, 매우 장기간에 걸쳐 기억내용을 홀딩하는 것이 가능한 반도체 장치가 얻어진다.

이상에 따라, 하부에 산화물 반도체층 이외의 반도체 재료를 사용한 트랜지스터를 가지며, 상부에 산화물 반도체를 사용한 트랜지스터를 갖는, 기억장치로서 사용할 수 있는 반도체 장치를 제공할 수 있다.

이와 같이, 산화물 반도체를 사용한 트랜지스터와, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 일체로 구비하는 구성으로 함으로써, 장시간에 걸친 정보의 홀딩이 가능하고 또한 정보의 읽기를 고속으로 수행하는 것이 가능한, 기억장치로서 사용할 수 있는 반도체 장치를 실현할 수 있다.

또한, 평탄성이 양호한 표면 위에 산화물 반도체층을 형성함으로써 트랜지스터 특성을 향상시킨 트랜지스터를, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터에 적층한 반도체 장치를 제공할 수 있다.

또한, 게이트 전극(210)과, 소스 전극 또는 드레인 전극(242a)을 서로 직접 접속함으로써, 콘택 면적을 축소할 수 있으므로, 반도체 장치의 고집적화를 도모할 수 있다. 따라서, 기억장치로서 사용할 수 있는 반도체 장치의 단위면적당 기억용량을 증가시킬 수 있다.

이상, 본 실시형태에 나타낸 구성, 방법 등은 다른 실시형태에 나타낸 구성, 방법 등과 적절히 조합하여 사용할 수 있다.

(실시형태 3)

본 실시형태에서는 개시하는 발명의 또 다른 일 양태에 따른 반도체 장치의 구성 및 그 제작방법에 대해, 도 14~도 16을 참조하여 설명한다. 또한, 본 실시형태에서는 특히 기억장치로서 사용할 수 있는 반도체 장치의 구성예에 대해 설명한다.

<반도체 장치의 단면 구성 및 평면 구성>

도 14는 본 실시형태에 따른 반도체 장치의 구성의 일 예이다. 도 14(A)에는 반도체 장치의 단면을, 도 14(B)에는 반도체 장치의 평면을 각각 나타낸다. 여기서, 도 14(A)는 도 14(B)의 C1-C2 및 D1-D2에 따른 단면에 상당한다. 도 14(A) 및 도 14(B)에 도시되는 반도체 장치는 하부에 제 1 반도체 재료를 사용한 트랜지스터(560)를 가지며, 상부에 제 2 반도체 재료를 사용한 트랜지스터(562)를 갖는 것으로, 트랜지스터(560)의 게이트 전극(524a)과 트랜지스터(562)의 소스 전극 또는 드레인 전극(542a)은 서로 직접 접속되어 있다. 여기서, 제 1 반도체 재료와 제 2 반도체 재료는 서로 다른 반도체 재료로 하는 것이 바람직하다. 예를 들면, 제 1 반도체 재료를 산화물 반도체 이외의 재료(실리콘 등)로 하고, 제 2 반도체 재료를 산화물 반도체로 할 수 있다. 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터(560)는 고속동작이 용이하다. 한편, 산화물 반도체를 사용한 트랜지스터(562)는 오프 전류를 충분히 저감함으로써 장시간의 전하 홀딩을 가능하게 한다.

이 때문에, 트랜지스터(562)를 오프 상태로 함으로써, 트랜지스터(560)의 게이트 전극(524a)의 전위를 매우 장시간에 걸쳐 홀딩하는 것이 가능하다. 그리고, 용량소자(564)를 가짐으로써, 트랜지스터(560)의 게이트 전극(524a)에 주어진 전하의 홀딩이 용이하게 되며, 또한 홀딩된 정보의 읽기가 용이하게 된다. 또한, 상기와 같은 반도체 재료를 사용한 트랜지스터(560)는 충분한 고속동작이 가능하므로, 정보의 읽기 속도를 향상시킬 수 있다.

또한, 상기 트랜지스터는 모두 n채널형 트랜지스터인 것으로 설명하지만, p채널형 트랜지스터를 사용할 수 있음은 말할 것까지도 없다. 또한, 개시하는 발명의 기술적 본질은 오프 전류가 충분히 저감된, 산화물 반도체를 사용한 트랜지스터와, 충분한 고속동작이 가능한, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 일체로 구비하는 점이기 때문에, 반도체 장치에 사용되는 재료나 반도체 장치의 구조 등 반도체 장치의 구체적인 구성을 여기에서 나타낸 것으로 한정할 필요는 없다.

도 14의 트랜지스터(560)는 베이스 기판(500) 위의 반도체층 중에 형성된 채널형성영역(526)과, 채널형성영역(526)을 사이에 끼우도록 형성된 불순물영역(528)과, 채널형성영역(526) 위에 형성된 게이트 절연층(522a)과, 게이트 절연층(522a) 위에 형성된 게이트 전극(524a)을 갖는다. 즉, 도 14의 트랜지스터(560)와 도 6의 트랜지스터(260)의 차이점 중 하나는 트랜지스터의 채널형성영역이 베이스 기판 위의 반도체층 중에 형성되는지 아닌지에 있다. 반도체 기판을 사용하는지, SOI 기판을 사용하는지의 차이라고 할 수도 있다. 또한, 도면에 있어서, 명시적으로는 소스 전극이나 드레인 전극을 갖지 않는 경우가 있지만, 편의상, 이와 같은 상태를 포함하여 트랜지스터라 부르는 경우가 있다.

또한, 트랜지스터(560)를 덮도록 절연층(532) 및 절연층(534)이 형성되어 있다. 또한, 도시하고 있지는 않지만, 트랜지스터(560)의 불순물영역(528)의 일부는 소스 전극이나 드레인 전극으로서 기능하는 전극을 통해 배선(556) 또는 다른 배선에 접속되어 있다. 또한, 고집적화를 실현하기 위해서는 도 14에 나타낸 바와 같이 트랜지스터(560)가 측벽 절연층을 갖지 않는 구성으로 하는 것이 바람직하다. 한편으로, 트랜지스터(560)의 특성을 중시하는 경우에는 게이트 전극(524a)의 측면에 측벽 절연층을 마련하고, 불순물 농도가 다른 영역을 포함하는 불순물영역(528)을 마련하여도 좋다.

도 14의 트랜지스터(562)는 도 6의 트랜지스터(262)와 마찬가지이다. 즉, 도 14의 트랜지스터(562)는 절연층(534) 위에 형성된 소스 전극 또는 드레인 전극(542a), 및 소스 전극 또는 드레인 전극(542b)과, 소스 전극 또는 드레인 전극(542a) 및 소스 전극 또는 드레인 전극(542b)과 전기적으로 접속되어 있는 산화물 반도체층(544)과, 소스 전극 또는 드레인 전극(542a), 소스 전극 또는 드레인 전극(542b), 산화물 반도체층(544)을 덮는 게이트 절연층(546)과, 게이트 절연층(546) 위에 산화물 반도체층(544)과 중첩하도록 형성된 게이트 전극(548a)과, 소스 전극 또는 드레인 전극(542a)과 산화물 반도체층(544) 사이의, 게이트 전극(548a)과 중첩하는 영역에 형성된 절연층(543a)과, 소스 전극 또는 드레인 전극(542b)과 산화물 반도체층(544) 사이의, 게이트 전극(548a)과 중첩하는 영역에 형성된 절연층(543b)을 갖는다. 또한, 소스 전극 또는 드레인 전극과 게이트 전극과의 사이의 용량을 저감하기 위해서는 절연층(543a) 및 절연층(543b)을 형성하는 것이 바람직하지만, 절연층(543a) 및 절연층(543b)을 형성하지 않는 구성으로 하는 것도 가능하다. 기타의 상세 사항에 대해서는 앞의 실시형태를 참작할 수 있다.

여기서, 산화물 반도체층(544)은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하인 표면을 갖는 절연층(534) 위에 형성된다. 이와 같이, 평탄성이 양호한 표면 위에 산화물 반도체층(544)을 형성함으로써, 산화물 반도체층(544)의 평탄성 및 균일성을 양호한 것으로 할 수 있다.

평탄성 및 균일성이 양호한 산화물 반도체층(544)을 사용함으로써, 산화물 반도체층의 계면에서의 캐리어 산란 방지, 계면 준위 저감을 도모할 수 있다. 이로써, 트랜지스터(562)의 이동도의 향상, S값 및 오프 전류의 저감을 도모하고, 트랜지스터 특성을 향상시킬 수 있다. 또한, 산화물 반도체층(544)의 평탄성을 향상시킴으로써, 트랜지스터(562)의 게이트 누설 전류를 저감할 수 있다.

또한, 도 14의 용량 소자(564)는 도 6의 용량소자(264)와 마찬가지이다. 즉, 도 14의 용량소자(564)는 소스 전극 또는 드레인 전극(542a), 산화물 반도체층(544), 게이트 절연층(546), 및 전극(548b)으로 구성된다. 즉, 소스 전극 및 드레인 전극(542a)은 용량소자(564)의 일측 전극으로서 기능하며, 전극(548b)은 용량 소자(564)의 타측 전극으로서 기능하게 된다. 기타 상세사항에 대해서는 앞의 실시형태를 참작할 수 있다.

트랜지스터(562) 및 용량소자(564) 위에 절연층(550)이 형성되며, 절연층(550) 위에는 절연층(552)이 형성되고, 게이트 절연층(546), 절연층(550), 절연층(552) 등에 형성된 개구에 전극(554)이 형성되고, 절연층(552) 위에는 전극(554)과 접속하는 배선(556)이 형성되어 있는 점에 대해서도 도 6과 마찬가지이다.

또한, 본 실시형태에 따른 반도체 장치의 구성은 도 14에 나타낸 반도체 장치에 한정되는 것이 아니다. 예를 들면, 트랜지스터(562) 및 용량소자(564) 대신에, 도 7에 나타낸 트랜지스터(272) 및 용량소자(274)를 사용하는 구성으로 하여도 좋고, 도 8에 나타낸 트랜지스터(282) 및 용량소자(284)를 사용하는 구성으로 하여도 좋으며, 도 9에 나타낸 트랜지스터(292) 및 용량소자(294)를 사용하는 구성으로 하여도 좋다.

<SOI 기판의 제작방법>

이어, 상기 반도체 장치의 제작에 사용되는 SOI 기판의 제작방법의 일 예에 대해, 도 15를 참조하여 설명한다.

먼저, 베이스 기판(500)을 준비한다(도 15(A) 참조). 베이스 기판(500)으로서는 절연체인 기판을 사용할 수 있다. 구체적으로는 알루미노실리케이트 유리, 알루미노보로실리케이트 유리, 바륨보로실리케이트 유리와 같은 전자공업용으로 사용되는 각종 유리 기판, 석영 기판, 세라믹 기판, 사파이어 기판을 들 수 있다. 또한, 질화실리콘과 산화알루미늄을 주성분으로 한 열팽창계수가 실리콘에 가까운 세라믹 기판을 사용하여도 좋다.

또한, 베이스 기판(500)으로서 단결정 실리콘 기판, 단결정 게르마늄 기판 등의 반도체 기판을 사용하여도 좋다. 베이스 기판(500)으로서 반도체 기판을 사용하는 경우에는 유리 기판 등을 사용하는 경우에 비해 열처리의 온도 조건이 완화되기 때문에, 양질의 SOI 기판을 얻는 것이 용이해진다. 여기서, 반도체 기판으로서는 태양전지급 실리콘(SOG-Si: Solar Grade Silicon) 기판 등을 사용하여도 된다. 또한, 다결정 반도체 기판을 사용하여도 좋다. 태양전지급 실리콘이나 다결정 반도체 기판 등을 사용할 경우에는 단결정 실리콘 기판 등을 사용하는 경우에 비해 제조 비용을 억제할 수 있다.

본 실시형태에서는 베이스 기판(500)으로서 유리 기판을 사용하는 경우에 대해 설명한다. 베이스 기판(500)으로서 대면적화가 가능하고 저렴한 유리 기판을 사용함으로써, 저비용화를 도모할 수 있다.

상기 베이스 기판(500)과 관해서는 그 표면을 미리 세척해 두는 것이 바람직하다. 구체적으로는 베이스 기판(500)에 대해, 염산 과산화수소수 혼합용액(HPM), 황산 과산화수소수 혼합용액(SPM), 암모니아 과산화수소수 혼합용액(APM), 희불산(DHF), FPM(불산, 과산화수소수, 순수의 혼합액) 등을 사용하여 초음파 세척을 실시한다. 이와 같은 세척처리를 실시함으로써, 베이스 기판(500) 표면의 평탄성 향상이나, 베이스 기판(500)의 표면에 잔존하는 연마입자의 제거 등이 실현된다.

이어, 베이스 기판(500)의 표면에, 질소함유층(502)(예를 들면, 질화실리콘막(SiNx)이나 질화산화실리콘막(SiNxOy)(x>y) 등의 질소를 함유하는 절연막을 포함하는 층)을 형성한다(도 15(B) 참조). 질소함유층(502)은 CVD법, 스퍼터링법 등을 사용하여 형성할 수 있다.

본 실시형태에서 형성되는 질소함유층(502)은 나중에 단결정 반도체층을 본딩하기 위한 층(접합층)이 된다. 또한, 질소함유층(502)은 베이스 기판에 포함되는 나트륨(Na) 등의 불순물이 단결정 반도체층으로 확산하는 것을 방지하기 위한 배리어층으로서도 기능한다.

상술한 바와 같이, 본 실시형태에서는 질소함유층(502)을 접합층으로서 사용하기 위해, 그 표면이 소정의 평탄성을 갖도록 질소함유층(502)을 형성하는 것이 바람직하다. 구체적으로는 표면의 평균 면거칠기(Ra, 산술 평균 거칠기라고도 함)가 0.5nm 이하, RMS 거칠기가 0.60nm 이하, 보다 바람직하게는 Ra가 0.35nm 이하, RMS가 0.45nm 이하가 되도록 질소함유층(502)을 형성한다. 또한, 상술한 평균 면거칠기나 제곱 평균 거칠기에는 예를 들면 10μm×10μm의 영역에서 측정한 값을 사용할 수 있다. 막두께는 10nm 이상 200nm 이하, 바람직하게는 50nm 이상 100nm 이하의 범위로 한다. 이와 같이, 표면의 평탄성을 높여 둠으로써, 단결정 반도체층의 접합 불량을 방지할 수 있다.

이어, 본딩 기판을 준비한다. 여기에서는 본딩 기판으로서 단결정 반도체 기판(510)을 사용한다(도 15(C) 참조). 또한, 여기에서는 본딩 기판으로서 단결정의 것을 사용하지만, 본딩 기판의 결정성을 단결정에 한정할 필요는 없다.

단결정 반도체 기판(510)으로서는 예를 들면 단결정 실리콘 기판, 단결정 게르마늄 기판, 단결정 실리콘 게르마늄 기판 등, 14족 원소로 이루어진 단결정 반도체 기판을 사용할 수 있다. 또한, 갈륨 비소나 인듐 인 등의 화합물 반도체 기판을 사용할 수도 있다. 시판하는 실리콘 기판으로서는 직경 5인치(125mm), 직경 6인치(150mm), 직경 8인치(200mm), 직경 12인치(300mm), 직경 16인치(400mm) 사이즈의 원형의 것이 대표적이다. 또한, 단결정 반도체 기판(510)의 형상은 원형에 한정되지 않으며, 예를 들면 직사각형 등으로 가공한 것이어도 좋다. 또한, 단결정 반도체 기판(510)은 CZ(초크랄스키)법이나 FZ(플로팅 존)법을 사용하여 제작할 수 있다.

단결정 반도체 기판(510)의 표면에는 산화막(512)을 형성한다(도 15(D) 참조). 또한, 오염물 제거의 관점에서, 산화막(512)의 형성 전에, 염산 과산화수소수 혼합용액(HPM), 황산 과산화수소 혼합용액(SPM), 암모니아 과산화수소수 혼합용액(APM), 희불산(DHF), FPM(불산, 과산화수소수, 순수의 혼합액) 등을 사용하여 단결정 반도체 기판(510)의 표면을 세척해 두는 것이 바람직하다. 희불산과 오존수를 교대로 토출하여 세척하여도 좋다.

산화막(512)은 예를 들면 산화실리콘막, 산화질화실리콘막 등을 단층으로 또는 적층시켜 형성할 수 있다. 상기 산화막(512)의 제작방법으로서는 열산화법, CVD법, 스퍼터링법 등이 있다. 또한, CVD법을 사용하여 산화막(512)을 형성할 경우, 양호한 본딩을 실현하기 위해서는 테트라에톡시실란(약칭; TEOS: 화학식 Si(OC2H5)4) 등의 유기 실란을 사용하여 산화실리콘막을 형성하는 것이 바람직하다.

본 실시형태에서는 단결정 반도체 기판(510)에 열산화처리를 실시함으로써 산화막(512)(여기에서는 SiOx막)을 형성한다. 열산화처리는 산화성 분위기 중에 할로겐을 첨가하여 수행하는 것이 바람직하다.

예를 들면, 염소(Cl)가 첨가된 산화성 분위기 중에서 단결정 반도체 기판(510)에 열산화처리를 실시함으로써, 염소산화된 산화막(512)을 형성할 수 있다. 이 경우, 산화막(512)은 염소 원자를 함유하는 막이 된다. 이와 같은 염소산화에 의해, 외인성의 불순물인 중금속(예를 들면, Fe, Cr, Ni, Mo 등)을 포집하여 금속의 염화물을 형성하고, 이를 바깥쪽으로 제거하여 단결정 반도체 기판(510)의 오염을 저감시킬 수 있다. 또한, 베이스 기판(500)과 본딩한 후에, 베이스 기판으로부터의 Na 등의 불순물을 고정하여 단결정 반도체 기판(510)의 오염을 방지할 수 있다.

또한, 산화막(512)에 함유시키는 할로겐 원자는 염소 원자에 한정되지 않는다. 산화막(512)에는 불소 원자를 함유시켜도 좋다. 단결정 반도체 기판(510)의 표면을 불소산화하는 방법으로서는 HF 용액에 침지시킨 후에 산화성 분위기 중에서 열산화처리를 실시하는 방법이나, NF3을 산화성 분위기에 첨가하여 열산화처리를 실시하는 방법 등이 있다.

이어, 이온을 전계에 의해 가속하여 단결정 반도체 기판(510)에 조사하고 첨가함으로써, 단결정 반도체 기판(510)의 소정 깊이에 결정구조가 손상된 취화(脆化)영역(514)을 형성한다(도 15(E) 참조).

취화영역(514)이 형성되는 영역의 깊이는 이온의 운동 에너지, 질량과 전하, 이온의 입사각 등에 따라 조절할 수 있다. 또한, 취화영역(514)은 이온의 평균 침입깊이와 거의 동일한 깊이의 영역에 형성된다. 이 때문에, 이온을 첨가하는 깊이로, 단결정 반도체 기판(510)으로부터 분리되는 단결정 반도체층의 두께를 조절할 수 있다. 예를 들면, 단결정 반도체층의 두께가 10nm 이상 500nm 이하, 바람직하게는 50nm 이상 200nm 이하 정도가 되도록 평균 침입 깊이를 조절하면 된다.

해당 이온의 조사처리는 이온 도핑 장치나 이온 주입 장치를 사용하여 수행할 수 있다. 이온 도핑 장치의 대표예로서는 프로세스 가스를 플라즈마 여기하여 생성된 모든 이온종을 피처리체에 조사하는 비질량분리형 장치가 있다. 해당 장치에서는 플라즈마 중의 이온종을 질량분리하지 않고 피처리체에 조사하게 된다. 이에 반해, 이온 주입 장치는 질량분리형 장치이다. 이온 주입 장치에서는 플라즈마 중의 이온종을 질량분리하고, 어느 특정 질량의 이온종을 피처리체에 조사한다.

본 실시형태에서는 이온 도핑 장치를 사용하여, 수소를 단결정 반도체 기판(510)에 첨가하는 예에 대해 설명한다. 소스 가스로서는 수소를 포함하는 가스를 사용한다. 조사하는 이온에 대해서는 H3+의 비율을 높게 하면 좋다. 구체적으로는 H+, H2+, H3+의 총량에 대해 H3+의 비율이 50% 이상(보다 바람직하게는 80% 이상)이 되도록 한다. H3+의 비율을 높임으로써, 이온 조사의 효율을 향상시킬 수 있다.

또한, 첨가하는 이온은 수소에 한정되지 않는다. 헬륨 등의 이온을 첨가하여도 좋다. 또한, 첨가하는 이온은 1종류에 한정되지 않고, 복수 종류의 이온을 첨가하여도 좋다. 예를 들면, 이온 도핑 장치를 사용하여 수소와 헬륨을 동시에 조사할 경우에는 다른 공정에서 조사하는 경우와 비교하여 공정 수를 저감할 수 있음과 아울러, 이후의 단결정 반도체층의 표면 거칠기를 억제하는 것이 가능하다.

또한, 이온 도핑 장치를 사용하여 취화영역(514)을 형성할 경우에는 중금속도 동시에 첨가될 우려가 있는데, 할로겐 원자를 함유하는 산화막(512)을 통해 이온 조사를 수행함으로써, 이들 중금속으로 인한 단결정 반도체 기판(510)의 오염을 방지할 수 있다.

이어, 베이스 기판(500)과 단결정 반도체 기판(510)을 서로 마주보게 하여, 질소함유층(502)의 표면과 산화막(512)의 표면을 서로 밀착시킨다. 이로써, 베이스 기판(500)과 단결정 반도체 기판(510)이 서로 본딩된다(도 15(F) 참조).

본딩 시에는 베이스 기판(500) 또는 단결정 반도체 기판(510)의 한군데에, 0.001N/cm2 이상 100N/cm2 이하, 예를 들면 1N/cm2 이상 20N/cm2 이하의 압력을 첨가하는 것이 바람직하다. 압력을 가해, 본딩면을 접근, 밀착시키면, 밀착시킨 부분에서 질소함유층(502)과 산화막(512)의 접합이 발생하며, 해당 부분을 시작점으로 하여 자발적인 접합이 거의 전면(全面)에 미친다. 이 접합에는 반데르발스힘(Van der Waals force)이나 수소 결합이 작용하고 있으며, 상온에서 수행할 수 있다.

또한, 단결정 반도체 기판(510)과 베이스 기판(500)을 서로 본딩하기 전에는 본딩과 관련된 표면에 대해 표면처리를 실시하는 것이 바람직하다. 표면처리를 실시함으로써, 단결정 반도체 기판(510)과 베이스 기판(500)과의 계면에서의 접합 강도를 향상시킬 수 있다.

표면처리로서는 습식 처리, 건식 처리, 또는 습식 처리와 건식 처리의 조합을 사용할 수 있다. 또한, 서로 다른 습식 처리들을 조합하여 사용하여도 좋고, 서로 다른 건식 처리들을 조합하여 사용하여도 좋다.

또한, 본딩 후에는 접합 강도를 증가시키기 위한 열처리를 실시하여도 좋다. 이 열처리의 온도는 취화영역(514)에서의 분리가 발생하지 않는 온도(예를 들면, 실온 이상 400℃ 미만)로 한다. 또한, 이 온도범위에서 가열하면서, 질소함유층(502)과 산화막(512)을 서로 접합시켜도 좋다. 상기 열처리에는 확산로, 저항가열로 등의 가열로, RTA(순간 열 어닐링, Rapid Thermal Anneal) 장치, 마이크로파 가열장치 등을 사용할 수 있다. 또한, 상기 온도 조건은 어디까지나 일 예에 지나지 않으며, 개시하는 발명의 일 양태가 이에 한정하여 해석되는 것이 아니다.

이어, 열처리를 실시함으로써, 단결정 반도체 기판(510)을 취화영역에서 분리하여, 베이스 기판(500) 위에 질소함유층(502) 및 산화막(512)을 통해 단결정 반도체층(516)을 형성한다(도 15(G) 참조).

또한, 상기 분리시의 열처리 온도는 가능한 낮은 것인 것이 바람직하다. 분리시의 온도가 낮을수록, 단결정 반도체층(516)의 표면 거칠기를 억제할 수 있기 때문이다. 구체적으로는 예를 들면 상기 분리시의 열처리 온도는 300℃ 이상 600℃ 이하로 하면 되며, 400℃ 이상 500℃ 이하로 하면, 보다 효과적이다.

또한, 단결정 반도체 기판(510)을 분리한 후에는 단결정 반도체층(516)에 대해 500℃ 이상의 온도에서 열처리를 실시하여, 단결정 반도체층(516) 중에 잔존하는 수소의 농도를 저감시켜도 좋다.

이어, 단결정 반도체층(516)의 표면에 레이저광을 조사함으로써, 표면의 평탄성을 향상시키고 또한 결함을 저감시킨 단결정 반도체층(518)을 형성한다(도 15(H) 참조). 또한, 레이저광의 조사처리 대신에, 열처리를 실시하여도 좋다.

또한, 본 실시형태에서는 단결정 반도체층(516)의 분리를 위한 열처리 직후에, 레이저광의 조사처리를 실시하고 있는데, 개시하는 발명의 일 양태는 이에 한정하여 해석되지 않는다. 단결정 반도체층(516)의 분리와 관련된 열처리 후에 에칭처리를 실시하여, 단결정 반도체층(516) 표면의 결함이 많은 영역을 제거하고 나서, 레이저광의 조사처리를 실시하여도 좋고, 단결정 반도체층(516) 표면의 평탄성을 향상시키고 나서 레이저광의 조사처리를 실시하여도 좋다. 또한, 상기 에칭처리로서는 습식 에칭, 건식 에칭 중 어느 것을 사용하여도 좋다. 또한, 본 실시형태에서는 상술한 바와 같이 레이저광을 조사한 후, 단결정 반도체층(516)의 막두께를 작게 하는 박막화 공정을 실시하여도 좋다. 단결정 반도체층(516)의 박막화에는 건식 에칭 및 습식 에칭 중 한쪽 또는 양쪽 모두를 사용하면 된다.

이상의 공정에 따라, 양호한 특성의 단결정 반도체층(518)을 갖는 SOI 기판을 얻을 수 있다(도 15(H) 참조).

<반도체 장치의 제작방법>

이어, 상기의 SOI 기판을 사용한 반도체 장치의 제작방법, 특히 트랜지스터(560)의 제작방법에 대해 도 16을 참조하여 설명한다. 또한, 도 16은 도 15에 나타낸 방법으로 작성한 SOI 기판의 일부로서, 도 14(A)에 상당하는 단면도이다.

먼저, 단결정 반도체층(518)을 섬형상으로 가공하여 반도체층(520)을 형성한다(도 16(A) 참조). 또한, 이 공정의 전후에, 트랜지스터의 문턱 전압을 제어하기 위해, n형의 도전성을 부여하는 불순물 원소나 p형의 도전성을 부여하는 불순물 원소를 반도체층에 첨가하여도 좋다. 반도체층이 실리콘인 경우, n형의 도전성을 부여하는 불순물 원소로서는 예를 들면 인이나 비소 등을 사용할 수 있다. 또한, p형의 도전성을 부여하는 불순물 원소로서는 예를 들면 비소, 알루미늄, 갈륨 등을 사용할 수 있다.

이어, 반도체층(520)을 덮도록 절연층(522)을 형성하고, 절연층(522) 위의 반도체층(520)과 중첩하는 영역에 도전층(524)을 형성한다(도 16(B) 참조).

절연층(522)은 나중에 게이트 절연층이 되는 것이다. 절연층(522)은 예를 들면 반도체층(520) 표면의 열처리(열산화처리나 열질화처리 등)에 의해 형성할 수 있다. 열처리 대신에, 고밀도 플라즈마 처리를 적용하여도 좋다. 고밀도 플라즈마 처리는 예를 들면 He, Ar, Kr, Xe 등의 희가스, 산소, 산화질소, 암모니아, 질소, 수소 등 중 어느 한 혼합가스를 사용하여 수행할 수 있다. 물론, CVD법이나 스퍼터링법 등을 사용하여 절연층을 형성하여도 좋다. 해당 절연층은 산화실리콘, 산화질화실리콘, 질화산화실리콘, 질화실리콘, 산화하프늄, 산화알루미늄, 산화탄탈, 산화이트륨, 하프늄 실리케이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 실리게이트(HfSixOy(x>0, y>0)), 질소가 첨가된 하프늄 알루미네이트(HfAlxOy(x>0, y>0)) 등을 포함하는 단층 구조 또는 적층 구조로 하는 것이 바람직하다. 또한, 절연층의 두께는 1nm 이상 100nm 이하, 바람직하게는 10nm 이상 50nm 이하로 할 수 있다. 여기에서는 플라즈마 CVD법을 사용하여, 산화실리콘을 포함하는 절연층을 단층으로 형성하는 것으로 한다.

도전층(524)은 나중에 게이트 전극이 되는 것이다. 도전층(524)은 알루미늄이나 구리, 티탄, 탄탈, 텅스텐 등의 금속재료를 사용하여 형성할 수 있다. 또한, 다결정 실리콘 등의 반도체 재료를 사용하여, 도전재료를 포함하는 층을 형성하여도 좋다. 형성방법도 특별히 한정되지 않으며, 증착법, CVD법, 스퍼터링법, 스핀 코팅법 등의 각종 성막방법을 사용할 수 있다. 또한, 본 실시형태에서는 도전재료를 포함하는 층을 금속재료를 사용하여 형성하는 경우의 일 예에 대해 나타내는 것으로 한다.

이어, 절연층(522) 및 도전층(524)을 선택적으로 에칭하여 반도체층(520)의 상방에 게이트 절연층(522a) 및 게이트 전극(524a)을 형성한다(도 16(C) 참조). 해당 에칭에는 건식 에칭을 사용하는 것이 바람직하지만, 습식 에칭을 사용하여도 좋다. 에칭가스나 에칭액은 피에칭재료에 따라 적절히 선택할 수 있다.

그 후, 게이트 전극(524a)을 마스크로 하여, 일 도전형을 부여하는 불순물 원소를 반도체층(520)에 첨가하여 채널형성영역(526) 및 불순물영역(528)을 형성한다(도 16(D) 참조). 또한, 여기에서는 n형 트랜지스터를 형성하기 위해 인(P)이나 비소(As)를 첨가하지만, p형 트랜지스터를 형성할 경우에는 붕소(B)나 알루미늄(Al) 등의 불순물 원소를 첨가하면 된다. 여기서, 첨가되는 불순물의 농도는 적절히 설정할 수 있다. 또한, 불순물 원소를 첨가한 후에는 활성화를 위한 열처리를 실시한다.

또한, 반도체층(520)이 실리콘을 포함하는 재료인 경우에는 소스 영역 및 드레인 영역을 더욱 저저항화하기 위해, 반도체층(520)의 일부를 실리사이드화한 실리사이드 영역을 형성하여도 좋다. 실리사이드 영역의 형성은 반도체층에 금속을 접촉시켜, 가열처리(예를 들면, GRTA법, LRTA법, 레이저광의 조사 등)에 의해, 반도체층 중의 실리콘과 금속을 서로 반응시켜 수행한다. 실리사이드로서는 예를 들면 코발트 실리사이드나 니켈 실리사이드를 형성하면 된다. 반도체층(520)이 얇은 경우에는 반도체층(520)의 저부까지 실리사이드 반응을 진행하여도 좋다. 실리사이드화에 사용할 수 있는 금속재료로서는 코발트나 니켈 외에, 티탄, 텅스텐, 몰리브덴, 지르코늄, 하프늄, 탄탈, 바나듐, 네오디뮴, 크롬, 백금, 팔라듐 등을 들 수 있다.

이어, 상술한 공정에 의해 형성된 각 구성을 덮도록, 절연층(532), 절연층(534)을 형성한다(도 16(D) 참조). 절연층(532)이나 절연층(534)은 산화실리콘, 산화질화실리콘, 산화알루미늄 등의 무기절연재료를 포함하는 재료를 사용하여 형성할 수 있다. 특히, 절연층(532)이나 절연층(534)에 유전율이 낮은(low-k) 재료를 사용함으로써, 각종 전극이나 배선의 오버랩에 기인하는 용량을 충분히 저감하는 것이 가능하게 되기 때문에 바람직하다. 또한, 절연층(532)이나 절연층(534)에는 이들 재료를 사용한 다공성 절연층을 적용하여도 좋다. 다공성 절연층에서는 밀도가 높은 절연층에 비해 유전율이 저하되기 때문에, 전극이나 배선에 기인하는 용량을 더욱 저감하는 것이 가능하다.

또한, 절연층(532)이나 절연층(534) 중에 질화산화실리콘, 질화실리콘 등의 질소를 많이 포함하는 무기절연재료로 이루어진 층을 포함하여도 좋다. 이로써, 하부 트랜지스터(560)를 구성하는 재료가 포함하는 물이나 수소 등의 불순물이 나중에 형성하는 상부 트랜지스터(562)의 산화물 반도체층(544)에 침입하는 것을 방지할 수 있다. 단, 이 경우, 이후의 공정에서 수행하는 CMP처리만으로는 질소를 많이 포함하는 무기절연재료로 이루어진 층의 제거가 곤란하므로, 에칭처리 등을 병용하는 것이 바람직하다.

예를 들면, 절연층(532)으로서 산화질화실리콘을 형성하고, 절연층(534)로서 산화실리콘을 형성할 수 있다. 이와 같이, 절연층(532) 및 절연층(534)을 산화질화실리콘이나 산화실리콘과 같은 산소를 많이 포함하는 무기절연재료만을 사용하여 형성함으로써, 이후의 공정에서 절연층(532) 및 절연층(534)에 용이하게 CMP처리를 실시할 수 있다.

또한, 여기에서는 절연층(532)과 절연층(534)의 적층구조로 하고 있는데, 개시하는 발명의 일 양태는 이에 한정되지 않는다. 1층으로 하여도 좋고, 3층 이상의 적층 구조로 하여도 좋다. 예를 들면, 상기의 절연층(532)으로서 산화질화실리콘을 형성하고, 절연층(534)으로서 산화실리콘막을 형성하는 구성에서, 추가로 절연층(532)과 절연층(534) 사이에 질화산화실리콘을 형성하는 구성으로 하여도 좋다.

이상에 따라, SOI 기판을 사용한 트랜지스터(560)가 형성된다(도 16(D) 참조). 산화물 반도체 이외의 재료를 사용한 트랜지스터(560)는 고속동작이 가능하기 때문에, 해당 트랜지스터를 읽기용 트랜지스터로서 사용함으로써, 읽기 동작을 고속화할 수 있다. 또한, 트랜지스터(560)를 이용하여, 다른 논리회로(연산회로라고도 함) 등을 구성할 수도 있다.

그 후, 절연층(532)이나 절연층(534)에 CMP처리를 실시하여 게이트 전극(524a)의 상면을 노출시킨다(도 16(E) 참조). 게이트 전극(524a)의 상면을 노출시키는 처리로서는 CMP처리 외에 에칭 처리 등을 적용하는 것도 가능하지만, 나중에 형성되는 트랜지스터(562)의 특성을 향상시키기 위해, 절연층(532)이나 절연층(534)의 표면은 가능한 평탄하게 해 두는 것이 바람직하다.

그 후, 트랜지스터(562) 형성 전의 처리로서, 절연층(532)이나 절연층(534)에 CMP처리를 실시하여, 절연층(532) 및 절연층(534)의 표면을 평탄화함과 동시에 게이트 전극(524a)의 상면을 노출시킨다(도 16(E) 참조).

CMP처리는 1회 실시하여도 좋으며, 복수회 실시하여도 좋다. 복수회로 나눠 CMP처리를 실시할 경우는 높은 연마율의 1차 연마를 실시한 후, 낮은 연마율의 마무리 연마를 수행하는 것이 바람직하다. 이와 같이 연마율이 다른 연마를 조합함으로써, 절연층(532) 및 절연층(534) 표면의 평탄성을 더욱 향상시킬 수 있다.

절연층(532) 및 절연층(534)을 평탄화시키는 처리로서는 CMP처리 외에 에칭처리 등을 적용하는 것도 가능하지만, 산화물 반도체층(544)의 평탄성 및 균일성을 향상시키고 트랜지스터(562)의 특성을 향상시키기 위해, 절연층(532)이나 절연층(534)의 표면은 RMS 거칠기가 1nm 이하, 바람직하게는 0.5nm 이하가 되도록 평탄화해 두는 것이 바람직하다.

또한, 절연층(532) 및 절연층(534)의 적층 구조에 질화실리콘이나 질화산화실리콘과 같은 질소를 많이 포함하는 무기절연재료가 포함될 경우, CMP처리만으로는 질소를 많이 포함하는 무기절연재료의 제거가 곤란하므로, 에칭 처리 등을 병용하는 것이 바람직하다. 질소를 많이 포함하는 무기절연재료의 에칭 처리에는 건식 에칭, 습식 에칭 중 어느 것을 사용하여도 좋지만, 소자의 미세화라는 관점에서는 건식 에칭을 사용하는 것이 바람직하다. 또한, 각 절연층의 에칭률이 균일하게 되되고, 또한 게이트 전극(524a)과는 에칭의 선택비가 취해지도록 에칭조건(에칭가스나 에칭액, 에칭시간, 온도 등)을 적절히 설정하는 것이 바람직하다. 또한, 건식 에칭에 사용하는 에칭가스에는 예를 들면, 불소를 포함하는 가스(트리플루오로메탄(CHF3) 등)나, 추가로 헬륨(He)이나 아르곤(Ar) 등의 희가스를 첨가한 가스 등을 사용할 수 있다.

또한, 게이트 전극(524a)의 상면을 절연층(534)으로부터 노출시켰을 때, 게이트 전극(524a)과 절연층(534)은 동일면을 형성하는 것이 바람직하다.

또한, 상기의 각 공정의 전후에는 추가로 전극이나 배선, 반도체층, 절연층 등을 형성하는 고정을 포함하고 있어도 좋다. 예를 들면, 불순물영역(528)의 일부와 접속되는, 트랜지스터(560)의 소스 전극 또는 드레인 전극으로서 기능하는 전극을 형성하여도 좋다. 또한, 배선의 구조로서, 절연층 및 도전층의 적층 구조로 이루어진 다층배선구조를 채용하여, 고도로 집적화된 반도체 장치를 실현하는 것도 가능하다.

그 후, 트랜지스터(560)와 전기적으로 접속하는 트랜지스터(562) 및 용량소자(564)를 형성한다(도 14(A) 참조). 트랜지스터(562) 및 용량소자(564)의 제작방법은 트랜지스터(262) 및 용량소자(264)의 경우와 마찬가지이기 때문에, 여기에서는 생략한다. 제작방법의 상세 사항에 대해서는 앞의 실시형태를 참작할 수 있다.

이상에 따라, 하부에 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터를 가지며, 상부에 산화물 반도체를 사용한 트랜지스터를 갖는, 기억장치로서 사용할 수 있는 반도체 장치를 제공할 수 있다.

이와 같이, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터와, 산화물 반도체를 사용한 트랜지스터를 일체로 구비하는 구성으로 함으로써, 장시간에 걸친 정보의 홀딩이 가능하며 또한 정보의 읽기를 고속으로 수행하는 것이 가능한, 기억장치로서 사용할 수 있는 반도체 장치를 실현할 수 있다.

또한, 평탄성이 양호한 표면 위에 산화물 반도체층을 형성함으로써 트랜지스터 특성을 향상시킨 트랜지스터를, 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터에 적층한 반도체 장치를 제공할 수 있다.

또한, 게이트 전극(524a)과 소스 전극 또는 드레인 전극(542a)을 서로 직접 접속함으로써, 콘택 면적을 축소할 수 있으므로, 반도체 장치의 고집적화를 도모할 수 있다. 따라서, 기억장치로서 사용할 수 있는 반도체 장치의 단위면적당 기억용량을 증가시킬 수 있다.

이상, 본 실시형태에 나타낸 구성, 방법 등은 다른 실시형태에 나타낸 구성, 방법 등과 적절히 조합하여 사용할 수 있다.

(실시형태 4)

본 실시형태에서는 개시하는 발명의 일 양태에 따른 반도체 장치의 응용예에 대해, 도 17을 참조하여 설명한다. 여기에서는 기억장치의 일 예에 대해 설명한다. 또한, 회로도에서는 산화물 반도체를 사용한 트랜지스터인 것을 나타내기 위해, OS의 부호를 함께 붙이는 경우가 있다.

도 17(A-1)에 나타낸 반도체 장치에서, 제 1 배선(1st Line)과 트랜지스터(700)의 소스 전극은 서로 전기적으로 접속되고, 제 2 배선(2nd Line)과 트랜지스터(700)의 드레인 전극은 서로 전기적으로 접속되어 있다. 그리고, 트랜지스터(700)의 게이트 전극과 트랜지스터(710)의 소스 전극 및 드레인 전극 중 한쪽은 용량소자(720)의 전극 중 한쪽과 전기적으로 접속된다. 또한, 제 3 배선(3rd Line)과 트랜지스터(710)의 소스 전극 및 드레인 전극 중 다른 쪽은 서로 전기적으로 접속되고, 제 4 배선(4th Line)과 트랜지스터(710)의 게이트 전극은 서로 전기적으로 접속되어 있다. 또한, 제 5 배선(5th Line)과 용량소자(720)의 전극 중 다른 쪽은 서로 전기적으로 접속되어 있다.

여기서, 트랜지스터(710)에는 산화물 반도체를 사용한 트랜지스터가 적용된다. 여기서, 산화물 반도체를 사용한 트랜지스터로서는 예를 들면, 앞의 실시형태에 나타낸 트랜지스터(262), 트랜지스터(272), 트랜지스터(282), 트랜지스터(292), 트랜지스터(562)를 사용할 수 있다. 산화물 반도체를 사용한 트랜지스터는 오프 전류가 극히 작다는 특징을 갖고 있다. 이 때문에, 트랜지스터(710)를 오프 상태로 함으로써, 트랜지스터(700)의 게이트 전극의 전위를 매우 장시간에 걸쳐 홀딩하는 것이 가능하다. 그리고, 용량소자(720)를 가짐으로써, 트랜지스터(700)의 게이트 전극에 주어진 전하의 홀딩이 용이하게 되며, 또한 홀딩된 정보의 읽기가 용이하게 된다. 여기서, 용량소자(720)로서는 예를 들면 앞의 실시형태에서 나타낸 용량소자(264), 용량소자(274), 용량소자(284), 용량소자(294), 용량소자(564)를 사용할 수 있다.

또한, 트랜지스터(700)에는 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터가 적용된다. 산화물 반도체 이외의 반도체 재료로서는 예를 들면 실리콘, 게르마늄, 실리콘 게르마늄, 탄화실리콘, 또는 갈륨 비소 등을 사용할 수 있으며, 단결정 반도체를 사용하는 것이 바람직하다. 그 밖에, 유기 반도체 재료 등을 사용하여도 좋다. 이와 같은 반도체 재료를 사용한 트랜지스터는 고속동작이 용이하다. 여기에서 산화물 반도체 이외의 반도체 재료를 사용한 트랜지스터로서는 예를 들면 앞의 실시형태에서 나타낸 트랜지스터(260) 또는 트랜지스터(560)를 사용할 수 있다.

또한, 도 17(B)에 나타낸 바와 같이, 용량소자(720)를 마련하지 않는 구성으로 하는 것도 가능하다.

도 17(A-1)에 나타낸 반도체 장치에서는 트랜지스터(700)의 게이트 전극의 전위가 홀딩가능하다는 특징을 살림으로써, 다음과 같이, 정보의 쓰기, 홀딩, 읽기가 가능하다.

먼저, 정보의 쓰기 및 홀딩에 대해 설명한다. 먼저, 제 4 배선의 전위를 트랜지스터(710)가 온 상태가 되는 전위로 하여 트랜지스터(710)를 온 상태로 한다. 이로써, 제 3 배선의 전위가 트랜지스터(700)의 게이트 전극 및 용량소자(720)에 부여된다. 즉, 트랜지스터(700)의 게이트 전극에는 소정의 전하가 부여된다(쓰기). 여기에서는 서로 다른 2개의 전위를 부여하는 전하(이하, 저전위를 부여하는 전하를 전하 QL라고 하고, 고전위를 부여하는 전하는 전하 QH라 한다) 중 어느 하나가 부여되는 것으로 한다. 또한, 서로 다른 3개 또는 그 이상의 전위를 부여하는 전하를 적용하여 기억용량을 향상시켜도 좋다. 그 후, 제 4 배선의 전위를 트랜지스터(710)가 오프 상태가 되는 전위로 하여 트랜지스터(710)를 오프 상태로 함으로써, 트랜지스터(700)의 게이트 전극에 부여된 전하가 홀딩된다(홀딩).

트랜지스터(710)의 오프 전류는 매우 작기 때문에, 트랜지스터(700)의 게이트 전극의 전하는 장시간에 걸쳐 홀딩된다.

이어, 정보의 읽기에 대해 설명한다. 제 1 배선에 소정의 전위(정전위)를 부여한 상태에서, 제 5 배선에 적절한 전위(읽기 전위)를 부여하면, 트랜지스터(700)의 게이트 전극에 홀딩된 전하량에 따라, 제 2 배선은 다른 전위를 취한다. 일반적으로, 트랜지스터(700)를 n채널형으로 하면, 트랜지스터(700)의 게이트 전극에 QH가 부여되어 있는 경우의 겉보기 문턱값(Vth_H)은 트랜지스터(700)의 게이트 전극에 QL가 부여되어 있는 경우의 겉보기 문턱값(Vth_L)보다 낮아지기 때문이다. 여기서, 겉보기 문턱 전압이란 트랜지스터(700)를 온 상태로 하기 위해 필요한 제 5 배선의 전위를 말하는 것으로 한다. 따라서, 제 5 배선의 전위를 Vth_H와 Vth_L의 중간 전위(V0)로 함으로써, 트랜지스터(700)의 게이트 전극에 부여된 전하를 판별할 수 있다. 예를 들면, 쓰기에 있어서, QH가 부여되어 있던 경우에는 제 5 배선의 전위가 V0(>Vth_H)가 되면, 트랜지스터(700)는 온 상태가 된다. QL이 부여되어 있던 경우에는 제 5 배선의 전위가 V0(<Vth_L)가 되더라도, 트랜지스터(700)는 오프 상태인 채이다. 이 때문에, 제 2 배선의 전위를 봄으로써, 홀딩되어 있는 정보를 읽어낼 수 있다.

또한, 메모리 셀을 어레이 형태로 배치하여 사용할 경우에는 원하는 메모리 셀의 정보만을 읽어낼 수 있는 것이 필요로 된다. 이와 같이, 소정의 메모리셀 정보를 읽어내고 그 이외의 메모리 셀의 정보를 읽어내지 않도록 하기 위해서는, 각 메모리 셀 사이에서 트랜지스터(700)가 각각 병렬로 접속되어 있는 경우에는, 읽기의 대상이 아닌 메모리 셀의 제 5 배선에 대해, 게이트 전극의 상태에 상관없이 트랜지스터(700)가 온 상태가 되는 전위, 즉 Vth_H보다 작은 전위를 부여하면 된다. 또한, 각 메모리 셀 사이에서 트랜지스터(700)가 각각 직렬로 접속되어 있는 경우에는, 읽기의 대상이 아닌 메모리 셀의 제 5 배선에 대해, 게이트 전극의 상태에 상관없이 트랜지스터(700)가 온 상태가 되는 전위, 즉 Vth_L보다 큰 전위를 제 5 배선에 부여하면 된다.

이어, 정보의 고쳐쓰기(rewriting)에 대해 설명한다. 정보의 고쳐쓰기는 상기 정보의 쓰기 및 홀딩과 마찬가지로 이루어진다. 즉, 제 4 배선의 전위를 트랜지스터(710)가 온 상태가 되는 전위로 하여, 트랜지스터(710)를 온 상태로 한다. 이로써, 제 3 배선의 전위(새로운 정보에 따른 전위)가 트랜지스터(700)의 게이트 전극 및 용량소자(720)에 주어진다. 그 후, 제 4 배선의 전위를 트랜지스터(710)가 오프 상태가 되는 전위로 하여 트랜지스터(710)를 오프 상태로 함으로써, 트랜지스터(700)의 게이트 전극은 새로운 정보에 따른 전하가 주어진 상태가 된다.

이와 같이, 개시하는 발명에 따른 반도체 장치는 다시 한번의 정보 쓰기에 의해 직접적으로 고쳐쓰는 것이 가능하다. 이 때문에, 플래시 메모리 등에서 필요로 되는 고전압을 사용한 플로팅 게이트로부터의 전하 추출이 불필요하며, 소거동작에 기인하는 동작속도의 저하는 억제할 수 있다. 즉, 반도체 장치의 고속동작이 실현된다.

또한, 트랜지스터(710)의 소스 전극 또는 드레인 전극은 트랜지스터(700)의 게이트 전극과 전기적으로 접속됨으로써, 비휘발성 메모리 소자로서 사용되는 플로팅 게이트형 트랜지스터의 플로팅 게이트와 동등한 작용을 나타낸다. 이 때문에, 도면 중, 트랜지스터(710)의 소스 전극 또는 드레인 전극과 트랜지스터(700)의 게이트 전극이 전기적으로 접속되는 부위를 플로팅 게이트부(FG)라 부르는 경우가 있다. 트랜지스터(710)가 오프인 경우, 해당 플로팅 게이트부(FG)는 절연체 중에 매설되었다고 볼 수 있으며, 플로팅 게이트부(FG)에는 전하가 홀딩된다. 산화물 반도체를 사용한 트랜지스터(710)의 오프 전류는 실리콘 반도체 등으로 형성되는 트랜지스터의 10만분의 1이하이기 때문에, 트랜지스터(710)의 누설로 인한, 플로팅 게이트부(FG)에 축적되는 전하의 소실을 무시하는 것이 가능하다. 즉, 산화물 반도체를 사용한 트랜지스터(710)에 의해, 전력 공급이 없어도 정보의 홀딩이 가능한 비휘발성 기억장치를 실현하는 것이 가능하다.

예를 들면, 트랜지스터(710)의 실온에서의 오프 전류가 10zA(1zA(zeptoampere)는 1×10-21A) 이하이며, 용량소자(720)의 용량값이 10fF 정도인 경우에는 적어도 104초 이상의 데이터 홀딩이 가능하다. 또한, 해당 홀딩시간이 트랜지스터 특성이나 용량값에 따라 변동하는 것은 말할 것까지도 없다.

또한, 이 경우, 종래의 플로팅 게이트형 트랜지스터에서 지적되고 있는 게이트 절연막(터널 절연막)의 열화(deterioration)라는 문제가 존재하지 않는다. 즉, 종래 문제가 되었던, 전자를 플로팅 게이트에 주입할 때의 게이트 절연막의 열화라는 문제를 해소할 수 있다. 이는 원리적인 쓰기 회수의 제한이 존재하지 않는 것을 의미하는 것이다. 또한, 종래의 플로팅 게이트형 트랜지스터에서 쓰기나 소거 시에 필요하였던 고전압도 불필요하다.

도 17(A-1)에 나타낸 반도체 장치는 해당 반도체 장치를 구성하는 트랜지스터 등의 요소가 저항 및 용량을 포함하는 것으로서, 도 17(A-2)와 같이 생각하는 것이 가능하다. 즉, 도 17(A-2)에서는 트랜지스터(700) 및 용량소자(720)가 각각 저항 및 용량을 포함하여 구성된다고 간주하고 있는 셈이 된다. R1 및 C1은 각각 용량소자(720)의 저항값 및 용량값이며, 저항값(R1)은 용량소자(720)를 구성하는 절연층에 따른 저항값에 상당한다. 또한, R2 및 C2는 각각 트랜지스터(700)의 저항값 및 용량값이며, 저항값(R2)은 트랜지스터(700)가 온 상태일 때의 게이트 절연층에 따른 저항값에 상당하고, 용량값(C2)은 소위 게이트 용량(게이트 전극과 소스 전극 또는 드레인 전극과의 사이에 형성되는 용량, 및 게이트 전극과 채널형성영역과의 사이에 형성되는 용량)의 용량값에 상당한다.

트랜지스터(710)가 오프 상태에 있는 경우의 소스 전극과 드레인 전극 사이의 저항값(실효 저항이라고도 부른다)을 ROS라고 하면, 트랜지스터(710)의 게이트 누설이 충분히 작은 조건에서, R1 및 R2가 R1≥ROS, R2≥ROS를 만족할 경우에는 전하의 홀딩기간(정보의 홀딩기간이라고 할 수도 있다)은 주로 트랜지스터(710)의 오프 전류에 의해 결정되게 된다.

역으로, 해당 조건을 만족하지 않을 경우에는 트랜지스터(710)의 오프 전류가 충분히 작아도, 홀딩기간을 충분히 확보하는 것이 곤란하게 된다. 트랜지스터(710)의 오프 전류 이외의 누설 전류(예를 들면, 소스 전극과 게이트 전극 사이에서 발생하는 누설 전류 등)가 크기 때문이다. 이에, 본 실시형태에서 개시하는 반도체 장치는 상술한 관계를 만족하는 것인 것이 바람직하다고 할 수 있다.

한편, C1과 C2는 C1≥C2의 관계를 만족하는 것이 바람직하다. C1을 크게 함으로써, 제 5 배선에 의해 플로팅 게이트부(FG)의 전위를 제어할 때에, 제 5 배선의 전위를 효율적으로 플로팅 게이트부(FG)에 부여할 수 있게 되며, 제 5 배선에 부여하는 전위간(예를 들면, 읽기(reading) 전위와, 비읽기(non-reading) 전위)의 전위차를 낮게 억제할 수 있기 때문이다.

상술한 관계를 만족함으로써, 보다 바람직한 반도체 장치를 실현하는 것이 가능하다. 또한, R1 및 R2는 트랜지스터(700)의 게이트 절연층이나 용량소자(720)의 절연층에 의해 제어된다. C1 및 C2에 대해서도 마찬가지이다. 따라서, 게이트 절연층의 재료나 두께 등을 적절히 설정하여, 상술한 관계를 만족하도록 하는 것이 바람직하다.

본 실시형태에서 나타내는 반도체 장치에서는 플로팅 게이트부(FG)가 플래시 메모리 등의 플로팅 게이트형 트랜지스터의 플로팅 게이트와 동시 작용을 하는데, 본 실시형태의 플로팅 게이트부(FG)는 플래시 메모리 등의 플로팅 게이트와 본질적으로 다른 특징을 갖는다. 플래시 메모리에서는 콘트롤 게이트에 인가되는 전압이 높기 때문에, 그 전위의 영향이 인접하는 셀의 플로팅 게이트에 미치는 것을 방지하기 위해, 셀과 셀의 간격을 어느 정도 유지할 필요가 생긴다. 이는 반도체 장치의 고집적화를 저해하는 요인 중 하나이다. 그리고, 해당 요인은 고전계를 걸어 터널 전류를 발생시킨다는 플래시 메모리의 근본적인 원리에 기인하는 것이다.

또한, 플래시 메모리의 상기 원리에 따라, 절연층의 열화가 진행되고, 고쳐쓰기 회수의 한계(104~105회 정도)라는 또 다른 문제도 발생한다.