まず、第1の実施の形態について説明する。

図1は第1の実施の形態に係る電子装置の一例を示す図である。尚、図1(A)には、第1の実施の形態に係る電子装置の一例の要部断面を模式的に図示している。図1(B)には、第1の実施の形態に係る電子装置の一例の、接合部の電子部品平面方向に沿った断面を模式的に図示している。図1(B)の接合部断面は、一例として、図1(A)のL1−L1線に沿った位置に相当する接合部断面を模式的に図示したものである。図1(A)の電子装置の接合部断面は、一例として、図1(B)のL2−L2線に沿った位置に相当する接合部断面を模式的に図示したものである。

図1(A)に示す電子装置1は、電子部品10及び電子部品20、並びに、電子部品10と電子部品20の間を接合する接合部30を有している。

電子部品10は、その表面10aに設けられた端子11を有している。ここでは一例として、1つの端子11を図示している。端子11には、各種導体材料を用いることができる。例えば、端子11には、その一部又は全部に銅(Cu)を用いることができる。

電子部品20は、電子部品10に対向して配置されている。電子部品20は、電子部品10の表面10aと対向する表面20aに設けられた端子21を有している。ここでは一例として、1つの端子21を図示している。電子部品20の端子21は、電子部品10の端子11に対応する位置に設けられている。端子21には、各種導体材料を用いることができる。例えば、端子21には、その一部又は全部にCuを用いることができる。

接合部30は、電子部品10の端子11と、電子部品20の端子21との間に設けられ、それらの端子11と端子21とを接合する。

電子部品10及び電子部品20にはそれぞれ、例えば、半導体素子(半導体チップ)、半導体素子を備える半導体パッケージ、又は回路基板を用いることができる。尚、電子部品10及び電子部品20の構成の詳細については後述する。

電子部品10と電子部品20の間を接合する接合部30には、半田を用いることができる。半田には、スズ(Sn)を含む半田を用いることができる。半田には、例えば、鉛(Pb)を含まないPbフリー半田が用いられる。例えば、接合部30には、Snと銀(Ag)とCuを含むSn−Ag−Cu系半田を用いることができる。Sn−Ag−Cu系半田として、例えば、Agを3.0wt%、Cuを0.5wt%含むSn−Ag−Cu系半田が用いられる。

接合部30は、図1(A)及び図1(B)に示すように、端子11から端子21、或いは、端子21から端子11に向かう方向に延びる、板状の化合物31を含有している。

ここで、図1(B)に示す接合部30の断面は、電子部品10と電子部品20の間の接合部30を、図1(A)のL1−L1線の位置で切断した時の断面の一例である。接合部30内の板状の化合物31は、図1(B)に示すように、端子11から端子21、或いは、端子21から端子11に向かう方向(図1(B)の紙面奥行き方向、或いは、紙面手前方向)と交差する方向を法線方向とする一対の主面31aを有する。図1(B)には、接合部30内に、主面31aが異なる方向を向いた複数の板状の化合物31が含まれる形態を例示している。図1(A)に示す接合部30の断面は、電子部品10と電子部品20の間の接合部30を、図1(B)のL2−L2線の位置で切断した時の断面の一例である。図1(A)の接合部30の断面内には、接合部30内に含まれる複数の板状の化合物31のうち、図1(B)のL2−L2線の位置で切断された3つの板状の化合物31(それらの切断面)を例示している。

例えば、接合部30に上記のようなSn−Ag−Cu系半田が用いられる場合、接合部30には、板状のCu6Sn5の化合物31(金属間化合物(InterMetallic Compound;IMC))が含有される。

このような板状の化合物31は、電子部品10と電子部品20を、接合部30となる材料(接合材)を用いて接合する過程で、形成することができる。

図2は第1の実施の形態に係る電子部品接合工程の一例を示す図である。尚、図2には、第1の実施の形態に係る電子部品接合工程の一例の要部断面を模式的に図示している。図2(A)は接合前の状態の一例を示す図、図2(B)は接合時の状態の一例を示す図、図2(C)は接合後の状態の一例を示す図である。

まず図2(A)に示すような、接合する電子部品10及び電子部品20が準備される。準備される電子部品10と電子部品20のうち、一方の端子上、この例では電子部品20の端子21上に、予め接合材30aが設けられる。接合材30aは、上記のような接合部30を形成するための材料である。接合材30aには、例えば、半田が用いられる。ここでは、接合材30aにSn−Ag−Cu系半田を用いる場合を例にして説明する。

図2(A)に示すような、電子部品20の端子21上の接合材30aは、例えば、端子21上に半田ボールを搭載したり半田をメッキにより堆積したりすることで配設された半田を、加熱により溶融し、冷却により凝固することで、形成される。ここでは一例として、略ボール状に成形された接合材30aを図示するが、接合材30aは、この形状に限定されるものではなく、種々の形状を採り得る。

上記のような電子部品10、及び接合材30aが設けられた電子部品20が準備された後、これらの電子部品10と電子部品20が、図2(A)に示すように、互いの端子11と端子21(又はその上の接合材30a)の位置合わせが行われて、対向配置される。

そして、図2(B)に示すように、電子部品20の端子21上の接合材30aが、加熱により溶融され、電子部品10の端子11に接続される。接合材30aと端子11の接続後、接合材30aは、冷却により凝固される。ここで、接合材30aの加熱は、窒素(N2)等の不活性ガス雰囲気とされた炉内で行われる。接合材30aの冷却は、不活性ガス雰囲気とされた炉内で行われ、例えば炉内をパージしたり炉内で自然放冷したりすることで行われる。

このような接合材30aの加熱後の冷却過程において、例えば少なくとも接合材30aの凝固開始から凝固終了までの間、電子部品10と電子部品20は、一方が他方よりも高温の状態になるように調節される。例えば、電子部品20が電子部品10よりも高温の状態になるように調節される。或いは、電子部品10が電子部品20よりも高温の状態になるように調節される。

例えば、電子部品10と電子部品20のうちの一方側に、所定の熱容量を有する部材を設け、その部材を設けた一方側の電子部品の冷却速度を低下させる。このようにすることで、例えば接合材30aの凝固開始から凝固終了までの間、一方側の電子部品を他方側の電子部品よりも高温の状態にする。

或いは、一方側の電子部品の冷却速度を低下させるように、その一方側の電子部品を選択的に温める。或いはまた、他方側の電子部品を選択的に冷却し、その他方側の電子部品の冷却速度を増大させる。このようにすることで、例えば接合材30aの凝固開始から凝固終了までの間、一方側の電子部品を他方側の電子部品よりも高温の状態にする。

このように、接合材30aの加熱後の冷却過程において、例えば接合材30aの凝固開始から凝固終了までの間、一方側の電子部品を他方側の電子部品よりも高温の状態にすることで、凝固時の接合材30aには温度勾配ができる。即ち、接合材30aの、高温の状態になるようにした一方の電子部品側が、他方の電子部品側よりも高温になるような温度勾配ができる。このような温度勾配ができることで、接合材30aは概ね、より低温の他方の電子部品側から、より高温の一方の電子部品側に向かって、凝固が進行していくようになる。

このように凝固が進行していくことで、Sn−Ag−Cu系半田の接合材30aには、図2(C)に示すように、その凝固の進行方向に延びるように、板状のCu6Sn5の化合物31が析出する。即ち、電子部品10の端子11から電子部品20の端子21に向かう方向に延びるように、或いは、電子部品20の端子21から電子部品10の端子11に向かう方向に延びるように、板状のCu6Sn5の化合物31が析出する。ここでは複数の板状の化合物31を例示している。板状のCu6Sn5の化合物31は、Sn、Ag及びCuを含有する部分32で覆われる。凝固の進行により、そのような部分32の内部に板状のCu6Sn5の化合物31を含有する接合部30が形成され、図2(C)に示すような、接合部30で電子部品10と電子部品20が接合された電子装置1が得られる。

接合部30に、上記のように端子11から端子21に向かう方向、或いは、端子21から端子11に向かう方向に延びる板状の化合物31が形成されることで、それが補強材の役割を果たし、接合部30の、外力や熱に起因した応力に対する強度の向上が図られる。例えば、接合部30の、端子11と端子21の対向方向と交差する方向の応力に対する強度の向上が図られる。

半導体素子の高密度実装、端子の狭ピッチ化に伴い、半導体素子や半導体パッケージが大型化したり、半導体素子や半導体パッケージと回路基板との間の半田の接合部が微細化したりすると、接合部に加わる外力や応力が大きくなる場合がある。接合部に上記のようなSn−Ag−Cu系半田を用いる場合で、上記図2で述べたような接合方法を用いない場合には、接合部内に、粗大なCu6Sn5の化合物が形成されたり、板状のCu6Sn5の化合物が端子面方向に延びて形成されたりすることがある。このような化合物に外力や熱に起因した応力が集中することで、その化合物の部位を起点とした接合部のクラックや剥離、せん断応力によるせん断剥離が発生し易い。

上記のように、電子部品10と電子部品20の間の接合部30に、端子11から端子21、或いは、端子21から端子11に向かう方向に延びるような板状の化合物31を設けることで、接合部30が、外力や熱に起因した応力に対し、より強い構造となる。このような接合部30の強度の向上により、外力や応力に起因した接合部30のクラックや剥離の発生、そのようなクラックや剥離による断線を、効果的に抑制することが可能になる。

ここでは接合材30aを、予め電子部品20の端子21上に設けるようにしたが、予め電子部品10の端子11上に設け、上記図2に例示した手順に従って接合を行っても、接合部30内に、上記のような板状の化合物31を析出させることが可能である。

尚、上記のような板状の化合物31は、必ずしも電子部品10の端子11から電子部品20の端子21に達するように形成されることを要しない。板状の化合物31が端子11から端子21に達するような長さでない場合でも、接合部30内に上記のような板状の化合物31が存在することで、上記のような接合部30の強度の向上、接合部30の強度の向上によるクラックや剥離を抑制することが可能である。例えば、上記の板状の化合物31は、端子11−端子21間距離の半分以上の長さで形成され得る。それにより、一定の強度向上効果を得ることが可能である。

電子部品10の端子11と電子部品20の端子21の間には、例えば、複数の板状の化合物31が、端子11から端子21、或いは、端子21から端子11に向かう方向に配向するように延在されて形成される。この場合、複数の板状の化合物31は、必ずしも互いに平行に延在されることを要しない。また、複数の板状の化合物31は、必ずしも互いに同じ長さで延在されることを要しない。更にまた、複数の板状の化合物31は、必ずしも互いに端子11面又は端子21面から同じ高さの位置を起点に延在されることを要しない。

また、板状の化合物31は、必ずしも接合部30内に複数含有されていることを要しない。接合部30内に少なくとも1つの板状の化合物31が存在することで、上記のような接合部30の強度の向上、接合部30の強度の向上によるクラックや剥離を抑制することが可能である。

ここでは板状の化合物31としてCu6Sn5を例示したが、板状の化合物31には、Cu及びSnを含む他の結晶相(Cu3Sn等)が含有されてもよい。そのような場合でも、板状の化合物31が含有されることによる上記のような接合部30の強度の向上、接合部30の強度の向上によるクラックや剥離を抑制することが可能である。

また、接合部30内には、上記のような板状の化合物31のほか、柱状の化合物が含有されてもよい。

図3は第1の実施の形態に係る電子装置の別例を示す図である。尚、図3(A)には、第1の実施の形態に係る電子装置の別例の要部断面を模式的に図示している。図3(B)には、第1の実施の形態に係る電子装置の別例の、接合部の電子部品平面方向に沿った断面を模式的に図示している。図3(B)の接合部断面は、一例として、図3(A)のL3−L3線に沿った位置に相当する接合部断面を模式的に図示したものである。図3(A)の電子装置の接合部断面は、一例として、図3(B)のL4−L4線に沿った位置に相当する接合部断面を模式的に図示したものである。

上記のように温度勾配を持たせてSn−Ag−Cu系半田の接合材30aを凝固させていくと、図3(A)及び図3(B)に示すように、Cu6Sn5のような板状の化合物31が析出される。更に、図3(A)及び図3(B)に示すように、端子11から端子21、或いは、端子21から端子11に向かう方向に延びる、Ag3Sn等の柱状の化合物33も析出され得る。

ここで、図3(B)に示す接合部30の断面は、電子部品10と電子部品20の接合部30を、図3(A)のL3−L3線の位置で切断した時の断面の一例である。図3(B)には、接合部30内に、主面31aが異なる方向を向いた複数の板状の化合物31、及び、複数の柱状の化合物33が含まれる形態を例示している。図3(A)に示す接合部30の断面は、電子部品10と電子部品20の接合部30を、図3(B)のL4−L4線の位置で切断した時の断面の一例である。図3(A)の接合部30の断面内には、接合部30内に含まれる複数の板状の化合物31及び柱状の化合物33のうち、図3(B)のL4−L4線の位置で切断された3つの板状の化合物31(それらの切断面)及び4つの柱状の化合物33(それらの切断面)を例示している。

このように接合部30内には、板状の化合物31のほか、柱状の化合物33が含有されていてもよい。接合部30内の板状の化合物31及び柱状の化合物33により、接合部30が、外力や熱に起因した応力に対して強い構造となり、接合部30のクラックや剥離の発生、そのようなクラックや剥離による断線を抑制することができる。

ところで、接合部30内に板状の化合物31として形成されるCu6Sn5のCuは、例えば、接合材30aに用いるSn−Ag−Cu系半田に含まれるCuである。このほか、形成されるCu6Sn5のCuは、接合材30a外から接合材30a内に拡散するCuであってもよい。電子部品10と電子部品20を接合する際の接合材30aの溶融時には、接合材30a内に、端子11や端子21の側からCuが拡散し得る(図2(B))。その場合、接合材30aが冷却、凝固される際には、Sn−Ag−Cu系半田に含まれるCuのほか、このように端子11や端子21の側から拡散してくるCuが用いられて、Cu6Sn5が形成され得る(図2(C))。

接合材30aに用いるSn−Ag−Cu系半田のCu含有量が少量の場合でも、溶融時に端子11や端子21の側から接合材30a内にCuが供給されることで、接合部30内に、応力に対して一定の強度向上効果を示す大きさや数のCu6Sn5が形成可能になる。このように端子11や端子21の側から接合材30a内にCuを供給するためには、端子11や端子21にCuを用いるほか、例えば次の図4に示すような構造を採用することもできる。

図4は第1の実施の形態に係る端子構造の例を示す図である。尚、図4(A)〜図4(F)にはそれぞれ、第1の実施の形態に係る電子部品の要部断面を模式的に図示している。

図4(A)には、電子部品10の端子11を例示している。図4(A)の端子11は、電子部品10の表面10aに設けられた電極層11aを備えている。電極層11aには、Cu等、各種導体材料を用いることができる。電極層11a上には、接合材30bが設けられている。接合材30bには、半田ペースト30baにCu粉30bbを混合したものを用いる。半田ペースト30baには、各種半田材料、例えば、Snを含む半田材料を用いることができる。Cu粉30bbには、例えば、粒径3μm〜5μmのCu粒子の粉末を用いることができる。端子11は、図4(B)に示すように、電極層11aと接合材30bの間に介在する、ニッケル(Ni)及び金(Au)を含む電極層11bを含んでもよい。端子11側に図4(A)又は図4(B)のような構造を用いると(図2(A))、接合材30b内のCu粉30bbがCuの供給源となり、溶融時の接合材30a内にCuが供給されて(図2(B))、接合部30内に板状のCu6Sn5が化合物31として形成される(図2(C))。

図4(A)及び図4(B)には、半田ペースト30baにCu粉30bbを混合した接合材30bを例示したが、例えば図4(C)に示すように、半田ペースト30ba上にCu粉30bbを付着させることで、接合材30bを形成してもよい。尚、図4(C)には、図4(B)と同様に、電極層11aと接合材30bの間にNi及びAuを含む電極層11bを介在させた構造を例示している。

従来の電子部品10と電子部品20の接合では、端子11及び端子21のうち、例えば一方の端子21上に予め接合材30bを設け、もう一方の端子11上に予め予備半田として半田ペースト(Cu粉30bbを含まない半田ペースト30ba)を設ける場合がある。図4(A)及び図4(B)の手法では、そのような予備半田として用いられる半田ペースト30baに予めCu粉30bbを混合しておき、これを接合材30bとして端子11の上方に設ければよい。また、図4(C)の手法では、端子11の上方に予備半田として半田ペースト30baを設け、その半田ペースト30baの上に、Cu粉30bbを付着させればよい。そのため、図4(A)〜図4(C)の手法では、電極層11aや電極層11bの形成条件を、半田ペースト30baのみを予備半田として設ける場合から変更することなく、或いは大きく変更することなく、Cuの供給源を含む構造を得ることができる。

図4(D)及び図4(E)には、電子部品10の端子11を例示している。図4(D)には、Cuを用い、平面サイズを増大させた端子11を例示し、図4(E)には、Cuを用い、厚みを増大させた端子11を例示している。このように平面サイズや厚みを増大させた端子11をCuの供給源とし、溶融時の接合材30a内にCuを拡散させて供給し、接合部30内に板状のCu6Sn5が形成されるようにしてもよい。

図4(D)のような構造は、端子11の形成領域を変更することで得られ、図4(E)のような構造は、形成する端子11の厚みを変更することで得られる。これらの変更は、端子11を形成する際のマスクの開口サイズを変更したり、マスクの厚み及び端子材料の堆積時間を変更したりする等、製造工程を大幅に複雑化することなく、比較的容易に行うことができる。

尚、ここでは図示を省略するが、図4(D)及び図4(E)の端子11上には、上記のような半田ペースト30baや、Cu粉30bbを混合した半田ペースト30baを設けることもできる。

以上の図4(A)〜図4(E)には、電子部品10の端子11側の構造を例示したが、図4(A)〜図4(E)のような構造を、電子部品20の端子21側に採用することもできる。

また、図4(F)には、電子部品20の端子21を例示している。端子21上には接合材30aが設けられ、接合材30aの表面にはCu粉30cが付着されている。このように端子21上に、Cu粉30cを付着させた接合材30aを設けた電子部品20を、電子部品10と対向させて配置し(図2(A))、加熱しながら、Cu粉30cを付着させた接合材30aを電子部品10の端子11に接続する(図2(B))。その後、冷却、凝固を行う(図2(C))。接合材30aに付着させたCu粉30cがCuの供給源となり、溶融時の接合材30a内にCuが供給されて、接合部30内に板状のCu6Sn5が化合物31として形成される。

図4(F)の手法では、端子21上に接合材30aを設け、その上にCu粉30cを付着させればよい。そのため、端子21の形成条件を、Cu粉30cを付着させない場合から変更することなく、或いは大きく変更することなく、Cuの供給源を含む構造を得ることができる。

電子部品10の端子11、電子部品20の端子21に、図4(A)〜図4(F)のような構造を採用し、接合材30a内のCu量を確保し、接合部30内に、応力に対して一定の強度向上効果を示す大きさや数の板状のCu6Sn5を形成するようにしてもよい。

尚、上記図2(B)の工程における接合材30a内のCu量を確保するためには、Sn−Ag−Cu系半田のCu含有量を増大させてもよい。但し、接合材30aのSn−Ag−Cu系半田のCu含有量を増大させることで、接合材30aの融点が、少量の場合に比べて上昇する可能性がある点に留意する。

ここでは接合材30aに、Sn−Ag−Cu系半田を用いる場合を例示したが、接合材30aに用いる半田は、これに限定されるものではない。接合材30aには、SnとCuを含むSn−Cu系半田、SnとAgを含むSn−Ag系半田、SnとAuを含むSn−Au系半田、SnとNiを含むSn−Ni系半田、Snとパラジウム(Pd)を含むSn−Pd系半田等を用いることもできる。尚、接合材30aにCuを含まないものを用いても、上記のように端子11や端子21の側からCuを供給できる構造を採用することで、板状のCu6Sn5を化合物31として含有する接合部30を形成することが可能である。接合材30aにこのような各種半田材料を用いた場合にも、上記図2或いは更に図4で述べたような手法を用いることで、板状の化合物31を含有する接合部30が形成可能であり、板状の化合物31によって得られる上記同様の効果を得ることが可能である。尚、いずれの系の半田も、2元系半田に限定されるものではない。

また、上記図3のように、接合部30内に、板状のCu6Sn5の化合物31に加え、柱状のAg3Snの化合物33を形成するため、Agの供給源として、上記図4のCu粉30bb,30cと共に、又はCu粉30bb,30cに替えて、Ag粉を用いてもよい。

前述のように、例えば電子部品10及び電子部品20にはそれぞれ、半導体素子、半導体素子を備える半導体パッケージ、又は回路基板を用いることができる。半導体素子、半導体パッケージ、回路基板の構成例について、以下の図5〜図9を参照して説明する。

図5は半導体素子の構成例を示す図である。尚、図5には、半導体素子の一例の要部断面を模式的に図示している。

図5に示す半導体素子100は、トランジスタ等の素子が設けられた半導体基板110と、半導体基板110上に設けられた配線層120とを有する。

半導体基板110には、シリコン(Si)、ゲルマニウム(Ge)、シリコンゲルマニウム(SiGe)等の基板のほか、ガリウムヒ素(GaAs)、インジウムリン(InP)等の基板が用いられる。このような半導体基板110に、トランジスタ、容量、抵抗等の素子が設けられる。図5には素子の一例として、MOS(Metal Oxide Semiconductor)トランジスタ130を図示している。

MOSトランジスタ130は、半導体基板110に設けられた素子分離領域110aにより画定された素子領域に設けられる。MOSトランジスタ130は、半導体基板110上にゲート絶縁膜131を介して形成されたゲート電極132と、ゲート電極132の両側の半導体基板110内に形成されたソース領域133及びドレイン領域134とを有する。ゲート電極132の側壁には、絶縁膜のスペーサ135(サイドウォール)が設けられる。

このようなMOSトランジスタ130等が設けられた半導体基板110上に、配線層120が設けられる。配線層120は、半導体基板110に設けられたMOSトランジスタ130等に電気的に接続された導体部121(配線及びビア)と、導体部121を覆う絶縁部122とを有する。図5には一例として、MOSトランジスタ130のソース領域133及びドレイン領域134に電気的に接続された導体部121を図示している。導体部121には、Cu、アルミニウム(Al)等の各種導体材料が用いられる。絶縁部122には、酸化シリコン等の無機絶縁材料や、樹脂等の有機絶縁材料が用いられる。

配線層120の最表面の導体部121は、外部接続用の端子121aとなる部位を含む。端子121a上には、他の電子部品との接合時に、或いは接合前に予め、上記の接合材30a(図2)に相当する半田等のバンプが接続される。

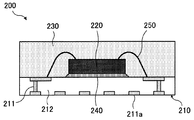

図6〜図8はそれぞれ半導体パッケージの構成例を示す図である。尚、図6〜図8にはそれぞれ、半導体パッケージの一例の要部断面を模式的に図示している。

まず、図6に示す半導体パッケージ200について述べる。

図6に示す半導体パッケージ200は、パッケージ基板210(回路基板)と、パッケージ基板210上に搭載された半導体素子220と、半導体素子220を封止する封止層230とを有する。

パッケージ基板210には、例えば、プリント基板が用いられる。パッケージ基板210は、導体部211(配線及びビア)と、導体部211を覆う絶縁部212とを有する。導体部211には、Cu、Al等の各種導体材料が用いられる。絶縁部212には、フェノール樹脂、エポキシ樹脂、ポリイミド樹脂等の樹脂材料、そのような樹脂材料をガラス繊維や炭素繊維に含浸した複合樹脂材料等が用いられる。

このようなパッケージ基板210上に、半導体素子220が、樹脂や導電性ペースト等のダイアタッチ材240で接着、固定され、ワイヤ250でパッケージ基板210に電気的に接続(ワイヤボンディング)される。パッケージ基板210上の半導体素子220及びワイヤ250は、封止層230で封止される。封止層230には、エポキシ樹脂等の樹脂材料、そのような樹脂材料に絶縁性フィラーを含有させた材料等が用いられる。

パッケージ基板210の、半導体素子220の搭載面と反対側の表面の導体部211は、外部接続用の端子211aとなる部位を含む。端子211a上には、他の電子部品との接合時に、或いは接合前に予め、上記の接合材30a(図2)に相当する半田等のバンプが接続される。

尚、ここでは半導体素子220をパッケージ基板210にワイヤボンディングする場合を例示したが、半導体素子220は、パッケージ基板210にフリップチップボンディングされてもよい。

また、パッケージ基板210上には、複数の半導体素子220が搭載されてもよく、また、半導体素子220のほか、チップコンデンサ等の他の電子部品が搭載されてもよい。

続いて、図7に示す半導体パッケージ300について述べる。

図7に示す半導体パッケージ300は、パッケージ基板310(回路基板)と、パッケージ基板310上に搭載された半導体素子320と、半導体素子320を覆う被覆材330とを有する。

パッケージ基板310には、例えば、プリント基板が用いられる。パッケージ基板310は、Cu、Al等の導体部311(配線及びビア)と、導体部311を覆う樹脂材料等の絶縁部312とを有する。

このようなパッケージ基板310に、半導体素子320が、それに設けられた半田等のバンプ340で電気的に接続(フリップチップボンディング)される。パッケージ基板310と半導体素子320の間には、アンダーフィル材341が充填される。パッケージ基板310上の半導体素子320は、被覆材330で覆われる。被覆材330には、Cu等の熱伝導性の部材が用いられる。被覆材330は、熱界面材料(Thermal Interface Material;TIM)350を用いて半導体素子320上に接着され、半導体素子320と熱的に接続される。被覆材330は、例えば、その端部が接着材351を用いてパッケージ基板310に接着される。

パッケージ基板310の、半導体素子320の搭載面と反対側の表面の導体部311は、外部接続用の端子311aとなる部位を含む。端子311a上には、他の電子部品との接合時に、或いは接合前に予め、上記の接合材30a(図2)に相当する半田等のバンプが接続される。

尚、パッケージ基板310上には、複数の半導体素子320が搭載されてもよく、また、半導体素子320のほか、チップコンデンサ等の他の電子部品が搭載されてもよい。

続いて、図8に示す半導体パッケージ400について述べる。

図8に示す半導体パッケージ400は、樹脂層410と、樹脂層410に埋設された複数(ここでは一例として2つ)の半導体素子420と、樹脂層410上に設けられた配線層430(再配線層)とを有する。

半導体素子420は、その端子420aの配設面が露出するように樹脂層410に埋設される。配線層430は、Cu、Al等の導体部431(再配線及びビア)と、導体部431を覆う樹脂材料等の絶縁部432とを有する。

配線層430の最表面の導体部431は、外部接続用の端子431aとなる部位を含む。導体部431により、半導体素子420の端子420aの位置が、外部接続用の端子431aの位置に再配置される。端子431a上には、他の電子部品との接合時に、或いは接合前に予め、上記の接合材30a(図2)に相当する半田等のバンプが接続される。

尚、樹脂層410には、1つ又は3つ以上の半導体素子420が埋設されてもよく、また、半導体素子420のほか、チップコンデンサ等の他の電子部品が埋設されてもよい。

図9は回路基板の構成例を示す図である。尚、図9(A)及び図9(B)にはそれぞれ、回路基板の一例の要部断面を模式的に図示している。

図9(A)には、回路基板500として、複数の配線層を含む多層プリント基板を例示している。回路基板500は、上記図6に示したパッケージ基板210及び上記図7に示したパッケージ基板310と同様、Cu、Al等の導体部511(配線及びビア)と、導体部511を覆う樹脂材料等の絶縁部512とを有する。

回路基板500の最表面の導体部511は、外部接続用の端子511aとなる部位を含む。端子511a上には、他の電子部品との接合時に、或いは接合前に予め、上記の接合材30a(図2)に相当する半田等のバンプが接続される。

図9(B)には、回路基板600として、ビルドアップ工法を用いて形成されるビルドアップ基板を例示している。回路基板600は、コア基板610と、コア基板610上に設けられた絶縁層620と、絶縁層620を介して設けられた導体パターン630と、異なる導体パターン630間を接続するビア640とを有する。コア基板610には、セラミックス材料や有機材料等が用いられる。絶縁層620には、プリプレグ等の絶縁材料が用いられる。導体パターン630及びビア640には、Cu等の導体材料が用いられる。

回路基板600の最表面の導体パターン630は、外部接続用の端子630aとなる部位を含む。端子630a上には、他の電子部品との接合時に、或いは接合前に予め、上記の接合材30a(図2)に相当する半田等のバンプが接続される。

例えば、図5のような半導体素子100、図6〜図8のような半導体パッケージ200,300,400、図9のような回路基板500,600を、上記図1〜図4に示した電子部品10及び電子部品20にそれぞれ用いることが可能である。

尚、接合する電子部品10と電子部品20の組合せとしては、例えば、半導体素子と回路基板の組合せ、半導体パッケージと回路基板の組合せ、半導体素子と半導体パッケージの組合せがある。このほか、接合する電子部品10と電子部品20の組合せとしては、半導体素子同士の組合せ、半導体パッケージ同士の組合せ、回路基板同士の組合せもある。

各種組合せの電子部品10と電子部品20の接合に、上記図2或いは更に図4のような手法を用いることで、接合材30aが凝固されて得られる接合部30に、端子11から端子21、或いは、端子21から端子11に向かう方向に延びる板状の化合物31を形成することができる。それにより、接合部30の強度の向上が図られ、外力や応力に起因した接合部30のクラックや剥離の発生、そのようなクラックや剥離による断線が効果的に抑制されるようになる。

次に、第2の実施の形態について説明する。

ここでは、接合する電子部品の一方を回路基板とし、他方を半導体パッケージとする場合を例にして説明する。

図10は第2の実施の形態に係る電子部品接合工程の一例を示す図である。尚、図10には、第2の実施の形態に係る電子部品接合工程の一例の要部断面を模式的に図示している。図10(A)は接合前の状態の一例を示す図、図10(B)は接合時の状態の一例を示す図、図10(C)は接合後の状態の一例を示す図である。

この例では、まず接合する電子部品として、図10(A)に示すような回路基板40と半導体パッケージ50が準備される。

回路基板40は、その表面40aに設けられた端子41を有する。端子41は、Cu等の電極層41aと、電極層41a上に設けられた、例えばNiとAuを積層したNi/Auの電極層41bとを含む。回路基板40の端子41(電極層41b)上には、接合材60bが予め設けられる。接合材60bには、例えば、上記図4(B)に例示した接合材30bと同様に、半田ペーストにCu粉を混合したものを用いる。或いは、接合材60bには、例えば、上記図4(C)に例示した接合材30bと同様に、半田ペースト上にCu粉を付着させたものを用いる。半田ペーストの半田には、Snを含む各種半田材料を用いることができる。Cu粉には、例えば、粒径3μm〜5μmのCu粒子の粉末を用いることができる。接合材60bは、例えば、このようなCu粉を混合した半田ペーストを端子41上に塗布することで、形成する。或いは、Cu粉を含まない半田ペーストを端子41上に塗布した後、その半田ペースト上にCu粉を付着させることで、接合材60bを形成する。

半導体パッケージ50は、回路基板40に対向して配置され、回路基板40の表面40aと対向する表面50aに設けられた端子51を有する。端子51は、Cu等の電極層51aと、電極層51a上に設けられた、例えばNi/Auの電極層51bとを含む。半導体パッケージ50の端子51(電極層51b)上には、例えばSn−Ag−Cu系半田の接合材60aが予め設けられる。接合材60aは、例えば、端子51上に半田ボールを搭載したり半田をメッキにより堆積したりすることで配設された半田を、加熱により溶融し、冷却により凝固することで、形成される。

半導体パッケージ50の、端子51が設けられた表面50aと反対側の表面(上面)50bには、所定の熱容量を有する部材70Aが設けられる。部材70Aには、後述のように接合材60a及び接合材60bを加熱により溶融しその後冷却して凝固する際に、この部材70Aを設けた半導体パッケージ50が回路基板40よりも高温の状態になるような熱容量を有する材料が用いられる。部材70Aは、このような所定の熱容量を有するように、材料(比熱)が選択されると共に、その平面サイズ及び厚みが設定される。部材70Aには、例えば、Cu、Al等のプレートを用いることができる。

図10では図示を省略するが、部材70Aは、樹脂や金属ペースト等の接着材を用いて半導体パッケージ50の上面50bに設けられる。尚、部材70Aの半導体パッケージ50上への配設については後述する。

接合材60bが設けられた回路基板40と、接合材60a及び部材70Aが設けられた半導体パッケージ50は、図10(A)に示すように、互いの端子41(接合材60b)と端子51(接合材60a)の位置合わせが行われて、対向配置される。

そして、図10(B)に示すように、半導体パッケージ50の端子51上の接合材60aが、加熱により溶融され、回路基板40の端子41上の、同様に溶融された接合材60bと接続される。加熱により溶融された接合材60bには、半田ペーストの溶融した半田と、その半田にCu粉のCu粒子から供給されたCuとが含まれる。溶融された接合材60bには、粒状のCuが残存し得る。このような接合材60bが、接合材60aと接続される。接合材60aと接合材60bは、溶融、接続により一体化される。このように接合材60aと接合材60bが一体化された部位(接合部位)60cには、接合材60aのSn、Ag、Cu等の成分、接合材60bのSn、Cu等の成分が含まれる。接合部位60cには、電極層41及び電極層51のCu、Ni、Au等の成分も含まれ得る。このような接合部位60cが、冷却により凝固される。

ここで、上記のように半導体パッケージ50には、所定の熱容量を有する部材70Aが設けられている。この部材70Aにより、接合材60a及び接合材60bの加熱後の冷却過程で、例えば接合材60a及び接合材60b(接合部位60c)の凝固開始から凝固終了までの間、半導体パッケージ50が回路基板40よりも高温の状態になるように調節される。

部材70Aを設けた半導体パッケージ50は、部材70Aを設けていない半導体パッケージ50に比べて大きな熱容量を有する。そのため、接合材60a及び接合材60bが加熱により溶融され、それらが一体化した接合部位60cが、凝固のために冷却される際、部材70Aを設けた半導体パッケージ50の冷却速度は、部材70Aを設けていない半導体パッケージ50に比べて低下する。即ち、半導体パッケージ50は、部材70Aが設けられることで、より冷え難くなる。例えば、部材70Aを設けた半導体パッケージ50の冷却速度は、1℃/min以下である。

接合材60a及び接合材60bが加熱により溶融され、それらが一体化した接合部位60cが、凝固のために冷却される際には、半導体パッケージ50と共に、回路基板40も冷却されていく。この時、半導体パッケージ50は、部材70Aにより冷却速度が低下し、部材70Aを設けていないものよりもゆっくりと冷却が進行していくことで、その間も冷却が進行する回路基板40よりも高温の状態となり得る。例えば接合部位60cの凝固開始から凝固終了までの間、このように部材70Aを設けた半導体パッケージ50が回路基板40よりも高温の状態になるように、所定の熱容量を有する部材70Aが設けられる。

このような部材70Aが設けられ、半導体パッケージ50が回路基板40よりも高温の状態とされることで、凝固時の接合部位60cには、半導体パッケージ50側が回路基板40側よりも高温になるような温度勾配ができる。このような温度勾配ができることで、接合部位60cは概ね、より低温の回路基板40側から、より高温の半導体パッケージ50側に向かって、凝固が進行していくようになる。

このように凝固が進行していくことで、接合部位60cには、図10(C)に示すように、その凝固の進行方向、即ち、回路基板40の端子41から半導体パッケージ50の端子51に向かう方向に延びるように、板状のCu6Sn5の化合物61が形成される。板状のCu6Sn5は、接合材60a及び接合材60bに含まれるSnとCuが用いられて形成される。Cu6Sn5の形成には、接合材60a及び接合材60bに含まれるCuのほか、Cuを用いた電極層41a及び電極層51aから拡散するCuが更に用いられてもよい。ここでは複数の板状の化合物61を例示するが、化合物61の数、配置は、例示の形態に限定されるものではない。板状のCu6Sn5の化合物61は、Sn、Ag及びCuを含有する部分62で覆われる。凝固の進行により、そのような部分62の内部に板状の化合物61を含有する接合部60が形成され、図10(C)に示すような、接合部60で回路基板40と半導体パッケージ50が接合された電子装置1Aが得られる。

尚、電極層41b及び電極層51bのNi層は、接合部位60cや接合部60の半田成分と反応し、金属間化合物を形成し得る。電極層41b及び電極層51bのAu層は、接合前のNi層の酸化を抑制する機能を有し、接合時には接合部位60cや接合部60の半田成分と反応して金属間化合物を形成し得る。

以上のように電子装置1Aでは、図10(C)に示すように、回路基板40の端子41と半導体パッケージ50の端子51を接合する接合部60に、端子41から端子51に向かう方向に延びる板状の化合物61が形成される。この板状の化合物61が補強材の役割を果たし、接合部60の、外力や熱に起因した応力、例えば、端子41と端子51の対向方向と交差する方向の応力に対する強度の向上が図られる。例えば、接合部60にこのような板状の化合物61を形成することで、形成しなかった場合に比べて、繰り返し曲げ試験寿命や温度サイクル試験寿命を2倍以上にすることも可能になる。

ここで、所定の熱容量を有する部材70Aの半導体パッケージ50上への配設に関し、次の図11及ぶ図12を参照して説明する。

図11は第2の実施の形態に係る電子装置の第1構成例を示す図である。尚、図11には、第2の実施の形態に係る電子装置の第1構成例の要部断面を模式的に図示している。

部材70Aは、図11に示す電子装置1Aaのように、半導体パッケージ50の上面50bに、接着材80aを用いて設けることができる。接着材80aには、例えば、エポキシ樹脂等の樹脂材料を用いることができる。また、接着材80aには、例えば、インジウム銀(InAg)合金、金スズ(AuSn)合金等の金属ペースト材料を用いることができる。

このような接着材80aを用いて予め部材70Aが接着された半導体パッケージ50が準備され、準備された半導体パッケージ50が、上記図10(A)〜図10(C)に示したように、回路基板40と接合される。これにより、図11に示すような、部材70Aが接着材80aで接着された半導体パッケージ50と、回路基板40とが、内部に板状の化合物61を含有する接合部60を介して接合された電子装置1Aaが得られる。電子装置1Aaの、半導体パッケージ50上に接着された部材70Aは、例えば、電子装置1Aaの使用時に、半導体パッケージ50で発生する熱を外部に放熱する放熱部材として用いることができる。

図12は第2の実施の形態に係る電子装置の第2構成例を示す図である。尚、図12(A)及び図12(B)には、第2の実施の形態に係る電子装置の第2構成例の要部断面を模式的に図示している。

この例では、図12(A)に示すように、接着材80bが用いられて、部材70Aが半導体パッケージ50の上面50bに接着される。ここでの接着材80bには、紫外線照射によって硬化し、剥離性が発現する(粘着力が低下する)紫外線硬化樹脂が用いられる。

このような紫外線硬化樹脂の接着材80bが用いられ、予め部材70Aが接着(仮接着)された半導体パッケージ50が準備される。準備された半導体パッケージ50が、上記図10(A)〜図10(C)に示したように、回路基板40と接合される。これにより、図12(A)に示すような、部材70Aが接着材80bで仮接着された半導体パッケージ50と、回路基板40とが、内部に板状の化合物61を含有する接合部60を介して接合された構造が得られる。

このような構造が得られた後、接着材80bに紫外線が照射される。これにより、接着材80bに剥離性が発現され、半導体パッケージ50上に仮接着されていた部材70A及び接着材80bが、半導体パッケージ50上から分離可能な状態になる。このような状態となった部材70A及び接着材80bが、半導体パッケージ50上から除去されることで、図12(B)に示すような電子装置1Abが得られる。このように部材70Aは、回路基板40と半導体パッケージ50の接合時には仮接着しておき、回路基板40と半導体パッケージ50の接合後に除去することもできる。

尚、この第2の実施の形態では、接合材60aにSn−Ag−Cu系半田を用いる場合を例示したが、以上述べた手法は、Sn−Cu系半田、Sn−Ag系半田、Sn−Au系半田、Sn−Ni系半田、Sn−Pd系半田等を用いる場合にも、同様に適用可能である。また、上記のような接合材60bを半導体パッケージ50側に設け、接合材60aを回路基板40側に設けて、接合を行うことも可能である。半導体パッケージ50側、回路基板40側には、上記図4の例に従い、板状の化合物61の原料となる元素を含む接合材60a、接合材60bを設けることが可能である。

また、この第2の実施の形態では、回路基板40と半導体パッケージ50の接合を例にして説明したが、このような部材70Aを用いる手法は、各種電子部品同士の接合の際に、同様に適用可能である。

次に、第3の実施の形態について説明する。

ここでは、上記第2の実施の形態と同様に、接合する電子部品の一方を回路基板とし、他方を半導体パッケージとする場合を例にして説明する。

図13は第3の実施の形態に係る電子部品接合工程の一例を示す図である。尚、図13には、第3の実施の形態に係る電子部品接合工程の一例の要部断面を模式的に図示している。図13(A)は接合前の状態の一例を示す図、図13(B)は接合時の状態の一例を示す図、図13(C)は接合後の状態の一例を示す図である。

この図13(A)〜図13(C)に示す、第3の実施の形態に係る電子部品接合工程は、回路基板40側に所定の熱容量を有する部材70Bが設けられる点で、上記第2の実施の形態に係る電子部品接合工程と相違する。

この第3の実施の形態では、まず接合する電子部品として、図13(A)に示すような、部材70Bを設けた回路基板40と、半導体パッケージ50が準備される。

回路基板40は、その表面40aに設けられた、Cu等の電極層41aとNi/Au等の電極層41bとを含む端子41を有する。端子41(電極層41b)上には、例えば、上記図4(B)に例示した接合材30bと同様に、半田ペーストにCu粉を混合した接合材60bが、予め設けられる。或いは、端子41上には、例えば、上記図4(C)に例示した接合材30bと同様に、半田ペースト上にCu粉を付着させた接合材60bが、予め設けられる。上記第2の実施の形態で述べたのと同様に、半田ペーストの半田には、Snを含む各種半田材料を用いることができ、Cu粉には、例えば粒径3μm〜5μmのCu粒子の粉末を用いることができる。接合材60bは、例えば、このようなCu粉を混合した半田ペーストを端子41上に塗布する、或いは端子41上に塗布した半田ペースト上にCu粉を付着させることで、形成される。

回路基板40の、端子41が設けられた表面40aと反対側の表面(下面)40bには、所定の熱容量を有する部材70Bが設けられる。部材70Bには、後述のように接合材60a及び接合材60bを加熱により溶融しその後冷却して凝固する際に、この部材70Bを設けた回路基板40が半導体パッケージ50よりも高温の状態になるような熱容量を有する材料が用いられる。部材70Bは、このような所定の熱容量を有するように、材料(比熱)が選択されると共に、その平面サイズ及び厚みが設定される。部材70Bには、例えば、Cu、Al等のプレートを用いることができる。

部材70Bは、回路基板40の下面40bに直に設けることができるほか、図13では図示を省略するが、樹脂等の接着材を用いて回路基板40の下面40bに設けることもできる。尚、部材70Bの回路基板40下への配設については後述する。

半導体パッケージ50は、回路基板40に対向して配置され、表面50aに設けられた、Cu等の電極層51aとNi/Au等の電極層51bとを含む端子51を有する。半導体パッケージ50の端子51(電極層51b)上には、例えばSn−Ag−Cu系半田の接合材60aが予め設けられる。

接合材60b及び部材70Bが設けられた回路基板40と、接合材60aが設けられた半導体パッケージ50は、図13(A)に示すように、互いの端子41(接合材60b)と端子51(接合材60a)の位置合わせが行われて、対向配置される。

そして、図13(B)に示すように、半導体パッケージ50の端子51上の接合材60aが、加熱により溶融され、回路基板40の端子41上の、同様に溶融された接合材60bと接続される。接合材60aと接合材60bは、このような溶融、接続により一体化され、一体化された接合部位60cが、冷却により凝固される。

ここで、上記のように回路基板40には、所定の熱容量を有する部材70Bが設けられている。この部材70Bにより、接合材60a及び接合材60bの加熱後の冷却過程で、例えば接合部位60cの凝固開始から凝固終了までの間、回路基板40が半導体パッケージ50よりも高温の状態になるように調節される。

部材70Bを設けた回路基板40は、部材70Bを設けていない回路基板40に比べて大きな熱容量を有する。そのため、接合材60a及び接合材60bが溶融されて一体化された接合部位60cが凝固のために冷却される際、部材70Bを設けた回路基板40の冷却速度は、部材70Bを設けていない回路基板40に比べて低下する。即ち、回路基板40は、部材70Bが設けられることで、より冷え難くなる。例えば、部材70Bを設けた回路基板40の冷却速度は、1℃/min以下である。

接合部位60cが凝固のために冷却される際には、回路基板40と共に、半導体パッケージ50も冷却されていく。この時、回路基板40は、部材70Bにより冷却速度が低下し、部材70Bを設けていないものよりもゆっくりと冷却が進行していくことで、その間も冷却が進行する半導体パッケージ50よりも高温の状態となり得る。例えば接合部位60cの凝固開始から凝固終了までの間、このように部材70Bを設けた回路基板40が半導体パッケージ50よりも高温の状態になるように、所定の熱容量を有する部材70Bが設けられる。

このような部材70Bが設けられ、回路基板40が半導体パッケージ50よりも高温の状態とされることで、凝固時の接合部位60cには、回路基板40側が半導体パッケージ50側よりも高温になるような温度勾配ができる。このような温度勾配ができることで、接合部位60cは概ね、より低温の半導体パッケージ50側から、より高温の回路基板40側に向かって、凝固が進行していくようになる。

このように凝固が進行していくことで、接合部位60cには、図13(C)に示すように、その凝固の進行方向、即ち、半導体パッケージ50の端子51から回路基板40の端子41に向かう方向に延びるように、板状のCu6Sn5の化合物61が形成される。板状のCu6Sn5は、接合材60a及び接合材60bに含まれるSnとCuが用いられて、或いは更に電極層41a及び電極層51aから拡散するCuが用いられて、形成される。ここでは複数の板状の化合物61を例示するが、化合物61の数、配置は、例示の形態に限定されるものではない。板状のCu6Sn5の化合物61は、Sn、Ag及びCuを含有する部分62で覆われる。凝固の進行により、そのような部分62の内部に板状の化合物61を含有する接合部60が形成され、図13(C)に示すような、接合部60で回路基板40と半導体パッケージ50が接合された電子装置1Bが得られる。

このように、所定の熱容量を有する部材70Bを回路基板40側に設けた場合にも、回路基板40の端子41と半導体パッケージ50の端子51を接合する接合部60に、端子51から端子41に向かう方向に延びる板状の化合物61を形成することができる。これにより、接合部60の、外力や熱に起因した応力、例えば、端子41と端子51の対向方向と交差する方向の応力に対する強度の向上が図られた、電子装置1Bを得ることができる。例えば、接合部60にこのような板状の化合物61を形成することで、形成しなかった場合に比べて、繰り返し曲げ試験寿命や温度サイクル試験寿命を2倍以上にすることも可能になる。

ここで、所定の熱容量を有する部材70Bの回路基板40下への配設に関して説明する。

部材70Bを回路基板40下に設ける方法の1つとして、部材70B上に回路基板40を載置する方法が挙げられる。この場合、回路基板40は、単に部材70B上に載置すればよく、接着材を用いて部材70B上に接着する等して固定することを要しない。このように部材70B上に載置された回路基板40に、図13(A)〜図13(C)に示したように、接合材60a及び接合材60bが用いられ、半導体パッケージ50が接合される。接合後の構造体は、部材70B上からピックアップされる。これにより、接合部60で回路基板40と半導体パッケージ50が接合された、部材70Bを含まない電子装置1Bが得られる。

また、部材70Bは、接着材を利用して回路基板40下に設けることも可能である。このような方法について、次の図14及び図15を参照して説明する。

図14は第3の実施の形態に係る電子装置の第1構成例を示す図である。尚、図14には、第3の実施の形態に係る電子装置の第1構成例の要部断面を模式的に図示している。

回路基板40が、その下面40bに回路パターンや外部接続用の端子を有しない片面回路基板である場合には、図14に示すように、回路基板40の下面40bに樹脂材料や金属ペースト材料等の接着材80aを用いて、部材70Bを設けてもよい。このような接着材80aを用いて予め部材70Bが接着された回路基板40が準備され、準備された回路基板40が、上記図13(A)〜図13(C)に示したように、接合材60a及び接合材60bを用いて、半導体パッケージ50と接合される。これにより、図14に示すような、半導体パッケージ50と、部材70Bが接着材80aで接着された回路基板40とが、内部に板状の化合物61を含有する接合部60を介して接合された電子装置1Baが得られる。電子装置1Baの部材70Bは、電子装置1Baの使用時に、回路基板40に伝熱された熱を外部に放熱する放熱部材として用いることができる。

図15は第3の実施の形態に係る電子装置の第2構成例を示す図である。尚、図15(A)及び図15(B)には、第3の実施の形態に係る電子装置の第2構成例の要部断面を模式的に図示している。

この例では、図15(A)に示すように、紫外線硬化樹脂の接着材80bが用いられて、部材70Bが回路基板40の下面40bに接着される。このような接着材80bで予め部材70Bが接着(仮接着)された回路基板40が準備され、上記図13(A)〜図13(C)に示したように、接合材60a及び接合材60bを用いて、半導体パッケージ50と接合される。これにより、図15(A)に示すような、半導体パッケージ50と、部材70Bが接着材80bで仮接着された回路基板40とが、内部に板状の化合物61を含有する接合部60を介して接合された構造が得られる。その後、接着材80bに紫外線が照射され、部材70B及び接着材80bが回路基板40下から除去されることで、図15(B)に示すような電子装置1Bbが得られる。このように回路基板40と半導体パッケージ50の接合時には部材70Bを仮接着しておき、接合後、その部材70Bを除去することもできる。

尚、この第3の実施の形態では、接合材60aにSn−Ag−Cu系半田を用いる場合を例示したが、以上述べた手法は、Sn−Cu系半田、Sn−Ag系半田、Sn−Au系半田、Sn−Ni系半田、Sn−Pd系半田等を用いる場合にも、同様に適用可能である。また、上記のような接合材60bを半導体パッケージ50側に設け、接合材60aを回路基板40側に設けて、接合を行うことも可能である。半導体パッケージ50側、回路基板40側には、上記図4の例に従い、板状の化合物61の原料となる元素を含む接合材60a、接合材60bを設けることが可能である。

また、この第3の実施の形態では、回路基板40と半導体パッケージ50の接合を例にして説明したが、このような部材70Bを用いる手法は、各種電子部品同士の接合の際に、同様に適用可能である。

次に、第4の実施の形態について説明する。

ここでは、上記第2及び第3の実施の形態と同様に、接合する電子部品の一方を回路基板とし、他方を半導体パッケージとする場合を例にして説明する。

図16は第4の実施の形態に係る電子部品接合工程の一例を示す図である。尚、図16には、第4の実施の形態に係る電子部品接合工程の一例の要部断面を模式的に図示している。図16(A)は接合前の状態の一例を示す図、図16(B)は接合時の状態の一例を示す図、図16(C)は接合後の状態の一例を示す図である。

この例では、まず接合する電子部品として、図16(A)に示すような回路基板40と半導体パッケージ50が準備される。

回路基板40は、その表面40aに設けられた、Cu等の電極層41aとNi/Au等の電極層41bとを含む端子41を有する。端子41(電極層41b)上には、例えば、半田ペーストにCu粉を混合した接合材60b、或いは半田ペースト上にCu粉を付着させた接合材60bが、予め設けられる。

半導体パッケージ50は、回路基板40に対向して配置され、表面50aに設けられた、Cu等の電極層51aとNi/Au等の電極層51bとを含む端子51を有する。半導体パッケージ50の端子51(電極層51b)上には、例えばSn−Ag−Cu系半田の接合材60aが予め設けられる。

接合材60bが設けられた回路基板40と、接合材60aが設けられた半導体パッケージ50は、図16(A)に示すように、互いの端子41(接合材60b)と端子51(接合材60a)の位置合わせが行われて、対向配置される。

そして、図16(B)に示すように、半導体パッケージ50の端子51上の接合材60aが、加熱により溶融され、回路基板40の端子41上の、同様に溶融された接合材60bと接続される。接合材60aと接合材60bは、このような溶融、接続により一体化された接合部位60cとなり、この接合部位60cが冷却により凝固される。

この冷却の際、回路基板40と半導体パッケージ50のうちの一方、ここでは一例として半導体パッケージ50を、選択的に冷却する。例えば、図16(C)に示すように、半導体パッケージ50に対して選択的に、ファン等を用いて送風91を行い、半導体パッケージ50を冷却する。このように半導体パッケージ50を送風91により冷却し、その冷却速度を増大させる。

接合部位60cが凝固のために冷却される際には、回路基板40及び半導体パッケージ50が共に冷却されていく。この時、半導体パッケージ50に対して選択的に送風91を行い、半導体パッケージ50の冷却速度を増大させることで、回路基板40は、半導体パッケージ50よりも高温の状態となり得る。半導体パッケージ50を、このような送風91により冷却し、例えば接合部位60cの凝固開始から凝固終了までの間、回路基板40が半導体パッケージ50よりも高温の状態になるように調節する。

回路基板40が半導体パッケージ50よりも高温の状態とされることで、凝固時の接合部位60cには、回路基板40側が半導体パッケージ50側よりも高温になるような温度勾配ができる。このような温度勾配ができることで、接合部位60cは概ね、より低温の半導体パッケージ50側から、より高温の回路基板40側に向かって、凝固が進行していくようになる。

このように凝固が進行していくことで、接合部位60cには、図16(C)に示すように、半導体パッケージ50の端子51から回路基板40の端子41に向かう方向に延びるように、板状のCu6Sn5の化合物61が形成される。ここでは複数の板状の化合物61を例示するが、化合物61の数、配置は、例示の形態に限定されるものではない。板状のCu6Sn5の化合物61は、Sn、Ag及びCuを含有する部分62で覆われる。凝固の進行により、そのような部分62の内部に板状の化合物61を含有する接合部60が形成され、図16(C)に示すような、接合部60で回路基板40と半導体パッケージ50が接合された電子装置1Cが得られる。

このように半導体パッケージ50に対して選択的に送風91を行う方法によっても、回路基板40と半導体パッケージ50の接合部60に、端子51から端子41に向かう方向に延びる板状の化合物61を形成することができる。これにより、接合部60の、外力や熱に起因した応力、例えば、端子41と端子51の対向方向と交差する方向の応力に対する強度の向上が図られた、電子装置1Cを得ることができる。

図17〜図19は第4の実施の形態に係る電子部品接合工程の別例を説明する図である。尚、図17〜図19にはそれぞれ、第4の実施の形態に係る電子部品接合工程の別例の要部断面を模式的に図示している。

上記図16(C)には、図16(B)の接合部位60cが凝固のために冷却される際、半導体パッケージ50に対して選択的に送風91を行って半導体パッケージ50を冷却し、回路基板40が半導体パッケージ50よりも高温の状態になるようにする場合を例示した。

このほか、図16(B)の接合部位60cが凝固のために冷却される際、同様に回路基板40が半導体パッケージ50よりも高温の状態になるようにするためには、図17に示すように、回路基板40に対して選択的にヒータ等で加熱92を行う方法を採用してもよい。加熱92を行うことで、回路基板40を温め、その冷却速度を低下させる。このような方法を用いて、凝固時の接合部位60cに、回路基板40側が半導体パッケージ50側よりも高温になるような温度勾配を生じさせ、概ね回路基板40側に向かって凝固を進行させて、上記のような板状のCu6Sn5の化合物61を形成する。

また、上記図16(C)には、半導体パッケージ50に対して選択的に送風91を行う場合を例示したが、図18に示すように、回路基板40に対して選択的に送風91を行い、半導体パッケージ50が回路基板40よりも高温の状態になるようにしてもよい。この場合は、まず上記図16(A)及び図16(B)に示したように、回路基板40と半導体パッケージ50が対向配置され、接合材60aと接合材60bが溶融、接続されて接合部位60cが形成された後、接合部位60cが冷却により凝固される。この冷却の際、回路基板40に対して選択的に、ファン等を用いて送風91を行い、回路基板40を冷却する。このように回路基板40を送風91により冷却し、その冷却速度を増大させ、例えば接合部位60cの凝固開始から凝固終了までの間、半導体パッケージ50が回路基板40よりも高温の状態になるようにする。このような方法を用いて、凝固時の接合部位60cに、半導体パッケージ50側が回路基板40側よりも高温になるような温度勾配を生じさせ、概ね半導体パッケージ50側に向かって凝固を進行させて、上記のような板状のCu6Sn5の化合物61を形成する。

半導体パッケージ50側が回路基板40側よりも高温の状態になるようにするためには、図19に示すように、半導体パッケージ50に対して選択的にヒータ等で加熱92を行う方法を採用してもよい。加熱92を行うことで、半導体パッケージ50を温め、その冷却速度を低下させる。このような方法を用いて凝固時の接合部位60cに、半導体パッケージ50側が回路基板40側よりも高温になるような温度勾配を生じさせ、上記のような板状のCu6Sn5の化合物61を形成する。

尚、この第4の実施の形態では、接合材60aに、Sn−Ag−Cu系半田を用いる場合を例示したが、以上述べた手法は、Sn−Cu系半田、Sn−Ag系半田、Sn−Au系半田、Sn−Ni系半田、Sn−Pd系半田等を用いる場合にも、同様に適用可能である。また、上記のような接合材60bを半導体パッケージ50側に設け、接合材60aを回路基板40側に設けて、接合を行うことも可能である。半導体パッケージ50側、回路基板40側には、上記図4の例に従い、板状の化合物61の原料となる元素を含む接合材60a、接合材60bを設けることが可能である。

この第4の実施の形態では、回路基板40と半導体パッケージ50の接合を例にして説明したが、このような送風91又は加熱92を行う手法は、各種電子部品同士の接合の際に、同様に適用可能である。

以上述べた第1〜第4の実施の形態に係る電子装置1,1A(1Aa,1Ab),1B(1Ba,1Bb),1Cは、例えば、次のような製造装置を用いて製造することができる。尚、ここでは、接合する電子部品の一方を回路基板40とし、他方を半導体パッケージ50とする場合を例にして説明する。

図20は電子装置の製造装置の一例を示す図である。

図20に示す製造装置1000は、配置部1100、加熱部1200及び冷却部1300を備える。

準備された回路基板40と半導体パッケージ50は、まず配置部1100に搬送され、配置部1100において位置合わせが行われ、対向配置される。尚、準備される回路基板40と半導体パッケージ50は、例えば、回路基板40と、部材70Aが設けられた半導体パッケージ50である。或いは、準備される回路基板40と半導体パッケージ50は、例えば、部材70Bが設けられた回路基板40と、半導体パッケージ50との組合せである。或いはまた、準備される回路基板40と半導体パッケージ50は、部材70Bが設けられていない回路基板40と、部材70Aが設けられていない半導体パッケージ50との組合せである。図20では便宜上、部材70A、部材70Bの図示を省略している。

位置合わせされた回路基板40と半導体パッケージ50は、配置部1100の後段に設けられた加熱部1200に移送され、回路基板40に設けられた接合材60b及び半導体パッケージ50に設けられた接合材60aの種類に応じた温度で加熱される。加熱は、不活性ガス雰囲気で行われる。加熱部1200において、回路基板40の接合材60bと半導体パッケージ50の接合材60aとが溶融、接続され、接合材60aと接合材60bが一体化された接合部位60cが形成される。尚、加熱部1200では、加熱温度を段階的に上昇させ、より低温の加熱(予備加熱)と、より高温の加熱(本加熱)とが実施されるようにすることができる。

加熱により接合部位60cが形成された回路基板40と半導体パッケージ50は、加熱部1200の後段に設けられた冷却部1300に移送され、接合部位60cが冷却により凝固される。冷却は、不活性ガス雰囲気で行われる。

ここで、冷却部1300は、パージ等で内部の全体的な雰囲気温度を調節し、回路基板40及び半導体パッケージ50並びに接合部位60cを冷却する温度調節装置1310を備える。冷却部1300は更に、このような温度調節装置1310に加えて、回路基板40側に設けられた温度調節装置1320、半導体パッケージ50側に設けられた温度調節装置1330を備える。温度調節装置1320には、例えば、送風機能若しくは加熱機能、又は送風機能と加熱機能の両方を備えたものが用いられる。温度調節装置1330には、例えば、送風機能若しくは加熱機能、又は送風機能と加熱機能の両方を備えたものが用いられる。

準備される回路基板40及び半導体パッケージ50が、それぞれ部材70B及び部材70Aを設けたものである場合には、温度調節装置1310が使用され、上記第2及び第3の実施の形態で述べたような冷却、接合部60の形成が行われる。この場合は、必ずしも温度調節装置1320及び温度調節装置1330を使用することを要しない。

準備される回路基板40及び半導体パッケージ50が、いずれも部材70B及び部材70Aを設けていないものである場合には、温度調節装置1310と、温度調節装置1320又は温度調節装置1330が使用される。即ち、温度調節装置1320又は温度調節装置1330が使用され、回路基板40と半導体パッケージ50のいずれか一方が選択的に加熱されるか又は冷却される。これにより、上記第4の実施の形態で述べたような冷却、接合部60の形成が行われる。

例えば、この図20に示すような構成を有する製造装置1000を用いて、上記第1〜第4の実施の形態に係る電子装置1,1A(1Aa,1Ab),1B(1Ba,1Bb),1Cを製造することができる。

以下に実施例を示す。

〔実施例1〕

平面サイズ35mm×35mmの半導体パッケージの背面に、その半導体パッケージと同等サイズのCuプレート(部材)を装着した。そして、このCuプレートを装着した半導体パッケージの端子と、回路基板の端子とを、Sn−3.0Ag−0.5Cu(Ag:3.0wt%,Cu:0.5wt%)の半田ボールを用いて接合した。接合は、N2雰囲気(酸素濃度100ppm以下)中、最大温度245℃、217℃以上で2分間の条件で行った。

このようにして回路基板と半導体パッケージとを接合した電子装置について、その接合部の導通に問題がないことを確認した後、接合信頼性の評価を行った。−40℃〜125℃の繰り返し温度サイクル試験を1000サイクル行った結果、抵抗上昇は10%以下と良好であった。また、温度121℃、湿度85%の環境下に1000時間放置した後も、温度サイクル試験同様、抵抗上昇は10%以下と良好であった。電子顕微鏡を用いて接合部の断面観察を行った結果、回路基板と半導体パッケージの端子間に、一方の端子から他方の端子に向かう方向に延びる板状のCu6Sn5化合物が形成されていることが確認された。

〔実施例2〕

平面サイズ35mm×35mmの半導体パッケージの背面に、その半導体パッケージと同等サイズのAlプレート(部材)を装着した。そして、このAlプレートを装着した半導体パッケージの端子と、回路基板の端子とを、Sn−3.0Ag−0.5Cu(Ag:3.0wt%,Cu:0.5wt%)の半田ボールを用いて接合した。接合は、N2雰囲気(酸素濃度100ppm以下)中、最大温度245℃、217℃以上で2分間の条件で行った。

このようにして回路基板と半導体パッケージとを接合した電子装置について、その接合部の導通に問題がないことを確認した後、接合信頼性の評価を行った。−40℃〜125℃の繰り返し温度サイクル試験を1000サイクル行った結果、抵抗上昇は10%以下と良好であった。また、温度121℃、湿度85%の環境下に1000時間放置した後も、温度サイクル試験同様、抵抗上昇は10%以下と良好であった。電子顕微鏡を用いて接合部の断面観察を行った結果、回路基板と半導体パッケージの端子間に、一方の端子から他方の端子に向かう方向に延びる板状のCu6Sn5化合物が形成されていることが確認された。

〔実施例3〕

平面サイズ35mm×35mmの半導体パッケージの背面に、その半導体パッケージと同等サイズのCuプレート(部材)を装着した。回路基板の端子上には、粒径3μm〜5μmのCu粉を混合したSn−Ag−Cuの半田ペーストを印刷法により塗布した。そして、Cuプレートを装着した半導体パッケージの端子と、Cu粉を混合した半田ペーストを設けた回路基板の端子とを、Sn−3.0Ag−0.5Cu(Ag:3.0wt%,Cu:0.5wt%)の半田ボールを用いて接合した。接合は、N2雰囲気(酸素濃度100ppm以下)中、最大温度245℃、217℃以上で2分間の条件で行った。

このようにして回路基板と半導体パッケージとを接合した電子装置について、その接合部の導通に問題がないことを確認した後、接合信頼性の評価を行った。−40℃〜125℃の繰り返し温度サイクル試験を1000サイクル行った結果、抵抗上昇は10%以下と良好であった。また、温度121℃、湿度85%の環境下に1000時間放置した後も、温度サイクル試験同様、抵抗上昇は10%以下と良好であった。電子顕微鏡を用いて接合部の断面観察を行った結果、回路基板と半導体パッケージの端子間に、一方の端子から他方の端子に向かう方向に延びる板状のCu6Sn5化合物が形成されていることが確認された。

〔実施例4〕

平面サイズ35mm×35mmの半導体パッケージの背面に、その半導体パッケージと同等サイズのAlプレート(部材)を装着した。回路基板の端子上には、粒径3μm〜5μmのCu粉を混合したSn−Ag−Cuの半田ペーストを印刷法により塗布した。そして、Alプレートを装着した半導体パッケージの端子と、Cu粉を混合した半田ペーストを設けた回路基板の端子とを、Sn−3.0Ag−0.5Cu(Ag:3.0wt%,Cu:0.5wt%)の半田ボールを用いて接合した。接合は、N2雰囲気(酸素濃度100ppm以下)中、最大温度245℃、217℃以上で2分間の条件で行った。

このようにして回路基板と半導体パッケージとを接合した電子装置について、その接合部の導通に問題がないことを確認した後、接合信頼性の評価を行った。−40℃〜125℃の繰り返し温度サイクル試験を1000サイクル行った結果、抵抗上昇は10%以下と良好であった。また、温度121℃、湿度85%の環境下に1000時間放置した後も、温度サイクル試験同様、抵抗上昇は10%以下と良好であった。電子顕微鏡を用いて接合部の断面観察を行った結果、回路基板と半導体パッケージの端子間に、一方の端子から他方の端子に向かう方向に延びる板状のCu6Sn5化合物が形成されていることが確認された。

〔実施例5〕

回路基板の背面に、その回路基板と同等サイズのCuプレート(部材)を装着した。そして、このCuプレートを装着した回路基板の端子と、平面サイズ35mm×35mmの半導体パッケージの端子とを、Sn−3.0Ag−0.5Cu(Ag:3.0wt%,Cu:0.5wt%)の半田ボールを用いて接合した。接合は、N2雰囲気(酸素濃度100ppm以下)中、最大温度245℃、217℃以上で2分間の条件で行った。

このようにして回路基板と半導体パッケージとを接合した電子装置について、その接合部の導通に問題がないことを確認した後、接合信頼性の評価を行った。−40℃〜125℃の繰り返し温度サイクル試験を1000サイクル行った結果、抵抗上昇は10%以下と良好であった。また、温度121℃、湿度85%の環境下に1000時間放置した後も、温度サイクル試験同様、抵抗上昇は10%以下と良好であった。電子顕微鏡を用いて接合部の断面観察を行った結果、回路基板と半導体パッケージの端子間に、一方の端子から他方の端子に向かう方向に延びる板状のCu6Sn5化合物が形成されていることが確認された。

〔実施例6〕

平面サイズ35mm×35mmの半導体パッケージの端子と、回路基板の端子とを、Sn−3.0Ag−0.5Cu(Ag:3.0wt%,Cu:0.5wt%)の半田ボールを用いて接合した。接合は、N2雰囲気(酸素濃度100ppm以下)中、最大温度245℃、217℃以上で2分間の条件で行い、冷却時に半導体パッケージに対して選択的にN2の吹き付けを行った。

このようにして回路基板と半導体パッケージとを接合した電子装置について、その接合部の導通に問題がないことを確認した後、接合信頼性の評価を行った。−40℃〜125℃の繰り返し温度サイクル試験を1000サイクル行った結果、抵抗上昇は10%以下と良好であった。また、温度121℃、湿度85%の環境下に1000時間放置した後も、温度サイクル試験同様、抵抗上昇は10%以下と良好であった。電子顕微鏡を用いて接合部の断面観察を行った結果、回路基板と半導体パッケージの端子間に、一方の端子から他方の端子に向かう方向に延びる板状のCu6Sn5化合物が形成されていることが確認された。

以上説明した実施の形態に関し、更に以下の付記を開示する。

(付記1) 第1端子を備える第1電子部品と、

前記第1端子に対向する第2端子を備える第2電子部品と、

前記第1端子と前記第2端子を接合し、前記第2端子から前記第1端子に向かう方向に延びる板状の第1化合物を含有する接合部と

を含むことを特徴とする電子装置。

(付記2) 前記接合部は、前記第1化合物を覆う部分を有し、

前記部分は、第1元素と第2元素とを含み、

前記第1化合物は、前記第1元素と前記第2元素とを含む金属間化合物であることを特徴とする付記1に記載の電子装置。

(付記3) 前記接合部は、前記第1化合物と、前記第2端子から前記第1端子に向かう方向に延びる柱状の第2化合物とを含有することを特徴とする付記1に記載の電子装置。

(付記4) 前記接合部は、前記第1化合物と前記第2化合物とを覆う部分を有し、

前記部分は、第1元素と第2元素と第3元素とを含み、

前記第1化合物は、前記第1元素と前記第2元素とを含む金属間化合物であり、

前記第2化合物は、前記第1元素と前記第3元素とを含む金属間化合物であることを特徴とする付記3に記載の電子装置。

(付記5) 前記第1電子部品に設けられ、第1熱容量を有する第1部材を更に含むことを特徴とする付記1乃至4のいずれかに記載の電子装置。

(付記6) 前記第1部材が設けられた前記第1電子部品の熱容量が、前記第2電子部品の熱容量よりも大きいことを特徴とする付記5に記載の電子装置。

(付記7) 第1電子部品に設けられた第1端子と、第2電子部品に設けられた第2端子とを、接合材を介して対向させる工程と、

前記接合材を加熱して溶融し、前記第1端子、前記接合材及び前記第2端子を接続する工程と、

前記第1電子部品を前記第2電子部品よりも高温にした状態で、前記接合材を冷却して凝固し、前記接合材の内部に、前記第2端子から前記第1端子に向かう方向に延びる板状の化合物を析出させる工程と

を含むことを特徴とする電子装置の製造方法。

(付記8) 前記化合物は、第1元素と第2元素とを含む金属間化合物であり、

前記接合材は、前記第1端子上に設けられた第1接合材と、前記第2端子上に設けられた第2接合材とを含み、

前記第1接合材と前記第2接合材には、前記第1元素と前記第2元素のうち、少なくとも前記第1元素を含む半田材料が用いられ、

前記第2接合材の前記半田材料に、前記第2元素の粉末材料が含まれていることを特徴とする付記7に記載の電子装置の製造方法。

(付記9) 前記第1電子部品に、第1熱容量を有する第1部材を設ける工程を更に含み、

前記第1部材が設けられた前記第1電子部品の前記第1端子と、前記第2電子部品の前記第2端子とを、前記接合材を介して対向させることを特徴とする付記7又は8に記載の電子装置の製造方法。

(付記10) 前記化合物を析出させる工程後に、前記第1部材を除去する工程を更に含むことを特徴とする付記9に記載の電子装置の製造方法。

(付記11) 前記第1部材を設ける工程は、前記第1電子部品に接着材を用いて前記第1部材を接着する工程を含み、

前記第1部材を除去する工程は、前記接着材の接着力を低下させて前記第1部材を前記第1電子部品から除去する工程を含むことを特徴とする付記10に記載の電子装置の製造方法。

(付記12) 前記接合材を冷却し凝固する工程は、前記第1電子部品が前記第2電子部品よりも高温になるように、前記第1電子部品と前記第2電子部品のうち、前記第2電子部品を選択的に冷却する工程を含むことを特徴とする付記7又は8に記載の電子装置の製造方法。

(付記13) 前記接合材を冷却し凝固する工程は、前記第1電子部品が前記第2電子部品よりも高温になるように、前記第1電子部品と前記第2電子部品のうち、前記第1電子部品を選択的に加熱する工程を含むことを特徴とする付記7又は8に記載の電子装置の製造方法。