JP3750468B2 - 半導体ウエハーの製造方法及び半導体装置 - Google Patents

半導体ウエハーの製造方法及び半導体装置 Download PDFInfo

- Publication number

- JP3750468B2 JP3750468B2 JP2000055864A JP2000055864A JP3750468B2 JP 3750468 B2 JP3750468 B2 JP 3750468B2 JP 2000055864 A JP2000055864 A JP 2000055864A JP 2000055864 A JP2000055864 A JP 2000055864A JP 3750468 B2 JP3750468 B2 JP 3750468B2

- Authority

- JP

- Japan

- Prior art keywords

- post

- layer

- external terminal

- semiconductor device

- spherical post

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 48

- 238000004519 manufacturing process Methods 0.000 title claims description 19

- 229910052751 metal Inorganic materials 0.000 claims description 55

- 239000002184 metal Substances 0.000 claims description 55

- 238000000034 method Methods 0.000 claims description 34

- 229910000679 solder Inorganic materials 0.000 claims description 26

- 239000011347 resin Substances 0.000 claims description 25

- 229920005989 resin Polymers 0.000 claims description 25

- 239000000463 material Substances 0.000 claims description 20

- 238000007789 sealing Methods 0.000 claims description 19

- 230000001681 protective effect Effects 0.000 claims description 14

- 238000002844 melting Methods 0.000 claims description 13

- 230000008018 melting Effects 0.000 claims description 13

- 239000000758 substrate Substances 0.000 claims description 11

- 239000002131 composite material Substances 0.000 claims description 5

- 239000010410 layer Substances 0.000 description 83

- 238000010438 heat treatment Methods 0.000 description 11

- 238000007747 plating Methods 0.000 description 10

- 239000004642 Polyimide Substances 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 229920001721 polyimide Polymers 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 238000003466 welding Methods 0.000 description 8

- 238000010586 diagram Methods 0.000 description 7

- 230000004907 flux Effects 0.000 description 7

- 238000000227 grinding Methods 0.000 description 7

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 229910052759 nickel Inorganic materials 0.000 description 6

- 230000004888 barrier function Effects 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 229910000838 Al alloy Inorganic materials 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 3

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 2

- XMPZTFVPEKAKFH-UHFFFAOYSA-P ceric ammonium nitrate Chemical compound [NH4+].[NH4+].[Ce+4].[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O XMPZTFVPEKAKFH-UHFFFAOYSA-P 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000000465 moulding Methods 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 238000000992 sputter etching Methods 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910010165 TiCu Inorganic materials 0.000 description 1

- QZPSXPBJTPJTSZ-UHFFFAOYSA-N aqua regia Chemical compound Cl.O[N+]([O-])=O QZPSXPBJTPJTSZ-UHFFFAOYSA-N 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 239000012776 electronic material Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000003801 milling Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

- H01L2224/0231—Manufacturing methods of the redistribution layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

- H01L2224/0233—Structure of the redistribution layers

- H01L2224/02333—Structure of the redistribution layers being a bump

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/03—Manufacturing methods

- H01L2224/033—Manufacturing methods by local deposition of the material of the bonding area

- H01L2224/0333—Manufacturing methods by local deposition of the material of the bonding area in solid form

- H01L2224/03334—Manufacturing methods by local deposition of the material of the bonding area in solid form using a preform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/119—Methods of manufacturing bump connectors involving a specific sequence of method steps

- H01L2224/1191—Forming a passivation layer after forming the bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は高密度実装対応のウエーハレベルのCSP(チップサイズパッケージ)型の半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

近年、携帯電話や情報端末等の機器類の小型化に伴い、搭載部品の小型,軽量化が要求され、LSI等の半導体装置も、従来のウエーハ処理工程とパッケージ組み立て工程を一本化したウエーハレベルのCSPの供給が行われるようになった。ウエーハレベルのCSPの特徴は、従来の単チップから作られるCSPに比べ、インタポーザ等の部品点数や工程数の削減による製造コストを抑え、パッケージトータルの低コスト化を図るものである。この技術は、例えば1999年の日経マイクロデバイス2月号p38〜p67や電子材料9月号p21〜p85にその構造や工程概要が記載されている。

【0003】

これらの製造方法は、例えば図7及び図8に示す。

【0004】

まず、図7(A)に示すように、半導体素子が作り込まれたシリコン基板11のAl合金配線パッド12上のシリコン窒化膜等の保護絶縁層13及びポリイミド層14を開孔した後に、CrやTiW等の密着層15上にCuをそれぞれスパッタしてシード層16を形成後、更にフォトレジスト17をマスクにCuを選択メッキし、引き出し用の再配線層18を形成する。次に、図7(B)に示すように、新たなフォトレジスト19をマスクに100μm程度の厚いCu層と、バリア層31を選択メッキして、バリアが積層されたCuポスト30を形成する。次に、図8(A)に示すように、レジスト19を剥離した後、再配線層18をマスクにシード層16、密着層15をエッチング除去すると、各々分離した再配線が形成される。更に、図8(B)に示すように、シリコン基板11全体の少なくとも表面を封止樹脂21で密閉した後、該樹脂21を研削もしくは機械研磨によってCuポスト30表面のバリア層31を露出させる。更に自動移載機によって各ポスト30領域にハンダボールを搭載し、ハンダボールがポスト30に溶着するように熱処理を施し、外部端子22を形成する。その後電気特性がチェックされチップ毎にダイシングし、携帯機器類のマザーボード等に装着される。

【0005】

しかしこの技術においては、以下のような問題を有する。

【0006】

Cuポスト30をメッキで形成することで、100μmを超すような厚いレジストのパターニングや長時間のメッキ工程を必要とし、コストと流動工数が問題となる。更にCuポスト30は垂直に形成されるため縦方向の引っ張り応力には弱く、特にフレキシブルボードに搭載した場合は再配線層18との剥離が生ずる問題がある。一方、ポスト30にかかる圧縮応力をシリコン基板11表面の半導体素子に不具合を与えないように、厚み数十〜100μm前後のポリイミド層14を敷いて弾力を持たせているが、逆にこの結果ポストの上下微動に伴い、パッド開孔部と再配線との接触部に応力が集中し、樹脂封止や研削工程あるいはボードへの装着等の後工程で、パッド12領域周辺に断線やクラックが生じ易い。

【0007】

又この他、薄いバリア層31を再現良く残すように研削しなくてはならず、封止樹脂の厚み,研削量及びメッキ厚み等の管理項目が多く量産性も問題である。

【0008】

【発明が解決しようとする課題】

本発明の目的は、ウエーハレベルのCSP型の半導体装置において、工程の増加を伴うことなく、低コストで信頼性の高い半導体装置及びその製造方法を提供することにある。

【0009】

【課題を解決するための手段】

本発明に係る半導体ウエハーの製造方法は、

(a)パッド及び前記パッド部が開孔されている保護絶縁層を有する半導体ウエハーの前記保護絶縁層上に応力緩和層を形成する工程

(b)前記パッドから前記応力緩和層上に至るまで再配線層を施す工程

(c)前記再配線層に球状ポストとなるメタルボールを搭載する工程

(d)樹脂にて封止を行った後に、前記樹脂の所望量を除去し前記球状ポストの一部を露出させる工程

(e)露出した前記球状ポストの上に外部端子を形成する工程

を有し、前記工程(e)において、前記外部端子は前記球状ポストより融点の低い組成材料でなることを特徴とする。

【0010】

(a)最終配線パッドから電極引き出し用の再配線層を施す工程

(b)前記再配線層の所望領域に球状ポストとなるメタルボールを搭載する工程

(c)樹脂にて封止を行った後に、前記樹脂の所望量を除去し前記ポストの一部を露出させる工程、及び

(d)露出した前記球状ポストの上に外部端子を形成する工程。

【0011】

本発明の製造方法においては、LSI等の最終配線の外部取り出し用パッド、あるいはダミーパッド開孔部に再配線層を施し、その所望領域に第1のメタルボールを搭載し、溶着させ、これを封止樹脂で包み、研削もしくは機械研磨等によって一部を露出させた後、更に第2のメタルボールを搭載し溶着することで、外部端子が形成される。

【0012】

この製造方法によれば、側面が弓形をなし引っ張り応力にも強いポストが形成でき、従って工数を増加させることなく、簡易なプロセスによりコストの削減と量産性及び信頼性の向上が図れる。

【0014】

ここで、前記工程(b)において、再配線層を選択メッキで形成する際に、第1のメタルボールを搭載する領域にフォトレジストを残すことにより、再配線層の金属がメッキされないようなへこみ部を同一工程で形成し、このへこみ部が第1のメタルボールの搭載時のアライメント誤差を吸収し、配置精度を向上するためのガイドとしての役割をなす。このことによりメタルボールの位置ずれや、又メタルボールがハンダ材でなる場合は溶着温度がばらついてもハンダ流れを起こすことがなく、ばらつきの少ない安定した球状ポストを確保することができる。溶着条件のマージン拡大に加え、ポストの固定も確実に行われ接触不良等の低減が可能となる。

【0015】

また、本発明の半導体装置の製造方法は、前記工程(d)において、前記樹脂の除去量は、上面から球状ポストの最大径に達するまでとすることを特徴とする。

【0017】

ここで、工程(c)及び(e)において、球状ポスト及び外部端子としてハンダでなるメタルボールを用いた場合は、熱処理によって再配線やポストに熱印可することで溶着させるが、ポストとなる第1のメタルボールの融点を、外部端子となる第2のメタルボールの融点より高い材料を用いることで、外部端子自身の溶着や、マザーボード等へ装着する際にポストの形状崩れに対して温度条件のマージンを広く設定することができ、歩留まりの良い組み立てが可能となる。

【0018】

さらには、本発明の半導体装置の製造方法は、前記工程(e)の後に、ダイシングを施してチップ毎に固片化する工程をさらに有することを特徴とする。

【0019】

前記チップ毎に固片化する工程は、前記工程(a)〜(e)を半導体ウエハーに対して行った場合に適用される工程であり、前記工程(a)〜(e)を固片チップに対して行った場合には適用されない。

【0020】

ここで、工程(c)及び(e)において、球状ポスト及び外部端子としてハンダでなるメタルボールを用いる場合に、内部にCuやNi等のハンダより融点の高い核を持ったボールを用いることで外部端子の高さや形状がばらつきが少なくなる。したがってボード搭載時の歩留まりが改善され、更に核の浮遊によってマザーボード等への装着時の応力緩和の役割も果たし、素子への特性影響と装着条件の制御が容易となる。

【0021】

また、本発明の半導体装置は、パッド及び前記パッド部が開孔されている保護絶縁層を有する基板の前記保護絶縁層上に形成された応力緩和層と、前記パッドから前記応力緩和層上に至るまで形成された再配線層と、前記再配線層の所望領域に封止樹脂で一部を囲まれたメタルボールでなる球状ポストと、前記球状ポストの上に形成された外部端子と、を有し、前記外部端子は、前記球状ポストより融点の低い組成材料でなることを特徴とする。

【0022】

この半導体装置によれば、樹脂で覆われるポスト側面の形状は、シリコン基板に対して少なくとも一部に垂直でない領域を持つことができ、ウエーハレベルのCSPとして、例えば携帯機器のマザーボード等に装着する場合の引っ張り応力に対して強度が確保され、歩留まりや信頼性の向上が図れる。更に、ポストが配置される領域の再配線層の少なくとも一部に、搭載するメタルボールの配置ガイドを設けることで、ポストの位置制御と密着強度の向上が図れる。

【0023】

本発明の半導体装置は半導体ウエハーであってもよい。

【0025】

さらには、本発明の半導体装置は、前記球状ポスト及び前記外部端子は、搭載メタルボールで形成されていることを特徴とする。

【0026】

あるいは、本発明の半導体装置は、前記球状ポスト及び前記外部端子を構成する搭載メタルボールは、ハンダ材で形成されていることを特徴とする。

【0027】

または、本発明の半導体装置は、最終配線パッドから電極引き出し用の再配線層において、ポストあるいは外部端子が搭載される領域の再配線層の膜厚の一部が、再配線層を主体的に形成する厚みより薄くなっていることを特徴とする。

【0029】

ここで、球状ポストや外部端子をハンダでなるメタルボールで形成する場合に、外部端子は、球状ポストより融点の低い組成材料とすることで、更には該ボール内部に、ハンダより融点の高い、例えばCuやNiあるいは合金等の核を保有させることで、外部端子の形状ばらつきを抑え、ボード等への装着時の溶着時に応力の緩和や装着条件マージンを広くとることが可能になり、歩留まりや信頼性の向上が図れる。

【0030】

【発明の実施の形態】

(第1の実施の形態)

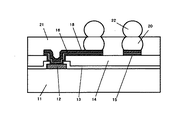

図1は、本発明の第1の実施の形態に係る半導体装置の断面構造図である。第1の実施の形態に係る半導体装置の構造を簡単に説明する。シリコン基板11にはMOSトランジスタ等の半導体素子が形成され、これらが層間絶縁膜を介してAl合金等の金属で配線され、シリコン酸化膜やシリコン窒化膜等でなる最終保護絶縁層13で覆っている。外部電極取り出しのために例えば最終配線の外部への電極取り出し用のパッド12を設け、該保護絶縁層13の必要領域を開孔し、その上層に開孔部を除いて例えば数十〜100μm程度のポリイミド層14が、素子への応力緩和のため積層されている。パッド12からはTiWでなる密着層15とCuシード層16、更に数μm厚みのCuをメッキ成膜した再配線層18を有する。再配線層18上の所定領域には、第1のメタルボールを搭載し熱処理によって溶着した球状ポスト20が形成され、その周囲をエポキシ等の封止樹脂21で包み、表面はほぼ同一面で研削され、結果的にポスト20側面は弓形をなしている。露出した頭部に第2のメタルボールを搭載した外部端子22が、所望ポスト20上に溶着形成されている。内部素子からパッド12、再配線層18、球状ポスト20等を介して外部端子22に電気的接続がなされる。

【0031】

次に、第1の実施の形態に係る半導体装置の製造方法を説明する。図2及び図3は、これを工程順に説明するための概略断面図である。

【0032】

図2(A)に示すように、まず半導体素子等が形成されたシリコン基板11にパッド12を含むAl合金の最終配線と、プラズマCVDによってシリコン窒化膜等の保護絶縁層13を1000nm程度成膜し、所望領域の該絶縁層13を選択エッチングして開孔する。更に応力緩和のため厚みが数十〜100μm程度のポリイミド層14を成膜しパッド開孔部を選択除去する。保護絶縁層13とポリイミド層14は同一フォトマスクで選択開孔してもよいが、パッド12周辺の開孔段差形状をテーパー化し、後述する再配線工程での段切れを防ぐ為に、別工程で行なった。又、感光性ポリイミドを用いるとポリイミド層の開孔工程が簡略化される。次いで、数十〜100nm程度のTiW,100〜1000nm程度のCuを連続スパッタして密着層15及びシード層16を形成した後、フォトレジスト17をパターニングしここに数百〜数千nm程度の厚みのCuを選択電界メッキし、Cu表面の酸化を防ぐためのキャップメタルとして例えばNiを薄く連続メッキした再配線層18を形成する。密着層15は、Tiwの他にCr,Ni,Ti,TiCu,Pt等高融点金属やその合金を適用しても良い。またシード層16にはCuの他にNi、AgやAuもしくはこれらの合金も適用できる。更にキャップメタルとしてNiの他に、Au,Pt,Pd等やその合金も適用できる。

【0033】

次に、図2(B)に示すように、フォトレジスト17を剥離後、必要に応じフラックスを回転塗布してから、再配線層18の所望領域に直径が100〜150μm程度の第1のメタルボール200を自動移載機で搭載させる。ボール組成はPb85〜97wt%/Snの組成でなる高温ハンダ材を用いた。

【0034】

次に、図2(C)に示すように、180〜230℃程度の窒素雰囲気中で数〜10分ほどの熱処理をするとメタルボール200が多少フローされて再配線層18に溶着し球状ポスト20が形成される。

【0035】

その後、再配線層18をマスクにイオンミーリングを用いて不要領域のシード層16と密着層15を選択除去することで、再配線が各々分離される。この除去工程には、王水、硝酸第二セリウムアンモニウムや水酸化カリウムの水溶液等のウエットエッチでも良いが、再配線を構成する各金属層のサイドエッチや、厚み減少を考慮するとドライエッチャーやミーリング等によるエッチバックが好ましい。又、エッチバックの工程は、メタルボールの搭載前の工程で行なってもよいが、キャップメタルの減少等を考慮すると、球状ポスト20を溶着した後が好ましい。

【0036】

続いて、図3(A)に示すように、モールド装置でエポキシ等の封止樹脂21で球状ポスト20が充分覆うように封止し、更に、図3(B)に示すように、グラインダーで該ポスト20が露出するように研削する。この時の研削量の管理は、球状ポスト20の頂点から最大径に達するまでの距離の1/5〜4/5の範囲として、研削量のマージンは従来のCuポストを用いる場合より十分に大きくできる。ここではポスト20が封止樹脂21で上面から包まれるかたちをなすことがポイントである。尚、樹脂21の研削にはグラインダーを用いたがウエーハ状のシリコン基板全面を一括機械研磨する方式あるいは、酸素やCF4あるいはNF3もしくはこれらの混合ガスを用いたドライエッチャーによるエッチバックも応用可能である。

【0037】

次に、図3(C)に示すように、必要に応じフラックスを塗布し、Pb/Sn60〜70wt%の低温ハンダ材でなる第2のメタルボール220を自動移載機で必要な球状ポスト20上に配置し、170〜200℃程度の窒素雰囲気で熱処理させると、図1に示すように、球状ポスト20と溶着した外部端子22が形成される。第2のメタルボール220の大きさは、BGA(Boll Grid Array)用に150〜300μm径を用いたが、用途によって特に限定されない。外部端子22用の第2のメタルボール220は、球状ポスト20に用いる第1のメタルボール200より融点の低い材料を用いた方が、熱処理時にポストの変形が少ないので、外部端子形状のばらつきが少ない。又、外部端子としてメタルボール220を搭載する代わりに、印刷法、メッキ法やメタルジェット法による外部端子用のハンダ層の形成も考えられるが、工数やコスト、形状再現性はボール搭載法に劣る。

【0038】

第1の実施の形態によれば、ポスト20の側面は弓形を保って封止樹脂21で包み込まれるように固定されている。従って後工程で生ずる各方向からの応力に対しても、ポスト20の密着力が確保され、特に従来に比べ引っ張り方向の応力に対する密着力は大幅に改善され、歩留まりや信頼性の向上が図れた。又、ポスト20の形成においては、厚いCu層の為のメッキやフォト工程を必要とせず、スループットやコストの改善がなされる。更に外部端子22を構成する材料の融点をポスト20の構成材料のそれより低くし、外部端子22の形状安定化も含めマザーボード等へのCSP装着歩留まりと信頼性が確保される。

【0039】

(他の実施の形態)

第1のメタルボール200を再配線層18上に搭載して球状ポストを形成するが、搭載時のアライメント誤差や、熱処理時にボールが所定位置から外れてしまうことがまれにあった。従って、図4(A)に示すように、再配線層18を形成する為のフォト工程で、再配線層を形成する領域の更に内部にパターンレジスト170を同一工程で形成しておき、Cuメッキで再配線層18とNiのキャップ層を選択メッキしてからレジスト17,170を剥離すると、図4(B)に示すように、第1のメタルボール200を搭載する再配線層18領域に、へこみ部40を形成することができる。次にフラックスを回転塗布し、その上部にハンダ材でなる第1のメタルボール200を自動搭載する。続いて、図5(A)に示すように、熱処理をするとメタルボール200が多少フローされて再配線層18とへこみ部40に溶着した球状ポスト20が形成される。

【0040】

その後、再配線層18をマスクにイオンミーリング等を用いて不要領域のシード層16と密着層15を選択除去することで、再配線が各々分離される。

【0041】

次に、図5(B)に示すように、モールド装置でエポキシ等の封止樹脂21で球状ポスト20を充分覆うように封止した後、グラインダーで、該ポスト20を露出させ、且つポスト20が封止樹脂21で上面から包まれるかたちをなすように研削し、ハンダ材でなる第2のメタルボール220を自動移載機で必要な球状ポスト20上に配置し、170〜200℃程度のベルト炉を用いて熱処理させると、球状ポスト20と溶着した外部端子22が形成される。第1のメタルボール200の大きさは直径が100〜150μm,第2のメタルボール220の大きさは150〜300μm径を用いたが、用途によって特に限定されるものではない。

【0042】

このようにしてなる半導体装置は、第1のメタルボールの搭載アライメント誤差が数〜10μm位あっても、へこみ部40が第1のメタルボール200のガイドとなって、ポスト20の想定座標位置に落とし込み配列することができる。更にフラックスを塗布する場合は、へこみ部40がフラックス溜りとなるため、塗布厚みを従来の1/2以下にしても、密着性や形状等に問題は発生しなかった。

【0043】

又、へこみ部40の効果として、熱処理装置のばらつきで温度が高くなってしまった場合に再配線層18の表面をハンダが流れてしまうような現象がなくなり、更に再配線層18とポスト20との密着面積が増し強度も大きくなった。このように、工程を増加することなく、ポストの密着強度や形状の安定化と、フラックスコスト低減が可能となり、量産性の半導体装置を提供できた。更にポストを持たず、直接外部端子を再配線層から取り出すような構造を採る場合にも、このへこみ部40の形成は、フラックスの溜り,あるいはハンダ材の位置や形状安定化に有効であった。

【0044】

この他、実施の形態ではポストや外部端子となるメタルボールは、ハンダ材を用いたが、図6に示すように、内部に融点の高いNi核50を含み、外周が従来のハンダ材で覆われたボールを試作適用した結果、従来の場合に比べポスト20や外部端子22の形状の安定化が図れた。マザーボードへCSPを装着する工程においては、ハンダ溶着の際に核の浮遊運動によ、外部端子に高さがばらついても確実な接触と固定が確保され、その結果溶着圧力や温度制御マージンが広がり、組み立て歩留まりの向上が図れた。

【0045】

尚、これまで説明した実施の形態においては、半導体装置の配線がAl合金で構成された場合について説明したが、Cuや高融点金属材料もしくはそれらの積層や合金配線層で形成されたものでも可能で、さらに配線層の形成がダマシン法で行われる半導体装置にも適用できる。特にCuを用いたダマシン配線にCuやNiの再配線を形成する場合は、平坦性やパッド材との密着相性が良好である。

【0046】

又、実施例でのメタルボールは、Pb/Sn系ハンダのほかに、Pbを含まないハンダ材としてSnにAg、CuやBi等を含む組成のハンダの適用も可能であり、更にハンダ意外の材料として、Ni,Cu,Auやその他高融点金属、あるいは各種合金を素材とするボールの適用も可能である。

【0047】

更に、各メタルボールを溶着するにあたってはベルト炉を用いていたが、ボール自動移載機において、基板を加熱しながらボ−ル搭載と同時に加熱処理を行ない、続けて溶着することもできる。

【0048】

【発明の効果】

以上のように、本発明によれば、ウエーハレベルのCSPにおて、搭載されたメタルボールによって球状ポスト及び外部端子が形成され、更に該ポストを封止樹脂で包むかたちとして、再配線からポストおよび外部端子強度を大きくし信頼性の高い半導体装置を低コストで供給することができる。更にハンダ外部端子内部に、該ハンダ材より高い融点の金属核を保有させることや、球状ポスト直下の再配線層に、メタルボールの配列ガイドのためのへこみ部を形成すること等により、更に各構成部材の形状ばらつきを抑え、CSPをマザーボードへ装着する際の歩留まり向上や、半導体素子へ加わる応力緩和が図れ、信頼性が高く量産性に富んだ微細CSP型の半導体装置を供給できる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係わる半導体装置の断面構造面である。

【図2】本発明の第1の実施の形態に係わる半導体装置の製造方法の一例を工程順に示す断面構造図である。

【図3】図2に示す工程に続いて行われる本発明の第1の実施の形態に係わる半導体装置の製造方法の一例を工程順に示す断面構造図である。

【図4】本発明の他の実施の形態に係わる半導体装置の製造方法の一例を工程順に示す断面構造図である。

【図5】図4に示す工程に続いて行われる本発明の他の実施の形態に係わる半導体装置の製造方法の一例を工程順に示す断面構造図である

【図6】本発明の更に他の実施の形態に係わる半導体装置を示す断面構造図である。

【図7】従来の半導体装置の製造方法の一例を工程順に示す断面構造図である。

【図8】図7に示す工程に続いて行われる従来の半導体装置の製造方法の一例を工程順に示す断面構造図である。

【符号の説明】

11 シリコン基板

12 パッド

13 保護絶縁層

14 ポリイミド層

15 密着層

16 シード層

17、19、170 レシスト

18 再配線層

20 球状ポスト

21 封止樹脂

22 外部端子

30 Cuポスト

31 バリア層

40 へこみ部

50 核

200 第1のメタルボール

220 第2のメタルボール

Claims (8)

- (a)パッド及び前記パッド部が開孔されている保護絶縁層を有する半導体ウエハーの前記保護絶縁層上に応力緩和層を形成する工程

(b)前記パッドから前記応力緩和層上に至るまで再配線層を施す工程

(c)前記再配線層に球状ポストとなるメタルボールを搭載する工程

(d)樹脂にて封止を行った後に、前記樹脂の所望量を除去し前記球状ポストの一部を露出させる工程

(e)露出した前記球状ポストの上に外部端子を形成する工程

を有し、前記工程(e)において、前記外部端子は前記球状ポストより融点の低い組成材料でなることを特徴とする半導体ウエハーの製造方法。 - 請求項1において、

前記工程(d)において、前記樹脂の除去量は、上面から球状ポストの最大径に達するまでとすることを特徴とする半導体ウエハーの製造方法。 - 請求項1において、

前記工程(e)の後に、ダイシングを施してチップ毎に固片化する工程をさらに有することを特徴とする半導体ウエハーの製造方法。 - チップサイズパッケージ型の半導体装置であって、

パッド及び前記パッド部が開孔されている保護絶縁層を有する基板の前記保護絶縁層上に形成された応力緩和層と、

前記パッドから前記応力緩和層上に至るまで形成された再配線層と、

前記再配線層の所望領域に封止樹脂で一部を囲まれたメタルボールでなる球状ポストと、

前記球状ポストの上に形成された外部端子と、

を有し、

前記外部端子は、前記球状ポストより融点の低い組成材料でなることを特徴とする半導体装置。 - 請求項4において、

前記半導体装置は、半導体ウエハーであることを特徴とする半導体装置。 - 請求項4において、

前記球状ポスト及び前記外部端子は、搭載メタルボールで形成されていることを特徴とする半導体装置。 - 請求項6において、

前記球状ポスト及び前記外部端子を構成する搭載メタルボールは、ハンダ材で形成されていることを特徴とする半導体装置。 - 最終配線パッドから電極引き出し用の再配線層において、ポストあるいは外部端子が搭載される領域の再配線層の膜厚の一部が、再配線層を主体的に形成する厚みより薄くなっていることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000055864A JP3750468B2 (ja) | 2000-03-01 | 2000-03-01 | 半導体ウエハーの製造方法及び半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000055864A JP3750468B2 (ja) | 2000-03-01 | 2000-03-01 | 半導体ウエハーの製造方法及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001244287A JP2001244287A (ja) | 2001-09-07 |

| JP3750468B2 true JP3750468B2 (ja) | 2006-03-01 |

Family

ID=18576914

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000055864A Expired - Fee Related JP3750468B2 (ja) | 2000-03-01 | 2000-03-01 | 半導体ウエハーの製造方法及び半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3750468B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4626008B2 (ja) * | 2000-04-04 | 2011-02-02 | 日本テキサス・インスツルメンツ株式会社 | 半導体装置 |

| JP4126891B2 (ja) | 2001-08-03 | 2008-07-30 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| JP4215571B2 (ja) * | 2002-06-18 | 2009-01-28 | 三洋電機株式会社 | 半導体装置の製造方法 |

| US7207096B2 (en) * | 2004-01-22 | 2007-04-24 | International Business Machines Corporation | Method of manufacturing high performance copper inductors with bond pads |

| US7068138B2 (en) | 2004-01-29 | 2006-06-27 | International Business Machines Corporation | High Q factor integrated circuit inductor |

| JP4972280B2 (ja) * | 2004-12-09 | 2012-07-11 | ローム株式会社 | 半導体装置 |

| JP5017872B2 (ja) | 2006-02-06 | 2012-09-05 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| US7834449B2 (en) * | 2007-04-30 | 2010-11-16 | Broadcom Corporation | Highly reliable low cost structure for wafer-level ball grid array packaging |

| KR20090047862A (ko) | 2007-11-08 | 2009-05-13 | 삼성전기주식회사 | 웨이퍼 레벨 패키지 제조방법 |

| DE102009016594A1 (de) * | 2009-04-08 | 2010-10-14 | Pac Tech-Packaging Technologies Gmbh | Kontaktanordnung zur Substratkontaktierung |

| JP2010183122A (ja) * | 2010-05-27 | 2010-08-19 | Texas Instr Japan Ltd | 半導体装置及びその製造方法 |

| JP6100480B2 (ja) | 2012-07-17 | 2017-03-22 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US10276481B2 (en) * | 2017-06-26 | 2019-04-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Package structure having a plurality of conductive balls having narrow width for the ball waist |

| WO2021085180A1 (ja) | 2019-10-30 | 2021-05-06 | 株式会社村田製作所 | 電子部品モジュール、および、電子部品モジュールの製造方法 |

| CN114284158A (zh) * | 2021-12-06 | 2022-04-05 | 立讯电子科技(昆山)有限公司 | 一种双面封装结构及其制作方法 |

-

2000

- 2000-03-01 JP JP2000055864A patent/JP3750468B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001244287A (ja) | 2001-09-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2001244372A (ja) | 半導体装置およびその製造方法 | |

| JP4126891B2 (ja) | 半導体装置の製造方法 | |

| JP3750468B2 (ja) | 半導体ウエハーの製造方法及び半導体装置 | |

| JP4809957B2 (ja) | 半導体装置の製造方法 | |

| JP4131595B2 (ja) | 半導体装置の製造方法 | |

| US6479900B1 (en) | Semiconductor device and method of manufacturing the same | |

| US11996383B2 (en) | Bonded semiconductor devices and methods of forming the same | |

| US6583039B2 (en) | Method of forming a bump on a copper pad | |

| CN105390473A (zh) | 集成电路装置及封装组件 | |

| JP3672297B2 (ja) | 半導体装置の製造方法 | |

| JP2003051569A (ja) | 半導体装置及びその製造方法 | |

| US8294266B2 (en) | Conductor bump method and apparatus | |

| US20240395639A1 (en) | Semiconductor package including test line structure | |

| JP3904496B2 (ja) | 半導体装置の製造方法 | |

| US6876077B2 (en) | Semiconductor device and its manufacturing method | |

| KR20070077686A (ko) | 비한정형 범프 패드를 갖는 웨이퍼 레벨 칩 스케일 패키지및 그의 제조 방법 | |

| US6929971B2 (en) | Semiconductor device and its manufacturing method | |

| US10867849B2 (en) | Package-on-package structure | |

| JP2000195862A (ja) | 半導体装置およびその製造方法 | |

| JP2001007135A (ja) | 半導体装置の製造方法 | |

| JP4462664B2 (ja) | チップサイズパッケージ型の半導体装置 | |

| JP2004273592A (ja) | 半導体装置及びその製造方法 | |

| JP2007258629A (ja) | チップサイズパッケージの製造方法 | |

| JP2003332417A (ja) | 半導体チップの製造方法 | |

| JP2004134709A (ja) | 半導体装置及びその製造方法、回路基板並びに電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040827 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040831 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041101 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20051128 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091216 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101216 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101216 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111216 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111216 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121216 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121216 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131216 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |