CN1267915A - 非易失性半导体存储装置及其制造方法 - Google Patents

非易失性半导体存储装置及其制造方法 Download PDFInfo

- Publication number

- CN1267915A CN1267915A CN00104074A CN00104074A CN1267915A CN 1267915 A CN1267915 A CN 1267915A CN 00104074 A CN00104074 A CN 00104074A CN 00104074 A CN00104074 A CN 00104074A CN 1267915 A CN1267915 A CN 1267915A

- Authority

- CN

- China

- Prior art keywords

- film

- technology

- memory cell

- peripheral circuit

- mentioned

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 101

- 238000000034 method Methods 0.000 title claims abstract description 96

- 230000002093 peripheral effect Effects 0.000 claims abstract description 188

- 230000003647 oxidation Effects 0.000 claims abstract description 102

- 238000007254 oxidation reaction Methods 0.000 claims abstract description 102

- 238000007667 floating Methods 0.000 claims abstract description 81

- 238000004519 manufacturing process Methods 0.000 claims abstract description 65

- 230000008569 process Effects 0.000 claims abstract description 18

- 239000012212 insulator Substances 0.000 claims abstract description 13

- 238000009413 insulation Methods 0.000 claims abstract description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 140

- 229920005591 polysilicon Polymers 0.000 claims description 139

- 238000005516 engineering process Methods 0.000 claims description 135

- 239000000758 substrate Substances 0.000 claims description 103

- 229910052710 silicon Inorganic materials 0.000 claims description 81

- 239000010703 silicon Substances 0.000 claims description 81

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 80

- 210000003323 beak Anatomy 0.000 claims description 56

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 48

- 230000015572 biosynthetic process Effects 0.000 claims description 31

- 229910052757 nitrogen Inorganic materials 0.000 claims description 24

- 230000007797 corrosion Effects 0.000 claims description 20

- 238000005260 corrosion Methods 0.000 claims description 20

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 16

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 16

- 230000008878 coupling Effects 0.000 claims description 13

- 238000010168 coupling process Methods 0.000 claims description 13

- 238000005859 coupling reaction Methods 0.000 claims description 13

- 239000012535 impurity Substances 0.000 claims description 13

- 238000000926 separation method Methods 0.000 claims description 13

- 230000009471 action Effects 0.000 claims description 9

- 230000001590 oxidative effect Effects 0.000 claims description 6

- UMVBXBACMIOFDO-UHFFFAOYSA-N [N].[Si] Chemical compound [N].[Si] UMVBXBACMIOFDO-UHFFFAOYSA-N 0.000 claims description 5

- 230000013011 mating Effects 0.000 claims description 3

- 238000003491 array Methods 0.000 claims description 2

- 238000005513 bias potential Methods 0.000 claims description 2

- 238000005530 etching Methods 0.000 abstract description 8

- 241000293849 Cordylanthus Species 0.000 abstract 3

- 239000010410 layer Substances 0.000 description 68

- 229910052581 Si3N4 Inorganic materials 0.000 description 28

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 28

- 238000003860 storage Methods 0.000 description 27

- 230000000694 effects Effects 0.000 description 16

- 150000004767 nitrides Chemical class 0.000 description 16

- 238000001039 wet etching Methods 0.000 description 13

- 239000012528 membrane Substances 0.000 description 12

- 238000005452 bending Methods 0.000 description 11

- 238000001259 photo etching Methods 0.000 description 8

- 230000005684 electric field Effects 0.000 description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 description 5

- 239000012141 concentrate Substances 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 230000003071 parasitic effect Effects 0.000 description 5

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- 239000007800 oxidant agent Substances 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 239000006185 dispersion Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 238000001035 drying Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 230000036632 reaction speed Effects 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000003628 erosive effect Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 230000008676 import Effects 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229940062097 nitrogen 90 % Drugs 0.000 description 1

- 238000006213 oxygenation reaction Methods 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/42—Simultaneous manufacture of periphery and memory cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

非易失性半导体存储装置,在填埋STI槽之前,比存储单元部分更大地形成周边电路部分的元件区上端部的鸟嘴氧化膜。具体地讲,在加入鸟嘴的氧化工艺之前,首先形成周边电路部分的STI槽,预先较大地形成周边电路元件区端部的鸟嘴。或者在周边电路部分的STI侧壁上形成氮氧化膜,防止氧化膜腐蚀时的侧壁绝缘膜的膜减少。防止形成非易失性存储器周边电路部分中的寄生晶体管,抑制了待机时的消耗电流。

Description

本发明涉及在同一个芯片上集成具有控制栅极和浮置栅极的叠层栅极型存储单元及其周边电路的非易失性半导体存储装置及其制造方法,特别涉及与浮置栅极用多晶硅层自匹配地形成槽元件分离,而且抑制在周边电路部分的晶体管中发生弯折效应的非易失性半导体存储装置及其制造方法。

在同一个芯片上集成了具有控制栅极和浮置栅极的叠层栅极型存储单元以及驱动该存储单元的周边电路的非易失性半导体存储装置已为人们熟知。一般在这样的半导体存储装置中,与浮置栅极用多晶硅膜层自匹配地形成槽元件分离(浅槽隔离:STI),对于周边电路的晶体管,在除去该浮置栅极用的多晶硅以后,进行再次栅极氧化以及电极形成。

在去除该浮置栅极用多晶硅时,露出周边电路元件区的端部,然后在其元件区域上形成的栅极电极有时落入并形成到元件区的上部侧面。如果发生了这样的栅极电极的落入,则在元件区侧面部分形成寄生晶体管,在MOSFET的漏极电压电流特性曲线中,将发生重叠了起因于该寄生晶体管的低阈值的特性曲线的所谓弯折效应。如果发生了该弯折效应,则将导致存储器待机时电流增大等的问题。

为了防止这样的弯折效应,需要预先在元件区与多晶硅层之间形成大量的鸟嘴。特别是,如果从浮置栅极在硅衬底上进行抽出电子的动作,则在形状变化了的部分将发生电场集中,带来各个单元的清除速度的分散。该清除速度的分散导致清除Vth分布幅度扩大,在NOR型闪速存储器中引起过清除的问题。然而,在存储单元中如果仅进行没有成为鸟嘴程度的氧化,则在周边电路部分中栅极电极落入到STI中将发生弯折效应。这样,伴随周边电路的亚阈值漏泄的增大,将增加半导体存储装置待机时的消耗电流。

参照图24A~24B至图26A~26C详细地说明以上的问题。

在硅衬底101上形成了隧道氧化膜102以后,淀积构成浮置栅极的下层部分的第1多晶硅层103(图24A)。接着,为了形成元件分离区,形成浅槽(STI区)104(图24B)。这时, 自匹配地形成浮置栅极的端部与STI,浮置栅极不会落入STI槽中,难以发生存储单元的动作分散。在该STI区域内埋入绝缘膜1055,接着,在淀积了成为浮置栅极的上层部分的第2多晶硅层106以后,在各个单元进行分离(图24C)。

接着,在其上面,形成浮置栅极与以后形成的控制栅极之间的绝缘膜107。通常是氧化膜/氮化膜/氧化膜的三层构造(图24D)。从下一个图开始示出周边电路部分的形成工艺。

去除周边电路部分的绝缘膜107,浮置栅极103、106,隧道氧化膜102。在除去该隧道氧化膜的湿法腐蚀工艺中,有时STI端部的埋入绝缘膜105退缩而发生坑洼的情况。在该情况下,周边电路的栅极电极108如图25所示,覆盖到AA(有源区)区域侧面的同时,在引起发生电场集中的AA边缘栅极电极重叠,形成寄生晶体管。该寄生晶体管具有低阈值特性,这将重迭到主晶体管的漏极电压·电流特性上发生弯折效应。

作为防止这一点的方法,如图26A所示那样,具有在形成STI204内的埋入绝缘膜205之前,充分地进行氧化,在第1多晶硅膜203与硅衬底201的界面上预先形成鸟嘴的方法。如果这样做,则在周边电路部分中,在去除了多晶硅膜和隧道氧化膜以后,也如图26B所示那样,能够防止在STI端部中的绝缘膜的退缩。多晶硅层206是成为浮置栅极的上层部分的第2多晶硅层。207是绝缘膜,208是多晶硅层。

然而,如果进行这样充分的氧化,已知将发生很大的问题。即,如图26C所示,如果在存储单元区的浮置栅极203与硅衬底202之间很大地侵入鸟嘴,则由于多晶硅层的面方位是多样的因此形状将分散,而且通过氧化将出现凸形形状,在这里集中电场。如果发生了这样的形状分散,例如,将发生在从浮置栅极进行了抽出电子的动作时的抽出速度的差异,引起消除Vth分布扩展这样的问题。广泛的消除分布在NOR型闪速存储器中将带来所谓过清除的动作不良。

如上述那样,在以往的STI型非易失性半导体存储装置中,为了抑制周边电路晶体管的弯折效应,有时在多晶硅与硅衬底界面上加大形成鸟嘴。然而,这将在存储单元部分的浮置栅极与硅衬底之间也大量侵入鸟嘴,因此发生从浮置栅极进行了抽出电子动作时的抽出速度的差异,产生清除Vth分布扩展这样的问题。

本发明是鉴于上述问题而产生的,目的在于提供存储单元部分的特性分散少,而且在周边电路部分中不发生弯折效应,从而不增大待机时消耗电流的非易失性半导体存储装置及其制造方法。

为了达到上述目的,本发明的一个形态的非易失性半导体存储装置的制造方法是以槽型元件分离形成元件区,而且具有包括浮置栅极的存储单元部分及其周边电路部分的非易失性半导体存储装置的制造方法,特征在于具有在硅衬底上经由绝缘膜形成多晶硅层的工艺;为了形成元件区,自匹配地把该多晶硅层与绝缘膜、硅衬底进行刻蚀,在硅衬底中形成具有底部并且包围元件区的元件分离用槽的多个槽的工艺;通过氧化把元件区与多晶硅层相对的面的每一个端部进行圆加工的工艺;用具有耐氧化性的膜覆盖存储单元部分的工艺;在上述耐氧化膜的形成以后添加氧化,在周边电路部分的元件区,在硅衬底与多晶硅层相对的面的端部之间形成比存储单元部分厚的鸟嘴形氧化膜的工艺。

在上述的制造方法中,在淀积了上述耐氧化膜以后,在进行对于周边电路部分的氧化之前,在存储单元部分中,进而还可以具有选择性地去除上述耐氧化膜的工艺,使得仅在浮置栅极侧面部分残留耐氧化膜。

另外,还可以在进行了对于周边电路部分的氧化以后,去除覆盖存储单元部分的耐氧化膜。

为了达到上述目的,本发明的另一个形态的半导体存储装置的制造方法是以槽型元件分离形成元件区,而且具有包括浮置栅极的存储单元部分及其周边电路部分的非易失性半导体存储装置的制造方法,特征在于具有在硅衬底上经由绝缘膜叠层形成多晶硅层的工艺;仅在周边电路部分自匹配地腐蚀多晶硅层和绝缘膜、硅衬底,形成第1元件分离用槽的工艺;在周边电路部分,把元件区与多晶硅层相对的面的每一个端部进行氧化,形成鸟嘴形氧化膜的工艺;自匹配地腐蚀存储单元部分的多晶硅层和绝缘膜、硅衬底,形成第2元件分离用槽的工艺;在第2元件分离用槽形成以后,把上述存储单元部分的元件区与多晶硅层相对的面的每一个端部进行氧化,形成比在周边电路部分中形成的鸟嘴形氧化膜更薄的鸟嘴形氧化膜的工艺。

为了达到上述目的,本发明的另一个形态的非易失性半导体存储装置的制造方法是以槽型元件分离形成元件区,而且具有包括浮置栅极的存储单元部分及其周边电路的非易失性半导体存储装置的制造方法,特征在于具有在硅衬底上经由绝缘膜叠层形成耐氧化膜的工艺;选择性地去除存储单元部分的耐氧化膜和绝缘膜的工艺;在存储单元部分上形成隧道氧化膜,然后将其进行氮化处理把隧道膜构成氮氧化膜的工艺;在存储单元部分的隧道氮氧化膜的上部以及周边电路部分的耐氧化膜的上部,形成多晶硅层的工艺;自匹配地腐蚀多晶硅与硅衬底,形成元件分离用的槽的工艺;在元件分离用槽形成以后通过氧化在元件区与多晶硅层相对的面的端部之间形成鸟嘴形氧化膜,在周边电路部分中形成比存储单元部分更厚的鸟嘴形氧化膜的工艺。

为了达到上述目的,本发明的另一个实施形态的非易失性半导体存储装置的制作方法是以槽型元件分离形成元件区,而且具有包括浮置栅极的存储单元部分及其周边电路部分的非易失性半导体存储装置的制造方法,特征在于具有在硅衬底上经由绝缘膜形成多晶硅层的工艺;自匹配地腐蚀该多晶硅层与硅衬底,为了形成元件区形成元件分离用槽的工艺;通过氧化,把元件区与多晶硅的相对的各个面的端部进行圆加工的工艺;用硅膜仅覆盖存储单元部分的工艺;在上述硅膜的覆盖以后添加氧化,在周边电路部分的硅衬底与对多晶硅层相对表面的端部之间,形成比存储单元更厚的鸟嘴形氧化膜的工艺;把覆盖存储单元部分的硅膜做成氧化膜的工艺。

为了达到上述目的,本发明的另一个形态的非易失性半导体存储装置的特征在于具有半导体衬底;形成了多个存储单元的上述半导体衬底上的存储单元部分;形成了控制上述存储单元的电路的上述半导体衬底上的周边电路部分;分别形成在上述存储单元部分与周边电路部分中,由多个槽分离了的多个元件区;形成在上述槽内壁的氮氧化膜;填埋上述槽的绝缘膜;在上述周边电路的元件区上,经由用上述氮氧化膜规定了端部的栅极绝缘膜形成的栅极电极。

本发明的另一个形态的半导体存储装置的制造方法的特征在于具有在硅衬底上形成绝缘膜与成为浮置栅极的多晶硅层的工艺;自匹配地腐蚀该多晶硅层与硅衬底,形成元件分离用槽的工艺;在槽的内壁以及多晶硅的侧壁形成硅氮氧化膜的工艺。

在该制造方法中,在槽的内壁以及多晶硅的侧壁形成硅氮氧化膜的工艺也可以是在槽的内壁以及多晶硅层的侧壁形成了硅氮化膜以后施加氮氧化处理,形成氮氧化膜的工艺。

本发明的另一个形态的半导体存储装置的特征在于具有形成多个半导体存储单元晶体管,由埋入元件分离区把上述存储单元晶体管的元件区绝缘分离的存储单元阵列区;形成多个存储单元阵列的周边电路晶体管,由埋入元件分离区把上述周边电路晶体管的元件区绝缘分离的周边晶体管区,上述周边电路晶体管区的元件区端部的曲率设定为实质上比上述存储单元晶体管的元件区端部的曲率大。

在该半导体装置中,上述元件区的平坦部分的高度与位于其上部的栅极电极的最低部分的高度的差可以是4nm以上。

另外,在该半导体装置中,上述周边电路晶体管的动作为待机状态时可以提供流过亚阈值电流的偏置电位。

另外,在该半导体装置中,上述存储单元晶体管的栅极电极的至少一部分也可以与上述存储单元阵列区中的埋入元件分离区进行自匹配。

另外,在该半导体存储装置中,上述存储单元晶体管可以是具有浮置栅极的非易失性半导体存储器的存储单元。

本发明的另一个形态的半导体装置的制造方法是在元件分离形成工艺之前形成MOS晶体管的栅极绝缘膜的一部分,在元件分离区形成工艺之后形成上述栅极绝缘膜的其它部分的半导体装置的制造中,特征在于形成MOS晶体管,使得在上述元件分离形成工艺以后形成栅极绝缘膜的MOS晶体管的元件区端部的曲率与在上述元件分离形成工艺之前形成的栅极绝缘膜的MOS晶体管的元件区端部的曲率相比较实质地加大。

本发明的另一个形态的半导体装置的制造方法是在具有存储单元阵列区以及形成了其周边电路晶体管的周边晶体管区的非易失性半导体存储器的制造中,特征在于具有在半导体衬底的整个面上形成存储单元晶体管用的第1栅极绝缘膜,在其上面形成多晶硅膜以及绝缘膜的工艺;在上述绝脂膜、多晶硅膜、第1栅极绝缘膜以及半导体衬底上形成元件分离区形成用槽的工艺;在覆盖了上述存储单元阵列区的基础上,去除周边晶体管区的元件区端部上的第1栅极绝缘膜的工艺;把上述槽的表面以及周边晶体管区中的元件区端部与其上面的多晶硅膜之间部分的表面进行氧化的工艺;在上述槽中把埋入绝缘体埋入,使整个面平坦的工艺;去除上述多晶硅膜上的绝缘膜的工艺;在去除了上述周边晶体管区的多晶硅膜以及第1栅极绝缘膜以后,形成周边电路晶体管用的第2栅极绝缘膜的工艺;在上述存储单元阵列区中形成作为浮置栅极具备了上述多晶硅膜的叠层栅极构造,在上述周边晶体管区在上述第2栅极绝缘膜上形成栅极电极的工艺;在衬底表层部分选择性地掺杂构成晶体管的源/漏的杂质的工艺。

本发明的另一个形态的半导体装置的制造方法是在具有存储单元阵列区以及形成了其周边电路晶体管的周边晶体管区的非易失性半导体存储器的制造中,特征在于在半导体衬底的整个面上形成存储单元晶体管用的第1栅极绝缘膜,在其上面形成多晶硅膜的工艺;在上述多晶硅膜、第1栅极绝缘膜以及半导体衬底上形成元件分离区形成用槽的工艺;在上述槽中把埋入绝缘体埋入,使整个面平坦的工艺;在衬底整个面上形成存储单元晶体管的浮置栅极·控制栅极间绝缘用的栅极间绝缘膜的工艺;去除上述周边晶体管区的栅极间绝缘膜、多晶硅膜以及第1栅极绝缘膜使元件区露出的工艺;把上述在周边晶体管区露出的元件区端部的角部进行腐蚀形成具有圆形形状的工艺;在上述周边晶体管区中形成上述周边电路晶体管用的第2栅极绝缘膜的工艺;在上述存储单元阵列区中形成作为浮置栅极具备了上述多晶硅膜的叠层栅极构造,在周边晶体管区中在上述第2栅极绝缘膜上形成栅极电极的工艺;在衬底表层部分掺入构成晶体管的源/漏的杂质的工艺。

图1A~1D是阶段性地示出本发明第1实施例的半导体存储装置的制造方法的剖面图。

图2A~2C是示出连接在图1D以后的工艺的剖面图。

图3A~3C是示出连接在图2C以后的工艺的剖面图。

图4A~4C是示出连接在图3C以后的工艺的剖面图。

图5是示出连接在图4C以后的工艺的剖面图。

图6是用于说明本发明第2实施例的半导体存储装置的制造方法的剖面图。

图7A~7C是阶段性地示出本发明第3实施例的半导体存储装置的制造方法的剖面图。

图8A,8B是示出连接在图7C以后的工艺的剖面图。

图9A~9D是阶段性地示出本发明第4实施例的半导体存储装置的制造方法的剖面图。

图10A~10C是示出连接在图9D以后的工艺的剖面图。

图11A~11D是阶段性地示出本发明第5实施例的半导体存储装置的制造方法的剖面图。

图12A~12C是示出连接在图11D以后的工艺的剖面图。

图13A~图13C是示出连接在图12C以后的工艺的剖面图。

图14A~14D是示出连接在图13C以后的工艺的剖面图。

图15A~15D是阶段性地示出本发明第6实施例的半导体存储装置的制造方法的剖面图。

图16A~16C是示出连接在图15D以后的工艺的剖面图。

图17A~17D是示出连接在图16C以后的工艺的剖面图。

图18A~18D是阶段性地示出本发明第7实施例的半导体存储装置的制造方法的剖面图。

图19A~19D是示出连接在图18D以后的工艺的剖面图。

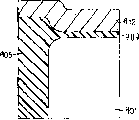

图20A,20B是分别放大地示出图2C中用○表示部分的形状一例以及该部分的器件完成以后的形状一例的剖面图。

图21A~21C是示出本发明第8实施例的NOR型闪速EEPROM的部分制造工艺的剖面图。

图22A~22D是示出连接在图21C以后的部分工艺的剖面图。

图23是放大地示出图22C中用○表示部分的形状一例的剖面图。

图24A~24D是阶段性地示出以往的半导体存储装置的制作方法的剖面图。

图25是用于说明在以往的半导体装置中发生的寄生晶体管的剖面图。

图26A~26C是用于说明在以往的半导体存储装置中,形成鸟嘴的方法及其问题点的剖面图。

发明实施例

以下,参照附图说明本发明的实施例。

第1实施例

图1A~1D至图5阶段性地示出本发明第1实施例的半导体存储装置的制作方法,是周边电路部分的剖面图。

首先,在硅衬底301的整个面上形成例如10nm的存储单元的隧道氧化膜302。接着,在其上部形成70nm的构成浮置栅极的下层部分的第1多晶硅层303(图1A)。进而,在其上面通常例如淀积200nm的硅氮化膜304。然后通过光刻工艺形成把STI的槽形成部分开口了的抗蚀剂图形,根据该抗蚀剂图形加工硅氮化膜304(图1B)。

接着,把该氮化膜304作为掩模,根据RIE法顺序地垂直刻蚀第1浮置栅极用多晶硅膜303、隧道氧化膜302、硅衬底301。在硅衬底301上挖出的浅槽305是元件分离用的槽(浅槽隔离:STI)。

其次,在成为浮置栅极的第1多晶硅303与硅衬底301的界面,进行抑制为尽可能少的氧化量的氧化使得鸟嘴不过于进入,例如,10nm的热氧化工艺。由此,形成热氧化膜306(图1C)。

其次,用CVD法在其上面很薄地淀积氧化膜307。进而在其上面例如淀积6nm的耐氧化膜,具体地讲是硅氮化膜408(图1D)。

其次,通过光刻工艺在衬底上形成仅在周边电路部分开口了的抗蚀剂图形309(图2B)。以该抗蚀剂图形309为掩模去除周边电路部分的耐氧化膜308(图2B)。例如如果是硅氮化膜则可以用CDE(化学干法腐蚀)等方法去除。另外在耐氧化膜的下方形成的CVD氧化膜307,以后在STI内部淀积埋入绝缘膜的情况下还起到减轻进入到硅衬底中的损伤的作用。

其次,在周边电路部分的元件区(硅衬底301)与第1多晶硅膜303的各个相对面的端部进行用于使鸟嘴进入的氧化(图2C)。通过该氧化形成的鸟嘴310以后在周边电路形成时可以降低栅极电极的落入。从而该氧化以充分的,例如在硅衬底上形成30nm的氧化膜的条件进行。

这时,存储单元部分用耐氧化膜308覆盖不被氧化。从而,存储单元部分的元件区(硅衬底301)与第1多晶硅层303的每一个的相对面端部上不形成鸟嘴。从而,与存储单元部分的元件区的曲率相比较,可以实质性地加大周边电路部分的元件区的曲率。另外,根据需要也可以在以后去除耐氧化膜。如果在存储单元附近存在硅氮化膜,则由于从这里扩散的氢存在着隧道氧化膜受到损伤的可能性,因此如果需要也可以去除,而在本例中示出没有去除的情况。另外,在去除硅氮化膜时,在图1D的工艺以后,可以用由热磷酸进行腐蚀或者CDE(化学干法腐蚀)去除。

接着,为了把STI内部进行填埋,例如淀积等离子体氧化膜311(图3A)。在高宽比高的情况下,使用高密度等离子体(HDP)CVD法进行淀积。例如,通过CMP(化学机械抛光)法使该等离子体氧化膜311平坦(图3B)。

其次,通过湿法腐蚀去除第1浮置栅极用多晶硅膜303上的硅氮化膜304。根据具体情况,为了调节在STI内埋入的绝缘膜311的高度,有时在去除氮化膜之前把绝缘膜311多少进行腐蚀。然后,在其上面形成第2浮置栅极用多晶硅层312。进而,在STI区域上进行浮置栅极分离用区域313的刻蚀工艺以及腐蚀。由此,在每个单元生成被分离了的浮置栅极312(图3C)。

接着,在浮置栅极上形成成为浮置栅极与控制栅极间绝缘膜的例如氧化膜/氮化膜/氧化膜(ONO)的叠层绝缘膜314(图4A)。以后的图仅示出周边电路部分。

接着,通过光刻工艺用抗蚀剂覆盖存储单元区,用干法腐蚀去除周边电路区的ONO膜314,浮置栅极的第1、第2多晶硅膜303,312,用湿法腐蚀去除隧道氧化膜312(图4B)。通过充分地形成栅极鸟嘴,在该湿法腐蚀时保护元件区上端部,能够防止氧化膜落入到上部中。

接着,在周边电路的衬底表面形成氧化膜厚例如为15nm的栅极氧化膜315(图4C),然后在其上部形成多晶硅层316(图5)。加工该多晶硅层316,构成周边电路部分的栅极电极以及存储单元部分的控制栅极电极。

另外,虽然没有进行图示,然而进行周边晶体管、存储单元晶体管的栅极加工,然后如通常所进行的那样,在存储单元部分和周边电路部分形成扩散层,进而进行布线工艺。由此,完成存储单元阵列。

通过采用以上那样的工艺,实现在存储单元部分不侵入鸟嘴,仅在周边电路部分较大地侵入鸟嘴的半导体存储装置。即,与存储单元部分的元件区的曲率相比较可以实质地加大周边电路部分的元件区的曲率。

第2实施例

在第1实施例中,用硅氮化膜覆盖了存储单元区整个表面,然而如果用硅氮化膜覆盖整个表面进行热处理,则有时将产生存储单元的隧道氧化膜302的恶化。为了把这种现象抑制为最小限度,也可以在存储单元的浮置栅极的侧面侧壁形地形成耐氧化膜。第2实施例提供这样的方法。

首先,实施第1实施例中的图1A~1D的工艺。在图1D中淀积了耐氧化膜308以后,在整个面上进行由RIE实施的回腐蚀,仅在侧壁留下耐氧化膜。由此,可以得到图6所示的构造。然后,通过实施与第1实施例的图2以后相同的工艺,完成耐氧化膜仅残留在浮置栅极侧壁以及STI内壁的构造。

第3实施例

图7以及图8是阶段性地示出本发明第3实施例的半导体存储装置的制作方法的剖面图。

首先,在硅衬底501的整个面上形成例如10nm的存储单元的隧道氧化膜502。其次,在其上部形成70nm的构成浮置栅极一部分的第1多晶硅层503(图7A)。进而,通过后续的光刻工艺,仅在周边电路部分形成把形成STI的槽的部分开口了的抗蚀剂图形(未图示),加工硅氮化膜504。其次,把该氮化膜504作为掩模,根据RIE法顺序地垂直腐蚀第1浮置栅极用多晶硅层503、隧道氧化膜502、硅衬底501,形成STI 505。

接着,在周边电路部分的多晶硅层503与硅衬底501的界面进行要形成充分的鸟嘴氧化膜506的例如30nm的氧化(图7C)。这时,存储单元部分上用硅氮化膜504覆盖因而不被氧化。

接着,形成存储单元部分的STI槽507(图8A)。接着,在存储单元上进行最低限度的必要氧化,例如6~10nm的氧化,形成氧化膜508(图8B)。然后,进行与第1实施例的图3对应的对STI内部的埋入绝缘膜形成工艺。

即使根据上述的工艺,也能够实现在存储单元部分中不侵入鸟嘴,仅在周边电路部分中较大地侵入鸟嘴的半导体存储装置。即,与存储单元部分的元件区的曲率相比较能够实质地加大周边电路部分的元件区的曲率。

第4实施例

图9A~图9D,图10A~10C是阶段性地示出本发明第4实施例的半导体存储装置的制作方法的剖面图。

首先,在硅衬底601形成第1厚氧化膜例如20nm左右的氧化膜608(图9A)。接着,在其上部淀积8nm的耐氧化膜例如硅氮化膜603(图9B)。

然后,通过刻蚀工艺在周边电路部分中残留抗蚀剂604,去除存储单元部分的硅氮化膜603(图9C),进而,在去除了抗蚀剂以后腐蚀去除存储器单元部分的20nm的硅氧化膜。

接着,在存储单元部分中例如以厚度9nm形成隧道氧化膜605。在周边电路部分中由于存在耐氧化膜(硅氮化膜)603因此不发生任何变化。接着,在隧道氧化膜605与硅衬底601之间通过氮化处理导入氮(图9D)。该氮化防止在以后的工艺中鸟嘴侵入的同时,一般由于隧道氧化膜成为氮氧化物,因此将提高存储单元的可靠性。另外,这时由于用氮化膜603覆盖周边电路部分,因此第1氧化膜602与硅衬底601的界面不被氮化。氮化处理一般可以通过在氨或N2O、NO这样的气体中实施热处理进行。

其次,在其上部形成70nm的构成浮置栅极的下层部分的第1多晶硅层606(图10A)。进而,在其上面通常淀积例如200nm的硅氮化膜607。然后,通过刻蚀工艺,形成把形成STI的槽的部分开口了的抗蚀剂图形,加工该硅氮化膜607。

接着,以该硅氮化膜607为掩模,使用RIE法在周边电路部分中顺序地垂直腐蚀第1浮置栅极用多晶硅层606、硅氮化膜603、基底的第1氧化膜602和硅衬底601,在存储单元部分中顺序地垂直腐蚀第1浮置栅极用多晶硅层606、隧道氧化膜605、硅衬底601。在硅衬底上挖出的浅槽是元件分离用槽(STI)(图10D)。

接着,进行用于在周边电路部分的元件区与硅氮化膜603的界面端部使鸟嘴进入的氧化(图10C)。通过该氧化形成氧化膜609、610,由此形成的周边电路部分的鸟嘴610以后在周边电路形成时能够减少栅极电极的落入。从而,虽然进行了充分量的氧化,然而这时存储单元部分的隧道氧化膜被氮化处理,因此鸟嘴难以侵入。

另一方面,在周边电路部分中,由于在元件区上存在没有被氮化的厚硅氧化膜602,因此在硅衬底601和硅氧化膜602的界面与存储单元部分相比较可以加入厚的鸟嘴610。另外,周边电路部分的厚氧化膜602及其上部的硅氮化膜603以及606、607在形成周边电路部分的栅极氧化膜之前全部去除(相当于第1实施例的图4B的工艺)。

即使根据上述的工艺,也能够实现在存储单元部分中不侵入鸟嘴,仅在周边电路部分较大地侵入鸟嘴的半导体存储装置。即,与存储单元部分的元件区的曲率相比较能够实质地加大周边电路部分的元件区的曲率。

第5实施例

图11A~11D至图14A~14C是阶段性地示出本发明第5实施例的半导体存储装置的制造方法的剖面图。

首先,在硅衬底701的整个面上形成例如10nm的存储单元的隧道氧化膜702。接着在上部形成70nm的成为浮置栅极的下层部分的第1多晶硅层703(图11A)。

进而在其上面通常淀积例如200nm的硅氮化膜704。然后通过光刻工艺,形成把形成STI的槽的部分开口了的图形。把该硅氮化膜进行加工。接着,以该氮化膜为掩模,根据RIE法顺序地加工第1浮置栅极用多晶硅层、隧道氧化膜、硅衬底。在硅衬底上挖出的浅槽是元件分离用槽(STI)(图11B)。

接着,进行抑制为尽可能少的氧化量的氧化使得在成为浮置栅极的第1多晶硅与硅衬底的界面上不过于进入鸟嘴。例如,进行10nm的热氧化工艺。由此,形成热氧化膜706(图11C)。

接着,在其上面用CVD法淀积氧化膜707。进而在其上面形成硅膜。具体地讲,例如用减压CVD(LPCVD)法淀积10nm的非晶硅膜708(图11D)。

接着,通过光刻工艺形成仅把周边部分开口了的抗蚀剂图形709(图12A)。以该抗蚀剂材料为掩模,去除周边电路部分的硅膜708(图12)。例如,如果是非晶硅膜则能够用CDE等方法去除。另外,形成在硅膜下面的CVD氧化膜707,以后在STI内部淀积埋入绝缘膜时起到减少进入到硅衬底的损伤的作用。

接着,进行用于在周边电路的STI边缘中进入鸟嘴的氧化(图12C)。通过该氧化形成的鸟嘴710以后在周边电路形成时能够减少栅极电极的落入。从而,进行充分量的热氧化。例如,在硅衬底上以形成30nm的氧化膜的条件进行。

另一方面,存储单元部分用非晶硅膜708覆盖,在周边电路部分的元件区上端部的鸟嘴氧化时被完全氧化,非晶硅膜708成为硅氧化膜711,膜厚也成为大约2倍的20nm。

在存储单元部分中非晶硅膜708完全成为硅氧化膜711以后,氧化剂沿着硅氧化膜711扩散,把硅衬底701以及作为浮置栅极的下层部分的第1多晶硅膜703也进行氧化。

而由于氧化剂沿着硅氮化膜711扩散,进而沿着由CVD法形成的硅氧化膜706扩散,到达硅衬底701或者多晶硅膜703,因此大幅度地抑制硅衬底701以及作为浮置栅极的下层部分的第1多晶硅膜703的氧化率。从而,在该工艺中鸟嘴几乎不进入到存储单元部分的元件区上端部。

用于在周边电路部分的元件区上端部使鸟嘴进入的氧化量需要与用于存储单元部分中淀积的硅膜708完全成为硅氧化膜711的氧化量相同,而且在存储单元部分需要在元件区上端部几乎不进入鸟嘴,考虑到这些要求,设定硅氧化膜708的淀积膜厚。

其次,为了填埋STI内部,例如淀积等离子体氧化膜712(图13A)。在高宽比高的情况下,有时也使用高密度等离子体(HDP)CVD进行淀积。接着,例如通过CMP法使等离子体氧化膜平坦(图13B)。

接着,通过湿法腐蚀去除第1浮置栅极用多晶硅膜703上的硅氮化膜704。根据具体情况,有时为了调节埋入到STI内部的绝缘膜712的高度,在去除氮化膜704之前把绝缘膜712多少进行腐蚀。

然后,在衬底整个面上形成第2浮置栅极用多晶硅层713。进而,在STI区域上进行浮置栅极分离区714的刻蚀工艺以及腐蚀,进行用于在各个单元分离浮置栅极的加工(图13C)。

接着,在浮置栅极713上,形成成为浮置栅极与控制栅极间的绝缘膜,例如氧化膜/氮化膜/氧化膜(ONO)的叠层绝缘膜715(图14A)。以后仅示出周边电路部分。

接着,通过光刻工艺用抗蚀剂图形覆盖存储单元部分,用干湿腐蚀去除周边电路部分的ONO膜715、浮置栅极用的第1、第2多晶硅膜703、713,用湿法腐蚀去除隧道氧化膜(图14B)。在该湿法腐蚀时,通过充分形成栅极鸟嘴,保护元件区上端部,能够防止氧化膜落入到上端部中。

接着,在周边电路部分中形成必要氧化膜厚度的例如15nm的栅极氧化膜716(图14C),接着在其上部形成多晶硅层717(图14D)。该多晶硅层717成为周边电路部分的栅极电极以及存储单元的控制栅极。

其次,虽然省略了图示,然而进行周边晶体管、存储单元晶体管的栅极加工,然后如通常所进行的那样在存储单元部分、周边电路部分形成扩散层,进而通过进行布线工艺,完成存储单元阵列。

即使通过上述的工艺,也能够实现在存储单元部分中不侵入鸟嘴,仅在周边电路部分中较大地侵入鸟嘴的半导体存储装置。即,与存储单元部分的元件区的曲率相比较能够实质地加大周边电路部分的元件区的曲率。

第6实施例

图15A~15D至图17A~17D是阶段性地示出本发明第6实施例的半导体存储装置的制造方法的剖面图。本实施例与第1~第5实施例不同,并不是在周边电路部分的元件区上端部形成很大的鸟嘴,而是通过用氮氧化膜覆盖周边电路部分的STI侧壁,进行STI埋入绝缘膜的回腐蚀时,防止元件区的侧面露出,抑制周边电路部分的栅极电极向元件区侧面的落入。

以下,参照附图说明制造工艺,图15~图17A适用于存储单元部分与周边电路部分两方,图17B~D适用于周边电路部分。

首先,在硅衬底801的整个面上形成例如10nm的成为存储单元的隧道氧化膜的硅氧化膜802。接着,在其上部形成70nm的成为浮置栅极的下层部分的第1多晶硅层803(图15A)。

进而在其上面,通常例如淀积200nm的硅氮化膜804。然后通过光刻工艺,形成把形成STI的槽的部分开口了的抗蚀剂图形,加工该硅氮化膜。接着,以该氮化膜为掩模,通过RIE法顺序地加工第1浮置栅极用多晶硅膜、隧道氧化膜、硅衬底。在该硅衬底上挖出的浅槽是元件分离用槽(STI)(图15B)。

接着,进行抑制为尽可能少的氧化量的氧化,例如10nm的热氧化工艺,使得在成为浮置栅极的第1多晶硅与硅衬底界面上不进入鸟嘴。由此,形成热氧化膜806(图15C)。

接着,在其上面淀积例如20nm的硅氧化膜807。然后,进行把硅氧化膜806以及807改变为热氮化膜的处理(图9D)。具体地讲,在900℃的NH3的气氛中进行60分钟处理,进而在900℃的O2的气氛中进行60分钟处理。通过该处理,硅氧化膜806与硅的界面区以及硅氧化膜807的表面区成为包括几个百分比的氮的氮氧化膜。

接着,为了填埋STI内部,例如淀积等离子体氧化膜812(图16A)。在高宽比高的情况下,有时也使用高密度等离子体(HDP)CVD进行淀积。接着,例如通过CMP法使该等离子体氧化膜平坦(图16B)。

接着,通过湿法腐蚀去除第1浮置栅极用多晶硅膜803上的硅氮化膜804。根据具体情况,有时为了调节在STI内埋入的绝缘膜812的高度,在去除氮化膜804之前,把绝缘膜812多少进行腐蚀。然后,在衬底整个面上形成第2浮置栅极用多晶硅层813。进而,STI区上进行浮置栅极分离区814的刻蚀工艺以及腐蚀,进行用于在各个单元分离浮置栅极的加工(图16C)。

然后,在浮置栅极813上,形成成为浮置栅极与控制栅极间绝缘膜的例如氧化膜/氮化膜/氧化膜(ONO)的叠层绝缘膜815(图17A)。以后仅示出成为周边电路的部分。

接着,用抗蚀剂(未图示)覆盖存储单元部分,用干法腐蚀去除周边电路部分的ONO膜,第1、第2多晶硅层803、813,用湿法腐蚀去除隧道氧化膜802(图17B)。在该湿法腐蚀时,由于STI的硅侧壁以及第1浮置栅极电极202的侧面用被氮氧化了的氮氧化膜806、807覆盖,因此与隧道氧化膜802的腐蚀速度相比较这部分的腐蚀速度慢。因此,不露出元件区上部侧面。

接着,在周边电路部分形成必要氧化膜厚的例如15nm的栅极氧化膜816(图17C),接着在上部形成多晶硅层817(图17D)。该多晶硅层成为周边电路部分的栅极电极以及存储单元的控制栅极。

在本实施例中,在STI内通过氧化处理形成硅氧化膜806以后,淀积硅氧化膜807,而硅氧化膜806与807并不一定需要做成2层,也可以是由淀积膜或者基于氧化处理的单层硅氧化膜。

其次,虽然省略了图示,然而进行周边晶体管、存储单元晶体管的栅极加工,然后如通常所进行的那样在存储单元、周边电路部分中形成扩散层,进而通过进行布线工艺,完成存储单元阵列。

在本实施例中,由于周边电路部分的栅极电极形成后的元件区上端部侧面至少用形成在STI内壁的氮氧化膜覆盖,因此不会发生由氧化膜的薄膜化引起的周边晶体管的弯折效应。

如果依据第1实施例至第5实施例中公开的发明,则由于在存储单元的激活区与硅衬底之间不过大地形成鸟嘴,在周边电路部分中能够形成很大的鸟嘴,因此可以减小存储单元的特性分散。另一方面,通过在周边电路形成鸟嘴,能够防止发生MOSFET的弯折效应,能够抑制待机时消耗电流的增大。

另外,如果依据第6实施例公开的发明,则由于STI内壁用硅氮氧化膜覆盖,因此在周边电路部分剥离隧道氧化膜时能够抑制元件区上端部的绝缘膜的膜减少,同样能够防止发生MOSFET的弯折效应,能够抑制待机时消耗电流的增大。

第7实施例

图18A~18D至图19A~19D是阶段性地示出本发明第7实施例的半导体存储装置的制造方法的剖面图。

本实施例的半导体存储装置(NOR型闪速EEPROM)具有用埋入元件分离区绝缘分离了的元件区,存储单元阵列区与周边晶体管区的MOS晶体管的栅极绝缘膜的膜厚不同。

首先,如图18A所示,在半导体衬底901的存储单元阵列区即存储单元部分以及周边晶体管区即周边电路部分使各个晶体管的阈值分别成为所希望的值那样掺入了杂质以后,在衬底整个面上形成成为存储单元晶体管的隧道氧化膜的栅极绝缘膜902。然后在其上面淀积多晶硅膜903、CVD氮化膜以及CVD氧化膜的叠层膜904。

然后,在衬底上形成抗蚀剂图形(未图示),使用该图形在把上述叠层膜904图形化了以后去除上述抗蚀剂图形。

然后,如图18B所示,把上述图形化了的叠层膜904作为掩模,通过去除与元件分离区形成预定部分对应的多晶硅膜903、栅极氧化膜902、硅衬底901,形成浅槽。

另外,在用抗蚀剂(未图示)把存储单元阵列区覆盖了以后,对于周边晶体管区进行湿法腐蚀处理(或者各向同性干法腐蚀处理,或者这两种处理),如图18C所示,去除周边晶体管区的元件区上的栅极绝缘膜902的一部分(元件区端部上的部分),做成易于向元件区的端部供给氧化剂的形状。

然后,去除上述抗蚀剂,在例如温度900度~1000度,氧浓度10%的气氛中进行氧化,使得上述槽表面的氧化膜厚成为20nm以上形成氧化膜913。这时,在周边晶体管区的元件区端部和其上面的多晶硅膜903之间的部分供给氧化剂进行氧化。因此,如图18D所示那样,所谓的鸟嘴较厚地进入的同时元件区的端部成为具有圆形的形状。即,加大周边晶体管区的元件区分布的曲率。

接着,如图19A所示,在上述槽中埋入作为埋入绝缘体的例如LP-TEOS膜905。然后,使用CMP法或者回腐蚀法使整个面平坦,使埋入绝缘体退缩到绝缘膜904的中部,接着进行回腐蚀处理,去除叠层膜904。

其次,如图19B所示,在衬底的整个面上淀积作为杂质掺入了磷的多晶硅膜906,在其上面形成抗蚀剂图形(未图示),通过使用该图形把上述多晶硅膜906进行图形化,形成在元件分离区上分断存储单元阵列区的多晶硅膜906的缝隙907,去除周边晶体管区的多晶硅膜906、903。然后,剥离上述抗蚀剂图形。

其次,在衬底的整个面上形成ONO绝缘膜908,在用抗蚀剂(未图示)把存储单元阵列区覆盖的基础上,去除了周边晶体管区的ONO绝缘膜908以及栅极绝缘膜(隧道绝缘膜)902以后,去除覆盖上述存储单元阵列区的抗蚀剂。

另外,也可以在存储单元阵列区形成缝隙907时预先留下周边晶体管区的多晶硅膜906,903,在去除上述ONO绝缘膜908以及栅极绝缘膜(隧道绝缘膜)902时去除上述多晶硅膜906,903。

以下,与以往相同,如图19C所示,形成周边电路用晶体管的栅极绝缘膜909,进而,如从与图19C的正交方向观看所示的图19D那样,在衬底上的整个面上淀积掺入了杂质的多晶硅膜。

而且,在存储单元阵列区通过把上述多晶硅膜、上述ONO绝缘膜908、多晶硅膜906以及903图形化,形成控制栅极910与浮置栅极911(多晶硅膜906以及903)为2层的叠层栅极构造,在周边晶体管区通过把上述多晶硅膜图形化形成栅极电极912。接着,虽然没有图示,然而在衬底表层部分选择性地掺入成为晶体管的源/漏的杂质,进而,进行层间绝缘膜的淀积,触点开孔,布线形成,表面保护绝缘膜的淀积,完成闪速EEPROM。

图20A放大地示出与图19C中用虚线的○符号示出的部分相对应的端部(即,在形成元件分离绝缘膜以后形成栅极绝缘膜的周边晶体管区中的元件区的端部)的形状一例,图20B中放大地示出该部分的器件完成后的形状一例。这里,901是半导体衬底,905是元件分离绝缘膜,909是栅极绝缘膜,912是栅极电极。

如从图20A、20B所示那样,元件区端部上的栅极绝缘膜909由于是鸟嘴进入的形状,因此抑制在制作栅极的分割工艺时剥离工艺中元件区端部的膜减少,难以引起元件区端部的电场集中。

另外,在图20A、20B所示的周边晶体管区的元件区端部的栅极绝缘膜909上形成的栅极绝缘膜12的落入形态成为落入量少的形状。顺便指出,实际测量的结果,上述元件区的平坦部分的高度与位于其上部的栅极电极的最低部分的高度差d是4nm以上。

第8实施例

图21A~21C至图22A~22D是阶段性地示出本发明第8实施例的半导体存储装置的制造方法的剖面图。

首先如图21A所示,在半导体衬底1001的存储单元阵列区以及周边晶体管区掺入了杂质使得各个晶体管的阈值分别成为所希望的阈值以后,在衬底的整个面上形成成为存储单元晶体管的隧道氧化膜的氧化膜1002,在其上面淀积作为杂质掺入了磷的多晶硅膜1003,CVD(化学气相生长)氮化膜以及CVD氧化膜的叠层膜1004。

其次,在衬底上形成抗蚀剂图形(未图示),使用该图形,在把上述叠层膜1004图形化了以后去除上述抗蚀剂图形。

然后,如图21B所示,把上述图形化了的叠层膜1004作为掩模,通过去除对应于元件分离区形成预定部分的多晶硅膜1003、栅极绝缘膜1002、硅衬底1001,形成浅槽。

其次,如图21C所示,在上述槽中埋入作为埋入绝缘体的例如LP-TEOS(低压四乙基氧化物硅)膜1005。然后,通过CMP(化学机械抛光)法或者回腐蚀法使整个面平坦,使埋入绝缘体退缩到叠层膜1004的中部。然后,进行湿法腐蚀处理,完全去除叠层膜1004。

接着,如图22A所示,在衬底的整个面上淀积作为杂质掺入了磷的多晶硅膜1006,在其上面形成抗蚀剂图形(未图示),使用该图形把上述多晶硅膜1006图形化。这时,形成在元件分离区上把存储单元阵列区的多晶硅膜1006分断的缝隙1007,去除周边晶体管区的多晶硅膜1006、1003。然后,剥离上述抗蚀剂图形。

接着,在衬底的整个面上形成ONO绝缘膜(氧化膜/氮化膜/氧化膜的叠层膜)1008,在用抗蚀剂(未图示)覆盖存储单元阵列区的基础上,去除周边晶体管区的ONO绝缘膜1008以及栅极氧化膜(隧道氧化膜)1002以后,去除覆盖上述存储单元阵列区的抗蚀剂。

另外,也可以在存储单元阵列区中形成缝隙1007时预先留下周边晶体管区的多晶硅膜1006、1003,在去除上述ONO绝缘膜1008以及栅极氧化膜(隧道氧化膜)1002时去除上述多晶硅膜1006、1003。在这个阶段,周边晶体管区的元件区端部的角部成为露出的状态。

其次,在用抗蚀剂覆盖了存储单元阵列区的状态下,如图22B所示,通过进行湿法腐蚀处理(或者各向同性的干法腐蚀处理,或者这两种处理),把露出的元件区端部的角部进行腐蚀成为具有圆形的形状。

接着,在去除了覆盖存储单元阵列区的抗蚀剂以后,如图22C所示,与以往相同,形成周边电路用晶体管的栅极氧化膜1009,进而,如从与图22C的正交方向观看所示的图22D那样,在衬底的整个面上淀积掺入了杂质的多晶硅膜。而且,在存储单元阵列区把上述多晶硅膜、上述ONO绝缘膜1008、多晶硅膜1006以及1003图形化,形成控制栅极1010与浮置栅极1011(多晶硅膜1006以及1003)成为2层的叠层栅极构造,在上述周边晶体管区通过把上述多晶硅膜图形化形成栅极电极1012。接着,虽然没有进行图示,然而在衬底表层部分上选择性地掺入成为晶体管的源/漏的杂质,进而,进行层间绝缘膜的淀积,触点的开孔,布线形成,表面保护绝缘膜的淀积,完成闪速EEPROM。

图23放大地示出与图22C中用虚线的○符号表示的部分对应的端部(即,形成了元件分离绝缘膜以后形成栅极氧化膜的周边晶体管区中的元件区的端部)的形状一例。这里,1001是半导体衬底,1005是元件分离用绝缘膜,1009是栅极氧化膜。

如从图23所知,由于元件区的端部成为具有圆形的形状,因此抑制了以往成为问题的元件区端部的电场集中。

如果简要地叙述与第7实施例以及第8实施例相关连的以往的制造方法,则在以往的制造方法中,在形成周边晶体管区的栅极氧化膜之前的ONO膜、隧道氧化膜的去除工艺中,在元件区端部露出角部。

如此,在以往的制造方法中,由于在周边电路晶体管的动作时在元件区端部的角部中引起电场集中,增加周边电路晶体管的漏电流,增加器件的消耗电流,周边晶体管的亚阈值特性对于栅极电压成为不连续,因此成为周边电路误动作,产品的成品率下降的原因。

与此不同,在第7实施例以及第8实施例的制造方法中,(1).对于周边晶体管区的元件区端部,通过进行湿法腐蚀处理,各向同性干法腐蚀处理,氧化处理或者其复合处理,加大元件区端部的曲率,另外,(2).在周边晶体管区的元件分离形成工艺中在元件区端部引入鸟嘴。

由此,能够抑制栅极电极落入元件区端部,使得栅极电极在元件区端部不产生电场集中,抑制周边电路晶体管的漏电流,改善周边电路晶体管的亚阈值电流特性,因此能够降低产品的功耗,提高成品率。

另外,作为使露出的元件区端部的角部圆形化的方法,一般已知如果在氧化时由氧的供给决定反应速度,则角部分与平坦的部分相比较易于氧化。

因此,代替上述各实施例中的处理,在周边电路晶体管的栅极形成之前,还加入在高温而且抑制了氧供给的条件,例如1000℃,氮90%,氧10%的条件下进行氧化的工艺,能够把露出的元件区端部的角部进行圆加工,即使把周边电路晶体管的栅极氧化膜形成工艺自身采用为由供给决定反应速度的氧化方法,也能够得到同样的效果。另外,通过把这些方法进行组合当然也能够得到同样的效果。

在进行存储单元阵列区与周边晶体管区的栅极氧化膜的分离时,把在周边晶体管区中通过埋入元件分离区被绝缘分离了的元件区端部的角部进行圆加工,在抑制栅极电极从元件区跨越元件分离区形成的周边电路晶体管的弯折效应方面极为有效。

另外,第7实施例以及第8实施例公开的半导体装置制造方法能够适用于在元件分离形成工艺之前形成栅极绝缘膜的一部分,在元件分离形成工艺之后形成栅极绝缘膜的剩余部分的半导体装置的制造。

通过把元件区的端部形状进行圆加工能够抑制晶体管的栅极电压低的区域的漏电流以及消耗电流,亚阈值电流特性对于栅极电压成为连续,栅极电压低的区域中的晶体管的动作稳定,能够使产品的成品率提高。

从而,例如把第7实施例以及第8实施例适用于闪速EEPROM及其制造,则通过把周边晶体管区中的元件区端部的曲率设定为比存储单元阵列区的元件区端部的曲率大,能够减小周边电路晶体管的漏电流,减小功耗。

虽然根据以上实施例说明了本发明,然而本发明例如周边电路还可以是仅包括存储单元部分的控制电路,以及CPU等。在以上实施例中,以闪速EEPROM为例进行了说明,然而本发明并不限定于此,在不脱离不受这些限制的本发明宗旨的范围内可以采用各种变形。

Claims (17)

1.一种非易失性半导体存储装置,特征在于:

具有

半导体衬底;

形成多个存储单元的上述半导体衬底上的存储单元部分;

形成控制上述存储单元的电路的上述半导体衬底上的周边电路部分;

在上述存储单元部分和周边电路部分上分别形成的由多个槽分离了的多个元件区;

在上述槽的内壁形成的氮氧化膜;

填埋上述槽的绝缘膜;

在上述周边电路部分的元件区上,通过用上述氮氧化膜规定了端部的栅极绝缘膜形成的栅极电极。

2.一种非易失性半导体存储装置,特征在于:

具有

形成多个存储单元晶体管,由埋入元件分离区把上述存储单元晶体管的元件区绝缘分离的存储单元阵列区;

形成多个存储单元阵列的周边电路晶体管,由埋入元件分离区把上述周边电路晶体管的元件区绝缘分离的周边电路晶体管区,

与上述存储单元晶体管的元件区端部的曲率相比较实质地较大设定上述周边电路晶体管的元件区端部的曲率。

3.如权利要求2中记述的非易失性半导体存储装置,特征在于:

上述元件区的平坦部分的高度与位于其上部的栅极电极的最低部分的高度的差是4nm以上。

4.如权利要求2中记述的非易失性半导体装置,特征在于:

在上述周边电路晶体管的动作为待机状态时,提供流过亚阈值电流的偏置电位。

5.如权利要求2中记述的非易失性半导体装置,特征在于:

上述存储单元晶体管的栅极电极的至少一部分与上述存储单元阵列区的埋入元件分离区自匹配。

6.如权利要求2中记述的非易失性半导体装置,特征在于:

上述存储单元晶体管是具备了浮置栅极的非易失性半导体存储器的存储单元。

7.一种非易失性半导体存储装置的制造方法,这是具有用槽型元件分离形成元件区,而且包括浮置栅极的存储单元部分和其周边电路部分的非易失性半导体存储装置的制造方法,特征在于:

具有

在硅衬底上经由绝缘膜形成多晶硅层的工艺;

为了形成元件区,自匹配地腐蚀该多晶硅层与绝缘膜、硅衬底,形成在硅衬底中具有底部并且包围元件区的元件分离用的多个槽的工艺;

通过氧化把元件区与多晶硅层相对的面的每一个端部进行圆加工的工艺;

用具有耐氧化性的膜覆盖存储单元部分的工艺;

在上述耐氧化膜的形成后加入氧化,在周边电路部分的元件区,在硅衬底与多晶硅层相对的面的端部之间,形成比存储单元部分厚的鸟嘴形氧化膜的工艺。

8.如权利要求7中记述的非易失性半导体存储装置的制造方法,特征在于:

还具有在淀积了上述耐氧化膜以后,在进行对于周边电路部分的氧化之前,选择性地去除上述耐氧化膜使得在存储单元部分中仅在浮置栅极侧面部分以及元件分离用槽的内壁残留耐氧化膜的工艺。

9.如权利要求7中记述的非易失性半导体存储装置的制造方法,特征在于:

在进行了对于周边电路部分的氧化以后,去除覆盖存储单元部分的耐氧化膜。

10.一种非易失性半导体存储装置的制造方法,这是具有用槽型元件分离形成元件区,而且包括浮置栅极的存储单元部分和其周边电路部分的非易失性半导体存储装置的制造方法,特征在于:

具有

在硅衬底上经由绝缘膜形成多晶硅层的工艺;

仅在周边电路部分,自匹配地腐蚀多晶硅层与绝缘膜、硅衬底,形成第1元件分离用槽的工艺;

在周边电路部分,氧化元件区与第1多晶硅层相对的面的每一个端部,形成鸟嘴形氧化膜的工艺;

自匹配地腐蚀存储单元部分的多晶硅层与绝缘膜、硅衬底,形成第2元件分离用槽的工艺;

在形成第2元件分离用槽以后,氧化存储单元部分的元件区与多晶硅层相对的面的每一个端部,形成比形成在周边电路部分的鸟嘴形氧化膜更薄的鸟嘴形氧化膜的工艺。

11.一种非易失性半导体存储装置的制造方法,这是具有用槽型元件分离形成元件区,而且包括浮置栅极的存储单元部分和其周边电路部分的非易失性半导体存储装置的制造方法,特征在于:

具有

在硅衬底上经由绝缘膜形成耐氧化膜的工艺;

选择性地去除存储单元部分的耐氧化膜和绝缘膜的工艺;

在存储单元部分上形成隧道氧化膜,把该膜进行氮化处理,把隧道膜形成为氮氧化膜的工艺;

在存储单元部分的隧道氮氧化膜的上部以及周边电路部分的耐氧化膜的上部,形成多晶硅层的工艺;

自匹配地腐蚀多晶硅膜与硅衬底,在存储单元部分以及周边电路部分形成元素分离用槽的工艺;

在元件分离用槽形成以后通过氧化,在元件区与多晶硅层相对的每一个面的端部形成鸟嘴形氧化膜,在周边电路部分形成比存储单元部分更厚的鸟嘴形氧化膜的工艺。

12.一种非易失性半导体存储装置的制造方法,这是具有用槽型元件分离形成元件区,而且包括浮置栅极的存储单元部分和其周边电路部分的非易失性半导体存储装置的制造方法,特征在于:

具有

在硅衬底上经由绝缘膜形成多晶硅层的工艺;

自匹配地腐蚀该多晶硅层与硅衬底,为了形成元件区,形成元件分离用槽的工艺;

通过氧化,把元件区与多晶硅相对的每一个面的端部进行圆加工的工艺;

用多晶硅膜仅把存储单元部分覆盖的工艺;

在上述多晶硅膜的覆盖以后加入氧化,在周边电路部分的硅衬底与多晶硅层的相对面的端部之间,形成比存储单元部分更厚的鸟嘴形氧化膜的工艺;

把覆盖存储单元部分的硅膜形成氧化膜的工艺。

13.一种非易失性半导体存储装置的制造方法,这是具有用槽型元件分离形成元件区,而且包括浮置栅极的存储单元部分和其周边电路部分的非易失性半导体存储装置的制造方法,特征在于:

具有

在硅衬底上形成绝缘膜与成为浮置栅极的多晶硅层的工艺;

自匹配地腐蚀该多晶硅膜与硅衬底,形成元件分离用槽的工艺;

在槽的内壁以及多晶硅的侧壁形成硅氮氧化膜的工艺。

14.如权利要求13中记述的非易失性半导体存储装置的制造方法,特征在于:

在槽的内壁以及多晶硅的侧壁形成硅氮氧化膜的工艺是在槽的内壁以及多晶硅层的侧壁形成硅氧化膜以后施加氮氧化处理,形成氮氧化膜的工艺。

15.一种非易失性半导体存储装置的制造方法,在元件分离形成工艺之前形成MOS晶体管的栅极绝缘膜的一部分,在元件分离形成工艺以后形成上述栅极绝缘膜的剩余部分的非易失性半导体存储装置的制造时,特征在于:

形成MOS晶体管使得与具有在上述元件分离形成工艺之前形成的栅极绝缘膜的MOS晶体管的元件区端部的曲率相比较实质地加大具有在上述元件分离形成工艺以后形成的栅极绝缘膜的MOS晶体管的元件区端部的曲率。

16.一种非易失性半导体存储装置的制造方法,在具有存储单元阵列区及形成了其周边电路晶体管的周边晶体管区的非易失性半导体存储装置的制造时,特征在于:

具有

在半导体衬底的整个面上形成存储单元晶体管用的第1栅极绝缘膜,在其上面形成多晶硅膜以及绝缘膜的工艺;

在上述绝缘膜、多晶硅膜、第1栅极绝缘膜以及半导体衬底上形成元件分离区形成用槽的工艺;

在覆盖上述存储单元阵列区的基础上,去除周边晶体管区的元件区端部上的第1栅极绝缘膜的工艺;

把上述槽的表面以及周边晶体管区的元件区的端部与其上面的多晶硅膜之间部分的表面进行氧化的工艺;

在上述槽中把埋入绝缘体进行埋入,并且使整个面平坦的工艺;

去除上述多晶硅膜上的绝缘膜的工艺;

在去除了上述周边晶体管区的多晶硅膜以及第1栅极绝缘膜以后,形成周边电路晶体管用的第2栅极绝缘膜的工艺;

在上述存储单元阵列区形成把上述多晶硅膜作为浮置栅极所具备的叠层栅极构造,在周边晶体管区在上述第2栅极绝缘膜上形成栅极电极的工艺;

在衬底表层部分选择性地掺入成为晶体管的源/漏的杂质的工艺。

17.一种非易失性半导体存储装置的制造方法,在具有存储单元阵列区及形成了其周边电路晶体管的周边晶体管区的非易失性半导体存储装置的制造时,特征在于:

具有

在半导体衬底的整个面上形成存储单元晶体管用的第1栅极绝缘膜,在其上面形成多晶硅膜的工艺;

在上述多晶硅膜、第1栅极绝缘膜以及半导体衬底上形成元件分离区形成用槽的工艺;

在上述槽中把埋入绝缘体进行埋入,而且使整个面平坦的工艺;

在衬底的整个面上形成存储单元晶体管用的浮置栅极·控制栅极间绝缘用的栅极间绝缘膜的工艺;

去除上述周边晶体管区的栅极间绝缘膜、多晶硅膜以及第1栅极绝缘膜使元件区露出的工艺;

把上述周边晶体管区露出的元件区端部的角部进行腐蚀做成具有圆形形状的工艺;

在上述周边晶体管区形成上述周边电路晶体管用的第2栅极绝缘膜的工艺;

在上述存储单元阵列区形成把上述多晶硅膜作为浮置栅极所具备的叠层栅极构造,在周边晶体管区在上述第2栅极绝缘膜上形成栅极电极的工艺;

在衬底表层部分选择性地掺入成为晶体管的源/漏的杂质的工艺。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP073074/1999 | 1999-03-18 | ||

| JP07307499A JP3651760B2 (ja) | 1999-03-18 | 1999-03-18 | 半導体装置の製造方法 |

| JP185118/1999 | 1999-06-30 | ||

| JP18511899A JP3833854B2 (ja) | 1999-06-30 | 1999-06-30 | 不揮発性半導体記憶装置の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1267915A true CN1267915A (zh) | 2000-09-27 |

Family

ID=26414201

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00104074A Pending CN1267915A (zh) | 1999-03-18 | 2000-03-17 | 非易失性半导体存储装置及其制造方法 |

Country Status (3)

| Country | Link |

|---|---|

| KR (1) | KR20000076914A (zh) |

| CN (1) | CN1267915A (zh) |

| TW (1) | TW452834B (zh) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100411144C (zh) * | 2005-08-16 | 2008-08-13 | 力晶半导体股份有限公司 | 非挥发性存储器及其制造方法 |

| CN100536139C (zh) * | 2005-03-25 | 2009-09-02 | 冲电气工业株式会社 | 半导体集成电路 |

| CN100547768C (zh) * | 2006-12-19 | 2009-10-07 | 力晶半导体股份有限公司 | 非易失性存储器的制作方法 |

| CN101373776B (zh) * | 2004-12-24 | 2010-08-04 | 株式会社理光 | 半导体装置 |

| CN114446955A (zh) * | 2020-11-04 | 2022-05-06 | 长鑫存储技术有限公司 | 半导体结构及半导体结构制作方法 |

| US12166032B2 (en) | 2020-11-04 | 2024-12-10 | Changxin Memory Technologies, Inc. | Semiconductor structure and method for manufacturing semiconductor structure |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100859081B1 (ko) * | 2001-08-06 | 2008-09-17 | 엔엑스피 비 브이 | 반도체 디바이스 제조 방법 |

| JP2004095886A (ja) * | 2002-08-30 | 2004-03-25 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| KR100479834B1 (ko) * | 2002-09-03 | 2005-04-06 | 주식회사 엑셀반도체 | 플래시메모리 제조방법 |

| KR100881847B1 (ko) * | 2002-12-28 | 2009-02-03 | 동부일렉트로닉스 주식회사 | 반도체 메모리 소자의 제조 방법 |

-

2000

- 2000-03-06 TW TW089103960A patent/TW452834B/zh not_active IP Right Cessation

- 2000-03-17 CN CN00104074A patent/CN1267915A/zh active Pending

- 2000-03-18 KR KR1020000013868A patent/KR20000076914A/ko not_active Application Discontinuation

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101373776B (zh) * | 2004-12-24 | 2010-08-04 | 株式会社理光 | 半导体装置 |

| CN100536139C (zh) * | 2005-03-25 | 2009-09-02 | 冲电气工业株式会社 | 半导体集成电路 |

| CN100411144C (zh) * | 2005-08-16 | 2008-08-13 | 力晶半导体股份有限公司 | 非挥发性存储器及其制造方法 |

| CN100547768C (zh) * | 2006-12-19 | 2009-10-07 | 力晶半导体股份有限公司 | 非易失性存储器的制作方法 |

| CN114446955A (zh) * | 2020-11-04 | 2022-05-06 | 长鑫存储技术有限公司 | 半导体结构及半导体结构制作方法 |

| WO2022095466A1 (zh) * | 2020-11-04 | 2022-05-12 | 长鑫存储技术有限公司 | 半导体结构及半导体结构制作方法 |

| US12166032B2 (en) | 2020-11-04 | 2024-12-10 | Changxin Memory Technologies, Inc. | Semiconductor structure and method for manufacturing semiconductor structure |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20000076914A (ko) | 2000-12-26 |

| TW452834B (en) | 2001-09-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1237616C (zh) | 具有浮置栅的半导体存储器及其制造方法 | |

| CN1205664C (zh) | 半导体装置及其制造方法 | |

| CN1134058C (zh) | 槽型元件分离结构的制造方法 | |

| CN1269214C (zh) | 半导体器件及其制造方法 | |

| CN100342539C (zh) | 半导体装置和半导体装置的制造方法 | |

| CN1181552C (zh) | 半导体装置及其制造方法 | |

| CN1181554C (zh) | 半导体器件及其制造方法 | |

| CN101051652A (zh) | 半导体器件及其制造方法 | |

| CN1542974A (zh) | 半导体器件及其制造方法 | |

| CN1303698C (zh) | 半导体器件及其制造方法 | |

| CN1514485A (zh) | 非挥发性内存及其制造方法 | |

| CN1485891A (zh) | 半导体存储器件及其制造方法 | |

| CN1449585A (zh) | 半导体器件及其制造方法 | |

| CN1961420A (zh) | 半导体器件及其制造方法 | |

| CN1297256A (zh) | 半导体装置及其制造方法 | |

| CN1277315C (zh) | 半导体器件 | |

| CN1115716C (zh) | 半导体衬底的处理方法和半导体衬底 | |

| CN1925161A (zh) | 半导体产品及其制作方法 | |

| CN1314713A (zh) | 垂直金属-氧化物-半导体晶体管及其制造方法 | |

| CN1303127A (zh) | 非易失性半导体存储器及其制造方法 | |

| CN1430285A (zh) | 使用了部分soi衬底的半导体器件及其制造方法 | |

| CN1421914A (zh) | 半导体装置及其制造方法 | |

| CN1498424A (zh) | 半导体存储器件及其制造方法 | |

| CN1267915A (zh) | 非易失性半导体存储装置及其制造方法 | |

| CN1518090A (zh) | 半导体器件的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |