WO2014126214A1 - Semiconductor device - Google Patents

Semiconductor device Download PDFInfo

- Publication number

- WO2014126214A1 WO2014126214A1 PCT/JP2014/053517 JP2014053517W WO2014126214A1 WO 2014126214 A1 WO2014126214 A1 WO 2014126214A1 JP 2014053517 W JP2014053517 W JP 2014053517W WO 2014126214 A1 WO2014126214 A1 WO 2014126214A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- channel region

- region

- semiconductor device

- bottom channel

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/36—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the transistor being a FinFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/482—Bit lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

- H10D86/215—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI comprising FinFETs

Definitions

- the present invention relates to a semiconductor device.

- DRAM Dynamic Random Access Memory

- the channel length of a transistor is also reduced by reducing the size of a memory cell. For this reason, the performance of the transistor decreases. Therefore, the retention of memory cells or the deterioration of write characteristics has become a problem.

- a trench (recess) type FET Field Effect Transistor

- a trench (recess) type FET Field Effect Transistor

- fin-type FETs having a three-dimensional channel have been developed (for example, Japanese Patent Application Laid-Open No. 2005-064500 (Patent Document 1), Japanese Patent Application Laid-Open No. 2007-027753 (Patent Document 2), and Japanese Patent Application Laid-Open No. 2007-027753. (See 2007-305827 (Patent Document 3)).

- the trench type FET is a transistor having a three-dimensional channel structure by forming a groove in a semiconductor substrate and disposing a gate electrode in the groove via a gate insulating film.

- a fin-type FET is a transistor having a three-dimensional channel structure by disposing a gate electrode through a gate insulating film so as to straddle a fin protruding from between grooves formed in a semiconductor substrate.

- the gate length can be increased with respect to the channel width. For this reason, the short channel effect can be suppressed.

- DRAM dynamic random access memory

- a transistor having an embedded gate electrode embedded on the main surface side of the semiconductor substrate as a selection transistor constituting the memory cell. Has been.

- the gate electrode (word line) is embedded in the main surface side of the semiconductor substrate. For this reason, the gate electrode does not protrude above the main surface of the semiconductor substrate.

- bit lines are located above the semiconductor substrate among the wirings connected to the memory cells. Therefore, there is an advantage that not only the arrangement when forming the capacitor, the contact plug, etc. constituting the memory cell on the semiconductor substrate is facilitated, but also the difficulty of the processing can be reduced.

- transistor (Tr) having a buried gate electrode as a material of the gate electrode (word line) buried on the main surface side of the semiconductor substrate, for example, a metal film (having a lower resistance than a polysilicon film) A tungsten film (W film) and a titanium nitride film (TiN film).

- a metal film By using a metal film, the capacitance of the gate electrode (word line) and the bit line is reduced, the current called GIDL (Gate-Induced-Drain-Leakage current) is suppressed, the retention characteristic is improved, and the consumption current is reduced. It has been found that effects such as reduction can be obtained.

- FIG. 23 is a cross-sectional view schematically showing a main part of a memory cell portion of a conventional semiconductor device for explaining a disturb failure.

- the bit line 212 that intersects with the first and second gate electrodes 223 and 228 is schematically illustrated.

- a conventional semiconductor device 200 includes a semiconductor substrate 201, an element isolation region 202, an active region 204, a first transistor 206, a second transistor 207, and a bit line contact plug 211. , A bit line 212, a first capacitor contact plug 214 (storage node contact plug), and a second capacitor contact plug 215 (storage node contact plug).

- the element isolation region 202 is provided on the main surface 201a side of the semiconductor substrate 201, and defines the active region 204. In the active region 204, first and second grooves 201A and 201B are formed.

- the first transistor 206 includes a gate insulating film 222 that covers the inner surface of the first groove 201A, a first gate electrode 223 that fills the lower portion of the first groove 201A via the gate insulating film 222, and a first The first impurity diffusion region 225 formed in the active region 204 located between the upper portion of the trench 201A and the element isolation region 202, and the active region 204 located between the upper portions of the first and second trenches 201A and 201B. And a second impurity diffusion region 226 formed on the substrate.

- the second transistor 207 includes a gate insulating film 222 that covers the inner surface of the second groove 201B, a second gate electrode 228 that fills the lower portion of the second groove 201B via the gate insulating film 222, and a second A first impurity diffusion region 227 and a second impurity diffusion region 226 (impurity diffusion region common to the first transistor 206) formed in the active region 204 located between the upper portion of the trench 201B and the element isolation region 202 And).

- the second transistor 207 is a transistor provided in the active region 204 in which the first transistor 206 is provided.

- the bit line contact plug 211 is provided on the upper surface 226 a of the second impurity diffusion region 226.

- the bit line 212 is provided on the bit line contact plug 211 and is integrated with the upper end of the bit line contact plug 211.

- the first capacitor contact plug 214 is connected to the upper surface 225 a of the first impurity diffusion region 225 constituting the first transistor 206.

- the second capacitor contact plug 215 is connected to the upper surface 227a of the first impurity diffusion region 227 constituting the second transistor 207.

- the second capacitor contact plug 215 is set to “High” and the second transistor 207 is turned off. In this state, when the on-off operation of the first transistor 206 is repeatedly performed, electrons that are excited in the channel region 231 of the first transistor 206 and are not trapped are in a floating state (shown in FIG. 23). “E ⁇ ”) floats around the second transistor 207. The electrons enter the second capacitor contact plug 215 with a certain probability.

- an SOI (Silicon on Insulator) substrate including a semiconductor substrate body, an insulating layer covering one surface of the semiconductor substrate body, and a semiconductor layer covering one surface of the insulating layer; A plurality of first element isolation regions that are divided into a plurality of parts in one direction, and a plurality of second element parts that are divided into a plurality of parts in a second direction that intersects the first direction.

- the groove is disposed in the groove via two grooves extending in the first direction and having a depth that does not reach the insulating layer, and a gate insulating film covering the inner surface of the groove.

- Gate power And two transistors disposed in the same active region, and the two transistors constitute two side surfaces of the trench disposed opposite to each other in the second direction in the active region And a bottom channel region disposed in a portion of the active region located between the bottom surface of the trench and the insulating layer, respectively.

- two transistors provided in the same active region are arranged in a portion of the active region that constitutes two side surfaces of the groove opposed to each other in the second direction.

- a bottom channel region disposed in a portion of the active region located between the bottom surface of the trench and the insulating layer.

- FIG. 3 is an enlarged plan view of a part of the memory cell unit configuring the semiconductor device according to the first embodiment of the present invention, and includes a first element isolation region and a second element among the components of the memory cell unit.

- FIG. 5 is a diagram illustrating only an isolation region, an active region, a first groove, a second groove, a first gate electrode, a second gate electrode, a bit line contact plug, and a bit line.

- FIG. 2 is a cross-sectional view of the memory cell portion of the semiconductor device shown in FIG. 1 in the AA line direction.

- FIG. 3 is an enlarged cross-sectional view of a portion surrounded by a region A in the memory cell portion shown in FIG. 2.

- FIG. 3 is an isometric view illustrating the main part of the memory cell portion of the semiconductor device according to the first embodiment by isometric projection.

- FIG. FIG. 2 is a cross-sectional view of the memory cell portion of the semiconductor device shown in FIG. 1 in the BB line direction, and is an enlarged view of only components arranged around a first bottom channel region. Positional relationship among first element isolation region, second element isolation region, active region, first bottom channel region, and second bottom channel region constituting memory cell portion of semiconductor device of first embodiment It is a top view for demonstrating. It is sectional drawing to which the part different from the semiconductor device of 1st Embodiment was expanded among the memory cell parts of the semiconductor device which concerns on the modification of the 1st Embodiment of this invention.

- FIG. 6 is a diagram (part 1) illustrating a manufacturing process of the semiconductor device according to the first embodiment of the present invention, and is a cross-sectional view for illustrating the manufacturing process of the SOI substrate;

- FIG. 8 is a second diagram illustrating the manufacturing process of the semiconductor device according to the first embodiment of the invention, and is a plan view illustrating a memory cell portion of the semiconductor device that is being manufactured;

- FIG. 9B is a diagram (part 2) illustrating the manufacturing process of the semiconductor device according to the first embodiment of the invention, and is a cross-sectional view taken along the line AA of the structure illustrated in FIG. 9A;

- FIG. 6 is a diagram (part 3) illustrating the manufacturing process of the semiconductor device according to the first embodiment of the invention, which is a cross-sectional view illustrating a memory cell portion of the semiconductor device that is being manufactured;

- FIG. 8 is a view (No. 4) showing a manufacturing step of the semiconductor device according to the first embodiment of the invention, and a cross-sectional view showing a memory cell portion of the semiconductor device in the manufacturing process;

- FIG. 7 is a view (No. 5) showing a manufacturing step of the semiconductor device according to the first embodiment of the invention, and is a plan view showing a memory cell portion of the semiconductor device in the process of manufacturing;

- FIG. 13B is a view (No.

- FIG. 6 is a sixth diagram illustrating the manufacturing process of the semiconductor device according to the first embodiment of the invention, and is a cross-sectional view illustrating the memory cell portion of the semiconductor device that is being manufactured;

- FIG. 6 is a sixth diagram illustrating the manufacturing process of the semiconductor device according to the first embodiment of the invention, and is a cross-sectional view illustrating the memory cell portion of the semiconductor device that is being manufactured;

- FIG. 6 is an isometric view illustrating a main part of a memory cell portion of a semiconductor device according to a second embodiment by isometric projection.

- FIG. 16 is an enlarged cross-sectional view of a memory cell portion surrounded by a region B shown in FIG. 15. It is sectional drawing which expanded the part different from the semiconductor device of 2nd Embodiment among the memory cell parts of the semiconductor device which concerns on the modification of the 2nd Embodiment of this invention. It is sectional drawing (the 1) which shows the process of the semiconductor device of the 2nd Embodiment of this invention. It is sectional drawing (the 2) which shows the process of the semiconductor device of the 2nd Embodiment of this invention.

- FIG. 10 is an isometric view illustrating a main part of a memory cell portion of a semiconductor device according to a third embodiment by isometric projection.

- FIG. 1 is an isometric view illustrating a main part of a memory cell portion of a semiconductor device according to a third embodiment by isometric projection.

- FIG. 21 is an enlarged cross-sectional view of a memory cell portion surrounded by a region C shown in FIG. 20. It is sectional drawing which shows the process of the semiconductor device of the 3rd Embodiment of this invention. It is sectional drawing which shows typically the principal part of the conventional semiconductor device for demonstrating a disturbance failure.

- FIG. 1 is an enlarged plan view of a part of the memory cell portion constituting the semiconductor device according to the first embodiment of the present invention.

- the first element isolation region FIG. 5 is a diagram illustrating only a second element isolation region, an active region, a first groove, a second groove, a first gate electrode, a second gate electrode, a bit line contact plug, and a bit line.

- FIG. 2 is a cross-sectional view taken along the line AA of the memory cell portion of the semiconductor device shown in FIG.

- FIG. 3 is an enlarged cross-sectional view of a portion surrounded by the region A in the memory cell portion shown in FIG.

- FIG. 4 is an isometric view illustrating the main part of the memory cell portion of the semiconductor device of the first embodiment by isometric projection.

- FIGS. 1 to 4 illustrate a DRAM (Dynamic Random Access Memory) as an example of the semiconductor device 10 according to the first embodiment.

- DRAM Dynamic Random Access Memory

- the X direction indicates the extending direction of the first element isolation region 14.

- the Y direction indicates the extending direction of the second element isolation region 17 that intersects the X direction (orthogonal in the case of FIG. 1).

- the Z direction indicates a direction orthogonal to the X direction and the Y direction (in other words, the thickness direction of the semiconductor substrate body 13-1).

- W1 represents the width in the Y direction (hereinafter referred to as “width W1”) of the first bottom channel region 66 that is illustrated in FIG. 3 and is not illustrated in FIG.

- W2 indicates the width in the Y direction (hereinafter referred to as “width W2”) of the second bottom channel region 77 shown in FIG. 3 and not shown in FIG.

- the widths W1 and W2 are equal to the width of the active region 19 in the Y direction.

- bit line 37 is schematically illustrated.

- the bit line 37 actually extends in the X direction as shown in FIG.

- a semiconductor device 10 includes a memory cell unit 11 provided in a memory cell region and a peripheral circuit region (not shown) located around the memory cell unit 11. And a peripheral circuit portion (not shown) provided in the device.

- a plurality of memory cells are arranged in a matrix.

- a circuit including peripheral circuit transistors not shown) for controlling the operation of each memory cell is arranged in the peripheral circuit section (not shown).

- the memory cell unit 11 of the semiconductor device 10 of the first embodiment includes an SOI (Silicon on Insulator) substrate 13, a first element isolation region 14, a second element isolation region 17, an active region 19, A first trench 21, a second trench 22, a first cell transistor 25 (first transistor), a second cell transistor 27 (second transistor), a first interlayer insulating film 29, The buried insulating film 32, the bit line contact opening 33, the bit line contact plug 35, the bit line 37, the cap insulating film 39, the first sidewall film 41, and the second sidewall film 42 , Second interlayer insulating film 44, first capacitor contact hole 45-1, second capacitor contact hole 45-2, first capacitor contact plug 46-1, With the amount contact plugs 46-2, a stopper film 48, the third interlayer insulating film 49, and the cylinder bore 51, a capacitor 53, a fourth interlayer insulating film 55, a protective film 57.

- SOI Silicon on Insulator

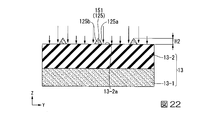

- the SOI substrate 13 includes a semiconductor substrate body 13-1, an insulating layer 13-2 covering one surface 13-1a of the semiconductor substrate body 13-1, and one surface of the insulating layer 13-2.

- the semiconductor layer 13-3 (SOI layer) covering the layer 13-2a is sequentially stacked.

- the semiconductor substrate body 13-1 is a substrate having a plate shape.

- As the semiconductor substrate body 13-1 for example, a p-type single crystal silicon substrate can be used.

- the insulating layer 13-2 is a buried insulating layer disposed between the semiconductor substrate body 13-1 and the semiconductor layer 13-3.

- the insulating layer 13-2 is disposed at a deep position from the main surface 13a of the SOI substrate 13 (in other words, the upper surface of the semiconductor layer 13-3) (for example, a position having a depth of 250 nm from the main surface 13a of the SOI substrate 13). ing.

- a silicon oxide film (SiO 2 film) called a buried oxide (BOX) film can be used as the insulating layer 13-2.

- the semiconductor layer 13-3 is a layer in which the first and second cell transistors 25 and 27 are formed.

- As the semiconductor layer 13-3 for example, a p-type single crystal silicon layer can be used.

- the thickness M1 of the semiconductor layer 13-3 can be set to, for example, 300 nm.

- a case where a p-type single crystal silicon layer is used as an example of the semiconductor layer 13-3 will be described.

- a plurality of first element isolation regions 14 are provided in the semiconductor layer 13-3 so as to extend in the X direction (second direction).

- the first element isolation region 14 extends in the X direction, and the first element isolation trench 14- provided in the semiconductor layer 13-3 so as to expose the one surface 13-2a of the insulating layer 13-2. 1 and a first element isolation insulating film 14-2 (for example, a silicon oxide film (SiO 2 film)) filling the first element isolation trench 14-1.

- a first element isolation insulating film 14-2 for example, a silicon oxide film (SiO 2 film) filling the first element isolation trench 14-1.

- the first element isolation region 14 has a depth reaching the one surface 13-2a of the insulating layer 13-2.

- the plurality of first element isolation regions 14 are arranged at predetermined intervals in the Y direction (first direction). Thus, the plurality of first element isolation regions 14 divide (divide) the semiconductor layer 13-3 into a plurality of parts in the Y direction.

- a plurality of second element isolation regions 17 are provided in the semiconductor layer 13-3 and the first element isolation region 14 so as to extend in the Y direction.

- the second element isolation region 17 divides the plurality of first element isolation regions 14 arranged in the Y direction.

- the second element isolation region 17 includes a second element isolation trench 17-1 and a second element isolation insulating film 17-2 (for example, a silicon oxide film (SiO 2 film)).

- the second element isolation trench 17-1 is provided in the semiconductor layer 13-3 and the first element isolation region 14 so as to extend in the Y direction and expose the one surface 13-2a of the insulating layer 13-2. It is done.

- the second element isolation insulating film 17-2 fills the second element isolation trench 17-1.

- the second element isolation region 17 has a depth reaching the one surface 13-2a of the insulating layer 13-2.

- a plurality of second element isolation regions 17 are arranged in the X direction.

- the plurality of second element isolation regions 17 divide (divide) the semiconductor layer 13-3 into a plurality of portions in the X direction.

- the active region 19 is composed of a semiconductor layer 13-3 partitioned by first and second element isolation regions 14 and 17.

- a plurality of active regions 19 are arranged so as to be aligned with respect to the X direction and the Y direction.

- the plurality of active regions 19 are insulated and isolated from the other active regions 19 arranged in the X and Y directions by the first and second element isolation regions 14 and 17.

- the active region 19 is a region that functions as an element formation layer in which the first and second cell transistors 25 and 27 are formed.

- the first and second grooves 21 and 22 are grooves extending in the Y direction, and are provided so as to straddle the plurality of active regions 19 and the first element isolation regions 14 arranged in the Y direction.

- One first and second grooves 21 and 22 are provided for each active region 19.

- the first trench 21 is a trench in which the first gate insulating film 59-1 and the first gate electrode 31 are disposed.

- the second trench 22 is a trench in which the second gate insulating film 59-2 and the second gate electrode 74 are disposed.

- the depth of the first and second grooves 21 and 22 (the depth when the main surface 13a of the SOI substrate 13 is used as a reference) is set to a depth that does not reach the one surface 13-2a of the insulating layer 13-2. .

- the depth of the first and second grooves 21 and 22 is such that the semiconductor layer 13 is located between the bottom surfaces 21a and 22a of the first and second grooves 21 and 22 and the one surface 13-2a of the insulating layer 13-2. -3 is the remaining thickness.

- the bottom surfaces 21a and 22a of the first and second grooves 21 and 22 are disposed so as to be close to the one surface 13-2a of the insulating layer 13-2.

- the semiconductor layer 13-3 is left between the bottom surface 21a of the first groove 21 and the one surface 13-2a of the insulating layer 13-2.

- the semiconductor layer 13-3 can function as a first bottom channel region 66 described later of the first cell transistor 25.

- the semiconductor layer 13-3 is left between the bottom surface 22a of the second groove 22 and the one surface 13-2a of the insulating layer 13-2. As a result, the semiconductor layer 13-3 can function as a second bottom channel region 77 described later of the second cell transistor 27.

- the depth of the first and second grooves 21 and 22 is increased.

- the thickness of the semiconductor layer 13-3 functioning as the first and second bottom channel regions 66 and 77 is reduced, and the first and second bottom channel regions 66 and 77 serving as charge paths are cut off. The area can be reduced.

- one first cell transistor 25 (selection transistor) is provided for each of the plurality of active regions 19.

- the first cell transistor 25 includes a first gate insulating film 59-1, a first gate electrode 61, a first sidewall channel region 63, a second sidewall channel region 64, a first A bottom channel region 66, a first capacitor impurity diffusion region 68, and a bit line impurity diffusion region 71 are provided.

- the first gate insulating film 59-1 is provided so as to cover the inner surface of the first trench 21.

- the first gate electrode 61 is provided so as to bury the lower portion of the first trench 21 via the first gate insulating film 59-1.

- a conductive material can be used as a material of the first gate electrode 61.

- a metal such as tungsten (W), polycrystalline silicon, or the like can be used.

- the first gate electrode 61 can be constituted by a laminated film in which, for example, a titanium nitride film (TiN film) and a tungsten film (W film) are sequentially laminated.

- TiN film titanium nitride film

- W film tungsten film

- the first side wall channel region 63 is constituted by the active region 19 (semiconductor layer 13-3).

- the active region 19 is formed between the second element isolation region 17 and the side surface 21 b (side surface intersecting with the X direction (orthogonal in the case of the first embodiment)) of the first groove 21. Located between.

- the second side wall channel region 64 is composed of the active region 19 (semiconductor layer 13-3).

- the active region 19 semiconductor layer 13-3 includes a side surface 21c of the first groove 21 (side surface facing the side surface 21b in the X direction) and a side surface 22b of the second groove 22 (crossing the X direction (first direction). In the case of the embodiment, it is located between the side surface orthogonal).

- the second side wall portion channel region 64 is a side wall portion channel region shared between the first and second cell transistors 25 and 27.

- FIG. 5 is a cross-sectional view of the memory cell portion of the semiconductor device shown in FIG. 1 in the BB line direction, and is an enlarged view of only the components arranged around the first bottom channel region. .

- FIG. 6 shows a first element isolation region, a second element isolation region, an active region, a first bottom channel region, and a second bottom channel that constitute the memory cell portion of the semiconductor device of the first embodiment. It is a top view for demonstrating the positional relationship of an area

- the first element isolation region 14, the second element isolation region 17, the active region 19, and the first bottom channel Only region 66 and second bottom channel region 77 are shown.

- the first bottom channel region 66 is constituted by the active region 19.

- the active region 19 is disposed between the bottom surface 21a of the first groove 21 and the one surface 13-2a of the insulating layer 13-2.

- the side surfaces 66 a and 66 b (two side surfaces) of the first bottom channel region 66 are disposed to face each other in the Y direction and are in contact with the first element isolation region 14. Further, the upper surface 66c of the first bottom channel region 66 is in contact with the first gate insulating film 59-1.

- the side surfaces 66 a and 66 b (two side surfaces) of the first bottom channel region 66 arranged to face each other in the Y direction are brought into contact with the first element isolation region 14. Yes. Further, in the first bottom channel region 66, the upper surface 66c of the first bottom channel region 66 is in contact with the first gate insulating film 59-1. Further, in the first bottom channel region 66, the lower surface 66d of the first bottom channel region 66 is in contact with the one surface 13-2a (upper surface) of the insulating layer 13-2.

- the cross-sectional area of the bottom channel region 66 can be reduced. Therefore, it is possible to limit the movement of floating electrons through the first bottom channel region 66, that is, the flow of floating electrons through the first bottom channel region 66. For this reason, a disturbance failure can be suppressed.

- the first bottom channel region 66 has ends 66A and 66B (two ends) arranged in the X direction.

- the end portion 66A (one end portion) is connected (integrated) with the first side wall portion channel region 63.

- the end portion 66B is connected (integrated) with the second side wall portion channel region 64.

- first sidewall channel region 63, the second sidewall channel region 64, and the first bottom channel region 66 are continuous from the first capacitor impurity diffusion region 68 to the bit line impurity diffusion region 71. To configure the channel.

- the first bottom channel region 66 is a flat channel region having an upper surface 66c and a lower surface 66d parallel to the one surface 13-1a of the semiconductor substrate body 13-1.

- the first bottom channel region 66 is a flat channel region having an upper surface 66c and a lower surface 66d parallel to the one surface 13-1a of the semiconductor substrate body 13-1. This makes it possible to limit the flow path of floating electrons that pass through the first bottom channel region 66, as compared to the configuration in which the flow path is not limited as in the prior art shown in FIG. Therefore, disturbance disturbance can be suppressed.

- the thickness M2 of the first bottom channel region 66 is less than 1/20 of the thickness M1 of the semiconductor layer 13-3. If it is thin, the cross-sectional area of the bottom channel region 66 becomes too small. For this reason, not only the movement of the floating electrons through the first bottom channel region 66 is restricted, but also the normal flow of electrons is restricted. Therefore, there arises a problem that the ON current is reduced.

- the thickness M2 of the first bottom channel region 66 is larger than 1/5 of the thickness M1 of the semiconductor layer 13-3, the cross-sectional area of the bottom channel region 66 is increased, so that the first bottom channel region 66 It becomes impossible to limit the movement of stray electrons via 66. Therefore, there arises a problem that disturb disturbance cannot be suppressed.

- the thickness M2 of the first bottom channel region 66 is preferably in the range of 1/20 to 1/5 of the thickness M1 of the semiconductor layer 13-3.

- the thickness M2 of the first bottom channel region 66 should be within a range of 1/15 to 1/10 of the thickness M1 of the semiconductor layer 13-3. As described above, by setting the thickness M2 of the first bottom channel region 66 within the range of 1/15 to 1/10 of the thickness M1 of the semiconductor layer 13-3, the disturb failure is more effectively suppressed. be able to.

- the thickness M2 of the first bottom channel region 66 may be set within a range of 20 to 30 nm, for example.

- the first bottom channel region 66 serving as a charge path is limited to a cross-sectional area defined by the width W1 ⁇ thickness M2 of the first bottom channel region due to the presence of the insulating layer 13-2 of the SOI substrate 13. Will be.

- the second bottom channel region 77 serving as a charge path is formed by a width W2 ⁇ thickness M3 of the second bottom channel region 77 due to the presence of the insulating layer 13-2 of the SOI substrate 13. It will be limited to the area.

- the first capacitor impurity diffusion region 68 is provided in the active region 19 located between the upper portion of the second element isolation region 17 and the upper portion of the first groove 21. ing. Thus, the first capacitor impurity diffusion region 68 is disposed on the first sidewall channel region 63.

- the first capacitor impurity diffusion region 68 functions as a source / drain region.

- the upper surface 68 a of the first capacitor impurity diffusion region 68 coincides with the main surface 13 a of the SOI substrate 13.

- the first capacitor impurity diffusion region 68 is a region formed by doping the active region 19 with an impurity (for example, an n-type impurity when the semiconductor layer 13-3 is a p-type semiconductor).

- the bit line impurity diffusion region 71 is provided in the active region 19 located between the upper part of the first groove 21 and the upper part of the second groove 22. As a result, the bit line impurity diffusion region 71 is disposed on the second sidewall channel region 64.

- the bit line impurity diffusion region 71 functions as a common source / drain region of the first and second cell transistors 25 and 27.

- the upper surface 71 a of the bit line impurity diffusion region 71 coincides with the main surface 13 a of the SOI substrate 13.

- the bit line impurity diffusion region 71 is a region formed by doping the active region 19 with an impurity (for example, an n-type impurity when the semiconductor layer 13-3 is a p-type semiconductor).

- One second cell transistor 27 (selection transistor) is provided for each of the plurality of active regions 19.

- the second cell transistor 27 includes a second gate insulating film 59-2, a second gate electrode 74, a second sidewall channel region 64, a third sidewall channel region 76, a second A bottom channel region 77, a bit line impurity diffusion region 71, and a second capacitor impurity diffusion region 78 are provided.

- the second gate insulating film 59-2 is configured in the same manner as the first gate insulating film 59-1 described above except that it is provided so as to cover the inner surface of the second trench 22. .

- the second gate electrode 74 is provided so as to embed the lower portion of the second trench 22 via the second gate insulating film 59-2.

- As the material of the second gate electrode 74 a material similar to the material of the first gate electrode 61 described above can be used.

- the third side wall channel region 76 has a side surface 22c (a side surface intersecting with the X direction (a side surface orthogonal to the first embodiment)) of the second groove 22 and the second side wall channel region 76.

- the active region 19 semiconductor layer 13-3) located between the two element isolation regions 17 is formed.

- the second bottom channel region 77 is composed of an active region 19 disposed between the bottom surface 22a of the second groove 22 and the one surface 13-2a of the insulating layer 13-2.

- the side surfaces 77 a and 77 b (two side surfaces) of the second bottom channel region 77 are disposed opposite to each other in the Y direction and are in contact with the first element isolation region 14.

- the upper surface 77c of the second bottom channel region 77 is in contact with the second gate insulating film 59-2.

- the second bottom channel region 77 has end portions 77A and 77B (two end portions) arranged in the X direction.

- the end 77A (one end) is connected (integrated) with the second side wall channel region 64.

- the end 77B is connected (integrated) with the third sidewall channel region 76.

- the second sidewall channel region 64, the third sidewall channel region 76, and the second bottom channel region 77 are continuous from the second capacitor impurity diffusion region 78 to the bit line impurity diffusion region 71. To configure the channel.

- the second bottom channel region 77 is a flat channel region having an upper surface 77c and a lower surface 77d parallel to the one surface 13-1a of the semiconductor substrate body 13-1.

- the thickness M3 of the second bottom channel region 77 is 1/20 to 1/2 of the thickness M1 of the semiconductor layer 13-3. It is preferable to set within the range of / 5, more preferably within the range of 1/15 to 1/10 of the thickness M1 of the semiconductor layer 13-3.

- the thickness M3 of the second bottom channel region 77 can be the same as the thickness M2 of the first bottom channel region 66, for example.

- the width W2 of the second bottom channel region 77 is configured to be equal to the width W1 of the first bottom channel region 66.

- the second capacitor impurity diffusion region 78 is provided in the active region 19 located between the upper portion of the second element isolation region 17 and the upper portion of the second groove 22. ing. Thus, the second capacitor impurity diffusion region 78 is disposed on the third sidewall channel region 76.

- the second capacitor impurity diffusion region 78 functions as a source / drain region.

- An upper surface 78 a of the second capacitor impurity diffusion region 78 coincides with the main surface 13 a of the SOI substrate 13.

- the second capacitor impurity diffusion region 78 is a region formed by doping the active region 19 with an impurity (for example, an n-type impurity when the semiconductor layer 13-3 is a p-type semiconductor).

- the first interlayer insulating film 29 is provided on the first and second element isolation regions 14 and 17.

- a silicon nitride film (SiN film) having a thickness of 20 nm can be used as the first interlayer insulating film 29, for example.

- the first interlayer insulating film 29 functions as an etching mask when the second element isolation trench 17-1 is formed in the semiconductor layer 13-3 by anisotropic dry etching by being patterned.

- the buried insulating film 32 is disposed so as to bury the upper portions of the first grooves 21 and 22. As a result, the upper surfaces of the first and second gate electrodes 61 and 74 are covered with the buried insulating film 32.

- the upper surface of the buried insulating film 32 is flush with the upper surface of the first interlayer insulating film 29.

- a silicon oxide film SiO 2 film

- the bit line contact opening 33 is provided on the bit line impurity diffusion region 71 and exposes the upper surface 71 a of the bit line impurity diffusion region 71.

- the bit line contact opening 33 is an opening formed by removing the first interlayer insulating film 29 located on the bit line impurity diffusion region 71 by anisotropic dry etching.

- the bit line contact plug 35 is provided so as to fill the bit line contact opening 33. Thus, the lower end of the bit line contact plug 35 is in contact with the upper surface 71 a of the bit line impurity diffusion region 71.

- the bit line contact plug 35 can be made of, for example, a polysilicon film.

- the bit line 37 is provided on the first interlayer insulating film 29.

- the lower end of the bit line 37 is integrated with the bit line contact plug 35. Thereby, the bit line 37 is electrically connected to the bit line impurity diffusion region 71 via the bit line contact plug 35.

- the shape of the bit line 37 is a snake pattern.

- the snake pattern includes a third direction (V direction) forming an angle ⁇ with the X direction and an angle ⁇ with the X direction so as to be connected to the upper ends of the bit line contact plugs 35 aligned in the X direction. And a meandering pattern along the X direction above the first element isolation region 14 and alternately having a slope of the fourth direction (W direction).

- the film constituting the bit line 37 for example, a laminated film in which a titanium nitride film and a tungsten film are sequentially laminated, a titanium nitride film, or the like can be used.

- the cap insulating film 39 is provided so as to cover the upper surface of the bit line 37.

- the cap insulating film 39 protects the upper surface of the bit line 37 and functions as an etching mask when patterning a base material that becomes the bit line 37 by anisotropic etching (specifically, dry etching).

- the cap insulating film 39 for example, a silicon nitride film (SiN film) can be used.

- the first sidewall film 41 is provided so as to cover the side surface of the bit line 37 and the side surface of the cap insulating film 39.

- the second sidewall film 42 is provided so as to cover the outer wall surface of the first sidewall film 41.

- a silicon nitride film SiN film

- SiN film silicon nitride film

- the second interlayer insulating film 44 is provided on the first interlayer insulating film 29 so as to fill the space between the bit lines 37 via the first and second sidewall films 41 and 42.

- the upper surface of the second interlayer insulating film 44 is set to the upper surface of the cap insulating film 39.

- the second interlayer insulating film 44 for example, a silicon oxide film (SiO 2 film) formed by a CVD (Chemical Vapor Deposition) method, or a coating type insulating film formed by an SOG (Spin On Glass) method (Silicon oxide film (SiO 2 film)) or the like can be used.

- a silicon oxide film (SiO 2 film) formed by a CVD (Chemical Vapor Deposition) method or a coating type insulating film formed by an SOG (Spin On Glass) method (Silicon oxide film (SiO 2 film)) or the like

- SOG Spin On Glass

- the first capacitor contact hole 45-1 exposes the first interlayer insulating film 29, the buried insulating film 32, and the second interlayer insulating film 44 so as to expose the upper surface 68 a of the first capacitor impurity diffusion region 68. Is formed.

- the second capacitor contact hole 45-2 exposes the first interlayer insulating film 29, the buried insulating film 32, and the second interlayer insulating film 44 so as to expose the upper surface 78a of the second capacitor impurity diffusion region 78. Is formed.

- the first capacitor contact plug 46-1 is provided so as to embed the first capacitor contact hole 45-1.

- the lower end of the first capacitor contact plug 46-1 is in contact with the upper surface 68a of the first capacitor impurity diffusion region 68.

- the first capacitor contact plug 46-1 is electrically connected to the first capacitor impurity diffusion region 68.

- the upper surface of the first capacitor contact plug 46-1 is flush with the upper surface of the second interlayer insulating film 44.

- the first capacitor contact plug 46-1 can have, for example, a laminated structure in which a titanium nitride film and a tungsten film are sequentially laminated.

- the second capacitor contact plug 46-2 is provided so as to fill the second capacitor contact hole 45-2.

- the lower end of the second capacitor contact plug 46-2 is in contact with the upper surface 78a of the second capacitor impurity diffusion region 78.

- the second capacitor contact plug 46-2 is electrically connected to the second capacitor impurity diffusion region 78.

- the upper surface of the second capacitor contact plug 46-2 is flush with the upper surface of the second interlayer insulating film 44.

- the second capacitor contact plug 46-2 can have a stacked structure in which, for example, a titanium nitride film and a tungsten film are sequentially stacked.

- the stopper film 48 is provided on the upper surface of the cap insulating film 39 and the upper surface of the second interlayer insulating film 44.

- the stopper film 48 has a function of protecting elements (for example, the first and second cell transistors 25 and 27) arranged in the lower layer.

- the stopper film 48 for example, a silicon nitride film (SiN film) can be used.

- the third interlayer insulating film 49 is provided on the stopper film 48.

- a silicon oxide film SiO 2 film

- the cylinder hole 51 is provided so as to penetrate the stopper film 48 and the third interlayer insulating film 49 located on the first capacitor contact plug 46-1 and the second capacitor contact plug 46-2. .

- the cylinder hole 51 disposed on the first capacitor contact plug 46-1 exposes the upper surface of the first capacitor contact plug 46-1.

- the cylinder hole 51 disposed on the second capacitor contact plug 46-2 exposes the upper surface of the second capacitor contact plug 46-2.

- One capacitor 53 is provided for each of the first and second capacitive contact plugs 46-1 and 46-2.

- One capacitor 53 includes one lower electrode 84, a capacitive insulating film 85 common to the plurality of lower electrodes 84, and an upper electrode 86 that is a common electrode to the plurality of lower electrodes 84.

- the lower electrode 84 has a crown shape and is provided on the first and second capacitor contact plugs 46-1 and 46-2, respectively.

- the lower electrode 84 disposed on the first capacitor contact plug 46-1 is electrically connected to the first capacitor impurity diffusion region 68 via the first capacitor contact plug 46-1. ing.

- the lower electrode 84 disposed on the second capacitor contact plug 46-2 is electrically connected to the second capacitor impurity diffusion region 78 via the second capacitor contact plug 46-2. Yes.

- the capacitor insulating film 85 is disposed so as to cover the surface of the lower electrode 84 and the upper surface of the third interlayer insulating film 49.

- the capacity insulating film 85 has a thickness that does not fill the cylinder hole 51.

- the upper electrode 86 is provided so as to cover the surface of the capacitive insulating film 85.

- the upper electrode 86 is disposed so as to bury the inside of the lower electrode 84 in which the capacitive insulating film 85 is formed.

- the upper surface of the upper electrode 86 is disposed above the upper ends of the plurality of lower electrodes 84.

- one cell includes one cell transistor (the first cell transistor 25 or the second cell transistor 27) and one capacitor 53. Therefore, two cells are provided in one active region 19. Specifically, the two cells are a cell composed of the first cell transistor 25 and the capacitor 53 and a cell composed of the second cell transistor 27 and the capacitor 53.

- the fourth interlayer insulating film 55 is provided so as to cover the upper surface of the upper electrode film 86.

- a silicon oxide film SiO 2 film

- a via penetrating the fourth interlayer insulating film 55 and having the lower end connected to the upper electrode 86 may be provided. Further, a wiring (not shown) connected to the upper end of the via may be provided on the fourth interlayer insulating film 55.

- the protective film 57 is provided on the fourth interlayer insulating film 55.

- the protective film 57 has a function of protecting the wiring when a wiring (not shown) is provided on the fourth interlayer insulating film 55.

- the semiconductor device includes a first cell transistor 25 and a second cell transistor 27.

- the first cell transistor 25 includes a first sidewall channel region 63 constituted by an active region 19 located between the first trench 21 and the second element isolation region 17, and a first sidewall channel.

- a first side wall channel region 64 composed of a first capacitor impurity diffusion region 68 disposed on the region 63, an active region 19 located between the first and second trenches 21, 22,

- the second cell transistor 27 includes a third sidewall channel region 76 constituted by an active region 19 located between the second trench 22 and the second element isolation region 17, and a third sidewall channel.

- the second cell transistor 27 is provided in the same active region 19 as the first cell transistor 25.

- the semiconductor layer 13-3 (in other words, disposed between the bottom surface of the first and second grooves 21 and 22 and the insulating layer)

- the thickness of the first and second bottom channel regions 66, 77) is reduced. Therefore, it is possible to reduce the cross-sectional areas of the first and second bottom channel regions 66 and 77 serving as charge paths.

- the passage of electric charges is restricted by the first and second bottom channel regions 66 and 77.

- the probability of electrons reaching the capacitor contact plug (the first capacitor contact plug 46-1 or the second capacitor contact plug 46-2) of the adjacent cell can be reduced to about 1/10 to 1/100. it can.

- the first cell transistor 25 Repeat on / off.

- the second capacitor contact plug 46-2 electrically connected to the second cell transistor 27 is set to “High” and the second cell transistor 27 is held off.

- the first cell transistor 25 Repeat on / off.

- the second bottom channel region located below the second trench 22 of the second cell transistor 27 even if floating electrons are generated in the active region 19 located below the bit line impurity diffusion region 71, the second bottom channel region located below the second trench 22 of the second cell transistor 27.

- the small cross-sectional area of 77 is an obstacle. Therefore, the probability that electric charge can circulate becomes extremely small.

- the semiconductor device 10 according to the first embodiment can suppress a disturb failure between two cells arranged in the same active region 19.

- the first and second cell transistors are operated during the operation of the first transistor.

- the second bottom channel regions 66 and 77 can be completely depleted.

- the first and second cell transistors 25 and 27 have a fully depleted channel structure, the first and second cell transistors 25 and 25 formed by the first and second gate electrodes 61 and 74 are provided. 27 threshold control characteristics can be improved.

- FIG. 7 is an enlarged cross-sectional view of a portion different from the semiconductor device of the first embodiment in the memory cell portion of the semiconductor device according to the modification of the first embodiment of the present invention.

- FIG. 7 corresponds to the cut surface of FIG. In FIG. 7, the same components as those of the structure shown in FIG.

- the semiconductor device 95 according to the modification of the first embodiment is arranged such that the first gate insulating film 59-1 covers the side surfaces 66a and 66b of the first bottom channel region 66. Is done.

- the side surfaces 66a and 66b of the first bottom channel region 66 and the first gate electrode 61 are arranged to face each other via the first gate insulating film 59-1.

- the second gate insulating film 59-2 is disposed so as to cover the side surfaces 77a and 77b of the second bottom channel region 77.

- the side surfaces 77a and 77b of the second bottom channel region 77 and the second gate electrode 74 are arranged to face each other via the second gate insulating film 59-2.

- the semiconductor device 95 according to the modification of the first embodiment is configured in the same manner as the semiconductor device 10 except that the configuration described above is different from the semiconductor device 10 of the first embodiment.

- the semiconductor device 95 having the saddle fin structure can obtain the same effects as those of the semiconductor device 10 of the first embodiment.

- FIG. 8 to 14 are diagrams showing manufacturing steps of the semiconductor device according to the first embodiment of the present invention. Specifically, FIG. 8 is a cross-sectional view for explaining a manufacturing process of the SOI substrate.

- FIG. 9A is a plan view showing a memory cell portion of a semiconductor device being manufactured.

- 9B is a cross-sectional view of the structure shown in FIG. 9A in the direction of the AA line.

- FIG. 10 and 11 are cross-sectional views showing the memory cell portion of the semiconductor device being manufactured.

- FIG. 12A is a plan view showing a memory cell portion of a semiconductor device being manufactured.

- 12B is a cross-sectional view of the structure shown in FIG. 12A in the direction of the AA line.

- 13 and 14 are cross-sectional views showing the memory cell portion of the semiconductor device being manufactured.

- a semiconductor substrate for example, a p-type single crystal silicon wafer

- Oxygen is implanted by ion implantation from a main surface of the semiconductor substrate (main surface 13a of the SOI substrate 13) to a predetermined depth (for example, 250 to 350 nm).

- the semiconductor substrate is heated to form an insulating layer 13-2 (in this case, a silicon oxide film (SiO 2 film)).

- the semiconductor substrate body 13-1 made of the semiconductor substrate located below the insulating layer 13-2, the insulating layer 13-2, and the semiconductor layer made of the semiconductor substrate located above the insulating layer 13-2.

- the SOI substrate 13 in which 13-3 are sequentially stacked is formed.

- the thickness M1 of the semiconductor layer 13-3 can be set to, for example, 300 nm.

- the thickness M4 of the insulating layer 13-2 can be set to 10 nm, for example.

- a well-known commercially available SOI substrate may be used.

- the semiconductor substrate body 13-1 and the semiconductor layer 13-3 are made of p-type single crystal silicon will be described as an example.

- a known technique for example, STI (Shallow trench isolation) method

- STI shallow trench isolation

- a first element isolation region 14 is formed.

- a plurality of first element isolation regions 14 are formed in the Y direction.

- the plurality of first element isolation regions 14 are formed so that the upper surfaces thereof are flush with the main surface 13 a of the SOI substrate 13.

- the first element isolation region 14 extends in the Y direction of the SOI substrate 13 on which the first element isolation region 14 is formed, and is formed on the one surface 13-2a of the insulating layer 13-2.

- a second element isolation region 17-1 that reaches the second element isolation region 17-1 for example, a silicon oxide film (SiO 2 film)

- SiO 2 film silicon oxide film

- a plurality of second element isolation regions 17 are formed in the X direction.

- the plurality of second element isolation regions 17 are formed so that the upper surfaces thereof are flush with the main surface 13 a of the SOI substrate 13.

- the width W3 of the active region 19 in the Y direction can be set to 40 nm, for example.

- an n-type impurity is implanted into the upper surfaces 19a of the plurality of active regions 19 (main surface 13a of the SOI substrate 13) by ion implantation, thereby forming an impurity diffusion layer 98 on the plurality of active regions 19.

- the impurity diffusion layer 98 is divided into the first capacitor impurity diffusion region 68, the bit line impurity diffusion region 71, and the second capacitor impurity diffusion region 78 shown in FIG.

- the structure shown in FIGS. 9A and 9B (specifically, the upper surface of the first element isolation region 14, the upper surface of the second element isolation region 17, Then, a first interlayer insulating film 29 covering the upper surface 19a) of the active region 19 is formed.

- the first interlayer insulating film 29 made of the silicon nitride film (SiN film) is formed.

- the first and second opening grooves 29A, 29B is formed.

- the first opening groove 29 ⁇ / b> A is formed so as to correspond to the formation region of the first groove 21.

- the second opening groove 29 ⁇ / b> B is formed so as to correspond to the formation region of the second groove 22.

- the plurality of active regions 19 and the first element isolation regions 14 are formed by anisotropic dry etching using the first interlayer insulating film 29 in which the first and second opening grooves 29A and 29B are formed as an etching mask.

- first and second grooves 21 and 22 having a depth that does not reach the one surface 13-2a of the insulating layer 13-2 are formed.

- the first capacitance impurity diffusion region 68 disposed between the side surface 21 b of the first groove 21 and the second element isolation region 17, the first groove 21, and the second groove 22 A bit line impurity diffusion region 71 disposed therebetween, a second capacitor impurity diffusion region 78 disposed between the side surface 22c of the second trench 22 and the second element isolation region 17, and a first First sidewall channel region 63 disposed between capacitor impurity diffusion region 68 and insulating layer 13-2, and disposed between bit line impurity diffusion region 71 and insulating layer 13-2.

- the thicknesses M2 and M3 of the first and second bottom channel regions 66 and 77 are equal to the thickness of the semiconductor layer 13-3. It is formed to be within a range of 1/20 to 1/5 of M1.

- the first and second trenches 21 and 22 are such that the thicknesses M2 and M3 of the first and second bottom channel regions 66 and 77 are 1/15 to 1 to the thickness M1 of the semiconductor layer 13-3. It is good to form so that it may become in the range of / 10.

- the first and second trenches 21 and 22 are, for example, the thickness M2 of the first and second bottom channel regions 66 and 77. It is preferable to form M3 within a range of 20 to 30 nm.

- the first bottom channel region 66 formed by the above method is a flat channel region having an upper surface 66c and a lower surface 66d parallel to one surface 13-1a of the semiconductor substrate body 13-1.

- An end portion 66 ⁇ / b> A arranged in the X direction is connected (integrated) with the first side wall portion channel region 63.

- An end 66B arranged in the X direction is connected (integrated) with the second side wall channel region 64.

- the second bottom channel region 77 formed by the above method is a flat channel region having an upper surface 77c and a lower surface 77d parallel to the one surface 13-1a of the semiconductor substrate body 13-1.

- the end 77A arranged in the X direction is connected (integrated) with the second side wall channel region 64.

- the end portion 77B arranged in the X direction is connected (integrated) with the side wall channel region 76 of the third rib.

- a first gate insulating film 59-1 (in this case, a silicon oxide film (SiO 2 film)) covering the inner surface of the first trench 21 and a second gate are formed by a known method (for example, thermal oxidation method).

- a second gate insulating film 59-2 (in this case, a silicon oxide film (SiO 2 film)) covering the inner surface of the trench 22 is formed in a lump.

- the first gate electrode 61 filling the lower portion of the first trench 21 via the first gate insulating film 59-1, and the second gate insulating film 59-2.

- a second gate electrode 74 that fills the lower portion of the second trench 22 is collectively formed.

- the conductive film Is etched back, so that the first and second gate electrodes 61 and 74 are collectively formed.

- the first cell transistor 25 includes a first gate insulating film 59-1, a first gate electrode 61, a first sidewall channel region 63, a second sidewall channel region 64, and a first bottom channel region 66.

- the first capacitor impurity diffusion region 68 and the bit line impurity diffusion region 71 are provided.

- the second cell transistor 27 includes a second gate insulating film 59-2, a second gate electrode 74, a second sidewall channel region 64, a third sidewall channel region 76, and a second bottom channel region 77.

- a bit line impurity diffusion region 71 and a second capacitor impurity diffusion region 78 is provided for one active region 19.

- the first cell transistor 25 includes a first gate insulating film 59-1, a first gate electrode 61, a first sidewall channel region 63, a second sidewall channel region 64, and a first bottom channel region 66.

- the first capacitor impurity diffusion region 68 and the bit line impurity diffusion region 71 are provided.

- a buried insulating film 32 that fills the upper portions of the first and second grooves 21 and 22 is formed by a known method. At this time, the buried insulating film 32 is formed so that the upper surface thereof is flush with the upper surface of the first interlayer insulating film 29.

- the first interlayer insulating film 29 located on the bit line impurity diffusion region 71 is removed by a photolithography technique and a dry etching technique, thereby exposing the upper surface 71a of the bit line impurity diffusion region 71.

- a contact opening 33 is formed.

- bit line contact plug 35 that fills the bit line contact opening 33 and has the lower end connected to the upper surface 71a of the bit line impurity diffusion region 71 is formed by a well-known method.

- bit line contact plug 35 is formed so that the upper surface thereof is flush with the upper surface of the buried insulating film 32 and the upper surface of the first interlayer insulating film 29.

- the conductive film constituting the bit line contact plug 35 for example, a laminated film in which a titanium nitride (TiN) film and a tungsten (W) film are sequentially laminated can be used.

- TiN titanium nitride

- W tungsten

- a metal film 101 for example, a titanium nitride film (TiN film) and a tungsten film (W film) covering the upper surface of the structure shown in FIG. 11 is sequentially stacked. Film) and the silicon nitride film 102 are sequentially stacked.

- the cap insulating film 39 made of the silicon nitride film 102 is formed by patterning the silicon nitride film 102 by a photolithography technique and a dry etching technique. At this time, the cap insulating film 39 is formed to have a snake pattern.

- the metal film 101 is patterned by anisotropic dry etching using the cap insulating film 39 as a mask, whereby the bit line 37 made of the metal film 101 is formed with a snake pattern.

- bit line 37 The lower end of the bit line 37 is connected to the bit line contact plug 35. Thereby, the bit line 37 is electrically connected to the bit line impurity diffusion region 71 via the bit line contact plug 35.

- a first sidewall film 41 and a second sidewall film 42 that cover the side surface of the cap insulating film 39 and the side surface of the bit line 37 are sequentially formed by a well-known method.

- the interlayer insulating film 44 is formed.

- the second interlayer insulating film 44 is formed so that the upper surface thereof is flush with the upper surface of the cap insulating film 39.

- the first and second interlayer insulating films 29 and 44 located on the first capacitor impurity diffusion region 68 and the second capacitor impurity diffusion region 78 are formed by a self-aligned contact method (SAC method).

- SAC method self-aligned contact method

- the first capacitor contact plug 46-1 having the first capacitor contact hole 45-1 buried therein and the lower end connected to the first capacitor impurity diffusion region 68, and the second capacitor A second capacitor contact plug 46-2 that fills the contact hole 45-2 and is connected to the second capacitor impurity diffusion region 78 is collectively formed.

- the first and second capacitor contact plugs 46-1 and 46-2 are formed so that the upper surfaces thereof are flush with the upper surface of the second interlayer insulating film 44.

- a stopper film 48 is formed on the structure shown in FIG. 13 by a known method.

- the stopper film 48 is formed by, for example, forming a silicon nitride film (SiN film).

- a third interlayer insulating film 49 is formed on the stopper film 48 by a known method.

- the third interlayer insulating film 49 is formed, for example, by forming a silicon oxide film (SiO 2 film).

- the stopper film 48 and the third interlayer insulating film 49 located on the first capacitor contact plug 46-1 and the second capacitor contact plug 46-2 are removed by photolithography technique and dry etching technique. As a result, the cylinder hole 51 exposing the upper surface of the first capacitor contact plug 46-1 or the upper surface of the second capacitor contact plug 46-2 is formed.

- the lower electrode 84 that covers the inner surface of the cylinder hole 51 is formed by a known method.

- the lower electrode 84 having a crown shape is disposed on the first and second capacitor contact plugs 46-1 and 46-2.

- a capacitor insulating film 85 that continuously covers the inner surfaces of the plurality of lower electrodes 84 and the upper surface of the third interlayer insulating film 49 is formed by a known method.

- an upper electrode 86 having a flat upper surface embedded in the plurality of lower electrodes 84 and disposed above the capacitor insulating film 85 is formed through the capacitor insulating film 85.

- one capacitor 53 (a capacitor composed of the lower electrode 84, the capacitor insulating film 85, and the upper electrode 86) is provided for each of the plurality of first and second capacitor contact plugs 46-1 and 46-2. Is formed.

- one active region 19 includes two cells (specifically, a cell composed of the first cell transistor 25 and the capacitor 53, a second cell transistor 27, A cell formed of the capacitor 53 is formed.

- a fourth interlayer insulating film 55 (for example, a silicon oxide film (SiO 2 film)) covering the upper surface of the upper electrode film 86 is formed by a known method.

- a via that penetrates through the fourth interlayer insulating film 55 and has a lower end connected to the upper electrode 86 may be formed. Further, a wiring (not shown) connected to the upper end of the via may be formed on the fourth interlayer insulating film 55.

- a protective film 57 is formed on the fourth interlayer insulating film 55, whereby the memory cell portion 11 of the semiconductor device 10 of the first embodiment is manufactured.

- FIG. 15 is an isometric view illustrating the main part of the memory cell portion of the semiconductor device of the second embodiment by isometric projection.

- FIG. 16 is an enlarged cross-sectional view of the memory cell portion surrounded by the region B shown in FIG.

- a DRAM is taken as an example as an example of the semiconductor device 110 according to the second embodiment.

- the same components as those of the semiconductor device 10 of the first embodiment are denoted by the same reference numerals.

- the semiconductor device 110 according to the second embodiment includes a first groove 21, a second groove 22, and a first groove constituting the semiconductor device 10 according to the first embodiment.

- the semiconductor device 10 except that it has a first groove 113, a second groove 114, a first cell transistor 116, and a second cell transistor 117 in place of the cell transistor 25 and the second cell transistor 27. It is configured in the same way.

- the first groove 113 has the same configuration as the first groove 21 described in the first embodiment except that the bottom surface 113a has a flat portion and a raised portion.

- the second groove 114 has the same configuration as the second groove 22 described in the first embodiment except that the bottom surface 114a has a flat portion and a raised portion.

- the first cell transistor 116 has a first bottom channel region 121 in place of the first bottom channel region 66 constituting the first cell transistor 25 described in the first embodiment.

- the configuration is the same as that of the first cell transistor 25.

- the first bottom channel region 121 has the same configuration as the second bottom channel region 122 shown in FIG. 16 except that the arrangement position thereof is different from that of the second bottom channel region 122.

- the first bottom channel region 121 is disposed between the bottom surface 121a of the first groove 121 and the insulating layer 13-2, and has a flat channel region 124 and a protruding channel region 125.

- the flat channel region 124 has an upper surface 124c and a lower surface 124d parallel to the one surface 13-1a of the semiconductor substrate body 13-1.

- the side surfaces 124 a and 124 b of the flat channel region 124 arranged to face each other in the Y direction are in contact with the first element isolation region 14. Further, the upper surface 124c of the flat channel region 124 is in contact with the first gate insulating film 59-1.

- the lower surface 124d of the flat channel region 124 is in contact with the one surface 13-2a of the insulating layer 13-2.

- one end is integrated with the first side wall channel region 63.

- the other end is integrated with the second side wall channel region 64.

- the thickness M5 of the flat channel region 124 configured as described above can be set to, for example, 25 nm.

- the protruding channel region 125 is a channel region protruding upward from the upper surface 124 c of the flat channel region 124, and is integrated with the flat channel region 124.

- the protruding channel region 125 has two inclined side surfaces 125a and 125b, and the shape of the cut surface is a triangle.

- the protruding amount H1 of the protruding channel region 125 when the upper surface 124c of the flat channel region 124 is used as a reference can be, for example, 25 nm.

- the second cell transistor 117 has a second bottom channel region 122 in place of the second bottom channel region 77 constituting the second cell transistor 27 described in the first embodiment.

- the configuration is the same as that of the second cell transistor 27.

- the second bottom channel region 122 is disposed between the bottom surface 122a of the second groove 122 and the insulating layer 13-2, and ends in the X direction are the second side wall channel region 64 and the third side wall.

- the configuration is the same as that of the first bottom channel region 121 described above except that it is integrated with the partial channel region 76.

- the second bottom channel region 122 has a flat channel region 124 and a protruding channel region 125.

- the semiconductor device 110 of the second embodiment configured as described above can obtain the same effects as the semiconductor device 10 of the first embodiment.

- first and second bottom channel regions 121 and 122 are maintained fully depleted, and the cross-sectional area is increased as compared with the first and second bottom channels 66 and 77 described in the first embodiment. It becomes possible to make it. Therefore, it is possible to increase Ion and improve the S characteristics when the first and second cell transistors 116 and 117 are operated.

- S characteristic is a common name in the industry for a subthreshold coefficient (S factor), and means a gate voltage required to change the drain current value by one digit. Therefore, the smaller the gate voltage, the more effectively the on / off control of the transistor can be achieved, which contributes to higher speed operation and lower power consumption.

- S factor subthreshold coefficient

- FIG. 17 is an enlarged cross-sectional view of a portion different from the semiconductor device of the second embodiment in the memory cell portion of the semiconductor device according to the modification of the second embodiment of the present invention.

- the same components as those of the structure shown in FIG. 17 are identical components as those of the structure shown in FIG. 17

- the side surfaces 124a and 124b of the flat channel region 124 are covered with the first gate insulating film 59-1 (not shown in FIG. 17) or the second gate insulating film 59-2. Yes.

- the side surfaces 124a and 124b of the planar channel region 124 are connected to the first gate electrode 61 (not shown in FIG. 17) or the first gate insulating film 59-1 or the second gate insulating film 59-2.

- the semiconductor device 130 according to the modified example of the second embodiment is configured similarly to the semiconductor device 110 of the second embodiment.

- the semiconductor device 130 having the saddle fin structure can obtain the same effects as those of the semiconductor device 10 of the first embodiment. Further, the semiconductor device 130 maintains the fully depleted first and second bottom channel regions 121 and 122, and the first and second bottom channels 66 and 77 described in the first embodiment. Also, the cross-sectional area can be increased. Therefore, the semiconductor device 130 can increase Ion and improve the S characteristic when the first and second cell transistors 116 and 117 are operated.

- 18 and 19 are cross-sectional views showing the steps of the semiconductor device according to the second embodiment of the present invention. 18 and 19, the same components as those shown in FIGS. 15 and 16 are denoted by the same reference numerals.

- FIGS. 9A and 9B is formed by sequentially performing the process shown in FIG. 8 described in the first embodiment and the process shown in FIGS. 9A and 9B.

- a step of forming the first interlayer insulating film 29 having the first and second opening grooves 29A and 29B is performed.

- the anisotropic process is performed using an etching condition in which the etching selectivity of the first element isolation region 14 is larger than that of the semiconductor layer 13-3 (for example, an etching condition with a selectivity of about 3 to 10).

- the semiconductor layer 13-3 and the first element isolation region 14 are etched through the first interlayer insulating film 29 having the first and second opening grooves 29A and 29B by the characteristic dry etching.

- the first element isolation region 14 is etched faster than the semiconductor layer 13-3.

- the upper surface of the first element isolation region 14 is disposed below the upper surface of the semiconductor layer 13-3, and the semiconductor layer 13-3 separated from the first element isolation region 14 is provided.

- a protruding portion having a mountain shape protruding upward is formed in the central portion.

- the first element isolation region 14 and the semiconductor layer 13-3 corresponding to the formation region of the second trench 114 are formed in the first element isolation shown in FIG.

- the region 14 and the semiconductor layer 13-3 are etched into the same shape.

- etching conditions for example, the selection ratio is about 3 to 10 having high anisotropy and a higher selection ratio of the semiconductor layer 13-3 than the first element isolation region 14 are used.

- the first and second opening grooves 29A and 29B (not shown in FIG. 19) are formed under the condition that the shape of the protruding portion remains at the upper end of the semiconductor layer 13-3 by anisotropic etching.

- the semiconductor layer 13-3 and the first element isolation region 14 that are located are etched.

- first and second bottom channel regions 121 and 122 (the second bottom channel region 122 is not shown in FIG. 19) including the flat channel region 124 and the protruding channel region 125 are collectively formed.

- the anisotropic etching is preferably performed so that the height H1 of the top of the protruding channel region 125 with respect to the upper surface of the first element isolation region 14 after etching is 50 nm or less.

- the memory cell unit 111 of the semiconductor device 110 of the second embodiment shown in FIG. 15 is manufactured.

- FIG. 20 is an isometric view illustrating the main part of the memory cell portion of the semiconductor device of the third embodiment by isometric projection.