KR102222438B1 - Semiconductor device and display device - Google Patents

Semiconductor device and display device Download PDFInfo

- Publication number

- KR102222438B1 KR102222438B1 KR1020207030938A KR20207030938A KR102222438B1 KR 102222438 B1 KR102222438 B1 KR 102222438B1 KR 1020207030938 A KR1020207030938 A KR 1020207030938A KR 20207030938 A KR20207030938 A KR 20207030938A KR 102222438 B1 KR102222438 B1 KR 102222438B1

- Authority

- KR

- South Korea

- Prior art keywords

- insulating layer

- layer

- oxide

- oxide semiconductor

- gate insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H01L29/7869—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H01L29/78606—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6757—Thin-film transistors [TFT] characterised by the structure of the channel, e.g. transverse or longitudinal shape or doping profile

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/40—Crystalline structures

- H10D62/405—Orientations of crystalline planes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/681—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered

- H10D64/685—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered being perpendicular to the channel plane

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/691—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator comprising metallic compounds, e.g. metal oxides or metal silicates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/693—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator the insulator comprising nitrogen, e.g. nitrides, oxynitrides or nitrogen-doped materials

Landscapes

- Thin Film Transistor (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Physics & Mathematics (AREA)

- Electroluminescent Light Sources (AREA)

- Nonlinear Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Liquid Crystal (AREA)

- Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Bipolar Transistors (AREA)

- Noodles (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

Abstract

정전기 방전 손상으로 인해 수율 감소가 예방되는 높은 신뢰도의 반도체 장치가 제공된다. 게이트 전극 층, 게이트 전극 층 위의 게이트 절연 층, 게이트 절연 층 위의 산화물 절연 층, 산화물 절연 층 위에서 산화물 절연 층과 접촉하고 게이트 전극 층과 중첩하는 산화물 반도체 층, 및 산화물 반도체 층에 전기적으로 연결된 소스 전극 층 및 드레인 전극 층을 포함하는 반도체 장치가 제공된다. 게이트 절연 층은 질소를 함유하는 실리콘 막을 포함한다. 산화물 절연 층은 산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유한다. 게이트 절연 층의 두께는 산화물 절연 층의 두께보다 더 두껍다.There is provided a highly reliable semiconductor device in which yield reduction is prevented due to electrostatic discharge damage. The gate electrode layer, the gate insulating layer over the gate electrode layer, the oxide insulating layer over the gate insulating layer, the oxide semiconductor layer contacting the oxide insulating layer over the oxide insulating layer and overlapping the gate electrode layer, and electrically connected to the oxide semiconductor layer. A semiconductor device comprising a source electrode layer and a drain electrode layer is provided. The gate insulating layer includes a silicon film containing nitrogen. The oxide insulating layer contains one or more metal elements selected from constituent elements of the oxide semiconductor layer. The thickness of the gate insulating layer is thicker than that of the oxide insulating layer.

Description

본 명세서 등에 개시된 본 발명의 일 실시예는, 반도체 장치 및 반도체 장치를 제작하는 방법에 관한 것이다.An embodiment of the present invention disclosed in this specification and the like relates to a semiconductor device and a method of manufacturing the semiconductor device.

본 명세서 등에 있어서, 반도체 장치는 일반적으로 반도체 특성들을 이용함으로써 기능할 수 있는 디바이스를 의미하고, 전기-광학 디바이스, 발광 표시 장치, 반도체 회로, 및 전자 디바이스는 모두 반도체 장치들이다.In this specification and the like, a semiconductor device generally means a device that can function by using semiconductor properties, and an electro-optical device, a light emitting display device, a semiconductor circuit, and an electronic device are all semiconductor devices.

절연 표면을 갖는 기판 위에 형성된 반도체 박막을 사용하여 트랜지스터를 형성하기 위한 기술에 주의가 집중되어왔다. 이러한 트랜지스터는 집적 회로(IC) 또는 이미지 표시 장치(간단히 표시 장치라고도 칭함)와 같은 넓은 범위의 전자 디바이스들에 적용된다. 실리콘-계 반도체 재료가 트랜지스터에 적용될 수 있는 반도체 박막을 위한 재료로서 널리 알려져 있다. 다른 재료로서, 산화물 반도체가 주의를 끌고 있다.Attention has been focused on a technique for forming a transistor using a semiconductor thin film formed on a substrate having an insulating surface. Such transistors are applied to a wide range of electronic devices such as integrated circuits (ICs) or image display devices (also simply referred to as display devices). Silicon-based semiconductor materials are widely known as materials for semiconductor thin films that can be applied to transistors. As another material, oxide semiconductors are attracting attention.

예컨대, 산화물 반도체로서 산화 아연 또는 In-Ga-Zn계 산화물 반도체를 사용하여 트랜지스터를 형성하는 기술이 개시된다(특허문헌 1 및 2 참조).For example, a technique for forming a transistor using zinc oxide or an In-Ga-Zn-based oxide semiconductor as an oxide semiconductor is disclosed (see

산화물 반도체들을 갖는 반도체 장치들의 대량 생산을 위한 개발 비용 및 속도를 고려하여, 실제 사용에 현재의 대량 생산 기술, 즉 비정질 실리콘 또는 다결정 실리콘과 같은 실리콘계 반도체 재료를 위한 트랜지스터 구조, 공정 조건들, 생산 장치들, 등을 사용하는 것이 바람직하다.Considering the development cost and speed for mass production of semiconductor devices having oxide semiconductors, the current mass production technology for practical use, i.e., transistor structure, process conditions, and production equipment for silicon-based semiconductor materials such as amorphous silicon or polycrystalline silicon It is preferable to use wild, etc.

그러나, 산화물 반도체 내의 캐리어 생성의 메커니즘은 실리콘계 반도체 재료에서의 캐리어 생성 메커니즘과 크게 다르다. 산화물 반도체의 물리적인 특성들은 트랜지스터의 특성들 또는 신뢰도에 크게 영향을 미친다.However, the mechanism of carrier generation in the oxide semiconductor is significantly different from the carrier generation mechanism in the silicon-based semiconductor material. The physical properties of the oxide semiconductor greatly affect the properties or reliability of the transistor.

특히, 실리콘계 반도체 재료를 위해 사용된 게이트 절연 층이 산화물 반도체를 위하여 사용될 때, 게이트 절연 층은 산화물 반도체와의 훌륭한 계면 특성들을 제공하지 않는다. 따라서, 산화물 반도체를 포함하는 반도체 장치에서 사용하는데 적합한 게이트 절연 층의 개발이 요구되어왔다.In particular, when the gate insulating layer used for the silicon-based semiconductor material is used for the oxide semiconductor, the gate insulating layer does not provide excellent interfacial properties with the oxide semiconductor. Accordingly, there has been a demand for development of a gate insulating layer suitable for use in a semiconductor device including an oxide semiconductor.

비정질 실리콘 또는 다결정 실리콘과 같은 실리콘계 반도체 재료를 사용하여 형성된 트랜지스터를 포함하는 반도체 장치를 위해, 제 8 세대(2160mm폭×2460mm길이) 또는 이후의 유리 기판이 사용될 수 있다. 따라서, 이러한 반도체 장치는 높은 생산성 및 낮은 비용의 장점들을 갖는다. 그러나, 이러한 유리 기판을 사용하는 경우, 높은 절연 특성들과 큰 면적으로 인해, 정전기 방전(ESD) 손상의 문제가 발생한다. 이러한 문제는 산화물 반도체 재료를 사용하는 경우에도 필수적으로 고려되어야 한다.For a semiconductor device including a transistor formed using a silicon-based semiconductor material such as amorphous silicon or polycrystalline silicon, a glass substrate of the eighth generation (2160 mm width x 2460 mm length) or later may be used. Therefore, such a semiconductor device has advantages of high productivity and low cost. However, when such a glass substrate is used, a problem of electrostatic discharge (ESD) damage occurs due to high insulating properties and a large area. This problem must be considered indispensably even when an oxide semiconductor material is used.

이러한 기술적인 배경의 견지에서, 본 발명의 일 실시예의 목적은, 실제 사용에 적용되어왔던 대량 생산 기술로부터 트랜지스터 구조, 공정 조건들, 생산 장치, 등에서 적은 수의 변경들을 통해 고도로 신뢰할 수 있고 전기적으로 안정적인 반도체 장치를 제공하는 것이다.In view of this technical background, the object of an embodiment of the present invention is to be highly reliable and electrically through a small number of changes in transistor structure, process conditions, production equipment, etc. from mass production technology that has been applied in actual use. It is to provide a stable semiconductor device.

본 발명의 일 실시예의 다른 목적은 정전기 방전 손상으로 인한 수율 감소가 방지되는 반도체 장치를 제공하는 것이다.Another object of an embodiment of the present invention is to provide a semiconductor device in which a yield decrease due to electrostatic discharge damage is prevented.

개시된 발명의 일 실시예는, 게이트 전극 층과 산화물 반도체 층 사이에서 게이트 전극 층에 근접한 측으로부터 순서대로 적층된, 질소를 함유하는 실리콘 막과, 산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 산화물 절연 층을 포함하는 구조가 반도체 장치이다.One embodiment of the disclosed invention includes a silicon film containing nitrogen and at least one metal element selected from constituent elements of the oxide semiconductor layer, which are sequentially stacked between the gate electrode layer and the oxide semiconductor layer from the side adjacent to the gate electrode layer. A structure including an oxide insulating layer containing them is a semiconductor device.

질소를 함유하는 실리콘 막은 산화 실리콘 막보다 더 높은 비유전율을 갖고, 따라서 등가 커패시턴스를 위해 더 두꺼운 두께를 필요로 한다. 따라서, 질소를 함유하는 실리콘 막이 게이트 절연 층으로 사용될 때, 게이트 절연 층의 물리적인 두께는 증가될 수 있고, 이는 내전압의 감소를 줄이고, 바람직하게는 내전압을 증가시키는 것을 가능케 한다. 따라서, 이러한 게이트 절연 층을 포함하는 반도체 장치에 대한 정전기 방전 손상을 줄이는 것이 가능하다.A silicon film containing nitrogen has a higher relative dielectric constant than a silicon oxide film, and thus requires a thicker thickness for equivalent capacitance. Therefore, when a silicon film containing nitrogen is used as the gate insulating layer, the physical thickness of the gate insulating layer can be increased, which makes it possible to reduce a decrease in withstand voltage, and preferably increase withstand voltage. Accordingly, it is possible to reduce electrostatic discharge damage to a semiconductor device including such a gate insulating layer.

질소를 함유하는 실리콘 막의 두께가 325nm 이상 550nm 이하, 보다 바람직하게는 355nm 이상 550nm 이하인 것이 바람직하다. 질소를 함유하는 실리콘 막으로서, 질화 실리콘 막이 바람직하게 사용된다.It is preferable that the thickness of the silicon film containing nitrogen is 325 nm or more and 550 nm or less, more preferably 355 nm or more and 550 nm or less. As the silicon film containing nitrogen, a silicon nitride film is preferably used.

질소를 함유하는 실리콘 막은 비정질 실리콘 또는 다결정 실리콘과 같은 실리콘계 반도체 재료를 위한 게이트 절연 층으로서 실제 사용되어왔고, 따라서 동일한 공정 조건들, 생산 장치들 등이 채용될 수 있다. 따라서, 게이트 절연 층으로서 질소를 함유하는 실리콘 막의 사용은 산화물 반도체를 갖는 트랜지스터들이 낮은 비용으로 대량 생산될 수 있게 한다.A silicon film containing nitrogen has actually been used as a gate insulating layer for a silicon-based semiconductor material such as amorphous silicon or polycrystalline silicon, and thus the same process conditions, production devices, and the like can be employed. Therefore, the use of a silicon film containing nitrogen as the gate insulating layer enables transistors having an oxide semiconductor to be mass-produced at low cost.

산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 산화물 절연 층이 산화물 반도체 층과 접촉하여 제공될 때, 산화물 절연 층과 산화물 반도체 층 사이의 계면은 양호한 상태로 유지될 수 있고, 열화되는 것이 방지될 수 있다. 특히, 산화물 절연 층과 산화물 반도체 층 사이의 계면에서 캐리어의 포획은 감소되어, 트랜지스터의 광열화(예, 음의 바이어스 온도 응력 열화)가 감소될 수 있고, 이에 의해 고도로 신뢰할 수 있는 트랜지스터가 얻어질 수 있다.When an oxide insulating layer containing one or more metal elements selected from the constituent elements of the oxide semiconductor layer is provided in contact with the oxide semiconductor layer, the interface between the oxide insulating layer and the oxide semiconductor layer can be maintained in a good state, and deteriorated. Can be prevented. In particular, the trapping of carriers at the interface between the oxide insulating layer and the oxide semiconductor layer is reduced, so that photodeterioration of the transistor (e.g., negative bias temperature stress degradation) can be reduced, thereby obtaining a highly reliable transistor. I can.

즉, 본 발명의 일 실시예에 따라, 질소를 함유하는 실리콘 막, 산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 산화물 절연 층, 및 산화물 반도체 층의 적층 구조가 실리콘계 반도체 재료들을 위한 실제 사용에 적용된 대량 생산 기술을 부분적으로 사용하여 형성되고; 실리콘계 반도체 재료들을 사용하여 형성된 반도체 장치들의 것들과는 다른 새로운 유리한 효과를 갖는 반도체 장치를 제공하는 것이 가능하다. 특히, 예컨대 다음의 구조들이 채용될 수 있다.That is, according to an embodiment of the present invention, a stacked structure of a silicon film containing nitrogen, an oxide insulating layer containing one or more metal elements selected from constituent elements of the oxide semiconductor layer, and the oxide semiconductor layer is formed of silicon-based semiconductor materials. Is formed using in part mass production techniques applied to actual use for; It is possible to provide a semiconductor device with new advantageous effects different from those of semiconductor devices formed using silicon-based semiconductor materials. In particular, for example, the following structures may be employed.

본 발명의 일 실시예는, 게이트 전극 층, 게이트 전극 층 위의 게이트 절연 층, 게이트 절연 층 위의 산화물 절연 층, 산화물 절연 층 위에 있고 산화물 절연 층과 접촉하고, 게이트 전극 층과 중첩하는 산화물 반도체 층, 및 산화물 반도체 층에 전기적으로 연결된 소스 전극 층 및 드레인 전극 층을 포함하는 반도체 장치이다. 게이트 절연 층은 질소를 함유하는 실리콘 막을 포함한다. 산화물 절연 층은 산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유한다. 게이트 절연 층의 두께는 산화물 절연 층의 두께보다 더 두껍다.An embodiment of the present invention is a gate electrode layer, a gate insulating layer over the gate electrode layer, an oxide insulating layer over the gate insulating layer, an oxide semiconductor over the oxide insulating layer and in contact with the oxide insulating layer, and overlapping the gate electrode layer. A semiconductor device comprising a layer, and a source electrode layer and a drain electrode layer electrically connected to the oxide semiconductor layer. The gate insulating layer includes a silicon film containing nitrogen. The oxide insulating layer contains one or more metal elements selected from constituent elements of the oxide semiconductor layer. The thickness of the gate insulating layer is thicker than that of the oxide insulating layer.

위에 기술한 반도체 장치에 있어서, 산화물 반도체 층 및 산화물 절연 층의 단부들이 서로 배향되는 것이 바람직하다. 본 명세서 등에서 "배향된다는 것"은 "실질적으로 배향되는 것"을 포함한다. 예컨대, 동일한 마스크를 사용하여 에칭된 적층 구조에 포함된 층 A의 단부와 층 B의 단부는 서로 배향되는 것으로 간주된다.In the semiconductor device described above, it is preferable that the ends of the oxide semiconductor layer and the oxide insulating layer are oriented with each other. In this specification and the like, "to be oriented" includes "substantially oriented". For example, the ends of the layer A and the ends of the layer B included in the laminated structure etched using the same mask are considered to be oriented to each other.

산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 산화물 절연 층과, 산화물 반도체 층의 아래에서 산화물 반도체 층과 접촉하여 제공되는 질소를 함유하는 실리콘 막의 적층 구조에 부가하여, 산화물 반도체 층 위에서 산화물 반도체 층과 접촉하는 적층 구조가 또한 제공될 수 있다. 이러한 구조는 반도체 장치가 더 안정된 전기 특성들을 갖고, 및/또는 정전기 방전으로 인한 손상으로부터 예방될 수 있게 한다.In addition to the lamination structure of an oxide insulating layer containing one or more metal elements selected from constituent elements of the oxide semiconductor layer, and a silicon film containing nitrogen provided in contact with the oxide semiconductor layer under the oxide semiconductor layer, an oxide semiconductor layer A stacked structure in contact with the oxide semiconductor layer above may also be provided. This structure enables the semiconductor device to have more stable electrical properties and/or to be prevented from damage due to electrostatic discharge.

즉, 본 발명의 다른 실시예는, 게이트 전극 층, 게이트 전극 층 위의 게이트 절연 층, 게이트 절연 층 위의 제 1 산화물 절연 층, 제 1 산화물 절연 층 위에 있고 제 1 산화물 절연 층과 접촉하고, 게이트 전극 층과 중첩하는 산화물 반도체 층, 산화물 반도체 층에 전기적으로 연결된 소스 전극 층 및 드레인 전극 층, 소스 전극 층 및 드레인 전극 층을 덮고 산화물 반도체 층의 일부와 접촉하는 제 2 산화물 절연 층, 및 제 2 산화물 절연 층 위의 보호 절연 층을 포함하는 반도체 장치이다. 게이트 절연 층과 보호 절연 층은 각각 질소를 함유하는 실리콘 막을 포함한다. 제 1 산화물 절연 층과 제 2 산화물 절연 층은 각각 산화물 반도체 층의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유한다. 게이트 절연 층의 두께는 제 1 산화물 절연 층의 두께보다 더 두껍다. 보호 절연 층의 두께는 제 2 산화물 절연 층의 두께보다 더 두껍다.That is, another embodiment of the present invention is a gate electrode layer, a gate insulating layer over the gate electrode layer, a first oxide insulating layer over the gate insulating layer, the first oxide insulating layer and in contact with the first oxide insulating layer, An oxide semiconductor layer overlapping the gate electrode layer, a source electrode layer and a drain electrode layer electrically connected to the oxide semiconductor layer, a second oxide insulating layer covering the source electrode layer and the drain electrode layer and contacting a portion of the oxide semiconductor layer, and a second 2 A semiconductor device comprising a protective insulating layer over an oxide insulating layer. Each of the gate insulating layer and the protective insulating layer includes a silicon film containing nitrogen. The first oxide insulating layer and the second oxide insulating layer each contain one or more metal elements selected from constituent elements of the oxide semiconductor layer. The thickness of the gate insulating layer is thicker than that of the first oxide insulating layer. The thickness of the protective insulating layer is thicker than that of the second oxide insulating layer.

위에 기술한 반도체 장치에 있어서, 산화물 반도체 층 및 제 1 산화물 절연 층의 단부들이 서로 배향되는 것이 바람직하다. In the semiconductor device described above, it is preferable that the ends of the oxide semiconductor layer and the first oxide insulating layer are oriented with each other.

위에 기술한 반도체 장치들 중 하나에 있어서, 게이트 절연 층의 두께가 325nm 이상 550nm 이하인 것이 바람직하다. 게이트 절연 층으로서, 질화 실리콘 막이 바람직하게 사용된다.In one of the semiconductor devices described above, it is preferable that the thickness of the gate insulating layer is 325 nm or more and 550 nm or less. As the gate insulating layer, a silicon nitride film is preferably used.

산화물 반도체 층과 접촉하는 산화물 절연 층이 화학양론적 조성을 초과하는 산소를 함유하는 영역(산소 과잉 영역)을 포함하는 것이 바람직하다. 산화물 반도체 층과 접촉하는 산화물 절연 층이 산소 과잉 영역을 포함하도록 함으로써, 산화물 반도체 층에 대한 산소의 공급이 가능해진다. 산화물 반도체 내의 산소의 빈자리들은 산화물 반도체 내에서 캐리어인 전자들을 생성하는 도너들로서 작용한다. 산화물 반도체 층에 산소를 공급하여 산소의 빈자리들을 채움으로써 고도로 신뢰할 수 있는 트랜지스터가 얻어질 수 있다.It is preferable that the oxide insulating layer in contact with the oxide semiconductor layer includes a region containing oxygen in excess of the stoichiometric composition (oxygen excess region). Supply of oxygen to the oxide semiconductor layer becomes possible by making the oxide insulating layer in contact with the oxide semiconductor layer contain an oxygen-excessive region. Vacancies of oxygen in the oxide semiconductor act as donors that generate electrons that are carriers in the oxide semiconductor. A highly reliable transistor can be obtained by supplying oxygen to the oxide semiconductor layer to fill voids in oxygen.

본 발명의 일 실시예에 따른 반도체 장치는 실제 사용에 적용되어왔던 대량 생산 기술로부터 적은 수의 변경들을 갖는 제작 방법으로 제작되고, 안정적인 전기 특성들과 높은 신뢰도를 갖는다.The semiconductor device according to an embodiment of the present invention is manufactured by a manufacturing method having a small number of changes from a mass production technology that has been applied to actual use, and has stable electrical characteristics and high reliability.

덧붙여, 본 발명의 일 실시예에 따라, 정전기 방전 손상으로 인한 수율 감소가 방지되는 반도체 장치를 제공하는 것이 가능하다. In addition, according to an embodiment of the present invention, it is possible to provide a semiconductor device in which a reduction in yield due to electrostatic discharge damage is prevented.

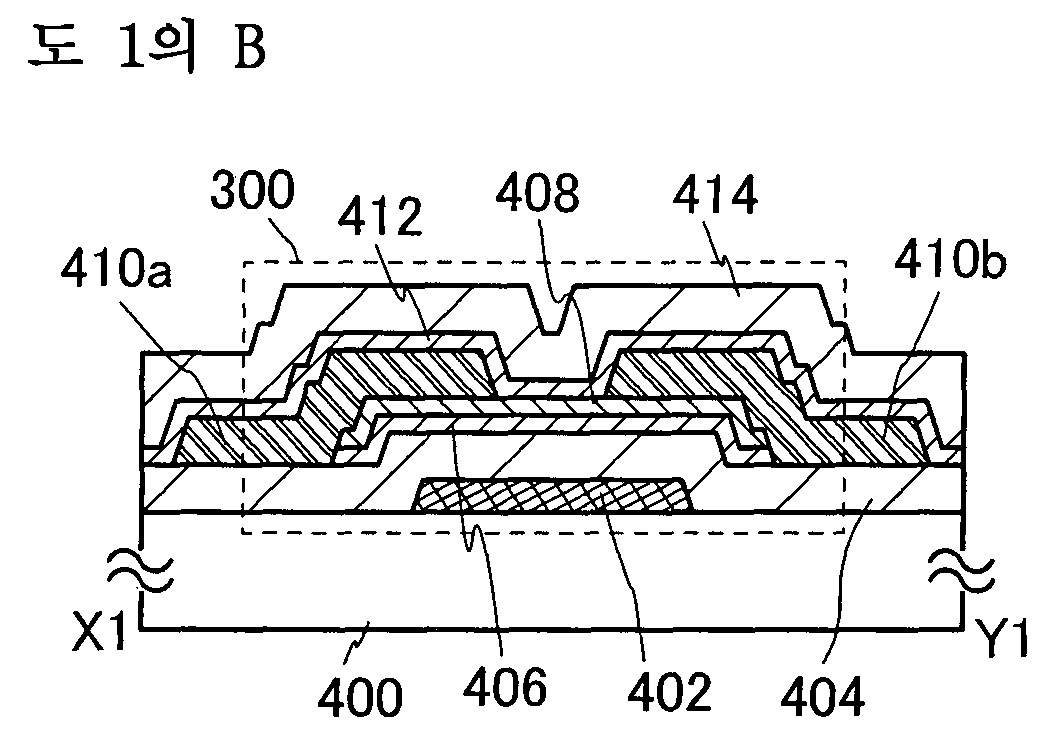

도 1은 반도체 장치의 일 실시예를 도시하는 평면도 및 단면도들.

도 2는 반도체 장치의 일 실시예를 도시하는 평면도 및 단면도들.

도 3은 반도체 장치의 제작 공정의 예를 도시하는 도면들.

도 4는 각각 반도체 장치의 일 실시예를 도시하는 도면들.

도 5는 반도체 장치의 일 실시예를 도시하는 도면들.

도 6은 각각 반도체 장치의 일 실시예를 도시하는 도면들.

도 7은 반도체 장치의 일 실시예를 도시하는 도면들.

도 8은 전자 디바이스들을 도시하는 도면들.

도 9는 전자 디바이스들을 도시하는 도면들.

도 10은 반도체 장치의 일 실시예를 도시하는 평면도 및 단면도들.

도 11은 반도체 장치의 일 실시예를 도시하는 평면도 및 단면도들.

도 12는 ESR 측정의 결과를 도시하는 도면들.

도 13은 TDS 측정의 결과를 도시하는 도면들.

도 14는 본 발명의 일 실시예의 트랜지스터 내에 포함된 적층 구조의 에너지 대역 도면.1 is a plan view and cross-sectional views illustrating an embodiment of a semiconductor device.

2 is a plan view and cross-sectional views illustrating an embodiment of a semiconductor device.

3 are diagrams showing examples of manufacturing steps of a semiconductor device.

4 are diagrams each showing an embodiment of a semiconductor device.

5 is a diagram illustrating an embodiment of a semiconductor device.

6 are views each showing an embodiment of a semiconductor device.

7 is a diagram illustrating an embodiment of a semiconductor device.

8 is diagrams illustrating electronic devices.

9 is diagrams illustrating electronic devices.

10 is a plan view and cross-sectional views illustrating an embodiment of a semiconductor device.

11 is a plan view and cross-sectional views illustrating an embodiment of a semiconductor device.

Fig. 12 is a diagram showing the result of ESR measurement.

13 are diagrams showing results of TDS measurement.

14 is an energy band diagram of a stacked structure included in a transistor according to an embodiment of the present invention.

본 발명의 실시예들은 도면들을 참조하여 아래에서 상세하게 기술될 것이다. 본 발명이 아래의 설명에 국한되지 않고, 본 발명의 모드들 및 세부사항들이 다양한 방식으로 수정될 수 있음을 당업자라면 쉽게 이해할 것임을 주목해야 한다. 그러므로, 본 발명은 아래에서 주어진 실시예들의 설명에 국한되는 것으로 해석되지 않아야 한다.Embodiments of the present invention will be described in detail below with reference to the drawings. It should be noted that those skilled in the art will readily understand that the present invention is not limited to the description below, and that the modes and details of the present invention can be modified in various ways. Therefore, the present invention should not be construed as being limited to the description of the embodiments given below.

아래에서 기술되는 본 발명의 구조들에서, 동일한 부분들 또는 유사한 기능을 갖는 부분들은 다른 도면들에서 동일한 참조 번호들로 지시되고, 이러한 부분들의 설명은 반복되지 않음을 주목해야 한다. 동일한 음영 패턴은 유사한 기능을 갖는 부분들에 적용되고, 이들 부분들은 일부 경우들에서 참조 번호들을 통해 특별하게 지정되지 않는다.It should be noted that in the structures of the present invention described below, the same parts or parts having a similar function are indicated by the same reference numerals in different drawings, and the description of these parts is not repeated. The same shading pattern is applied to parts having a similar function, and these parts are not specifically designated through reference numbers in some cases.

본 명세서에서 기술된 각 도면에서, 각 구성 요소의 크기, 막 두께, 또는 영역은 명확성을 위해 과장될 수 있음을 주목해야 한다. 그러므로, 본 발명의 실시예들은 이러한 축적들에 국한되는 것은 아니다.It should be noted that in each drawing described herein, the size, film thickness, or area of each component may be exaggerated for clarity. Therefore, embodiments of the present invention are not limited to these accumulations.

본 명세서에서 "제 1" 및 "제 2", 등과 같은 서수들은 편리성을 위해 사용되고, 단계들의 순서 또는 층들의 적층 순서를 언급하지는 않음을 주목해야 한다. 덧붙여, 본 명세서에서 서수들, 등은 본 발명을 한정하기 위한 임의의 특별한 명칭들을 지정하지 않는다.It should be noted that ordinal numbers such as “first” and “second” in this specification are used for convenience and do not refer to the order of steps or the order of stacking of layers. In addition, ordinal numbers, etc. in this specification do not designate any special names for limiting the present invention.

(실시예 1)(Example 1)

본 실시예에 있어서, 반도체 장치 및 반도체 장치를 제작하기 위한 방법의 실시예들은 도 1, 도 2, 도 3, 도 10 및 도 11을 참조하여 기술될 것이다. 본 실시예에서, 산화물 반도체 층들을 포함하는 하부-게이트 트랜지스터들이 반도체 장치의 일 예로서 기술된다.In this embodiment, embodiments of a semiconductor device and a method for manufacturing a semiconductor device will be described with reference to FIGS. 1, 2, 3, 10, and 11. In this embodiment, lower-gate transistors including oxide semiconductor layers are described as an example of a semiconductor device.

<반도체 장치의 구조 예 1><Structure Example 1 of a semiconductor device>

도 1은 트랜지스터(300)의 구조 예를 도시한다. 도 1의 A는 트랜지스터(300)의 평면도이고, 도 1의 B는 도 1의 A에서 1점 쇄선(X1-Y1)을 따라 취해진 단면도이고, 도 1의 C는 도 1의 A에서 1점 쇄선(V1-W1)을 따라 취해진 단면도이다.1 shows an example of a structure of a

트랜지스터(300)는, 절연 표면을 갖는 기판(400) 위의 게이트 전극 층(402), 게이트 전극 층(402) 위의 게이트 절연 층(404), 게이트 절연 층(404) 위의 산화물 절연 층(406), 산화물 절연 층(406) 위에서 산화물 절연 층(406)과 접촉하고 게이트 전극 층(402)과 중첩하는 산화물 반도체 층(408), 및 산화물 반도체 층(408)과 전기적으로 연결된 소스 전극 층(410a) 및 드레인 전극 층(410b)을 포함한다.The

트랜지스터(300)에서, 게이트 절연 층(404)은 질소를 함유하는 실리콘 막을 포함한다. 질소를 함유하는 실리콘 막은 산화 실리콘 막보다 높은 비유전율을 갖고, 등가의 커패시턴스를 위해 더 두꺼운 두께를 필요로 한다. 따라서, 게이트 절연 층의 물리적인 두께는 증가할 수 있다. 이것은 트랜지스터(300)의 내전압의 감소를 줄일 수 있고, 추가로 내전압을 증가시킬 수 있고, 이에 의해 반도체 장치에 대한 정전기 방전 손상을 감소시킨다.In the

게이트 절연 층(404)의 두께는 적어도 산화물 절연 층(406)의 두께보다 두껍고, 바람직하게는 325nm 이상 550nm 이하, 보다 바람직하게는 355nm 이상 550nm 이하이다.The thickness of the

질소를 함유하는 실리콘 막의 예들은, 질화 실리콘 막, 질화산화 실리콘 막, 산화질화 실리콘 막, 등을 포함한다. 높은 질소 함량을 갖는 재료가 더 높은 비유전율을 갖기 때문에, 질화 실리콘 막을 사용하는 것이 바람직하다. 산화 실리콘은 8eV의 에너지 갭을 갖고, 반면 질화 실리콘은 5.5eV의 작은 에너지 갭을 갖고, 따라서 낮은 저항률을 갖는다. 따라서 질화 실리콘 막의 사용은 ESD에 대한 저항을 증가시킬 수 있다. 덧붙여, 질화 실리콘 막이 CVD 방법에 의해 형성되는 경우, 질화산화 실리콘 막과 같이 산소와 질소를 함유하는 실리콘 막이 CVD 방법에 의해 형성될 때 사용되고, 온실 가스인, N2O 가스를 사용할 필요가 없다. 본 명세서에서, "산화질화 실리콘 막"은 질소보다 산소를 더 많이 함유하는 막을 언급하고, "질화산화 실리콘 막"은 산소보다 질소를 더 많이 함유하는 막을 언급함을 주목해야 한다.Examples of the silicon film containing nitrogen include a silicon nitride film, a silicon nitride oxide film, a silicon oxynitride film, and the like. Since a material with a high nitrogen content has a higher relative dielectric constant, it is preferable to use a silicon nitride film. Silicon oxide has an energy gap of 8 eV, whereas silicon nitride has a small energy gap of 5.5 eV, and thus has a low resistivity. Therefore, the use of a silicon nitride film can increase the resistance to ESD. In addition, when the silicon nitride film is formed by the CVD method, it is used when a silicon film containing oxygen and nitrogen, such as a silicon nitride oxide film, is formed by the CVD method, and there is no need to use N 2 O gas, which is a greenhouse gas. It should be noted that in this specification, "silicon oxynitride film" refers to a film containing more oxygen than nitrogen, and "silicon nitride oxide film" refers to a film containing more nitrogen than oxygen.

트랜지스터(300)에서, 산화물 절연 층(406)은 산화물 반도체 층(408)의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유한다. 산화물 절연 층(406)이 이러한 재료를 사용하여 형성되기 때문에, 산화물 절연 층(406)과 산화물 반도체 층(408) 사이의 계면을 안정시킬 수 있고, 계면에서 전하 포획을 줄일 수 있다. 따라서, 트랜지스터의 열화, 특히 광열화를 방지할 수 있고, 따라서 높은 신뢰성의 트랜지스터를 획득할 수 있다.In

특히, 산화물 절연 층(406)으로서, 예컨대 산화 갈륨 막(GaOx(x는 반드시 자연수일 필요는 없고, 비자연수일 수 있음을 주목해야 한다)로도 언급됨), 산화 갈륨 아연 막(Ga2ZnxOy(x=1 내지 5)로도 언급됨, Ga2O3(Gd2O3)막), 높은 갈륨 함량과 낮은 인듐 함량을 갖는 In-Ga-Zn계 산화물 절연 막, 등을 제공하는 것이 바람직하다.In particular, as the

산화물 절연 층(406)과 산화물 반도체 층(408)은 동일한 구성 원소들의 상이한 조성들을 가질 수 있다. 예컨대, In-Ga-Zn계 산화물 반도체 층이 산화물 반도체 층(408)으로 사용되는 경우, 에너지 갭이 인듐(In)과 갈륨(Ga) 사이의 비율에 의해 제어될 수 있으므로, 산화물 반도체 층(408)은 In:Ga:Zn=1:1:1 또는 In:Ga:Zn=3:1:2의 원자 비율을 가질 수 있고, 산화물 절연 층(406)은 In:Ga:Zn=1:3:2의 원자 비율을 가질 수 있다. 산화물 절연 층(406)과 산화물 반도체 층(408)이 스퍼터링 방법에 의해 형성될 수 있고, 인듐을 함유하는 스퍼터링 타깃을 통해, 막 형성 도중의 입자들의 생성이 감소될 수 있음을 주목해야 한다. 따라서, 인듐을 함유하는 산화물 절연 층(406)과 인듐을 함유하는 산화물 반도체 층(408)이 바람직하다.The

도 1에 도시된 트랜지스터(300)의 예에서, 산화물 반도체 층(408)을 섬 형태로 처리하기 위한 에칭 처리를 통해, 산화물 절연 층(406)이 또한 섬 형태로 처리됨을 주목해야 한다. 따라서, 산화물 절연 층(406)과 산화물 반도체 층(408)의 단부들은 서로 배향된다. It should be noted that in the example of the

산화물 반도체 층의 구조는 아래에 기술된다.The structure of the oxide semiconductor layer is described below.

산화물 반도체 층은 대략 단결정 산화물 반도체 층과 비-단결정 산화물 반도체 층으로 분류된다. 비-단결정 산화물 반도체 층은 비정질 산화물 반도체 층, 미결정 산화물 반도체 층, 다결정 산화물 반도체 층, c-축 배향 결정 산화물 반도체(CAAC-OS) 막, 등 중 어느 하나를 포함한다.The oxide semiconductor layer is roughly classified into a single crystal oxide semiconductor layer and a non-single crystal oxide semiconductor layer. The non-single crystal oxide semiconductor layer includes any one of an amorphous oxide semiconductor layer, a microcrystalline oxide semiconductor layer, a polycrystalline oxide semiconductor layer, a c-axis oriented crystal oxide semiconductor (CAAC-OS) film, and the like.

비정질 산화물 반도체 층은 불규칙한 원자 배향을 갖고, 결정 성분을 전혀 갖지 않는다. 이의 전형적인 예는 미소 영역에서 조차 결정부를 전혀 갖지 않고, 층의 전체가 비정질인, 산화물 반도체 층이다.The amorphous oxide semiconductor layer has an irregular atomic orientation and has no crystal components at all. A typical example of this is an oxide semiconductor layer, which has no crystal parts even in a small region, and the entire layer is amorphous.

미결정 산화물 반도체 층은 예컨대 1nm 이상 10nm 미만의 크기를 갖는 미결정(나노결정이라고도 함)을 포함한다. 따라서, 미결정 산화물 반도체 층은 비정질 산화물 반도체 층보다 높은 정도의 원자 규칙성을 갖는다. 따라서, 미결정 산화물 반도체 층의 결함 상태들의 밀도는 비정질 산화물 반도체 층의 밀도보다 낮다.The microcrystalline oxide semiconductor layer includes microcrystals (also referred to as nanocrystals) having a size of 1 nm or more and less than 10 nm, for example. Thus, the microcrystalline oxide semiconductor layer has a higher degree of atomic regularity than the amorphous oxide semiconductor layer. Accordingly, the density of the defect states of the microcrystalline oxide semiconductor layer is lower than that of the amorphous oxide semiconductor layer.

CAAC-OS 막은, 복수의 결정부들을 포함하고, 대부분의 각 결정부가 한 측면이 100nm 미만인 입방체 내에 들어가는 산화물 반도체 층들 중 하나이다. 따라서, CAAC-OS 막 내에 포함된 결정부가, 10nm 미만, 5nm 미만, 또는 3nm 미만인 한 측면을 갖는 입방체 내에 들어가는 경우가 존재한다. CAAC-OS 막의 결함 상태들의 밀도는 미결정 산화물 반도체 층의 것보다 낮다. CAAC-OS 막은 아래에서 상세하게 기술된다.The CAAC-OS film includes a plurality of crystal portions, and most of each crystal portion is one of oxide semiconductor layers that fit into a cube whose one side is less than 100 nm. Accordingly, there is a case where the crystal part contained in the CAAC-OS film enters a cube having one side of less than 10 nm, less than 5 nm, or less than 3 nm. The density of the defect states of the CAAC-OS film is lower than that of the microcrystalline oxide semiconductor layer. The CAAC-OS membrane is described in detail below.

CAAC-OS 막의 투과 전자 현미경(TEM) 이미지에서, 결정부들 사이의 경계, 즉 결정입계는 명확하게 관찰되지 않는다. 따라서, CAAC-OS 막 내에서, 결정입계로 인한 전자 이동도 내의 감소는 발생하기 어렵다.In the transmission electron microscopy (TEM) image of the CAAC-OS film, the boundary between the crystal parts, that is, the grain boundary is not clearly observed. Therefore, in the CAAC-OS film, a decrease in electron mobility due to grain boundaries is unlikely to occur.

샘플 표면에 실질적으로 평행한 방향에서 관찰된 CAAC-OS 막의 TEM 이미지(단면 TEM 이미지)에 따라, 금속 원자들은 결정부들 내에서 층상으로 배열된다. 각 금속 원자 층은 CAAC-OS막이 형성되는 표면(이후로, CAAC-OS막이 형성되는 표면을 피형성면이라 칭한다) 또는 CAAC-OS막의 상면을 반영한 지형을 갖고, CAAC-OS막의 피형성면 또는 상면에 평행하게 배열된다.According to the TEM image (cross-sectional TEM image) of the CAAC-OS film observed in a direction substantially parallel to the sample surface, the metal atoms are arranged in layers in the crystal parts. Each metal atomic layer has a topography reflecting the surface on which the CAAC-OS film is formed (hereinafter, the surface on which the CAAC-OS film is formed is referred to as the surface to be formed) or the top surface of the CAAC-OS film, and the surface on which the CAAC-OS film is formed or It is arranged parallel to the top surface.

본 명세서에 있어서, 용어, "평행"은 2개의 직선들 사이에 형성된 각도가 -10° 이상 10°이하인 것을 말하고, 따라서 각도가 -5° 이상 5° 이하인 경우도 또한 포함한다. 덧붙여, 용어, "수직"이란 2개의 직선들 사이에서 형성된 각도가 80°이상 100°이하인 것을 말하고, 따라서, 각도가 85°이상 95°이하인 경우를 포함한다. In the present specification, the term "parallel" means that an angle formed between two straight lines is -10° or more and 10° or less, and therefore, also includes a case where the angle is -5° or more and 5° or less. In addition, the term "vertical" means that the angle formed between two straight lines is 80° or more and 100° or less, and thus includes the case where the angle is 85° or more and 95° or less.

다른 한 편으로, 샘플 표면에 실질적으로 수직인 방향에서 관찰된 CAAC-OS막의 TEM 이미지(평면 TEM 이미지)에 따라, 금속 원자들은 결정부들 내에서 삼각형 또는 육각형 구성으로 배열된다. 그러나, 상이한 결정부들 사이에서 금속 원자들의 배열의 규칙성은 존재하지 않는다.On the other hand, according to the TEM image (planar TEM image) of the CAAC-OS film observed in a direction substantially perpendicular to the sample surface, the metal atoms are arranged in a triangular or hexagonal configuration within the crystal parts. However, there is no regularity of the arrangement of metal atoms between different crystal parts.

단면 TEM 이미지 및 평면 TEM 이미지의 결과들로부터, CAAC-OS막 내의 결정부들 내에서 배향이 발견된다.From the results of the cross-sectional TEM image and the planar TEM image, the orientation is found in the crystal parts in the CAAC-OS film.

CAAC-OS막은 X선 회절(XRD) 장치를 통한 구조 해석을 받는다. 예컨대, InGaZnO4 결정을 포함하는 CAAC-OS막이 아웃-오브-플레인(out-of-plane)법에 의해 분석될 때, 회절각(2θ)이 대략 31°일 때 피크가 빈번하게 나타난다. 이 피크는, InGaZnO4의 결정의 (009)면으로부터 유도되고, 이는 CAAC-OS막 내의 결정들이 c-축 배향을 갖고, c-축들이 CAAC-OS막의 피형성면 또는 상면에 실질적으로 수직인 방향으로 배향되는 것을 나타낸다.The CAAC-OS film is subjected to structural analysis through an X-ray diffraction (XRD) device. For example, when a CAAC-OS film including an InGaZnO 4 crystal is analyzed by an out-of-plane method, a peak frequently appears when the diffraction angle 2θ is approximately 31°. This peak is derived from the (009) plane of the crystal of InGaZnO 4 , which means that the crystals in the CAAC-OS film have a c-axis orientation, and the c-axis are substantially perpendicular to the formation surface or top surface of the CAAC-OS film. Indicates oriented in a direction.

다른 한 편으로, CAAC-OS막이 c-축에 수직인 방향으로 X선이 샘플로 입사하는 인-플레인(in-plane)법을 통해 분석될 때, 2θ가 대략 56°일 때 피크가 빈번하게 나타난다. 이 피크는 InGaZnO4 결정의 (110)면으로부터 유도된다. 여기에서, 2θ가 대략 56°에서 고정된 상태로, 샘플이 샘플 표면의 법선 벡터를 축(φ축)으로 하여 회전하는 조건들 하에서 분석(φ 스캔)이 수행된다. 샘플이 InGaZnO4의 단결정 산화물 반도체 층인 경우, 6개의 피크들이 출현한다. 6개의 피크들은 (110)면에 등가인 결정 면들로부터 유도된다. 다른 한 편으로, CAAC-OS막의 경우, 2θ가 대략 56°에 고정된 상태에서 φ 스캔이 수행될 때조차, 피크는 명료하게 관찰되지 않는다.On the other hand, when the CAAC-OS film is analyzed by an in-plane method in which X-rays are incident on the sample in a direction perpendicular to the c-axis, the peak frequently occurs when 2θ is approximately 56°. appear. This peak is derived from the (110) plane of the InGaZnO 4 crystal. Here, analysis (φ scan) is performed under conditions in which 2θ is fixed at approximately 56°, and the sample rotates with the normal vector of the sample surface as an axis (φ axis). When the sample is a single crystal oxide semiconductor layer of InGaZnO 4, six peaks appear. The six peaks are derived from crystal planes equivalent to the (110) plane. On the other hand, in the case of the CAAC-OS film, even when a φ scan is performed with 2θ fixed at approximately 56°, the peak is not clearly observed.

위의 결과들에 따라, c-축 배향을 갖는 CAAC-OS막에서, a-축들 및 b-축들의 방향들이 결정부들 사이에서 상이하지만, c-축들은 피형성면의 법선 벡터 또는 상면의 법선 벡터에 평형한 방향으로 배향된다. 따라서, 단면 TEM 이미지에서 관찰된 층상으로 배열된 각 금속 원자 층은 결정의 a-b면에 평행한 면에 대응한다.According to the above results, in a CAAC-OS film having a c-axis orientation, the directions of the a-axis and the b-axis are different between the crystal parts, but the c-axis is the normal vector of the surface to be formed or the normal of the top surface. Oriented in a direction parallel to the vector. Thus, each layer of metal atoms arranged in layers observed in the cross-sectional TEM image corresponds to a plane parallel to the a-b plane of the crystal.

결정부가 CAAC-OS막의 증착과 동시에 형성되거나, 또는 열처리와 같은 결정화 처리를 통해 형성됨을 주목해야 한다. 상술한 바와 같이, 결정의 c-축은 피형성면의 법선 벡터 또는 상면의 법선 벡터에 평행한 방향으로 배향된다. 따라서, 예컨대 CAAC-OS막의 형태가 에칭 등에 의해 변화되는 경우, c-축은 반드시 CAAC-OS막의 피형성면의 법선 벡터 또는 상면의 법선 벡터에 반드시 평행한 것은 아닐 수 있다.It should be noted that the crystal portion is formed simultaneously with the deposition of the CAAC-OS film, or is formed through a crystallization treatment such as heat treatment. As described above, the c-axis of the crystal is oriented in a direction parallel to the normal vector of the surface to be formed or the normal vector of the upper surface. Therefore, for example, when the shape of the CAAC-OS film is changed by etching or the like, the c-axis may not necessarily be parallel to the normal vector of the surface to be formed or the normal vector of the upper surface of the CAAC-OS film.

더욱이, CAAC-OS막 내의 결정화 정도는 반드시 균일한 것은 아니다. 예컨대, CAAC-OS막을 초래하는 결정 성장이 막의 상면의 근처로부터 발생하는 경우, 상면 근처에서 결정화 정도는 일부 경우들에서 피형성면의 근처에서의 결정화 정도보다 높다. 더욱이, CAAC-OS막에 불순물이 첨가될 때, 불순물이 첨가되는 영역 내의 결정화는 변화되고, CAAC-OS막 내의 결정화 정도는 영역들에 따라 변한다.Moreover, the degree of crystallization in the CAAC-OS film is not necessarily uniform. For example, when crystal growth resulting in the CAAC-OS film occurs near the upper surface of the film, the degree of crystallization near the upper surface is higher than the degree of crystallization near the surface to be formed in some cases. Moreover, when an impurity is added to the CAAC-OS film, the crystallization in the region to which the impurity is added changes, and the degree of crystallization in the CAAC-OS film varies depending on the regions.

InGaZnO4 결정을 갖는 CAAC-OS막이 아웃-오브-플레인 법에 의해 분석될 때, 2θ의 피크가 또한 대략 31°에서 2θ의 피크에 부가하여, 대략 36°에서 관찰될 수 있음을 주목해야 한다. 대략 36°에서 2θ의 피크는 c-축 배향을 갖지 않는 결정이 CAAC-OS막의 부분 내에 포함되는 것을 나타낸다. CAAC-OS막 내에서, 2θ의 피크가 대략 31°에서 출현하고, 2θ의 피크가 대략 36°에서 출현하지 않는 것이 바람직하다.It should be noted that when the CAAC-OS film with InGaZnO 4 crystals is analyzed by the out-of-plane method, a peak of 2θ can also be observed at about 36°, in addition to the peak of 2θ at about 31°. A peak of 2θ at approximately 36° indicates that a crystal having no c-axis orientation is included in a portion of the CAAC-OS film. In the CAAC-OS film, it is preferable that the peak of 2θ appears at approximately 31° and the peak of 2θ does not appear at approximately 36°.

본 명세서에서, 삼방정계 또는 능면체정계는 육방정계 내에 포함된다.In the present specification, the trigonal system or rhombohedral system is included in the hexagonal system.

CAAC-OS 막을 사용하는 트랜지스터에서, 가시광 또는 자외광의 조사로 인한 전기 특성들의 변화는 작다. 따라서, 트랜지스터는 높은 신뢰도를 갖는다.In a transistor using a CAAC-OS film, the change in electrical properties due to irradiation of visible light or ultraviolet light is small. Therefore, the transistor has high reliability.

산화물 반도체 층(408)이 예컨대 비정질 산화물 반도체 층, 미결정 산화물 반도체 층, 또는 CAAC-OS 막 중 임의의 구조가 될 수 있거나, 또는 이들의 혼합된 막, 또는 이들 구조들 중 둘 이상의 막들을 포함하는 적층 막일 수 있음을 주목해야 한다.The

일부 경우들에서, 산화물 절연 층(406)은 산화물 반도체 층(408)보다 낮은 결정화도를 가짐을 주목해야 한다. 산화물 절연 층(406)은 비정질부 또는 나노결정을 포함할 수 있다.It should be noted that in some cases,

다른 구성요소들로서, 트랜지스터(300)는 소스 전극 층(410a) 및 드레인 전극 층(410b)을 덮고, 산화물 반도체 층(408)과 접촉하는 산화물 절연 층(412) 및/또는 산화물 절연 층(412) 위의 보호 절연 층(414)을 포함할 수 있다.As other components, the

산화물 절연 층(412)으로, 산화물 절연 층(406)과 같이, 산화물 반도체 층(408)의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 층을 사용하는 것이 바람직하다. 이러한 재료가 사용될 때, 산화물 절연 층(412)과 산화물 반도체 층(408) 사이의 계면을 안정시키는 것이 가능하다. 산화물 절연 층(412)이 산화물 반도체 층(408)의 백 채널 측과 접촉하는 절연 층이기 때문에, 두 층들 사이의 계면에서 전하 포획은 감소되고, 이에 의해 기생 채널의 생성이 줄어들 수 있다. As the

덧붙여, 산화물 반도체 층(408)의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 산화물 절연 층들이 산화물 반도체 층(408)이 사이에 개재되도록 산화물 반도체 층(408)과 접촉하여 산화물 반도체 층(408)의 위와 아래에 제공될 때, 산화물 절연 층들이 산화물 반도체 층에 악영향을 미칠 수 있는 불순물들(질소 및 금속 원소들과 같은)의 확산에 의한 외부로부터의 진입을 차단하도록 작용할 수 있다. 따라서, 산화물 반도체 층이 개재되도록 또는 둘러싸이도록 산화물 절연 층들이 제공될 때, 둘러싸인 산화물 반도체 층의 조성 및 순도는 일정하게 유지될 수 있고, 안정된 전기 특성들을 갖는 반도체 장치가 얻어질 수 있다.In addition, oxide insulating layers containing one or more metal elements selected from the constituent elements of the

보호 절연 층(414)으로서, 산화 실리콘 막, 산화 갈륨 막, 산화 알루미늄 막, 질화 실리콘 막, 산화질화 실리콘 막, 산화질화 알루미늄 막, 질화산화 실리콘 막, 등이 사용될 수 있다.As the protective insulating

<반도체 장치의 구조 예 2><Structure Example 2 of a semiconductor device>

도 2는 트랜지스터(310)의 구조 예를 도시한다. 도 2의 A는 트랜지스터(310)의 평면도이고, 도 2의 B는 도 2의 A에서 1점 쇄선(X2-Y2)을 따라 취해진 단면도이고, 도 2의 C는 도 2의 A에서 1점 쇄선(V2-W2)을 따라 취해진 단면도이다.2 shows an example of the structure of the

도 1의 트랜지스터(300)와 같이, 도 2의 트랜지스터(310)는, 절연 표면을 갖는 기판(400) 위의 게이트 전극 층(402), 게이트 전극 층(402) 위의 게이트 절연 층(404), 게이트 절연 층(404) 위의 산화물 절연 층(406), 산화물 절연 층(406) 위에서 산화물 절연 층(406)과 접촉하고, 게이트 전극 층(402)과 중첩하는 산화물 반도체 층(408), 및 산화물 반도체 층(408)에 전기적으로 연결된 소스 전극 층(410a) 및 드레인 전극 층(410b)을 포함한다. 다른 구성요소들로서, 트랜지스터(310)는 소스 전극 층(410a) 및 드레인 전극 층(410b)을 덮고, 산화물 반도체 층(408)과 접촉하는 산화물 절연 층(412) 및 산화물 절연 층(412) 위의 보호 절연 층(414)을 포함할 수 있다.Like the

트랜지스터(310)는 게이트 절연 층(404)과 산화물 반도체 층(408)의 구조들에서 트랜지스터(300)와 다르다. 즉, 트랜지스터(310) 내의 게이트 절연 층(404)은 게이트 전극 층(402)과 접촉하는 게이트 절연 층(404a)과 게이트 절연 층(404a)과 산화물 절연 층(406) 사이의 게이트 절연 층(404b)을 포함한다. 트랜지스터(310) 내의 산화물 반도체 층(408)은 산화물 절연 층(406)과 접촉하는 산화물 반도체 층(408a)과 산화물 절연 층(412)과 접촉하는 산화물 반도체 층(408b)을 포함한다. 트랜지스터(310) 내의 게이트 절연 층(404)과 산화물 반도체 층(408) 이외의 다른 구성요소들이 트랜지스터(300)의 다른 구성요소들과 유사하고, 이를 위해 트랜지스터(300)의 설명이 인용될 수 있음을 주목해야 한다.

트랜지스터(310)에서, 게이트 절연 층(404a)과 게이트 절연 층(404b)은 각각 질화 실리콘 막을 포함한다.In the

게이트 절연 층(404a)은 게이트 절연 층(404b)보다 더 두꺼운 두께를 갖고, 더 적은 수의 결함들을 포함하는 질화 실리콘 막을 포함한다. 예컨대, 게이트 절연 층(404a)의 두께는 300nm 이상 400nm 이하이다. 덧붙여, 전자 스핀 공명(ESR) 분광법에서 Nc 중심에서(2.003의 g 계수에서) 나타나는 신호에 대응하는 1×1017spins//㎤ 이하, 바람직하게는 5×1016spins/㎤ 이하의 스핀 밀도를 갖는 질화 실리콘 막이 사용된다. 두꺼운 두께(예, 300nm 이상)를 갖고, 적은 수의 결함들을 포함하는 이러한 질화 실리콘 막이 제공될 때, 게이트 절연 층(404a)의 내전압은 예컨대 300V 이상이 될 수 있다.The

게이트 절연 층(404b)이 산화물 반도체 층(408)과 접촉하기 때문에, 게이트 절연 층(404b)은 낮은 농도의 수소를 함유하는 질화 실리콘 막을 포함하여야 하고, 수소 농도는 적어도 게이트 절연 층(404a)의 수소 농도보다 낮아야 한다. 예컨대, 게이트 절연 층(404a)과 게이트 절연 층(404b)이 플라즈마 CVD 방법에 의해 형성되는 경우, 게이트 절연 층(404b)의 수소 농도는 공급 가스 내에 함유된 수소의 농도를 감소시킴으로써 게이트 절연 층(404a)의 수소 농도보다 낮게 이루어질 수 있다. 특히, 질화 실리콘 막들이 게이트 절연 층(404a)과 게이트 절연 층(404b)으로서 형성되는 경우, 게이트 절연 층(404b)은 게이트 절연 층(404a)을 형성하기 위한 공급 가스 내에서보다 더 낮은 암모니아 유동율로 형성될 수 있거나, 또는 암모니아를 사용하지 않고 형성될 수 있다.Since the

게이트 절연 층(404b)의 두께는 25nm 이상 150nm 이하이다. 낮은 농도의 수소를 함유하는 질화 실리콘 막이 게이트 절연 층(404b)으로서 제공되기 때문에, 산화물 절연 층(406) 및 산화물 반도체 층(408)으로 수소 또는 수소 화합물(예, 물)의 진입을 줄이는 것이 가능하다. 산화물 반도체 내의 수소는 캐리어들이 생성되게 하고, 트랜지스터의 문턱 전압이 음의 방향으로 이동하게 한다. 따라서, 낮은 수소 농도를 갖는 질화 실리콘 막이 게이트 절연 층(404b)으로서 제공될 때, 트랜지스터의 전기 특성들은 안정화될 수 있다. 덧붙여, 낮은 수소 농도를 갖는 질화 실리콘 막이 게이트 절연 층(404b)으로서 제공될 때, 게이트 절연 층(404b)은 또한, 게이트 절연 층(404a) 내에 함유된 수소 또는 수소 화합물과 같은 불순물들이 산화물 절연 층(406) 및 산화물 반도체 층(408)으로 확산되는 것을 방지하기 위한 장벽 막으로서 작용한다.The thickness of the

본 실시예에서 게이트 절연 층(404a)과 게이트 절연 층(404b) 모두 질화 실리콘 막들이고, 이들 게이트 절연 층들 사이의 계면이 재료들 또는 막 형성 조건들에 따라 불명확하게 될 수 있음을 주목해야 한다. 따라서, 도 2의 B 및 C에서, 게이트 절연 층(404a)과 게이트 절연 층(404b) 사이의 계면은 개략적으로 점선으로 도시된다. 아래에 기술된 다른 도면들에 대해서도 동일하다.It should be noted that in this embodiment, both the

산화물 반도체 층(408) 내에 포함된 산화물 반도체 층(408a)과 산화물 반도체 층(408b)은 동일한 구성 원소들의 상이한 조성들을 갖는 것이 바람직하다. 인듐과 갈륨을 함유하는 산화물 반도체 층들이 산화물 반도체 층(408a)과 산화물 반도체 층(408b)으로 형성되는 경우, 게이트 전극 층(402)에 근접한 측(채널 측) 상의 산화물 반도체 층(408a) 내에서 인듐의 함량이 갈륨의 함량보다 높은(In > Ga) 것이 바람직하다. 또한, 게이트 전극 층(402)으로부터 먼 측(백 채널 측) 상의 산화물 반도체 층(408b) 내에서 인듐의 함량은 갈륨의 함량 이하인(In ≤ Ga) 것이 바람직하다.It is preferable that the

산화물 반도체에서, 중금속의 s 궤도는 주로 캐리어 전도에 기여하고, 산화물 반도체 내의 인듐 함량이 증가할 때 s 궤도들의 중첩들은 증가하기 쉽다. 그러므로, In > Ga의 조성을 갖는 산화물은 In ≤ Ga의 조성을 갖는 산화물보다 더 높은 이동도를 갖는다. 더욱이, Ga에서, 산소의 빈자리의 형성 에너지는 더 크고, 따라서 산소의 빈자리들은 In 내에서보다 생성되기 어렵고; 따라서 In ≤ Ga의 조성을 갖는 산화물은 In > Ga의 조성을 갖는 산화물보다 더 안정된 특성들을 갖는다.In an oxide semiconductor, the s orbitals of the heavy metal mainly contribute to carrier conduction, and the overlaps of the s orbitals tend to increase when the indium content in the oxide semiconductor increases. Therefore, an oxide having a composition of In> Ga has a higher mobility than an oxide having a composition of In? Ga. Moreover, in Ga, the formation energy of oxygen vacancies is larger, and thus oxygen vacancies are more difficult to generate than in In; Therefore, an oxide having a composition of In ≤ Ga has more stable properties than an oxide having a composition of In> Ga.

In > Ga의 조성을 갖는 산화물 반도체는 채널 측 상에서 사용되고, In ≤ Ga의 조성을 갖는 산화물 반도체는 백 채널 측 상에서 사용되어, 트랜지스터의 이동도와 신뢰도는 추가로 개선될 수 있다. 예컨대, 산화물 반도체 층(408a)은 In:Ga:Zn = 3:1:2의 원자 비율을 가질 수 있고, 산화물 반도체 층(408b)은 In:Ga:Zn = 1:1:1의 원자 비율을 가질 수 있다.An oxide semiconductor having a composition of In>Ga is used on the channel side, and an oxide semiconductor having a composition of In≦Ga is used on the back channel side, so that the mobility and reliability of the transistor can be further improved. For example, the

산화물 반도체 층(408a) 및 산화물 반도체 층(408b)과 접촉하는 산화물 절연 층(406)이 동일한 구성 원소들의 상이한 조성들을 가져, 두 층의 계면이 추가로 안정화될 수 있기 때문에 산화물 절연 층(406)이 절연 특성을 갖는 것이 바람직함을 주목해야 한다. 산화물 반도체 층(408b)과 접촉하는 산화물 절연 층(412)에 대해서도 동일하다.The

또한, 상이한 결정도들을 갖는 산화물 반도체들이 산화물 반도체 층(408a) 및 산화물 반도체 층(408b)을 위하여 사용될 수 있다. 즉, 산화물 반도체 층들(408a 및 408b)은 단결정 산화물 반도체, 다결정 산화물 반도체, 나노결정 산화물 반도체, 비정질 산화물 반도체, 및 CAAC-OS 중 임의의 것의 조합을 적절하게 사용하여 형성될 수 있다. 비정질 산화물 반도체는 수소와 같은 불순물들을 흡착하기 쉽고, 산소의 빈자리들을 갖기 쉽고, 따라서 쉽게 n-형이 될 수 있음을 주목해야 한다. 그러므로, 채널 측 상의 산화물 반도체 층(408a)은 CAAC-OS와 같은 결정 산화물 반도체를 사용하여 형성되는 것이 바람직하다.Also, oxide semiconductors having different crystallinities may be used for the

백 채널 측 상의 산화물 반도체 층(408b)이 비정질 산화물 반도체를 사용하여 형성될 때, 산화물 반도체 층(408b)은 소스 전극 층(410a) 및 드레인 전극 층(410b)을 형성하기 위한 에칭 처리를 통해 산소의 빈자리들을 갖기 쉽고, 쉽게 n-형이 된다. 따라서 산화물 반도체 층(408b)이 결정 산화물 반도체를 사용하여 형성되는 것이 바람직하다.When the

도 14는 게이트 절연 층(GI), 산화물 절연 층(OI1), 산화물 반도체 층들(OS1 및 OS2), 산화물 절연 층(OI2), 및 보호 절연 층(Passi)의 적층구조를 갖는 본 실시예에서의 트랜지스터의 에너지 밴드 도면(개략도)이다. 게이트 절연 층, 산화물 절연 층들, 산화물 반도체 층들, 및 보호 절연 층이 모두 진성인 이상적인 상황을 간주하여, 도 14는 게이트 절연 층(GI)과 보호 절연 층(Passi)이 질화 실리콘 막들(밴드 갭(Eg): 5eV)이고, 산화물 절연 층(OI1)과 산화물 절연 층(OI2)이 In:Ga:Zn=1:3:2(밴드 갭(Eg): 3.6eV)인 In-Ga-Zn계 산화물 절연 층들이고, 산화물 반도체 층(OS1)이 In:Ga:Zn=3:1:2(밴드 갭(Eg): 2.8eV)인 In-Ga-Zn계 산화물 반도체 층이고, 산화물 반도체 층(OS2)이 In:Ga:Zn=1:1:1(밴드 갭(Eg): 3.2eV)인 In-Ga-Zn계 산화물 반도체 층인 경우를 도시한다.14 is a diagram in the present embodiment having a stacked structure of a gate insulating layer GI, an oxide insulating layer OI1, oxide semiconductor layers OS1 and OS2, an oxide insulating layer OI2, and a protective insulating layer Passi. It is a diagram (schematic diagram) of the energy band of the transistor. Considering an ideal situation in which the gate insulating layer, the oxide insulating layers, the oxide semiconductor layers, and the protective insulating layer are all intrinsic, FIG. 14 shows that the gate insulating layer GI and the protective insulating layer Passi are silicon nitride films (band gaps). Eg): 5eV), and the oxide insulating layer (OI1) and the oxide insulating layer (OI2) are In:Ga:Zn = 1:3:2 (band gap (Eg): 3.6 eV) In-Ga-Zn oxide Insulation layers, the oxide semiconductor layer (OS1) is an In-Ga-Zn-based oxide semiconductor layer with In:Ga:Zn=3:1:2 (band gap (Eg): 2.8 eV), and an oxide semiconductor layer (OS2) A case of an In-Ga-Zn-based oxide semiconductor layer having an In:Ga:Zn=1:1:1 (band gap (Eg): 3.2 eV) is shown.

도 14에서 산화물 절연 층(OI1), 산화물 절연 층(OI2), 산화물 반도체 층(OS1) 및 산화물 반도체 층(OS2)은 모두 15의 비유전율을 갖는 것으로 가정됨을 주목해야 한다. 또한, 산화물 절연 층(OI1)과 산화물 절연 층(OI2)은 4㎠/Vs의 이동도를 갖고, 산화물 반도체 층(OS1)은 25㎠/Vs의 이동도를 갖고, 산화물 반도체 층(OS2)은 10㎠/Vs의 이동도를 갖는 것으로 간주된다. 더욱이, 게이트 절연 층(GI)이 325nm의 두께를 갖고, 산화물 절연 층(OI1)이 30nm의 두께를 갖고, 산화물 반도체 층(OS1)이 10nm의 두께를 갖고, 산화물 반도체 층(OS2)이 10nm의 두께를 갖고, 산화물 절연 층(OI2)이 30nm의 두께를 갖고, 보호 절연 층(Passi)이 300nm의 두께를 갖는 것으로 간주된다. 이들 가정들에 기초하여 계산이 수행된다.In FIG. 14, it should be noted that the oxide insulating layer OI1, the oxide insulating layer OI2, the oxide semiconductor layer OS1, and the oxide semiconductor layer OS2 are all assumed to have a relative dielectric constant of 15. In addition, the oxide insulating layer OI1 and the oxide insulating layer OI2 have a mobility of 4 cm 2 /Vs, the oxide semiconductor layer OS1 has a mobility of 25 cm 2 /Vs, and the oxide semiconductor layer OS2 It is considered to have a mobility of 10 cm 2 /Vs. Moreover, the gate insulating layer GI has a thickness of 325 nm, the oxide insulating layer OI1 has a thickness of 30 nm, the oxide semiconductor layer OS1 has a thickness of 10 nm, and the oxide semiconductor layer OS2 has a thickness of 10 nm. It is considered that it has a thickness, the oxide insulating layer OI2 has a thickness of 30 nm, and the protective insulating layer Passi has a thickness of 300 nm. Calculations are performed based on these assumptions.

도 14에 도시된 바와 같이, 산화물 반도체 층(OS1)의 게이트 전극 측(채널 측) 상에서, 산화물 반도체 층(OS1)과 산화물 절연 층(OI1) 사이의 계면에 에너지 장벽이 존재한다. 유사하게, 산화물 반도체 층(OS2)의 백 채널 측(게이트 전극 측의 반대편) 상에서, 산화물 반도체 층(OS2)과 산화물 절연 층(OI2) 사이의 계면에 에너지 장벽이 존재한다. 이러한 에너지 장벽들은 산화물 반도체 층들과 산화물 절연 층들 사이의 계면들에 존재하므로, 계면들에서 캐리어들의 이동은 방지될 수 있고; 따라서 캐리어들은 산화물 반도체 층들 내부에서 이동하고, 산화물 반도체 층들로부터 산화물 절연 층들로 이동하지 않는다. 즉, 산화물 반도체의 밴드 갭보다 계단적으로 큰 밴드 갭들을 갖는 재료들 사이에 산화물 반도체 층들이 개재되도록 적층 구조가 형성될 때, 캐리어들은 산화물 반도체 층(OS1)과 산화물 반도체 층(OS2) 내부에서 이동한다.14, on the gate electrode side (channel side) of the oxide semiconductor layer OS1, an energy barrier exists at the interface between the oxide semiconductor layer OS1 and the oxide insulating layer OI1. Similarly, on the back channel side (opposite of the gate electrode side) of the oxide semiconductor layer OS2, an energy barrier exists at the interface between the oxide semiconductor layer OS2 and the oxide insulating layer OI2. Since these energy barriers exist at the interfaces between the oxide semiconductor layers and the oxide insulating layers, the movement of carriers at the interfaces can be prevented; Thus, carriers move inside the oxide semiconductor layers and do not migrate from the oxide semiconductor layers to the oxide insulating layers. That is, when a stacked structure is formed such that oxide semiconductor layers are interposed between materials having band gaps stepwise larger than the band gap of the oxide semiconductor, carriers move inside the oxide semiconductor layer OS1 and the oxide semiconductor layer OS2. do.

<반도체 장치의 제작 방법><Method of manufacturing semiconductor device>

트랜지스터(310)를 제작하는 방법의 일 예가 도 3을 참조하여 아래에서 기술될 것이다.An example of a method of manufacturing the

먼저, 게이트 전극 층(402)이 절연 표면을 갖는 기판(400) 위에 형성된다. First, a

절연 표면을 갖는 기판(400)으로서 사용될 수 있는 기판에 대한 특별한 제한은 없지만, 기판이 이후에 수행되는 열처리를 견디기에 충분한 열 저항을 갖는 것이 최소한 필요하다. 예컨대, 바륨 붕규산염 유리, 알루미노 붕규산염 유리, 등의 유리 기판, 세라믹 기판, 수정 기판, 사파이어 기판, 등이 사용될 수 있다. 대안적으로, 실리콘, 탄화 실리콘, 등으로 만들어진 단결정 반도체 기판 또는 다결정 반도체 기판, 실리콘 게르마늄, 등으로 만들어진 복합 반도체 기판, SOI 기판, 등이 기판(400)으로 사용될 수 있다. 또 다른 대안으로서, 반도체 소자를 추가로 구비한 이들 기판들 중 임의의 기판이 기판(400)으로 사용될 수 있다.There is no particular limitation on the substrate that can be used as the

게이트 전극 층(402)은 몰리브덴, 티타늄, 탄탈, 텅스텐, 알루미늄, 구리, 크롬, 네오디뮴, 또는 스칸듐, 또는 주 성분으로서 이들 재료들 중 임의의 것을 함유한 합금재료와 같은 금속 재료를 사용하여 형성될 수 있다. 대안적으로, 인과 같은 불순물 원소로 도핑된 다결정 실리콘 막으로 전형화된 반도체 막, 또는 규화 니켈 막과 같은 규화물 막이 게이트 전극 층(402)으로 사용될 수 있다. 게이트 전극 층(402)은 단일층 구조 또는 적층 구조를 가질 수 있다. 게이트 전극 층(402)은 예컨대 30°이상 70°이하의 경사 각도를 갖는 경사진 형태를 가질 수 있다. 여기에서, 경사 각도는 경사진 형태를 갖는 층의 측면 표면과 층의 바닥 표면 사이에 형성된 각도를 언급한다.The

게이트 전극 층(402)의 재료는 산화 인듐 산화 주석, 산화 텅스텐을 함유하는 산화 인듐, 산화 텅스텐을 함유하는 산화 인듐 아연, 산화 티타늄을 함유하는 산화 인듐, 산화 티타늄을 함유하는 산화 인듐 주석, 산화 인듐 산화 아연, 또는 산화 실리콘이 첨가된 산화 인듐 주석과 같은 전도성 재료가 될 수 있다.The material of the

대안적으로, 게이트 전극 층(402)의 재료는 질소를 함유하는 In-Ga-Zn계 산화물, 질소를 함유하는 In-Sn계 산화물, 질소를 함유하는 In-Ga계 산화물, 질소를 함유하는 In-Zn계 산화물, 질소를 함유하는 Sn계 산화물, 질소를 함유하는 In계 산화물, 또는 질화 금속(질화 인듐, 질화 아연, 질화 탄탈, 또는 질화 텅스텐과 같은)이 될 수 있다. 이들 재료들 각각은 5eV 이상의 일함수를 갖고, 이는 게이트 전극 층(402)을 위해 사용될 때 트랜지스터의 문턱 전압이 양이 될 수 있게 한다. 따라서, 정상 오프 스위칭 트랜지스터가 제공될 수 있다.Alternatively, the material of the

다음에, 게이트 절연 층(404a)과 게이트 절연 층(404b)을 포함하는 게이트 절연 층(404)은 게이트 전극 층(402)을 덮도록 형성된다(도 3의 A 참조). 질소를 함유하는 실리콘 막은 게이트 절연 층(404)을 위해 사용될 수 있다. 본 실시예에 있어서, 게이트 절연 층(404)은 질화 실리콘 막을 포함하는 게이트 절연 층(404a)과 질화 실리콘 막을 포함하는 게이트 절연 층(404b)을 적층함으로써 형성된다. 면 내의 변동, 입자들의 혼합, 및 막 형성 주기 시간의 감소를 위해, 게이트 절연 층(404)을 형성하기 위해 CVD 방법을 사용하는 것이 효과적이다. CVD 방법은 또한 대형 기판 위에 막을 형성하는데 효과적이다.Next, a

본 실시예에 있어서, 게이트 절연 층(404a) 및 게이트 절연 층(404b)은 플라즈마 CVD 방법에 의해 연속적으로 형성된다. 먼저, 공급 가스로서 실란(SiH4), 질소(N2) 및 암모니아(NH3)의 혼합 가스를 사용하여, 질화 실리콘 막이 게이트 절연 층(404a)으로서 형성되고, 이후 공급 가스가 실란(SiH4)과 질소(N2)의 혼합 가스로 변경되고, 질화 실리콘 막이 게이트 절연 층(404b)으로서 형성된다.In this embodiment, the

공급 가스로서 실란(SiH4), 질소(N2) 및 암모니아(NH3)의 혼합 가스를 사용하는 플라즈마 CVD 방법에 의해 형성된 질화 실리콘 막은 공급 가스로서 실란(SiH4)과 질소(N2)의 혼합 가스를 사용하여 형성된 질화 실리콘 막보다 더 적은 결함들을 포함한다. 따라서, 게이트 절연 층(404a)은 적어도 게이트 절연 층(404b)보다 더 적은 결함들을 포함하고, 전자 스핀 공명(ESR) 분광법에서 Nc 중심에서(2.003의 g 계수에서) 나타나는 신호에 대응하는 1×1017spins/㎤ 이하, 바람직하게는 5×1016spins/㎤ 이하의 스핀 밀도를 가질 수 있다. 암모니아를 포함하는 혼합 가스를 사용하여 형성된 질화 실리콘 막은 공급 가스로서 실란과 질소의 혼합 가스를 사용하여 형성된 것보다 더 양호한 커버리지를 제공한다. 따라서, 게이트 전극 층(402)과 접촉하는 게이트 절연 층으로서, 상술한 혼합 가스를 사용하여 형성된 질화 실리콘 막을 제공하는 것이 효과적이다. 적은 수의 결함들을 포함하는 게이트 절연 층(404a)이 300nm 이상 400nm 이하의 두께를 갖도록 형성될 때, 게이트 절연 층(404)의 내전압은 300V 이상이 될 수 있다.The silicon nitride film formed by the plasma CVD method using a mixed gas of silane (SiH 4 ), nitrogen (N 2 ) and ammonia (NH 3 ) as a supply gas is a combination of silane (SiH 4 ) and nitrogen (N 2 ) as a supply gas. It contains fewer defects than a silicon nitride film formed using a mixed gas. Thus, the

한편, 암모니아를 함유하지 않는 소스 가스를 통해 형성된 게이트 절연 층(404b)은 게이트 절연 층(404a)보다 더 낮은 수소 농도를 함유한다. 25nm 이상 150nm 이하의 두께를 갖는 이러한 막이 산화물 절연 층(406)과 게이트 전극 층(402) 사이에 제공될 때, 게이트 절연 층(404b)으로부터 산화물 절연 층(406) 및 산화물 반도체 층(408)으로의 수소의 진입을 줄일 수 있다. 게이트 절연 층(404b)은 또한 게이트 절연 층(404a)에 함유된 수소 또는 수소 화합물의 산화물 절연 층(406) 및 산화물 반도체 층(408)으로의 진입을 감소시키는 장벽 막으로서 기능한다.On the other hand, the

큰 두께를 갖고, 적은 수의 결함들을 포함하는 게이트 절연 층(404a)과 낮은 수소 농도를 갖는 게이트 절연 층(404b)이 게이트 절연 층(404)으로서 적층될 때, 양호한 내전압을 얻고, 동시에 수소와 같은 불순물의 산화물 절연 층(406) 및 산화물 반도체 층(408)으로의 확산을 감소시키는 것이 가능하다. 따라서, 게이트 절연 층(404)을 포함하는 트랜지스터에 대한 정전기 방전 손상을 줄이고, 이의 전기 특성들을 안정화시키는 것이 가능하다.When the

다음에, 산화물 절연 층과 산화물 반도체 층이 게이트 절연 층(404b) 위에 형성되고, 에칭 처리에 의해 섬 형태로 처리되고, 이에 의해 산화물 절연 층(406), 및 산화물 반도체 층(408a)과 산화물 반도체 층(408b)을 포함하는 산화물 반도체 층(408)이 형성된다(도 3의 B 참조). 하나의 포토마스크를 사용하여 에칭 처리가 수행되기 때문에, 산화물 절연 층(406)과 산화물 반도체 층(408)은 평면도에서 동일한 패턴 형태를 갖고, 이들의 단부들은 서로 배향된다.Next, an oxide insulating layer and an oxide semiconductor layer are formed over the

산화물 절연 층(406)으로서, 산화물 반도체 층(408)의 구성 원소들로부터 선택된 하나 이상의 금속 원소들을 함유하는 산화물 절연 층이 제공된다. 예컨대, 산화 갈륨 막, 산화 갈륨 아연 막, 산화 갈륨 가돌리늄 막, 또는 높은 갈륨 함량과 낮은 인듐 함량을 갖는 In-Ga-Zn계 산화물 절연 막과 같은 절연 막을 사용하는 것이 바람직하다.As the

산화물 반도체 층(408)은 비정질 구조 또는 결정 구조를 가질 수 있다. 형성된 후의 산화물 반도체 층이 비정질 구조를 갖는 경우, 산화물 반도체 층은, 산화물 반도체 층(408)이 결정 구조를 갖도록, 이후의 제조 공정에서 열처리를 받을 수 있다. 비정질 산화물 반도체 층을 결정화하기 위한 열처리는, 250℃ 이상 700℃ 이하, 바람직하게는 400℃ 이상, 더 바람직하게는 500℃ 이상, 추가로 더욱 바람직하게는 550℃ 이상의 온도에서 수행된다. 열처리가 또한 제조 공정 내의 다른 열처리로서 작용할 수 있음을 주목해야 한다.The

산화물 절연 층(406) 및 산화물 반도체 층(408)은 스퍼터링 방법, 분자빔 에피택시(MBE) 방법, CVD 방법, 펄스드 레이저 증착 방법, 원자층 증착(ALD) 방법, 등에 의해 적절하게 형성될 수 있다.The

산화물 절연 층(406) 및 산화물 반도체 층(408)의 형성시, 함유될 수소의 농도는 가능한 한 많이 감소되는 것이 바람직하다. 수소의 농도를 줄이기 위하여, 예컨대, 산화물 절연 층 및 산화물 반도체 층이 스퍼터링 방법에 의해 형성되는 경우, 수소, 물, 수산기 및 수산화물과 같은 불순물들이 제거된 높은 순도의 희 가스(전형적으로 아르곤), 높은 순도의 산소, 또는 희 가스와 산소의 높은 순도의 혼합 가스가 스퍼터링 장치의 막 형성 챔버에 공급되는 대기 가스로서 적절하게 사용된다.When forming the

산화물 절연 층 및 산화물 반도체 층은, 막 형성 챔버 내에 남아 있는 습기가 제거되는 동안, 수소와 습기가 제거된 스퍼터링 가스가 막 형성 챔버 내로 도입되는 방식으로 형성되고, 이에 의해 산화물 절연 층 및 산화물 반도체 층 내의 수소의 농도는 감소될 수 있다. 막 형성 챔버 내에 남아 있는 습기를 제거하기 위하여, 크라이오 펌프, 이온 펌프, 또는 티타늄 승화 펌프와 같은 흡착 진공 펌프가 사용되는 것이 바람직하다. 저온 동결 트랩(cold trap)을 구비한 터보 분자 펌프가 대안적으로 사용될 수 있다. 막 형성 챔버가 수소 분자, 물(H2O)과 같은 수소 원자를 함유한 화합물(바람직하게는 또한 탄소 원자를 포함하는 화합물), 등을 제거하는 높은 성능을 갖는 크라이오 펌프로 배기될 때, 막 형성 챔버 내에서 형성된 막 내에 함유될 불순물 농도는 감소될 수 있다.The oxide insulating layer and the oxide semiconductor layer are formed in such a way that hydrogen and a sputtering gas from which moisture has been removed are introduced into the film forming chamber while the moisture remaining in the film forming chamber is removed, whereby the oxide insulating layer and the oxide semiconductor layer The concentration of hydrogen in the can be reduced. In order to remove moisture remaining in the film forming chamber, it is preferable to use an adsorption vacuum pump such as a cryo pump, an ion pump, or a titanium sublimation pump. Turbomolecular pumps with cold traps can alternatively be used. When the film forming chamber is evacuated to a cryopump with high performance to remove hydrogen molecules, compounds containing hydrogen atoms such as water (H 2 O) (preferably also compounds containing carbon atoms), etc., The concentration of impurities to be contained in the film formed in the film formation chamber can be reduced.

산화물 절연 층 및 산화물 반도체 층이 공기에 노출되지 않고 연속적으로 형성되는 것이 바람직함을 주목해야 한다. 공기에 노출되지 않고 산화물 절연 층 및 산화물 반도체 층의 연속적인 형성에 의해, 수소 또는 수소 화합물(예, 물)은 산화물 절연 층의 표면 또는 그 위에 적층된 산화물 반도체 층의 표면에 부착되는 것이 방지될 수 있다. 따라서, 불순물들의 진입은 감소될 수 있다.It should be noted that it is preferable that the oxide insulating layer and the oxide semiconductor layer are formed continuously without being exposed to air. By the continuous formation of the oxide insulating layer and the oxide semiconductor layer without exposure to air, hydrogen or a hydrogen compound (e.g., water) can be prevented from adhering to the surface of the oxide insulating layer or the surface of the oxide semiconductor layer stacked thereon. I can. Thus, the ingress of impurities can be reduced.

산화물 절연 층 또는 산화물 반도체 층이 스퍼터링 방법에 의해 형성될 때, 막 형성을 위해 사용된 금속 산화물 타깃의 상대적인 밀도(충진 계수)는 90% 이상 100% 이하, 바람직하게는 95% 이상 99.9% 이하이다. 높은 상대 밀도를 갖는 금속 산화물 타깃을 사용하여, 조밀한 산화물 막이 형성될 수 있다.When the oxide insulating layer or oxide semiconductor layer is formed by the sputtering method, the relative density (filling factor) of the metal oxide target used for film formation is 90% or more and 100% or less, preferably 95% or more and 99.9% or less. . By using a metal oxide target having a high relative density, a dense oxide film can be formed.

산화물 반도체 층의 불순물 농도를 줄이기 위하여, 기판(400)이 높은 온도로 유지되는 동안 산화물 반도체 층을 형성하는 것이 또한 효과적임을 주목해야 한다. 기판(400)이 가열되는 온도는 150℃ 이상 450℃ 이하일 수 있고; 기판 온도는 바람직하게는 200℃ 이상 350℃ 이하이다. 결정 산화물 반도체 층은 기판을 형성시에 높은 온도로 가열함으로써 형성될 수 있다.It should be noted that in order to reduce the impurity concentration of the oxide semiconductor layer, it is also effective to form the oxide semiconductor layer while the

CAAC-OS 막이 산화물 반도체 층(408)으로 사용되는 경우, CAAC-OS 막은 다음의 방법들로 얻어질 수 있다. 하나의 방법은 200℃ 이상 450℃ 이하의 막 형성 온도에서 산화물 반도체 층을 형성하는 것이고, 이에 의해 표면에 실질적으로 수직인 c-축 배향을 얻는다. 다른 방법은 얇은 산화물 반도체 층을 형성하고, 이후 이 층을 200℃ 이상 700℃ 이하의 온도로 수행되는 열처리를 받게 하고, 이에 의해 표면에 실질적으로 수직인 c-축 배향을 얻는다. 또 다른 방법은 제 1의 얇은 산화물 반도체 막을 형성하고, 이 막을 200℃ 이상 700℃ 이하의 온도로 수행되는 열처리를 받게 하고, 이후 제 2 산화물 반도체 막을 형성하고, 이에 의해 표면에 실질적으로 수직인 c-축 배향을 얻는다.When the CAAC-OS film is used as the

산화물 반도체 층(408)을 위해 사용된 산화물 반도체는 적어도 인듐(In)을 함유한다. 특히, 인듐과 아연(Zn)이 바람직하게 함유된다. 덧붙여, 산화물 반도체를 사용하는 트랜지스터의 전기 특성들의 변동을 줄이기 위한 안정제로서, 갈륨(Ga)이 추가적으로 함유되는 것이 바람직하다. 주석(Sn), 하프늄(Hf), 알루미늄(Al) 및 지르코늄(Zr)으로부터 선택된 하나 이상의 원소들이 안정제로서 함유되는 것이 바람직하다.The oxide semiconductor used for the

다른 안정제로서, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유러퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 튤륨(Tm), 이테르븀(Yb), 및 루테튬(Lu)으로부터 선택된 하나 이상의 란탄족원소가 함유될 수 있다.As other stabilizers, lanthanum (La), cerium (Ce), praseodymium (Pr), neodymium (Nd), samarium (Sm), europium (Eu), gadolinium (Gd), terbium (Tb), dysprosium (Dy), One or more lanthanide elements selected from holmium (Ho), erbium (Er), thulium (Tm), ytterbium (Yb), and lutetium (Lu) may be contained.

산화물 반도체로서, 예컨대, 산화 인듐, 산화 주석, 산화 아연, 2-원소 금속의 산화물인 In-Zn계 산화물, In-Mg계 산화물 또는 In-Ga계 산화물, 3-원소 금속의 산화물인 In-Ga-Zn계 산화물, In-Al-Zn계 산화물, In-Sn-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물 또는 In-Lu-Zn계 산화물, 또는 4-원소 금속 산화물인 In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물 또는 In-Hf-Al-Zn계 산화물이 사용될 수 있다.As an oxide semiconductor, for example, indium oxide, tin oxide, zinc oxide, an In-Zn-based oxide that is an oxide of a two-element metal, an In-Mg-based oxide or an In-Ga-based oxide, and an In-Ga that is an oxide of a three-element metal. -Zn-based oxide, In-Al-Zn-based oxide, In-Sn-Zn-based oxide, In-Hf-Zn-based oxide, In-La-Zn-based oxide, In-Ce-Zn-based oxide, In-Pr-Zn Oxide, In-Nd-Zn oxide, In-Sm-Zn oxide, In-Eu-Zn oxide, In-Gd-Zn oxide, In-Tb-Zn oxide, In-Dy-Zn oxide , In-Ho-Zn-based oxide, In-Er-Zn-based oxide, In-Tm-Zn-based oxide, In-Yb-Zn-based oxide or In-Lu-Zn-based oxide, or 4-element metal oxide In- Sn-Ga-Zn-based oxide, In-Hf-Ga-Zn-based oxide, In-Al-Ga-Zn-based oxide, In-Sn-Al-Zn-based oxide, In-Sn-Hf-Zn-based oxide or In- Hf-Al-Zn-based oxide may be used.

예컨대, "In-Ga-Zn계 산화물"은 주요 구성원소들로서 In, Ga 및 Zn을 함유하는 산화물을 의미하고, In:Ga:Zn의 비율에 대한 어떠한 제한도 존재하지 않는다. 더욱이, In, Ga 및 Zn에 부가하여 금속 원소가 함유될 수 있다.For example, "In-Ga-Zn-based oxide" means an oxide containing In, Ga, and Zn as major constituent elements, and there is no restriction on the ratio of In:Ga:Zn. Moreover, metal elements may be contained in addition to In, Ga and Zn.

대안적으로, InMO3(ZnO)m(m>0, 여기에서 m은 정수가 아님)으로 표현된 재료가 산화물 반도체로서 사용될 수 있다. M은 Ga, Fe, Mn 및 Co로부터 선택된 하나 이상의 금속 원소들을 나타냄을 주목해야 한다. 대안적으로, In2SnO5(ZnO)n(n>0, 여기에서 n은 정수)으로 표현된 재료가 산화물 반도체로서 사용될 수 있다.Alternatively, a material expressed as InMO 3 (ZnO) m (m>0, where m is not an integer) can be used as the oxide semiconductor. It should be noted that M represents one or more metal elements selected from Ga, Fe, Mn and Co. Alternatively, a material represented by In 2 SnO 5 (ZnO) n (n>0, where n is an integer) can be used as the oxide semiconductor.

예컨대, In:Ga:Zn = 1:1:1(=1/3:1/3:1/3), In:Ga:Zn = 2:2:1(=2/5:2/5:1/5), 또는 In:Ga:Zn = 3:1:2(=1/2:1/6:1/3)의 원자 비율을 갖는 In-Ga-Zn계 산화물 또는 위의 원자 비율들에 근접한 원자 비율을 갖는 산화물이 사용될 수 있다. 대안적으로, In:Sn:Zn = 1:1:1(=1/3:1/3:1/3), In:Sn:Zn = 2:1:3(=1/3:1/6:1/2), 또는 In:Sn:Zn = 2:1:5(=1/4:1/8:5/8)의 원자 비율을 갖는 In-Sn-Zn계 산화물 또는 위의 원자 비율들에 근접한 원자 비율을 갖는 산화물이 사용될 수 있다.For example, In:Ga:Zn = 1:1:1(=1/3:1/3:1/3), In:Ga:Zn = 2:2:1(=2/5:2/5:1 /5), or an In-Ga-Zn-based oxide with an atomic ratio of In:Ga:Zn = 3:1:2 (=1/2:1/6:1/3) or close to the above atomic ratios An oxide having an atomic ratio can be used. Alternatively, In:Sn:Zn = 1:1:1(=1/3:1/3:1/3), In:Sn:Zn = 2:1:3(=1/3:1/6 :1/2), or In:Sn:Zn = 2:1:5 (=1/4:1/8:5/8) In-Sn-Zn oxide having an atomic ratio of or above atomic ratios An oxide having an atomic ratio close to can be used.

그러나, 트랜지스터에 포함된 인듐을 함유하는 산화물 반도체는 위에서 주어진 재료들로 국한되지 않고; 적절한 조성을 갖는 재료가 필요한 전기 특성들(예, 전계-효과 이동도, 문턱 전압, 및 변동)에 의존하여 인듐을 함유하는 산화물 반도체를 포함하는 트랜지스터를 위해 사용될 수 있다. 필요한 전기 특성들을 얻기 위하여, 캐리어 농도, 불순물 농도, 결함 밀도, 산소에 대한 금속 원소의 원자 비율, 원자간 거리, 밀도, 등이 적절하게 설정되는 것이 바람직하다.However, the oxide semiconductor containing indium contained in the transistor is not limited to the materials given above; A material of an appropriate composition can be used for a transistor comprising an oxide semiconductor containing indium depending on the required electrical properties (eg, field-effect mobility, threshold voltage, and fluctuation). In order to obtain necessary electrical properties, it is preferable that the carrier concentration, impurity concentration, defect density, atomic ratio of metal elements to oxygen, interatomic distance, density, etc. are set appropriately.

예컨대, 높은 전계-효과 이동도는 In-Sn-Zn계 산화물을 포함하는 트랜지스터 내에서 상대적으로 쉽게 얻어질 수 있다. 또한 In-Ga-Zn계 산화물을 포함하는 트랜지스터의 경우, 부피 내의 결함 밀도를 줄임으로써 전계-효과 이동도는 증가할 수 있다.For example, high field-effect mobility can be obtained relatively easily in a transistor containing an In-Sn-Zn-based oxide. In addition, in the case of a transistor including an In-Ga-Zn-based oxide, the field-effect mobility can be increased by reducing the defect density in the volume.

예컨대, "원자 비율, In:Ga:Zn = a:b:c(a+b+c=1)로 In, Ga 및 Zn을 포함하는 산화물의 조성이, 원자 비율, In:Ga:Zn = A:B:C(A+B+C=1)로 In, Ga 및 Zn을 포함하는 산화물의 조성의 이웃에 있다"라는 표현은 예컨대 a, b 및 c가 다음의 관계: (a-A)2 + (b-B)2 + (c-C)2 ≤ r2이고, r이 0.05일 수 있는 관계를 충족시킴을 의미함을 주목해야 한다. 이러한 관계는 다른 산화물들에도 동일하게 적용된다.For example, "atomic ratio, In:Ga:Zn = a:b:c (a + b + c = 1), the composition of the oxide containing In, Ga, and Zn, the atomic ratio, In:Ga:Zn = A :B:C(A+B+C=1) is adjacent to the composition of the oxide containing In, Ga and Zn", for example a, b and c have the following relationship: (aA) 2 + ( It should be noted that bB) 2 + (cC) 2 ≤ r 2 , meaning that r meets a relationship that could be 0.05. This relationship applies equally to other oxides.

더욱이, 과잉 수소(물 및 수산기를 포함)를 제거하기(탈수화 또는 탈수소화 를 수행하기) 위하여 산화물 절연 층(406) 및/또는 산화물 반도체 층(408)에 대해 열처리가 수행되는 것이 바람직하다. 열처리 온도는 300℃ 이상 700℃ 이하, 또는 기판의 변형점 미만이다. 열처리는 감소된 압력, 질소 분위기, 등 하에서 수행될 수 있다. n-형 전도성을 부가하는 불순물인 수소는 열처리에 의해 제거될 수 있다.Moreover, it is preferable that a heat treatment is performed on the

탈수화 또는 탈수소화를 위한 이러한 열처리가 산화물 절연 층 및/또는 산화물 반도체 층의 형성 이후 수행되는 한, 이러한 열처리는 트랜지스터를 제작하는 공정 내의 임의의 타이밍에 수행될 수 있음을 주목해야 한다. 탈수화 또는 탈수소화를 위한 이러한 열처리는 복수 횟수로 수행될 수 있고, 또한 다른 열처리로서 작용할 수 있다.It should be noted that as long as this heat treatment for dehydration or dehydrogenation is performed after formation of the oxide insulating layer and/or oxide semiconductor layer, this heat treatment can be performed at any timing in the process of fabricating the transistor. This heat treatment for dehydration or dehydrogenation may be performed a plurality of times, and may also serve as another heat treatment.

산화물 절연 층이 산소 과잉 영역을 포함하는 경우, 탈수화 또는 탈수소화를 위한 이러한 열처리는, 산화물 절연 층 내에 함유된 산소가 열 처리를 통해 방출되는 것이 예방될 수 있기 때문에, 산화물 절연 층 및 산화물 반도체 층이 섬 형태로 처리되기 이전에 수행되는 것이 바람직함을 주목해야 한다.When the oxide insulating layer contains an oxygen-excessive region, this heat treatment for dehydration or dehydrogenation can prevent the oxygen contained in the oxide insulating layer from being released through heat treatment, so that the oxide insulating layer and the oxide semiconductor It should be noted that it is preferred that the layer is carried out before it is treated in the form of an island.

열처리시, 물, 수소, 등이 질소, 또는 헬륨, 네온 또는 아르곤과 같은 희가스에 함유되지 않는 것이 바람직하다. 대안적으로, 열처리 장치에 도입된 질소, 또는 헬륨, 네온 또는 아르곤과 같은 희가스의 순도는 바람직하게 6N(99.9999 %) 이상, 더 바람직하게는 7N(99.99999 %) 이상(즉, 불순물 농도는 1 ppm 이하, 바람직하게는 0.1 ppm 이하)으로 설정된다.During the heat treatment, it is preferable that water, hydrogen, and the like are not contained in nitrogen or a noble gas such as helium, neon or argon. Alternatively, the purity of nitrogen or rare gases such as helium, neon or argon introduced into the heat treatment apparatus is preferably 6N (99.9999%) or more, more preferably 7N (99.99999%) or more (i.e., the impurity concentration is 1 ppm. Or less, preferably 0.1 ppm or less).

덧붙여, 산화물 반도체 층(408)이 열처리에 의해 가열된 후, 고-순도의 산소 가스, 고-순도의 일산화 이질소 가스, 또는 초-건조 공기(캐비티 링 다운 레이저 분광(CRDS)계를 사용하는 이슬점 미터로 측정할 때, 20 ppm(이슬점으로 환산하여 -55℃) 이하, 바람직하게는 1 ppm 이하, 더욱 바람직하게는 10 ppb 이하의 습기 함량을 갖는)가, 가열 온도가 유지되고 있거나 또는 점진적으로 감소하고 있는 동안 동일한 노 안으로 도입될 수 있다. 물, 수소, 등이 산소 가스 또는 일산화 이질소 가스에 함유되지 않는 것이 바람직하다. 열처리 장치에 도입되는 산소 가스 또는 일산화 이질소 가스의 순도는 바람직하게 6N 이상, 더 바람직하게는 7N 이상(즉, 산소 가스 또는 일산화 이질소 가스 내의 불순물들의 농도는 바람직하게 1 ppm 이하, 더욱 바람직하게는 0.1 ppm 이하)이다. 산소 가스 또는 일산화 이질소 가스는, 산화물 반도체의 주된 구성원소 재료이고 탈수화 또는 탈수소화를 위한 불순물 제거 단계에 의해 감소되는 산소를 공급하도록 작용하여, 산화물 반도체 층이 고도로 순화된 i-형(진성) 산화물 반도체 층이 될 수 있게 된다.In addition, after the

산화물 반도체의 주요 구성원소인 산소가 또한 방출되어 탈수화 또는 탈수소화 처리에 의해 감소될 가능성이 존재하기 때문에, 산소(산소 라디칼, 산소 원자 및 산소 이온 중 적어도 하나를 포함하는)는 탈수화 또는 탈수소화 처리를 겪은 산화물 반도체 층에 도입되어, 층에 산소를 공급할 수 있다.Oxygen (which contains at least one of an oxygen radical, an oxygen atom and an oxygen ion) is dehydrated or dehydrogenated, since oxygen, a major element of the oxide semiconductor, is also released and has the potential to be reduced by dehydration or dehydrogenation treatment. It is introduced into the oxide semiconductor layer that has undergone treatment, so that oxygen can be supplied to the layer.

산소는 탈수화되거나 탈수소화된 산화물 반도체 층에 도입 및 공급됨으로써, 산화물 반도체 층은 고도로 순화되어 i-형(진성)이 될 수 있다. 고도로 순화된 i-형(진성) 산화물 반도체를 갖는 트랜지스터의 전기 특성들의 변화는 억제되고, 트랜지스터는 전기적으로 안정된다.By introducing and supplying oxygen to the dehydrated or dehydrogenated oxide semiconductor layer, the oxide semiconductor layer can be highly purified and become i-type (intrinsic). Changes in the electrical properties of a transistor having a highly purified i-type (intrinsic) oxide semiconductor are suppressed, and the transistor is electrically stable.

산화물 반도체 층(408)에 산소의 도입 단계에서, 산소는 산화물 반도체 층(408)에 직접 도입될 수 있거나, 또는 이후에 형성될 다른 절연 층을 통해 산화물 반도체 층(408)에 도입될 수 있다. 산소(산소 라디칼, 산소 원자 및 산소 이온 중 적어도 하나를 포함하는)를 도입하는 방법으로서, 이온 주입 방법, 이온 도핑 방법, 플라즈마 이머전 이온 주입 방법, 플라즈마 처리, 등이 사용될 수 있다. 산소를 함유하는 가스는 산소 도입 처리를 위해 사용될 수 있다. 산소를 함유하는 가스로서, 산소, 일산화 이질소, 이산화질소, 이산화탄소, 일산화탄소, 등이 사용될 수 있다. 또한, 희 가스가 산소 도입 처리를 위해 산소를 함유하는 가스 내에 포함될 수 있다.In the step of introducing oxygen into the

예컨대, 산소 이온이 이온 주입 방법에 의해 산화물 반도체 층(408)에 주입되는 경우, 주입량은 1×1013이온/㎠ 이상 5×1016이온/㎠ 이하가 될 수 있다.For example, when oxygen ions are implanted into the

대안적으로, 산소는 산화물 반도체 층(408)에 다음의 방식으로 공급될 수 있다: 산화물 반도체 층과 접촉하는 산화물 절연 층(406)이 산소 과잉 영역을 포함하도록 형성되고; 산화물 절연 층(406)과 산화물 반도체 층(408)이 서로 접촉하는 상태에서 열 처리가 수행되어 산화물 절연 층(406) 내에 함유된 과잉 산소가 산화물 반도체 층(408)으로 확산된다. 이러한 열 처리는 트랜지스터를 제작하는 공정 내의 다른 열 처리로서 작용할 수 있다.Alternatively, oxygen may be supplied to the

산화물 절연 층(406) 내에 산소 과잉 영역을 제공하기 위하여, 예컨대 산화물 절연 층은 산소 분위기 내에서 형성될 수 있다. 대안적으로, 산소는 산화물 절연 층(406) 내에 산소 과잉 영역을 제공하기 위하여 형성된 후의 산화물 절연 층으로 도입될 수 있다.In order to provide an oxygen-rich region in the

산화물 절연 층(406) 또는 산화물 반도체 층(408)에 산소의 공급 타이밍이 산화물 절연 층 또는 산화물 반도체 층의 형성 이후인 한, 상술한 것에 특별히 국한되지 않는다. 산소를 도입하는 단계는 복수 횟수로 수행될 수 있다. As long as the timing of supplying oxygen to the

다음에, 전도성 막이 산화물 반도체 층(408) 위에 형성되어, 이후 처리되고, 이에 의해 소스 전극 층(410a) 및 드레인 전극 층(410b)이 형성된다(도 3의 C 참조).Next, a conductive film is formed over the

소스 전극 층(410a) 및 드레인 전극 층(410b)은 예컨대, Al, Cr, Cu, Ta, Ti, Mo 및 W로부터 선택된 원소를 함유하는 금속 막, 구성 원소로서 이들 원소들 중 임의의 것을 함유하는 질화 금속 막(질화 티타늄 막, 질화 몰리브덴 막, 또는 질화 텅스텐 막), 등을 사용하여 형성될 수 있다. 대안적으로, Ti, Mo, 또는 W와 같은 높은 용융점 금속의 막 또는 이들의 질화 금속 막(예, 질화 티타늄 막, 질화 몰리브덴 막, 또는 질화 텅스텐 막)이 Al 막 또는 Cu 막과 같은 금속 막 위에 및/또는 아래에 형성될 수 있다. 또한 대안적으로, 소스 전극 층(410a) 및 드레인 전극 층(410b)은 전도성 금속 산화물을 사용하여 형성될 수 있다. 전도성 금속 산화물로서, 산화 인듐(In2O3), 산화 주석(SnO2), 산화 아연(ZnO), 산화 인듐 산화 주석(In2O3-SnO2), 산화 인듐 산화 아연(In2O3-ZnO), 또는 산화 실리콘을 함유하는 이들 금속 산화물 재료들 중 임의의 것이 사용될 수 있다.The

소스 전극 층(410a) 및 드레인 전극 층(410b)을 위해, 질소를 함유하는 In-Ga-Zn-O 막, 질소를 함유하는 In-Sn-O 막, 질소를 함유하는 In-Ga-O 막, 질소를 함유하는 In-Zn-O 막, 질소를 함유하는 Sn-O 막 또는 질소를 함유하는 In-O 막과 같은 질화 금속 막이 사용될 수 있다. 이들 막들은 산화물 반도체 층(408)과 동일한 구성 원소들을 포함하고, 따라서 산화물 반도체 층(408)과 안정된 계면을 형성할 수 있다. 예컨대, 소스 전극 층(410a) 및 드레인 전극 층(410b)은 질소를 함유하는 In-Ga-Zn-O 막과 텅스텐 막이 산화물 반도체 층(408)과 접촉하는 측으로부터 순서대로 적층된 적층 구조를 가질 수 있다.For the

이후, 산화물 절연 층(412)은 소스 전극 층(410a), 드레인 전극 층(410b) 및 노출된 산화물 반도체 층(408)을 덮도록 형성된다. 산화물 절연 층(412)은 산화물 절연 층(406)을 위한 것들과 유사한 재료 및 제작 방법을 사용하여 형성될 수 있다.Thereafter, the

이후 보호 절연 층(414)이 산화물 절연 층(412) 위에 형성된다(도 3의 D 참조).A protective insulating

보호 절연 층(414)은 산화 실리콘 막, 산화 갈륨 막, 산화 알루미늄 막, 질화 실리콘 막, 산화질화 실리콘 막, 산화질화 알루미늄 막, 질화산화 실리콘 막, 등을 사용하여, 플라즈마 CVD 방법 또는 스퍼터링 방법에 의해 형성될 수 있다. 제조 공정 도중에 또는 제조 이후 반도체 장치에 대한 정전기 방전 손상을 추가로 감소시키는 것이 가능하기 때문에, 보호 절연 층(414)은 바람직하게 질소를 함유하는 실리콘 막, 보다 더 바람직하게는 질화 실리콘 막을 포함하는 층임을 주목해야 한다.The protective

상기 방식으로, 본 실시예의 트랜지스터(310)가 형성될 수 있다.In this way, the

<반도체 장치의 구조 예 3><Structure Example 3 of a semiconductor device>

도 10은 트랜지스터(320)의 구조 예를 도시한다. 도 10의 A는 트랜지스터(320)의 평면도이고, 도 10의 B는 도 10의 A의 일점쇄선(X3-Y3)을 따라 취해진 단면도이고, 도 10의 C는 도 10의 A의 일점쇄선(V3-W3)을 따라 취해진 단면도이다.10 shows an example of the structure of the

도 1의 트랜지스터(300)와 같이, 도 10의 트랜지스터(320)는, 절연 표면을 갖는 기판(400) 위의 게이트 전극 층(402), 게이트 전극 층(402) 위의 게이트 절연 층(404), 게이트 절연 층(404) 위의 산화물 절연 층(406), 산화물 절연 층(406) 위에서 산화물 절연 층(406)과 접촉하고, 게이트 전극 층(402)과 중첩하는 산화물 반도체 층(408), 및 산화물 반도체 층(408)에 전기적으로 연결된 소스 전극 층(410a) 및 드레인 전극 층(410b)을 포함한다. 다른 구성요소들로서, 트랜지스터(320)는 소스 전극 층(410a) 및 드레인 전극 층(410b)을 덮고, 산화물 반도체 층(408)과 접촉하는 산화물 절연 층(412) 및 산화물 절연 층(412) 위의 보호 절연 층(414)을 포함할 수 있다.Like the

트랜지스터(320)는 게이트 절연 층(404)과 산화물 반도체 층(408)의 구조들에서 트랜지스터(300)와 다르다. 즉, 트랜지스터(320) 내의 게이트 절연 층(404)은 게이트 전극 층(402)과 접촉하는 게이트 절연 층(404c), 게이트 절연 층(404c) 위의 게이트 절연 층(404a), 및 게이트 절연 층(404a)과 산화물 절연 층(406) 사이의 게이트 절연 층(404b)을 포함한다. 트랜지스터(310) 내에서와 같이, 트랜지스터(320) 내의 산화물 반도체 층(408)은 산화물 절연 층(406)과 접촉하는 산화물 반도체 층(408a)과 산화물 절연 층(412)과 접촉하는 산화물 반도체 층(408b)을 포함한다.

트랜지스터(320) 내에서 게이트 절연 층(404)과 산화물 반도체 층(408) 이외의 다른 구성요소들이 트랜지스터(300)의 다른 구성요소들과 유사하고, 이를 위해 트랜지스터(300)의 설명이 인용될 수 있음을 주목해야 한다.In the

트랜지스터(320) 내의 산화물 반도체 층(408)의 구조는 트랜지스터(310) 내의 것과 유사하고, 이를 위해 트랜지스터(310)의 설명이 인용될 수 있다. 트랜지스터(320)가, 산화물 절연 층(412)과 접촉하는 산화물 절연 층(408b)의 영역의 두께가 소스 전극 층(410a) 및 드레인 전극 층(410b)과 접촉하는 영역들의 두께보다 얇은 예임을 주목해야 한다. 얇은 두께를 갖는 영역은 소스 전극 층(410a)과 드레인 전극 층(410b)을 형성하기 위하여 전도성 막을 처리하는 시간에 부분적으로 에칭됨으로써, 또는 소스 전극 층(410a)과 드레인 전극 층(410b)을 형성한 이후 산화물 반도체 층(408b)의 노출된 영역에 대한 에칭 처리를 수행함으로써 형성된다. 얇은 두께를 갖는 영역은 트랜지스터(320)의 채널 형성 영역으로 작용한다. 채널 형성 영역의 두께를 줄임으로써, 소스 전극 층(410a) 및 드레인 전극 층(410b)과 접촉하는 영역들의 저항은 채널 형성 영역의 저항보다 낮게 만들어질 수 있다. 따라서, 소스 전극 층(410a) 및 드레인 전극 층(410b)과의 접촉 저항은 감소될 수 있다.The structure of the

트랜지스터(320)에 포함된 게이트 절연 층(404)은, 게이트 전극 층(402)과 접촉하는 게이트 절연 층(404c), 게이트 절연 층(404c) 위에서 게이트 절연 층(404c)과 접촉하는 게이트 절연 층(404a), 및 산화물 절연 층(406)과 접촉하는 게이트 절연 층(404b)을 포함한다.The

본 실시예에 있어서, 질화 실리콘 막들은 게이트 절연 층(404c), 게이트 절연 층(404a) 및 게이트 절연 층(404b)으로 사용되고, 게이트 절연 층들은 플라즈마 CVD 방법에 의해 연속적으로 형성된다. 먼저, 공급 가스로서 실란(SiH4)과 질소(N2)의 혼합 가스의 공급을 통해, 질화 실리콘 막이 게이트 절연 층(404c)으로 형성된다. 이후, 공급 가스는 실란(SiH4), 질소(N2) 및 암모니아(NH3)의 혼합 가스로 변경되고, 질화 실리콘 막이 게이트 절연 층(404a)으로서 형성된다. 이후, 공급 가스는 실란(SiH4) 및 질소(N2)의 혼합 가스로 변경되고, 질화 실리콘 막이 게이트 절연 층(404b)으로서 형성된다.In this embodiment, silicon nitride films are used as the

실란(SiH4) 및 질소(N2)의 혼합 가스의 공급을 통해 형성된 게이트 절연 층(404c)은 더 적은 암모니아를 함유하는 막 형성 분위기 내에서 형성되고, 적어도 실란(SiH4), 질소(N2) 및 암모니아(NH3)의 혼합 가스의 공급을 통해 형성된 게이트 절연 층(404a)보다 더 낮은 암모니아 함량을 갖는다. 암모니아는 질소 원자 상의 외톨이 쌍의 전자들의 작용에 의해 금속 착물의 리간드가 된다. 따라서, 예컨대 구리가 게이트 전극 층(402)을 위해 사용되는 경우, 높은 암모니아 함량을 갖는 게이트 절연 층이 게이트 전극 층과 접촉하여 제공되고, 구리는 다음의 수학식 1에 의해 표현되는 반응에 의해 게이트 절연 층으로 확산될 수 있다.The

도 10에 도시된 트랜지스터(320)에서, 적어도 게이트 절연 층(404a)보다 낮은 암모니아 함량을 갖는 게이트 절연 층(404c)이 게이트 전극 층(402)과 접촉하여 제공되기 때문에, 게이트 전극 층(402) 재료(예, 구리)의 게이트 절연 층(404)으로의 확산은 줄어들 수 있다. 즉, 게이트 절연 층(404c)은 게이트 전극 층(402)에 포함된 금속 재료에 대한 장벽 막으로서 작용할 수 있다. 게이트 절연 층(404c)은 추가로 트랜지스터의 신뢰도를 개선할 수 있다.In the

트랜지스터(320)에 포함된 게이트 절연 층(404) 내의 게이트 절연 층(404a) 및 게이트 절연 층(404b)이 트랜지스터(310) 내의 것들과 유사할 수 있음을 주목해야 한다. 위의 구조를 갖는 게이트 절연 층을 포함하여, 트랜지스터는 정전기 방전에 의한 손상으로부터 예방될 수 있고, 안정적인 전기 특성들을 가질 수 있다. 따라서, 높은 신뢰성의 반도체 장치가 얻어질 수 있다.It should be noted that the

게이트 절연 층(404c)의 두께는 30nm 이상 100nm 이하이고, 바람직하게는 30nm 이상 50nm 이하이다. 상술한 바와 같이 트랜지스터에 대한 정전기 방전 손상의 대응책으로서 제공되는 게이트 절연 층(404a)의 두께는 바람직하게 300nm 이상 400nm 이하이다. 산화물 반도체 층(408)으로 수소의 확산을 방지하는 장벽 막으로서 기능하는 게이트 절연 층(404b)의 두께는 바람직하게 25nm 이상 150nm 이하이다. 바람직하게 각 게이트 절연 층의 두께가 적절히 조절되어, 게이트 절연 층(404)의 두께(게이트 절연 층(404c), 게이트 절연 층(404a) 및 게이트 절연 층(404b)의 총 두께)가 355nm에서 550nm의 범위에 들게 됨을 주목해야 한다.The thickness of the

<반도체 장치의 구조 예 4><Structure Example 4 of a semiconductor device>

도 11은 트랜지스터(330)의 구조 예를 도시한다. 도 11의 A는 트랜지스터(330)의 평면도이고, 도 11의 B는 도 11의 A의 일점쇄선(X4-Y4)을 따라 취해진 단면도이고, 도 11의 C는 도 11의 A의 일점쇄선(V4-W4)을 따라 취해진 단면도이다.11 shows an example of the structure of the

도 11에 도시된 트랜지스터(330)는, 절연 표면을 갖는 기판(400) 위의 게이트 전극 층(402), 게이트 전극 층(402) 위의 게이트 절연 층(404), 게이트 절연 층(404) 위의 산화물 절연 층(406), 산화물 절연 층(406) 위에서 산화물 절연 층(406)과 접촉하고, 게이트 전극 층(402)과 중첩하는 산화물 반도체 층(408), 산화물 반도체 층(408)에 전기적으로 연결된 소스 전극 층(410a) 및 드레인 전극 층(410b), 소스 전극 층(410a) 및 드레인 전극 층(410b)을 덮고, 산화물 반도체 층(408)과 접촉하는 산화물 절연 층(412) 및 산화물 절연 층(412) 위의 보호 절연 층(414)을 포함한다.The

트랜지스터(330) 내에서, 보호 절연 층(414)은 산화물 절연 층(412)과 접촉하는 보호 절연 층(414a)과 보호 절연 층(414a) 위의 보호 절연 층(414b)을 포함하는 적층 구조를 갖고, 이들 각각을 위해 질화 실리콘 막이 사용될 수 있다.Within the

보호 절연 층(414a)은 트랜지스터(310)의 게이트 절연 층(404b)과 유사할 수 있다. 보호 절연 층(414a)은 수소 또는 수소 화합물의 산화물 절연 층(412) 및 산화물 반도체 층(408)으로의 진입을 줄일 수 있고; 따라서 트랜지스터의 전기 특성들은 추가로 안정될 수 있다.The protective

보호 절연 층(414b)은 트랜지스터(310)의 게이트 절연 층(404a)과 유사할 수 있다. 보호 절연 층(414b)은 제작 공정 도중 또는 제작 이후에 반도체 장치에 대한 정전기 방전 손상을 줄일 수 있다.The protective

트랜지스터(330)의 다른 구성요소들이 트랜지스터(310)의 다른 구성요소들과 유사하고, 이를 위해 트랜지스터(310)의 설명이 인용될 수 있음을 주목해야 한다.It should be noted that the other components of the

도 1, 도 2, 도 10 및 도 11에 도시된 트랜지스터들의 구조들은 부분적으로 서로 상이하다; 하지만 본 발명의 실시예들은 이들 구조들에 국한되지 않고, 다양한 조합들이 가능함을 주목해야 한다.The structures of the transistors shown in Figs. 1, 2, 10 and 11 are partially different from each other; However, it should be noted that embodiments of the present invention are not limited to these structures, and various combinations are possible.