以下、本発明の好適な実施形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成の全てが本発明の必須構成要件であるとは限らない。

1.リアルタイムクロック回路、リアルタイムクロックモジュール

1-1.第1実施形態

1-1-1.リアルタイムクロックモジュールの構成

図1は、第1実施形態のリアルタイムクロックモジュール1の機能ブロック図である。図1に示すように、リアルタイムクロックモジュール1は、振動子2と、リアルタイムクロック回路3とを備える。

リアルタイムクロックモジュール1は、メイン電源4からリアルタイムクロック回路3の端子P1を介して第1の電源電圧である電源電圧VDDが供給され、バックアップ電源

5からリアルタイムクロック回路3の端子P2を介して第2の電源電圧である電源電圧VBATが供給される。

振動子2は、音叉型水晶振動子、ATカット水晶振動子、SCカット水晶振動子等であってもよいし、SAW(Surface Acoustic Wave)共振子や水晶振動子以外の圧電振動子であってもよい。また、振動子2は、シリコン半導体を材料とするMEMS(Micro Electro Mechanical Systems)振動子であってもよい。振動子2は、圧電効果によって励振されてもよいし、クーロン力(静電気力)によって駆動されてもよい。

リアルタイムクロック回路3は、発振回路10、第1分周回路20、第2分周回路30、計時回路40、論理回路50、ライトバッファー60、リードバッファー70、イベント時刻レジスター80、インターフェース回路90、記憶部100、割込発生回路110、電源電圧選択回路120、電源電圧判定回路130及びレギュレーター140を備える。ただし、リアルタイムクロック回路3は、これらの要素の一部を省略又は変更し、あるいは他の要素を追加した構成としてもよい。本実施形態では、リアルタイムクロック回路3は、1チップの集積回路(IC:Integrated Circuit)であるが、複数チップの集積回路で構成されてもよいし、少なくとも一部がディスクリート部品で構成されてもよい。

電源電圧判定回路130は、電源電圧VDDを監視し、電源電圧VDDが所定の電圧値VT以上であるか否かを判定し、判定信号VDETを出力する。本実施形態では、電源電圧判定回路130は、電源電圧VDDが電圧値VT以上であると判定した場合はハイレベルの判定信号VDETを出力し、電源電圧VDDが電圧値VT未満であると判定した場合はローレベルの判定信号VDETを出力する。

電源電圧選択回路120は、判定信号VDETに基づいて電源電圧VDD又は電源電圧VBATを選択して電源電圧VOUTとして出力する。具体的には、電源電圧選択回路120は、判定信号VDETがハイレベルである場合、すなわち、電源電圧判定回路130により電源電圧VDDが電圧値VT以上であると判定された場合は、電源電圧VDDを選択する。また、電源電圧選択回路120は、判定信号VDETがローレベルである場合、すなわち、電源電圧判定回路130により電源電圧VDDが電圧値VT未満であると判定された場合は、電源電圧VBATを選択する。

したがって、メイン電源4からリアルタイムクロックモジュール1に電源電圧VDDが供給されているときは、電源電圧VOUTは、電源電圧VDDであり、VT以上の所定の電圧値である。メイン電源4からリアルタイムクロックモジュール1への電源電圧VDDの供給が遮断されると、電源電圧VOUTは、直ちに電源電圧VBATに切り替わり、VT以下の所定の電圧値となる。そのため、リアルタイムクロックモジュール1は、メイン電源4からの電源電圧VDDの供給が遮断されている間も計時動作を継続することができる。これに対して、リアルタイムクロックモジュール1の動作を制御するホストデバイス6は、メイン電源4から電源電圧VDDが供給されて動作し、メイン電源4からの電源電圧VDDの供給が遮断されると動作を停止する。

レギュレーター140は、電源電圧VOUTに基づいて、一定の電圧値の安定化された電源電圧VOSC及び電源電圧VLOGICを生成する。

電源電圧VOSCは、発振回路10に供給される。また、電源電圧VLOGICは、第1分周回路20、第2分周回路30、計時回路40、論理回路50、ライトバッファー60、リードバッファー70、イベント時刻レジスター80、インターフェース回路90、記憶部100及び割込発生回路110に供給される。

発振回路10は、振動子2を発振させて第1クロック信号CK1を生成する。具体的には、発振回路10は、リアルタイムクロック回路3の端子P3,P4を介して振動子2の両端と電気的に接続されており、振動子2の出力信号を増幅してフィードバックすることにより振動子2を発振させて第1クロック信号CK1を出力する。本実施形態では、共振周波数の異なる2種類の振動子2を選択可能であり、第1クロック信号CK1の周波数は異なる2つの周波数、例えば、32.768kHz及び32kHzのいずれかとなる。第1クロック信号CK1を正確な周波数とするために、発振回路10は、温度補償機能や周波数制御機能を備えた発振回路であることが好ましい。

第1分周回路20は、第1クロック信号CK1を分周して、所望の周波数を有する第2クロック信号CK2を生成する。本実施形態では、第1分周回路20の分周比は固定されている。例えば、第1クロック信号CK1の周波数が32.768kHz又は32kHzであり、第1分周回路20の分周比が32である場合、第2クロック信号CK2の周波数は1.024kHz又は1kHzである。なお、第1分周回路20の詳細については後述する。

第2分周回路30は、第2クロック信号CK2を分周して、所望の周波数を有する第3クロック信号CK3を生成する。本実施形態では、第2分周回路30は、選択データSELの値に応じて、バイナリーカウンター又はBCD(Binary Coded Decimal)カウンターとして動作し、いずれの場合も生成される第3クロック信号CK3の周波数は1Hzとなる。具体的には、第2分周回路30は、選択データSELが0であればバイナリーカウンターとして動作し、第2クロック信号CK2を第1の分周比で分周して1Hzの第3クロック信号CK3を生成する。例えば、第2クロック信号CK2の周波数が1.024kHzである場合、第1の分周比は1024である。また、第2分周回路30は、選択データSELが1であればBCDカウンターとして動作し、第2クロック信号CK2を第2の分周比で分周して1Hzの第3クロック信号CK3を生成する。例えば、第2クロック信号CK2の周波数が1kHzである場合、第2の分周比は1000である。

また、第2分周回路30は、第2クロック信号CK2に基づいて、1秒よりも短い時間の計時データSUB_Tを生成する。例えば、計時データSUB_Tは、第2クロック信号CK2の周波数が1.024kHであれば1/1024秒単位の計時データであり、第2クロック信号CK2の周波数が1kHであれば1/1000秒単位の計時データである。

また、第2分周回路30は、論理回路50に第4クロック信号CK4を出力する。本実施形態では、第2分周回路30は、選択データSELが0であってバイナリーカウンターとして動作する場合は8Hzの第4クロック信号CK4を出力し、選択データSELが1であってBCDカウンターとして動作する場合は10Hzの第4クロック信号CK4を出力する。なお、第2分周回路30の詳細については後述する。

計時回路40は、第3クロック信号CK3に基づいて1秒以上の時間の計時データBCD_T,BIN_Tを生成する。計時データBCD_Tは、年、月、日、時、分及び秒の各BCD値を含み、計時データBIN_Tは2進数の値である。なお、計時回路40の詳細については後述する。

論理回路50は、補正データTDを用いて、基準信号REFに同期した間隔に相当する長さの期間である補正期間において、第1分周回路20に対して緩急処理を行う。本実施形態では、基準信号REFは、ホストデバイス6が生成し、リアルタイムクロック回路3の端子P5から入力される信号である。基準信号REFは、正確に所定の周波数を有する信号である。例えば、ホストデバイス6が不図示のGPS受信機を有し、基準信号REF

は、当該GPS受信機から出力される信号であってもよいし、当該GPS受信機から出力される信号に基づいて生成される信号であってもよい。補正データTDは、基準信号REFに同期した間隔での計時データSUB_Tの変化量に基づいて生成されたデータである。本実施形態では、補正データTDは、記憶部100に記憶されている。また、基準信号REFに同期した間隔は、基準信号REFの1周期の整数倍の長さである。したがって、論理回路50は、補正データTDを用いて、基準信号REFの1周期の整数倍の長さの補正期間において、第1分周回路20に対して緩急処理を行う。具体的には、論理回路50は、補正期間における第2クロック信号CK2の周波数を増加させるための制御信号PE又は補正期間における第2クロック信号CK2の周波数を減少させるための制御信号PDを生成する。例えば、論理回路50は、補正データTDに対してデルタシグマ変調を行って、制御信号PE,PDを生成してもよい。第1分周回路20は、制御信号PE,PDに応じて、補正期間における平均周波数が所定の周波数となる第2クロック信号CK2を生成する。

本実施形態では、論理回路50には補正期間設定データPNが入力され、論理回路50は、補正期間設定データPNと第2分周回路30が出力する第4クロック信号CK4とに基づいて、前述の基準信号REFに同期した間隔を決定する。具体的には、補正期間設定データPNの値をnとし、第4クロック信号CK4の周波数をfとし、あらかじめ決められた所定値をmとしたとき、当該間隔はn×m/f秒である。例えば、nが32であり、第4クロック信号CK4の周波数が8Hzであり、mが8である場合、当該間隔は32×8/8=32秒である。このとき、例えば、基準信号REFの周波数は1Hzであり、当該間隔は基準信号REFの1周期の32倍の長さである。また、nが256であり、第4クロック信号CK4の周波数が10Hzであり、mが8である場合、当該間隔は32×8/10=25.6秒である。このとき、例えば、基準信号REFの周波数は1.25Hzであり、当該間隔は基準信号REFの1周期の32倍の長さである。このように、補正期間設定データPNは、前述の基準信号REFに同期した間隔を指定する情報である。

また、本実施形態では、論理回路50は、補正期間において、第4クロック信号CK4の周期で第1分周回路20に対して緩急処理を行う。例えば、第2クロック信号CK2の周波数が1.024kHzである場合、第4クロック信号CK4の周波数は8Hzであるので、論理回路50は0.125秒間隔で緩急処理を行う。また、第2クロック信号CK2の周波数が1kHzである場合、第4クロック信号CK4の周波数は10Hzであるので、論理回路50は0.1秒間隔で緩急処理を行う。

ライトバッファー60は、インターフェース回路90からの不図示の書き込み要求信号に応じて、インターフェース回路90から出力される書き込みデータWDATを取得して保持する。ライトバッファー60が保持する書き込みデータWDATの一部は、書き込みデータSUB_WDとして第2分周回路30に出力され、書き込みデータWDATの他の一部は、書き込みデータBCD_WD,BIN_WDとして計時回路40に出力される。

リードバッファー70は、インターフェース回路90からの不図示の読み出し要求信号に応じて、第2分周回路30が生成した計時データSUB_T及び計時回路40が生成した計時データBCD_T,BIN_Tの少なくとも1つを取得して保持し、保持した計時データを読み出しデータRDATとしてインターフェース回路90に出力する。

イベント時刻レジスター80は、リアルタイムクロック回路3の端子P5から入力される基準信号REFの電圧レベルが遷移する所定のタイミングで、第2分周回路30が生成した計時データSUB_T及び計時回路40が生成した計時データBCD_T,BIN_Tを保持するバッファー回路である。例えば、基準信号REFの電圧レベルが遷移する所定のタイミングは、基準信号REFがローレベルからハイレベルに遷移するタイミングで

あってもよいし、基準信号REFがハイレベルからローレベルに遷移するタイミングであってもよい。イベント時刻レジスター80は、所定数の計時データを保持することが可能なサイズであり、保持した所定数の計時データを時刻データTSTMPとしてインターフェース回路90に出力する。以下では、イベント時刻レジスター80が基準信号REFに基づいて計時データSUB_T,BCD_T,BIN_Tを取得して保持する機能を「タイムスタンプ機能」という。

インターフェース回路90は、リアルタイムクロックモジュール1とホストデバイス6との間の通信のインターフェース回路である。本実施形態では、インターフェース回路90は、I2C(Inter-Integrated Circuit)バス対応のインターフェース回路であり、リアルタイムクロック回路3の端子P6を介して入力されるシリアルクロック信号SCLと、リアルタイムクロック回路3の端子P7を介して入出力されるシリアルデータ信号SDAとに基づいて、ホストデバイス6と通信する。ただし、インターフェース回路90は、SPI(Serial Peripheral Interface)などの他のシリアルバス対応のインターフェース回路であってもよいし、パラレルバス対応のインターフェース回路であってもよい。

インターフェース回路90は、ホストデバイス6から端子P6,P7を介してアクセス信号を受信し、受信したアクセス信号に応じた各種の処理を行う。

具体的には、インターフェース回路90は、計時データSUB_T,BCD_T,BIN_Tの少なくとも1つの書き換えを要求するアクセス信号を受信した場合、書き換え対象となる計時データの書き込みを要求する不図示の書き込み要求信号を発生する。そして、インターフェース回路90は、書き込み要求信号及び書き込みデータWDATをライトバッファー60に出力する。その後、計時データSUB_Tが書き換え対象である場合は、インターフェース回路90は、書き込みクロック信号SUB_WCKを第2分周回路30に出力し、第2分周回路30は、書き込みクロック信号SUB_WCKに応じて、計時データSUB_Tを、書き込みデータWDATの一部である書き込みデータSUB_WDに更新する。また、計時データBCD_Tが書き換え対象である場合は、インターフェース回路90は、書き込みクロック信号BCD_WCKを計時回路40に出力し、計時回路40は、書き込みクロック信号BCD_WCKに応じて、計時データBCD_Tを、書き込みデータWDATの一部である書き込みデータBCD_WDに更新する。また、計時データBIN_Tが書き換え対象である場合は、インターフェース回路90は、書き込みクロック信号BIN_WCKを計時回路40に出力し、計時回路40は、書き込みクロック信号BIN_WCKに応じて、計時データBIN_Tを、書き込みデータWDATの一部である書き込みデータBIN_WDに更新する。

また、インターフェース回路90は、計時データSUB_T,BCD_T,BIN_Tの少なくとも1つの読み出しを要求するアクセス信号を受信した場合、読み出し対象となる計時データの読み出しを要求する不図示の読み出し要求信号を発生し、リードバッファー70に出力する。そして、インターフェース回路90は、リードバッファー70が取得して保持した読み出し対象の計時データである読み出しデータRDATを取得し、読み出しデータRDATをシリアルデータ信号SDAに変換して端子P7を介してホストデバイス6に送信する。

また、インターフェース回路90は、時刻データTSTMPの読み出しを要求するアクセス信号を受信した場合、イベント時刻レジスター80が保持する時刻データTSTMPに含まれる計時データSUB_T,BCD_T,BIN_Tのうち読み出し対象となる計時データを取得し、当該計時データをシリアルデータ信号SDAに変換して端子P7を介してホストデバイス6に送信する。

なお、本実施形態では、タイムスタンプ機能が有効の場合に、インターフェース回路90がタイムスタンプ機能を無効にすることを指示するアクセス信号を受信した場合、インターフェース回路90は、タイムスタンプ機能を無効にするための不図示の制御信号をイベント時刻レジスター80に出力する。また、タイムスタンプ機能が無効の場合に、インターフェース回路90がタイムスタンプ機能を有効にすることを指示するアクセス信号を受信した場合、インターフェース回路90は、タイムスタンプ機能を有効にするための不図示の制御信号をイベント時刻レジスター80に出力する。

また、インターフェース回路90は、記憶部100に対するデータの書き込みや読み出しを要求するアクセス信号を受信した場合、記憶部100に対するデータの書き込みや読み出しを行う。特に、本実施形態では、インターフェース回路90は、ホストデバイス6から補正データTDを受信して記憶部100に書き込む。また、インターフェース回路90は、ホストデバイス6から補正期間設定データPNを受信して記憶部100に書き込んでもよい。これにより、ホストデバイス6は、リアルタイムクロック回路3の環境変化や計時変化に応じて、補正期間設定データPNを適宜最適な値に変更することができる。同様に、インターフェース回路90は、ホストデバイス6から選択データSELを受信して記憶部100に書き込んでもよい。

記憶部100は、各種のデータを記憶する回路である。本実施形態では、記憶部100は、不図示の不揮発性メモリーとレジスターとを備えている。不揮発性メモリーには、各種データが記憶されており、電源電圧VLOGICが0Vから上昇して所定の電圧値に達すると、不揮発性メモリーに記憶されている各種データはレジスターに転送される。そして、レジスターに転送された各種データが各回路に出力される。

例えば、記憶部100の不揮発性メモリーには、選択データSELや補正期間設定データPNの初期値が記憶されており、レジスターに転送された選択データSELは第2分周回路30に出力され、レジスターに転送された補正期間設定データPNは論理回路50及び割込発生回路110に出力される。その後、選択データSELや補正期間設定データPNは、ホストデバイス6からインターフェース回路90を介して記憶部100のレジスターに書き込まれることによって更新されてもよい。なお、選択データSELや補正期間設定データPNを変更する必要がなければ、選択データSELや補正期間設定データPNは初期値のまま更新されなくてもよい。また、補正データTDは、ホストデバイス6からインターフェース回路90を介して記憶部100のレジスターに書き込まれ、論理回路50に出力される。

割込発生回路110は、基準信号REFと補正期間設定データPNとに基づいて割込み信号IRQを発生し、割込み信号IRQを、リアルタイムクロック回路3の端子P8を介してホストデバイス6に出力する。具体的には、補正期間設定データPNの値をnとすると、割込発生回路110は、基準信号REFの電圧レベルが遷移する所定のタイミングがn+1回発生すると割込み信号IRQを発生する。例えば、基準信号REFの電圧レベルが遷移する所定のタイミングは、基準信号REFがローレベルからハイレベルに遷移するタイミングであってもよいし、基準信号REFがハイレベルからローレベルに遷移するタイミングであってもよい。ホストデバイス6は、割込み信号IRQを受けると、割込み処理を行って時刻データTSTMPに含まれる2つの計時データを読み出し、当該2つの計時データに基づいて補正データTDを生成する。ホストデバイス6が読み出す2つの計時データは、例えば、基準信号REFの電圧レベルが1回目とn+1回目に遷移したタイミングでイベント時刻レジスター80に保持された2つの計時データである。ホストデバイス6は、当該2つの計時データにそれぞれ含まれる計時データSUB_Tの差分により、基準信号REFのn周期の間隔での計時データSUB_Tの変化量を算出し、補正データTDを生成する。

なお、計時データSUB_Tは「第1計時データ」の一例であり、計時データBCD_T又は計時データBIN_Tは「第2計時データ」の一例である。

1-1-2.計時回路の構成

図2は、計時回路40の構成例を示す図である。図2に示すように、計時回路40は、カウンター41~47を備える。

カウンター41は、秒カウンターであり、第3クロック信号CK3に同期してカウント動作を行うことにより、秒単位の時刻を表すカウント値を生成する。例えば、カウンター41は、60進BCD(Binary Coded Decimal)カウンターであり、第3クロック信号CK3のパルスに同期して、十進数の0~59を表すBCDカウント値を順次生成する。カウント値が十進数の59を表す値に等しくなると、カウンター41は、第3クロック信号CK3の次のパルスに同期して、カウント値を0にリセットすると共に、キャリー信号CA1を出力する。カウンター41によって生成されるカウント値は、秒単位の時刻を表す計時データBCD_T1として用いられる。すなわち、カウンター41は、1秒単位で計時データBCD_T1を更新する。また、カウンター41は、書き込みクロック信号BCD_WCKのパルスに同期して、カウント値、すなわち計時データBCD_T1を書き込みデータBCD_WDのビット0~7の1バイトの値に更新する。

カウンター42は、分カウンターであり、キャリー信号CA1に同期してカウント動作を行うことにより、分単位の時刻を表すカウント値を生成する。例えば、カウンター42は、60進BCDカウンターであり、キャリー信号CA1のパルスに同期して、十進数の0~59を表すBCDカウント値を順次生成する。カウント値が十進数の59を表す値に等しくなると、カウンター42は、キャリー信号CA1の次のパルスに同期して、カウント値を0にリセットすると共に、キャリー信号CA2を出力する。カウンター42によって生成されるカウント値は、分単位の時刻を表す計時データBCD_T2として用いられる。すなわち、カウンター42は、分単位で計時データBCD_T2を更新する。また、カウンター42は、書き込みクロック信号BCD_WCKのパルスに同期して、カウント値、すなわち計時データBCD_T2を書き込みデータBCD_WDのビット8~15の1バイトの値に更新する。

カウンター43は、時カウンターであり、キャリー信号CA2に同期してカウント動作を行うことにより、時単位の時刻を表すカウント値を生成する。例えば、カウンター43は、24進BCDカウンターであり、キャリー信号CA2のパルスに同期して、十進数の0~23を表すBCDカウント値を順次生成する。カウント値が十進数の23を表す値に等しくなると、カウンター43は、キャリー信号CA2の次のパルスに同期して、カウント値を0にリセットすると共に、キャリー信号CA3を出力する。カウンター43によって生成されるカウント値は、時単位の時刻を表す計時データBCD_T3として用いられる。すなわち、カウンター43は、時単位で計時データBCD_T3を更新する。また、カウンター43は、書き込みクロック信号BCD_WCKのパルスに同期して、カウント値、すなわち計時データBCD_T3を書き込みデータBCD_WDのビット16~23の1バイトの値に更新する。

カウンター44は、日カウンターであり、キャリー信号CA3に同期してカウント動作を行うことにより、日単位の時刻を表すカウント値を生成する。例えば、カウンター44は、10進BCDカウンターであり、キャリー信号CA3のパルスに同期して、十進数の1~31を表すBCDカウント値を順次生成する。ただし、月によっては、月の最後の日のカウント値を28又は30とする必要があり、うるう年の2月の場合には、月の最後の日のカウント値を29とする必要がある。そこで、カウンター44は、日単位の時刻を表

すカウント値を、月単位の時刻を表すカウント値及び年単位の時刻を表すカウント値に基づいて設定されたカウント上限値と比較する。カウント値がカウント上限値に等しくなると、カウンター44は、キャリー信号CA3の次のパルスに同期して、カウント値を1にリセットすると共に、キャリー信号CA4を出力する。カウンター44によって生成されるカウント値は、日単位の時刻を表す計時データBCD_T4として用いられる。すなわち、カウンター44は、日単位で計時データBCD_T4を更新する。また、カウンター44は、書き込みクロック信号BCD_WCKのパルスに同期して、カウント値、すなわち計時データBCD_T4を書き込みデータBCD_WDのビット24~31の1バイトの値に更新する。

カウンター45は、月カウンターであり、キャリー信号CA4に同期してカウント動作を行うことにより、月単位の時刻を表すカウント値を生成する。例えば、カウンター45は、12進BCDカウンターで構成され、キャリー信号CA4のパルスに同期して、十進数の1~12を表すBCDカウント値を順次生成する。カウント値が十進数の12を表す値に等しくなると、カウンター45は、キャリー信号CA4の次のパルスに同期して、カウント値を1にリセットすると共に、キャリー信号CA5を出力する。カウンター45によって生成されるカウント値は、月単位の時刻を表す計時データBCD_T5として用いられる。すなわち、カウンター45は、月単位で計時データBCD_T5を更新する。また、カウンター45は、書き込みクロック信号BCD_WCKのパルスに同期して、カウント値、すなわち計時データBCD_T5を書き込みデータBCD_WDのビット32~39の1バイトの値に更新する。

カウンター46は、年カウンターであり、キャリー信号CA5に同期してカウント動作を行うことにより、年単位の時刻を表すカウント値を生成する。例えば、カウンター46は、10進BCDカウンターで構成され、キャリー信号CA5のパルスに同期して、西暦年号の場合に、十進数の2020、2021、2022・・・の下2桁を表すBCDカウント値を順次生成する。カウンター46によって生成されるカウント値は、年単位の時刻を表す計時データBCD_T6として用いられる。すなわち、カウンター46は、年単位で計時データBCD_T6を更新する。また、カウンター46は、書き込みクロック信号BCD_WCKのパルスに同期して、カウント値、すなわち計時データBCD_T6を書き込みデータBCD_WDのビット40~47の1バイトの値に更新する。

前述の計時データBCD_Tは、年、月、日、時、分及び秒のカウント値である計時データBCD_T6~BCD_T1によって構成される。

カウンター47は、秒カウンターであり、第3クロック信号CK3に同期してカウント動作を行うことにより、秒単位の時刻を表すカウント値を生成する。例えば、カウンター41は、2進カウンターであり、第3クロック信号CK3のパルスに同期して増加する2進数の値を順次生成する。カウンター47によって生成されるカウント値は、年、月、日、時、分及び秒を秒単位の時刻として表す計時データBIN_Tとして用いられる。すなわち、カウンター47は、1秒単位で計時データBIN_Tを更新する。また、カウンター47は、書き込みクロック信号BIN_WCKのパルスに同期して、カウント値、すなわち計時データBIN_Tを書き込みデータBIN_WDの値に更新する。

このように、本実施形態では、計時回路40は、年、月、日、時、分及び秒をそれぞれBCDカウント値で表す計時データBCD_Tを生成するとともに、年、月、日、時、分及び秒を秒単位の2進数の値で表す計時データBIN_Tも生成する。ホストデバイス6は、システムの用途に応じて、リアルタイムクロックモジュール1から計時データBCD_T,BIN_Tの一方又は両方に対して読み出しや書き込みを行い、システムに必要な処理を行うことができる。

1-1-3.第1分周回路の構成

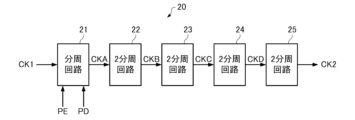

図3は、第1分周回路20の構成例を示す図である。図3に示すように、第1分周回路20は、分周回路21及び2分周回路22~25を備える。

分周回路21は、基本的には第1クロック信号CK1を2分周することによってクロック信号CKAを生成する。2分周回路22は、クロック信号CKAを2分周することによってクロック信号CKBを生成する。2分周回路23は、クロック信号CKBを2分周することによってクロック信号CKCを生成する。2分周回路24は、クロック信号CKCを2分周することによってクロック信号CKDを生成する。2分周回路25は、クロック信号CKDを2分周することによって第2クロック信号CK2を生成する。

このように構成されている第1分周回路20は、バイナリーカウンターとして動作し、第1クロック信号CK1を32分周した第2クロック信号CK2を生成する。例えば、第1クロック信号CK1の周波数が32.764kHzである場合、第2クロック信号CK2の周波数は1.024kHzとなる。また、第1クロック信号CK1の周波数が32kHzである場合、第2クロック信号CK2の周波数は1kHzとなる。

しかしながら、例えば、環境温度が25℃のときに第1クロック信号CK1の周波数が目標周波数となるように調整されている場合、高温や低温の環境では、振動子2の温度特性によって第1クロック信号CK1の周波数の目標周波数に対する誤差が大きくなる。また、振動子2の経時変化によっても第1クロック信号CK1の周波数の目標周波数に対する誤差が大きくなる。

そこで、本実施形態では、図3に示すように、論理回路50から出力される制御信号PE,PDが分周回路21に入力され、分周回路21に対して制御信号PE,PDに応じた緩急処理が行われる。本実施形態では、制御信号PE,PDは、ともにローレベルか一方のみがハイレベルとなる信号であり、分周回路21は、制御信号PE,PDがともにローレベルのときは第1クロック信号CK1を2分周したクロック信号CKAを出力する。また、分周回路21は、制御信号PEがハイレベルのときは、第1クロック信号CK1を2分周せずにそのままクロック信号CKAとして出力する。また、分周回路21は、制御信号PDがハイレベルのときは、第1クロック信号CK1を4分周したクロック信号CKAを出力する。このように、分周回路21に対して緩急処理が行われることにより、第2クロック信号CK2の平均周波数が所望の周波数に近づくことになる。

1-1-4.第2分周回路の構成

前述の通り、第2分周回路30は、選択データSELの値に応じて、バイナリーカウンター又はBCDカウンターとして動作する。

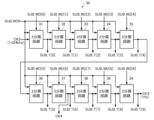

図4は、選択データSELが0である場合の第2分周回路30の構成例を示す図である。図4に示すように、第2分周回路30は、2分周回路31~3Aを備える。選択データSELが0である場合、第2分周回路30に入力される第2クロック信号CK2の周波数は1.024kHzである。

2分周回路31は、1.024kHzの第2クロック信号CK2を2分周して512Hzのクロック信号を生成する。この512Hzのクロック信号は、計時データSUB_Tのビット0として用いられる。また、2分周回路31は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット0の値を書き込みデータSUB_WDのビット0の値に更新する。

2分周回路32は、2分周回路31が生成した512Hzのクロック信号を2分周して256Hzのクロック信号を生成する。この256Hzのクロック信号は、計時データSUB_Tのビット1として用いられる。また、2分周回路32は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット1の値を書き込みデータSUB_WDのビット1の値に更新する。

2分周回路33は、2分周回路32が生成した256Hzのクロック信号を2分周して128Hzのクロック信号を生成する。この128Hzのクロック信号は、計時データSUB_Tのビット2として用いられる。また、2分周回路33は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット2の値を書き込みデータSUB_WDのビット2の値に更新する。

2分周回路34は、2分周回路33が生成した128Hzのクロック信号を2分周して64Hzのクロック信号を生成する。この64Hzのクロック信号は、計時データSUB_Tのビット3として用いられる。また、2分周回路34は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット3の値を書き込みデータSUB_WDのビット3の値に更新する。

2分周回路35は、2分周回路34が生成した64Hzのクロック信号を2分周して32Hzのクロック信号を生成する。この32Hzのクロック信号は、計時データSUB_Tのビット4として用いられる。また、2分周回路35は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット4の値を書き込みデータSUB_WDのビット4の値に更新する。

2分周回路36は、2分周回路35が生成した32Hzのクロック信号を2分周して16Hzのクロック信号を生成する。この16Hzのクロック信号は、計時データSUB_Tのビット5として用いられる。また、2分周回路36は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット5の値を書き込みデータSUB_WDのビット5の値に更新する。

2分周回路37は、2分周回路36が生成した16Hzのクロック信号を2分周して8Hzのクロック信号を生成する。この8Hzのクロック信号は、計時データSUB_Tのビット6として用いられるとともに、第4クロック信号CK4として用いられる。また、2分周回路37は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット6の値を書き込みデータSUB_WDのビット6の値に更新する。

2分周回路38は、2分周回路37が生成した8Hzのクロック信号を2分周して4Hzのクロック信号を生成する。この4Hzのクロック信号は、計時データSUB_Tのビット7として用いられる。また、2分周回路38は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット7の値を書き込みデータSUB_WDのビット7の値に更新する。

2分周回路39は、2分周回路38が生成した4Hzのクロック信号を2分周して2Hzのクロック信号を生成する。この2Hzのクロック信号は、計時データSUB_Tのビット8として用いられる。また、2分周回路39は、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット8の値を書き込みデータSUB_WDのビット8の値に更新する。

2分周回路3Aは、2分周回路39が生成した2Hzのクロック信号を2分周して1Hzの第3クロック信号CK3を生成する。第3クロック信号CK3は、計時データSUB

_Tのビット9として用いられる。また、2分周回路3Aは、書き込みクロック信号SUB_WCKのパルスに同期して、計時データSUB_Tのビット9の値を書き込みデータSUB_WDのビット9の値に更新する。

このように、選択データSELが0である場合、第2分周回路30は、1.024kHzの第2クロック信号CK2を1024分周して1Hzの第3クロック信号CK3を生成するとともに、1.024kHzの第2クロック信号CK2を128分周して8Hzの第4クロック信号CK4を生成する。

図5は、選択データSELが1である場合の第2分周回路30の構成例を示す図である。図5に示すように、第2分周回路30は、カウンター3B,3C,3Dを備える。選択データSELが0である場合、第2分周回路30に入力される第2クロック信号CK2の周波数は1kHzである。

カウンター3Bは、1kHzの第2クロック信号CK2に同期してカウント動作を行うことにより、1/1000秒単位の時刻を表すカウント値を生成する。例えば、カウンター3Bは、10進BCDカウンターであり、第2クロック信号CK2のパルスに同期して、十進数の0~9を表すBCDカウント値を順次生成する。カウント値が十進数の9を表す値に等しくなると、カウンター3Bは、第2クロック信号CK2の次のパルスに同期して、カウント値を0にリセットすると共に、100Hzのキャリー信号CA11を出力する。カウンター3Bによって生成されるカウント値は、1/1000秒単位の時刻を表す計時データSUB_T1として用いられる。すなわち、カウンター3Bは、1/1000秒単位で計時データSUB_T1を更新する。また、カウンター3Bは、書き込みクロック信号SUB_WCKのパルスに同期して、カウント値、すなわち計時データSUB_T1を書き込みデータSUB_WDのビット0~7の1バイトの値に更新する。

カウンター3Cは、100Hzのキャリー信号CA11に同期してカウント動作を行うことにより、1/100秒単位の時刻を表すカウント値を生成する。例えば、カウンター3Cは、10進BCDカウンターであり、キャリー信号CA11のパルスに同期して、十進数の0~9を表すBCDカウント値を順次生成する。カウント値が十進数の9を表す値に等しくなると、カウンター3Cは、キャリー信号CA11の次のパルスに同期して、カウント値を0にリセットすると共に、10Hzのキャリー信号CA12を出力する。カウンター3Cによって生成されるカウント値は、1/100秒単位の時刻を表す計時データSUB_T2として用いられる。すなわち、カウンター3Cは、1/100秒単位で計時データSUB_T2を更新する。また、10Hzのキャリー信号CA12は、第4クロック信号CK4として用いられる。また、カウンター3Cは、書き込みクロック信号SUB_WCKのパルスに同期して、カウント値、すなわち計時データSUB_T2を書き込みデータSUB_WDのビット8~15の1バイトの値に更新する。

カウンター3Dは、10Hzのキャリー信号CA12に同期してカウント動作を行うことにより、1/10秒単位の時刻を表すカウント値を生成する。例えば、カウンター3Dは、10進BCDカウンターであり、キャリー信号CA12のパルスに同期して、十進数の0~9を表すBCDカウント値を順次生成する。カウント値が十進数の9を表す値に等しくなると、カウンター3Dは、キャリー信号CA12の次のパルスに同期して、カウント値を0にリセットすると共に、1Hzの第3クロック信号CK3を出力する。カウンター3Dによって生成されるカウント値は、1/10秒単位の時刻を表す計時データSUB_T3として用いられる。すなわち、カウンター3Dは、1/10秒単位で計時データSUB_T3を更新する。また、カウンター3Dは、書き込みクロック信号SUB_WCKのパルスに同期して、カウント値、すなわち計時データSUB_T3を書き込みデータSUB_WDのビット16~23の1バイトの値に更新する。

このように、選択データSELが1である場合、第2分周回路30は、1kHzの第2クロック信号CK2を1000分周して1Hzの第3クロック信号CK3を生成するとともに、1kHzの第2クロック信号CK2を100分周して10Hzの第4クロック信号CK4を生成する。また、前述の計時データSUB_Tは、1/10秒、1/100秒及び1/1000秒のカウント値である計時データSUB_T3,SUB_T2,SUB_T1によって構成される。

1-1-5.論理回路による緩急処理

前述の通り、選択データSELの値に応じて、論理回路50による緩急処理が行われる補正期間の長さが異なる。

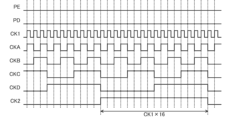

図6は、選択データSELが0の場合の補正期間と緩急処理のタイミングとの関係の一例を示す図である。図6に示すように、選択データSELが0の場合は、1回の補正期間は、8Hzの第4クロック信号CK4の1周期の時間である0.125秒の256倍に相当する32秒である。また、緩急処理のタイミングは、第4クロック信号CK4の1周期毎に、すなわち0.125秒間隔で到来する。すなわち、1回の補正期間において、最大256回の緩急処理が可能である。

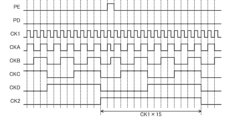

図7は、選択データSELが1の場合の補正期間と緩急処理のタイミングとの関係の一例を示す図である。図7に示すように、選択データSELが1の場合は、1回の補正期間は、10Hzの第4クロック信号CK4の1周期の時間である0.1秒の256倍に相当する25.6秒である。また、緩急処理のタイミングは、第4クロック信号CK4の1周期毎に、すなわち0.1秒間隔で到来する。すなわち、1回の補正期間において、最大256回の緩急処理が可能である。

なお、図6及び図7では、1つの補正期間のみが図示されているが、実際には、1つの補正期間が終了する毎に次の補正期間が開始する。すなわち、図6又は図7に示す補正期間が間隔を空けずに繰り返される。

補正期間において各タイミングで行われる緩急処理は、制御信号PE,PDによって制御される。図8、図9及び図10は、制御信号PE,PDに応じて行われる緩急処理について説明するための図である。図8は、緩急処理のタイミングで制御信号PE,PDがともにローレベルのときのタイミングチャート図である。図9は、緩急処理のタイミングで制御信号PEがハイレベル、制御信号PDがローレベルのときのタイミングチャート図である。図10は、緩急処理のタイミングで制御信号PEがローレベル、制御信号PDがハイレベルのときのタイミングチャート図である。

図8に示すように、緩急処理のタイミングで制御信号PE,PDがともにローレベルのときは、クロック信号CKAは第1クロック信号CK1を2分周した信号のままである。その結果、当該タイミングの直後の第2クロック信号CK2の半周期における第1クロック信号CK1のパルス数は16のままである。すなわち、第2クロック信号CK2の1周期における第1クロック信号CK1のパルス数は32のまま変わらない。

これに対して、図9に示すように、緩急処理のタイミングで制御信号PEがハイレベル、制御信号PDがローレベルのときは、クロック信号CKAは第1クロック信号CK1と一致する。その結果、当該タイミングの直後の第2クロック信号CK2の半周期における第1クロック信号CK1のパルス数は15となる。すなわち、緩急処理のタイミングで制御信号PEがハイレベル、制御信号PDがローレベルとなる場合、その直後の第2クロック信号CK2の1周期だけ第1クロック信号CK1のパルス数が31となり、第2クロッ

ク信号CK2の当該周期は他の各周期よりも第1クロック信号CK1の1周期分だけ短くなる。

また、図10に示すように、緩急処理のタイミングで制御信号PEがローレベル、制御信号PDがハイレベルのときは、クロック信号CKAは第1クロック信号CK1を4分周した信号となる。その結果、当該タイミングの直後の第2クロック信号CK2の半周期における第1クロック信号CK1のパルス数は17となる。すなわち、緩急処理のタイミングで制御信号PEがローレベル、制御信号PDがハイレベルとなる場合、その直後の第2クロック信号CK2の1周期だけ第1クロック信号CK1のパルス数が33となり、第2クロック信号CK2の当該周期は他の各周期よりも第1クロック信号CK1の1周期分だけ長くなる。

補正データTDを9ビットのデータとして-255以上+255以下の511個の整数値を取り得るものとしたとき、論理回路50は、補正データTDの値に応じて、1回の補正期間における256回の緩急処理のタイミングのうちの0~255回のタイミングで緩急処理を行う。

例えば、基準信号REFでカウントした32秒間における第1クロック信号CK1のパルス数が32×32768=1048576である場合、第1クロック信号CK1の周波数が目標周波数の32.768kHzと一致しているため、補正データTDの値は0となる。この場合、論理回路50は、各補正期間において制御信号PE,PDをローレベルに固定することにより、常に第2クロック信号CK2の1周期の長さが第1クロック信号CK1の32周期の長さと等しくなるようにする。これにより、1.024kHzの第2クロック信号CK2の32768周期における第1クロック信号CK1のパルス数は1048576となり、第2クロック信号CK2の32768周期が基準信号REFでカウントした32秒と一致する。

これに対して、基準信号REFでカウントした32秒間における第1クロック信号CK1のパルス数が1048576-255=1048321である場合、第1クロック信号CK1の周波数が目標周波数の32.768kHzよりも低く、補正データTDの値は+255となる。この場合、論理回路50は、各補正期間において256回の緩急処理のタイミングのうち255回のタイミングで制御信号PEをハイレベルにすることにより、255回だけ第2クロック信号CK2の1周期の長さが第1クロック信号CK1の31周期の長さと等しくなるようにする。これにより、1.024kHzの第2クロック信号CK2の32768周期における第1クロック信号CK1のパルス数は1048576-255=1048321となり、第2クロック信号CK2の32768周期が基準信号REFでカウントした32秒と一致する。

また、基準信号REFでカウントした32秒間における第1クロック信号CK1のパルス数が1048576+255=1048831である場合、第1クロック信号CK1の周波数が目標周波数の32.768kHzよりも高く、補正データTDの値は-255となる。この場合、論理回路50は、各補正期間において256回の緩急処理のタイミングのうち255回のタイミングで制御信号PDをハイレベルにすることにより、255回だけ第2クロック信号CK2の1周期の長さが第1クロック信号CK1の33周期の長さと等しくなるようにする。これにより、1.024kHzの第2クロック信号CK2の32768周期における第1クロック信号CK1のパルス数は1048576+255=1048831となり、第2クロック信号CK2の32768周期が基準信号REFでカウントした32秒と一致する。

このように、本実施形態のリアルタイムクロック回路3では、論理回路50は、第3ク

ロック信号CK3の周期である1秒よりも長い間隔に相当する補正期間において第1分周回路20に対して緩急処理を行う。これにより、リアルタイムクロック回路3は、第2クロック信号CK2を高い分解能で補正することができる。例えば、第1クロック信号CK1の目標周波数が32.768kHzであり、補正期間が32秒である場合は、分解能は1/32.768kH/32=0.954ppmである。また、第1クロック信号CK1の目標周波数が32kHzであり、補正期間が25.6秒である場合は、分解能は1/32kH/25.6=1.22ppmである。

また、本実施形態では、論理回路50が、補正期間において、第2クロック信号CK2の周期よりも長い時間間隔で第1分周回路20に対して緩急処理を行う。すなわち、論理回路50が時間的に分散して緩急処理を行うことにより、第2クロック信号CK2の周波数変動量のばらつきを小さくすることができる。

1-1-6.リアルタイムクロック回路の補正方法

図11は、第1実施形態のリアルタイムクロック回路3の補正方法の手順の一例を示す図である。

図11に示すように、まず、ホストデバイス6がリアルタイムクロック回路3のタイムスタンプ機能を有効にする(工程S1)。

次に、ホストデバイス6がリアルタイムクロック回路3に基準信号REFを送信する(工程S2)。

次に、リアルタイムクロック回路3が、基準信号REFの電圧レベルが遷移する所定のタイミングで、イベント時刻レジスター80に計時データを保持する(工程S3)。工程S3において保持される計時データは、計時データSUB_Tを含み、さらに計時データBCD_T又は計時データBIN_Tを含む。

そして、リアルタイムクロック回路3が基準信号REFをn+1回受信するまで(工程S4のN)、工程S2及び工程S3が繰り返される。整数nは、前述の補正期間設定データPNの値である。例えば、nが32であり、基準信号REFの周期が1秒であれば、リアルタイムクロック回路3が基準信号REFを33回受信するまで、すなわち、基準信号REFの1回目の受信から32秒が経過するまで工程S2及び工程S3が繰り返される。

リアルタイムクロック回路3が基準信号REFをn+1回受信すると(工程S4のY)、ホストデバイス6がリアルタイムクロック回路3のタイムスタンプ機能を無効にする(工程S5)。

次に、リアルタイムクロック回路3が、ホストデバイス6に割込み信号IRQを送信する(工程S6)。

次に、ホストデバイス6が、割込み信号IRQを受信し、リアルタイムクロック回路3からイベント時刻レジスター80に保持された1番目とn+1番目の計時データを読み出す(工程S7)。

次に、ホストデバイス6が、n+1番目の計時データと1番目の計時データとの差分ΔTを計算する(工程S8)。例えば、nが32であり、基準信号REFの周期が1秒であれば、差分ΔTは計時データの32秒間の増加量に相当する。

そして、差分ΔTの期待値に対する誤差が1秒以内である場合は(工程S9のY)、ホ

ストデバイス6が、1秒未満の変化量ΔSubCntに基づき補正データTDを生成し、生成した補正データTDをリアルタイムクロック回路3の記憶部100に書き込む(工程S10)。変化量ΔSubCntは、n+1番目の計時データSUB_Tと1番目の計時データSUB_Tとの差分である。例えば、nが32であり、基準信号REFの周期が1秒であれば、差分ΔTの期待値は32秒であるので、差分ΔTが31秒以上33秒以下である場合に工程S10が行われる。また、工程S10において、ホストデバイス6は、変化量ΔSubCntが-255~+255の範囲の値である前提で、補正データTDの値を200h-ΔSubCntによって計算する。

次に、リアルタイムクロック回路3が、工程S10で記憶部100に書き込まれた補正データTDを用いて第1分周回路20に対して緩急処理を行う(工程S11)。以降、リアルタイムクロック回路3は、補正データTDが更新されるまで、各補正期間において当該補正データTDを用いて時間的に分散して緩急処理を行う。

一方、差分ΔTが1秒よりも大きい場合は(工程S9のN)、ホストデバイス6が、現在時刻のデータをリアルタイムクロック回路3のライトバッファー60に書き込む(工程S12)。例えば、ホストデバイス6は、年、月、日、時、分及び秒の時刻データ及び年、月、日、時、分及び秒を秒単位で表した時刻データをライトバッファー60に書き込む。

次に、リアルタイムクロック回路3が、計時回路40の計時データBCD_T,BIN_Tをライトバッファー60が保持する現在時刻のデータに更新する(工程S13)。

そして、工程S11又は工程S13の後、所定のインターバル時間が経過する毎に(工程S14のY)、工程S1~工程S13が繰り返し行われる。

このように、本実施形態では、論理回路50は、例えば、32秒間の1秒未満の変化量ΔSubCntに基づいて生成された補正データTDに基づいて、同じく32秒間の補正期間における第2クロック信号CK2の周波数が平均して1.024kHzとなるように緩急処理を行う。あるいは、論理回路50は、25.6秒間の1秒未満の変化量ΔSubCntに基づいて生成された補正データTDに基づいて、同じく25.6秒である補正期間における第2クロック信号CK2の周波数が平均して1kHzとなるように緩急処理を行う。例えば、変化量ΔSubCntが-255~+255の範囲とすると、第1クロック信号CK1の目標周波数が32.768kHzであり、補正期間が32秒である場合は、前述の通り、緩急処理の分解能が約0.954ppmであるので、緩急幅は-243.19ppm~+243.19ppmである。また、第1クロック信号CK1の目標周波数が32kHzであり、補正期間が25.6秒である場合は、緩急処理の分解能が約1.22ppmであるので、緩急幅は-311.28ppm~+311.28ppmである。したがって、環境温度の変化や経時変化による第1クロック信号CK1の最大周波数変動量を数ppm~数十ppmであるとすると、リアルタイムクロック回路3は十分な幅で緩急処理を行うことができる。

また、1秒未満の変化量ΔSubCntを計算するための期間である基準信号REFに同期した間隔と補正期間の長さを一致させることにより、補正データTDの値を変化量ΔSubCntの符号を反転した値とすればよく、ホストデバイス6による補正データTDの計算負荷を低減させることができる。

1-1-7.作用効果

以上に説明したように、第1実施形態では、リアルタイムクロック回路3において、論理回路50が、基準信号REFに同期した間隔での1秒よりも短い時間の計時データSU

B_Tの変化量に基づいて生成された補正データTDを用いて、第2クロック信号CK2を生成する第1分周回路20に対して緩急処理を行う。したがって、1秒以上の任意の短時間で生成された補正データTDを用いて、第2クロック信号CK2が補正される。そして、第2分周回路30が第2クロック信号CK2を分周して第3クロック信号CK3を生成し、計時回路40が第3クロック信号CK3に基づいて1秒以上の時間の計時データBCD_T,BIN_Tを生成するので、計時データBCD_T,BIN_Tが短時間で補正される。また、リアルタイムクロック回路3では、基準信号REFに同期した間隔での計時データSUB_Tの変化量に基づいて補正データTDが生成される。そのため、リアルタイムクロック回路3が第3クロック信号CK3をホストデバイス6に出力し、ホストデバイス6が第3クロック信号CK3の周波数を計測して補正データTDを作成する必要がない。したがって、第1実施形態によれば、リアルタイムクロック回路3は、短時間で簡易に計時データの補正データTDを取得することができる。さらに、第1実施形態では、リアルタイムクロック回路3において、補正データTDを用いた緩急処理が行われる期間の長さが、補正データTDを生成するために計時データSUB_Tの変化量が算出される間隔と一致するので、計時データSUB_Tの変化量の符号を反転した値を補正データTDの値とすることができる。したがって、第1実施形態によれば、ホストデバイス6による補正データTDの生成が容易である。以上より、第1実施形態によれば、優れたユーザー利便性を実現することができる。

また、第1実施形態では、リアルタイムクロック回路3において、補正データTDを生成するために計時データSUB_Tの変化量が算出される間隔が、第3クロック信号CK3の周期である1秒よりも長いので、論理回路50は高い分解能で第2クロック信号CK2を補正することができる。また、計時データSUB_Tの誤差が平均化されるため、第1クロック信号CK1のジッター等の影響も低減される。さらに、リアルタイムクロック回路3において、論理回路50が、第2クロック信号CK2の周期よりも長い時間間隔で時間的に分散して第1分周回路20に対して緩急処理を行うので、第2クロック信号CK2の周波数変動量のばらつきを小さくすることができる。例えば、前述の通り、緩急処理による補正の分解能を0.954ppmとすることにより、計時データBCD_T,BIN_Tの1秒の誤差を1ppm以下にすることも可能である。特に、論理回路50が、第1分周回路20に含まれる先頭の分周回路21に対して緩急処理を行うことにより、1秒未満の計時データSUB_Tの誤差も小さくすることができる。

また、第1実施形態では、リアルタイムクロック回路3において、選択データSELの値に応じて第2分周回路30の動作が切り替わることにより、第4クロック信号CK4の周波数が8Hz又は10Hzに切り替わる。これに対して、選択データSELの値によらず、ホストデバイス6が補正データTDを作成するための期間や、補正期間と基準信号REFの周期との比を共通にすることによって、論理回路50による緩急処理の論理が共通化される。したがって、第1実施形態によれば、リアルタイムクロック回路3において、第2分周回路30の動作が切り替わっても緩急処理の制御に対する影響が小さい。

また、第1実施形態では、ホストデバイス6は、リアルタイムクロック回路3のタイムスタンプ機能によってイベント時刻レジスター80に保持された計時データSUB_Tに基づいて、補正データTDを生成する。したがって、第1実施形態によれば、イベント時刻レジスター80に保持された計時データSUB_Tの読み出しに要する遅延時間にばらつきがあっても、遅延時間のばらつきによる計時データSUB_Tの誤差が生じないので、ホストデバイス6は正確な補正データTDを生成することができる。また、ホストデバイス6は、リアルタイムクロックモジュール1の動作を停止することなく短時間で補正データTDを生成することができるので、例えば、エージング補正にも適用可能である。特に、発振回路10に対してエージング補正を行った場合には、振動子2の温度特性の影響で、高温や低温の環境では第1クロック信号CK1の周波数誤差が大きくなり、その結果

、1秒の誤差が大きくなるのに対して、第1実施形態では、論理回路50の緩急処理により、振動子2の温度特性による第1クロック信号CK1の周波数誤差を加味して第2クロック信号CK2の周波数が補正されるので、1秒の誤差を小さくすることができる。

また、第1実施形態によれば、ホストデバイス6が補正データTDを生成するので、リアルタイムクロック回路3が補正データTDを生成する必要がなく、リアルタイムクロック回路3のサイズを低減させることができる。

また、第1実施形態では、ホストデバイス6がリアルタイムクロック回路3の記憶部100に補正期間設定データPNを書き込むことができる。しったがって、第1実施形態によれば、ホストデバイス6が補正データTDを生成するために計時データSUB_Tの変化量が算出される間隔、すなわち、補正期間の長さを、補正の精度と補正に要する時間とのトレードオフを考慮して、ユーザーが任意に設定することができる。

1-2.第2実施形態

第1実施形態では、ホストデバイス6が補正データTDを生成するのに対して、第2実施形態では、リアルタイムクロック回路3が補正データTDを生成する。以下、第2実施形態について、第1実施形態と同様の構成要素には同じ符号を付し、第1実施形態と重複する説明は省略または簡略し、主に第1実施形態と異なる内容について説明する。

図12は、第2実施形態のリアルタイムクロックモジュール1の機能ブロック図である。図12において、図1と同様の構成要素には同じ符号が付されている。

図12に示すように、第2実施形態のリアルタイムクロックモジュール1では、リアルタイムクロック回路3は、図1と同様の構成要素を含み、さらに補正データ生成回路150を備える。

補正データ生成回路150は、イベント時刻レジスター80が保持した計時データに基づいて補正データTDを生成する。補正データ生成回路150は、時刻データTSTMPに含まれる2つの計時データを取得し、当該2つの計時データに基づいて補正データTDを生成する。具体的には、補正データ生成回路150は、基準信号REFの電圧レベルが遷移する所定のタイミングが発生した回数をカウントし、基準信号REFの電圧レベルが1回目とn+1回目に遷移したタイミングでイベント時刻レジスター80に保持された2つの計時データを取得する。例えば、基準信号REFの電圧レベルが遷移する所定のタイミングは、基準信号REFがローレベルからハイレベルに遷移するタイミングであってもよいし、基準信号REFがハイレベルからローレベルに遷移するタイミングであってもよい。また、整数nは、前述の補正期間設定データPNの値である。そして、補正データ生成回路150は、取得した2つの計時データにそれぞれ含まれる計時データSUB_Tの差分により、基準信号REFのn周期の間隔での計時データSUB_Tの変化量を算出し、補正データTDを生成する。このように、補正データTDは、基準信号REFに同期した間隔での計時データSUB_Tの変化量に基づいて生成されたデータである。

論理回路50は、補正データ生成回路150が生成した補正データTDを用いて、第1実施形態と同様に、補正期間において第1分周回路20に対して緩急処理を行う。

また、補正データ生成回路150は、基準信号REFのn周期の間隔での計時データSUB_Tの変化量が所定値よりも大きい場合は、割込発生回路110に割込み制御信号IREを出力する。所定値は、例えば1秒である。割込発生回路110は、割込み制御信号IREを受けると割込み信号IRQを発生し、割込み信号IRQを、リアルタイムクロック回路3の端子P8を介してホストデバイス6に出力する。ホストデバイス6は、割込み

信号IRQを受けると、割込み処理を行って現在時刻のデータをリアルタイムクロック回路3のライトバッファー60に書き込み、計時回路40の計時データBCD_T,BIN_Tを更新する。

第2実施形態のリアルタイムクロックモジュール1のその他の構成は、第1実施形態と同様であるため、その設営を省略する。

図13は、第2実施形態のリアルタイムクロック回路3の補正方法の手順の一例を示す図である。

図13に示すように、まず、ホストデバイス6がリアルタイムクロック回路3のタイムスタンプ機能を有効にする(工程S101)。

次に、ホストデバイス6がリアルタイムクロック回路3に基準信号REFを送信する(工程S102)。

次に、リアルタイムクロック回路3が、基準信号REFの電圧レベルが遷移する所定のタイミングで、イベント時刻レジスター80に計時データを保持する(工程S103)。工程S3において保持される計時データは、計時データSUB_Tを含み、さらに計時データBCD_T又は計時データBIN_Tを含む。

そして、リアルタイムクロック回路3が基準信号REFをn+1回受信するまで(工程S104のN)、工程S102及び工程S103が繰り返される。整数nは、前述の補正期間設定データPNの値である。例えば、nが32であり、基準信号REFの周期が1秒であれば、リアルタイムクロック回路3が基準信号REFを33回受信するまで、すなわち、基準信号REFの1回目の受信から32秒が経過するまで工程S102及び工程S103が繰り返される。

リアルタイムクロック回路3が基準信号REFをn+1回受信すると(工程S104のY)、ホストデバイス6がリアルタイムクロック回路3のタイムスタンプ機能を無効にする(工程S105)。

次に、リアルタイムクロック回路3が、イベント時刻レジスター80に保持されたn+1番目の計時データと1番目の計時データとの差分ΔTを計算する(工程S106)。例えば、nが32であり、基準信号REFの周期が1秒であれば、差分ΔTは計時データの32秒間の増加量に相当する。

そして、差分ΔTの期待値に対する誤差が1秒以内である場合は(工程S107のY)、リアルタイムクロック回路3が、1秒未満の変化量ΔSubCntに基づき補正データTDを生成する(工程S108)。変化量ΔSubCntは、n+1番目の計時データSUB_Tと1番目の計時データSUB_Tとの差分である。例えば、nが32であり、基準信号REFの周期が1秒であれば、差分ΔTの期待値は32秒であるので、差分ΔTが31秒以上33秒以下である場合に工程S108が行われる。また、工程S108において、ホストデバイス6は、変化量ΔSubCntが-255~+255の範囲の値である前提で、補正データTDの値を200h-ΔSubCntによって計算する。

次に、リアルタイムクロック回路3が、工程S108で生成された補正データTDを用いて第1分周回路20に対して緩急処理を行う(工程S109)。以降、リアルタイムクロック回路3は、補正データTDが更新されるまで、各補正期間において当該補正データTDを用いて時間的に分散して緩急処理を行う。

一方、差分ΔTが1秒よりも大きい場合は(工程S107のN)、リアルタイムクロック回路3が、ホストデバイス6に割込み信号IRQを送信する(工程S110)。

次に、ホストデバイス6が、割込み信号IRQを受信し、現在時刻のデータをリアルタイムクロック回路3のライトバッファー60に書き込む(工程S111)。例えば、ホストデバイス6は、年、月、日、時、分及び秒の時刻データ及び年、月、日、時、分及び秒を秒単位で表した時刻データをライトバッファー60に書き込む。

次に、リアルタイムクロック回路3が、計時回路40の計時データBCD_T,BIN_Tをライトバッファー60が保持する現在時刻のデータに更新する(工程S112)。

そして、工程S109又は工程S112の後、所定のインターバル時間が経過する毎に(工程S113のY)、工程S101~工程S112が繰り返し行われる。

このように、本実施形態では、論理回路50は、例えば、32秒間の1秒未満の変化量ΔSubCntに基づいて生成された補正データTDに基づいて、同じく32秒間の補正期間における第2クロック信号CK2の周波数が平均して1.024kHzとなるように緩急処理を行う。あるいは、論理回路50は、25.6秒間の1秒未満の変化量ΔSubCntに基づいて生成された補正データTDに基づいて、同じく25.6秒である補正期間における第2クロック信号CK2の周波数が平均して1kHzとなるように緩急処理を行う。このように、1秒未満の変化量ΔSubCntを計算するための期間である基準信号REFに同期した間隔と補正期間の長さを一致させることにより、補正データTDの値を変化量ΔSubCntの符号を反転した値とすればよく、補正データ生成回路150のサイズを低減させることができる。

以上に説明したように、第2実施形態では、リアルタイムクロック回路3において、補正データ生成回路150が、基準信号REFの電圧レベルが遷移する所定のタイミングでイベント時刻レジスター80に保持された計時データSUB_Tに基づいて、補正データTDを生成する。したがって、第2実施形態によれば、ホストデバイス6が補正データTDを生成する必要がないので、ホストデバイス6の計算負荷を低減させることができる。

また、第2実施形態によれば、ホストデバイス6が計時データSUB_Tを読み出す必要がないので、読み出しに要する遅延時間のばらつきによる計時データSUB_Tの誤差が生じないので、補正データ生成回路150は正確な補正データTDを生成することができる。

その他、第2実施形態のリアルタイムクロックモジュール1は、適宜、第1実施形態のリアルタイムクロックモジュール1と同様の効果を奏する。

1-3.第3実施形態

第1実施形態では、ホストデバイス6はリアルタイムクロック回路3のイベント時刻レジスター80に保持されている計時データを読み出して補正データTDを生成するのに対して、第3実施形態では、ホストデバイス6はリアルタイムクロック回路3から現在時刻の計時データを読み出して補正データTDを生成する。以下、第3実施形態について、第1実施形態と同様の構成要素には同じ符号を付し、第1実施形態と重複する説明は省略または簡略し、主に第1実施形態と異なる内容について説明する。

第3実施形態のリアルタイムクロックモジュール1の機能ブロック図は、図1と同様であるため、その図示を省略する。

本実施形態では、ホストデバイス6は、内部で発生し、あるいは外部から受け取った基準信号REFに同期した間隔で、リアルタイムクロック回路3から計時データを読み出す。ホストデバイス6が読み出す計時データは、計時データSUB_Tを含み、さらに計時データBCD_T又は計時データBIN_Tを含む。

具体的には、ホストデバイス6は、基準信号REFの電圧レベルが遷移する所定のタイミングで、リアルタイムクロック回路3に、計時データSUB_T及び計時データBCD_T又は計時データBIN_Tの読み出しを要求するアクセス信号を送信する。例えば、基準信号REFの電圧レベルが遷移する所定のタイミングは、基準信号REFがローレベルからハイレベルに遷移するタイミングであってもよいし、基準信号REFがハイレベルからローレベルに遷移するタイミングであってもよい。リアルタイムクロック回路3のインターフェース回路90は、当該アクセス信号を受信し、読み出し対象となる計時データの読み出しを要求する不図示の読み出し要求信号を発生し、リードバッファー70に出力する。そして、インターフェース回路90は、リードバッファー70が取得して保持した読み出し対象の計時データである読み出しデータRDATを取得し、読み出しデータRDATをシリアルデータ信号SDAに変換して端子P7を介してホストデバイス6に送信し、ホストデバイス6は、計時データを取得する。

その後、ホストデバイス6は、基準信号REFの電圧レベルが遷移する所定のタイミングがn回発生すると、リアルタイムクロック回路3に、計時データSUB_T及び計時データBCD_T又は計時データBIN_Tの読み出しを要求するアクセス信号を再度送信し、当該計時データを取得する。整数nは、前述の補正期間設定データPNの値である。そして、ホストデバイス6は、取得した2つの計時データにそれぞれ含まれる計時データSUB_Tの差分により、基準信号REFのn周期の間隔での計時データSUB_Tの変化量を算出し、補正データTDを生成する。このように、補正データTDは、基準信号REFに同期した間隔での計時データSUB_Tの変化量に基づいて生成されたデータである。

論理回路50は、記憶部100に記憶された補正データTDを用いて、第1実施形態と同様に、補正期間において第1分周回路20に対して緩急処理を行う。

また、ホストデバイス6は、基準信号REFのn周期の間隔での計時データSUB_Tの変化量が所定値よりも大きい場合は、現在時刻のデータをリアルタイムクロック回路3のライトバッファー60に書き込み、計時回路40の計時データBCD_T,BIN_Tを更新する。

第3実施形態のリアルタイムクロックモジュール1のその他の構成は、第1実施形態と同様であるため、その設営を省略する。なお、リアルタイムクロック回路3は、タイムスタンプ機能及び割込発生機能がなくてもよいので、端子P5、イベント時刻レジスター80及び割込発生回路110を備えていなくてもよい。

図14は、第3実施形態のリアルタイムクロック回路3の補正方法の手順の一例を示す図である。

図14に示すように、まず、基準信号REFの電圧レベルが例えばローレベルからハイレベルに遷移すると(工程S201のY)、ホストデバイス6がリアルタイムクロック回路3から計時データを読み出す(工程S202)。工程S202において読み出される計時データは、計時データSUB_Tを含み、さらに計時データBCD_T又は計時データBIN_Tを含む。

次に、基準信号REFの電圧レベルが例えばローレベルからハイレベルにn回遷移すると(工程S203のY)、ホストデバイス6がリアルタイムクロック回路3から計時データを読み出す(工程S204)。工程S204において読み出される計時データは、計時データSUB_Tを含み、さらに計時データBCD_T又は計時データBIN_Tを含む。整数nは、前述の補正期間設定データPNの値である。例えば、nが32であり、基準信号REFの周期が1秒であれば、リアルタイムクロック回路3が基準信号REFを32回受信すると、すなわち、工程S201で基準信号REFの電圧レベルが遷移してから32秒が経過すると、再度、計時データが読み出される。

次に、ホストデバイス6が、工程S204で読み出した計時データと工程S202で読み出した計時データとの差分ΔTを計算する(工程S205)。例えば、nが32であり、基準信号REFの周期が1秒であれば、差分ΔTは計時データの32秒間の増加量に相当する。

そして、差分ΔTの期待値に対する誤差が1秒以内である場合は(工程S206のY)、ホストデバイス6が、1秒未満の変化量ΔSubCntに基づき補正データTDを生成し、生成した補正データTDをリアルタイムクロック回路3の記憶部100に書き込む(工程S207)。変化量ΔSubCntは、工程S204で読み出した計時データSUB_Tと工程S202で読み出した計時データSUB_Tとの差分である。例えば、nが32であり、基準信号REFの周期が1秒であれば、差分ΔTの期待値は32秒であるので、差分ΔTが31秒以上33秒以下である場合に工程S207が行われる。また、工程S207において、ホストデバイス6は、変化量ΔSubCntが-255~+255の範囲の値である前提で、補正データTDの値を200h-ΔSubCntによって計算する。

次に、リアルタイムクロック回路3が、工程S207で記憶部100に書き込まれた補正データTDを用いて第1分周回路20に対して緩急処理を行う(工程S208)。以降、リアルタイムクロック回路3は、補正データTDが更新されるまで、各補正期間において当該補正データTDを用いて時間的に分散して緩急処理を行う。

一方、差分ΔTが1秒よりも大きい場合は(工程S206のN)、ホストデバイス6が、現在時刻のデータをリアルタイムクロック回路3のライトバッファー60に書き込む(工程S209)。例えば、ホストデバイス6は、年、月、日、時、分及び秒の時刻データ及び年、月、日、時、分及び秒を秒単位で表した時刻データをライトバッファー60に書き込む。

次に、リアルタイムクロック回路3が、計時回路40の計時データBCD_T,BIN_Tをライトバッファー60が保持する現在時刻のデータに更新する(工程S210)。

そして、工程S208又は工程S210の後、所定のインターバル時間が経過する毎に(工程S211のY)、工程S201~工程S210が繰り返し行われる。

以上に説明したように、第3実施形態では、ホストデバイス6が、リアルタイムクロック回路3から計時データを読み出して補正データTDを生成し、生成した補正データTDをリアルタイムクロック回路3の記憶部100に書き込む。したがって、第3実施形態によれば、リアルタイムクロック回路3が補正データTDを生成する必要がないので、リアルタイムクロック回路3のサイズを低減させることができる。

また、第3実施形態では、リアルタイムクロック回路3が、基準信号REFの電圧レベ

ルが遷移する所定のタイミング毎に計時データを保持する必要がないので、リアルタイムクロック回路3のサイズを低減させ、あるいは、リアルタイムクロック回路3の処理負荷を低減させることができる。

その他、第3実施形態のリアルタイムクロックモジュール1は、適宜、第1実施形態のリアルタイムクロックモジュール1と同様の効果を奏する。

1-4.変形例

上記の各実施形態では、第2分周回路30がバイナリーカウンターとして動作する場合は、補正データTDが生成される間隔及び補正期間の長さが、1Hzの基準信号REFの1周期の長さの32倍に相当する32秒である例を挙げ、第2分周回路30がBCDカウンターとして動作する場合は、補正データTDが生成される間隔及び補正期間の長さが、1.25Hzの基準信号REFの1周期の長さの32倍に相当する25.6秒である例を挙げたが、補正データTDが生成される間隔及び補正期間の長さや基準信号REFの周期はこれに限られない。例えば、基準信号REFの1周期を、補正データTDが生成される間隔及び補正期間の長さである32秒又は25.6秒と一致させてもよい。

また、上記の各実施形態では、第2分周回路30がBCDカウンターとして動作する場合、1.25Hzの基準信号REFの1周期の長さは0.8秒であり、1PPSの信号の1周期の長さである1秒の整数倍となっていないが、基準信号REFの1周期の長さが1秒の整数倍となるようにしてもよい。例えば、基準信号REFの1周期の長さを256秒とし、基準信号REFの1周期の間隔で取得された2つの計時データSUB_Tの差分を1/10して符号を反転した値を補正データTDの値としてもよい。あるいは、基準信号REFの1周期の長さを1秒とし、すなわち、1PPSの信号を基準信号REFとし、基準信号REFの256周期の間隔で取得された2つの計時データSUB_Tの差分を1/10して符号を反転した値を補正データTDの値としてもよい。

また、上記の各実施形態では、第1分周回路20、第2分周回路30及び計時回路40が非同期リップル回路である例を挙げたが、第1分周回路20、第2分周回路30及び計時回路40は同期型カウンター回路であってもよい。例えば、第1分周回路20は第1クロック信号CK1に同期して動作するカウンター回路であってもよいし、第2分周回路20は第2クロック信号CK2に同期して動作するカウンター回路であってもよいし、計時回路40は第2クロック信号CK2又は第3クロック信号CK3に同期して動作するカウンター回路であってもよい。

2.電子機器

図15は、上述した各実施形態のリアルタイムクロックモジュール1又はリアルタイムクロック回路3を用いた電子機器の実施形態の構成の一例を示す機能ブロック図である。また、図16は、本実施形態の電子機器の一例であるスマートフォンの外観の一例を示す図である。

本実施形態の電子機器300は、リアルタイムクロックモジュール1、ホストデバイス320、操作部330、記憶部340、通信部350、表示部360及び音出力部370を含んで構成されている。なお、本実施形態の電子機器300は、図15の構成要素の一部を省略又は変更し、あるいは、他の構成要素を付加した構成としてもよい。

前述の通り、リアルタイムクロックモジュール1は、振動子2と、リアルタイムクロック回路3とを備える。

ホストデバイス320は、記憶部340等に記憶されているプログラムに従い、各種の

計算処理や制御処理を行う。具体的には、ホストデバイス320は、操作部330からの操作信号に応じた各種の処理、他の機器とデータ通信を行うために通信部350を制御する処理、表示部360に各種の情報を表示させるための表示信号を送信する処理、音出力部370から各種の音を出力させるための音信号を送信する処理等を行う。

また、ホストデバイス320は、リアルタイムクロック回路3と通信する。例えば、ホストデバイス320は、リアルタイムクロック回路3から計時データ等を読み出して各種の計算処理や制御処理を行う。また、ホストデバイス320は、リアルタイムクロック回路3に対して計時データの書き換え等を行う。また、ホストデバイス320は、リアルタイムクロック回路3に対して、前述の補正データTDを含む各種のデータや基準信号REFを送信してもよい。ホストデバイス320は、例えば、MCU(Micro Controller Unit)やMPU(Micro Processor Unit)によって実現される。なお、ホストデバイス320は、上述したホストデバイス6に対応する。

操作部330は、操作キーやボタンスイッチ等により構成される入力装置であり、ユーザーによる操作に応じた操作信号をホストデバイス320に出力する。ホストデバイス320は、例えば、操作部330から入力される信号に応じて、リアルタイムクロック回路3に時刻情報を設定することができる。

記憶部340は、ホストデバイス320が各種の計算処理や制御処理を行うためのプログラムやデータ等を記憶している。また、記憶部340は、ホストデバイス320の作業領域として用いられ、記憶部340から読み出されたプログラムやデータ、操作部330から入力されたデータ、ホストデバイス320が各種プログラムに従って実行した演算結果等を一時的に記憶する。記憶部340は、ROM(Read Only Memory)やRAM(Random Access Memory)を含んで構成され、例えば、ハードディスク、フレキシブルディスク、MO、MT、各種のメモリー、CD-ROM、又は、DVD-ROM等によって実現される。

通信部350は、ホストデバイス320と外部装置との間のデータ通信を成立させるための各種制御を行う。

表示部360は、LCD(Liquid Crystal Display)等により構成される表示装置であり、ホストデバイス320から入力される表示信号に基づいて各種の情報を表示する。表示部360には操作部330として機能するタッチパネルが設けられていてもよい。

音出力部370は、スピーカー等によって構成され、ホストデバイス320から入力される音信号に基づいて各種の情報を音や音声として出力する。

本実施形態の電子機器300は、短時間で簡易に計時データの補正データを取得することが可能なリアルタイムクロック回路3を備えるので、高い信頼性を実現することができる。

このような電子機器300としては種々の電子機器が考えられ、例えば、電子時計、モバイル型、ラップトップ型、タブレット型などのパーソナルコンピューター、スマートフォンや携帯電話機などの移動体端末、ディジタルカメラ、インクジェットプリンターなどのインクジェット式吐出装置、ルーターやスイッチなどのストレージエリアネットワーク機器、ローカルエリアネットワーク機器、移動体端末基地局用機器、テレビ、ビデオカメラ、ビデオレコーダー、カーナビゲーション装置、リアルタイムクロック装置、ページャー、電子手帳、電子辞書、電卓、電子ゲーム機器、ゲーム用コントローラー、ワードプロセッサー、ワークステーション、テレビ電話、防犯用テレビモニター、電子双眼鏡、PO

S端末、電子体温計、血圧計、血糖計、心電図計測装置、超音波診断装置、電子内視鏡等の医療機器、魚群探知機、各種測定機器、車両、航空機、船舶等の計器類、フライトシミュレーター、ヘッドマウントディスプレイ、モーショントレース、モーショントラッキング、モーションコントローラー、歩行者自立航法(PDR:Pedestrian Dead Reckoning)装置等が挙げられる。

本発明は本実施形態に限定されず、本発明の要旨の範囲内で種々の変形実施が可能である。

上述した実施形態および変形例は一例であって、これらに限定されるわけではない。例えば、各実施形態および各変形例を適宜組み合わせることも可能である。

本発明は、実施の形態で説明した構成と実質的に同一の構成(例えば、機能、方法及び結果が同一の構成、あるいは目的及び効果が同一の構成)を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。

上述した実施形態および変形例から以下の内容が導き出される。

リアルタイムクロック回路の一態様は、

振動子を発振させて第1クロック信号を生成する発振回路と、

前記第1クロック信号を分周して第2クロック信号を生成する第1分周回路と、

前記第2クロック信号を分周して第3クロック信号を生成するとともに、前記第2クロック信号に基づいて1秒よりも短い時間の第1計時データを生成する第2分周回路と、

前記第3クロック信号に基づいて1秒以上の時間の第2計時データを生成する計時回路と、

基準信号に同期した間隔での前記第1計時データの変化量に基づいて生成された補正データを用いて、前記間隔に相当する長さの期間において、前記第1分周回路に対して緩急処理を行う論理回路と、を備える。

このリアルタイムクロック回路では、論理回路が、基準信号に同期した間隔での1秒よりも短い時間の第1計時データの変化量に基づいて生成された補正データを用いて、第2クロック信号を生成する第1分周回路に対して緩急処理を行う。したがって、1秒以上の任意の短時間で生成された補正データを用いて、第2クロック信号が補正される。そして、第2分周回路が第2クロック信号を分周して第3クロック信号を生成し、計時回路が第3クロック信号に基づいて1秒以上の時間の第2計時データを生成するので、第2計時データが短時間で補正される。また、このリアルタイムクロック回路では、基準信号に同期した間隔での第1計時データの変化量に基づいて補正データが生成される。そのため、リアルタイムクロック回路が第3クロック信号を外部装置に出力し、外部装置が第3クロック信号の周波数を計測して補正データを作成する必要がない。したがって、このリアルタイムクロック回路によれば、短時間で簡易に計時データの補正データを取得することができる。さらに、このリアルタイムクロック回路では、補正データを用いた緩急処理が行われる期間の長さが、補正データを生成するために第1計時データの変化量が算出される間隔と一致するので、第1計時データの変化量の符号を反転した値を補正データの値とすることができる。したがって、このリアルタイムクロック回路によれば、補正データの生成が容易である。以上より、このリアルタイムクロック回路によれば、優れたユーザー利便性を実現することができる。

前記リアルタイムクロック回路の一態様において、

前記間隔は、前記第3クロック信号の周期よりも長く、

前記論理回路は、前記期間において、前記第2クロック信号の周期よりも長い時間間隔で前記緩急処理を行ってもよい。

このリアルタイムクロック回路によれば、補正データを生成するために第1計時データの変化量が算出される間隔が、1秒以上の第2計時データを生成する計時回路が用いる第3クロック信号の周期よりも長いので、論理回路は高い分解能で第2クロック信号を補正することができる。さらに、このリアルタイムクロック回路によれば、論理回路が、第2クロック信号の周期よりも長い時間間隔で時間的に分散して第1分周回路に対して緩急処理を行うので、第2クロック信号の周波数変動量のばらつきを小さくすることができる。

前記リアルタイムクロック回路の一態様は、

前記基準信号の電圧レベルが遷移する所定のタイミングで前記第1計時データを保持するバッファー回路を備えてもよい。

このリアルタイムクロック回路では、補正データが、基準信号の電圧レベルが遷移する所定のタイミングでバッファー回路に保持された第1計時データに基づいて生成される。したがって、このリアルタイムクロック回路によれば、例えば、外部装置がバッファー回路に保持された第1計時データを読み出して補正データを生成する場合において、第1計時データの読み出しに要する遅延時間にばらつきがあっても、遅延時間のばらつきによる第1計時データの誤差が生じないので、高い精度で計時データを補正することができる。

前記リアルタイムクロック回路の一態様は、

保持した前記第1計時データに基づいて前記補正データを生成する補正データ生成回路を備えてもよい。

このリアルタイムクロック回路では、補正データ生成回路が、基準信号の電圧レベルが遷移する所定のタイミングでバッファー回路に保持された第1計時データに基づいて、補正データを生成する。したがって、このリアルタイムクロック回路によれば、外部装置が補正データを生成する必要がないので、外部装置の計算負荷を低減させることができる。また、このリアルタイムクロックによれば、外部装置が第1計時データを読み出す必要がないので、読み出しに要する遅延時間のばらつきによる第1計時データの誤差が生じないので、高い精度で計時データを補正することができる。

前記リアルタイムクロック回路の一態様は、

前記第1計時データを送信するインターフェース回路を備えてもよい。

このリアルタイムクロック回路によれば、外部装置が、インターフェース回路が送信する第1計時データを受信して補正データを生成することができる。したがって、リアルタイムクロック回路が補正データを生成する必要がないので、リアルタイムクロック回路のサイズを低減させることができる。

前記リアルタイムクロック回路の一態様において、

前記インターフェース回路は、前記間隔を指定する情報を受信してもよい。

このリアルタイムクロック回路によれば、補正データを生成するために第1計時データの変化量が算出される間隔、すなわち、補正データを用いた緩急処理が行われる期間の長さを、補正の精度と補正に要する時間とのトレードオフを考慮して、ユーザーが任意に設定することができる。

リアルタイムクロックモジュールの一態様は、

前記リアルタイムクロック回路の一態様と、

前記振動子と、を備える。

電子機器の一態様は、

前記リアルタイムクロック回路の一態様と、

前記リアルタイムクロック回路と通信するホストデバイスと、を備える。

リアルタイムクロック回路の補正方法の一態様は、

振動子を発振させて第1クロック信号を生成する発振回路と、前記第1クロック信号を分周して第2クロック信号を生成する第1分周回路と、前記第2クロック信号を分周して第3クロック信号を生成するとともに、前記第2クロック信号に基づいて1秒よりも短い時間の第1計時データを生成する第2分周回路と、前記第3クロック信号に基づいて1秒以上の時間の第2計時データを生成する計時回路と、を備えたリアルタイムクロック回路の補正方法であって、

前記リアルタイムクロック回路が、基準信号に同期した間隔での前記第1計時データの変化量に基づいて生成された補正データを用いて、前記間隔に相当する長さの期間において、前記第1分周回路に対して緩急処理を行う工程を備える。

このリアルタイムクロック回路の補正方法では、リアルタイムクロック回路が、基準信号に同期した間隔での1秒よりも短い時間の第1計時データの変化量に基づいて生成された補正データを用いて、第2クロック信号を生成する第1分周回路に対して緩急処理を行う。したがって、1秒以上の任意の短時間で生成された補正データを用いて、第2クロック信号が補正される。そして、第2分周回路が第2クロック信号を分周して第3クロック信号を生成し、計時回路が第3クロック信号に基づいて1秒以上の時間の第2計時データを生成するので、第2計時データが短時間で補正される。また、このリアルタイムクロック回路の補正方法では、基準信号に同期した間隔での第1計時データの変化量に基づいて補正データが生成される。そのため、リアルタイムクロック回路が第3クロック信号を外部装置に出力し、外部装置が第3クロック信号の周波数を計測して補正データを作成する必要がない。したがって、このリアルタイムクロック回路の補正方法によれば、短時間で簡易に計時データの補正データを取得することができる。さらに、このリアルタイムクロック回路の補正方法では、補正データを用いた緩急処理が行われる期間の長さが、補正データを生成するために第1計時データの変化量が算出される間隔と一致するので、第1計時データの変化量の符号を反転した値を補正データの値とすることができる。したがって、このリアルタイムクロック回路の補正方法によれば、補正データの生成が容易である。以上より、このリアルタイムクロック回路の補正方法によれば、優れたユーザー利便性を実現することができる。

前記リアルタイムクロック回路の補正方法の一態様は、

ホストデバイスが、前記リアルタイムクロック回路に前記基準信号を送信する工程と、

前記リアルタイムクロック回路が、前記基準信号の電圧レベルが遷移する所定のタイミング毎に前記第1計時データを保持する工程と、

前記リアルタイムクロック回路が、前記ホストデバイスに割込み信号を送信する工程と、

前記ホストデバイスが、前記割込み信号を受信し、前記間隔で保持された2つの前記第1計時データを読み出す工程と、

前記ホストデバイスが、読み出した2つの前記第1計時データに基づいて前記補正データを生成し、生成した前記補正データを前記リアルタイムクロック回路の記憶部に書き込む工程と、を含んでもよい。

このリアルタイムクロック回路の補正方法では、ホストデバイスが、リアルタイムクロック回路から第1計時データを読み出して補正データを生成し、生成した補正データをリアルタイムクロック回路の記憶部に書き込む。したがって、このリアルタイムクロック回路の補正方法によれば、リアルタイムクロック回路が補正データを生成する必要がないので、リアルタイムクロック回路のサイズを低減させることができる。また、このリアルタイムクロック回路の補正方法では、リアルタイムクロック回路が基準信号の電圧レベルが遷移する所定のタイミングで保持した第1計時データに基づいて、ホストデバイスが補正データを生成する。したがって、このリアルタイムクロック回路の補正方法によれば、ホストデバイスが第1計時データの読み出しに要する遅延時間にばらつきがあっても、遅延時間のばらつきによる第1計時データの誤差が生じないので、高い精度で計時データを補正することができる。

前記リアルタイムクロック回路の補正方法の一態様は、

ホストデバイスが、前記リアルタイムクロック回路に前記基準信号を送信する工程と、

前記リアルタイムクロック回路が、前記基準信号の電圧レベルが遷移する所定のタイミング毎に前記第1計時データを保持する工程と、

前記リアルタイムクロック回路が、前記間隔で保持された2つの前記第1計時データに基づいて前記補正データを生成する工程と、を含んでもよい。

このリアルタイムクロック回路の補正方法では、リアルタイムクロック回路が、基準信号の電圧レベルが遷移する所定のタイミングでバッファー回路に保持された第1計時データに基づいて、補正データを生成する。したがって、このリアルタイムクロック回路の補正方法によれば、ホストデバイスが補正データを生成する必要がないので、ホストデバイスの計算負荷を低減させることができる。また、このリアルタイムクロック回路の補正方法では、リアルタイムクロック回路が、基準信号の電圧レベルが遷移する所定のタイミングで保持した第1計時データに基づいて、補正データを生成する。したがって、このリアルタイムクロック回路の補正方法によれば、ホストデバイスが第1計時データを読み出す必要がないので、読み出しに要する遅延時間のばらつきによる第1計時データの誤差が生じないので、高い精度で計時データを補正することができる。

前記リアルタイムクロック回路の補正方法の一態様は、

ホストデバイスが、前記間隔で前記リアルタイムクロック回路から2つの前記第1計時データを読み出す工程と、

前記ホストデバイスが、読み出した2つの前記第1計時データに基づいて前記補正データを生成し、生成した前記補正データを前記リアルタイムクロック回路の記憶部に書き込む工程と、を含んでもよい。

このリアルタイムクロック回路の補正方法では、ホストデバイスが、リアルタイムクロック回路から第1計時データを読み出して補正データを生成し、生成した補正データをリアルタイムクロック回路の記憶部に書き込む。したがって、このリアルタイムクロック回路の補正方法によれば、リアルタイムクロック回路が補正データを生成する必要がないので、リアルタイムクロック回路のサイズを低減させることができる。また、このリアルタイムクロック回路の補正方法では、リアルタイムクロック回路が、基準信号の電圧レベルが遷移する所定のタイミング毎に第1計時データを保持する必要がないので、リアルタイムクロック回路のサイズを低減させ、あるいは、リアルタイムクロック回路の処理負荷を低減させることができる。