JP7021033B2 - 変調器及び信号伝送システム - Google Patents

変調器及び信号伝送システム Download PDFInfo

- Publication number

- JP7021033B2 JP7021033B2 JP2018168233A JP2018168233A JP7021033B2 JP 7021033 B2 JP7021033 B2 JP 7021033B2 JP 2018168233 A JP2018168233 A JP 2018168233A JP 2018168233 A JP2018168233 A JP 2018168233A JP 7021033 B2 JP7021033 B2 JP 7021033B2

- Authority

- JP

- Japan

- Prior art keywords

- logic

- input data

- oscillation

- signal

- oscillator

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000008054 signal transmission Effects 0.000 title claims description 22

- 230000010355 oscillation Effects 0.000 claims description 131

- 230000007704 transition Effects 0.000 claims description 85

- 230000003111 delayed effect Effects 0.000 claims description 15

- 230000001934 delay Effects 0.000 claims description 9

- 238000010586 diagram Methods 0.000 description 33

- 238000004891 communication Methods 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000007562 laser obscuration time method Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000009966 trimming Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/02—Amplitude-modulated carrier systems, e.g. using on-off keying; Single sideband or vestigial sideband modulation

- H04L27/04—Modulator circuits; Transmitter circuits

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/50—Transmitters

- H04B10/516—Details of coding or modulation

- H04B10/524—Pulse modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/50—Transmitters

- H04B10/516—Details of coding or modulation

- H04B10/548—Phase or frequency modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/02—Amplitude-modulated carrier systems, e.g. using on-off keying; Single sideband or vestigial sideband modulation

- H04L27/06—Demodulator circuits; Receiver circuits

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Transmitters (AREA)

- Dc Digital Transmission (AREA)

Description

前記入力データが前記第2論理から前記第1論理に遷移するタイミングに応じて、予め定めたパルス幅及びパルス数のパルス信号を出力するパルス発生部と、

前記入力データが前記第2論理のときは前記発振器から出力された発振信号を選択し、前記入力データが前記第1論理のときは前記パルス発生部から出力された前記パルス信号を選択する信号選択部と、を備える、変調器が提供される。

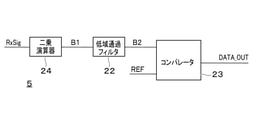

図1は第1の実施形態による変調器1を備えた信号伝送システム2のブロック図である。図1の信号伝送システム2は、送信器3と、絶縁デバイス4と、受信器5とを備えている。図1の信号伝送システム2は、送信器3側と受信器5側とで、直流電圧レベルが大きく相違していても、2値の信号伝送を行えるように、絶縁デバイス4によって、送信器3側と受信器5側との電気的な絶縁を図りつつ、信号伝送を行う。

第1の実施形態によるOOK変調器1では、入力データDATA_INがハイからローに遷移する際に、発振信号にパルス信号を付加して変調信号を生成するため、付加するパルス信号のパルス幅とパルス数に応じて、変調信号の伝搬遅延時間が増加する。第1の実施形態による変調器1から出力される変調信号の伝搬遅延時間は、入力データDATA_INがハイからローに遷移するときのみ増加し、入力データDATA_INがローからハイに遷移する際には増加しない。このように、入力データDATA_INがローからハイに遷移する場合と、ハイからローに遷移する場合とで、変調信号の伝搬遅延時間に差異が生じる。この結果、入力データDATA_INのパルス幅と、受信器5の出力データDATA_OUTのパルス幅とが相違してしまう。これは、パルス幅歪と呼ばれ、用途によっては好ましくないため、低減するのが望ましい。

第1及び第2の実施形態における発振器11は、遅延回路付きのリング発振回路で構成可能である。

上述した第2の実施形態では、入力データDATA_INがハイからローに遷移する際の変調信号の遅延時間を抑制するために、発振器11の前段に遅延器14を接続する例を説明した。これに対して、第4の実施形態は、発振器11の前段に遅延器14を接続する代わりに、受信器5側にタイミング調整部を設けるものである。

上述した第1~第4の実施形態におけるパルス発生部12から出力されるパルス信号は、入力データDATA_INの立ち下がりごとに変動しないパルス波形を持っていればよく、パルス信号の周波数は必ずしも発振器11から出力される発振信号の周波数と同一でなくてもよい。このため、発振器11は、LC発振回路やリング発振回路16など、任意の回路方式の発振回路でよい。また、パルス発生部12も任意の回路構成にて構成可能である。ただし、発振器11から出力される発振信号の周波数とパルス発生部12から出力されるパルス信号の周波数が著しくかけ離れていると、絶縁デバイス4や受信器5の通過信号帯域を広くしなければならず、システム構成が複雑化し、コストも嵩んでしまう。このような観点から、パルス発生部12から出力されるパルス信号の周波数は、発振器11から出力される発振信号の周波数と概ね一致させるのが望ましい。

第6の実施形態によるOOK変調器1は、第1~第5の実施形態とは根本的に異なる構成を備えている。

Claims (8)

- 入力データが第1論理から第2論理に遷移するタイミングに応じて発振を開始し、前記第2論理から前記第1論理に遷移するタイミングに応じて発振を停止する発振器と、

前記入力データが前記第2論理から前記第1論理に遷移するタイミングに応じて、予め定めたパルス幅及びパルス数のパルス信号を出力するパルス発生部と、

前記入力データが前記第2論理のときは前記発振器から出力された発振信号を選択し、前記入力データが前記第1論理のときは前記パルス発生部から出力された前記パルス信号を選択する信号選択部と、を備える、変調器。 - 入力データを所定の時間遅延させた遅延データを出力する遅延器と、

前記遅延データが第1論理から第2論理に遷移するタイミングに応じて発振を開始し、前記第2論理から前記第1論理に遷移するタイミングに応じて発振を停止する発振器と、

前記入力データが前記第2論理から前記第1論理に遷移するタイミングに応じて、予め定めたパルス幅及びパルス数のパルス信号を出力するパルス発生部と、

前記入力データが前記第2論理のときは前記発振器から出力された発振信号を選択し、前記入力データが前記第1論理のときは前記パルス発生部から出力された前記パルス信号を選択する信号選択部と、を備える、変調器。 - 前記発振器は、

前記入力データを遅延させる第1遅延回路と、

前記遅延された入力データをさらに遅延させる第2遅延回路と、

前記第2遅延回路の出力データ及び前記第2遅延回路の出力データを反転遅延させたデータに基づいて発振信号を生成する発振回路と、を有する、請求項1に記載の変調器。 - 入力データを遅延させる第1遅延回路と、

前記遅延された入力データをさらに遅延させる第2遅延回路と、

前記さらに遅延された入力データが第1論理から第2論理に遷移するタイミングに応じて発振を開始し、前記第2遅延回路の出力データ及び前記第2遅延回路の出力データを反転遅延させたデータに基づいて発振信号を生成する発振回路と、

前記入力データが前記第1論理から前記第2論理に遷移するタイミングに応じて、予め定めたパルス幅及びパルス数のパルス信号を出力するパルス発生部と、

前記入力データが前記第1論理のときは前記発振回路から出力された発振信号を選択し、前記入力データが前記第2論理のときは前記パルス発生部から出力された前記パルス信号を選択する信号選択部と、を備える、変調器。 - 前記第1遅延回路は、前記パルス信号のパルス幅で前記入力データを遅延させ、

前記第2遅延回路は、前記パルス信号のパルス幅で前記遅延された入力データをさらに遅延させ、

前記パルス発生部は、前記入力データ、前記遅延された入力データ、及び前記さらに遅延された入力データに基づいて前記パルス信号を生成する、請求項3又は4に記載の変調器。 - 入力データが第1論理から第2論理に遷移するタイミングに応じて発振を開始し、前記第2論理から前記第1論理に遷移するタイミングに応じて発振を停止する第1発振器と、

前記第1発振器の発振回数が第1発振回数に到達したことを検知する第1計測器と、

前記入力データが前記第2論理から前記第1論理に遷移するタイミングに応じて発振を開始する第2発振器と、

前記第2発振器の発振回数が第2発振回数に到達したことを検知する第2計測器と、

前記第2計測器で前記第2発振回数に到達したことが検知されると、前記第2発振器の発振動作を停止させる発振制御部と、

前記第1計測器で前記第1発振回数に到達したことが検知されてから、前記入力データが前記第2論理から前記第1論理に遷移するまでは前記第1発振器から出力された発振信号を選択し、前記入力データが前記第2論理から前記第1論理に遷移した以降は前記第2発振器から出力された発振信号を選択する信号選択部と、を備える、変調器。 - 請求項1乃至6のいずれか一項に記載の変調器を有する送信器と、

前記送信器から出力された変調信号を絶縁した状態で伝送する絶縁デバイスと、

前記絶縁デバイスを介して伝送された前記変調信号を復調する復調器を有する受信器と、を備える、信号伝送システム。 - 変調器を有する送信器と、

前記送信器から出力された変調信号を絶縁した状態で伝送する絶縁デバイスと、

前記絶縁デバイスを介して伝送された前記変調信号を復調する復調器を有する受信器と、を備え、

前記変調器は、

入力データが第1論理から第2論理に遷移するタイミングに応じて発振を開始し、前記第2論理から前記第1論理に遷移するタイミングに応じて発振を停止する発振器と、

前記入力データが前記第2論理から前記第1論理に遷移するタイミングに応じて、予め定めたパルス幅及びパルス数のパルス信号を出力するパルス発生部と、

前記入力データが前記第2論理のときは前記発振器から出力された発振信号を選択し、前記入力データが前記第1論理のときは前記パルス発生部から出力された前記パルス信号を選択する信号選択部と、を有し、

前記受信器は、前記パルス信号のパルス幅及びパルス数に基づいて、前記復調された変調信号が出力されるタイミングを調整するタイミング調整部を有する、信号伝送システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018168233A JP7021033B2 (ja) | 2018-09-07 | 2018-09-07 | 変調器及び信号伝送システム |

| US16/290,098 US10666474B2 (en) | 2018-09-07 | 2019-03-01 | Modulator and signal transmission system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018168233A JP7021033B2 (ja) | 2018-09-07 | 2018-09-07 | 変調器及び信号伝送システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020043429A JP2020043429A (ja) | 2020-03-19 |

| JP7021033B2 true JP7021033B2 (ja) | 2022-02-16 |

Family

ID=69720156

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018168233A Active JP7021033B2 (ja) | 2018-09-07 | 2018-09-07 | 変調器及び信号伝送システム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10666474B2 (ja) |

| JP (1) | JP7021033B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7366849B2 (ja) * | 2020-07-09 | 2023-10-23 | 株式会社東芝 | 通信装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001177584A (ja) | 1999-12-17 | 2001-06-29 | Tamura Electric Works Ltd | 変調回路 |

| JP2002043067A (ja) | 2000-07-21 | 2002-02-08 | Matsushita Electric Works Ltd | 照明装置 |

| US20150171901A1 (en) | 2013-12-13 | 2015-06-18 | Silicon Laboratories Inc. | Techniques for reduced jitter in digital isolators |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4415861A (en) * | 1981-06-08 | 1983-11-15 | Tektronix, Inc. | Programmable pulse generator |

| JPS63268336A (ja) * | 1987-04-24 | 1988-11-07 | Matsushita Electric Works Ltd | パルス変調送信回路 |

| JP2825252B2 (ja) * | 1989-01-20 | 1998-11-18 | 株式会社東芝 | 波形整形回路 |

| JPH0615308Y2 (ja) * | 1989-06-08 | 1994-04-20 | 株式会社ケンウッド | キーイング回路 |

| JP3077154B2 (ja) * | 1990-03-02 | 2000-08-14 | ソニー株式会社 | エンハンサ回路 |

| JP2900772B2 (ja) * | 1993-12-24 | 1999-06-02 | 株式会社デンソー | パルス位相差符号化回路とパルス発生回路との複合装置及びデジタル制御pll装置 |

| JP4282998B2 (ja) * | 2003-01-08 | 2009-06-24 | パナソニック株式会社 | 変調器及びその補正方法 |

| US7459951B2 (en) * | 2006-02-22 | 2008-12-02 | Exar Corporation | Self-calibrating digital pulse-width modulator (DPWM) |

| JP4106383B2 (ja) * | 2006-06-08 | 2008-06-25 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 遅延比率調整回路、遅延パルス生成回路及びパルス幅変調パルス信号発生装置。 |

| WO2012151050A2 (en) * | 2011-05-02 | 2012-11-08 | Rambus Inc. | Integrated circuit having a multiplying injection-locked oscillator |

-

2018

- 2018-09-07 JP JP2018168233A patent/JP7021033B2/ja active Active

-

2019

- 2019-03-01 US US16/290,098 patent/US10666474B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001177584A (ja) | 1999-12-17 | 2001-06-29 | Tamura Electric Works Ltd | 変調回路 |

| JP2002043067A (ja) | 2000-07-21 | 2002-02-08 | Matsushita Electric Works Ltd | 照明装置 |

| US20150171901A1 (en) | 2013-12-13 | 2015-06-18 | Silicon Laboratories Inc. | Techniques for reduced jitter in digital isolators |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2020043429A (ja) | 2020-03-19 |

| US10666474B2 (en) | 2020-05-26 |

| US20200084075A1 (en) | 2020-03-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100459709B1 (ko) | 여유 있는 셋업 앤드 홀드 타임 마진을 가지는 병렬-직렬송신 회로 | |

| US8634509B2 (en) | Synchronized clock phase interpolator | |

| US7667544B2 (en) | Clock reproducing apparatus | |

| US6819153B2 (en) | Semiconductor device for clock signals synchronization accuracy | |

| KR101326117B1 (ko) | 위상 반전 록킹 알고리즘을 이용한 디지털 지연 고정 루프 회로 및 제어방법 | |

| WO2012147258A1 (ja) | チャネル間スキュー調整回路 | |

| WO2014041924A1 (ja) | クロック生成装置およびクロックデータ復元装置 | |

| KR20170112674A (ko) | 다위상 클록 신호 보정 장치 | |

| US8804887B2 (en) | Transmission and receiving apparatus and method having different sending and receiving clocks | |

| JP7021033B2 (ja) | 変調器及び信号伝送システム | |

| JP4992947B2 (ja) | パラレル−シリアル変換器及びパラレルデータ出力器 | |

| JP5491454B2 (ja) | パラレル−シリアル変換回路 | |

| TWI578708B (zh) | 內插器系統和方法 | |

| US20150102862A1 (en) | Oscillator | |

| TWI495266B (zh) | 環型振盪器電路 | |

| JP5697066B1 (ja) | パルス生成装置 | |

| US20170077918A1 (en) | High-speed programmable clock divider | |

| JP3476448B2 (ja) | 信号同期回路 | |

| US9762183B2 (en) | Voltage-controlled ring oscillator with delay line | |

| JP6823268B2 (ja) | 分周回路、デマルチプレクサ回路、及び半導体集積回路 | |

| JP5038323B2 (ja) | ジッタ印加装置、ジッタ印加方法、試験装置、及び通信チップ | |

| CN115441865A (zh) | 一种相位插值器以及时钟信号的相位插值方法 | |

| US10326456B2 (en) | Phase combiner circuit | |

| WO2007069139A2 (en) | Electric counter circuit | |

| JP2002094495A (ja) | 電圧制御オシレータ及びそれを用いたマルチビットレート・タイミング抽出回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200625 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210622 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210831 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211101 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220104 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220203 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 7021033 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |