JP4982014B2 - 画像表示装置 - Google Patents

画像表示装置 Download PDFInfo

- Publication number

- JP4982014B2 JP4982014B2 JP2001187478A JP2001187478A JP4982014B2 JP 4982014 B2 JP4982014 B2 JP 4982014B2 JP 2001187478 A JP2001187478 A JP 2001187478A JP 2001187478 A JP2001187478 A JP 2001187478A JP 4982014 B2 JP4982014 B2 JP 4982014B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- pixel

- image display

- display device

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000003990 capacitor Substances 0.000 claims description 54

- 239000000758 substrate Substances 0.000 claims description 11

- 238000000034 method Methods 0.000 claims description 8

- 238000012545 processing Methods 0.000 claims description 7

- 230000008569 process Effects 0.000 claims description 3

- 239000013078 crystal Substances 0.000 claims description 2

- 230000000295 complement effect Effects 0.000 claims 1

- 229910044991 metal oxide Inorganic materials 0.000 claims 1

- 150000004706 metal oxides Chemical class 0.000 claims 1

- 239000004065 semiconductor Substances 0.000 claims 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 46

- 238000010586 diagram Methods 0.000 description 25

- 239000002184 metal Substances 0.000 description 8

- 238000007796 conventional method Methods 0.000 description 7

- 230000002093 peripheral effect Effects 0.000 description 7

- 239000011159 matrix material Substances 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 230000000630 rising effect Effects 0.000 description 4

- 239000000872 buffer Substances 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000003086 colorant Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3258—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the voltage across the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0259—Details of the generation of driving signals with use of an analog or digital ramp generator in the column driver or in the pixel circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/066—Waveforms comprising a gently increasing or decreasing portion, e.g. ramp

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2014—Display of intermediate tones by modulation of the duration of a single pulse during which the logic level remains constant

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of El Displays (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Led Devices (AREA)

Description

【発明の属する技術分野】

本発明は多階調表示が可能な画像表示装置に係り、特に、画素間での表示特性ばらつきが十分に小さい画像表示装置に関する。

【0002】

【従来の技術】

以下に図16及び図17,図18を用いて、2つの従来の技術に関して説明する。

図16は従来の技術を用いた、発光表示デバイスの構成図である。画素発光体としての有機EL(Organic Electro-luminescent)素子204を有する画素205が表示部にマトリクス状に配置され、画素205はゲートライン206、ソースライン207、電源線208等を介して外部の駆動回路に接続されている。各画素205においては、ソースライン207は論理TFT(Thin-Film-Transistor)201を介して電力TFT203のゲート及び記憶コンデンサ202に接続されており、電力TFT203の一端と記憶コンデンサ202の他端とは共通に電源線208に接続されている。また電力TFT203の他端は有機EL素子204を介して共通電源端子に接続されている。

以下、本第一の従来例の動作を説明する。ゲートライン206が所定の画素行の論理TFT201を開閉することによって、外部の駆動回路からソースライン207に入力されていた信号電圧は電力TFT203のゲート及び記憶コンデンサ202に入力、保持される。電力TFT203は、上記信号電圧に応じた駆動電流を有機EL素子204に入力し、これによって有機EL素子204は上記信号電圧に対応して発光する。

このような従来技術に関しては、例えば公開特許広報/特開平8-241048等に詳しく記載されている。

【0003】

なお本従来例では上記公知例に合せて有機EL(Organic Electro-luminescent)素子という呼称を用いたが、これは近年は有機発光ダイオード(OLED, Organic Light Emitting Diode)素子と称されることが多い。本明細書中でも、以降では後者の呼称を用いることとする。

次に図17及び図18を用いて、他の従来の技術を説明する。

図17は第二の従来の技術を用いた発光表示デバイスの構成図である。画素発光体としての有機発光ダイオード(OLED, Organic Light Emitting Diode)素子214を有する画素215が、表示部にマトリクス状に配置されている。但し図17では図面の簡略化のため、単一の画素のみを記載している。画素215は選択線216、データ線217、電源線218等を介して外部の駆動回路に接続されている。各画素215においては、データ線217は入力TFT211を介してキャンセルコンデンサ210に接続されており、キャンセルコンデンサ210の他端は駆動TFT213のゲート、記憶コンデンサ212、オートゼロスイッチ221の一端に入力されている。記憶コンデンサ212の他端と駆動TFT213の一端は共通に電源線218に接続されている。また駆動TFT213とオートゼロスイッチ221の他端とは、共通にELスイッチ223の一端に接続され、ELスイッチ223の他端はOLED素子214を介して共通電源端子に接続されている。なおここで、オートゼロスイッチ221とELスイッチ223はTFTで構成されており、これらのゲートはそれぞれオートゼロ入力線(AZ)222とEL入力線(AZB)224に接続されている。

以下、本第二の従来例の動作を図18を用いて説明する。ここで図18には、画素への表示信号入力時におけるデータ線217、オートゼロ入力線(AZ)222、EL入力線(AZB)224、選択線216の駆動波形が示されている。なお本画素はpチャネルのTFTで構成されているため、図18の駆動波形は、上(高電圧側)がTFTのオフ、下(低電圧側)がTFTのオンに対応する。

【0004】

始めに図に記載したタイミング(1)では、選択線216がオン、オートゼロ入力線(AZ)222がオン、EL入力線(AZB)224がオフである。これに対応してそれぞれ入力TFT211がオン、オートゼロスイッチ221がオン、ELスイッチ223がオフする。これによってデータ線217に入力されていたオフレベルの信号電圧がキャンセルコンデンサ210の一端に入力されると同時に、オートゼロスイッチ221がオンすることによってダイオード接続された駆動TFT213のゲート・ソース間電圧は、(電源線218の電圧+Vth)にリセットされる。ここでVthは駆動TFT213のしきい値電圧である。この動作によって、画素はオフレベルの信号電圧が入力した場合に、駆動TFT213のゲートが丁度しきい値電圧にオートゼロバイアスされることになる。

【0005】

次に図に記載したタイミング(2)では、オートゼロ入力線(AZ)222がオフ、データ線217に所定レベルの信号が入力される。これによってそれぞれオートゼロスイッチ221がオフし、キャンセルコンデンサ210の一端にはオンレベルの信号が入力される。この動作によって、駆動TFT213のゲート電圧は上記オートゼロバイアス条件時に比べて、信号の入力レベルを加算した分だけ電圧が変化する。

【0006】

次に図に記載したタイミング(3)では、選択線216がオフ、EL入力線(AZB)224がオンする。これによって入力TFT211がオンして印加されていた入力レベルの信号をキャンセルコンデンサ210に記憶し、更にELスイッチ223がオンする。この動作によって、駆動TFT213のゲートはしきい値電圧から信号の入力レベルを加算した分だけ電圧が変化した状態で固定され、更に駆動TFT213によって駆動される信号電流がOLED素子214を所定の輝度で発光させる。

このような従来技術に関しては、例えばDigest of Technical Papers, SID98, pp.11-14等に詳しく記載されている。

【0007】

【発明が解決しようとする課題】

上記従来技術によれば、多階調表示が可能であり、かつまた画素間での表示特性ばらつきが十分に小さい画像表示装置を提供するには困難があった。以下これに関して説明する。

図16を用いて説明した第一の従来例においては、多階調の表示を行うことは困難であった。有機EL素子204は電流駆動型の素子であり、これを駆動する電力TFT203は電圧入力の電流出力素子として機能している。ところがここで電力TFT203のしきい値電圧,Vthにばらつきがあると、このばらつき成分は入力した信号電圧に加算されてしまい、画素毎に固定した輝度むらを生じてしまう。一般にTFTは単結晶Si素子と比較して個々の素子間ばらつきが大きく、特に画素のように多数のTFTをつくり込んだ場合は、各素子間の特性ばらつきを抑えることは非常に困難である。例えば低温多結晶Si TFTの場合、1V単位でVthのばらつきが生じてしまうことが知られている。OLED素子は一般に入力電圧に対しては発光特性が敏感であり、1Vの入力電圧の違いによって発光輝度が倍近く変わることもあるため、中間調表示ではこのような輝度むらを許容することはできない。そこでこの輝度むらを回避するためには入力する信号電圧をオン、オフの二値に限定せざるを得ず、このために中間調表示を含む多階調表示は困難であった。

これに対して図17、図18を用いて説明した第二の従来例は、キャンセルコンデンサ210とオートゼロスイッチ221の導入によって、上記問題点の解決を図っている。即ち本従来例は、駆動TFT213のVthばらつきをキャンセルコンデンサ210の両端電圧に吸収することによって、OLED素子214における輝度むらの発生回避を狙ったものである。しかしながら本従来例でも、Vth以外の駆動TFT213の特性ばらつきによって、OLED素子214の階調発光精度は低下してしまう。本従来例ではOLED素子214の駆動電流は、駆動TFT213の電流出力によって得られている。このことは例え駆動TFT213のVthばらつきをキャンセルすることができたとしても、駆動TFT213に移動度ばらつき等に起因する電流駆動能力のばらつきがあれば、同様に画素毎に利得ばらつき様の輝度むらを生じてしまうことを意味している。前述のように一般にTFTは個々の素子間ばらつきが大きく、特に画素のように多数のTFTをつくり込んだ場合は、各素子間のばらつきを抑えることは非常に困難である。例えば低温多結晶Si TFTの場合、数十%単位で移動度のばらつきが生じてしまうことが知られている。このため本従来例を持ってしても、このような輝度むらの発生に起因する画素間の表示特性ばらつきを、十分に小さくすることは困難であった。

なお以上のような画素間の表示特性ばらつきを解決する方法として、「入力信号の振幅をパルス幅変調に変換する」ための「PWM(Pulse Width Modulation)信号変換回路」を各画素に集積するという方法が公開特許公報「特開2000-235370」に開示されている。この方法ではOLED素子の駆動はオンとオフのみで制御されるため、表示画面が低温多結晶Si TFTの特性ばらつきに影響されることはない、という考え方である。しかしながら本公知例には以下のような問題点がある。1つ目は「PWM信号変換回路」もまた、低温多結晶Si TFTで構成することが低コスト化のためには望ましいが、その場合には低温多結晶Si TFTの特性ばらつきのため、今度は「PWM信号変換回路」の出力であるパルス幅変調特性がばらついてしまうという問題である。2つ目は従来知られている「PWM表示方式」では、「擬似輪郭」ノイズに起因する画質劣化が生じることである。これはプラズマディスプレイで問題となった現象であり、表示期間がフレーム中で時間的に片寄ってしまうと、動画像に輪郭状のノイズが生じるという問題である。プラズマディスプレイではこれを変調パルス幅の信号処理によって対策しているが、画素内に設けられた「PWM信号変換回路」でそのような高度な信号処理機能を実現することは現実的ではない。

【0008】

【課題を解決するための手段】

上記の課題は、複数の画素により構成された表示部と、画素領域に表示信号電圧を入力するための信号線とを少なくとも有する画像表示装置において、信号線から第一の容量の一端に表示信号電圧を入力するために設けられた第一のスイッチ手段と、第一の容量の他端に入力が接続された入力電圧反転出力手段と、入力電圧反転出力手段の出力によって制御された発光手段と、入力電圧反転出力手段の入力端と出力端の間に設けられた第二のスイッチ手段とを画素領域の少なくとも1つに有し、更に上記表示信号電圧を含む所定の電圧範囲内で掃引される画素駆動電圧を発生するための画素駆動電圧発生手段と、上記画素駆動電圧を画素における第一の容量の一端に入力するための画素駆動電圧入力手段を有することによって解決することができる。

【0009】

上記画像表示装置には、通常、外部から取り込まれた表示信号を記憶し、更にそのデータ処理を行う表示信号処理部が設けられる。

【0010】

また、本発明の課題は、複数の画素により構成された表示部と、該画素領域に表示信号電圧を入力するための信号線を有する画像表示装置において、上記複数の画素領域の少なくとも1つにおいて、上記信号線から上記画素領域に入力された表示信号電圧を記憶する記憶手段と、該表示信号電圧に基づいて上記画素領域における画像出力のオン期間とオフ期間を決定する画素オン期間決定手段と、上記画像出力のオン動作を1フレーム内で複数回繰り返させるための画素駆動手段とを有することによっても解決することができる。

【0011】

【発明の実施の形態】

(第一の実施例)

以下図1〜図8を用いて、本発明の第一の実施例に関して説明する。

始めに図1を用いて、本実施例の全体構成に関して述べる。

【0012】

図1は本実施例であるOLED(Organic Light Emitting Diode)表示パネルの構成図である。画素発光体としてのOLED素子4を有する画素5が表示部にマトリクス状に配置され、画素5はゲート線6、信号線7、リセット線10等を介して所定の駆動回路に接続されている。なおここでゲート線6及びリセット線10はゲート駆動回路22に、信号線7は信号駆動回路21及び三角波入力回路20に接続されており、画素5、ゲート駆動回路22、信号駆動回路21及び三角波入力回路20は全て、多結晶Si TFTを用いてガラス基板上に構成されている。各画素5においては、信号線7は入力TFT 1を介して記憶コンデンサ2に接続されており、記憶コンデンサ2の他端はリセットTFT 9の一端とインバータ回路 3の入力端子に接続されている。リセットTFT 9の他端とインバータ回路 3の出力端子は共通に、OLED素子4を介して共通接地端子に接地されている。

【0013】

次に図6を用いて、上記インバータ回路 3に関して説明する。

【0014】

図6は本実施例における一画素の構成図である。インバータ回路 3は、nチャネル多結晶Si TFT 32及びpチャネル多結晶Si TFT 31で構成されており、両者のソースはそれぞれ、nチャネルソース線 24及びpチャネルソース線 23に接続されている。また本実施例では後に述べるように縦方向配線を低抵抗メタルで、横方向配線をゲートメタルで構成したため、両ソース線 24,23はより低抵抗な縦方向配線で実現されている。

【0015】

以下、本実施例の全体の動作を説明するに先立って、図6に示したインバータ回路 3の動作について図2〜図4を用いて述べる。

【0016】

図3はインバータ回路 3の入力電圧,Vin−出力電圧,Vout特性であり、図中に実線で示した曲線がこの電圧特性である。さてここでリセットTFT 9がオンした場合を考えると、この場合にはVinとVoutが等しくなる。図中に”A”と記入した白丸がその際の動作点であり、入出力電圧はVrstにリセットされる。良く知られているように、このときVrstはインバータ電圧特性上における論理反転しきい値になる。

【0017】

次にOLED素子4の入力電圧,Voled−出力電流,Ioled特性を図2に示した。OLEDはダイオードであるから、図に示すようにある電圧,Velonを超えると急激にその電流が立上る(ターンオンする)ことが判る。一般にはこのOLED電流特性は、入力電圧に対して6乗から7乗程度の関数になると報告されている。

【0018】

さてここで図3に示したインバータ回路 3の特性と、図2に示したOLED素子4の特性を組み合わせることを考える。即ちインバータ回路 3の出力電圧,VoutをOLED素子4の入力電圧,Voledと置く。更に図3に示すように、Velonを”A”よりも大きく、かつインバータ回路 3の出力ハイレベルよりも小さい(インバータ回路 3の出力範囲内でOLED素子4がターンオンする)ように、nチャネルソース線 24及びpチャネルソース線 23の電圧を設定する。このとき出力,Velonに対応する入力をVonとすると、OLED素子4の電流,Ioledはインバータ回路 3の入力電圧,Von近傍で急激に立上るであろうことが理解される。

【0019】

図4はインバータ回路 3の入力電圧,Vinを横軸に、OLED素子4の電流,Ioledを縦軸に取って、この様子を示したものである。Ioledは、Vrstより若干低い入力電圧であるVonにおいて、ほぼ矩形に近い立上りでターンオンする。またインバータ回路 3の立上り特性が十分に急峻ならば、このVrstとVonの値は非常に近い値になり、近似的には同電圧と見なすことができるようになる。

【0020】

次に本実施例の全体の動作を、図5を用いて説明する。

【0021】

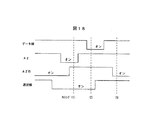

図5は本実施例におけるn行目のゲート線6及びリセット線10と、(n+1)行目のゲート線6及びリセット線10、更に任意の信号線7の動作波形を、2行分の画素の書込み期間(二水平期間)に渡って示したものである。

【0022】

一水平期間の前半は表示信号の「書込み期間」であり、図中に示したタイミング(1)で、選択された行(ここではn行目)のゲート線6及びリセット線10が立上る。なおここで本実施例では入力TFT 1、リセットTFT 9はnチャネルなので、ゲート線6及びリセット線10は上(高電圧側)がオン、下(低電圧側)がオフに対応し、選択された行の入力TFT 1及びリセットTFT 9がオンになる。リセットTFT 9がオンになると、先にインバータ回路 3の動作説明で述べたように、インバータ回路 3の入出力電圧はVrstにリセットされ、この電圧は記憶コンデンサ2の一端に印加される。またこのとき同時に各信号線7には所定の表示信号電圧が入力されており、この表示信号電圧はオンになった入力TFT 1を通して記憶コンデンサ2の他端に印加される。この後リセット線10の電圧が下がってリセットTFT 9はオフするが、以上の動作によって、選択された行の画素の各記憶コンデンサ2には、信号線7から上記表示信号電圧が入力されたときにインバータ回路 3の入力にVrstを入力するように、必要な信号電荷が書込まれたことになる。なお前述のようにインバータ回路 3の立上り特性が十分に急峻ならば、VrstとVonの値は極めて近い値になり、近似的に同電圧と見なすことができる。即ちこの画素は、信号線7から上記の表示信号電圧が入力されると、インバータ回路3の出力がほぼVelonとなってOLED素子4がターンオンないしターンオフすることになる。なお図5では簡略化のために、このVrstとVonの値を近似的に同電圧として示してある。

【0023】

一水平期間の後半は選択された画素行のみならず、全画素に対する「駆動期間」である。図5に示したタイミング(2)では、全画素のゲート線6が立上り、全画素の入力TFT 1がオン状態になる。またこの期間には、各信号線7には先程画素に書込まれた表示信号電圧レベルを含む範囲で、三角波状の画素駆動電圧が印加、掃引される。入力TFT 1がオンしているため、この画素駆動電圧は全ての画素の各記憶コンデンサ2に入力されるが、ここで三角波状の画素駆動電圧が、予め書込まれていた表示信号電圧に一致した画素から順番に、インバータ回路 3の入力電圧はVrst(=Von)となり、その画素のOLED 4がターンオン(点灯)する。これによって本実施例においては、予め書込まれた表示信号電圧に基づき、各画素の点灯時間を変調することで、多階調の画素点灯表示が可能である。このとき画素駆動電圧の電圧掃引範囲の下端を、最も低電圧の表示信号電圧レベルと一致させておけば、最も低電圧の表示信号電圧レベルが書込まれた画素だけはOLED 4が全く点灯しない黒レベルとすることができる。但し現実にはノイズ等の影響もあるため、全く点灯しない黒レベルを保証して表示パネルのコントラストを十分に大きくするためには、画素駆動電圧の掃引電圧範囲の下端は、最も低電圧の表示信号電圧レベルより若干高い電圧で止めておくことが望ましい。

【0024】

なお本実施例によれば、OLED 4を駆動するインバータ回路 3を構成するnチャネル多結晶Si TFT 32及びpチャネル多結晶Si TFT 31の特性ばらつきは、殆んど輝度むらを生じることはなく、画素間の表示特性ばらつき発生を回避することができる。なぜならばリセットTFT 9がオンした際のインバータ回路 3入力電圧,Vrstは、先に述べたようにTFT特性のばらつきとは無関係に、近似的にVonとみなすことができるからである。このための前提条件は、インバータ回路 3の出力立上り特性が十分に急峻ならば満足される。これはnチャネル多結晶Si TFT 32及びpチャネル多結晶Si TFT 31の相互コンダクタンスを、各TFTのドレインコンダクタンスやOLED 4の入力コンダクタンスよりも十分に大きくなるように、各素子のパラメータやその動作条件を設計することで達成可能である。

【0025】

次に本実施例の具体的な構造について、図7,図8を用いて説明する。

【0026】

図7は本実施例の画素 5のレイアウト図である。縦方向に信号線7、nチャネルソース線 24、pチャネルソース線 23が低抵抗Al配線で設けられており、横方向にはゲート線6及びリセット線10がゲート配線で設けられている。信号線7とゲート線6の交点には低温多結晶Si TFTプロセスで作られた入力TFT 1が構成されており、入力TFT 1の他端はそのまま横方向に延在して記憶コンデンサ2の一方の電極を構成している。記憶コンデンサ2の対向電極は、そのままnチャネル低温多結晶Si TFT 32及びpチャネル低温多結晶Si TFT 31のゲート電極になっている。ここで既に述べたように、nチャネル低温多結晶Si TFT 32及びpチャネル低温多結晶Si TFT 31のソースはそれぞれnチャネルソース線 24及びpチャネルソース線 23に接続されており、nチャネル低温多結晶Si TFT 32及びpチャネル低温多結晶Si TFT 31のドレインは共通にOLED素子4に入力している。またこのドレイン端子は同時に、リセット線10でゲートが構成されているリセットTFT 9の一端にも接続されており、リセットTFT 9の他端は前述の記憶コンデンサ2の対向電極に接続されている。なおここでOLED素子4における共通接地端子は、各画素間で共通に接続されかつ接地されているが、図面の簡略化のために図7では省略した。

【0027】

図8は、図7に示したライン”L−M−N”における断面図である。既に述べたように入力TFT 1のチャネルを構成する多結晶Siアイランドは横方向に延在し、nチャネル低温多結晶Si TFT 32及びpチャネル低温多結晶Si TFT 31のゲート電極との間で記憶コンデンサ2を構成している。ここで記憶コンデンサ2はTFTのゲート容量で構成されているため、記憶コンデンサ2のチャネルが構成されるように、常にゲート容量の両電極間にはVth以上の電圧が印加される条件の下で駆動されている。なお記憶コンデンサ2は、予め十分に大きい値に設計しておくことが重要である。これはnチャネル低温多結晶Si TFT 32及びpチャネル低温多結晶Si TFT 31のゲート電極入力容量が、ミラー効果によって見かけ上極めて大きくなることに起因する。図8に示したように、上記構造は透明なガラス基板33上に構成され、OLED素子4からの発光を基板下方に取り出せるようにしている。

【0028】

なおシフトレジスタと切替スイッチで構成されるゲート駆動回路22、6bitのDA変換回路で構成される信号駆動回路21、外部から入力される三角波をバッファする三角波入力回路20からなる周辺駆動回路も、図8に示した画素部と同様の低温多結晶Si TFT回路で構成されている。これらの回路形態は一般に知られている技術で実現が可能であるため、ここではその説明は省略する。

さて以上に述べた本実施例においては、本発明の主旨を損なわない範囲でいくつもの変更が可能である。例えば本実施例ではTFT基板としてガラス基板33を用いたが、これを石英基板や透明プラスチック基板等の他の透明絶縁基板に変更することも可能であるし、またOLED素子4の発光を上面に取り出すようにすれば、不透明基板を用いることも可能である。

或いは各TFTに関しても本実施例では入力TFT 1やリセットTFTにnチャネルを用いたが、駆動波形を適宜変更すれば、これらをpチャネルやCMOSスイッチに変更することも可能である。インバータ回路 3に関しても、ここで用いたようなCMOSインバータに限る必要はなく、例えばnチャネルTFTを定電流源回路に変更する等の変形が可能であることは言うまでもない。

また本実施例においては、先に述べたように記憶コンデンサ2の構造をTFTゲート構造と同一のプロセスで形成することによって、製造プロセスの簡略化による低コスト化を実現している。しかしながら本発明の目的とする効果を得るためには、必ずしもこれらの各構成要素の共通化を図る必要はなく、記憶コンデンサ2のゲート下に高濃度不純物を導入したりすることや、或いは記憶コンデンサ2の構造をゲート層と配線層で形成する等の変更も可能である。

また本実施例の説明においては、画素数やパネルサイズ等に関しては敢えて言及していない。これは本発明が特にこれらのスペックないしフォーマットに制限されるものではないためである。また今回は表示信号電圧を64階調(6bit)のディスクリートな階調電圧としているが、これを例えばアナログ電圧にすることも容易であり、或いは信号電圧階調数も特に特定の値に制限されるものではない。またOLED素子4における共通端子の電圧を接地電圧としているが、この電圧値も所定の条件の下で変更可能であることは言うまでもない。

【0029】

また本実施例ではゲート駆動回路22、信号駆動回路21、三角波入力回路20からなる周辺駆動回路は、低温多結晶Si TFT回路で構成している。しかしながらこれらの周辺駆動回路あるいはその一部分を単結晶LSI(Large Scale Integrated circuit)回路で構成して実装することも、本発明の範囲内で可能である。

【0030】

本実施例では、発光デバイスとしてOLED素子4を用いることとした。しかしこれに代えてその他の無機を含む一般の発光素子を用いても、本発明を実現することが可能であることは明らかである。

【0031】

なお発光デバイスを赤、緑、青の3種類の色毎に作り分けてカラー化を実現する場合には、色バランスを取るために各発光デバイスの面積や、駆動電圧条件を変化させることが好ましい。ここで駆動電圧条件を変化させる場合、本実施例においてはnチャネルソース線24及びpチャネルソース線23の電圧を色毎に変化させて調整することができる。この場合、配線の簡略化の観点からは、特に3色はストライプ配置することが望ましい。また本実施例でOLED素子4の共通端子電圧を接地電圧としたことに対しても、OLED素子4の共通端子を赤、緑、青の3種類の色毎に作り分け、それぞれ適当な電圧で駆動することも可能である。更にこの駆動電圧を表示条件や表示の絵柄等によって適当に調整することで、色温度補正機能を実現することも可能である。

以上の種々の変更等は、本実施例に限らず以下のその他の実施例においても、基本的に同様に適用可能である。

(第二の実施例)

以下図9を用いて、本発明の第二の実施例に関して説明する。

本実施例の構成及び動作は、第一の実施例では図5に示した信号線7の動作波形が異なっていることを除けば、基本的に第一の実施例のそれと同一である。従ってここでは構成及びその動作の記載は省略し、本実施例の特徴である信号線7の動作波形に関して以下説明する。

第9は、本第二の実施例における信号線7の動作波形を示したものである。ここで第一の実施例では駆動期間中の画素駆動電圧掃引波形は、水平期間毎に同一波形の繰返しであったが、本第二の実施例では、画素駆動電圧掃引波形は3つの部分に分割されており、三水平期間を合せて一回の三角波を構成している。

これによって本実施例においては三角波の駆動周波数が低減されるため、三角波入力回路20の出力インピーダンスをより大きく設計することができ、駆動消費電力の低減が可能となっている。

なお本実施例では三角波の掃引周波数を水平期間の3倍としたが、これは一般的には任意のn倍とすることが可能であり、全画素の書換え期間に相当するフレーム周波数としたり、さらにフレーム周波数の任意のm倍とすること、或いは三角波の掃引周波数を表示画像の内容(静止画か動画か、など)やその他の使い方によって可変とすることも可能である。但し三角波の掃引周波数をあまり遅くしすぎた場合、或いは水平期間の自然数倍から外した場合には、視覚上でフリッカとなってしまうことがあるので注意が必要である。

【0032】

また三角波の掃引周波数をフレーム周波数以下とした場合は、プラズマディスプレイ(PDP, Plasma Display Panel)で問題になったと同様な擬似輪郭雑音が生じる可能性がある。このことから三角波の掃引周波数はフレーム周波数以上、できればフレーム周波数の2倍以上であることが望ましい。

(第三の実施例)

以下図10を用いて、本発明の第三の実施例に関して説明する。

本実施例の構成及び動作は、第一の実施例では図5に示した信号線7の動作波形が異なっていることを除けば、基本的に第一の実施例のそれと同一である。従ってここでも構成及びその動作の記載は省略し、本実施例の特徴である信号線7の動作波形に関して以下説明する。

第10は、本第三の実施例における信号線7の動作波形を示したものである。ここで第一の実施例では駆動期間中の画素駆動電圧掃引波形は連続して変化する三角波であったが、本第三の実施例では書込み信号は4階調(2bit)であると同時に、画素駆動電圧掃引波形も4階調の階段波形となっている。なおここでは特に、4階調の各書込み信号電圧レベルは、画素駆動電圧掃引波形における階段波形の各階段電圧レベルの丁度中間値になるように設定されている。

これによって本実施例においては、雑音等に起因する微妙な信号線電圧の変化がOLED素子4の発光に反映されることが殆んど無くなるため、よりS/Nの良い表示を得ることができる。4階調の各書込み信号電圧レベルは、画素駆動電圧掃引波形における階段波形の各階段電圧レベルの丁度中間値になるように設定されているため、各階段電圧レベルの半分以下の雑音では、対応する電圧レベルがずれてしまうことはないからである。

なお本実施例では書込み信号及び画素駆動電圧掃引波形を4階調(2bit)としたが、明らかに本発明はその信号階調数を制限するものではない。例えば同様の考え方から64階調(6bit)等、任意の階調表示が実現可能である。但し先程のS/Nの考え方からは、各階調間の電圧差が小さくなるほど雑音に対しては弱くなるため注意が必要である。

【0033】

なお本実施例を含め、以上の実施例では画素駆動電圧掃引波形は基本的に線形であった。しかしながら上記のS/Nの観点や、或いはγ特性の観点から、非線型の画素駆動電圧掃引を行うことも必要に応じて可能である。

(第四の実施例)

以下図11を用いて、本発明の第四の実施例に関して説明する。

本実施例の構成及び動作は、第一の実施例では図6に示した画素構造が異なっていることを除けば、基本的に第一の実施例のそれと同一である。従ってここでも全体の構成及びその動作の記載は省略し、本実施例の特徴である画素構造に関して以下説明する。

図11は第四の実施例における一画素の構成図である。

画素発光体としてのOLED素子44を有する画素45は、ゲート線46、信号線47、リセット線50、pチャネルソース線 54を介して周辺の駆動回路に接続されている。信号線47はゲート線46で制御される入力TFT 41を介して記憶コンデンサ42に接続されており、記憶コンデンサ42の他端はリセット線50で制御されるリセットTFT 49の一端とpチャネル多結晶Si TFT 51のゲート端子に接続されている。リセットTFT 49の他端とpチャネル多結晶Si TFT 51の一端は共通に、OLED素子44を介して共通接地端子に接地されている。またpチャネル多結晶Si TFT 51のゲートは補助容量40を介してpチャネル多結晶Si TFT 51のソースに接続されており、pチャネル多結晶Si TFT 51のソースはpチャネルソース線 54に接続されている。また本実施例でも縦方向配線を低抵抗メタルで、横方向配線をゲートメタルで構成したため、信号線47とpチャネルソース線 54はより低抵抗な縦方向配線で実現されている。ここで本第四の実施例においては、第一の実施例におけるインバータ回路 3は等価的に、OLED素子44を負荷としたpチャネル多結晶Si TFT 51で構成されていることになる。なお補助容量40は、OLED素子44を負荷としたpチャネル多結晶Si TFT 51で構成されるインバータ回路の入力容量値を安定化させるために付加されたものである。但し等価インバータ回路の立上り特性が安定していれば、補助容量40はなくとも構わない。

本第四の実施例の画素部の動作は、基本的には第一の実施例のそれと同様である。但し本実施例においては入力TFT 41とリセットTFT 49はnチャネルではなくpチャネル低温多結晶Si TFTで構成されているため、ゲート線46とリセット線50の駆動波形が第一の実施例とは反転していることに注意が必要である。

本実施例においては、画素45を構成するTFTの数が減っており、より高歩留りで低価格の表示パネルを提供することが可能である。また更に画素にnチャネル多結晶Si TFTが存在しないことから、周辺回路を外付けLSIで構成したり、或いは同様にnチャネル多結晶Si TFTを用いずにpチャネルの回路のみで構成すれば、nチャネル多結晶Si TFTを形成せずに表示パネルを製造することも可能である。この場合はnチャネル形成工程が不要になるため、より低価格な表示パネルを実現することができる。

(第五の実施例)

以下図12を用いて、本発明の第五の実施例に関して説明する。

本実施例の構成及び動作は、第一の実施例では図6に示した画素構造が異なっていることを除けば、基本的に第一の実施例のそれと同一である。従ってここでも全体の構成及びその動作の記載は省略し、本実施例の特徴である画素構造に関して以下に説明する。

図12は第五の実施例における一画素の構成図である。

画素発光体としてのOLED素子64を有する画素65は、ゲート線66、信号線67、リセット線70、nチャネルソース線 73及びpチャネルソース線 74を介して周辺の駆動回路に接続されている。信号線67はゲート線66で制御される入力TFT 61を介して記憶コンデンサ62に接続されており、記憶コンデンサ62の他端はリセット線70で制御されるリセットTFT 69の一端とpチャネル多結晶Si TFT 71及びnチャネル多結晶Si TFT 72のゲート端子に接続されている。リセットTFT 69の他端とpチャネル多結晶Si TFT 71及びnチャネル多結晶Si TFT 72のドレインは共通に、OLED駆動TFT70のゲートに入力し、OLED駆動TFT70のドレインはOLED素子64を介して共通接地端子に接地されている。またpチャネル多結晶Si TFT 71及びOLED駆動TFT70のソースは共にpチャネルソース線 74に接続され、nチャネル多結晶Si TFT 72のソースはnチャネルソース線 73に接続されている。また本実施例でも縦方向配線を低抵抗メタルで、横方向配線をゲートメタルで構成したため、、信号線67とnチャネルソース線 73及びpチャネルソース線 74はより低抵抗な縦方向配線で実現されている。ここで本第五の実施例においては、第一の実施例におけるインバータ回路 3は等価的に、OLED駆動TFT70をバッファとして有していることになる。

本第五の実施例の画素部の動作は、基本的には第一の実施例のそれと同様であるので、ここでは説明は省略する。

本実施例においては、pチャネル多結晶Si TFT 71及びnチャネル多結晶Si TFT 72で構成されるインバータ回路とOLED素子64とは、OLED駆動TFT70によるバッファで隔てられているため、インバータ回路はOLED素子64の特性とは無関係に駆動される。従ってインバータ回路の動作安定性が増してより立上り特性の良いインバータ回路を実現することができ、その結果画素間の発光特性のばらつきをより低減することができる。

(第六の実施例)

以下図13、図14を用いて、本発明の第六の実施例に関して説明する。

本実施例の構成及び動作は、第一の実施例では図6に示した画素構造が異なっていることを除けば、基本的に第一の実施例のそれと同一である。従ってここでも全体の構成及びその動作の記載は省略し、本実施例の特徴である画素構造に関して以下説明する。

図13は第六の実施例における一画素の構成図である。

画素発光体としてのOLED素子84を有する画素85は、ゲート線86、信号線87、リセット線90、pチャネルソース線 94、駆動信号線96、駆動ゲート線97を介して周辺の駆動回路に接続されている。信号駆動回路21(図示せず)から伸びる信号線87はゲート線86で制御される入力TFT 81を介して記憶コンデンサ82に接続されており、同時に三角波入力回路20(図示せず)から伸びる駆動信号線96も駆動ゲート線97で制御される駆動入力TFT 98を介して同様に記憶コンデンサ82に接続されている。記憶コンデンサ82の他端はリセット線90で制御されるリセットTFT 89の一端とpチャネル多結晶Si TFT 91のゲート端子に接続されている。リセットTFT 89の他端とpチャネル多結晶Si TFT 91の一端は共通に、OLED素子84を介して共通接地端子に接地されている。またpチャネル多結晶Si TFT 91のソースはpチャネルソース線 94に接続されている。また本実施例でも縦方向配線を低抵抗メタルで、横方向配線をゲートメタルで構成したため、信号線87、駆動信号線96、pチャネルソース線 94はより低抵抗な縦方向配線で実現されている。ここで本第六の実施例においては、第一の実施例におけるインバータ回路 3が等価的に、OLED素子84を負荷としたpチャネル多結晶Si TFT 91で構成されていることは、第四の実施例と同様である。

本第六の実施例の画素部の動作は、基本的には第一の実施例のそれと同様である。但し本実施例においては記憶コンデンサ82への入力経路は、信号線87を経由するものと駆動信号線96を経由するものの二通りが使い分けられている。以下これに関して図14を用いて説明する。

図14は信号線87及び駆動信号線96の駆動波形である。選択された画素行では、「書込み期間」に選択された行のゲート線86がオンし、信号線87と入力TFT 81を経由して表示信号電圧が書込まれる。一方選択されていないその他の画素行では、常に全ての駆動ゲート線97がオンし、駆動信号線96と駆動入力TFT 98を経由して三角波である画素駆動電圧が入力し、各画素に予め書込まれていた表示信号に対応してOLED素子84が発光する。

【0034】

本実施例においては、画素に対して表示信号電圧と画素駆動電圧のいずれかがそれぞれ、信号線87と駆動信号線96という別々の配線を経由して入力される。このために選択された画素に表示信号電圧が書込まれている期間内にも、書込み選択されていない画素は常に発光駆動されることが可能であり、同一の電流駆動条件では表示輝度が向上する。また選択された画素行では、「書込み期間」を最大で一水平期間にまで延長することが可能である。従って書込みの時定数を拡大することができ、表示信号電圧書込み時の消費電力低減も可能である。

(第七の実施例)

以下図15を用いて、本発明における第七の実施例に関して説明する。

図15は第七の実施例である画像表示端末(PDA:Personal Digital Assistants)100の構成図である。

無線インターフェース(I/F)回路101には、圧縮された画像データ等が外部からbluetooth規格に基づく無線データとして入力し、無線I/F回路101の出力はI/O(Input/Output)回路102を介してデータバス103に接続される。データバス103にはこの他にマイクロプロセサ104、表示パネルコントローラ105、フレームメモリ106等が接続されている。更に表示パネルコントローラ105の出力はOLED表示パネル110に入力しており、OLED表示パネル110には画素マトリクス111、ゲート駆動回路22、信号駆動回路21等が設けられている。なお画像表示端末100には更に、三角波発生回路112、電源107が設けられており、三角波発生回路112の出力はOLED表示パネル110に入力している。なおここでOLED表示パネル110は、パネル内に三角波入力回路20が設けられていないことを除けば、先に延べた第一の実施例と同一の構成および動作を有しているので、その内部の構成及び動作の記載はここでは省略する。

以下に本第七の実施例の動作を説明する。始めに無線I/F回路101は命令に応じて圧縮された画像データを外部から取り込み、この画像データをI/O回路102を介してマイクロプロセサ104及びフレームメモリ106に転送する。マイクロプロセサ104はユーザからの命令操作を受けて、必要に応じて画像表示端末100を駆動し、圧縮された画像データのデコードや信号処理、情報表示を行う。ここで信号処理された画像データは、フレームメモリ106に一時的に蓄積される。

ここでマイクロプロセサ104が表示命令を出した場合には、その指示に従ってフレームメモリ106から表示パネルコントローラ105を介してOLED表示パネル110に画像データが入力され、画素マトリクス111は入力された画像データをリアルタイムで表示する。このとき表示パネルコントローラ105は、同時に画像を表示するために必要な所定のタイミングパルスを出力し、これと同期して三角波発生回路112は三角波状の画素駆動電圧を出力する。なおOLED表示パネル110がこれらの信号を用いて、画素マトリクス111に6ビット画像データから生成された表示データをリアルタイムで表示することに関しては、第一の実施例で述べたとおりである。なおここで電源107には二次電池が含まれており、これらの画像表示端末100全体を駆動する電力を供給する。

本実施例によれば、多階調表示が可能であり、かつまた画素間での表示特性ばらつきが十分に小さい画像表示端末100を提供することができる。

なお本実施例では画像表示デバイスとして、第一の実施例で説明したOLED表示パネルと類似のパネルを用いたが、これ以外のその他の本発明の実施例に記載されたような種々の表示パネルを用いることが可能であることは明らかである。

【0035】

【発明の効果】

本発明によれば、多階調表示が可能であり、かつまた画素間での表示特性ばらつきが十分に小さい画像表示装置を提供することができる。

【図面の簡単な説明】

【図1】第一の実施例であるOLED表示パネルの構成図。

【図2】第一の実施例におけるOLED素子の電圧−電流特性図。

【図3】第一の実施例におけるインバータ回路の入力電圧−出力電圧特性図。

【図4】第一の実施例におけるインバータ回路の入力電圧−電流特性図。

【図5】第一の実施例におけるゲート線、リセット線、信号線動作波形図。

【図6】第一の実施例における一画素の構成図。

【図7】第一の実施例における画素レイアウト図。

【図8】第一の実施例における画素断面図。

【図9】第二の実施例における信号線の動作波形図。

【図10】第三の実施例における信号線の動作波形図。

【図11】第四の実施例における画素の構成図。

【図12】第五の実施例における画素の構成図。

【図13】第六の実施例における画素の構成図。

【図14】第六の実施例における信号線及び駆動信号線の駆動波形図。

【図15】第七の実施例における画像表示端末の構成図。

【図16】従来の技術を用いた発光表示デバイスの構成図。

【図17】第二の従来の技術を用いた発光表示デバイスの構成図。

【図18】第二の従来の技術を用いた発光表示デバイスの動作説明図。

【符号の説明】

1…入力TFT、2…記憶コンデンサ、3…インバータ回路、4…OLED素子、5…画素、6…ゲート線、7…信号線、10…リセット線、20…三角波入力回路、21…信号駆動回路、22…ゲート駆動回路、33…ガラス基板。

Claims (32)

- 複数の画素領域により構成された表示部と、該画素領域に表示信号電圧を入力するための信号線を有する画像表示装置において、

上記信号線から第一の容量の一端に表示信号電圧を入力するために設けられた第一のスイッチ手段と、

該第一の容量の他端に入力が接続された入力電圧反転出力手段と、

該入力電圧反転出力手段の出力によって制御された画素発光体である発光手段と、

該入力電圧反転出力手段の入力端と出力端の間に設けられた第二のスイッチ手段とを上記複数の画素領域の少なくとも1つに有し、更に、

上記表示信号電圧を含む所定の電圧範囲内で掃引される画素駆動電圧を発生するための画素駆動電圧発生手段と、

上記画素駆動電圧を上記画素における上記第一の容量の一端に入力するための画素駆動電圧入力手段と、を有することを特徴とする画像表示装置。 - 上記発光手段は、発光ダイオード素子であることを特徴とする請求項1記載の画像表示装置。

- 上記発光ダイオード素子は、有機発光ダイオード(OLED, Organic Light Emitting Diode)素子であることを特徴とする請求項2記載の画像表示装置。

- 上記各スイッチ手段及び入力電圧反転出力手段は、多結晶Si-TFT(Thin-Film-Transistor)を用いて透明基板上に設けられていることを特徴とする請求項1記載の画像表示装置。

- 上記入力電圧反転出力手段は、CMOS(Complementary Metal Oxide Semiconductor)インバータ回路で構成されていることを特徴とする請求項1記載の画像表示装置。

- 上記入力電圧反転出力手段は、多結晶Si-TFT(Thin-Film-Transistor)と、負荷となる発光ダイオード素子で構成されていることを特徴とする請求項2記載の画像表示装置。

- 上記多結晶Si-TFTのゲートとソースの間には、更に第二の容量が設けられていることを特徴とする請求項6記載の画像表示装置。

- 上記画素駆動電圧発生手段が発生する、所定の電圧範囲内でスイープする画素駆動電圧は、三角波であることを特徴とする請求項1記載の画像表示装置。

- 上記画素駆動電圧発生手段が発生する、所定の電圧範囲内で掃引される画素駆動電圧は、階段波形であることを特徴とする請求項1記載の画像表示装置。

- 上記表示信号電圧は、該階段波形において離散的に分布する画素駆動各電圧の、隣接する2つの電圧の実質的中間の値をとることを特徴とする請求項9記載の画像表示装置。

- 該信号線と第一のスイッチ手段は、上記画素駆動電圧入力手段を兼ねることを特徴とする、特許請求の範囲第1項記載の画像表示装置。

- 上記画素駆動電圧入力手段は、該信号線と並行に設けられた画素駆動電圧線と、該画素駆動電圧線と該第一の容量の一端との間に設けられた第三のスイッチ手段で構成されることを特徴とする請求項1記載の画像表示装置。

- 上記表示信号電圧は、多結晶Si-TFT(Thin-Film-Transistor)を用いて構成したD-A変換器によって発生させたものであることを特徴とする請求項4記載の画像表示装置。

- 上記表示信号電圧は、単結晶Si-LSI(Large Scale Integrated circuit)によって発生させたものであることを特徴とする請求項4記載の画像表示装置。

- 上記第一の容量は、多結晶Si-TFTのゲート絶縁膜容量で構成されていることを特徴とする請求項4記載の画像表示装置。

- 上記画素駆動電圧は、画素一行分の表示信号電圧書込みタイミングと同期して掃引することを特徴とする請求項1記載の画像表示装置。

- 上記画素駆動電圧は、画素複数行分の表示信号電圧書込みタイミングと同期して掃引することを特徴とする請求項1記載の画像表示装置。

- 上記画素駆動電圧は、全画素の表示信号電圧書込みタイミングと同期して掃引することを特徴とする請求項1記載の画像表示装置。

- 上記画素駆動電圧の掃引繰返し周波数は、可変であることを特徴とする請求項1記載の画像表示装置。

- 上記画素駆動電圧の印加期間は、画素一行分の表示信号電圧の書込み期間と交互に設けられていることを特徴とする請求項1記載の画像表示装置。

- 複数の画素領域により構成された表示部と、外部から取り込まれた表示信号を記憶し、更にそのデータ処理を行う表示信号処理部と、該画素領域に表示信号電圧を入力するための信号線を有する画像表示装置において、

上記信号線から第一の容量の一端に表示信号電圧を入力するために設けられた第一のスイッチ手段と、該第一の容量の他端に入力が接続された入力電圧反転出力手段と、

該入力電圧反転出力手段の出力によって制御された画素発光体である発光手段と、

該入力電圧反転出力手段の入力端と出力端の間に設けられた第二のスイッチ手段とを上記複数の画素領域の少なくとも一つに有し、更に、

上記表示信号電圧を含む所定の電圧範囲内でスイープする画素駆動電圧を発生するための画素駆動電圧発生手段と、

該画素駆動電圧を上記画素における上記第一の容量の一端に入力するための画素駆動電圧入力手段と、を有することを特徴とする画像表示装置。 - 複数の画素により構成された表示部と、

該画素内に画素発光体である発光手段を有する画像表示装置において、

該発光手段の点灯及び非点灯を制御するための点灯制御手段と、

第一の端子を該点灯制御手段に接続された容量と、

表示信号電圧を生成するための表示信号電圧生成手段と、

所定の画素駆動電圧を生成するための画素駆動電圧生成手段とを有し、

該容量の第二の端子に該表示信号電圧と該画素駆動電圧とを二者択一的に印加可能としたことを特徴とする画像表示装置。 - 上記発光手段は、発光ダイオード素子であることを特徴とする請求項22記載の画像表示装置。

- 上記発光ダイオード素子は、有機発光ダイオード(OLED, Organic Light Emitting Diode)素子であることを特徴とする請求項23記載の画像表示装置。

- 上記画素駆動電圧発生手段が発生する、所定の電圧範囲内でスイープする画素駆動電圧は、三角波であることを特徴とする請求項22記載の画像表示装置。

- 上記画素駆動電圧発生手段が発生する、所定の電圧範囲内で掃引される画素駆動電圧は、階段波形であることを特徴とする請求項22記載の画像表示装置。

- 上記表示信号電圧は、該階段波形において離散的に分布する画素駆動各電圧の、隣接する2つの電圧の実質的中間の値をとることを特徴とする請求項26記載の画像表示装置。

- 上記画素駆動電圧は、画素一行分の表示信号電圧書込みタイミングと同期して掃引することを特徴とする請求項22記載の画像表示装置。

- 上記画素駆動電圧は、画素複数行分の表示信号電圧書込みタイミングと同期して掃引することを特徴とする請求項22記載の画像表示装置。

- 上記画素駆動電圧は、全画素の表示信号電圧書込みタイミングと同期して掃引することを特徴とする請求項22記載の画像表示装置。

- 上記画素駆動電圧の掃引繰返し周波数は、可変であることを特徴とする請求項22記載の画像表示装置。

- 上記画素駆動電圧の印加期間は、画素一行分の表示信号電圧の書込み期間と交互に設けられていることを特徴とする請求項22記載の画像表示装置。

Priority Applications (12)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001187478A JP4982014B2 (ja) | 2001-06-21 | 2001-06-21 | 画像表示装置 |

| TW090130964A TW530277B (en) | 2001-06-21 | 2001-12-13 | Image display |

| US10/075,591 US6876345B2 (en) | 2001-06-21 | 2002-02-15 | Image display |

| KR1020020008709A KR100842511B1 (ko) | 2001-06-21 | 2002-02-19 | 화상 표시 장치 |

| CN2006101017043A CN1877681B (zh) | 2001-06-21 | 2002-02-20 | 图像显示装置 |

| CNB021046980A CN1220168C (zh) | 2001-06-21 | 2002-02-20 | 图像显示装置 |

| CN2005100039303A CN1630437B (zh) | 2001-06-21 | 2002-02-20 | 图像显示装置 |

| US10/965,864 US7277072B2 (en) | 2001-06-21 | 2004-10-18 | Image display |

| US11/095,615 US7142180B2 (en) | 2001-06-21 | 2005-04-01 | Image display |

| US11/859,414 US8031144B2 (en) | 2001-06-21 | 2007-09-21 | Image display |

| US13/195,588 US8159427B2 (en) | 2001-06-21 | 2011-08-01 | Image display |

| US13/412,771 US8633878B2 (en) | 2001-06-21 | 2012-03-06 | Image display |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001187478A JP4982014B2 (ja) | 2001-06-21 | 2001-06-21 | 画像表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008235865A Division JP5015887B2 (ja) | 2008-09-16 | 2008-09-16 | 画像表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003005709A JP2003005709A (ja) | 2003-01-08 |

| JP2003005709A5 JP2003005709A5 (ja) | 2008-10-30 |

| JP4982014B2 true JP4982014B2 (ja) | 2012-07-25 |

Family

ID=19026758

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001187478A Expired - Fee Related JP4982014B2 (ja) | 2001-06-21 | 2001-06-21 | 画像表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (5) | US6876345B2 (ja) |

| JP (1) | JP4982014B2 (ja) |

| KR (1) | KR100842511B1 (ja) |

| CN (3) | CN1220168C (ja) |

| TW (1) | TW530277B (ja) |

Families Citing this family (138)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8633878B2 (en) | 2001-06-21 | 2014-01-21 | Japan Display Inc. | Image display |

| JP4982014B2 (ja) | 2001-06-21 | 2012-07-25 | 株式会社日立製作所 | 画像表示装置 |

| US6777885B2 (en) * | 2001-10-12 | 2004-08-17 | Semiconductor Energy Laboratory Co., Ltd. | Drive circuit, display device using the drive circuit and electronic apparatus using the display device |

| US7365713B2 (en) | 2001-10-24 | 2008-04-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| JP3923341B2 (ja) | 2002-03-06 | 2007-05-30 | 株式会社半導体エネルギー研究所 | 半導体集積回路およびその駆動方法 |

| KR100870004B1 (ko) * | 2002-03-08 | 2008-11-21 | 삼성전자주식회사 | 유기 전계발광 표시 장치와 그 구동 방법 |

| GB0209502D0 (en) * | 2002-04-25 | 2002-06-05 | Cambridge Display Tech Ltd | Display driver circuits |

| JP3972359B2 (ja) * | 2002-06-07 | 2007-09-05 | カシオ計算機株式会社 | 表示装置 |

| TWI220046B (en) * | 2002-07-04 | 2004-08-01 | Au Optronics Corp | Driving circuit of display |

| JP4019843B2 (ja) * | 2002-07-31 | 2007-12-12 | セイコーエプソン株式会社 | 電子回路、電子回路の駆動方法、電気光学装置、電気光学装置の駆動方法及び電子機器 |

| JP4467909B2 (ja) * | 2002-10-04 | 2010-05-26 | シャープ株式会社 | 表示装置 |

| GB0224277D0 (en) * | 2002-10-18 | 2002-11-27 | Koninkl Philips Electronics Nv | Electroluminescent display devices |

| JP2004157250A (ja) | 2002-11-05 | 2004-06-03 | Hitachi Ltd | 表示装置 |

| JP4053433B2 (ja) * | 2003-01-07 | 2008-02-27 | 株式会社半導体エネルギー研究所 | 電流出力daコンバータ回路、表示装置及び電子機器 |

| WO2004066248A1 (ja) | 2003-01-17 | 2004-08-05 | Semiconductor Energy Laboratory Co., Ltd. | 電流源回路、信号線駆動回路及びその駆動方法並びに発光装置 |

| KR100490622B1 (ko) * | 2003-01-21 | 2005-05-17 | 삼성에스디아이 주식회사 | 유기 전계발광 표시장치 및 그 구동방법과 픽셀회로 |

| JP3702879B2 (ja) * | 2003-02-21 | 2005-10-05 | セイコーエプソン株式会社 | 電気光学パネル、その駆動回路及び駆動方法、並びに電子機器 |

| JP4049018B2 (ja) | 2003-05-19 | 2008-02-20 | ソニー株式会社 | 画素回路、表示装置、および画素回路の駆動方法 |

| KR100537545B1 (ko) * | 2003-05-31 | 2005-12-16 | 매그나칩 반도체 유한회사 | 유기전계 발광 디스플레이 패널의 구동방법 |

| JP4049037B2 (ja) * | 2003-06-30 | 2008-02-20 | ソニー株式会社 | 表示装置およびその駆動方法 |

| JP2005099715A (ja) * | 2003-08-29 | 2005-04-14 | Seiko Epson Corp | 電子回路の駆動方法、電子回路、電子装置、電気光学装置、電子機器および電子装置の駆動方法 |

| US7196682B2 (en) * | 2003-09-29 | 2007-03-27 | Wintek Corporation | Driving apparatus and method for active matrix organic light emitting display |

| KR100600865B1 (ko) * | 2003-11-19 | 2006-07-14 | 삼성에스디아이 주식회사 | 전자파차폐수단을 포함하는 능동소자표시장치 |

| JP4804711B2 (ja) | 2003-11-21 | 2011-11-02 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| JP5051565B2 (ja) * | 2003-12-10 | 2012-10-17 | 奇美電子股▲ふん▼有限公司 | 画像表示装置 |

| US7502000B2 (en) * | 2004-02-12 | 2009-03-10 | Canon Kabushiki Kaisha | Drive circuit and image forming apparatus using the same |

| JP5008110B2 (ja) * | 2004-03-25 | 2012-08-22 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| KR100792467B1 (ko) * | 2004-04-16 | 2008-01-08 | 엘지.필립스 엘시디 주식회사 | 디지털 구동을 위한 유기전계 발광 디스플레이 장치 및이의 구동방법 |

| US8581805B2 (en) | 2004-05-21 | 2013-11-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method thereof |

| JP4879515B2 (ja) * | 2004-05-21 | 2012-02-22 | 株式会社半導体エネルギー研究所 | 表示装置及び電子機器 |

| JP2005347516A (ja) * | 2004-06-03 | 2005-12-15 | Jsr Corp | 発光装置 |

| KR101080351B1 (ko) * | 2004-06-22 | 2011-11-04 | 삼성전자주식회사 | 표시 장치 및 그 구동 방법 |

| JP4742527B2 (ja) * | 2004-06-25 | 2011-08-10 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP4834876B2 (ja) * | 2004-06-25 | 2011-12-14 | 京セラ株式会社 | 画像表示装置 |

| KR100578806B1 (ko) * | 2004-06-30 | 2006-05-11 | 삼성에스디아이 주식회사 | 역다중화 장치와, 이를 이용한 표시 장치 및 그 표시 패널 |

| CN100395793C (zh) * | 2004-07-01 | 2008-06-18 | 友达光电股份有限公司 | 有机电致发光显示器 |

| JP2006106141A (ja) * | 2004-09-30 | 2006-04-20 | Sanyo Electric Co Ltd | 有機el画素回路 |

| KR100658297B1 (ko) * | 2004-10-13 | 2006-12-14 | 삼성에스디아이 주식회사 | 화소와 이를 가지는 발광 표시장치 및 그의 구동방법 |

| JP4846999B2 (ja) * | 2004-10-20 | 2011-12-28 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| WO2006059737A1 (en) * | 2004-11-30 | 2006-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method thereof, semiconductor device, and electronic apparatus |

| JP5264014B2 (ja) * | 2004-11-30 | 2013-08-14 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置及び電子機器 |

| KR100604067B1 (ko) * | 2004-12-24 | 2006-07-24 | 삼성에스디아이 주식회사 | 버퍼 및 이를 이용한 데이터 집적회로와 발광 표시장치 |

| JP5177953B2 (ja) * | 2005-01-21 | 2013-04-10 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| US7646367B2 (en) * | 2005-01-21 | 2010-01-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device and electronic apparatus |

| JP2006208743A (ja) * | 2005-01-28 | 2006-08-10 | Sony Corp | 画素回路及び表示装置 |

| JP4897225B2 (ja) | 2005-02-17 | 2012-03-14 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| US8681077B2 (en) * | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| KR100729060B1 (ko) * | 2005-03-31 | 2007-06-14 | 삼성에스디아이 주식회사 | 발광 표시장치 및 그의 구동방법 |

| JP4509004B2 (ja) * | 2005-03-31 | 2010-07-21 | 三星モバイルディスプレイ株式會社 | バッファー及びこれを利用したデータ駆動回路と発光表示装置 |

| US7852298B2 (en) | 2005-06-08 | 2010-12-14 | Ignis Innovation Inc. | Method and system for driving a light emitting device display |

| US7649513B2 (en) * | 2005-06-25 | 2010-01-19 | Lg Display Co., Ltd | Organic light emitting diode display |

| JP4923505B2 (ja) * | 2005-10-07 | 2012-04-25 | ソニー株式会社 | 画素回路及び表示装置 |

| JP4812080B2 (ja) | 2005-10-12 | 2011-11-09 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| KR101324756B1 (ko) | 2005-10-18 | 2013-11-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 그의 구동방법 |

| JP4661557B2 (ja) | 2005-11-30 | 2011-03-30 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| JP5114841B2 (ja) * | 2005-11-30 | 2013-01-09 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| JP2007148222A (ja) * | 2005-11-30 | 2007-06-14 | Hitachi Displays Ltd | 画像表示装置 |

| JP4939045B2 (ja) * | 2005-11-30 | 2012-05-23 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| US8063858B2 (en) | 2005-12-06 | 2011-11-22 | Pioneer Corporation | Active matrix display apparatus and driving method therefor |

| US9489891B2 (en) | 2006-01-09 | 2016-11-08 | Ignis Innovation Inc. | Method and system for driving an active matrix display circuit |

| US7652646B2 (en) * | 2006-04-14 | 2010-01-26 | Tpo Displays Corp. | Systems for displaying images involving reduced mura |

| EP1847981A1 (en) * | 2006-04-18 | 2007-10-24 | Toppoly Optoelectronics Corp. | Systems for displaying images involving reduced mura |

| KR101279115B1 (ko) * | 2006-06-27 | 2013-06-26 | 엘지디스플레이 주식회사 | 유기전계발광표시장치의 화소 회로 |

| EP1873746A1 (en) * | 2006-06-30 | 2008-01-02 | Deutsche Thomson-Brandt Gmbh | Method and apparatus for driving an amoled with variable driving voltage |

| KR100807277B1 (ko) | 2006-08-10 | 2008-02-28 | 삼성전자주식회사 | 표시장치와 그 제조방법 |

| US20080062088A1 (en) * | 2006-09-13 | 2008-03-13 | Tpo Displays Corp. | Pixel driving circuit and OLED display apparatus and electrionic device using the same |

| JP4259556B2 (ja) | 2006-09-13 | 2009-04-30 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP2008170788A (ja) | 2007-01-12 | 2008-07-24 | Hitachi Displays Ltd | 画像表示装置 |

| JP5342111B2 (ja) | 2007-03-09 | 2013-11-13 | 株式会社ジャパンディスプレイ | 有機el表示装置 |

| JP2008268437A (ja) | 2007-04-18 | 2008-11-06 | Hitachi Displays Ltd | 有機el表示装置 |

| JP2008292649A (ja) | 2007-05-23 | 2008-12-04 | Hitachi Displays Ltd | 画像表示装置 |

| GB2453373A (en) * | 2007-10-05 | 2009-04-08 | Cambridge Display Tech Ltd | Voltage controlled display driver for an electroluminescent display |

| JP2009109784A (ja) * | 2007-10-31 | 2009-05-21 | Hitachi Displays Ltd | 画像表示装置 |

| JP5298284B2 (ja) * | 2007-11-30 | 2013-09-25 | 株式会社ジャパンディスプレイ | 画像表示装置とその駆動方法 |

| JP5066432B2 (ja) | 2007-11-30 | 2012-11-07 | 株式会社ジャパンディスプレイイースト | 画像表示装置 |

| JP2009139820A (ja) * | 2007-12-10 | 2009-06-25 | Hitachi Displays Ltd | 有機el表示装置 |

| JP2009168849A (ja) * | 2008-01-10 | 2009-07-30 | Seiko Epson Corp | 電気光学装置、電気光学装置の駆動方法、電子機器 |

| KR100914929B1 (ko) * | 2008-03-12 | 2009-09-01 | 한국과학기술원 | 화소회로 및 그 구동방법 |

| JP5236324B2 (ja) * | 2008-03-19 | 2013-07-17 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | 表示パネル |

| JP5399008B2 (ja) | 2008-06-06 | 2014-01-29 | 株式会社ジャパンディスプレイ | 画像表示装置 |

| US8207918B2 (en) | 2008-06-11 | 2012-06-26 | Hitachi Displays, Ltd. | Image display device having a set period during which a step signal is supplied at different levels to provide a uniform display |

| JP2010060648A (ja) * | 2008-09-01 | 2010-03-18 | Hitachi Displays Ltd | 画像表示装置 |

| JP5260230B2 (ja) | 2008-10-16 | 2013-08-14 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | 表示装置 |

| US9370075B2 (en) | 2008-12-09 | 2016-06-14 | Ignis Innovation Inc. | System and method for fast compensation programming of pixels in a display |

| TWI405166B (zh) * | 2008-12-23 | 2013-08-11 | Univ Nat Chiao Tung | The pixel drive circuit of the display device |

| JP2010249955A (ja) * | 2009-04-13 | 2010-11-04 | Global Oled Technology Llc | 表示装置 |

| JP2011013340A (ja) * | 2009-06-30 | 2011-01-20 | Hitachi Displays Ltd | 発光素子表示装置及び表示方法 |

| JP2011039207A (ja) * | 2009-08-07 | 2011-02-24 | Hitachi Displays Ltd | 表示装置及びその駆動方法 |

| JP2011048101A (ja) * | 2009-08-26 | 2011-03-10 | Renesas Electronics Corp | 画素回路および表示装置 |

| JP2009294676A (ja) * | 2009-09-17 | 2009-12-17 | Hitachi Ltd | 表示装置 |

| JP5491835B2 (ja) * | 2009-12-02 | 2014-05-14 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | 画素回路および表示装置 |

| KR101128831B1 (ko) * | 2009-12-10 | 2012-03-27 | 한양대학교 산학협력단 | 디스플레이 장치 및 디스플레이 장치의 동작 방법 |

| JP2011150270A (ja) * | 2009-12-25 | 2011-08-04 | Sony Corp | 駆動回路および表示装置 |

| JP2011145344A (ja) | 2010-01-12 | 2011-07-28 | Seiko Epson Corp | 電気光学装置とその駆動方法、及び電子機器 |

| TWI404040B (zh) * | 2010-03-10 | 2013-08-01 | Au Optronics Corp | 畫素電路與其驅動方法以及所應用之顯示面板與顯示器 |

| CN102201197A (zh) * | 2010-03-23 | 2011-09-28 | 索尼公司 | 驱动电路和显示装置 |

| JP2010160526A (ja) * | 2010-04-23 | 2010-07-22 | Seiko Epson Corp | 発光装置および電子機器 |

| JP5655371B2 (ja) | 2010-05-26 | 2015-01-21 | セイコーエプソン株式会社 | 電子装置およびその駆動方法 |

| JP5565098B2 (ja) | 2010-05-26 | 2014-08-06 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP5565097B2 (ja) | 2010-05-26 | 2014-08-06 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| TWI471840B (zh) * | 2010-11-05 | 2015-02-01 | Wintek Corp | 發光元件驅動電路 |

| KR20120065139A (ko) * | 2010-12-10 | 2012-06-20 | 삼성모바일디스플레이주식회사 | 표시 장치를 위한 화소, 이를 이용한 표시 장치 및 그 구동 방법 |

| KR20120070921A (ko) * | 2010-12-22 | 2012-07-02 | 엘지디스플레이 주식회사 | 타이밍 컨트롤러 및 이를 이용한 유기발광다이오드 표시장치 |

| TWI571128B (zh) * | 2011-04-01 | 2017-02-11 | 半導體能源研究所股份有限公司 | 半導體裝置及其驅動方法 |

| US20140368491A1 (en) | 2013-03-08 | 2014-12-18 | Ignis Innovation Inc. | Pixel circuits for amoled displays |

| US9351368B2 (en) | 2013-03-08 | 2016-05-24 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US9886899B2 (en) | 2011-05-17 | 2018-02-06 | Ignis Innovation Inc. | Pixel Circuits for AMOLED displays |

| EP2715711A4 (en) | 2011-05-28 | 2014-12-24 | Ignis Innovation Inc | SYSTEM AND METHOD FOR FAST COMPENSATION PROGRAMMING OF PIXELS ON A DISPLAY |

| JP5035455B2 (ja) * | 2011-07-26 | 2012-09-26 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| JP5141812B2 (ja) * | 2011-11-09 | 2013-02-13 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| US9747834B2 (en) | 2012-05-11 | 2017-08-29 | Ignis Innovation Inc. | Pixel circuits including feedback capacitors and reset capacitors, and display systems therefore |

| US9786223B2 (en) | 2012-12-11 | 2017-10-10 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US9336717B2 (en) | 2012-12-11 | 2016-05-10 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US9721505B2 (en) | 2013-03-08 | 2017-08-01 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| CA2894717A1 (en) | 2015-06-19 | 2016-12-19 | Ignis Innovation Inc. | Optoelectronic device characterization in array with shared sense line |

| CN103400548B (zh) * | 2013-07-31 | 2016-03-16 | 京东方科技集团股份有限公司 | 像素驱动电路及其驱动方法、显示装置 |

| JP5761308B2 (ja) * | 2013-11-08 | 2015-08-12 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| KR20150142943A (ko) * | 2014-06-12 | 2015-12-23 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| US9799261B2 (en) * | 2014-09-25 | 2017-10-24 | X-Celeprint Limited | Self-compensating circuit for faulty display pixels |

| CA2873476A1 (en) | 2014-12-08 | 2016-06-08 | Ignis Innovation Inc. | Smart-pixel display architecture |

| CN104505050B (zh) * | 2014-12-31 | 2017-02-01 | 深圳市华星光电技术有限公司 | 用于氧化物半导体薄膜晶体管的扫描驱动电路 |

| CA2886862A1 (en) | 2015-04-01 | 2016-10-01 | Ignis Innovation Inc. | Adjusting display brightness for avoiding overheating and/or accelerated aging |

| JP5979272B2 (ja) * | 2015-04-07 | 2016-08-24 | セイコーエプソン株式会社 | 発光装置および電子機器 |

| US10255834B2 (en) | 2015-07-23 | 2019-04-09 | X-Celeprint Limited | Parallel redundant chiplet system for controlling display pixels |

| CA2898282A1 (en) | 2015-07-24 | 2017-01-24 | Ignis Innovation Inc. | Hybrid calibration of current sources for current biased voltage progra mmed (cbvp) displays |

| US10657895B2 (en) | 2015-07-24 | 2020-05-19 | Ignis Innovation Inc. | Pixels and reference circuits and timing techniques |

| US10373554B2 (en) | 2015-07-24 | 2019-08-06 | Ignis Innovation Inc. | Pixels and reference circuits and timing techniques |

| KR101763616B1 (ko) * | 2015-07-29 | 2017-08-02 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| JP2017068033A (ja) | 2015-09-30 | 2017-04-06 | ソニー株式会社 | 表示素子、表示素子の駆動方法、表示装置、及び、電子機器 |

| CA2908285A1 (en) | 2015-10-14 | 2017-04-14 | Ignis Innovation Inc. | Driver with multiple color pixel structure |

| EP3389037B1 (en) | 2017-04-11 | 2020-12-09 | Samsung Electronics Co., Ltd. | Pixel circuit of display panel |

| EP3389039A1 (en) * | 2017-04-13 | 2018-10-17 | Samsung Electronics Co., Ltd. | Display panel and driving method of display panel |

| KR102664219B1 (ko) * | 2017-04-13 | 2024-05-09 | 삼성전자주식회사 | 디스플레이 패널 및 디스플레이 패널의 구동 방법 |

| KR20230164225A (ko) | 2018-02-01 | 2023-12-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 전자 기기 |

| KR102583109B1 (ko) | 2019-02-20 | 2023-09-27 | 삼성전자주식회사 | 디스플레이 패널 및 디스플레이 패널의 구동 방법 |

| KR102652718B1 (ko) * | 2019-03-29 | 2024-04-01 | 삼성전자주식회사 | 디스플레이 모듈 및 디스플레이 모듈의 구동 방법 |

| CN111243498B (zh) * | 2020-03-17 | 2021-03-23 | 京东方科技集团股份有限公司 | 像素电路及其驱动方法、显示装置 |

| KR20240054439A (ko) | 2022-10-18 | 2024-04-26 | 삼성디스플레이 주식회사 | 표시 장치 |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4996523A (en) * | 1988-10-20 | 1991-02-26 | Eastman Kodak Company | Electroluminescent storage display with improved intensity driver circuits |

| JPH03183175A (ja) * | 1989-08-22 | 1991-08-09 | Mitsubishi Electric Corp | 光量調節装置 |

| FI91684C (fi) * | 1992-05-15 | 1994-07-25 | Planar International Oy Ltd | Menetelmä ja laitteisto elektroluminenssimatriisinäytön ohjaamiseksi |

| JP3275991B2 (ja) * | 1994-07-27 | 2002-04-22 | シャープ株式会社 | アクティブマトリクス型表示装置及びその駆動方法 |

| DE69535970D1 (de) | 1994-12-14 | 2009-08-06 | Eastman Kodak Co | Elektrolumineszente Vorrichtung mit einer organischen elektrolumineszenten Schicht |

| JP3305946B2 (ja) * | 1996-03-07 | 2002-07-24 | 株式会社東芝 | 液晶表示装置 |

| US6157356A (en) * | 1996-04-12 | 2000-12-05 | International Business Machines Company | Digitally driven gray scale operation of active matrix OLED displays |

| JPH09329806A (ja) * | 1996-06-11 | 1997-12-22 | Toshiba Corp | 液晶表示装置 |

| TW441136B (en) * | 1997-01-28 | 2001-06-16 | Casio Computer Co Ltd | An electroluminescent display device and a driving method thereof |

| JP4114216B2 (ja) * | 1997-05-29 | 2008-07-09 | カシオ計算機株式会社 | 表示装置及びその駆動方法 |

| US6462722B1 (en) * | 1997-02-17 | 2002-10-08 | Seiko Epson Corporation | Current-driven light-emitting display apparatus and method of producing the same |

| US5952789A (en) * | 1997-04-14 | 1999-09-14 | Sarnoff Corporation | Active matrix organic light emitting diode (amoled) display pixel structure and data load/illuminate circuit therefor |

| US6229506B1 (en) * | 1997-04-23 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| JPH118534A (ja) * | 1997-06-18 | 1999-01-12 | Seiko Epson Corp | 半導体集積回路 |

| JP3541625B2 (ja) * | 1997-07-02 | 2004-07-14 | セイコーエプソン株式会社 | 表示装置及びアクティブマトリクス基板 |

| JP3767877B2 (ja) * | 1997-09-29 | 2006-04-19 | 三菱化学株式会社 | アクティブマトリックス発光ダイオード画素構造およびその方法 |

| US6329974B1 (en) * | 1998-04-30 | 2001-12-11 | Agilent Technologies, Inc. | Electro-optical material-based display device having analog pixel drivers |

| US6188375B1 (en) * | 1998-08-13 | 2001-02-13 | Allied Signal Inc. | Pixel drive circuit and method for active matrix electroluminescent displays |

| US6384804B1 (en) * | 1998-11-25 | 2002-05-07 | Lucent Techonologies Inc. | Display comprising organic smart pixels |

| JP3353731B2 (ja) | 1999-02-16 | 2002-12-03 | 日本電気株式会社 | 有機エレクトロルミネッセンス素子駆動装置 |

| TW483287B (en) * | 1999-06-21 | 2002-04-11 | Semiconductor Energy Lab | EL display device, driving method thereof, and electronic equipment provided with the EL display device |

| US6747638B2 (en) * | 2000-01-31 | 2004-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Adhesion type area sensor and display device having adhesion type area sensor |

| TW531901B (en) * | 2000-04-27 | 2003-05-11 | Semiconductor Energy Lab | Light emitting device |

| TW466466B (en) * | 2000-06-21 | 2001-12-01 | Chi Mei Optoelectronics Corp | Driving circuit of thin film transistor light emitting display and the usage method thereof |

| TWI282080B (en) * | 2000-07-07 | 2007-06-01 | Seiko Epson Corp | Circuit, driver circuit, electro-optical device, organic electroluminescent display device electronic apparatus, method of controlling the current supply to a current driven element, and method for driving a circuit |

| GB2367413A (en) * | 2000-09-28 | 2002-04-03 | Seiko Epson Corp | Organic electroluminescent display device |

| JP4982014B2 (ja) * | 2001-06-21 | 2012-07-25 | 株式会社日立製作所 | 画像表示装置 |

-

2001

- 2001-06-21 JP JP2001187478A patent/JP4982014B2/ja not_active Expired - Fee Related

- 2001-12-13 TW TW090130964A patent/TW530277B/zh not_active IP Right Cessation

-

2002

- 2002-02-15 US US10/075,591 patent/US6876345B2/en not_active Expired - Lifetime

- 2002-02-19 KR KR1020020008709A patent/KR100842511B1/ko active IP Right Grant

- 2002-02-20 CN CNB021046980A patent/CN1220168C/zh not_active Expired - Lifetime

- 2002-02-20 CN CN2006101017043A patent/CN1877681B/zh not_active Expired - Lifetime

- 2002-02-20 CN CN2005100039303A patent/CN1630437B/zh not_active Expired - Lifetime

-

2004

- 2004-10-18 US US10/965,864 patent/US7277072B2/en not_active Expired - Lifetime

-

2005

- 2005-04-01 US US11/095,615 patent/US7142180B2/en not_active Expired - Lifetime

-

2007

- 2007-09-21 US US11/859,414 patent/US8031144B2/en not_active Expired - Lifetime

-

2011

- 2011-08-01 US US13/195,588 patent/US8159427B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8159427B2 (en) | 2012-04-17 |

| US20110279434A1 (en) | 2011-11-17 |

| CN1877681A (zh) | 2006-12-13 |

| CN1630437A (zh) | 2005-06-22 |

| US8031144B2 (en) | 2011-10-04 |

| US20080007493A1 (en) | 2008-01-10 |

| KR20020096851A (ko) | 2002-12-31 |

| KR100842511B1 (ko) | 2008-07-01 |

| CN1220168C (zh) | 2005-09-21 |

| US20020196213A1 (en) | 2002-12-26 |

| US7142180B2 (en) | 2006-11-28 |

| JP2003005709A (ja) | 2003-01-08 |

| US7277072B2 (en) | 2007-10-02 |

| CN1877681B (zh) | 2012-07-04 |

| US20050078067A1 (en) | 2005-04-14 |

| US6876345B2 (en) | 2005-04-05 |

| US20050168457A1 (en) | 2005-08-04 |

| TW530277B (en) | 2003-05-01 |

| CN1630437B (zh) | 2010-11-17 |

| CN1393838A (zh) | 2003-01-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4982014B2 (ja) | 画像表示装置 | |

| KR101060017B1 (ko) | 화상 표시 장치 | |

| US6950081B2 (en) | Image display device | |

| KR101005646B1 (ko) | 화상표시장치 | |

| KR20030089404A (ko) | 화상 표시 장치 | |

| KR100610711B1 (ko) | 표시 장치 | |

| WO2004054114A1 (ja) | 半導体装置、デジタル・アナログ変換回路及びそれらを用いた表示装置 | |

| KR102588103B1 (ko) | 표시 장치 | |

| JP5015887B2 (ja) | 画像表示装置 | |

| US8633878B2 (en) | Image display | |

| JP5094929B2 (ja) | 画像表示装置および画像表示装置の駆動方法 | |

| JP4100418B2 (ja) | 画像表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060418 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080618 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080916 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100127 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120301 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120403 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120423 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150427 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |