JP4770103B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4770103B2 JP4770103B2 JP2002229051A JP2002229051A JP4770103B2 JP 4770103 B2 JP4770103 B2 JP 4770103B2 JP 2002229051 A JP2002229051 A JP 2002229051A JP 2002229051 A JP2002229051 A JP 2002229051A JP 4770103 B2 JP4770103 B2 JP 4770103B2

- Authority

- JP

- Japan

- Prior art keywords

- dummy

- capacitor

- electrode

- switching element

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Control Of El Displays (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Description

【発明の属する技術分野】

本発明は、半導体基板上に有効領域の周辺のダミー領域に形成されているダミーの半導体素子に含まれているコンデンサを利用して、電源電圧などの変動を抑制する半導体装置に関するものである。

【0002】

【従来の技術】

液晶表示装置やDRAMメモリのように、スイッチング素子とこのスイッチング素子に接続されており、当該スイッチング素子を介して電荷の入出力が行われる電荷保持素子、例えば、容量素子(コンデンサ)によって構成される画素セルまたはメモリセルがマトリクス状に配置されている。画素セルにおいて、スイッチング素子を介してコンデンサに画素情報に応じた電荷が書き込まれたあと、スイッチング素子を遮断させると、書き込まれた電荷がコンデンサによって保持されるので、画素情報が所定の時間において保持される。同様に、DRAMのようなダイナミック記憶装置のメモリセルにおいて、スイッチング素子を介してコンデンサに記憶すべきデータに応じた電荷が書き込まれたあと、スイッチング素子を遮断させると、書き込まれた電荷がコンデンサによって保持されるので、書き込まれたデータが所定の時間においてメモリセルによって保持される。

【0003】

通常、表示装置またはメモリ装置において、半導体基板あるいは絶縁基板上に、表示画素領域またはメモリセル領域の平坦化あるいはレイアウトの不連続性による素子の電気的特性のバラツキを低減させるために、表示画素領域またはメモリセル領域周辺に表示画素セルまたはメモリセルと同じ構成を有するダミーの画素セルまたはメモリセルが配置されている。

【0004】

【発明が解決しようとする課題】

ところで、上述した半導体装置において、ダミーの画素セルまたはメモリセルは、有効な画素セルまたはメモリセルが配置されている領域の周辺に配置され、通常、電源電圧供給線または駆動信号線から切り離されているため、本来の画素セルまたはメモリセルとしての機能を有せず、半導体基板上に無駄な領域が生じてしまう。

一方、多数の画素セルまたはメモリセルが行列状に配置されてなる半導体表示装置または記憶装置において、複数の画素セルに書き込みを行うとき、または複数のメモリセルに書き込み若しくは読み出しを行うとき、あるいは周辺回路が動作するとき、基板上に電流が流れる。特に同期型の回路、即ち、基準クロック信号に同期して全回路が動作する場合、回路に瞬時電流が大きくなる。この瞬時電流の影響によってグランド電位、電源電位が変動し、これによってノイズが発生するので、半導体装置の誤動作や書き込み精度、読み出し精度の低下を引き起こす原因となる。

【0005】

特に、高速化、微細化が進んだ近年の半導体装置では、単位面積に集積された半導体素子の数が従来に較べて大きくなり、また、動作速度も大きくなる。このため、同期動作時に生じた瞬時電流が極めて大きくなり、その結果、瞬時電流に起因するノイズの増大を招いてしまう。

【0006】

一般に、半導体チップの外部では、電源−グランド間にバイパスコンデンサを設けてグランド電位、及び電源電位の変動を抑制するなどの対策が講じられているが、チップ面積が大きくなると、これだけではノイズ抑制の効果を十分得られず、チップ内でグランド電位、電源電位の変動が起こってしまう。この観点からチップ内にコンデンサを設けて、ノイズを低減させる方法が有効である。従来では、チップレイアウト中の空き領域に容量を形成し、電源のバイパスコンデンサとすることで電源の変動を抑える方法が公開特許公報「特開2001−203272」により開示されている。しかし、この方法はチップのレイアウト中の空き領域を利用することを前提としており、高集積化が求められている半導体集積回路においては実現が難しくなる。

【0007】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、基板上に有効な半導体素子の周辺に形成されているダミーの半導体素子、例えば、画素セル及びメモリセルにある容量素子をバイパスコンデンサとして利用し、電源電圧とグランド間に、または異なる電源電圧間に当該バイパスコンデンサを接続することで、レイアウトに影響を与えることなく、電源電圧の変動及びそれに起因するノイズを抑制できる半導体装置を提供することにある。

【0008】

上記目的を達成するため、本発明の半導体装置は、複数の半導体素子がマトリクス状に配列されている有効領域と、上記有効領域に隣接して複数配列された第1のダミー半導体素子と、上記第1のダミー半導体素子に隣接し、かつ、上記有効領域には隣接しないように複数配列された第2のダミー半導体素子と、を含むダミー領域と、を有し、上記有効領域の上記各半導体素子は、選択信号線に応じて導通または遮断する第1のスイッチング素子と、上記第1のスイッチング素子が導通するとき、入力信号線から入力される信号が第1の電極に入力され、第2の電極が最大の駆動電圧のほぼ中間レベルの電圧である中間電圧の供給線に接続され、上記第1のスイッチング素子が遮断するとき、当該第1および当該第2の電極間の電圧を入力された信号のレベルとして保持するコンデンサと、を有し、上記ダミー領域には、少なくとも上記中間電圧の供給線と、電源電圧の供給線とが配置され、上記ダミー領域の上記各第1のダミー半導体素子は、第2のスイッチング素子と、上記第2のスイッチング素子から切り離され、第3の電極と第4の電極とを有し、上記第3の電極が上記中間電圧の供給線に接続され、上記第4の電極が接地電位に接続されている第1のダミーコンデンサと、を有し、上記ダミー領域の上記各第2のダミー半導体素子は、第3のスイッチング素子と、上記第3のスイッチング素子から切り離され、第5の電極と第6の電極とを有し、上記第5の電極が電源電圧の供給線に接続され、上記第6の電極が上記接地電位に接続されている第2のダミーコンデンサと、を有する。

【0009】

また、本発明では、好適には、上記有効領域の上記半導体素子は、上記コンデンサの保持電圧が印加される液晶を含む画素表示素子であって、上記ダミー領域の上記各第1および上記各第2のダミー半導体素子は、上記液晶を含み、上記第1のダミーコンデンサは上記第2のスイッチング素子および上記液晶から切り離され、上記第2のダミーコンデンサは上記第3のスイッチング素子及び上記液晶から切り離される。

【0010】

また、本発明では、好適には、上記有効領域の上記半導体素子は、上記コンデンサに保持した電圧が電流変換されて印加される有機ELを有する画素表示素子であって、上記ダミー領域の上記各第1および上記各第2のダミー半導体素子は、上記有機ELを有し、上記第1のダミーコンデンサは上記第2のスイッチング素子および上記有機ELから切り離され、上記第2のダミーコンデンサは上記第3のスイッチング素子及び上記有機ELから切り離される。

【0011】

また、本発明では、好適には、上記選択信号線は、ワード線であって、上記第1のスイッチング素子は、上記ワード線に印加される選択信号に応じて導通または遮断し、上記有効領域の上記各半導体素子は、上記第1の電極が上記第1のスイッチング素子に接続され、上記第2の電極が上記接地電位に接続されたメモリセルであって、上記第1のダミーコンデンサは上記第2のスイッチング素子および上記メモリセルから切り離され、上記第2のダミーコンデンサは上記第3のスイッチング素子及び上記メモリセルから切り離される。

【0018】

本発明によれば、有効領域の周辺に配置されている複数のダミーの半導体素子からなるダミー領域において、それぞれの半導体素子にあるコンデンサを電源電圧のバイパスコンデンサとして用いる。即ち、当該コンデンサを他の素子から切り離され、その一方の電極が電源電圧の供給線に接続され、他方の電極が基準電位、例えば、グランド(接地電位)に接続される。これにより、電源電圧の変動が抑制される。

また、ダミー領域において、複数のダミーの半導体素子のうち、コンデンサがそれぞれ異なる電源電圧のバイパスコンデンサとして用いることにより、異なる電源電圧の変動が抑制される。

また、本発明によれば、もっとも変動を抑制したい電圧のバイパスコンデンサとして、ダミー領域において有効領域に隣接して配置されている半導体素子のコンデンサを用いることにより、その電源電圧の変動の抑制効果を向上できる。

【0019】

本発明の半導体装置によれば、ダミー領域の半導体素子のコンデンサを電源電圧のバイパスコンデンサとして用いるので、半導体装置の製造工程の変更を要せず、さらにレイアウトの増加もほとんどなく、電源電圧の変動を抑制し、安定した動作を達成可能である。

【0020】

【発明の実施の形態】

第1実施形態

図1は本発明に係る半導体装置の第1の実施形態を示す構成図である。

図1(a)は、本実施形態の半導体装置のレイアウトを示し、図1(b)は、同図(a)に示すレイアウトの一部分を拡大した図である。

【0021】

図1(a)に示すように、本実施形態の半導体装置において、有効領域とダミー領域がそれぞれ形成されている。有効領域は、例えば、画像を表示する画素セルまたはメモリセルがマトリクス状に配置され、形成されている。一方、ダミー領域は、有効領域を形成する半導体素子と同じ画素セルまたはメモリセルが、有効領域の周辺に配置されて、形成されている。

【0022】

図1(b)は、同図(a)に示すレイアウトの一部分を拡大して、回路の内部構成を示している。図示のように、有効領域及びダミー領域の両方において、半導体素子、例えば、画素セルまたはメモリセルがマトリクス状に配置されている。半導体素子には、選択信号に応じて導通または遮断状態に制御されるスイッチング素子と、電荷を保持する記憶素子としてのコンデンサが設けられている。

【0023】

図示のように、有効領域において、各半導体素子にあるコンデンサの一方の電極がスイッチング素子に接続され、他方の電極が基準電位に接続されている。スイッチング素子は、入力信号線とコンデンサの一方の電極間に設けられており、選択信号線に印加されている選択信号に応じて、導通または遮断状態の何れかに制御される。

有効領域において、各行における半導体素子のスイッチング素子の制御端子が選択信号線SL1,SL2…に接続されている。これらの選択信号線に印加される選択信号に応じて、マトリクス状に配置されている複数の半導体素子が、行単位に選択される。また、各列の半導体素子のスイッチング素子の一方の端子が駆動信号線DL1,DL2…に接続されている。これらの駆動信号線に、駆動信号が印加されるので、複数の選択信号線のうち、何れかの選択信号線にアクティブ状態の選択信号が印加されたとき、当該選択信号線によって選択された一行の各半導体素子のコンデンサに、駆動信号に応じた電荷が入力される。その後、選択信号が非アクティブ状態に保持されている間、その行にあるすべての半導体素子のスイッチング素子が遮断されるので、入力された電荷が各半導体素子のコンデンサによって保持され、それに応じてディジタル信号が記憶される。

【0024】

一方、ダミー領域において、各半導体素子のコンデンサがバイパスコンデンサとして利用されている。図示のように、本実施形態では、ダミー領域の各半導体素子のコンデンサの一方の電極が電源電圧VDDに接続され、他方の電極が基準電位、例えば、グランド(接地電位GND)に接続されている。なお、ダミー領域の各半導体素子のスイッチング素子は、コンデンサから切り離された状態にあり、スイッチング素子として機能しない。

【0025】

上述したように、本実施形態の半導体装置において、ダミー領域に配置されている複数の半導体素子において、各半導体素子に形成されているコンデンサの一方の電極が電源電圧VDDに接続され、他方の電極がグランドに接続されている。即ち、これらのコンデンサが電源電圧VDDのバイパスコンデンサとして利用されている。

【0026】

図1に示すように、電源電圧VDDの入力端子とグランドとの間に、電圧安定化のためのバイパスコンデンサCBPが設けられている。通常、この電圧安定化コンデンサCBPは、大きな容量をもち、半導体チップの外部に接続されている。しかし、半導体装置の高集積化、高密度化により、チップ上の半導体回路の規模が大きくなり、この電圧安定化コンデンサCBPのみでは、半導体チップ内部に供給されている電源電圧VDDを十分に安定させることができない。このため、本実施形態に示すように、半導体チップ上にダミー領域に設けられている半導体素子にあるコンデンサを有効に活用することによって、半導体装置のレイアウトを変更させることなく、半導体チップ上に電源電圧の変動を抑制する目的を達成する。

【0027】

以下、本実施形態の半導体装置を構成する半導体素子の具体例について説明する。図2〜図5は、それぞれ液晶表示素子及びDRAMのメモリセルの構成を示している。以下、これらの図面を参照しつつ、本実施形態の半導体素子の構成及び当該半導体素子をバイパスコンデンサとして利用する場合の接続について説明する。

【0028】

図2は、本実施形態の半導体装置における液晶表示素子の構成例を示す回路図である。なお、図2(a)では、有効領域の液晶表示素子10aを示し、同図(b)は、ダミー領域の液晶表示素子10bを示している。

【0029】

図2(a)に示すように、液晶表示素子(液晶画像表示装置において、各液晶表示素子は、それぞれ1つの画素に対応するので、以下、便宜上液晶表示素子を画素セルと略称する)10aは、スイッチング素子12、コンデンサ14と液晶16によって構成されている。なお、本例の画素セルは、いわゆるアクティブマトリクス型画像表示装置の基本構成単位である。各画素セルごとに画素電極と当該画素電極を駆動する駆動素子が設けられている。なお、図2(a)の画素セルの例では、スイッチング素子12は、駆動素子として機能し、画素電極は、スイッチング素子12と液晶16の共通の端子に設けられている。

【0030】

スイッチング素子12は、例えば、MOSトランジスタまたは、TFT(薄膜トランジスタ:Thin Film Transistor)によって構成されている。スイッチング素子12の制御端子(ゲート電極)が選択信号線SLiに接続されている。このため、選択信号線SLiに印加される選択信号に応じて、スイッチング素子が導通または遮断する。スイッチング素子12の一方の端子が駆動信号線DLjに接続され、他方の端子がコンデンサ14に接続されている。

【0031】

図示のように、コンデンサ14は、電荷を保持するために設けられている。コンデンサ14の一方の電極がスイッチング素子12の一方の端子に接続され、他方の電極が基準電位に接続されている。このため、スイッチング素子12が導通するとき、駆動信号線DLjに印加された駆動信号電圧がコンデンサ14に印加される。これに応じて、コンデンサ14に駆動信号に応じた電荷が蓄積される。そして、駆動信号入力後、スイッチング素子12が遮断されると、コンデンサ14によって電荷が保持される。

【0032】

画素セル10aにおいて、コンデンサ14の電極とほぼ同じ面積を持つ画素電極が形成されている。液晶16は、画素電極と対向電極との間に設けられている。液晶16は、それに印加される電界の強度に応じて光透過率、偏光特性などが変化する。この特性を利用することによって、画素セルに印加される駆動信号に応じた画素を表示することができる。

図示のように、対向電極に所定の共通電極電位VCOMが印加されている。このため、コンデンサ14によって画素電極に保持されている電圧と上記共通電極電位VCOMとの電圧差に応じた電界が液晶16に印加される。これに応じて、画素セルが所定の画素を表示する。

なお、対向電極に印加される共通電極電位VCOMは、液晶の駆動電極に印加される最大の駆動電圧のほぼ中間レベルの電位である。このため、以下の説明において、この共通電極電位VCOMを中間電圧VCOMと表記する。

【0033】

図2(b)は、ダミー領域の画素セル10bを示している。上述したように、ダミー領域の画素セル10bのコンデンサが電圧を安定化を図るために、バイパスコンデンサとして用いられる。以下、図2(b)を参照しつつ、これについてさらに詳しく説明する。なお、図2(b)において、図2(a)と実質的に同じ構成部分に、同じ記号を付して表記している。

【0034】

図2(b)に示すように、ダミー領域の画素セル10bにおいて、コンデンサ14がスイッチング素子12及び液晶16から切り離されている。コンデンサ14の一方の電極が電源電圧VDDに接続され、他方の電極が基準電位に接続されている。即ち、製造工程において、ダミー領域の各画素セル10bのコンデンサ14の一方の電極と電源電圧VDDの配線との間に、ビアが形成されている。コンデンサ14の一方の電極がビアを介して電源電圧VDDの配線に接続されている。

【0035】

製造工程において、ダミー領域のフォトレジストマスクを変えることにより、ダミー領域の画素セルにおいて、コンデンサ14の一方の電極と電源電圧VDDの配線間のビアを形成することができる。このため、製造工程を変更することなく、ダミー領域における画素セルの既存のコンデンサを電源電圧VDDのバイパスコンデンサとして利用することができる。これによって、半導体装置の製造コストの増加を抑制しながら、チップ内の電源電圧VDDの安定性を図ることができ、半導体装置の性能の改善を実現できる。

【0036】

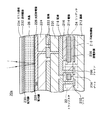

図3は、反射型液晶表示素子(以下、反射型画素セル)の一構成例を示す断面図である。本例の反射型画素セルは、図2に示す画素セルと同様に、アクティブマトリクス型表示装置を構成する基本単位である。しかし、本例の画素セルは、液晶を通過した反射光の特性を制御することにより、画素を表示するので、反射型表示装置、例えば、プロジェクタに適用することができ、高輝度、高解像度かつ大画面の画像表示を実現できる。

【0037】

図3は、有効領域の反射型画素セル20aの構成を示し、図4は、ダミー領域の反射型画素セル20bを示している。

図3に示すように、反射型画素セル20aは、トランジスタ22、コンデンサ24及び液晶26によって構成されている。

【0038】

本例の反射型画素セル20aにおいて、トランジスタ22のソース202は、図示しない駆動信号線DLjに接続され、ゲート204は、図示しない選択信号線SLi接続されている。トランジスタ22のドレインが配線218を介してコンデンサ24の電極214に接続されている。

このため、選択信号線SLiに印加されている選択信号に応じて、トランジスタ22が導通するとき、ソース202に印加されている駆動信号がトランジスタ22及び配線218を介して、コンデンサ24の電極214に印加される。その後、トランジスタ22が遮断すると、コンデンサ24において、駆動信号に応じた電荷が保持される。

【0039】

コンデンサ24は、基板212の表面に形成されている不純物領域210、電極214、及び不純物領域210と電極214によって挟まれている誘電体膜(絶縁膜)208によって構成されている。図示のように、電極214は、ビアを介して配線218、222及び光反射電極226に接続されている。光反射電極226は、金属膜、例えばアルミニウム(Al)の薄膜からなり、導電性を有する一方、ガラス基板234、透明電極232及び液晶26を通過した入射光を反射する光反射層として機能する。

なお、コンデンサ24の電極214と配線218との間、層間絶縁膜216が生成され、配線218と配線222との間、層間絶縁膜220が形成され、さらに、配線222と光反射電極226との間、層間絶縁膜224が生成されている。これらの層間絶縁膜は、例えば、酸化シリコン(Si02 )などの絶縁体からなる。

【0040】

コンデンサ24は、トランジスタ22のソース202が接続されている駆動信号線より入力される駆動信号に応じた電荷を蓄積し、蓄積されている電荷に応じて、その一方の電極214が所定の電圧に保持される。このため、ビアを介して電極214に接続されている光反射電極226がコンデンサ24とほぼ同電位に保持される。

【0041】

液晶26は、透明電極232と光反射電極226との間に封入されている垂直配向液晶材料からなる。図3に示すように、液晶26と光反射電極226との間に配向膜228が形成され、また、液晶26と透明電極232との間にも配向膜230が形成されている。

透明電極232は、例えば、ITO(Indium-Tin-Oxide)によって形成された

導電性膜からなる。当該透明電極232には、中間電圧VCOMが印加される。このため、液晶26に透明電極232に印加される中間電圧VCOMと光反射電極226に印加される電圧、即ち、コンデンサ24の電極214の電圧との差に応じた電界が印加される。液晶26は、印加される電界強度に応じて液晶分子の配列が制御され、これに応じて光特性、例えば、光透過率、偏光方向などが変化するので、駆動信号に応じて輝度が変調された画素を表示できる。

【0042】

次に、図4を参照してダミー領域の反射型画素セル20bについて説明する。

図4に示すように、ダミー領域における反射型画素セル20bにおいて、トランジスタ22のドレイン206とコンデンサ24の電極214が切り離された。これは、配線218において、トランジスタ22のドレイン206が接続されている部分とコンデンサ24の電極214が接続されている部分の間に、スリット240が形成することで実現される。

【0043】

また、コンデンサ24の電極214が接続されている配線218の部分が光反射電極と切り離され、代わりに電源電圧VDDを供給する電源配線222との間に、ビア242が形成されている。このため、コンデンサ24の電極214は、配線層218及びビア242を介して、電源配線222に接続されている。

【0044】

また、図4に示していないが、コンデンサ24の他方の電極を形成する不純物領域210は、例えば、グランドに接続されている。

即ち、ダミー領域の反射型画素セル20bにおいて、コンデンサ24は、駆動信号を供給するトランジスタ22から切り離され、さらに、液晶26の光反射電極からも切り離される。その代わりに、コンデンサ24の一方の電極214は、配線218及びビア242を介して、電源配線222に接続され、他方の電極210は、グランドに接続されている。

【0045】

これによって、ダミー領域の反射型画素セル20bのコンデンサ24は、電源電圧VDDとグランドとの間に接続されているバイパスコンデンサとして用いられる。このバイパスコンデンサは、ダミー領域の画素セル20bのコンデンサを用いて形成され、ダミー領域にほぼ均等に配分されている。このため、ダミー領域の反射型画素セル20bを用いたバイパスコンデンサと半導体チップの外部に、電源電圧VDDの供給線に接続されているバイパスコンデンサと合わせて、電源電圧VDDの変動を抑制する。

【0046】

なお、ダミー領域の反射型画素セル20bにおいて、コンデンサ24とトランジスタ22及び液晶26との切り離しは、配線にスリット240を形成することで実現でき、また、コンデンサ24の電極214と電源配線222との接続は、ビア242を形成することによって実現できる。このため、製造工程を変えることなく、ダミー領域部分のフォトレジストマスクを変えるのみで、この変更を実現できる。これによって、製造コストの増加を必要最小限に抑制でき、レイアウトを変えることなく、半導体チップの内部において電源電圧VDDの安定化を実現できる。

【0047】

なお、図示を省略するが、有機EL(エレクトロルミネセンス)においても同様に動作される。即ち、液晶がコンデンサに蓄えた電圧をそのまま印加するのに対し、駆動トランジスタによって電圧から電流に変換して電流駆動するのが有機ELである。従って、上記本発明の構成および動作は有機ELにおいてもそのまま適用可能である。

【0048】

図5は、本実施形態の半導体装置において、DRAMのメモリセルの構成例を示す回路図である。なお、図5(a)では、有効領域のメモリセル30aを示し、同図(b)は、ダミー領域のメモリセル30bを示している。

【0049】

図5(a)に示すように、メモリセル30aは、スイッチング素子としてのMOSトランジスタ32と、コンデンサ34とによって構成されている。

MOSトランジスタ32は、ゲートがワード線WLiに接続され、ソースがビット線BLjに接続されている。

コンデンサ34は、一方の電極がMOSトランジスタ32のドレインに接続され、他方の電極がグランドに接続されている。

【0050】

動作時に、ワード線WLiに印加されている選択信号に応じて、メモリセルが選択される。例えば、ワード線WLiに、電源電圧VDDまたはそれよりわずかに高い活性化電圧が印加されると、当該ワード線WLiに接続されているメモリセルがすべて選択される。

【0051】

書き込みの場合、選択メモリセルのMOSトランジスタ32がゲートに印加される活性化電圧により導通するので、ビット線BLjに印加される書き込み電圧がメモリセルのコンデンサ34に印加される。そして、書き込み後選択ワード線WLiが低電圧、例えば、グランド電圧に保持されるので、MOSトランジスタ32が遮断し、コンデンサ34に印加される書き込み電圧に応じた電圧が保持される。

【0052】

一方、読み出しの場合、選択メモリセルのMOSトランジスタ32がゲートに印加される活性化電圧により導通するので、コンデンサ34によって保持されている電圧がMOSトランジスタ32を介して、ビット線BLjに印加される。このため、ビット線BLjの電位が変化する。センスアンプによってビット線BLjの電位変化を検出することによって、選択メモリセルのコンデンサに保持されている電圧を検出でき、この保持電圧に対応したメモリセルの記憶データを読み出すことができる。

【0053】

図5(b)は、ダミー領域のメモリセル30bを示している。図示のように、ダミー領域のメモリセル30bにおいて、コンデンサ34の一方の電極がMOSトランジスタ32から切り離され、電源電圧VDDの供給線に接続されている。

ダミー領域のメモリセル30bにおいて、コンデンサ34の一方の電極が電源電圧VDDの供給線に接続され、他方の電極がグランドに接続されている。これによって、コンデンサ34が電源電圧VDDのバイパスコンデンサとして利用される。このため、半導体チップの内部に電源電圧VDDの変動を抑制され、電源電圧の安定化を実現できる。

【0054】

なお、ダミー領域においてメモリセル30bのこの変更は、製造工程においてダミー領域に対応するフォトレジスト膜を変えることで実現できる。これによって、製造工程数を増加することなく、また、半導体装置のレイアウトが変化せずに、半導体チップ上の電源電圧の安定化を実現できる。

【0055】

以上説明したように、本実施形態の半導体装置によれば、有効領域の周辺に配置されているダミー領域の半導体素子、例えば、画素セル、メモリセルにおいて、コンデンサをスイッチング素子としてのトランジスタから切り離し、その一方の電極を電源電圧の供給線に接続し、他方の電極をグランドに接続することによって、半導体素子のコンデンサを電源電圧のバイパスコンデンサとして機能するので、チップ上の電源電圧の変動を抑制できる。ダミー領域における製造工程に使用するフォトレジスト膜を変更するのみで、ダミー領域の半導体素子のコンデンサを利用することができ、製造工程数及び製造コストの増加を抑制でき、かつ半導体装置のレイアウトを変更せずに、チップ上の電源電圧の安定性を実現できる。

【0056】

第2実施形態

図6は本発明に係る半導体装置の第2の実施形態を示す構成図である。

本実施形態の半導体装置において、ダミー領域の半導体素子のコンデンサは、それぞれに異なる電源電圧に割り当てることによって、複数の電源電圧で動作する半導体チップ上、それぞれの電源電圧の変動を抑制できる。

なお、本実施形態の半導体素子は、上述した第1の実施形態に説明したように、画素セルまたはメモリセルからなる。

【0057】

図6に示すように、例えば、ダミー領域にある複数の半導体素子のうち、半導体素子301,302と303のコンデンサ(第1のダミーコンデンサ)が、電源電圧VDD (第2の電源電圧)の供給線とグランド間に接続されているので、これらのコンデンサが電源電圧VDDのバイパスコンデンサとして機能する。また、半導体素子304と305のコンデンサ(第2のダミーコンデンサ)が、中間電圧(第1の電源電圧)VCOMの供給線とグランドとの間に接続されているので、これらのコンデンサが中間電圧VCOMのバイパスコンデンサとして機能する。

なお、電源電圧VDDは、例えば、半導体装置内のロジック回路に供給される動作電圧であって、例えば、3Vである。また、中間電圧VCOMは、画素セルに供給される共通電極電位であって、例えば、6Vである。

【0058】

即ち、本実施形態の半導体において、ダミー領域の半導体素子のコンデンサがそれぞれ異なる電源電圧のバイパスコンデンサとして利用される。このため、本実施形態の半導体装置によれば、ダミー領域の半導体素子のコンデンサを利用して、異なる電源電圧の安定化を図ることができる。また、上述した本発明の第1の実施形態と同様に、ダミー領域の半導体素子のコンデンサの利用は、製造工程においてダミー領域に対応するフォトレジスト膜を変更することで実現でき、製造工程の追加を要せず、製造コストの増加及びレイアウト面積の拡大を回避でき、低コストで電源電圧の安定化を実現できる。

【0059】

なお、図6に示す本実施形態の半導体装置の例では、ダミー領域の半導体素子のコンデンサは、電源電圧VDDとグランド間、または中間電圧VCOMとグランド間のバイパスコンデンサとして用いられているが、本発明はこれに限定されるものではなく、例えば、ダミー領域の半導体素子のコンデンサは、異なる電源電圧間のバイパスコンデンサとして用いることもできる。その一例として、例えば、ダミー領域の半導体素子において、コンデンサの一方の電極を電源電圧VDDの供給線に接続し、他方の電極を中間電圧VCOMの供給線に接続することにより、電源電圧VDDと中間電圧VCOM間のバイパスコンデンサを形成できる。

【0060】

第3実施形態

図7は本発明に係る半導体装置の第3の実施形態を示す構成図である。

本実施形態の半導体装置において、ダミー領域の半導体素子のコンデンサを用いて、電源電圧のバイパスコンデンサを形成する点では、上述した本実施形態の第1または第2の実施形態と同じである。ただし、本実施形態では、ダミー領域にマトリクス状に配置されている多数の半導体素子のコンデンサを、有効領域との距離に応じて、異なる電源電圧のバイパスコンデンサとして利用する。

もっと具体的に、例えば、有効領域に隣接するダミー領域における半導体素子のコンデンサを、有効領域に供給される電源電圧のうち、もっともその変動を抑制したい電源電圧のバイパスコンデンサとして用いる。有効領域から離れたダミー領域の半導体素子のコンデンサをその他の電源電圧のバイパスコンデンサとして用いる。

【0061】

以下、図7を参照しつつ、本実施形態の半導体装置について説明する。

図示のように、ここで、本実施形態の半導体装置は、例えば、画像を表示する表示装置であって、この画像表示装置は、マトリクス状に配置されている複数の画素セルによって構成されている。また、有効領域の周辺に、表示領域の平坦化、またはレイアウトに起因の素子の電気的特性のバラツキを低減のため、ダミーの画素セルからダミー領域が形成されている。

【0062】

有効領域において、マトリクス状に配置されている画素セルのうち、選択信号線SL1,SL2…によって選択された画素セルに、駆動信号線DL1,DL2…から入力される駆動信号が印加されるので、選択される画素セルによって駆動信号に応じた輝度または色の画素が表示される。

【0063】

各画素セルにおいて、駆動信号線から駆動信号が印加されるほか、中間電圧VCOMも入力される。また、チップ上のロジック回路の動作電源電圧として、電源電圧VDDもチップに供給される。

【0064】

これらの電源電圧のうち、各画素セルに供給される中間電圧VCOMは、電流の変動などに応じて変動する。または、周辺回路の動作時の発生する瞬時電流の影響によって、電源電圧VDDの電位及びグランドの電位もそれぞれ変動する。特に各画素セルに供給される中間電圧VCOMの変動は、画素セルによって表示される画素の輝度、色合いなどを敏感に影響するので、中間電圧VCOMの変動をできるだけ抑えたい。

【0065】

このため、本実施形態の半導体装置において、図7に示すように、ダミー領域に配置されている画素セルのうち、有効領域に隣接した画素セルのコンデンサの一方の電極を中間電圧VCOMの供給線に接続し、他方の電極をグランドに接続する。これによって、これらのダミー画素セルのコンデンサは、中間電圧VCOMのバイパスコンデンサとして利用される。このため、有効領域における中間電圧VCOMの変動が有効領域にもっとも近くに配置されているダミー画素セルのコンデンサによって抑制されるので、有効領域の中間電圧VCOMの変動をもっとも効果的に抑制することができる。

ダミー領域に配置されているその他の画素セルのコンデンサは、電源電圧VDDなどのバイパスコンデンサとして用いることができる。

【0066】

以上説明したように、本実施形態によれば、有効領域においてもっともその変動を抑制した電圧、例えば、中間電圧VCOMのバイパスコンデンサとして、有効領域に隣接して配置されているダミー画素セルのコンデンサが用いられる。これによって、有効領域において中間電圧VCOMの変動をもっとも効果的に抑制することができ、チップのレイアウトに何ら影響を与えることなく、所望の電源電圧のバイパスコンデンサを形成することができ、電源電圧の変動を抑制する効果を達成できる。

【0067】

【発明の効果】

以上説明したように、本発明の半導体装置によれば、従来より表示領域の平坦化やレイアウト起因の半導体素子の電気的特性のバラツキを低減させるため、有効な画素セルまたはメモリセルからなる有効領域の周辺に配置されているダミーの画素セルまたはダミーのメモリセル内の容量素子を電源−グランド間、または電源−電源間に接続し、バイパスコンデンサを形成することでグランド電位、電源電位の変動を抑え、ノイズ低減が可能となり、安定した動作が実現できる。

また、本発明の半導体装置によれば、従来よりチップ内に形成していたダミーの画素セルやダミーのメモリセル内の容量素子をバイパスコンデンサとして利用するため、新たな素子の追加やチップ面積の増加を必要とせずにチップ内にバイパスコンデンサを形成することができる利点がある。

【図面の簡単な説明】

【図1】本発明に係る半導体装置の第1の実施形態を示す構成図である。

【図2】本実施形態の半導体装置における液晶表示素子の構成を示す回路図である。

【図3】本実施形態の半導体装置における反射型液晶表示素子の一構成例を示す断面図である。

【図4】ダミー領域における反射型液晶表示素子を示す断面図である。

【図5】本実施形態の半導体装置におけるメモリセルの一構成例を示す回路図である。

【図6】本発明に係る半導体装置の第2の実施形態を示す構成図である。

【図7】本発明に係る半導体装置の第3の実施形態を示す構成図である。

【符号の説明】

10a,10b…画素セル、12…スイッチング素子、14…コンデンサ、16…液晶、20a,20b…反射型画素セル、22…トランジスタ、24…コンデンサ、26…液晶、30a,30b…DRAMメモリセル、32…トランジスタ、34…コンデンサ。

Claims (4)

- 複数の半導体素子がマトリクス状に配列されている有効領域と、

上記有効領域に隣接して複数配列された第1のダミー半導体素子と、上記第1のダミー半導体素子に隣接し、かつ、上記有効領域には隣接しないように複数配列された第2のダミー半導体素子と、を含むダミー領域と、

を有し、

上記有効領域の上記各半導体素子は、

選択信号線に応じて導通または遮断する第1のスイッチング素子と、

上記第1のスイッチング素子が導通するとき、入力信号線から入力される信号が第1の電極に入力され、第2の電極が最大の駆動電圧のほぼ中間レベルの電圧である中間電圧の供給線に接続され、上記第1のスイッチング素子が遮断するとき、当該第1および当該第2の電極間の電圧を入力された信号のレベルとして保持するコンデンサと、

を有し、

上記ダミー領域には、少なくとも上記中間電圧の供給線と、電源電圧の供給線とが配置され、

上記ダミー領域の上記各第1のダミー半導体素子は、

第2のスイッチング素子と、

上記第2のスイッチング素子から切り離され、第3の電極と第4の電極とを有し、上記第3の電極が上記中間電圧の供給線に接続され、上記第4の電極が接地電位に接続されている第1のダミーコンデンサと、

を有し、

上記ダミー領域の上記各第2のダミー半導体素子は、

第3のスイッチング素子と、

上記第3のスイッチング素子から切り離され、第5の電極と第6の電極とを有し、上記第5の電極が電源電圧の供給線に接続され、上記第6の電極が上記接地電位に接続されている第2のダミーコンデンサと、

を有する

半導体装置。 - 上記有効領域の上記半導体素子は、

上記コンデンサの保持電圧が印加される液晶を含む画素表示素子であって、

上記ダミー領域の上記各第1および上記各第2のダミー半導体素子は、

上記液晶を含み、

上記第1のダミーコンデンサは上記第2のスイッチング素子および上記液晶から切り離され、上記第2のダミーコンデンサは上記第3のスイッチング素子及び上記液晶から切り離される

請求項1に記載の半導体装置。 - 上記有効領域の上記半導体素子は、

上記コンデンサに保持した電圧が電流変換されて印加される有機ELを有する画素表示素子であって、

上記ダミー領域の上記各第1および上記各第2のダミー半導体素子は、

上記有機ELを有し、

上記第1のダミーコンデンサは上記第2のスイッチング素子および上記有機ELから切り離され、上記第2のダミーコンデンサは上記第3のスイッチング素子及び上記有機ELから切り離される

請求項1に記載の半導体装置。 - 上記選択信号線は、ワード線であって、

上記第1のスイッチング素子は、上記ワード線に印加される選択信号に応じて導通または遮断し、

上記有効領域の上記各半導体素子は、上記第1の電極が上記第1のスイッチング素子に接続され、上記第2の電極が上記接地電位に接続されたメモリセルであって、

上記第1のダミーコンデンサは上記第2のスイッチング素子および上記メモリセルから切り離され、上記第2のダミーコンデンサは上記第3のスイッチング素子及び上記メモリセルから切り離される

請求項1に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002229051A JP4770103B2 (ja) | 2002-08-06 | 2002-08-06 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002229051A JP4770103B2 (ja) | 2002-08-06 | 2002-08-06 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004069993A JP2004069993A (ja) | 2004-03-04 |

| JP4770103B2 true JP4770103B2 (ja) | 2011-09-14 |

Family

ID=32015582

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002229051A Expired - Fee Related JP4770103B2 (ja) | 2002-08-06 | 2002-08-06 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4770103B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006065284A (ja) | 2004-07-26 | 2006-03-09 | Seiko Epson Corp | 発光装置及び電子機器 |

| US20090097301A1 (en) * | 2005-06-01 | 2009-04-16 | Matsushita Electric Industrial Co., Ltd. | Semiconductor storage apparatus and semiconductor integrated circuit incorporating the same |

| JP2009245503A (ja) * | 2008-03-31 | 2009-10-22 | Nec Electronics Corp | 半導体記憶装置 |

| JP5700907B2 (ja) * | 2008-06-26 | 2015-04-15 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 半導体記憶装置 |

| CN102043295B (zh) * | 2009-12-25 | 2014-03-26 | 京东方科技集团股份有限公司 | 阵列基板及其制造方法和液晶显示器 |

| JP5651387B2 (ja) | 2010-06-24 | 2015-01-14 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| US9620077B2 (en) * | 2014-05-09 | 2017-04-11 | Innolux Corporation | Display panel structure |

| JP6359332B2 (ja) * | 2014-05-09 | 2018-07-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US10490122B2 (en) * | 2016-02-29 | 2019-11-26 | Samsung Display Co., Ltd. | Display device |

| KR102613863B1 (ko) | 2016-09-22 | 2023-12-18 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102611958B1 (ko) | 2016-09-23 | 2023-12-12 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102559096B1 (ko) | 2016-11-29 | 2023-07-26 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20180096875A (ko) | 2017-02-21 | 2018-08-30 | 삼성디스플레이 주식회사 | 표시 장치 |

| JP6556294B2 (ja) * | 2018-05-17 | 2019-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| CN112859466A (zh) | 2019-11-28 | 2021-05-28 | 京东方科技集团股份有限公司 | 显示基板和显示面板 |

| CN111179873B (zh) * | 2020-02-19 | 2022-12-06 | 京东方科技集团股份有限公司 | 一种关机降噪电路、关机降噪芯片及显示装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0561072A (ja) * | 1991-03-15 | 1993-03-12 | Hitachi Ltd | 液晶表示装置 |

| JP2735722B2 (ja) * | 1991-12-26 | 1998-04-02 | シャープ株式会社 | アクティブマトリクス基板 |

| JP3256810B2 (ja) * | 1992-02-27 | 2002-02-18 | キヤノン株式会社 | 液晶表示装置 |

| JPH07253564A (ja) * | 1994-03-15 | 1995-10-03 | Toshiba Corp | 液晶表示装置 |

| JP3246194B2 (ja) * | 1994-06-10 | 2002-01-15 | ソニー株式会社 | アクティブマトリクス型液晶表示装置 |

| JP3304706B2 (ja) * | 1995-09-20 | 2002-07-22 | ソニー株式会社 | アクティブマトリクス表示装置 |

| US5952789A (en) * | 1997-04-14 | 1999-09-14 | Sarnoff Corporation | Active matrix organic light emitting diode (amoled) display pixel structure and data load/illuminate circuit therefor |

| JP3169920B2 (ja) * | 1998-12-22 | 2001-05-28 | 日本電気アイシーマイコンシステム株式会社 | 半導体記憶装置、その装置製造方法 |

-

2002

- 2002-08-06 JP JP2002229051A patent/JP4770103B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004069993A (ja) | 2004-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4770103B2 (ja) | 半導体装置 | |

| KR100661850B1 (ko) | 반도체장치 제작방법 | |

| JP3139134B2 (ja) | 液晶表示装置 | |

| US6724359B2 (en) | Electronic device and method for driving the same | |

| US8803776B2 (en) | Liquid crystal display device | |

| US6888164B2 (en) | Display pixel having a capacitive electrode with different conductivity type from the switching element | |

| US7323718B2 (en) | Input display with embedded photo sensor | |

| US6037923A (en) | Active matrix display device | |

| CN113869095A (zh) | 指纹显示设备及驱动其之整合集成电路及方法 | |

| CN100399119C (zh) | 显示设备 | |

| JP4017371B2 (ja) | アクティブマトリクス型表示装置 | |

| JP3982992B2 (ja) | アクティブマトリクス型表示装置 | |

| KR100516091B1 (ko) | 표시 장치 | |

| JPH06100745B2 (ja) | アクティブマトリクス型液晶表示装置 | |

| US20150338692A1 (en) | Display device | |

| JPH06214254A (ja) | 反射型薄膜トランジスタアレイ素子 | |

| KR100469192B1 (ko) | 액티브 매트릭스형 표시 장치 | |

| JPS60192370A (ja) | 薄膜トランジスタアレイ | |

| JP3166367B2 (ja) | 液晶表示回路 | |

| JP4163203B2 (ja) | 液晶表示装置 | |

| US12118935B2 (en) | Display substrate and display apparatus | |

| JP2005521191A (ja) | 表示装置用画素内メモリ | |

| JPH08146384A (ja) | アクティブマトリックス型液晶表示素子 | |

| JP2001235722A (ja) | 液晶表示装置 | |

| WO2023123138A1 (zh) | 显示面板及显示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050610 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080902 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081104 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100608 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100727 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110524 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110606 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140701 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140701 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |