JP3896214B2 - 半導体メモリデバイス及びその製造方法 - Google Patents

半導体メモリデバイス及びその製造方法 Download PDFInfo

- Publication number

- JP3896214B2 JP3896214B2 JP17859098A JP17859098A JP3896214B2 JP 3896214 B2 JP3896214 B2 JP 3896214B2 JP 17859098 A JP17859098 A JP 17859098A JP 17859098 A JP17859098 A JP 17859098A JP 3896214 B2 JP3896214 B2 JP 3896214B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- conductivity type

- region

- drain

- pass

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/403—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh

- G11C11/405—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells with charge regeneration common to a multiplicity of memory cells, i.e. external refresh with three charge-transfer gates, e.g. MOS transistors, per cell

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/903—FET configuration adapted for use as static memory cell

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/903—FET configuration adapted for use as static memory cell

- Y10S257/904—FET configuration adapted for use as static memory cell with passive components,, e.g. polysilicon resistors

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/908—Dram configuration with transistors and capacitors of pairs of cells along a straight line between adjacent bit lines

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

Description

【発明の属する技術分野】

本発明は、半導体メモリデバイス(記憶装置)及びその製造方法に関し、特に、メモリセルの大きさを減少させることができる半導体メモリデバイス及びその製造方法に関する。

【0002】

【従来の技術】

ダイナミックランダムアクセスメモリ(Dynamic Random Access Memory:DRAM)の単位セルは一つのトランジスタと一つのキャパシタとから構成される。従って、単位セルが占める面積が小さいという利点がある。しかし、このような構造のDRAMを製造するには、ワードラインを形成するための第1ポリシリコンの蒸着工程、ビットラインを形成するための第2ポリシリコンの蒸着工程、キャパシタの蓄積ノードを形成するための第3ポリシリコンの蒸着工程、及びキャパシタのプレートノードを形成するための第4ポリシリコンの蒸着工程を施すべきであるので、DRAMの製造工程が複雑である。かつ、DRAMのリード及びライトアクセスポートが同一のデータラインに連結されており、ロジックデバイスとしてのDRAMセルの動作が複雑である。

従って、前述した問題を除去するため、従来は単一のポリシリコン蒸着工程にDRAMセルを製造する方法が提案された。

【0003】

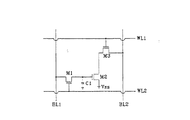

図1には、ライト用パストランジスタ、リード用パストランジスタ及び蓄積トランジスタ及びキャパシタ、トランジスタ等を駆動させるワードラインと前記ワードラインと垂直交差してデータを入力(data-in)かつ出力(data-out)するビットラインを備えたDRAMが示される。

【0004】

M1はライト用パストランジスタであり、M2は蓄積トランジスタであり、M3はリード用パストランジスタである。WL1はリード用ワードラインとして、リード用パストランジスタM3のゲートに連結される。WL2はライト用ワードラインとして、ライト用パストランジスタM1のゲートに連結される。BL1はデータライト用ビットラインとしてライト用トランジスタM1のソースに連結される。BL2はデータリード用ビットラインとしてリード用トランジスタM3のソースに連結される。ライト用トランジスタM1のドレインは蓄積キャパシタM2のゲートに連結される。蓄積キャパシタM2のドレインはリード用パストランジスタM3のドレインと連結される。蓄積キャパシタM2のソースはVss段に連結される。ライト用トランジスタM1のドレインと蓄積キャパシタM2のゲート間には寄生キャパシタC1が形成される。前記キャパシタC1の容量が増加すればDRAMのデータの貯蔵力が増加する。

【0005】

図1の回路を含む半導体デバイスは、ビットラインを通じてVss電圧レベルが感知されれば、DRAMセルに情報が保存されたと判断し、Vss電圧レベルより高い電圧レベルが感知されれば、DRAMセルに情報がないと判断するように設計された。

【0006】

ライト動作時、ライト用ワードラインWL2がアクセスされライト用パストランジスタM1がターンオンされる。したがって、ライト用ビットラインBL1のデータはライト用パストランジスタM1を通過してキャパシタC1に保存される。

リード動作時、リード用ワードラインWL1がアクセスされると、リード用パストランジスタM3がターンオンされる。この時、蓄積トランジスタM2はキャパシタC1に保存されたデータによってターンオン又はターンオフされる。キャパシタC1にデータが保存されている場合、蓄積トランジスタM2はターンオンされリード用ビットラインBL2にはVss電圧レベルが感知される。一方、キャパシタC1にデータのない場合には、蓄積トランジスタM2はターンオフされリード用ビットラインBL2にはVssより高いレベルの電圧が感知される。

【0007】

図2は、図1のDRAMを基板上に設計した平面図を示す。

Y1、Y2は、DRAM単位セルの領域を示す。A1は蓄積キャパシタM2およびリード用トランジスタM3が形成される第1アクティブ領域であり、A2はライト用トランジスタM1が形成される第2アクティブ領域である。4Aはライト用パストランジスタM1のゲート、4Bは蓄積トランジスタM2のゲート、4Cはリード用パストランジスタのM3のゲートである。特に、蓄積トランジスタM2のゲート4Bの幅はキャパシタC1の容量に比例するので、リード用パストランジスタM3及びライト用パストランジスタM1のゲートの幅4C、4Aよりも大きく設計する。図面符号2はアクティブ領域A1、A2を分離する素子分離領域である。図面符号5はそれぞれのアクティブ領域A1、A2の中、ゲート4A、4B、4Cの両側に該当する領域である。C−1はリード用パストランジスタM3のソースとリード用ビットラインBL2がコンタクトされる部分である。C−2は蓄積キャパシタM2のソースVss電圧段がコンタクトされる領域である。C−3はライト用パストランジスタM1のソースとライト用ビットラインBL1がコンタクトされる領域である。C−4は蓄積トランジスタM2のゲート4Bとライト用パストランジスタM1のドレインとがコンタクトされる領域である。

【0008】

図3は図2のIII−III’に沿う断面図であって、これを基づき、図1及び図2に示されたようなDRAMの製造方法を説明する。

【0009】

半導体基板1の上部の所定部分に、第1及び第2アクティブ領域A1、A2を分離する素子分離領域2を形成する。ゲート酸化膜及びポリシリコン膜を基板1の上部に順次的に積層した後、ゲート酸化膜とポリシリコン膜を公知の写真触刻法にパターニングしてゲート酸化膜3A、3B、3Cとゲート4A、4B、4Cとを形成する。先に説明したように、蓄積トランジスタM2のゲート4Bの幅は他のトランジスタM1、M3のゲート4A、4Cの幅より大きい。次に、ゲートが形成された基板にN型の不純物イオン注入工程を行い、各トランジスタの接合領域5−1、5−2、5−3、5−4、5−5を形成する。接合領域5−2は蓄積トランジスタM2とリード用トランジスタM3の共通接合領域である。

【0010】

トランジスタM1、M2、M3が形成された結果物の上部に、接合領域5−1、5−3、5−5を露出させるコンタクトホールC−1、C−2、C−3を備えた層間絶縁膜6を形成する。

【0011】

次いで、コンタクトホールを通じて前記露出された接合領域等と接触する金属配線7−1、7−2、7−3を形成する。

【0012】

以上から明らかなように、3個のトランジスタから構成されたDRAMを形成するには、図2に示されたような4個のコンタクトホール領域C−1、C−2、C−3、C−4が必要である。したがって、DRAMセルの面積が増加して半導体デバイスの集積度を低下させる。

【0013】

しかも、半導体デバイスの高集積化に伴い金属配線7−1、7−2、7−3間のピッチがますます小さくなるので、半導体デバイスの信頼性が低減される。

【0014】

【発明が解決しようとする課題】

従って、本発明の目的は、高集積化に応えながらデバイス信頼性が改善できる半導体デバイスのDRAMセル及びその製造方法を提供することにある。

【0015】

【課題を解決するための手段】

本発明の目的を達成するための、一つの見地に係る半導体メモリデバイスは、第1ワードライン、第2ワードライン、第1ビットライン、第2ビットライン及び、前後第1ワードラインがアクセスされる時ターンオンされ前記第1ビットラインに載せたデータを通過させる第1パス手段を備える。また、前記半導体メモリデバイスは、前記第1パス手段から出力されたデータを保存する蓄積手段、前記第2ワードラインがアクセスされる時ターンオンされ前記蓄積手段に保存されたデータを前記第2ビットラインへ伝達する第2パス手段、及び前記蓄積手段に基板電圧を供給する供給手段を備える。

【0016】

一実施例では、前記第1ワードライン及び前記第2ワードラインは、各々ライト用ワードライン及びリード用ワードラインであり、前記第1ビットライン及び前記第2ビットラインは、各々ライト用ビットライン及びリード用ビットラインである。前記第1パス手段は第2導電型MOSトランジスタを含み、前記供給手段は第1導電型不純物領域を有するディプリーション第2導電型MOSトランジスタを備える。前記第2パス手段と前記蓄積手段は第2導電型MOSトランジスタを備える。

【0017】

具体的に、前記第1パス手段のゲート、ソース及びドレインは、各々前記ライト用ワードライン、前記ライト用ビットライン及び前記蓄積手段のゲートに連結される。前記第2パス手段のゲート、ソース及びドレインは、各々前記リード用ワードライン、前記リード用ビットライン及び前記蓄積手段のドレインに連結される。前記蓄積手段のソースは前記供給手段のソースに連結される。前記供給手段のゲートは、上記ライト用ワードラインに連結される。前記供給手段のドレインの一部に前記P型の不純物領域が形成され前記P型不純物領域に前記基板電圧が連結される。前記第1パス手段の前記ドレインと前記蓄積手段の前記ゲート間にキャパシタが形成される。

【0018】

本発明の目的を達成するための、ほかの見地に係る半導体メモリデバイスは、隣接する4個の単位セル領域により限定された領域の中央部分に配置された胴体と、前記胴体から前記4個の単位セルのそれぞれの領域へ伸張する分岐とを持つ第1導電型の第1アクティブ領域、前記第1アクティブ領域と所定距離をおいて離隔されており、隣接する2個の単位セル領域にかけて配置された第1導電型の第2アクティブ領域、及び前記胴体に形成された第2導電型のディプリーション領域を備える。特に、前記ディプリーション領域の中央部分には第1導電型の基板電極領域が配置される。また、半導体メモリデバイスは、前記第1アクティブ領域の前記分岐に形成された蓄積手段、前記第1アクティブ領域の前記分岐に形成され前記蓄積手段と連結された第2パス手段、前記基板電極領域を含む前記ディプリーション領域に形成され前記基板電極領域を通じて基板電圧を前記蓄積手段に供給する供給手段、及び第2アクティブ領域に形成され前記蓄積手段と連結される第1パス手段を備える。前記第1導電型はP型で、前記第2導電型はN型である。

【0019】

具体的に、前記第2パス手段は、前記第1アクティブ領域を横切るゲートと、前記ゲート両側の前記第1アクティブ領域に形成された第2導電型のソース及びドレインとを備えたトランジスタである。前記供給手段は、前記ディプリーション領域を横切るゲートと、前記ゲート両側の前記ディプリーション領域に形成された第2導電型のソース及びドレインとを備えたディプリーショントランジスタである。前記ディプリーショントランジスタのソース及びドレインのいずれか一部に第1導電型の不純物を注入して基板電極領域を形成する。前記第1パス手段は、前記第2アクティブ領域を横切るゲートと、前記ゲート両側の前記第2アクティブ領域へ伸張して配置された第2導電型のソース及びドレインとを備えたトランジスタである。蓄積手段は、前記第1アクティブ領域から前記第2アクティブ領域にかけて配置されたゲートと、前記ゲートの両側の前記第1アクティブ領域に形成された第2導電型のソース及びドレインとを備えたトランジスタである。

前記第2パス手段のドレインと前記蓄積手段のドレインとは共通である。前記蓄積手段のゲートの幅は、前記第1パス手段及び第2パス手段のゲート幅よりも大きい。

【0020】

他の例として、前記第1パス手段のゲートと供給手段のゲートが一体である。

本発明の目的を達成するための、他の見地により、第1導電型の第1アクティブ領域と、前記第1アクティブ領域と所定距離において隔離された第1導電型の第2アクティブ領域とを備えた半導体基板を提供する。前記第1アクティブ領域の所定部分に第2導電型のディプリーション領域を形成する。前記第1アクティブ領域に第2パス手段及び蓄積手段を形成し、前記第2アクティブ領域に第1パス手段を形成し、基板電圧を前記蓄積手段に供給する供給手段を前記ディプリーション領域に形成する。前記第1及び第2パス手段、前記蓄積手段及び前記供給手段を備えた結果物の全面に絶縁層を形成する。前記絶縁層の所定部分をエッチングし、前記第2パス手段の一部分を露出させる第1コンタクトホール、前記第1パス手段の一部分を露出させる第2コンタクトホール及び前記第1パス手段の他部分と前記蓄積手段の一部分を共に露出させる第3コンタクトホールを形成する。前記第1乃至第3コンタクトホールの各々を満たす第1乃至第3金属配線を形成する。

【0021】

第1と第2パス手段、蓄積手段及び供給手段の形成段階は、前記半導体基板の全面に絶縁膜とポリシリコンを連続的に形成してパターニングし、前記第1パス手段、前記第2パス手段、蓄積手段及び供給手段のゲート絶縁膜とゲートを形成する段階と、前記ディプリーション領域を含んだ前記第1アクティブ領域及び前記第2アクティブ領域に第2導電型の不純物をイオン注入して前記第1パス手段、前記第2パス手段、蓄積手段及び供給手段のソース及びドレインを形成する段階と、前記ディプリーション領域に形成された供給手段のソースの一部に第1導電型の不純物をイオン注入して前記基板電圧と連結する基板電極領域を形成する段階とを備える。

【0022】

また、第1と第2パス手段、蓄積手段及び供給手段の形成段階と絶縁層の形成段階との間に、前記第1パス手段、前記第2パス手段、蓄積手段及び供給手段それぞれのゲート、ソース及びドレインの上部にシリサイド層を形成する。

【0023】

ライト用パストランジスタ、リード用パストランジスタ及び蓄積トランジスタを備えたDRAMセルにおいて、DRAMセルの動作に影響しないながら蓄積トランジスタのソースにVss段を連結させるため、蓄積トランジスタ、ライト用パストランジスタ及び基板電圧に連結されるディプリーショントランジスタを形成する。ディプリーショントランジスタのソース及びドレインのいずれか一つに、DRAMセルが形成される基板と同じ導電型を持つ不純物領域を形成し、別の追加電極なしに、蓄積トランジスタのソースに基板電圧を供給する。

【0024】

蓄積トランジスタをVss電圧段に連結するために必要なコンタクトホール形成用面積が要求されず、半導体デバイスの高集積化が達成できる。また、本発明のDRAMセルでは従来に比しコンタクトホールの数が少ないので、コンタクトホールを満たす金属配線間のピッチが相対的に広くなり、半導体デバイスの信頼性の低下を低減させることができる。

【0025】

【発明の実施の形態】

以下、添付の図面を参照しながら本発明を説明する。

図4において、図1に似ているように、ライト用パストランジスタMM1のソースはライト用ビットラインBBL1に連結され、そのゲートはライト用ワードラインWWL2に連結され、そのドレインは蓄積トランジスタMM2のゲートに連結される。リード用パストランジスタMM3のソースはリード用ビットラインBBL2に連結され、そのゲートはリード用ワードラインWWL1に連結され、そのドレインは蓄積トランジスタのドレインに連結される。蓄積トランジスタMM2のソースはディプリーショントランジスタDのソースに連結される。ディプリーショントランジスタDはトランジスタMM1、MM2、MM3と同型のトランジスタである。前記ディプリーショントランジスタDのゲートはライト用ワードラインWWL2及びライト用パストランジスタMM1のゲートに連結され、そのドレインはVss段に連結される。ここで、図4には示されないが、Vss段は基板電圧Vssと連結される。ライト用パストランジスタMM1のドレインと蓄積トランジスタMM2のゲート間には寄生キャパシタCC1が形成される。

【0026】

ディプリーショントランジスタDは、DRAM回路動作に影響せず蓄積トランジスタのソースに基板電圧を印加する橋渡しの役割をする。すなわち、ディプリーショントランジスタDのドレインに基板電圧の誘導する基板電極を形成し、蓄積トランジスタMM2に基板電圧Vssを供給する。

【0027】

ライト動作を説明すれば、ライト用ワードラインWWL2がアクセスされると、ライト用パストランジスタMM1はターンオンされる。よって、ライト用ビットラインBBL1の情報はライト用パストランジスタMM1を通じキャパシタCC1に保存される。一方、ディプリーショントランジスタDはライト用ワードラインWWL2の駆動によりターンオフされる。

【0028】

リード動作を説明する前に、まず、キャパシタCC1にデータが保存されたと仮定しよう。リード用ワードラインWWL1が駆動されリード用トランジスタMM3がターンオンされ、キャパシタCC1のデータにより蓄積トランジスタMM2がターンオンされる。この時、ライト用ワードラインWWL2はアクセスされない状態であるが、ワードラインWWL2にゲートが連結されたディプリーショントランジスタDはターンオンされる。よって、リード用ビットラインBBL2にVss電圧レベルが感知される一方に、キャパシタCC1にデータが保存されていない場合には、蓄積トランジスタMM2はターンオフされリード用パストランジスタMM3とディプリーショントランジスタDがターンオンされ、ライト用ビットラインBBL2にはVss電圧レベルより高い電圧レベルが感知される。

【0029】

図5は、図4に示すような回路を基板上に設計した平面図である。

破線に示された各ボックスX1、X2、X3、X4はDRAM単位セル領域を示す。隣接する4個の単位セル領域に限定された空間にDRAMセルを配置する。各セル領域において、AA1は蓄積トランジスタMM2及びリード用パストランジスタMM3が形成される第1アクティブ領域であり、AA2はライト用バストランジスタMM1が形成される第2アクティブ領域である。図面符号12は第1アクティブ領域と第2アクティブ領域とを絶縁分離させる素子分離領域である。前記第1アクティブ領域及び第2アクティブ領域はP型の導電型を持つ。第1アクティブ領域AA1は、隣接する4個の単位セル領域に限定された空間の中央部分に配置された胴体B1と、前記胴体B1からそれぞれの単位セル領域へ伸張する分岐B2とを含む。前記胴体B1にはディプリーショントランジスタDが形成されるディプリーション領域DAが配置される。ディプリーション領域はN型の導電型を持つ。ディプリーション領域DAの中央部分には基板電圧を誘導する基板電極領域20が配置される。基板電極領域20は第1及び第2アクティブ領域のようなP型の導電型を持つ。

【0030】

17Aはライト用パストランジスタMM1のゲートであり、17Bは蓄積トランジスタMM2のゲートであり、17Cはリード用パストランジスタMM3のゲートであり、17DはディプリーショントランジスタDのゲートである。ゲート17Aはディプリーション領域DA及び第2アクティブ領域AA2を上部に配置する。ゲート17Bは単位セルの中央部分で第1アクティブ領域の一部から第2アクティブ領域の一部にまで伸張するように配置される。ゲート17Cは単位セル端部に位置する第1アクティブ領域の上部に配置される。特に、蓄積トランジスタMM2のゲート17Bの幅はキャパシタCC1の容量に比例するので、リード用パストランジスタMM3及びライト用パストランジスタMM1のゲート17C、17Aの幅より大きく設計する。

【0031】

ゲート17A、17B、17C両側のP型のアクティブ領域AA1、AA2には、トランジスタMM1、MM2、MM3、DのN型のソース及びドレインが形成される。

【0032】

一方、リード用パストランジスタMM3のソースは、コンタクトホールCC−1を通じてリード用ビットラインBBL2と接続される。蓄積トランジスタMM2のゲート17BはコンタクトホールCC−2を通じてライト用パストランジスタMM1のドレインと接続される。ライト用トランジスタMM1のソースはコンタクトホールCC−3を通じてライト用ビットラインBBL1と接続される。本実施例ではビットラインまたは電源ライン等の配置は本発明のレイアウトを詳細に示すために省略した。

【0033】

図6A乃至図6Cは、図5のVI-VI’に沿う断面図であって、製造工程段階を示す。

図6Aにおいて、半導体基板11の上部に素子分離領域12を公知のLOCOS方法(local oxidation silicon)形成する。前記半導体基板11はシリコンまたは化合物半導体から構成することができ、不純物が基板にドーピングすることもできる。本実施例では基板11へP型の不純物がドーピングされたシリコン基板を使用する。半導体基板の上部に基板表面を保護するための保護膜13を全面に形成する。前記保護膜13の上部にディプリーション領域DAが露出されるようにマスクパターン14を形成する。以後、N型の不純物イオンを基板に注入してディプリーション領域DAにN型の不純物領域15を形成する。N型の不純物領域15を形成する工程は、DRAM素子の周辺回路領域に配置されるPMOSトランジスタのN型不純物領域の形成工程と共に進行されるので、不純物領域15形成のための別の追加工程は要求されない。前記N型の不純物領域15はディプリーショントランジスタDのチャンネルを形成するためのもので、N型の不純物領域の接合深さは以後に形成されるトランジスタMM1、MM2、MM3の接合深さより深くないようにすることが好適である。

【0034】

図6Bにおいて、前記マスクパターン14と保護膜13を公知の方法により除去する。以後、基板11の上面に酸化膜とポリシリコン膜を順次的に積層してパターニングし、トランジスタMM1、MM2、MM3、Dのゲート酸化膜16A、16B、16C、16D及びゲート17A、17B、17C、17Dを形成する。各ゲートの壁に公知の方法により空間18を形成する。次に、基板にN型の不純物イオンを注入して各トランジスタの接合領域19−1、19−2、19−3、19−4、19−5、19−6、19−7を形成する。接合領域19−7はライト用パストランジスタMM1のソースであり、接合領域19−6はライト用パストランジスタMM1のドレインである。接合領域19−5、19−3各々は蓄積トランジスタMM2とディプリーショントランジスタ17Dとの共通ソースである。接合領域19−4はディプリーショントランジスタ17Dのドレインであり、接合領域19−2は蓄積トランジスタMM2とリード用パストランジスタMM3との共通ドレインである。接合領域19−1はリード用パストランジスタMM3のソースである。接合領域19−1、19−2、19−3、19−4、19−5、19−6及び19−7を形成した後、接合領域19−4の所定部分に高濃度のP型不純物をイオン注入することにより基板電極領域20を形成する。基板電極領域20はP型基板11と接続される。よって、基板11のフローティング現象を防止する基板電圧Vssが、別の追加電極なしディプリーション領域DAに形成されたトランジスタDを通じて蓄積トランジスタMM2のソースに連結される。基板電極領域20の形成工程は周辺回路のPMOS接合領域の形成工程時実施されるので、別のイオン注入工程は要求されない。

【0035】

図6Cにおいて、ゲート17A、17B、17C、17Dと接合領域19−1、19−2、19−3、19−4、19−5、19−6、19−7との上部には自己整列シリサイド膜21、21’が形成される。前記シリサイド膜21、21’は以後の金型配線の接触抵抗を低減させる。具体的に、チタニウム、クロム、白金、ニッケルのような転移金属を図6Bに示した結果物の上面に蒸着する。蒸着後、500℃乃至800℃の温度で熱処理を行い転移金属とシリコンが反応してシリコンサイド膜を形成する。連続的にシリコンと反応しない転移金属をNH4OH/H2O2/H2Oの溶液またはH2SO4/H2O2溶液で除ける。

【0036】

シリサイド膜21、21’形成後、基板全面に層間絶縁膜を形成し、層間絶縁膜に、接合領域中ライト用パストランジスタMM1のソース19−7、ライト用パストランジスタMM1のドレイン19−6及びリード用パストランジスタMM3のソース19−1を露出させるコンタクトホールCC−1、CC−2、CC−3を形成する。次に、コンタクトホール等を満たして露出された接合領域等と接続する金属配線23A、23B、23Cを形成する。

【0037】

【発明の効果】

蓄積トランジスタのソースに、蓄積トランジスタが形成された基板と同じ導電型で構成された基板電極領域を含んだディプリーショントランジスタを接続し、基板電圧Vssが前記ディプリーショントランジスタを通じて蓄積トランジスタのソースに印加される。よって、蓄積トランジスタのソースにVss電圧を印加するための別の金属配線用コンタクトホール面積が必要ではない。即ち、Vss電圧印加用コンタクト領域だけセル面積が低減でき、半導体デバイスの高集積化が向上できる。

【0038】

また、可能であれば、同じ単位セル面積に図2のDRAMや図5のDRAMを集積する場合、図2のコンタクトホールC−1を満たす金属配線7−1とコンタクトホールC−3を満たす金属配線7−3間の距離と、図5のコンタクトホールCC−1を満たす金属配線23CとコンタクトホールCC−3を満たす金属配線23A間の距離とが同一に設計される。しかし、従来の技術では、コンタクトホールが形成されるので、コンタクトホールC−1を満たす金属配線7−1とコンタクトホールC−2を満たす金属配線7−2間の距離、コンタクトホールC−2を満たす金属配線7−2とコンタクトホールC−3を満たす金属配線7−3間の距離とが狭くなることにより、半導体デバイスの信頼性を低下させている。本発明は実施例で説明した通り、Vss電圧段と蓄積トランジスタのソースを接続するためのコンタクトホールC−2に該当するコンタクトホールは形成しない。従って、半導体デバイスの高集積化に伴い、金属配線間のピッチ減少による半導体デバイスの信頼性の低下を低減できる。

【0039】

本実施例では、全てのトランジスタをNMOSで構成したが、DRAMの動作条件を変更すれば、ライト用パストランジスタ、リード用パストランジスタ、蓄積トランジスタ及びディプリーショントランジスタの一部または全部をPMOSトランジスタで構成できる。この時にも、ディプリーショントランジスタに形成される基板電極領域は前述したトランジスタ等が形成される基板と同じ導電型を持つ。

【0040】

この発明の構成と、上述の実施例との対応において、

第1ワードラインは、ライト用ワードラインWWL2に対応し、

第2ワードラインは、リード用ワードラインWWL1に対応し、

第1ビットラインは、ライト用ビットラインBBL1に対応し、

第2ビットラインは、リード用ビットラインBBL2に対応し、

第1パス手段は、ライト用パストランジスタMM1に対応し、

第2パス手段は、リード用パストランジスタMM3に対応し、

蓄積手段は、蓄積トランジスタMM2に対応し、

供給手段は、ディプリーショントランジスタDに対応し、

第1アクティブ領域は、第1アクティブ領域AA1に対応し、

第1アクティブ領域は、第1アクティブ領域AA2に対応し、

胴体は胴体B1に対応し、

分岐は分岐B2に対応し、

第1ゲートは、ゲート17Cに対応し、

第1ソースは、接合領域19−1に対応し、

第1ドレインは、接合領域19−2に対応し、

第2ゲートは、ゲート17A、17Dに対応し、

第2ソースは、接合領域19−3に対応し、

第2ドレインは、接合領域19−4に対応し、

第3ソースは、接合領域19−7に対応し、

第3ドレインは、接合領域19−6に対応し、

第3ゲートは、ゲート17Bに対応し、

第4ソースは、接合領域19−3、19−5に対応し、

第4ドレインは、接合領域19−2に対応し、

第1コンタクトホールは、コンタクトホールCC−1に対応し、

第2コンタクトホールは、コンタクトホールCC−3に対応し、

第3コンタクトホールは、コンタクトホールCC−2に対応するも、

本発明の特定の実施例に限定して説明したが、本発明は、これに限定されず、本発明の要旨から逸脱しない範囲内で種々に変形できることは当業者に明らかである。

【図面の簡単な説明】

【図1】 従来技術に係るDRAM回路である。

【図2】 図1の回路の配置平面図である。

【図3】 図2のIII−III’に沿う断面図である。

【図4】 本発明にかかるDRAM回路図である。

【図5】 図4の回路の配置平面図である。

【図6】 6A、6B及び6Cは図5のVI−VI’に沿う断面図として、本発明にかかるDRAMセルの製造工程段階を示す。

【符号の説明】

MM1、MM2、MM3…トランジスタ

D…ディプリーショントランジスタ

CC−1、CC−2、CC−3…コンタクトホール

16A、16B、16C、16D…ゲート酸化膜

17A、17B、17C、17D…ゲート

19−1、19−2、19−3、19−4、19−5、19−6、19−7…接合領域

20…基板電極領域

DA…ディプリーション領域

Claims (8)

- 基板、

前記基板上に形成された第1ワードライン、

前記基板上に形成された第2ワードライン、

前記基板上に形成された第1ビットライン、

前記基板上に形成された第2ビットライン、

前記基板上に形成されて前記第1ワードラインがアクセスされる時ターンオンされ、前記第1ビットラインに載せたデータをパスさせる第1パス手段、

前記基板上に形成されて前記第1パス手段から出力されたデータを保存する蓄積手段、

前記基板上に形成されて前記第2ワードラインがアクセスされる時ターンオンされ、前記蓄積手段に保存されたデータを前記第2ビットラインに伝達する第2パス手段、及び

前記基板上に形成されて前記蓄積手段に基板電圧を供給する供給手段を備え、

前記第1パス手段、前記第2パス手段及び前記蓄積手段は第2導電型MOSトランジスタであり、

前記供給手段は第1導電型不純物領域を備えたディプリーション第2導電型MOSトランジスタであり、

前記第1パス手段のゲート、ソース及びドレインは、各々前記第1ワードライン、前記第1ビットライン及び前記蓄積手段のゲートに連結され、

前記第2パス手段のゲート、ソース及びドレインは、各々前記第2ワードライン、前記第2ビットライン及び前記蓄積手段のドレインに連結され、

前記蓄積手段のソースは前記供給手段のソースに連結され、

前記供給手段のゲートは前記第1ワードラインに連結されて、

前記供給手段のドレインの一部に前記第1導電型の不純物領域が形成され前記第1導電型不純物領域に前記基板電圧が連結される

半導体デバイス。 - 前記第1パス手段の前記ドレインと前記蓄積手段の前記ゲート間にキャパシタが形成される

請求項1記載の半導体メモリデバイス。 - 前記第2パス手段のドレインと前記蓄積手段のドレインが共通である

請求項2記載の半導体メモリデバイス。 - 基板、

前記基板において、隣接する4個の単位セルにより限定された領域の中央部分に配置された胴体と前記胴体から前記4個の単位セルのそれぞれの領域へ伸張する分岐を持つ第1導電型の第1アクティブ領域、

前記第1アクティブ領域と所定距離をおいて離隔されており、隣接する2個の単位セル領域にかけて配置された第1導電型の第2アクティブ領域、

前記胴体に形成された第2導電型のディプリーション領域、

前記ディプリーション領域の中央部分に形成された基板と同じ導電型を持つ第1導電型の基板電極領域、

前記第1アクティブ領域の前記分岐に形成された蓄積手段、

前記第1アクティブ領域の前記分岐に形成され前記蓄積手段と連結された第2パス手段、

前記基板電極領域を含む前記ディプリーション領域に形成され前記基板電極領域を介して基板電圧を前記蓄積手段に供給する供給手段、及び

前記第2アクティブ領域に形成され前記蓄積手段と連結される第1パス手段を備え、

前記第2パス手段は、前記第1アクティブ領域を横切る第1ゲートと、前記第1ゲート両側の前記第1アクティブ領域に形成された第2導電型の第1ソース及び第1ドレインとを備えた第2導電型MOSトランジスタであり、

前記供給手段は、前記ディプリーション領域及び前記第2アクティブ領域を横切る第2ゲートと、前記第2ゲート両側の前記ディプリーション領域に形成された第2導電型の第2ソース及び第2ドレインとを備えたディプリーション第2導電型MOSトランジスタであり、

前記基板電極領域は前記第2ドレインの一部に第1導電型不純物が注入された不純物領域であり、

前記第1パス手段は、前記第2ゲートと、前記第2ゲート両側の前記第2アクティブ領域に形成された第2導電型の第3ソース及び第3ドレインとを備えた第2導電型MOSトランジスタであり、

前記蓄積手段は、前記第1アクティブ領域から前記第2アクティブ領域にかけて配置された第3ゲートと、前記第3ゲート両側の前記第1アクティブ領域に形成された第2導電型の第4ソース及び第4ドレインとを備えた第2導電型MOSトランジスタであり、

前記第1パス手段の第2ゲート、第3ソース及び第3ドレインは、各々第1ワードライン、第1ビットライン及び前記蓄積手段の第3ゲートに連結され、前記第2パス手段の第1ゲート、第1ソース及び第1ドレインは、各々第2ワードライン、第2ビットライン及び前記蓄積手段の第4ドレインに連結され、前記蓄積手段の第4ソースは前記供給手段の第2ソースに連結され、前記供給手段の第2ゲートは前記第1ワードラインに連結されて、前記供給手段の第2ドレインの一部に前記第1導電型の不純物領域が形成され前記第1導電型不純物領域に前記基板電圧が連結される

半導体メモリデバイス。 - (a)第1導電型の第1アクティブ領域と、前記第1アクティブ領域と所定距離をおいて離隔された第1導電型の第2アクティブ領域とを備えた半導体基板を提供する段階、

(b)前記第1アクティブ領域の所定部分に第2導電型のディプリーション領域を形成する段階、

(c)前記第1アクティブ領域に第2導電型MOSトランジスタで構成される第2パス手段及び蓄積手段を形成し、前記第2アクティブ領域に第2導電型MOSトランジスタで構成される第1パス手段を形成し、前記ディプリーション領域に、基板電圧を前記蓄積手段に供給するディプリーション第2導電型MOSトランジスタで構成され、前記基板と同じ導電型を持つ不純物領域を含む供給手段を形成する段階、

(d)前記第1及び第2パス手段、前記蓄積手段及び前記供給手段が形成された結合物の全面に絶縁層を形成する段階、

(e)前記絶縁層の所定部分をエッチングし、前記第2パス手段の一部分を露出させる第1コンタクトホール、前記第1パス手段の一部分を露出させる第2コンタクトホール及び前記第1パス手段の他の部分と前記蓄積手段の一部分を共通露出させる第3コンタクトホールを形成する段階、及び

(f)前記第1乃至第3コンタクトホールに各々第1乃至第3金属配線を形成する段階を備えると共に、

前記 ( c ) 段階は、

( c−1 ) 前記半導体基板の全面に絶縁膜とポリシリコンを連続的に形成してパターニングし、前記第1パス手段、前記第2パス手段、前記蓄積手段及び前記供給手段のゲート絶縁膜とゲートを形成する段階、

( c−2 ) 前記ゲート両側に位置する前記ディプリーション領域を含んだ前記第1アクティブ領域及び前記第2アクティブ領域に第2導電型の不純物をイオン注入し、前記第1パス手段、前記第2パス手段、前記蓄積手段及び前記供給手段のソース及びドレインを形成する段階、及び

( c−3 ) 前記ディプリーション領域に形成された供給手段のドレインの一部に、第1導電 型の不純物をイオン注入して前記基板電圧と連結される基板電極領域を形成する段階を備え、

前記第1パス手段のゲート、ソース及びドレインは、各々第1ワードライン、第1ビットライン及び前記蓄積手段のゲートに連結され、前記第2パス手段のゲート、ソース及びドレインは、各々第2ワードライン、第2ビットライン及び前記蓄積手段のドレインに連結され、前記蓄積手段のソースは前記供給手段のソースに連結され、前記供給手段のゲートは前記第1ワードラインに連結されて、前記供給手段のドレインの一部に前記第1導電型の不純物領域が形成され前記第1導電型不純物領域に前記基板電圧が連結される

半導体メモリデバイスの製造方法。 - 前記(c)段階と前記(d)段階との間に、前記第1パス手段、前記第2パス手段、前記蓄積手段及び前記供給手段の各々のゲート、ソース及びドレイン上部にシリサイド層を形成する段階をさらに備える

請求項5記載の半導体メモリデバイスの製造方法。 - 前記第2パス手段のドレインと前記蓄積手段のドレインが共通である

請求項5記載の半導体メモリデバイスの製造方法。 - 前記蓄積手段のゲートの幅は、前記第1パス手段及び前記第2パス手段のゲートの幅よりも大きい

請求項5記載の半導体メモリデバイスの製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR97-27409 | 1997-06-25 | ||

| KR1019970027409A KR100248205B1 (ko) | 1997-06-25 | 1997-06-25 | 반도체 메모리 디바이스 및 그 형성방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000243857A JP2000243857A (ja) | 2000-09-08 |

| JP3896214B2 true JP3896214B2 (ja) | 2007-03-22 |

Family

ID=19511251

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP17859098A Expired - Fee Related JP3896214B2 (ja) | 1997-06-25 | 1998-06-25 | 半導体メモリデバイス及びその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US6121079A (ja) |

| JP (1) | JP3896214B2 (ja) |

| KR (1) | KR100248205B1 (ja) |

| GB (1) | GB2326763B (ja) |

| TW (1) | TW406416B (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6504745B2 (en) * | 1996-05-24 | 2003-01-07 | Uniram Technology, Inc. | High performance erasable programmable read-only memory (EPROM) devices with multiple dimension first-level bit lines |

| JPH11265987A (ja) * | 1998-01-16 | 1999-09-28 | Oki Electric Ind Co Ltd | 不揮発性メモリ及びその製造方法 |

| EP0996152A1 (en) * | 1998-10-23 | 2000-04-26 | STMicroelectronics S.r.l. | Process for manufacturing electronic devices comprising non-salicidated nonvolatile memory cells, non-salicidated HV transistors, and salicidated-junction LV transistors |

| FR2789519B1 (fr) * | 1999-02-05 | 2003-03-28 | Commissariat Energie Atomique | Transistor mos a tension de seuil dynamique equipe d'un limiteur de courant, et procede de realisation d'un tel transistor |

| JP2001093988A (ja) * | 1999-07-22 | 2001-04-06 | Sony Corp | 半導体記憶装置 |

| JP4323749B2 (ja) * | 2002-03-25 | 2009-09-02 | パナソニック株式会社 | ダイナミックランダムアクセスメモリ |

| JP4927321B2 (ja) * | 2004-06-22 | 2012-05-09 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| JP2007103862A (ja) * | 2005-10-07 | 2007-04-19 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| KR101539667B1 (ko) * | 2008-06-18 | 2015-07-28 | 삼성전자주식회사 | 인버터 소자 및 그 동작 방법 |

| JP2010245081A (ja) * | 2009-04-01 | 2010-10-28 | Seiko Epson Corp | 半導体装置 |

| TWI608486B (zh) * | 2010-09-13 | 2017-12-11 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| KR102199143B1 (ko) * | 2014-01-09 | 2021-01-06 | 삼성전자주식회사 | 단위 메모리 셀 및 이를 포함하는 메모리 셀 어레이 |

| US11482276B2 (en) | 2020-10-30 | 2022-10-25 | Taiwan Semiconductor Manufacturing Company Limited | System and method for read speed improvement in 3T DRAM |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4618945A (en) * | 1982-08-11 | 1986-10-21 | Tokyo Shibaura Denki Kabushiki Kaisha | Semiconductor memory device |

| JPS59121691A (ja) * | 1982-12-01 | 1984-07-13 | Fujitsu Ltd | ダイナミツク型半導体記憶装置 |

| US4744056A (en) * | 1986-02-28 | 1988-05-10 | Advanced Micro Devices, Inc. | Stable high density RAM |

| EP0386282B1 (de) * | 1989-03-06 | 1993-12-29 | Siemens Aktiengesellschaft | Integrierte Referenzspannungsquelle |

| JPH04188869A (ja) * | 1990-11-22 | 1992-07-07 | Mitsubishi Electric Corp | 接合型電界効果トランジスタとキャパシタとを含む半導体記憶装置およびその製造方法 |

| US5452244A (en) * | 1994-08-10 | 1995-09-19 | Cirrus Logic, Inc. | Electronic memory and methods for making and using the same |

| KR100218144B1 (ko) * | 1995-12-30 | 1999-09-01 | 김영환 | 3개의 트랜지스터를 구비한 디램 디바이스 및 그의 제조방법 |

| US5831897A (en) * | 1996-12-12 | 1998-11-03 | Stmicroelectronics, Inc. | SRAM memory cell design having complementary dual pass gates |

| JPH1126604A (ja) * | 1997-07-03 | 1999-01-29 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

-

1997

- 1997-06-25 KR KR1019970027409A patent/KR100248205B1/ko not_active IP Right Cessation

-

1998

- 1998-06-22 TW TW087110032A patent/TW406416B/zh not_active IP Right Cessation

- 1998-06-24 GB GB9813664A patent/GB2326763B/en not_active Expired - Fee Related

- 1998-06-25 JP JP17859098A patent/JP3896214B2/ja not_active Expired - Fee Related

- 1998-06-25 US US09/104,561 patent/US6121079A/en not_active Expired - Lifetime

-

2000

- 2000-08-21 US US09/642,379 patent/US6339240B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| GB2326763A (en) | 1998-12-30 |

| TW406416B (en) | 2000-09-21 |

| US6339240B1 (en) | 2002-01-15 |

| GB9813664D0 (en) | 1998-08-26 |

| KR19990003528A (ko) | 1999-01-15 |

| GB2326763B (en) | 2002-06-26 |

| JP2000243857A (ja) | 2000-09-08 |

| US6121079A (en) | 2000-09-19 |

| KR100248205B1 (ko) | 2000-03-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4755864A (en) | Semiconductor read only memory device with selectively present mask layer | |

| US6417549B1 (en) | Static random access memory device and method for manufacturing the same | |

| US7936579B2 (en) | Semiconductor memory device and semiconductor device group | |

| US5300804A (en) | Mask ROM device having highly integrated memory cell structure | |

| KR0120926B1 (ko) | 반도체 집적회로 장치 및 그 제조방법 | |

| JP3896214B2 (ja) | 半導体メモリデバイス及びその製造方法 | |

| JP2802455B2 (ja) | 半導体装置およびその製造方法 | |

| JP3686144B2 (ja) | 半導体記憶装置およびその製造方法 | |

| US7214572B2 (en) | Semiconductor memory device and manufacturing method thereof | |

| US4319263A (en) | Double level polysilicon series transistor devices | |

| US6091628A (en) | Static random access memory device and method of manufacturing the same | |

| US5684315A (en) | Semiconductor memory device including memory cells each having an information storage capacitor component formed over control electrode of cell selecting transistor | |

| JP3940495B2 (ja) | Sramセルの構造及びその製造方法 | |

| US6015996A (en) | Cell structure of an improved CMOS static RAM and its fabrication method | |

| US5751035A (en) | Semiconductor device provided with LDD transistors | |

| US5994180A (en) | Method of making SRAM having part of load resistance layer functions as power supply line | |

| US5598020A (en) | Semiconductor integrated circuit device and method of manufacturing the same | |

| JP4024495B2 (ja) | 半導体集積回路装置 | |

| KR100199274B1 (ko) | 반도체장치 및 그의 제조방법 | |

| JP3967746B2 (ja) | 半導体集積回路装置及びその製造方法 | |

| JP2685372B2 (ja) | スタティックramセル | |

| JP2000124152A (ja) | 半導体装置の製造方法 | |

| JP4024813B2 (ja) | 半導体集積回路装置 | |

| JPH06105776B2 (ja) | 半導体装置の製造方法 | |

| JPH04109670A (ja) | Mos型読み出し専用半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060418 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060718 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060808 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061218 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101222 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101222 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111222 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111222 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121222 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121222 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131222 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |