JP3887035B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP3887035B2 JP3887035B2 JP09952996A JP9952996A JP3887035B2 JP 3887035 B2 JP3887035 B2 JP 3887035B2 JP 09952996 A JP09952996 A JP 09952996A JP 9952996 A JP9952996 A JP 9952996A JP 3887035 B2 JP3887035 B2 JP 3887035B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating layer

- layer

- wiring

- layers

- carbon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 239

- 238000004519 manufacturing process Methods 0.000 title claims description 94

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 486

- 229910052799 carbon Inorganic materials 0.000 claims description 486

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 claims description 344

- 239000001301 oxygen Substances 0.000 claims description 250

- 229910052760 oxygen Inorganic materials 0.000 claims description 250

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 246

- 239000000463 material Substances 0.000 claims description 242

- 239000007789 gas Substances 0.000 claims description 230

- 238000000034 method Methods 0.000 claims description 196

- 229910002092 carbon dioxide Inorganic materials 0.000 claims description 181

- 239000001569 carbon dioxide Substances 0.000 claims description 163

- 238000004544 sputter deposition Methods 0.000 claims description 151

- 238000005530 etching Methods 0.000 claims description 115

- 239000000126 substance Substances 0.000 claims description 102

- 230000008569 process Effects 0.000 claims description 82

- 239000000758 substrate Substances 0.000 claims description 56

- 238000009832 plasma treatment Methods 0.000 claims description 49

- 238000000059 patterning Methods 0.000 claims description 20

- 239000012298 atmosphere Substances 0.000 claims description 18

- 238000010438 heat treatment Methods 0.000 claims description 16

- 239000004020 conductor Substances 0.000 claims description 3

- 239000007787 solid Substances 0.000 claims description 2

- 230000003647 oxidation Effects 0.000 claims 1

- 238000007254 oxidation reaction Methods 0.000 claims 1

- 230000001590 oxidative effect Effects 0.000 claims 1

- 238000000206 photolithography Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 2299

- 229910052751 metal Inorganic materials 0.000 description 231

- 239000002184 metal Substances 0.000 description 231

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 228

- 229910052814 silicon oxide Inorganic materials 0.000 description 228

- 239000003870 refractory metal Substances 0.000 description 183

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 129

- 239000010937 tungsten Substances 0.000 description 129

- 230000004888 barrier function Effects 0.000 description 126

- 229910000838 Al alloy Inorganic materials 0.000 description 122

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 122

- 239000010949 copper Substances 0.000 description 122

- 229910052721 tungsten Inorganic materials 0.000 description 117

- 229910052802 copper Inorganic materials 0.000 description 82

- 239000005360 phosphosilicate glass Substances 0.000 description 80

- 239000000203 mixture Substances 0.000 description 74

- 238000005498 polishing Methods 0.000 description 63

- 239000012535 impurity Substances 0.000 description 55

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 55

- 229920005591 polysilicon Polymers 0.000 description 55

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 54

- 229910052581 Si3N4 Inorganic materials 0.000 description 53

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 53

- 239000011241 protective layer Substances 0.000 description 51

- 238000001259 photo etching Methods 0.000 description 50

- 238000004380 ashing Methods 0.000 description 49

- 150000002739 metals Chemical class 0.000 description 49

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 42

- 229910052719 titanium Inorganic materials 0.000 description 42

- 239000010936 titanium Substances 0.000 description 42

- 229910000881 Cu alloy Inorganic materials 0.000 description 40

- 230000010354 integration Effects 0.000 description 29

- 238000005229 chemical vapour deposition Methods 0.000 description 27

- 238000001020 plasma etching Methods 0.000 description 26

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 24

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 23

- 229910052710 silicon Inorganic materials 0.000 description 23

- 239000010703 silicon Substances 0.000 description 23

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 22

- 229910052796 boron Inorganic materials 0.000 description 22

- 239000012495 reaction gas Substances 0.000 description 22

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 20

- 229910052750 molybdenum Inorganic materials 0.000 description 20

- 239000011733 molybdenum Substances 0.000 description 20

- 230000008901 benefit Effects 0.000 description 18

- 238000006243 chemical reaction Methods 0.000 description 18

- 229910001069 Ti alloy Inorganic materials 0.000 description 12

- 229910001080 W alloy Inorganic materials 0.000 description 12

- 229910045601 alloy Inorganic materials 0.000 description 12

- 239000000956 alloy Substances 0.000 description 12

- 230000008018 melting Effects 0.000 description 12

- 238000002844 melting Methods 0.000 description 12

- 229910052697 platinum Inorganic materials 0.000 description 12

- 229910052723 transition metal Inorganic materials 0.000 description 12

- 150000003624 transition metals Chemical class 0.000 description 12

- 229910052715 tantalum Inorganic materials 0.000 description 11

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 11

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 9

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 9

- IUHFWCGCSVTMPG-UHFFFAOYSA-N [C].[C] Chemical compound [C].[C] IUHFWCGCSVTMPG-UHFFFAOYSA-N 0.000 description 9

- 230000003247 decreasing effect Effects 0.000 description 9

- 239000011737 fluorine Substances 0.000 description 9

- 229910052731 fluorine Inorganic materials 0.000 description 9

- 238000005520 cutting process Methods 0.000 description 8

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 8

- 230000009172 bursting Effects 0.000 description 7

- 230000007547 defect Effects 0.000 description 7

- 230000003071 parasitic effect Effects 0.000 description 7

- -1 platinum Chemical class 0.000 description 7

- 230000001681 protective effect Effects 0.000 description 6

- 230000006872 improvement Effects 0.000 description 4

- 239000012212 insulator Substances 0.000 description 4

- 150000002926 oxygen Chemical class 0.000 description 4

- 230000002411 adverse Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/7682—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing the dielectric comprising air gaps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0149—Manufacturing their interconnections or electrodes, e.g. source or drain electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76834—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers formation of thin insulating films on the sidewalls or on top of conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76885—By forming conductive members before deposition of protective insulating material, e.g. pillars, studs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

- H01L23/53295—Stacked insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

- H01L21/76883—Post-treatment or after-treatment of the conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明は、配線間の絶縁構造に特徴を有する半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

LSIの性能の向上は、基本的に、素子の集積度を高めること、即ち素子の微細化を図ることにより達成できる。しかし、素子の集積度が極端に高くなると配線間の容量が増大するため、LSIの性能(高速動作など)を向上させることが容易ではなくなる。

【0003】

従って、マイクロプロセッサなどの超大規模集積回路(ULSIC)においては、その性能の向上を達成するために集積回路の内部配線の寄生抵抗及び寄生容量を減少させることが不可欠である。

【0004】

内部配線の寄生抵抗の減少は、抵抗率が低い材料により内部配線を構成することにより達成できる。現在では、アルミニウム合金に比べて抵抗率が30%以上低い銅を、アルミニウム合金に変えて内部配線に用いることが研究されている。

内部配線の寄生容量には、二つの成分がある。

【0005】

一つめは、異なるレベルに存在する配線間に生じる容量、即ち上下の配線間に生じる容量である。この容量は、下側の配線上に形成される層間絶縁膜の厚さを増すことにより減少させることが可能である。

【0006】

二つめは、同じレベルに存在する配線間に生じる容量、即ち左右の配線間に生じる容量である。この容量は、配線の間隔を広げること及び配線の厚さを減らすことにより達成できる。

【0007】

しかし、配線の間隔を広げると素子の集積度を低下させることになり、配線の厚さを減らすと配線抵抗が増大することになるため、かえってLSIの性能の向上を図ることができない。

【0008】

そこで、現在では、内部配線の寄生容量を減少させるために、配線間の絶縁層に誘電率εの低いものを使用することが研究されている。

【0009】

図233は、配線間に誘電率εの低い絶縁層を満たした構造の半導体装置を示すものである。

【0010】

半導体基板11上には絶縁層12が形成されている。配線13は、絶縁層12上に配置されている。配線13間及び配線13上には、弗素を含むプラズマTEOS層14が形成されている。

【0011】

この弗素を含むプラズマTEOS層14は、誘電率εが約3.3であり、弗素を含まないプラズマTEOS層に比べて誘電率εを約15%減少させている。

【0012】

しかし、近年の素子の集積度の向上に伴い、LSIの性能の向上は、配線間の誘電率εを3.3以下にしなければ達成できない状態になっている。

【0013】

【発明が解決しようとする課題】

このように、従来は、LSIの性能の向上を図るため、配線間の絶縁層の誘電率を減少させることが必須である。しかし、絶縁層の誘電率を3.3以下にすることは非常に困難であるため、絶縁層の誘電率は、素子の集積度が進む中で、LSIの性能の向上の支障となっている。

【0014】

一方、近年では、同じレベルに存在する配線間を空洞にすることで、配線間の寄生容量を低減しようとする試みがなされている。

【0015】

文献(特開平7−45701号公報)は、同じレベルに存在する配線間を空洞にする技術を開示している。この技術の特徴は、予め配線間に満たしておいた氷膜を蒸発させる点にある。

【0016】

しかし、この技術は、材料の相転移を利用しているために以下の欠点がある。第一に、配線間の水を凍結する際に体積膨脹が生じて配線に悪影響を与える。この欠点は、配線を形成した後に、相転移を利用して材料を埋め込むことに起因しており、氷膜に限られず、文献が示す全ての材料について生じる。第二に、CMP(化学的機械研磨)により氷膜を研磨する際に、摩擦熱により氷膜の全てが溶けてしまう場合がある。第三に、固体膜の蒸発前の全ての工程を低温(氷膜の場合、摂氏零度以下)で行う必要があり、ウェハの取り扱いが困難になる。

【0017】

また、この技術では、配線間の空洞には水蒸気が満たされることになるため、この水蒸気が配線のショ−トや腐食の原因となり、配線の信頼性に悪影響を与える。さらに、この技術では、異なるレベルに存在する配線間を空洞にする技術を開示していないため、配線間の寄生容量の低減は必ずしも十分とはいえない。

【0018】

本発明は、上記欠点を解決すべくなされたもので、その目的は、配線間に誘電率が低く、配線に悪影響を与えないようなガスを満たすことにより、素子の集積度の向上とLSIの性能の向上を同時に達成することである。

【0019】

【課題を解決するための手段】

本発明の半導体装置の製造方法は、半導体基板上に第1の絶縁層を形成する工程と、前記第1の絶縁層上に炭素層を形成する工程と、前記炭素層に複数の溝を形成する工程と、前記複数の溝内にのみ導電体を埋め込んで複数の配線を形成する工程と、前記炭素層上及び前記複数の配線上に酸化物からなる第2の絶縁層を形成する工程と、酸素を前記第2の絶縁層を透過させて前記炭素層と反応させることにより前記炭素層を酸化し、前記炭素層をガス層に変換する工程とを備える。

【0155】

【発明の実施の形態】

以下、図面を参照しながら、本発明の実施の形態について詳細に説明する。

【0156】

図1は、本発明の第1の実施の形態に関わる半導体装置を示している。

【0157】

半導体基板(例えば、シリコンウェハ)11上には、絶縁層(例えば、シリコン酸化層)12が形成されている。配線13は、絶縁層12上に配置されている。配線13は、銅、アルミニウム合金などの金属、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成されている。

【0158】

配線13間を満たすことがない板状の絶縁層(例えば、シリコン酸化層)14は、配線13を柱として、配線13上に形成されている。つまり、配線13間は、空洞(キャビティ)15になっている。空洞15内には、誘電率εが1.0程度のガス、即ち、酸素O2 と二酸化炭素CO2 の混合ガスが主として満たされている。

【0159】

なお、空洞内の二酸化炭素CO2 のガスの濃度は、少なくとも空気(大気)中の二酸化炭素のガスの濃度よりも高くなっている。また、空洞15を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞15内に空気を満たすようにしてもよい。

【0160】

上記構成の半導体装置によれば、配線13間には、主として酸素O2 と二酸化炭素CO2 の混合ガス、又は空気が満たされている。この混合ガス又は空気の誘電率εは、1.0程度である。これにより、配線13間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0161】

次に、図1の半導体装置の製造方法について説明する。

【0162】

まず、図2に示すように、半導体基板11上に絶縁層12を形成する。スパッタリング法などにより絶縁層12上に炭素(カ−ボン)層16を形成する。ここで、炭素層16の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0163】

スパッタリング法又はCVD法により、炭素層16上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)17を形成する。ここで、マスク材17が酸化物により構成されている場合には、マスク材17は、スパッタリング法により形成するのがよい。CVD法を用いる場合、反応ガスに含まれる酸素により炭素層16が消滅する場合があるからである。

【0164】

次に、マスク材17上にレジストを塗布し、PEP(写真蝕刻工程)を用いてこのレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材17をパタ−ニングする。この後、レジストを剥離し、マスク材17をマスクにして、異方性エッチングにより炭素層16をエッチングし、炭素層16に溝を形成する。

【0165】

なお、炭素層16は、レジストをマスクにしてエッチングしてもよい。

【0166】

レジストの剥離は、H2 SO4 とH2 O2 の薬液により行われる。レジストは、酸素プラズマ処理でも剥離できるが、酸素プラズマ処理を用いると、炭素層16も消滅してしまうからである。

【0167】

次に、図3に示すように、CVD法又はスパッタリング法により、半導体基板11上の全面に銅などから構成される導電層を形成する。化学機械的研磨(CMP)により、炭素層16の間の溝内にのみ導電層を残存させ、配線13を形成する。

【0168】

なお、CMPの代わりに、異方性エッチング又は等方性エッチングを用いて配線13を形成するようにしてもよい。

【0169】

この後、マスク材17は、剥離される。

【0170】

次に、図4に示すように、スパッタリング法により、配線13及び炭素層16上に絶縁層(例えば、シリコン酸化層)14を形成する。ここで、絶縁層14がシリコン酸化層のような酸化物の場合には、CVD法を用いない方がよい。なぜなら、反応ガスの中に酸素O2 が含まれているため、絶縁層14の形成時に、炭素層16が除去されてしまう可能性があるからである。

【0171】

次に、図5及び図6に示すように、炭素層16を灰化し、炭素層16を、酸素O2 と二酸化炭素CO2 の混合ガスが主として満たされた空洞15に変換する。なお、炭素層16の灰化は、以下の二つの方法のいずれかを使用することにより達成される。

【0172】

一つめは、酸素雰囲気中(酸素を含む雰囲気のことをいう、例えば大気中でもよい)での熱処理(温度400〜450℃、時間2h程度)である。この方法では、炭素層16が二酸化炭素CO2 に変換する反応が緩やかに進むため、炭素層16の体積の膨脹による絶縁層14の破裂を防止できる利点がある反面、処理時間が長くなる欠点がある。

【0173】

二つめは、酸素プラズマ処理(アッシャ−)である。この方法では、炭素層16が二酸化炭素CO2 に変換する反応が速やかに進むため、処理時間が短くなる利点がある反面、炭素層16の体積の膨脹による絶縁層14の破裂が生じる可能性が高くなるという欠点がある。しかし、この欠点は、絶縁層14の質の改善や酸素プラズマ処理の温度の低下などにより回避できる。

【0174】

なお、空洞15を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞15内に空気を満たすようにしてもよい。

【0175】

上述の方法によれば、配線を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。従って、容易に、図1の半導体装置を提供することができる。

図7は、本発明の第2の実施の形態に関わる半導体装置を示している。

【0176】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0177】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0178】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0179】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0180】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0181】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0182】

配線W1の上部には、絶縁層29,30が形成されている。この絶縁層29,30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0183】

なお、絶縁層29は、配線W1のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0184】

絶縁層30上には、絶縁層32が形成されている。絶縁層32は、例えば、シリコン酸化層から構成される。絶縁層32には、配線W1に達するコンタクトホ−ルが形成されている。

【0185】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層33a,33bが埋め込まれている。但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0186】

配線W2は、絶縁層32上に配置され、導電層33a,33bに接続されている。配線W2は、銅、アルミニウム合金などの金属35a,35bと、この金属35a,35bの底面及び側面を覆うU字溝状のバリア層34a,34bとから構成されている。

【0187】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0188】

配線W2の上部には、絶縁層36,37が形成されている。この絶縁層36,37は、配線W2に支えられている。配線W2間は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0189】

なお、絶縁層36は、配線W2のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層37は、配線W2間に空洞38を設ける際に重要となると共に、絶縁層37上に層を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0190】

なお、空洞31,38を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38内に空気を満たすようにしてもよい。

【0191】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞38が形成されている。

【0192】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、配線W1間及び配線W2間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0193】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0194】

次に、図7の半導体装置の製造方法について説明する。

【0195】

まず、図8に示すように、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0196】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0197】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0198】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0199】

次に、図9に示すように、スパッタリング法により、絶縁層25上に炭素(カ−ボン)層39を形成する。ここで、炭素層39の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0200】

次に、図10に示すように、スパッタリング法により、炭素層39上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)29を、約0.05μmの厚さで形成する。

【0201】

ここで、マスク材29が酸化物から構成される場合には、マスク材29は、炭素層39の消滅を防ぐため、CVD法でなく、スパッタリング法で形成するのがよい。

【0202】

次に、図11に示すように、マスク材29上にレジストを塗布し、PEP(写真蝕刻工程)を用いてこのレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材29をパタ−ニングする。この後、レジストを剥離する。マスク材29のパタ−ンは、配線のパタ−ンと同じになる。

【0203】

次に、図12に示すように、マスク材29をマスクにして、異方性エッチングにより炭素層39をエッチングする。

【0204】

なお、本実施例では、PEPにより、直接、炭素層39をエッチングすることなく、PEPで加工したマスク材29をマスクにして炭素層39をエッチングしている。

【0205】

この理由は、以下のとおりである。PEPに用いるレジストは、酸素プラズマ処理(アッシャ−)、又はH2 SO4 とH2 O2 の薬液により除去される。しかし、酸素プラズマ処理でレジストを除去する場合は、せっかくパタ−ニングした炭素層39が同時に除去されてしまう。一方、H2 SO4 とH2 O2 の薬液によりレジストを除去する場合は、導電層(高融点金属の場合のみ)26a,26bが同時に除去されてしまう。

【0206】

そこで、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材29をマスクにして炭素層39をエッチングするのがよい。

【0207】

次に、図13に示すように、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27を、配線溝XXの内面上及びマスク材29上に形成する。

【0208】

次に、図14に示すように、スパッタリング法又はCVD法により、バリア層27上に、銅、アルミニウム合金などなどから構成される金属28を形成する。なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0209】

次に、図15に示すように、化学機械的研磨(CMP)により、炭素層39の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。

【0210】

なお、CMPに代えて、異方性エッチング又は等方性エッチングを用いて配線W1を形成してもよい。

【0211】

次に、図16に示すように、スパッタリング法により、マスク材29上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。

【0212】

ここで、絶縁層30が酸化物の場合には、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層39が除去されてしまう可能性があるからである。

【0213】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0214】

次に、図17及び図18に示すように、炭素層39を灰化し、炭素層39を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。炭素層39の灰化は、以下の二つの方法のいずれかを使用することにより達成される。

【0215】

一つめは、酸素雰囲気中での熱処理(温度400〜450℃、時間2h程度)である。この方法では、炭素層39が二酸化炭素CO2 に変換する反応が緩やかに進むため、炭素層39の体積の膨脹による絶縁層29,30の破裂を防止できる利点がある反面、処理時間が長くなる欠点がある。

【0216】

二つめは、酸素プラズマ処理(アッシャ−)である。この方法では、炭素層39が二酸化炭素CO2 に変換する反応が速やかに進むため、処理時間が短くなる利点がある反面、炭素層39の体積の膨脹による絶縁層29,30の破裂が生じる可能性が高くなるという欠点がある。しかし、この欠点は、絶縁層29,30の質の改善や酸素プラズマ処理の温度の低下などにより回避できる。

【0217】

次に、図19に示すように、CVD法を用いて、絶縁層30上に低い誘電率を有する絶縁層(例えば、弗素を含むTEOSなど)32を形成する。

【0218】

次に、図20に示すように、PEP(写真蝕刻工程)及びRIE(反応性イオンエッチング)を用いて、配線W1に達するビアホ−ルを絶縁層30,32に設ける。

【0219】

次に、図21に示すように、選択成長法を用いて、ビアホ−ル内のみに、タングステンなどの高融点金属から構成される導電層33a,33bを埋め込む。なお、絶縁層30,32のビアホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0220】

次に、図22に示すように、配線W1を形成する際に使用した工程と同様の工程により配線W2を形成する。

【0221】

即ち、まず、スパッタリング法により、絶縁層32上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、配線W2の厚さと等しい値に設定されている。スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)36を、約0.05μmの厚さで形成する。

【0222】

この後、PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材36をパタ−ニングする。また、マスク材36をマスクにして、異方性エッチングにより炭素層をエッチングする。スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層34a,34bを形成する。

【0223】

スパッタリング法又はCVD法により、バリア層34a,34b上に、銅、アルミニウム合金などなどから構成される金属層35a,35bを形成する。化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層34a,34b及び金属層35a,35bを残存させ、配線W2を形成する。

【0224】

なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W2を形成するようにしてもよい。

【0225】

スパッタリング法により、マスク材36上及び配線W2上に絶縁層(例えば、シリコン酸化層)37を形成する。この後、炭素層を灰化し、炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38に変換する。

【0226】

なお、空洞31,38を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38内に空気を満たすようにしてもよい。

【0227】

上述の製造方法によれば、配線W1,W2を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。従って、容易に、図7の半導体装置を提供することができる。

【0228】

図23は、本発明の第3の実施の形態に関わる半導体装置を示している。

【0229】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0230】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0231】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0232】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0233】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0234】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0235】

配線W1の上部には、絶縁層30が形成されている。この絶縁層30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0236】

絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0237】

絶縁層30上には、絶縁層32が形成されている。絶縁層32は、例えば、シリコン酸化層から構成される。絶縁層32には、配線W1に達するコンタクトホ−ルが形成されている。

【0238】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層33a,33bが埋め込まれている。但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0239】

配線W2は、絶縁層32上に配置され、導電層33a,33bに接続されている。配線W2は、銅、アルミニウム合金などの金属35a,35bと、この金属35a,35bの底面及び側面を覆うU字溝状のバリア層34a,34bとから構成されている。

【0240】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0241】

配線W2の上部には、絶縁層37が形成されている。この絶縁層37は、配線W2に支えられている。配線W2間は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0242】

絶縁層37は、配線W2間に空洞38を設ける際に重要となると共に、絶縁層37上に層を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0243】

なお、空洞31,38を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38内に空気を満たすようにしてもよい。

【0244】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞38が形成されている。

【0245】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、配線W1間及び配線W2間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0246】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0247】

次に、図23の半導体装置の製造方法について説明する。

【0248】

まず、図24に示すように、絶縁層25上に炭素層39を形成するまでを、上述の第2の実施の形態における製造方法と同様の方法により行う。

【0249】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0250】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0251】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0252】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0253】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層39を形成する。ここで、炭素層39の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0254】

スパッタリング法により、炭素層39上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)を、約0.05μmの厚さで形成する。

【0255】

マスク材上にレジストを塗布し、PEP(写真蝕刻工程)を用いてこのレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材をパタ−ニングする。この後、レジストを剥離し、マスク材をマスクにして、異方性エッチングにより炭素層39をエッチングする。

【0256】

なお、PEPにより、直接、炭素層39をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層39をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0257】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材をマスクに炭素層39をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層39をエッチングするのがよい。

【0258】

この後、マスク材を除去し、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27を、配線溝XXの内面上及び炭素層39上に形成する。

【0259】

次に、図25に示すように、スパッタリング法又はCVD法により、バリア層27上に、銅、アルミニウム合金などなどから構成される金属28を形成する。なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0260】

次に、図26に示すように、化学機械的研磨(CMP)により、炭素層39の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。

【0261】

なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成するようにしてもよい。

【0262】

次に、図27に示すように、スパッタリング法により、炭素層39上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層39が除去されてしまう可能性があるからである。

【0263】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0264】

次に、図28及び図29に示すように、炭素層39を灰化し、炭素層39を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。炭素層39の灰化は、以下の二つの方法のいずれかを使用することにより達成される。

【0265】

一つめは、酸素雰囲気中での熱処理(温度400〜450℃、時間2h程度)である。この方法では、炭素層39が二酸化炭素CO2 に変換する反応が緩やかに進むため、炭素層39の体積の膨脹による絶縁層30の破裂を防止できる利点がある反面、処理時間が長くなる欠点がある。

【0266】

二つめは、酸素プラズマ処理(アッシャ−)である。この方法では、炭素層39が二酸化炭素CO2 に変換する反応が速やかに進むため、処理時間が短くなる利点がある反面、炭素層39の体積の膨脹による絶縁層30の破裂が生じる可能性が高くなるという欠点がある。しかし、この欠点は、絶縁層30の質の改善や酸素プラズマ処理の温度の低下などにより回避できる。

【0267】

次に、図30に示すように、CVD法を用いて、絶縁層30上に低い誘電率を有する絶縁層(例えば、弗素を含むTEOSなど)32を形成する。

【0268】

次に、図31に示すように、PEP(写真蝕刻工程)及びRIE(反応性イオンエッチング)を用いて、配線W1に達するビアホ−ルを絶縁層30,32に設ける。

【0269】

次に、図32に示すように、選択成長法を用いて、ビアホ−ル内のみに、タングステンなどの高融点金属から構成される導電層33a,33bを埋め込む。なお、絶縁層30,32のビアホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0270】

次に、図33に示すように、配線W1を形成する際に使用した工程と同様の工程により配線W2を形成する。

【0271】

即ち、まず、スパッタリング法により、絶縁層32上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、配線W2の厚さと等しい値に設定されている。スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)を、約0.05μmの厚さで形成する。

【0272】

この後、マスク材上にレジストを塗布し、PEP(写真蝕刻工程)を用いてこのレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材をパタ−ニングする。この後、レジストを剥離し、マスク材をマスクにして、異方性エッチングにより炭素層をエッチングする。

【0273】

また、マスク材を除去し、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層34a,34bを形成する。

【0274】

スパッタリング法又はCVD法により、バリア層34a,34b上に、銅、アルミニウム合金などなどから構成される金属層35a,35bを形成する。化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層34a,34b及び金属層35a,35bを残存させ、配線W2を形成する。

【0275】

なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W2を形成するようにしてもよい。

【0276】

スパッタリング法により、炭素層上及び配線W2上に絶縁層(例えば、シリコン酸化層)37を形成する。この後、炭素層を灰化し、炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38に変換する。

【0277】

なお、空洞31,38を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38内に空気を満たすようにしてもよい。

【0278】

上述の製造方法によれば、配線W1,W2を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。従って、容易に、図23の半導体装置を提供することができる。

【0279】

また、マスク材は、炭素層をパタ−ニングした後、炭素層の灰化前に、除去されている。従って、炭素層の灰化を迅速かつ正確に行うことができる。

【0280】

図34は、本発明の第4の実施の形態に関わる半導体装置を示している。

【0281】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0282】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0283】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0284】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0285】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0286】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0287】

配線W1の上部には、絶縁層29,30が形成されている。この絶縁層29,30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0288】

なお、絶縁層29は、配線W1のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0289】

絶縁層30には、配線W1に達するコンタクトホ−ルが形成されている。このコンタクトホ−ル内及びコンタクトホ−ル上には、タングステンなどの高融点金属から構成される柱状の導電層33a,33bが形成されている。

【0290】

但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0291】

柱状の導電層33a,33bの上部には、棚状の絶縁層36,37が形成されている。この絶縁層36,37は、導電層33a,33bに支えられている。柱状の導電層33a,33bの間は、空洞(キャビティ)40になっている。この空洞40には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0292】

なお、絶縁層36は、導電層33a,33bの位置や断面積を決めるもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層37は、空洞40を設ける際に重要となると共に、絶縁層37上にさらに配線を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0293】

なお、空洞31,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,40内に空気を満たすようにしてもよい。

【0294】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、導電層(上下配線のコンタクトプラグ)33a,33bの間にも、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞40が形成されている。

【0295】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、配線W1間及び導電層33a,33bの間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0296】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0297】

次に、図34の半導体装置の製造方法について説明する。

【0298】

まず、図35に示すように、絶縁層25上に配線W1を形成するまでを、上述の第2の実施の形態における製造方法と同様の方法により行う。

【0299】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0300】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0301】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0302】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0303】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0304】

スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)29を、約0.05μmの厚さで形成する。

【0305】

また、マスク材29上にレジストを塗布し、PEP(写真蝕刻工程)を用いてこのレジストをパタ−ニングする。パタ−ニングされたレジストをマスクにしてマスク材29をパタ−ニングする。この後、レジストを剥離し、マスク材29をマスクにして、異方性エッチングにより炭素層をエッチングする。

【0306】

なお、PEPにより、直接、炭素層をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0307】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材29をマスクに炭素層をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層をエッチングするのがよい。

【0308】

この後、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27a,27bを形成する。スパッタリング法又はCVD法により、バリア層27a,27b上に、銅、アルミニウム合金などから構成される金属層28a,28bを形成する。

【0309】

なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0310】

化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。

【0311】

なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成するようにしてもよい。

【0312】

スパッタリング法により、マスク材29上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層39が除去されてしまう可能性があるからである。

【0313】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0314】

この後、炭素層を灰化し、この炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。

【0315】

上述の工程により配線W1を形成した後、スパッタリング法により、絶縁層30上に炭素層41を形成する。また、スパッタリング法により、炭素層41上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)36を、約0.05μmの厚さで形成する。

【0316】

PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材36をパタ−ニングする。このマスク材36をマスクにして、異方性エッチングにより炭素層41及び絶縁層30をエッチングする。その結果、炭素層41及び絶縁層30には、配線W1に達するビアホ−ルが形成される。

【0317】

次に、図36に示すように、選択成長法を用いて、ビアホ−ル内のみに、タングステンなどの高融点金属から構成される導電層33a,33bを埋め込む。なお、絶縁層30及び炭素層41のビアホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0318】

次に、図37に示すように、スパッタリング法により、マスク材36上及び導電層33a,33b上に絶縁層(例えば、シリコン酸化層)37を形成する。ここで、絶縁層37は、炭素層41の消滅を防ぐため、CVD法により形成しない方がよい。

【0319】

また、絶縁層37の厚さは、絶縁層37がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層37の破裂なしに灰化を行うのに都合がよい。但し、絶縁層37の種類や質などにより、絶縁層37の最適な厚さは、それぞれ異なる。

【0320】

次に、図38及び図39に示すように、炭素層41を灰化し、この炭素層41を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞40に変換する。炭素層41の灰化は、以下の二つの方法のいずれかを使用することにより達成される。

【0321】

一つめは、酸素雰囲気中での熱処理(温度400〜450℃、時間2h程度)である。この方法では、炭素層41が二酸化炭素CO2 に変換する反応が緩やかに進むため、炭素層41の体積の膨脹による絶縁層36,37の破裂を防止できる利点がある反面、処理時間が長くなる欠点がある。

【0322】

二つめは、酸素プラズマ処理(アッシャ−)である。この方法では、炭素層41が二酸化炭素CO2 に変換する反応が速やかに進むため、処理時間が短くなる利点がある反面、炭素層41の体積の膨脹による絶縁層36,37の破裂が生じる可能性が高くなるという欠点がある。しかし、この欠点は、絶縁層36,37の質の改善や酸素プラズマ処理の温度の低下などにより回避できる。

【0323】

なお、空洞31,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,40内に空気を満たすようにしてもよい。

【0324】

上述の製造方法によれば、配線W1を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0325】

また、導電層(上下配線のコンタクトプラグ)33a,33bを形成するためのビアホ−ルを有する絶縁層に炭素層を用い、かつ、ビアホ−ル内に導電層33a,33bを形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0326】

これにより、多層配線構造の半導体装置において、同一層(左右)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たし、かつ、異なる層(上下)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たすことができる。

【0327】

図40は、本発明の第5の実施の形態に関わる半導体装置を示している。

【0328】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0329】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0330】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0331】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0332】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0333】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0334】

配線W1の上部には、絶縁層30が形成されている。この絶縁層30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0335】

絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0336】

絶縁層30には、配線W1に達するコンタクトホ−ルが形成されている。このコンタクトホ−ル内及びコンタクトホ−ル上には、タングステンなどの高融点金属から構成される柱状の導電層33a,33bが形成されている。

【0337】

但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0338】

柱状の導電層33a,33bの上部には、棚状の絶縁層36,37が形成されている。この絶縁層36,37は、導電層33a,33bに支えられている。柱状の導電層33a,33bの間は、空洞(キャビティ)40になっている。この空洞40には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0339】

絶縁層36は、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層37は、空洞40を設ける際に重要となると共に、絶縁層37上にさらに配線を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0340】

なお、空洞31,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,40内に空気を満たすようにしてもよい。

【0341】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、導電層(上下配線のコンタクトプラグ)33a,33bの間にも、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞40が形成されている。

【0342】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、配線W1間及び導電層33a,33bの間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0343】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0344】

次に、図40の半導体装置の製造方法について説明する。

【0345】

まず、図41に示すように、絶縁層25上に配線W1を形成するまでを、上述の第3の実施の形態における製造方法と同様の方法により行う。

【0346】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0347】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0348】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0349】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0350】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0351】

スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)を、約0.05μmの厚さで形成する。PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材をパタ−ニングする。このマスク材をマスクにして、異方性エッチングにより炭素層をエッチングする。

【0352】

なお、PEPにより、直接、炭素層をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0353】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材をマスクに炭素層をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層をエッチングするのがよい。

【0354】

この後、マスク材を除去し、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27a,27bを形成する。スパッタリング法又はCVD法により、バリア層27a,27b上に、銅、アルミニウム合金などから構成される金属28a,28bを形成する。

【0355】

なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0356】

化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成していもよい。

【0357】

スパッタリング法により、炭素層上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層39が除去されてしまう可能性があるからである。

【0358】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0359】

この後、炭素層を灰化し、この炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。

【0360】

上述の工程により配線W1を形成した後、スパッタリング法により、絶縁層30上に炭素層41を形成する。また、スパッタリング法により、炭素層41上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)36を、約0.05μmの厚さで形成する。

【0361】

マスク材36上にレジストを塗布し、PEP(写真蝕刻工程)を用いてこのレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材36をパタ−ニングする。

【0362】

この後、レジストを剥離し、マスク材36をマスクにして、異方性エッチングにより炭素層41及び絶縁層30をエッチングする。その結果、炭素層41及び絶縁層30には、配線W1に達するビアホ−ルが形成される。この後、マスク材36は、除去される。

【0363】

次に、図42に示すように、選択成長法を用いて、ビアホ−ル内のみに、タングステンなどの高融点金属から構成される導電層33a,33bを埋め込む。なお、絶縁層30,32のビアホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0364】

次に、図43に示すように、スパッタリング法により、炭素層41上及び導電層33a,33b上に絶縁層(例えば、シリコン酸化層)37を形成する。ここで、絶縁層37は、炭素層41の消滅を防ぐため、CVD法により形成しない方がよい。

【0365】

また、絶縁層37の厚さは、絶縁層37がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層37の破裂なしに灰化を行うのに都合がよい。但し、絶縁層37の種類や質などにより、絶縁層37の最適な厚さは、それぞれ異なる。

【0366】

次に、図44及び図45に示すように、炭素層41を灰化し、この炭素層41を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞40に変換する。炭素層41の灰化は、以下の二つの方法のいずれかを使用することにより達成される。

【0367】

一つめは、酸素雰囲気中での熱処理(温度400〜450℃、時間2h程度)である。この方法では、炭素層41が二酸化炭素CO2 に変換する反応が緩やかに進むため、炭素層41の体積の膨脹による絶縁層36,37の破裂を防止できる利点がある反面、処理時間が長くなる欠点がある。

【0368】

二つめは、酸素プラズマ処理(アッシャ−)である。この方法では、炭素層41が二酸化炭素CO2 に変換する反応が速やかに進むため、処理時間が短くなる利点がある反面、炭素層41の体積の膨脹による絶縁層36,37の破裂が生じる可能性が高くなるという欠点がある。しかし、この欠点は、絶縁層36,37の質の改善や酸素プラズマ処理の温度の低下などにより回避できる。

【0369】

なお、空洞31,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,40内に空気を満たすようにしてもよい。

【0370】

上述の製造方法によれば、配線W1を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0371】

また、導電層(上下配線のコンタクトプラグ)33a,33bを形成するためのビアホ−ルを有する絶縁層に炭素層を用い、かつ、ビアホ−ル内に導電層33a,33bを形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0372】

これにより、多層配線構造の半導体装置において、同一層(左右)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たし、かつ、異なる層(上下)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たすことができる。

【0373】

また、マスク材は、炭素層をパタ−ニングした後、炭素層の灰化前に、除去されている。従って、炭素層の灰化を迅速かつ正確に行うことができる。

【0374】

図46は、本発明の第6の実施の形態に関わる半導体装置を示している。

【0375】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0376】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0377】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0378】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0379】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0380】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0381】

配線W1の上部には、絶縁層29,30が形成されている。この絶縁層29,30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0382】

なお、絶縁層29は、配線W1のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0383】

絶縁層30には、配線W1に達するコンタクトホ−ルが形成されている。このコンタクトホ−ル内及びコンタクトホ−ル上には、タングステンなどの高融点金属から構成される柱状の導電層33a,33bが形成されている。但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0384】

導電層33a,33bの上部には、絶縁層42,43が形成されている。この絶縁層42,43は、導電層33a,33bに支えられている。導電層33a,33bの間は、空洞(キャビティ)40になっている。この空洞40には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0385】

なお、絶縁層42は、導電層33a,33bの位置及び断面積を決めるもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層43は、導電層33a,33bの間に空洞40を設ける際に重要となると共に、絶縁層43上に配線W2を積み重ねる際の土台となる重要なものである。絶縁層43は、例えば、シリコン酸化膜などから構成される。

【0386】

配線W2は、絶縁層43上に配置され、導電層33a,33bに接続されている。配線W2は、銅、アルミニウム合金などの金属35a,35bと、この金属35a,35bの底面及び側面を覆うU字溝状のバリア層34a,34bとから構成されている。

【0387】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0388】

配線W2の上部には、絶縁層36,37が形成されている。この絶縁層36,37は、配線W2に支えられている。配線W2間は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0389】

絶縁層36は、配線W2のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層37は、配線W2間に空洞38を設ける際に重要となると共に、絶縁層37上に層を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0390】

なお、空洞31,38,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40に空気を満たすようにしてもよい。

【0391】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞38が形成されている。

【0392】

さらに、導電層33a,33bの間、即ち、配線W1と配線W2の間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞40が形成されている。

【0393】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、同一層(左右)の配線間及び異なる層(上下)の配線間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0394】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0395】

次に、図46の半導体装置の製造方法について説明する。

【0396】

まず、図47に示すように、絶縁層25上に配線W1を形成するまでを、上述の第2の実施の形態における製造方法と同様の方法により行う。

【0397】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0398】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0399】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0400】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0401】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0402】

スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)29を、約0.05μmの厚さで形成する。

【0403】

マスク材29上にレジストを塗布し、PEP(写真蝕刻工程)を用いてレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材29をパタ−ニングする。この後、レジストを剥離し、マスク材29をマスクにして、異方性エッチングにより炭素層をエッチングする。

【0404】

なお、PEPにより、直接、炭素層をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0405】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材29をマスクに炭素層をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層をエッチングするのがよい。

【0406】

この後、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27a,27bを形成する。スパッタリング法又はCVD法により、バリア層27a,27b上に、銅、アルミニウム合金などから構成される金属28a,28bを形成する。

【0407】

なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0408】

化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成するようにしてもよい。

【0409】

スパッタリング法により、マスク材29上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層39が除去されてしまう可能性があるからである。

【0410】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0411】

この後、炭素層を灰化し、この炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。

【0412】

上述の工程により配線W1を形成した後、スパッタリング法により、絶縁層30上に炭素層41を形成する。また、スパッタリング法により、炭素層41上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)42を、約0.05μmの厚さで形成する。

【0413】

PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材42をパタ−ニングする。このマスク材42をマスクにして、異方性エッチングにより炭素層41及び絶縁層30をエッチングする。その結果、炭素層41及び絶縁層30には、配線W1に達するビアホ−ルが形成される。

【0414】

次に、図48に示すように、選択成長法を用いて、ビアホ−ル内のみに、タングステンなどの高融点金属から構成される導電層33a,33bを埋め込む。なお、絶縁層30及び炭素層41のビアホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0415】

次に、図49に示すように、スパッタリング法により、マスク材42及び導電層33a,33b上に絶縁層(例えば、シリコン酸化層)43を形成する。ここで、絶縁層43は、CVD法により形成しない方がよい。なぜなら、絶縁層43を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層43の形成時に、炭素層41が除去されてしまう可能性があるからである。

【0416】

また、絶縁層43の厚さは、絶縁層43がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層43の破裂なしに灰化を行うのに都合がよい。但し、絶縁層43の種類や質などにより、絶縁層43の最適な厚さは、それぞれ異なる。

【0417】

次に、図50に示すように、配線W1を形成する際に使用した工程と同様の工程により配線W2を形成する。

【0418】

即ち、まず、スパッタリング法により、絶縁層43上に炭素(カ−ボン)層44を形成する。ここで、炭素層44の厚さは、配線W2の厚さと等しい値に設定されている。スパッタリング法により、炭素層44上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)36を、約0.05μmの厚さで形成する。マスク材36上にレジストを塗布し、PEP(写真蝕刻工程)を用いてレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材36をパタ−ニングする。

【0419】

この後、レジストを剥離し、マスク材36をマスクにして異方性エッチングにより炭素層44をエッチングする。

【0420】

スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層34a,34bを、絶縁層43上及びマスク材36上に形成する。

【0421】

スパッタリング法又はCVD法により、バリア層34a,34b上に、銅、アルミニウム合金などなどから構成される金属層35a,35bを形成する。化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層34a,34b及び金属層35a,35bを残存させ、配線W2を形成する。

【0422】

スパッタリング法により、マスク材36上及び配線W2上に絶縁層(例えば、シリコン酸化層)37を形成する。

【0423】

絶縁層37の厚さは、絶縁層37がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層37の破裂なしに灰化を行うのに都合がよい。但し、絶縁層37の種類や質などにより、絶縁層37の最適な厚さは、それぞれ異なる。

【0424】

次に、図51及び図52に示すように、酸素雰囲気中での熱処理又は酸素プラズマ処理により、炭素層41,44を同時に灰化し、炭素層41を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞40に変換し、炭素層44を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38に変換する。

【0425】

なお、空洞31,38,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40に空気を満たすようにしてもよい。

【0426】

上述の製造方法によれば、配線W1,W2を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0427】

また、導電層(上下配線のコンタクトプラグ)33a,33bを形成するためのビアホ−ルを有する絶縁層に炭素層を用い、かつ、ビアホ−ル内に導電層33a,33bを形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0428】

これにより、多層配線構造の半導体装置において、同一層(左右)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たし、かつ、異なる層(上下)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たすことができる。

【0429】

図53は、本発明の第7の実施の形態に関わる半導体装置を示している。

【0430】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0431】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0432】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0433】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0434】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0435】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0436】

配線W1の上部には、絶縁層30が形成されている。この絶縁層30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0437】

絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0438】

絶縁層30には、配線W1に達するコンタクトホ−ルが形成されている。このコンタクトホ−ル内及びコンタクトホ−ル上には、タングステンなどの高融点金属から構成される柱状の導電層33a,33bが形成されている。但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0439】

導電層33a,33bの上部には、絶縁層43が形成されている。この絶縁層43は、導電層33a,33bに支えられている。導電層33a,33bの間は、空洞(キャビティ)40になっている。この空洞40には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0440】

絶縁層43は、導電層33a,33bの間に空洞40を設ける際に重要となると共に、絶縁層43上に配線W2を積み重ねる際の土台となる重要なものである。絶縁層43は、例えば、シリコン酸化膜などから構成される。

【0441】

配線W2は、絶縁層43上に配置され、導電層33a,33bに接続されている。配線W2は、銅、アルミニウム合金などの金属35a,35bと、この金属35a,35bの底面及び側面を覆うU字溝状のバリア層34a,34bとから構成されている。

【0442】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0443】

配線W2の上部には、絶縁層37が形成されている。この絶縁層37は、配線W2に支えられている。配線W2間は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0444】

絶縁層37は、配線W2間に空洞38を設ける際に重要となると共に、絶縁層37上に層を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0445】

なお、空洞31,38,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40に空気を満たすようにしてもよい。

【0446】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞38が形成されている。

【0447】

さらに、導電層33a,33bの間、即ち、配線W1と配線W2の間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞40が形成されている。

【0448】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、同一層(左右)の配線間及び異なる層(上下)の配線間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0449】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0450】

次に、図53の半導体装置の製造方法について説明する。

【0451】

まず、図54に示すように、絶縁層25上に配線W1を形成するまでを、上述の第3の実施の形態における製造方法と同様の方法により行う。

【0452】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0453】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0454】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0455】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0456】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0457】

スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)29を、約0.05μmの厚さで形成する。PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材29をパタ−ニングする。このマスク材29をマスクにして、異方性エッチングにより炭素層をエッチングする。

【0458】

なお、PEPにより、直接、炭素層をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0459】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材29をマスクに炭素層をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層をエッチングするのがよい。

【0460】

この後、マスク材29を除去し、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27a,27bを形成する。スパッタリング法又はCVD法により、バリア層27a,27b上に、銅、アルミニウム合金などから構成される金属28a,28bを形成する。

【0461】

なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0462】

化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成するようにしてもよい。

【0463】

スパッタリング法により、炭素層上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層39が除去されてしまう可能性があるからである。

【0464】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0465】

この後、炭素層を灰化し、この炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。

【0466】

上述の工程により配線W1を形成した後、スパッタリング法により、絶縁層30上に炭素層41を形成する。また、スパッタリング法により、炭素層41上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)42を、約0.05μmの厚さで形成する。

【0467】

マスク材42上にレジストを塗布し、PEP(写真蝕刻工程)を用いてレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材42をパタ−ニングする。この後、レジストを剥離し、マスク材42をマスクにして、異方性エッチングにより炭素層41及び絶縁層30をエッチングする。その結果、炭素層41及び絶縁層30には、配線W1に達するビアホ−ルが形成される。

【0468】

次に、図55に示すように、選択成長法を用いて、ビアホ−ル内のみに、タングステンなどの高融点金属から構成される導電層33a,33bを埋め込む。なお、絶縁層30及び炭素層41のビアホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0469】

次に、図56に示すように、スパッタリング法により、炭素層41及び導電層33a,33b上に絶縁層(例えば、シリコン酸化層)43を形成する。ここで、絶縁層43は、CVD法により形成しない方がよい。なぜなら、絶縁層43を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層43の形成時に、炭素層41が除去されてしまう可能性があるからである。

【0470】

また、絶縁層43の厚さは、絶縁層43がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層43の破裂なしに灰化を行うのに都合がよい。但し、絶縁層43の種類や質などにより、絶縁層43の最適な厚さは、それぞれ異なる。

【0471】

次に、図57に示すように、配線W1を形成する際に使用した工程と同様の工程により配線W2を形成する。

【0472】

即ち、まず、スパッタリング法により、絶縁層43上に炭素(カ−ボン)層44を形成する。ここで、炭素層44の厚さは、配線W2の厚さと等しい値に設定されている。スパッタリング法により、炭素層44上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)を、約0.05μmの厚さで形成する。

【0473】

この後、PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材をパタ−ニングする。マスク材をマスクにして、異方性エッチングにより炭素層44及び絶縁層43をエッチングする。

【0474】

マスク材を除去し、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層34a,34bを、配線溝YYの内面上及び炭素層44上に形成する。

【0475】

スパッタリング法又はCVD法により、バリア層34a,34b上に、銅、アルミニウム合金などなどから構成される金属層35a,35bを形成する。化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層34a,34b及び金属層35a,35bを残存させ、配線W2を形成する。

【0476】

なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W2を形成するようにしてもよい。

【0477】

スパッタリング法により、炭素層44上及び配線W2上に絶縁層(例えば、シリコン酸化層)37を形成する。

【0478】

絶縁層37の厚さは、絶縁層37がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層37の破裂なしに灰化を行うのに都合がよい。但し、絶縁層37の種類や質などにより、絶縁層37の最適な厚さは、それぞれ異なる。

【0479】

次に、図58及び図59に示すように、酸素雰囲気中での熱処理又は酸素プラズマ処理により、炭素層41,44を同時に灰化し、炭素層41を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞40に変換し、炭素層44を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38に変換する。

【0480】

なお、空洞31,38,40を、製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40に空気を満たすようにしてもよい。

【0481】

上述の製造方法によれば、配線W1,W2を形成するための溝を有する絶縁層に炭素層を用い、かつ、溝内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0482】

また、導電層(上下配線のコンタクトプラグ)33a,33bを形成するためのビアホ−ルを有する絶縁層に炭素層を用い、かつ、ビアホ−ル内に導電層33a,33bを形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0483】

これにより、多層配線構造の半導体装置において、同一層(左右)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たし、かつ、異なる層(上下)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たすことができる。

【0484】

また、マスク材は、炭素層をパタ−ニングした後、炭素層の灰化前に、除去されている。従って、炭素層の灰化を迅速かつ正確に行うことができる。

【0485】

図60は、本発明の第8の実施の形態に関わる半導体装置を示している。

【0486】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0487】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0488】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0489】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0490】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属28a,28bと、この金属28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0491】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0492】

配線W1の上部には、絶縁層29,30が形成されている。この絶縁層29,30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0493】

なお、絶縁層29は、配線W1のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0494】

絶縁層30には、配線W1に達するコンタクトホ−ルが形成されている。このコンタクトホ−ル内及びコンタクトホ−ル上には、銅、アルミニウム合金などの金属層35a,35bと、この金属層35a,35bの底面及び側面を覆うバリア層34a,34bとから構成される配線W2が形成されている。

【0495】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0496】

配線W2の上部と下部の間には、絶縁層(例えば、シリコン酸化層)43が形成されている。この絶縁層43は、配線W2に支えられている。配線W2の下部は、柱状であり、また、配線W2の上部は、線状であり、絶縁層43上に配置されている。

【0497】

配線W2上には、絶縁層(例えば、シリコン酸化層)37が形成されている。配線W2の下部の間(上下の配線W1と配線W2の間)は、空洞(キャビティ)40になっている。この空洞40には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0498】

配線W2の上部の間(左右の配線W2の間)は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0499】

なお、空洞31,38,40を製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40内に空気を満たすようにしてもよい。

【0500】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞38が形成されている。

【0501】

さらに、導電層33a,33bの間、即ち、配線W1と配線W2の間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞40が形成されている。

【0502】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、同一層(左右)の配線間及び異なる層(上下)の配線間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0503】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0504】

次に、図60の半導体装置の製造方法について説明する。

【0505】

まず、図61に示すように、絶縁層25上に配線W1を形成するまでを、上述の第2の実施の形態における製造方法と同様の方法により行う。

【0506】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0507】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0508】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0509】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0510】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0511】

スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)29を、約0.05μmの厚さで形成する。

【0512】

マスク材29上にレジストを塗布し、PEP(写真蝕刻工程)を用いてレジストをパタ−ニングする。また、パタ−ニングされたレジストをマスクにしてマスク材29をパタ−ニングする。この後、レジストを剥離し、マスク材29をマスクにして異方性エッチングにより炭素層をエッチングする。

【0513】

なお、PEPにより、直接、炭素層をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0514】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材29をマスクに炭素層をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層をエッチングするのがよい。

【0515】

この後、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27a,27bを形成する。スパッタリング法又はCVD法により、バリア層27a,27b上に、銅、アルミニウム合金などから構成される金属層28a,28bを形成する。

【0516】

なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0517】

化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層27a,27b及び金属28a,28bを残存させ、配線W1を形成する。なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成してもよい。

【0518】

スパッタリング法により、マスク材29上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層が除去されてしまう可能性があるからである。

【0519】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0520】

この後、炭素層を灰化し、この炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。

【0521】

上述の工程により配線W1を形成した後、スパッタリング法により、絶縁層30上に炭素層41を形成する。また、スパッタリング法により、炭素層41上に絶縁層(例えば、シリコン酸化層)43を約0.05μmの厚さで形成する。

【0522】

なお、絶縁層43は、CVD法により形成しない方がよい。なぜなら、絶縁層43を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層43の形成時に、炭素層41が除去されてしまう可能性があるからである。

【0523】

また、絶縁層43の厚さは、絶縁層43がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層43の破裂なしに灰化を行うのに都合がよい。但し、絶縁層43の種類や質などにより、絶縁層43の最適な厚さは、それぞれ異なる。

【0524】

続けて、スパッタリング法により、絶縁層43上に炭素層44を形成する。

【0525】

この後、炭素層44をパタ−ニングして、配線を形成するための溝を炭素層44に設ける。炭素層44のパタ−ニングには、PEP(写真蝕刻工程)とRIEを用いる方法と、PEPとRIEで加工したマスク材をマスクにパタ−ニングする方法の2つがある。

【0526】

本実施例では、PEPとRIEを用いる方法について述べる。即ち、炭素層44上にレジスト45を形成する。レジスト45をパタ−ニングした後、このレジスト45をマスクに異方性エッチングにより炭素層44をエッチングし、炭素層44に溝を形成する。

【0527】

この後、H2 SO4 とH2 O2 の薬液を用いて、レジスト45を除去する。なお、酸素プラズマ処理は炭素層44の消滅を招くため、この酸素プラズマ処理はレジスト45の剥離に用いない。

【0528】

次に、図62に示すように、炭素層44上に再びレジスト46を形成する。レジスト46をパタ−ニングした後、このレジスト46をマスクにして、異方性エッチングにより、溝の底部に露出した絶縁層43及び炭素層41をエッチングする。

【0529】

この後、H2 SO4 とH2 O2 の薬液を用いて、レジスト46を除去する。なお、酸素プラズマ処理は炭素層46の消滅を招くため、この酸素プラズマ処理はレジスト46の剥離に用いない。

【0530】

次に、図63に示すように、異方性エッチングを用いて、溝の底部に露出した絶縁層30をエッチングし、配線W1に達するビアホ−ルを形成する。

【0531】

スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層34を、炭素層44上、炭素層44の間の溝内及び炭素層41のビアホ−ル内に形成する。また、スパッタリング法又はCVD法により、バリア層34上に、銅、アルミニウム合金などなどから構成される金属層35を形成する。

【0532】

次に、図64に示すように、化学機械的研磨(CMP)又はエッチングにより、炭素層44の間の溝内及び炭素層41のビアホ−ル内に、それぞれバリア層34a,34b及び金属層35a,35bを残存させる。

【0533】

また、スパッタリング法により、炭素層44上に絶縁層(例えば、シリコン酸化層)37を、約0.05μmの厚さで形成する。

【0534】

なお、絶縁層37,43の厚さは、絶縁層37,43がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層37,43の破裂なしに灰化を行うのに都合がよい。但し、絶縁層37,43の種類や質などにより、絶縁層37,43の最適な厚さは、それぞれ異なる。

【0535】

次に、図65及び図66に示すように、酸素雰囲気中での熱処理又は酸素プラズマ処理により、炭素層41,44を同時を灰化し、炭素層41を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞40に変換し、炭素層44を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38に変換する。

【0536】

なお、空洞31,38,40を製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40内に空気を満たすようにしてもよい。

【0537】

上述の製造方法によれば、配線W1,W2を形成するための溝又はビアホ−ルを有する絶縁層に炭素層を用い、かつ、溝内及びビアホ−ル内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0538】

また、配線W2は、コンタクトプラグを用いることなく、配線W1に直接接続されるているため、上述の第2〜7の実施の形態における製造方法に比べて大幅に工程数を減らすことができる。

【0539】

これにより、多層配線構造の半導体装置において、同一層(左右)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たし、かつ、異なる層(上下)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たすことができる。

【0540】

図67は、本発明の第9の実施の形態に関わる半導体装置を示している。

【0541】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0542】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0543】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0544】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0545】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属層28a,28bと、この金属層28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0546】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0547】

配線W1の上部には、絶縁層30が形成されている。この絶縁層30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0548】

絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0549】

絶縁層30には、配線W1に達するコンタクトホ−ルが形成されている。このコンタクトホ−ル内及びコンタクトホ−ル上には、銅、アルミニウム合金などの金属層35a,35bと、この金属層35a,35bの底面及び側面を覆うバリア層34a,34bとから構成される配線W2が形成されている。

【0550】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0551】

配線W2の上部と下部の間には、絶縁層(例えば、シリコン酸化層)43が形成されている。この絶縁層43は、配線W2に支えられている。配線W2の下部は、柱状であり、また、配線W2の上部は、線状であり、絶縁層43上に配置されている。

【0552】

配線W2上には、絶縁層(例えば、シリコン酸化層)37が形成されている。配線W2の下部の間(上下の配線W1と配線W2の間)は、空洞(キャビティ)40になっている。この空洞40には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0553】

配線W2の上部の間(左右の配線W2の間)は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0554】

なお、空洞31,38,40を製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40内に空気を満たすようにしてもよい。

【0555】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞38が形成されている。

【0556】

さらに、導電層35a,35bの間、即ち、配線W1と配線W2の間には、酸素O2 と二酸化炭素CO2 の混合ガス又は空気が満たされた空洞40,43が形成されている。

【0557】

この混合ガス又は空気の誘電率εは、1.0程度である。これにより、同一層(左右)の配線間及び異なる層(上下)の配線間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0558】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0559】

次に、図67の半導体装置の製造方法について説明する。

【0560】

まず、図68に示すように、絶縁層25上に配線W1を形成するまでを、上述の第3の実施の形態における製造方法と同様の方法により行う。

【0561】

即ち、LOCOS法により半導体基板21上にフィ−ルド酸化層22を形成する。また、フィ−ルド酸化層22に囲まれた素子領域に、例えば、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有するMOSトランジスタを形成する。

【0562】

半導体基板21上の全面に、MOSトランンジスタを完全に覆う絶縁層(BPSGやPSGなど)25を形成する。この後、化学機械的研磨(CMP)を行い、絶縁層25の表面を平坦にする。

【0563】

PEP(写真蝕刻工程)により、絶縁層25にソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルを形成する。選択成長法により、絶縁層25のコンタクトホ−ル内のみに、タングステンなどの高融点金属から構成される導電層26a,26bを埋め込む。

【0564】

なお、絶縁層25のコンタクトホ−ル内には、高融点金属以外の他の材料を埋め込んでも構わない。

【0565】

スパッタリング法により、絶縁層25上に炭素(カ−ボン)層を形成する。ここで、炭素層の厚さは、LSIの内部配線の厚さと等しい値(例えば、約0.7〜約0.2μm)に設定される。

【0566】

スパッタリング法により、炭素層上にマスク材(例えば、シリコン酸化層やシリコン窒化層など)を、約0.05μmの厚さで形成する。PEP(写真蝕刻工程)及び異方性エッチングを用いて、マスク材をパタ−ニングする。このマスク材をマスクにして、異方性エッチングにより炭素層をエッチングする。

【0567】

なお、PEPにより、直接、炭素層をエッチングすることなく、PEPで加工したマスク材をマスクにして炭素層をエッチングする理由は、上述の第2の実施の形態における製造方法で説明した理由と同じである。

【0568】

従って、導電層26a,26bが高融点金属の場合には、PEPで加工したマスク材をマスクに炭素層をエッチングし、導電層26a,26bがH2 SO4 とH2 O2 の薬液により腐蝕されないような材質である場合には、レジストをマスクに炭素層をエッチングするのがよい。

【0569】

この後、マスク材を除去し、スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層27a,27bを形成する。スパッタリング法又はCVD法により、バリア層27上に、銅、アルミニウム合金などから構成される金属層28a,28bを形成する。

【0570】

なお、配線は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属であってもよい。

【0571】

化学機械的研磨(CMP)により、炭素層の間の溝内にのみ、バリア層27a,27b及び金属層28a,28bを残存させ、配線W1を形成する。なお、CMPに代えて、異方性エッチング又は等方性エッチングにより配線W1を形成するようにしてもよい。

【0572】

スパッタリング法により、炭素層上及び配線W1上に絶縁層(例えば、シリコン酸化層)30を形成する。ここで、絶縁層30は、CVD法により形成しない方がよい。なぜなら、絶縁層30を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層30の形成時に、炭素層が除去されてしまう可能性があるからである。

【0573】

また、絶縁層30の厚さは、絶縁層30がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層30の破裂なしに灰化を行うのに都合がよい。但し、絶縁層30の種類や質などにより、絶縁層30の最適な厚さは、それぞれ異なる。

【0574】

この後、炭素層を灰化し、この炭素層を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31に変換する。

【0575】

上述の工程により配線W1を形成した後、スパッタリング法により、絶縁層30上に炭素層41を形成する。また、スパッタリング法により、炭素層41上に絶縁層(例えば、シリコン酸化層)43を約0.05μmの厚さで形成する。

【0576】

なお、絶縁層43は、CVD法により形成しない方がよい。なぜなら、絶縁層43を形成する際の反応ガス中には、酸素O2 ガスが含まれているため、絶縁層43の形成時に、炭素層41が除去されてしまう可能性があるからである。

【0577】

また、絶縁層43の厚さは、絶縁層43がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層43の破裂なしに灰化を行うのに都合がよい。但し、絶縁層43の種類や質などにより、絶縁層43の最適な厚さは、それぞれ異なる。

【0578】

続けて、スパッタリング法により、絶縁層43上に炭素層44を形成する。

【0579】

この後、炭素層44をパタ−ニングして、配線を形成するための溝を炭素層44に設ける。炭素層44のパタ−ニングには、PEP(写真蝕刻工程)とRIEを用いる方法と、PEPとRIEで加工したマスク材をマスクにパタ−ニングする方法の2つがある。

【0580】

本実施例では、PEPとRIEを用いる方法について述べる。即ち、炭素層44上にレジスト45を形成する。レジスト45をパタ−ニングした後、このレジスト45をマスクに異方性エッチングにより炭素層44をエッチングし、炭素層44に溝を形成する。

【0581】

この後、H2 SO4 とH2 O2 の薬液を用いて、レジスト45を除去する。なお、酸素プラズマ処理は炭素層44の消滅を招くため、この酸素プラズマ処理はレジスト45の剥離に用いない。

【0582】

次に、図69に示すように、炭素層44上に再びレジスト46を形成する。レジスト46をパタ−ニングした後、このレジスト46をマスクにして異方性エッチングにより溝の底部に露出した絶縁層43及び炭素層41をエッチングする。

この後、H2 SO4 とH2 O2 の薬液を用いて、レジスト46を除去する。なお、酸素プラズマ処理は炭素層46の消滅を招くため、この酸素プラズマ処理はレジスト46の剥離に用いない。

【0583】

次に、図70に示すように、異方性エッチングを用いて、溝の底部に露出した絶縁層30をエッチングし、配線W1に達するビアホ−ルを形成する。

【0584】

スパッタリング法又はCVD法により、例えば、チタンと窒化チタンの積層から構成されるバリア層34を、炭素層44上、炭素層44の間の溝内及び炭素層41のビアホ−ル内に形成する。また、スパッタリング法又はCVD法により、バリア層34上に、銅、アルミニウム合金などなどから構成される金属層35を形成する。

【0585】

次に、図71に示すように、化学機械的研磨(CMP)又はエッチングにより、炭素層44の間の溝内及び炭素層41のビアホ−ル内に、それぞれバリア層34a,34b及び金属層35a,35bを残存させる。

【0586】

また、スパッタリング法により、炭素層44上に絶縁層(例えば、シリコン酸化層)37を、約0.05μmの厚さで形成する。

【0587】

なお、絶縁層37,43の厚さは、絶縁層37,43がシリコン酸化層の場合は、0.01〜0.1μmの範囲にあるのが、絶縁層37,43の破裂なしに灰化を行うのに都合がよい。但し、絶縁層37,43の種類や質などにより、絶縁層37,43の最適な厚さは、それぞれ異なる。

【0588】

次に、図72及び図73に示すように、酸素雰囲気中での熱処理又は酸素プラズマ処理により、炭素層41,44を同時を灰化し、炭素層41を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞40に変換し、炭素層44を、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38に変換する。

【0589】

なお、空洞31,38,40を製造時に空気に接触させることにより、又はパッケ−ジに穴を設けておくことにより、空洞31,38,40内に空気を満たすようにしてもよい。

【0590】

上述の製造方法によれば、配線W1,W2を形成するための溝又はビアホ−ルを有する絶縁層に炭素層を用い、かつ、溝内及びビアホ−ル内に配線を形成した後にこの炭素層を灰化してガスが満たされた空洞に変換している。

【0591】

また、配線W2は、コンタクトプラグを用いることなく、配線W1に直接接続されるているため、上述の第2〜7の実施の形態における製造方法に比べて大幅に工程数を減らすことができる。

【0592】

これにより、多層配線構造の半導体装置において、同一層(左右)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たし、かつ、異なる層(上下)の配線間に酸素O2 と二酸化炭素CO2 の混合ガス又は空気を満たすことができる。

【0593】

また、マスク材は、炭素層をパタ−ニングした後、炭素層の灰化前に、除去されている。従って、炭素層の灰化を迅速かつ正確に行うことができる。

【0594】

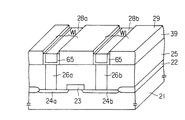

図74乃至図76は、本発明の第10の実施の形態に関わる半導体装置を示している。

【0595】

この半導体装置は、図74に示すように、ウェハ47に形成される複数のチップ48の各々に形成される。

【0596】

図76を参照して、この実施の形態に関わる半導体装置について説明する。

【0597】

半導体基板(例えば、シリコンウェハ)21上には、フィ−ルド酸化層(例えば、シリコン酸化層)22が形成されている。フィ−ルド酸化層22に囲まれた素子領域には、MOSトランジスタが形成されている。このMOSトランジスタは、ゲ−ト電極23及びソ−ス・ドレイン領域24a,24bを有している。

【0598】

絶縁層25は、MOSトランジスタを覆っている。絶縁層25は、例えば、硼素燐ケイ酸ガラス(BPSG)や燐ケイ酸ガラス(PSG)などから構成することができる。

【0599】

絶縁層25の表面は、平坦である。絶縁層25の表面は、化学機械的研磨(CMP)により平坦にすることができる。絶縁層25には、ソ−ス・ドレイン領域24a,24bに達するコンタクトホ−ルが形成されている。

【0600】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層26a,26bが埋め込まれている。但し、導電層26a,26bは、高融点金属以外の他の材料から構成しても構わない。

【0601】

配線W1は、絶縁層25上に配置され、導電層26a,26bに接続されている。配線W1は、銅、アルミニウム合金などの金属層28a,28bと、この金属層28a,28bの底面及び側面を覆うU字溝状のバリア層27a,27bとから構成されている。

【0602】

なお、配線W1は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層27a,27bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0603】

配線W1の上部には、絶縁層29,30が形成されている。この絶縁層29,30は、配線W1に支えられている。配線W1間は、空洞(キャビティ)31になっている。この空洞31には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0604】

なお、絶縁層29は、配線W1のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層30は、配線W1間に空洞31を設ける際に重要となると共に、絶縁層30上に層を積み重ねる際の土台となる重要なものである。絶縁層30は、例えば、シリコン酸化膜などから構成される。

【0605】

絶縁層30上には、絶縁層32が形成されている。絶縁層32は、例えば、シリコン酸化層から構成される。絶縁層32には、配線W1に達するコンタクトホ−ルが形成されている。

【0606】

このコンタクトホ−ル内には、タングステンなどの高融点金属から構成される導電層33a,33bが埋め込まれている。但し、導電層33a,33bは、高融点金属以外の他の材料から構成しても構わない。

【0607】

配線W2は、絶縁層32上に配置され、導電層33a,33bに接続されている。配線W2は、銅、アルミニウム合金などの金属層35a,35bと、この金属層35a,35bの底面及び側面を覆うU字溝状のバリア層34a,34bとから構成されている。

【0608】

なお、配線W2は、銅、アルミニウム合金などの金属に限られず、例えば、不純物を含むポリシリコンなどの半導体、タングステンなどの高融点金属から構成してもよい。また、バリア層34a,34bは、例えば、チタンと窒化チタンの積層などから構成することができる。

【0609】

配線W2の上部には、絶縁層36,37が形成されている。この絶縁層36,37は、配線W2に支えられている。配線W2間は、空洞(キャビティ)38になっている。この空洞38には、主として酸素O2 と二酸化炭素CO2 の混合ガスが満たされている。

【0610】

なお、絶縁層36は、配線W2のパタ−ンを決定するもので、例えば、シリコン酸化層やシリコン窒化層などから構成される。絶縁層37は、配線W2間に空洞38を設ける際に重要となると共に、絶縁層37上に層を積み重ねる際の土台となる重要なものである。絶縁層37は、例えば、シリコン酸化膜などから構成される。

【0611】

また、各チップ48の縁部には、そのチップの縁に沿ってリング状のガ−ドリングGが形成されている。このガ−ドリングGは、空洞31に形成されるバリア層27c及び金属層28cと、空洞38に形成されるバリア層34c及び金属層35cと、絶縁層30,32中に形成される導電層33cとから構成される。

【0612】

空洞31に形成されるバリア層27c及び金属層28cは、配線W1と同じ構成を有し、空洞38に形成されるバリア層34c及び金属層35cは、配線W2と同じ構成を有し、絶縁層30,32中に形成される導電層33cは、導電層(コンタクトプラグ)33a,33bと同じ構成を有している。

【0613】

なお、図77に示すように、絶縁層30,32中の導電層33cは、なくてもよい。

【0614】

上記構成の半導体装置によれば、配線W1間には、酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞31が形成され、配線W2間には、酸素O2 と二酸化炭素CO2 の混合ガスが満たされた空洞38が形成されている。

【0615】

この混合ガスの誘電率εは、1.0程度である。これにより、配線W1間及び配線W2間をシリコン酸化層などの絶縁層で満たす場合に比べて、極端に誘電率を低下させることができる。

【0616】

従って、素子の集積度の向上とLSIの性能の向上を同時に達成することができる。

【0617】

さらに、チップ48の縁部には、リング状のガ−ドリングGが形成されている。従って、ウェハから個々のチップを切り出した後において、水分H2 Oがチップの縁から空洞31,38を介して配線W1,W2に達するという事態が回避できる。

【0618】

即ち、ガ−ドリングGを設けることにより、チップ内の配線W1,W2を、水分H2 Oに対して保護することができる。

【0619】

また、この実施の形態における半導体装置は、上述の第2の実施の形態における製造方法を用いることにより、容易に形成することができる。

【0620】

図78及び図79は、本発明の第11の実施の形態に関わる半導体装置を示している。

【0621】