JP2014090207A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2014090207A JP2014090207A JP2014004209A JP2014004209A JP2014090207A JP 2014090207 A JP2014090207 A JP 2014090207A JP 2014004209 A JP2014004209 A JP 2014004209A JP 2014004209 A JP2014004209 A JP 2014004209A JP 2014090207 A JP2014090207 A JP 2014090207A

- Authority

- JP

- Japan

- Prior art keywords

- region

- layer

- conductivity type

- type

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Thin Film Transistor (AREA)

Abstract

【解決手段】BOX層4上に積層されたN−型のSOI層5に、環状のディープトレンチ6が形成されている。ディープトレンチ6は、SOI層5の表面からBOX層4に至る深さを有している。ディープトレンチ6に取り囲まれる素子形成領域9には、P型のボディ領域10と、このボディ領域10以外の残余の領域からなるN−型のドリフト領域11とが形成されている。ボディ領域10の表層部には、N+型のソース領域12が形成されている。ドリフト領域11の表層部には、N+型のドレイン領域14が形成されている。ドリフト領域11には、SOI層5のN型不純物濃度よりも高く、かつ、ドレイン領域のN型不純物濃度よりも低いN型不純物濃度を有するN型領域42が形成されている。N型領域42の最深部は、ドレイン領域14よりも深い位置に達している。

【選択図】図4

Description

図6は、高耐圧のLDMOSFETを備える半導体装置の模式的な断面図である。

半導体装置101の基体をなす厚膜SOI基板102は、シリコン基板103上に、SiO2(酸化シリコン)からなるBOX(Buried Oxide)層104を介して、Si(シリコン)からなるSOI層105を積層した構造を有している。

この構造では、ドレイン領域113に印加される正極性の高電圧(ドレイン電圧)を、ドリフト領域110に生じる空乏層とBOX層104とに分担させることができ、LDMOSFETの高耐圧化を図ることができる。

請求項3記載の発明は、前記第1導電型領域の前記第2部分は、前記絶縁膜の前記開口部の周縁部に形成されている、請求項2に記載の半導体装置である。

請求項5記載の発明は、前記ドリフト領域の表面において、前記ソース領域から前記ボディ領域を介して前記ドレイン領域へ向かって延びるように形成され、ゲート絶縁膜を介して配置されたゲート電極をさらに含み、前記第1導電型領域の前記ドリフト領域の表面に沿う方向の端部は、前記ゲート電極に対して前記ドレイン領域側に配置されている、請求項1〜4のいずれか一項に記載の半導体装置である。

図1は、本発明の参考例に係る半導体装置の構造を示す模式的な断面図である。

半導体装置1は、厚膜SOI基板2を備えている。厚膜SOI基板2は、シリコン基板3上に、SiO2からなる絶縁層としてのBOX層4を介して、SiからなるN−型のSOI層5を積層した構造を有している。BOX層4の層厚は、たとえば、1.5μmである。SOI層5の層厚は、たとえば、30μmである。SOI層5のN型不純物濃度は、たとえば、3.5×1014/cm3である。

ドリフト領域11の表層部には、平面視で中央部に、N+型のドレイン領域14が形成されている。ドレイン領域14のN型不純物濃度は、たとえば、1020/cm3である。

層間絶縁膜20上には、ソース配線23およびドレイン配線24が形成されている。ソース配線23は、ソースコンタクトホール21を介して、ソース領域12およびボディコンタクト領域13に接続されている。ドレイン配線24は、ドレインコンタクトホール22を介して、ドレイン領域14に接続されている。

そして、ドレイン領域14のBOX層4側にN型領域15が形成されていることにより、ドレイン電圧の印加時に、空乏層がドレイン領域14に向かって延びるのを抑制することができる。そのため、素子形成領域9に形成されるLDMOSFETの耐圧を下げることなく、SOI層5の層厚を小さくすることができる。たとえば、BOX層4の層厚が1.5μmであり、ドリフト領域11のN型不純物濃度が3.5×1014/cm3であり、N型領域15のピーク濃度が1019/cm3であり、そのピーク濃度をドレイン領域14の表面からの深さが5μmの位置に有する場合、SOI層5の層厚を30μmとして、600V以上の耐圧を得ることができる。すなわち、600V以上の耐圧を得るために、従来の構造では、SOI層の層厚が40μm以上必要であるのに対し、半導体装置1では、SOI層5の層厚が30μmでよい。SOI層5の層厚を小さくすることにより、ディープトレンチ6を容易に形成することができるようになるので、半導体装置1の製造に要する手間および時間を低減することができる。

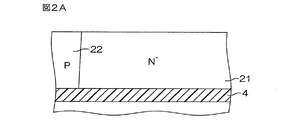

たとえば、イオン注入法によって、実質的に一定の不純物濃度を有するN−型シリコン基板内にO(酸素)を埋め込んだ後、そのOを熱酸化させることにより、図2Aに示すように、層厚1.5μmのBOX層4および層厚25μmのN−型シリコン層21を有する厚膜SOI基板が作成される。この作成過程において、B(ボロン)などのP型不純物がN−型シリコン層21に選択的に注入されることにより、P型領域22が形成される。

なお、図2Aに示す工程の後、図2Bに示す工程に代えて、図3に示す工程が行われてもよい。図3に示す工程では、まず、熱酸化法により、N−型シリコン層21上に、SiO2からなる熱酸化膜23が形成される。つづいて、公知のフォトリソグラフィ技術およびエッチング技術により、熱酸化膜23の表面に、N型拡散領域26を形成すべき部分に対向する凹部31が形成される。その後、イオン注入法により、熱酸化膜23の凹部31からN−型シリコン層21の表層部に、AsまたはPなどのN型不純物が注入される。そして、熱処理(アニール処理)が行われることにより、図2Cに示すように、N−型シリコン層21の表層部に、N型拡散領域26が形成される。熱酸化膜23は、N型拡散領域26の形成後に除去される。

図1に示す半導体装置1では、ドレイン領域14からBOX層4側に間隔を空けて、N型領域15が形成されている。これに対し、図4に示す半導体装置41では、ドリフト領域11において、SOI層5のN型不純物濃度よりも高く、かつ、ドレイン領域14のN型不純物濃度よりも低いN型不純物濃度を有するN型領域42が、ドレイン領域14に対してBOX層4側に隣接して形成されている。N型領域42は、たとえば、N型不純物濃度の極大値(ピーク濃度)が1018/cm3であり、そのピーク濃度をドレイン領域14の表面からの深さが2μmの位置に有している。

たとえば、イオン注入法によって、N−型シリコン基板内にOを埋め込んだ後、そのOを熱酸化させることにより、図5Aに示すように、層厚1.5μmのBOX層4および層厚30μmのSOI層5を有する厚膜SOI基板2が作成される。この作成過程において、B(ボロン)などのP型不純物がSOI層5に選択的に注入されることにより、ボディ領域10およびドリフト領域11が形成される。

N型領域42の形成後、熱酸化膜51が除去される。そして、図5Dに示すように、LOCOS法により、ドリフト領域11の表面に、LOCOS酸化膜16が形成される。また、熱酸化法により、ボディ領域10の表面とドリフト領域11の表面とに跨って、ゲート酸化膜17が形成される。さらに、P−CVD法により、SOI層5、LOCOS酸化膜16およびゲート酸化膜17上に、N型不純物が高濃度にドーピングされたポリシリコンの堆積層が形成され、公知のフォトリソグラフィ技術およびエッチング技術により、そのポリシリコンの堆積層がパターニングされる。これにより、ゲート酸化膜17上に、ゲート電極18が形成されるとともに、LOCOS酸化膜16上に、フィールドプレート19が形成される。

以上、本発明の実施形態および参考例を説明したが、本発明は、さらに他の形態で実施することもできる。たとえば、半導体装置1,41において、ソース領域12およびボディコンタクト領域13の形成位置とドレイン領域14の形成位置とが逆であってもよい。すなわち、SOI層5において、その中央部に、P型のボディ領域10が形成され、ディープトレンチ6の側面に沿って環状をなす領域(ボディ領域10を取り囲む領域)が、N−型のドリフト領域11とされて、ボディ領域10の表層部の平面視中央部にソース領域12およびボディコンタクト領域13が形成され、ドリフト領域11の表層部に環状のドレイン領域14が形成されてもよい。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

4 BOX層

5 SOI層

6 ディープトレンチ

9 素子形成領域

10 ボディ領域

11 ドリフト領域

12 ソース領域

14 ドレイン領域

15 N型領域

41 半導体装置

42 N型領域

Claims (6)

- 絶縁層と、

前記絶縁層上に積層された第1導電型の半導体層と、

前記半導体層の表面から前記絶縁層に至る深さを有する環状のディープトレンチと、

前記ディープトレンチに取り囲まれる素子形成領域において、前記ディープトレンチの側面に沿って、前記半導体層の全厚にわたって形成される第2導電型のボディ領域と、

前記素子形成領域において、前記ボディ領域以外の残余の領域からなる第1導電型のドリフト領域と、

前記ボディ領域の表層部に形成された第1導電型のソース領域と、

前記ドリフト領域の表層部に形成された第1導電型のドレイン領域と、

前記ドリフト領域の表面に形成され、前記ドレイン領域を露出させる開口部を有する絶縁膜と、

前記ドリフト領域において、前記絶縁膜の前記開口部の周縁部およびその内側の領域に選択的に前記ドレイン領域に対して隣接して形成され、前記ドレイン領域の下部全体を覆う第1部分を含み、最深部が前記ドレイン領域よりも深い位置に達し、前記ドリフト領域の第1導電型不純物濃度よりも高く、かつ、前記ドレイン領域の第1導電型不純物濃度よりも低い第1導電型不純物濃度を有する第1導電型領域とを含み、

前記ドリフト領域において、前記ドレイン領域および前記第1導電型領域を除く領域は、実質的に一定の不純物濃度を有する、半導体装置。 - 前記第1導電型領域は、前記ドレイン領域の側方部に前記ドレイン領域に対して隣接して形成された第2部分を含む、請求項1に記載の半導体装置。

- 前記第1導電型領域の前記第2部分は、前記絶縁膜の前記開口部の周縁部に形成されている、請求項2に記載の半導体装置。

- 前記第1導電型領域の前記第2部分における前記ドリフト領域の表面に沿う方向の厚さは、前記第1導電型領域の前記第1部分における前記ドリフト領域の深さ方向の厚さよりも薄い、請求項2または3に記載の半導体装置。

- 前記ドリフト領域の表面において、前記ソース領域から前記ボディ領域を介して前記ドレイン領域へ向かって延びるように形成され、ゲート絶縁膜を介して配置されたゲート電極をさらに含み、

前記第1導電型領域の前記ドリフト領域の表面に沿う方向の端部は、前記ゲート電極に対して前記ドレイン領域側に配置されている、請求項1〜4のいずれか一項に記載の半導体装置。 - 前記絶縁膜は、LOCOS酸化膜を含む、請求項1〜5のいずれか一項に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014004209A JP5735668B2 (ja) | 2014-01-14 | 2014-01-14 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014004209A JP5735668B2 (ja) | 2014-01-14 | 2014-01-14 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007234472A Division JP5479671B2 (ja) | 2007-09-10 | 2007-09-10 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015084525A Division JP6061979B2 (ja) | 2015-04-16 | 2015-04-16 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014090207A true JP2014090207A (ja) | 2014-05-15 |

| JP5735668B2 JP5735668B2 (ja) | 2015-06-17 |

Family

ID=50791832

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014004209A Active JP5735668B2 (ja) | 2014-01-14 | 2014-01-14 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5735668B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5778872A (en) | 1996-11-18 | 1998-07-14 | Medlis, Inc. | Artificial ventilation system and methods of controlling carbon dioxide rebreathing |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11251597A (ja) * | 1998-02-27 | 1999-09-17 | Denso Corp | 半導体装置 |

| JP2001025235A (ja) * | 1999-07-07 | 2001-01-26 | Mitsubishi Electric Corp | 駆動装置および電力変換装置 |

| JP2001352070A (ja) * | 2000-04-07 | 2001-12-21 | Denso Corp | 半導体装置およびその製造方法 |

-

2014

- 2014-01-14 JP JP2014004209A patent/JP5735668B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11251597A (ja) * | 1998-02-27 | 1999-09-17 | Denso Corp | 半導体装置 |

| JP2001025235A (ja) * | 1999-07-07 | 2001-01-26 | Mitsubishi Electric Corp | 駆動装置および電力変換装置 |

| JP2001352070A (ja) * | 2000-04-07 | 2001-12-21 | Denso Corp | 半導体装置およびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5735668B2 (ja) | 2015-06-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8716791B1 (en) | LDMOS with corrugated drift region | |

| JP5298565B2 (ja) | 半導体装置およびその製造方法 | |

| CN105590962A (zh) | 碳化硅半导体装置和用于制造碳化硅半导体装置的方法 | |

| JP5410012B2 (ja) | 半導体装置 | |

| JP2009065117A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2013058575A (ja) | 半導体装置及びその製造方法 | |

| JP4308096B2 (ja) | 半導体装置及びその製造方法 | |

| TW201606857A (zh) | 半導體裝置之製造方法 | |

| JP5371358B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| WO2012011225A1 (ja) | 半導体装置及びその製造方法 | |

| TW201511135A (zh) | 半導體裝置之製造方法 | |

| JP5983122B2 (ja) | 半導体装置 | |

| JP2008135474A (ja) | 半導体装置 | |

| JP5479671B2 (ja) | 半導体装置 | |

| JP2010192691A (ja) | 半導体装置 | |

| JP5390760B2 (ja) | 半導体装置の製造方法および半導体装置 | |

| JP5735668B2 (ja) | 半導体装置 | |

| JP2008159916A (ja) | 半導体装置 | |

| JP6092680B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2009146946A (ja) | 半導体装置およびその製造方法 | |

| JP6286010B2 (ja) | 半導体装置 | |

| JP6061979B2 (ja) | 半導体装置 | |

| JP2016058541A (ja) | 横型半導体装置 | |

| JP6243748B2 (ja) | 半導体素子及びその製造方法 | |

| JP2010258210A (ja) | 半導体装置とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20141218 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150227 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150319 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150416 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5735668 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |