JP2013530421A - ディスプレイモードを選択するためのシステムおよび方法 - Google Patents

ディスプレイモードを選択するためのシステムおよび方法 Download PDFInfo

- Publication number

- JP2013530421A JP2013530421A JP2013511288A JP2013511288A JP2013530421A JP 2013530421 A JP2013530421 A JP 2013530421A JP 2013511288 A JP2013511288 A JP 2013511288A JP 2013511288 A JP2013511288 A JP 2013511288A JP 2013530421 A JP2013530421 A JP 2013530421A

- Authority

- JP

- Japan

- Prior art keywords

- display

- data

- displayed

- line

- addressing mode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 128

- 238000012545 processing Methods 0.000 claims abstract description 73

- 230000004044 response Effects 0.000 claims description 39

- 238000004590 computer program Methods 0.000 claims description 23

- 239000003086 colorant Substances 0.000 claims description 17

- 230000002085 persistent effect Effects 0.000 claims description 12

- 239000010410 layer Substances 0.000 description 152

- 230000008569 process Effects 0.000 description 55

- 230000003287 optical effect Effects 0.000 description 53

- 238000010586 diagram Methods 0.000 description 31

- 239000000463 material Substances 0.000 description 24

- 239000000758 substrate Substances 0.000 description 19

- 239000006096 absorbing agent Substances 0.000 description 12

- 238000004519 manufacturing process Methods 0.000 description 12

- 230000002829 reductive effect Effects 0.000 description 11

- 238000000151 deposition Methods 0.000 description 10

- 230000008859 change Effects 0.000 description 9

- 238000000059 patterning Methods 0.000 description 8

- 238000013461 design Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000005530 etching Methods 0.000 description 6

- 238000000926 separation method Methods 0.000 description 6

- 229910004298 SiO 2 Inorganic materials 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 230000003750 conditioning effect Effects 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- ORQBXQOJMQIAOY-UHFFFAOYSA-N nobelium Chemical compound [No] ORQBXQOJMQIAOY-UHFFFAOYSA-N 0.000 description 4

- 229910000838 Al alloy Inorganic materials 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 238000003491 array Methods 0.000 description 3

- 230000001413 cellular effect Effects 0.000 description 3

- 230000033001 locomotion Effects 0.000 description 3

- 230000000873 masking effect Effects 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 230000036961 partial effect Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 230000003595 spectral effect Effects 0.000 description 2

- 238000001228 spectrum Methods 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 230000000007 visual effect Effects 0.000 description 2

- 238000005406 washing Methods 0.000 description 2

- BLIQUJLAJXRXSG-UHFFFAOYSA-N 1-benzyl-3-(trifluoromethyl)pyrrolidin-1-ium-3-carboxylate Chemical compound C1C(C(=O)O)(C(F)(F)F)CCN1CC1=CC=CC=C1 BLIQUJLAJXRXSG-UHFFFAOYSA-N 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- BJQHLKABXJIVAM-UHFFFAOYSA-N bis(2-ethylhexyl) phthalate Chemical group CCCCC(CC)COC(=O)C1=CC=CC=C1C(=O)OCC(CC)CCCC BJQHLKABXJIVAM-UHFFFAOYSA-N 0.000 description 1

- -1 but not limited to Substances 0.000 description 1

- OJIJEKBXJYRIBZ-UHFFFAOYSA-N cadmium nickel Chemical compound [Ni].[Cd] OJIJEKBXJYRIBZ-UHFFFAOYSA-N 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- VNTLIPZTSJSULJ-UHFFFAOYSA-N chromium molybdenum Chemical compound [Cr].[Mo] VNTLIPZTSJSULJ-UHFFFAOYSA-N 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000001066 destructive effect Effects 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000004146 energy storage Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000001746 injection moulding Methods 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910001416 lithium ion Inorganic materials 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 230000005226 mechanical processes and functions Effects 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 239000003973 paint Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 239000005060 rubber Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 1

- 238000009827 uniform distribution Methods 0.000 description 1

- 238000001429 visible spectrum Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3433—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices

- G09G3/3466—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices based on interferometric effect

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2003—Display of colours

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/06—Passive matrix structure, i.e. with direct application of both column and row voltages to the light emitting or modulating elements, other than LCD or OLED

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0205—Simultaneous scanning of several lines in flat panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0254—Control of polarity reversal in general, other than for liquid crystal displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/10—Special adaptations of display systems for operation with variable images

- G09G2320/103—Detection of image changes, e.g. determination of an index representative of the image change

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0435—Change or adaptation of the frame rate of the video stream

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Mechanical Light Control Or Optical Switches (AREA)

Abstract

Description

本開示は、「System and Method for Choosing Display Modes」という名称の2010年5月18日に出願した米国仮特許出願第61/345,954号、「System and Method for Choosing Display Modes」という名称の2010年5月21日に出願した米国仮特許出願第61/346,994号、および「System and Method for Choosing Display Modes」という名称の2010年10月21日に出願した米国仮特許出願第61/405,610号の優先権を主張し、それらの全ては、これに関して譲受人に譲渡されている。先願の開示は、本開示の一部とみなされ、参照により本開示に組み込まれる。

特定のディスプレイでは、ディスプレイ要素にデータを書き込むのに必要な時間は、ディスプレイが書き込まれ得る全体的なレートに制限される。各コモンラインが別個にアドレス指定される場合、各ラインに必要な書き込み時間は、全体的なフレーム書き込み時間を決定する。特定の実施形態では、ディスプレイの増加されたリフレッシュレートまたはフレームレートが所望であり得、また、ユーザへの良好な外観のためのディスプレイの解像度または色の範囲よりもより重要であり得る。特定の実施形態では、幅広い色の範囲とともに高解像度の画像を提示することができるドライバ回路およびディスプレイ配列が、配列のコモンラインをストローブする種々の異なる「モード」で利用され得る。これらのモードは、解像度および色の範囲の一方または両方を減少するように設計され得、代わりに、同時に配列のマルチラインをストローブすることにより、ディスプレイのポテンシャルリフレッシュレートを増大させ、および/または電力消費を低下させる。これらのモードは、以下でさらに説明され、本明細書では、ディスプレイコントローラ操作の「マルチラインアドレッシングモード」と呼ばれる。まず、これらのモードの操作が説明され、モード制御の新規な方法が続く。

場合によっては、コモンラインをストローブする異なるモードは、ディスプレイの外観に影響を及ぼすが、フレーム書き込み時間または電力消費は大幅に変化させない。これらは本明細書では、「ラインオーダーアドレッシングモード」と呼ばれる。図13は、非線形の順序で更新されているディスプレイ要素の配列の一例を概略的に示す。図示されたストローブパターンは、不可視スキャン(invisible scan)と呼ばれることがある。このアドレッシングモードでは、ディスプレイ830のラインは、従来の順次的隣接ライン更新順序以外の順序で更新される。例えば、一実施形態では、ディスプレイ830のラインは、ランダムな順序で更新され得る。図示したように、タイムワン(Time one)1035では、ライン1036が更新される。タイムツー(Time two)1050では、ライン1038が更新される。ライン1036および1038は隣接していない。タイムスリー(Time three)1060では、ライン1046が更新される。この場合もやはり、ライン1040はライン1038と隣接していない。不可視スキャンモードにおけるライン更新の順序は、生成疑似乱数に基づいてダイナミックに決定される。代わりに、ラインに対する更新順序は、ランダムに見える一つまたは複数の所定のシーケンスに応じて決定され得る。図13における例は、直前または直後のライン更新と隣接していないライン更新を示すが、「不可視スキャン」効果を維持しつつ、いくつかのライン更新が直前または直後のライン更新と隣接していることが可能である。不可視スキャンモードは、特定の条件で視覚効果を届けるために使用され得る。例えば、不可視スキャンモードは、スライドショーにおける静止画像間のスイッチングの際に使用され得る。代わりに、不可視スキャンモードは、ホストを作動する異なるアプリケーションを表すウィンドウ間のスイッチングの際に使用され得る。前に注意したように、ホストまたはコントローラは、ディスプレイデータに関するデータにおけるフラッグ、ディスプレイデータの特性、またはホストのステータスに基づいて、不可視の更新モードを選択することができる。

ホストが制御できる他のモードは、マルチラインアドレッシングまたはラインオーダーアドレッシングを含まないことがある。これらのディスプレイデバイスの多くの実施形態では、画像データの各画素は、三色のそれぞれを規定する特定データ値として規定される。ディスプレイのカラーパレットは、入ってくるデータのカラーパレットとは異なることがある。これらの場合、また同様に他の理由のために、ディスプレイコントローラは、各画素の元のデータを処理し、元の画像データの外観を正確に再生するディスプレイ配列に適している三つの画素明度を作ることができる。画像データの性質に応じて、このカラープロセッシングは実行される必要がないことがある。ホストが元のデータフォーマットの情報を有するため、それは多数の異なる「カラープロセッシング」モードでディスプレイコントローラを配置することができる。画像データが既にディスプレイに適合するフォーマットである場合、カラープロセッシングは止めることができ、電力および計算時間を省くことができる。

13 矢印、光

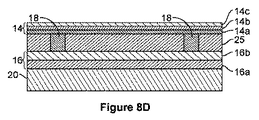

14 可動反射層

14a 反射副層、導電層

14b 誘電体支持層、副層

14c 導電層

15 光

16 光学スタック

16a 吸収体層、光吸収体、副層

16b 副層、誘電体

18 支持支柱、支持体

19 キャビティ、ギャップ

20 透明基板

21 システムプロセッサ

22 配列ドライバ

23 黒色マスク構造

24 行ドライバ回路

25 犠牲層、犠牲材料

26 列ドライバ回路

27 ネットワークインタフェース

28 フレームバッファ

29 ドライバコントローラ

30 ディスプレイ、ディスプレイ配列、パネル

32 連結部

34 変形可能層

35 スペーサ層

40 ディスプレイデバイス

41 筐体

43 アンテナ

45 スピーカ

46 マイクロホン

47 トランシーバ

48 入力デバイス

50 電源

52 調整用ハードウェア

60a 第1のライン時間

60b 第2のライン時間

60c 第3のライン時間

60d 第4のライン時間

60e 第5のライン時間

62 セグメント電圧

64 セグメント電圧

70 解放電圧

72 高い保持電圧

74 アドレス電圧

76 低い保持電圧

78 アドレス電圧

104 セグメントドライバ回路

106 コモンドライバ回路

Claims (72)

- 複数のコモンラインを含むディスプレイを駆動するためのプロセッサを含む装置であって、前記プロセッサが、

表示されるデータを得、

表示される画像の更新レートに少なくとも一部基づくシングルまたはマルチラインアドレッシングモードであって、前記マルチラインアドレッシングモードは、いくつのコモンラインが同一のデータで同時に書き込まれるかを決定する、シングルまたはマルチラインアドレッシングモードを選択し、かつ

前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新する

ように構成される、装置。 - 前記プロセッサと通じるように構成されたメモリデバイスをさらに含む、請求項1に記載の装置。

- 前記ディスプレイに少なくとも一つの信号を送るように構成されたドライバ回路をさらに含む、請求項1に記載の装置。

- 前記ドライバ回路に前記画像データの少なくとも一部を送るように構成されたコントローラをさらに含む、請求項3に記載の装置。

- 前記プロセッサに前記画像データを送るように構成された画像ソースモジュールをさらに含む、請求項1に記載の装置。

- 前記画像ソースモジュールは、受信機、トランシーバ、および送信機の少なくとも一つを含む、請求項5に記載の装置。

- 入力データを受け取り、かつ前記入力データを前記プロセッサに通信するように構成された入力デバイスをさらに含む、請求項1に記載の装置。

- 前記ディスプレイはIMODを含む、請求項1に記載の装置。

- 複数のコモンラインを有するディスプレイを更新する方法であって、前記方法が、

表示されるデータを得る段階と、

表示される画像の更新レートに少なくとも一部基づくシングルまたはマルチラインアドレッシングモードを選択する段階であって、前記マルチラインアドレッシングモードは、いくつのコモンラインが同一のデータで同時に書き込まれるかを決定する、段階と、

前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新する段階と、

を含む、方法。 - 前記マルチラインアドレッシングモードに応じてディスプレイを更新する段階は、異なるディスプレイ要素に対応する少なくとも二つのコモンラインに第一波形を同時に印加する段階を含む、請求項9に記載の方法。

- 前記少なくとも二つのコモンラインは、同一の色のディスプレイ要素に対応する、請求項10に記載の方法。

- 前記少なくとも二つのコモンラインは、異なる色のディスプレイ要素に対応する、請求項10に記載の方法。

- 前記少なくとも二つのコモンラインは、正確には三つのコモンラインであり、それぞれが異なる色のディスプレイ要素に対応する、請求項10に記載の方法。

- 前記少なくとも二つのコモンラインは隣接している、請求項10に記載の方法。

- 前記少なくとも二つのコモンラインは隣接していない、請求項10に記載の方法。

- 前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新する段階は、異なるディスプレイ要素に対応する少なくとも二つのコモンラインに第二波形を同時に印加する段階をさらに含み、前記第一波形は第一極性を有し、前記第二波形は第二極性を有し、前記第一および第二極性は反対である、請求項10に記載の方法。

- 前記表示されるデータはビデオデータを含む、請求項10に記載の方法。

- 前記ディスプレイは、各コモンラインの個別アドレス指定に対応する最大リフレッシュレートを有し、前記ビデオは前記最大リフレッシュレートよりも大きいフレームレートを有する、請求項17に記載の方法。

- 前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新する段階は、一度に一つのみのコモンラインに波形を印加する段階を含む、請求項9に記載の方法。

- 前記表示されるデータは静止画像を含む、請求項19に記載の方法。

- 前記表示されるデータはテキストを含む、請求項19に記載の方法。

- 前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新する段階は、ディスプレイの一部を更新する段階のみ含む、請求項9に記載の方法。

- 前記選択されたアドレッシングモードは電力消費を低下させる、請求項9に記載の方法。

- 前記選択されたアドレッシングモードは高いリフレッシュレートを提供する、請求項9に記載の方法。

- 前記選択されたアドレッシングモードは高い画像解像度を提供する、請求項9に記載の方法。

- 前記ディスプレイはIMODを含む、請求項9に記載の方法。

- 複数のコモンラインを含むディスプレイを駆動するためのシステムであって、前記システムが、

表示されるデータを得るための手段と、

表示される画像の更新レートに少なくとも一部基づくシングルまたはマルチラインアドレッシングモードを選択するための手段であって、前記マルチラインアドレッシングモードは、いくつのコモンラインが同一のデータで同時に書き込まれるかを決定する、手段と、

前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新するための手段と、

を含む、システム。 - 前記表示されるデータを得るための手段が入力デバイスを含む、請求項27に記載のシステム。

- 前記表示される画像の更新レートに少なくとも一部基づくシングルまたはマルチラインアドレッシングモードを選択するための手段がプロセッサを含む、請求項27に記載のシステム。

- 前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新するための手段がコモンドライバを含む、請求項27に記載のシステム。

- 前記ディスプレイはIMODを含む、請求項27に記載のシステム。

- 複数のコモンラインを含むディスプレイを駆動するように構成されたプログラムのためのデータを処理するコンピュータプログラム製品であって、前記コンピュータプログラム製品が、

表示されるデータを得、

表示される画像の更新レートに少なくとも一部基づくシングルまたはマルチラインアドレッシングモードであって、前記マルチラインアドレッシングモードは、いくつのコモンラインが同一のデータで同時に書き込まれるかを決定する、シングルまたはマルチラインアドレッシングモードを選択し、かつ

前記シングルまたはマルチラインアドレッシングモードに応じてディスプレイを更新する

ための処理回路をもたらすコードがその上に記憶された持続性コンピュータ可読媒体を含む、コンピュータプログラム製品。 - 前記ディスプレイはIMODを含む、請求項32に記載のコンピュータプログラム製品。

- 複数のコモンラインを含むディスプレイを駆動するためのプロセッサを含む装置であって、前記プロセッサが、

表示されるデータを得、

前記表示されるデータに少なくとも一部基づくラインオーダーアドレッシングモードであって、前記ラインオーダーアドレッシングモードは、前記コモンラインが前記データで書き込まれる順序を決定する、ラインオーダーアドレッシングモードを選択し、かつ

前記ラインオーダーアドレッシングモードに応じてディスプレイを更新する

ように構成される、装置。 - 前記プロセッサと通じるように構成されたメモリデバイスをさらに含む、請求項34に記載の装置。

- 前記ディスプレイに少なくとも一つの信号を送るように構成されたドライバ回路をさらに含む、請求項34に記載の装置。

- 前記ドライバ回路に前記画像データの少なくとも一部を送るように構成されたコントローラをさらに含む、請求項36に記載の装置。

- 前記プロセッサに前記画像データを送るように構成された画像ソースモジュールをさらに含む、請求項34に記載の装置。

- 前記画像ソースモジュールは、受信機、トランシーバ、および送信機の少なくとも一つを含む、請求項38に記載の装置。

- 入力データを受け取り、かつ前記入力データを前記プロセッサに通信するように構成された入力デバイスをさらに含む、請求項34に記載の装置。

- 前記ディスプレイはIMODを含む、請求項34に記載の装置。

- 複数のコモンラインを有するディスプレイを更新する方法であって、前記方法が、

表示されるデータを得る段階と、

前記表示されるデータに少なくとも一部基づくラインオーダーアドレッシングモードを選択する段階であって、前記ラインオーダーアドレッシングモードは、前記コモンラインが前記データで書き込まれる順序を決定する、段階と、

前記ラインオーダーアドレッシングモードに応じてディスプレイを更新する段階と、

を含む、方法。 - 前記コモンラインが前記データで書き込まれる順序がランダムである、請求項42に記載の方法。

- 前記コモンラインが前記データで書き込まれる順序が、生成疑似乱数に基づいてダイナミックに決定される、請求項42に記載の方法。

- 前記コモンラインが前記データで書き込まれる順序が、ランダムに見える一つまたは複数のシーケンスに応じて決定される、請求項42に記載の方法。

- 前記表示されるデータはスライドショーを含む、請求項42に記載の方法。

- 前記ディスプレイはIMODを含む、請求項42に記載の方法。

- 複数のコモンラインを含むディスプレイを駆動するためのシステムであって、前記システムが、

表示されるデータを得るための手段と、

前記表示されるデータに少なくとも一部基づくラインオーダーアドレッシングモードを選択するための手段であって、前記ラインオーダーアドレッシングモードは、前記コモンラインが前記データで書き込まれる順序を決定する、手段と、

前記ラインオーダーアドレッシングモードに応じてディスプレイを更新するための手段と、

を含む、システム。 - 前記表示されるデータを得るための手段が入力デバイスを含む、請求項48に記載のシステム。

- 前記表示されるデータに少なくとも一部基づくラインオーダーアドレッシングモードを選択するための手段がプロセッサを含む、請求項48に記載のシステム。

- 前記ラインオーダーアドレッシングモードに応じてディスプレイを更新するための手段がコモンドライバを含む、請求項48に記載のシステム。

- 前記ディスプレイはIMODを含む、請求項48に記載のシステム。

- 複数のコモンラインを含むディスプレイを駆動するように構成されたプログラムのためのデータを処理するコンピュータプログラム製品であって、前記コンピュータプログラム製品が、

表示されるデータを得、

前記表示されるデータに少なくとも一部基づくラインオーダーアドレッシングモードであって、前記ラインオーダーアドレッシングモードは、前記コモンラインが前記データで書き込まれる順序を決定する、ラインオーダーアドレッシングモードを選択し、かつ

前記ラインオーダーアドレッシングモードに応じてディスプレイを更新する

ための処理回路をもたらすコードがその上に記憶された持続性コンピュータ可読媒体を含む、コンピュータプログラム製品。 - 前記ディスプレイはIMODを含む、請求項53に記載のコンピュータプログラム製品。

- ディスプレイを駆動するためのプロセッサを含む装置であって、前記プロセッサが、

表示されるデータを得、

前記表示されるデータに少なくとも一部基づくカラープロセッシングモードであって、前記カラープロセッシングモードは、前記表示されるデータ内の色情報が表示される前に処理されるかどうかを決定する、カラープロセッシングモードを選択し、かつ

前記カラープロセッシングモードに応じてディスプレイを更新する

ように構成される、装置。 - 前記プロセッサと通じるように構成されたメモリデバイスをさらに含む、請求項55に記載の装置。

- 前記ディスプレイに少なくとも一つの信号を送るように構成されたドライバ回路をさらに含む、請求項55に記載の装置。

- 前記ドライバ回路に前記画像データの少なくとも一部を送るように構成されたコントローラをさらに含む、請求項57に記載の装置。

- 前記プロセッサに前記画像データを送るように構成された画像ソースモジュールをさらに含む、請求項55に記載の装置。

- 前記画像ソースモジュールは、受信機、トランシーバ、および送信機の少なくとも一つを含む、請求項59に記載の装置。

- 入力データを受け取り、かつ前記入力データを前記プロセッサに通信するように構成された入力デバイスをさらに含む、請求項55に記載の装置。

- 前記ディスプレイはIMODを含む、請求項55に記載の装置。

- ディスプレイを更新する方法であって、前記方法が、

表示されるデータを得る段階と、

前記表示されるデータに少なくとも一部基づくカラープロセッシングモードを選択する段階であって、前記カラープロセッシングモードは、前記表示されるデータ内の色情報が表示される前に処理されるかどうかを決定する、段階と、

前記カラープロセッシングモードに応じてディスプレイを更新する段階と、

を含む、方法。 - カラープロセッシングモードを選択する段階および前記カラープロセッシングモードに応じてディスプレイを更新する段階は、色情報が処理を必要としないことを決定する段階、および前記色情報を処理することなくディスプレイを更新する段階を含む、請求項63に記載の方法。

- 前記ディスプレイはIMODを含む、請求項63に記載の方法。

- ディスプレイを駆動するためのシステムであって、前記システムが、

表示されるデータを得るための手段と、

前記表示されるデータに少なくとも一部基づくカラープロセッシングモードを選択するための手段であって、前記カラープロセッシングモードは、前記表示されるデータ内の色情報が表示される前に処理されるかどうかを決定する、手段と、

前記カラープロセッシングモードに応じてディスプレイを更新するための手段と、

を含む、システム。 - 前記表示されるデータを得るための手段が入力デバイスを含む、請求項66に記載のシステム。

- 前記表示されるデータに少なくとも一部基づくカラープロセッシングモードを選択するための手段がプロセッサを含む、請求項66に記載のシステム。

- 前記カラープロセッシングモードに応じてディスプレイを更新するための手段がコモンドライバを含む、請求項66に記載のシステム。

- 前記ディスプレイはIMODを含む、請求項66に記載のシステム。

- ディスプレイを駆動するように構成されたプログラムのためのデータを処理するコンピュータプログラム製品であって、前記コンピュータプログラム製品が、

表示されるデータを得、

前記表示されるデータに少なくとも一部基づくカラープロセッシングモードであって、前記カラープロセッシングモードは、前記表示されるデータ内の色情報が表示される前に処理されるかどうかを決定する、カラープロセッシングモードを選択し、かつ

前記カラープロセッシングモードに応じてディスプレイを更新する

ための処理回路をもたらすコードがその上に記憶された持続性コンピュータ可読媒体を含む、コンピュータプログラム製品。 - 前記ディスプレイはIMODを含む、請求項71に記載のコンピュータプログラム製品。

Applications Claiming Priority (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US34595410P | 2010-05-18 | 2010-05-18 | |

| US61/345,954 | 2010-05-18 | ||

| US34699410P | 2010-05-21 | 2010-05-21 | |

| US61/346,994 | 2010-05-21 | ||

| US40561010P | 2010-10-21 | 2010-10-21 | |

| US61/405,610 | 2010-10-21 | ||

| PCT/US2011/036798 WO2011146476A1 (en) | 2010-05-18 | 2011-05-17 | System and method for choosing display modes |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2013530421A true JP2013530421A (ja) | 2013-07-25 |

Family

ID=44972134

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013511288A Pending JP2013530421A (ja) | 2010-05-18 | 2011-05-17 | ディスプレイモードを選択するためのシステムおよび方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US20110285757A1 (ja) |

| EP (1) | EP2572350A1 (ja) |

| JP (1) | JP2013530421A (ja) |

| KR (1) | KR20130108510A (ja) |

| CN (1) | CN102947875A (ja) |

| TW (1) | TW201209792A (ja) |

| WO (2) | WO2011146459A1 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012103797A (ja) * | 2010-11-08 | 2012-05-31 | Sony Corp | 入力装置、座標検出方法及びプログラム |

| US20130100109A1 (en) * | 2011-10-21 | 2013-04-25 | Qualcomm Mems Technologies, Inc. | Method and device for reducing effect of polarity inversion in driving display |

| US20130194295A1 (en) * | 2012-01-27 | 2013-08-01 | Qualcomm Mems Technologies, Inc. | System and method for choosing display modes |

| CN104704485B (zh) | 2012-07-19 | 2018-11-30 | 格兰斯电讯网络有限公司 | 一种在第二位置查看第一浏览器的内容的方法 |

| US9190013B2 (en) * | 2013-02-05 | 2015-11-17 | Qualcomm Mems Technologies, Inc. | Image-dependent temporal slot determination for multi-state IMODs |

| US8970577B2 (en) * | 2013-03-13 | 2015-03-03 | Synaptics Incorporated | Reducing display artifacts after non-display update periods |

| US9183800B2 (en) * | 2013-07-22 | 2015-11-10 | Shenzhen China Star Optoelectronics Technology Co., Ltd | Liquid crystal device and the driven method thereof |

| JP2015079078A (ja) * | 2013-10-16 | 2015-04-23 | セイコーエプソン株式会社 | 表示制御装置及び方法、半導体集積回路装置、並びに、表示装置 |

| US9830871B2 (en) * | 2014-01-03 | 2017-11-28 | Nvidia Corporation | DC balancing techniques for a variable refresh rate display |

| US9711099B2 (en) | 2014-02-26 | 2017-07-18 | Nvidia Corporation | Techniques for avoiding and remedying DC bias buildup on a flat panel variable refresh rate display |

| US9384703B2 (en) | 2014-02-26 | 2016-07-05 | Nvidia Corporation | Techniques for avoiding and remedying DC bias buildup on a flat panel variable refresh rate display |

| KR102257170B1 (ko) | 2015-01-05 | 2021-05-27 | 시냅틱스 인코포레이티드 | 디스플레이 및 센싱 데이터의 시간 공유 |

| US10394391B2 (en) | 2015-01-05 | 2019-08-27 | Synaptics Incorporated | System and method for reducing display artifacts |

| KR102294133B1 (ko) * | 2015-06-15 | 2021-08-27 | 삼성디스플레이 주식회사 | 유기발광 디스플레이 장치의 스캔 드라이버, 유기발광 디스플레이 장치 및 이를 포함하는 디스플레이 시스템 |

| US10592022B2 (en) | 2015-12-29 | 2020-03-17 | Synaptics Incorporated | Display device with an integrated sensing device having multiple gate driver circuits |

| US9940898B2 (en) | 2016-02-25 | 2018-04-10 | Nvidia Corporation | Variable refresh rate video capture and playback |

| KR102539185B1 (ko) * | 2016-12-01 | 2023-06-02 | 삼성전자주식회사 | 디스플레이 장치, 그의 구동 방법 및 비일시적 컴퓨터 판독가능 기록매체 |

| JP6539684B2 (ja) * | 2017-01-31 | 2019-07-03 | 矢崎総業株式会社 | 車両用表示装置および車両用表示装置の表示方法 |

| KR102497515B1 (ko) | 2018-02-23 | 2023-02-10 | 삼성전자주식회사 | 디스플레이 패널을 통해 표시되는 콘텐트의 저장을 제어하기 위한 전자 장치 및 방법 |

| CN112399157A (zh) * | 2019-08-15 | 2021-02-23 | 中强光电股份有限公司 | 投影机及投影方法 |

| CN112687222B (zh) * | 2020-12-28 | 2021-12-17 | 北京大学 | 基于脉冲信号的显示方法、装置、电子设备及介质 |

| CN113077743A (zh) * | 2021-03-17 | 2021-07-06 | Tcl华星光电技术有限公司 | 提高显示面板刷新率的驱动方法、驱动器及显示装置 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05341745A (ja) * | 1992-03-10 | 1993-12-24 | Hitachi Ltd | 表示制御装置 |

| JPH1010517A (ja) * | 1996-06-21 | 1998-01-16 | Fujitsu Ltd | 画像表示装置 |

| JPH11109923A (ja) * | 1997-09-30 | 1999-04-23 | Toshiba Corp | 液晶表示装置の駆動方法 |

| JP2000214831A (ja) * | 1999-01-27 | 2000-08-04 | Hitachi Ltd | 表示処理装置及び情報処理装置 |

| JP2002132202A (ja) * | 2000-10-25 | 2002-05-09 | Mitsubishi Electric Corp | 表示装置 |

| JP2005529366A (ja) * | 2002-06-11 | 2005-09-29 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | ディスプレイにおけるライン走査 |

| JP2006099074A (ja) * | 2004-09-27 | 2006-04-13 | Idc Llc | 双安定ディスプレイを駆動する方法とシステム |

| JP2006267140A (ja) * | 2005-03-22 | 2006-10-05 | Hitachi Ltd | 映像処理装置および携帯端末装置 |

| JP2007240912A (ja) * | 2006-03-09 | 2007-09-20 | Epson Imaging Devices Corp | 電気光学装置及び電子機器 |

| JP2008107378A (ja) * | 2006-10-23 | 2008-05-08 | Epson Imaging Devices Corp | 電気光学装置、電気光学装置の駆動方法、及び電気機器 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07152340A (ja) * | 1993-11-30 | 1995-06-16 | Rohm Co Ltd | ディスプレイ装置 |

| US5844534A (en) * | 1993-12-28 | 1998-12-01 | Kabushiki Kaisha Toshiba | Liquid crystal display apparatus |

| DE69509953T2 (de) * | 1994-03-11 | 1999-10-28 | Canon K.K., Tokio/Tokyo | Dynamische Verfeinerung der Pixelstruktur in einer Anzeige |

| JPH11338427A (ja) * | 1998-05-22 | 1999-12-10 | Fujitsu Ltd | 表示装置 |

| JP2002123208A (ja) * | 2000-10-13 | 2002-04-26 | Nec Corp | 画像表示装置およびその駆動方法 |

| GB2378343B (en) * | 2001-08-03 | 2004-05-19 | Sendo Int Ltd | Image refresh in a display |

| JP2003162267A (ja) * | 2001-11-29 | 2003-06-06 | Seiko Epson Corp | 表示駆動回路、電気光学装置、電子機器及び表示駆動方法 |

| JP2004013115A (ja) * | 2002-06-11 | 2004-01-15 | Fuji Electric Holdings Co Ltd | 有機発光素子を用いた表示デバイスの駆動方法および駆動装置 |

| US7532194B2 (en) * | 2004-02-03 | 2009-05-12 | Idc, Llc | Driver voltage adjuster |

| US7532195B2 (en) * | 2004-09-27 | 2009-05-12 | Idc, Llc | Method and system for reducing power consumption in a display |

| KR100827453B1 (ko) * | 2004-12-29 | 2008-05-07 | 엘지디스플레이 주식회사 | 일렉트로 루미네센스 표시소자 및 그 구동방법 |

| US7920136B2 (en) * | 2005-05-05 | 2011-04-05 | Qualcomm Mems Technologies, Inc. | System and method of driving a MEMS display device |

| US7975215B2 (en) * | 2007-05-14 | 2011-07-05 | Microsoft Corporation | Sharing editable ink annotated images with annotation-unaware applications |

-

2011

- 2011-05-17 KR KR1020127032855A patent/KR20130108510A/ko not_active Withdrawn

- 2011-05-17 WO PCT/US2011/036779 patent/WO2011146459A1/en active Application Filing

- 2011-05-17 JP JP2013511288A patent/JP2013530421A/ja active Pending

- 2011-05-17 CN CN2011800297192A patent/CN102947875A/zh active Pending

- 2011-05-17 WO PCT/US2011/036798 patent/WO2011146476A1/en active Application Filing

- 2011-05-17 EP EP11724326A patent/EP2572350A1/en not_active Withdrawn

- 2011-05-18 TW TW100117465A patent/TW201209792A/zh unknown

- 2011-05-18 US US13/110,766 patent/US20110285757A1/en not_active Abandoned

- 2011-05-18 US US13/110,747 patent/US20110285683A1/en not_active Abandoned

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05341745A (ja) * | 1992-03-10 | 1993-12-24 | Hitachi Ltd | 表示制御装置 |

| JPH1010517A (ja) * | 1996-06-21 | 1998-01-16 | Fujitsu Ltd | 画像表示装置 |

| JPH11109923A (ja) * | 1997-09-30 | 1999-04-23 | Toshiba Corp | 液晶表示装置の駆動方法 |

| JP2000214831A (ja) * | 1999-01-27 | 2000-08-04 | Hitachi Ltd | 表示処理装置及び情報処理装置 |

| JP2002132202A (ja) * | 2000-10-25 | 2002-05-09 | Mitsubishi Electric Corp | 表示装置 |

| JP2005529366A (ja) * | 2002-06-11 | 2005-09-29 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | ディスプレイにおけるライン走査 |

| JP2006099074A (ja) * | 2004-09-27 | 2006-04-13 | Idc Llc | 双安定ディスプレイを駆動する方法とシステム |

| JP2006267140A (ja) * | 2005-03-22 | 2006-10-05 | Hitachi Ltd | 映像処理装置および携帯端末装置 |

| JP2007240912A (ja) * | 2006-03-09 | 2007-09-20 | Epson Imaging Devices Corp | 電気光学装置及び電子機器 |

| JP2008107378A (ja) * | 2006-10-23 | 2008-05-08 | Epson Imaging Devices Corp | 電気光学装置、電気光学装置の駆動方法、及び電気機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2572350A1 (en) | 2013-03-27 |

| US20110285757A1 (en) | 2011-11-24 |

| WO2011146459A1 (en) | 2011-11-24 |

| TW201209792A (en) | 2012-03-01 |

| US20110285683A1 (en) | 2011-11-24 |

| KR20130108510A (ko) | 2013-10-04 |

| CN102947875A (zh) | 2013-02-27 |

| WO2011146476A1 (en) | 2011-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2013530421A (ja) | ディスプレイモードを選択するためのシステムおよび方法 | |

| KR101158349B1 (ko) | 디스플레이의 전력 소비를 저감시키는 방법 및 시스템 | |

| KR101222096B1 (ko) | 미소 기전 시스템 디스플레이 소자의 작동을 위한 시스템및 방법 | |

| JP5696216B2 (ja) | Imodディスプレイのための誘電性の向上したミラー | |

| JP2014517930A (ja) | 一体型の容量性タッチデバイスのための配線および周辺機器 | |

| KR20140125820A (ko) | 디스플레이 모드들을 선정하기 위한 시스템 및 방법 | |

| JP2013522665A (ja) | ディスプレイのリフレッシュレートを増大可能とするライン逓倍 | |

| JP2014527194A (ja) | 反射モード式変調器のフィールド順次式カラー構造 | |

| JP2014514597A (ja) | 単一のインダクタから正電圧と負電圧とを供給するためのシステムおよび方法 | |

| JP2015504532A (ja) | ディスプレイのためのシフトされたクワッドピクセルおよび他のピクセルのモザイク | |

| TW201407587A (zh) | 用於反射式顯示器的場色序架構的增強型灰階方法 | |

| JP2015502570A (ja) | ディスプレイを駆動するためのシステム、デバイス、および方法 | |

| JP5801424B2 (ja) | 非アクティブダミーピクセル | |

| KR20120098776A (ko) | 컬러 행 및 에너지 절감 행 구동 시퀀스를 구비하는 디스플레이 | |

| JP2014510950A (ja) | ライン時間低減のための方法および装置 | |

| US20130314449A1 (en) | Display with selective line updating and polarity inversion | |

| JP2014510951A (ja) | 色依存の書込み波形のタイミング | |

| JP2014512566A (ja) | マルチカラーディスプレイを調整するためのシステムおよび方法 | |

| JP2014519050A (ja) | 機械層およびそれを製作する方法 | |

| JP2015502571A (ja) | 書込み波形のポーチ重複 | |

| JP2014535074A (ja) | ディスプレイの駆動における極性反転の影響を低減するための方法およびデバイス | |

| JP2014531057A (ja) | フレームレートを上げるための適応ライン時間 | |

| JP2015505985A (ja) | ディスプレイ用の駆動方式 | |

| US20130113771A1 (en) | Display drive waveform for writing identical data |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131121 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131217 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140314 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140324 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140417 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140516 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141201 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150420 |