JP2010157690A - 電子部品実装用基板及び電子部品実装用基板の製造方法 - Google Patents

電子部品実装用基板及び電子部品実装用基板の製造方法 Download PDFInfo

- Publication number

- JP2010157690A JP2010157690A JP2009261724A JP2009261724A JP2010157690A JP 2010157690 A JP2010157690 A JP 2010157690A JP 2009261724 A JP2009261724 A JP 2009261724A JP 2009261724 A JP2009261724 A JP 2009261724A JP 2010157690 A JP2010157690 A JP 2010157690A

- Authority

- JP

- Japan

- Prior art keywords

- electronic component

- insulating layer

- conductor

- component mounting

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 49

- 239000004020 conductor Substances 0.000 claims abstract description 285

- 239000000758 substrate Substances 0.000 claims description 152

- 238000000034 method Methods 0.000 claims description 80

- 229920005989 resin Polymers 0.000 claims description 45

- 239000011347 resin Substances 0.000 claims description 45

- 239000004065 semiconductor Substances 0.000 claims description 27

- 239000003990 capacitor Substances 0.000 claims description 22

- 239000000463 material Substances 0.000 claims description 16

- 239000000654 additive Substances 0.000 claims description 6

- 229910044991 metal oxide Inorganic materials 0.000 claims description 5

- 150000004706 metal oxides Chemical class 0.000 claims description 5

- 230000007423 decrease Effects 0.000 claims description 3

- 238000009413 insulation Methods 0.000 abstract 7

- 239000010408 film Substances 0.000 description 38

- 238000007747 plating Methods 0.000 description 38

- 229910052802 copper Inorganic materials 0.000 description 32

- 239000010949 copper Substances 0.000 description 32

- 230000001681 protective effect Effects 0.000 description 30

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 28

- 229910052751 metal Inorganic materials 0.000 description 27

- 239000002184 metal Substances 0.000 description 27

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 23

- 229910052710 silicon Inorganic materials 0.000 description 23

- 239000010703 silicon Substances 0.000 description 23

- 230000004888 barrier function Effects 0.000 description 20

- 229910004298 SiO 2 Inorganic materials 0.000 description 18

- 238000005530 etching Methods 0.000 description 16

- 238000004544 sputter deposition Methods 0.000 description 10

- 230000000694 effects Effects 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 229910010272 inorganic material Inorganic materials 0.000 description 8

- 239000011147 inorganic material Substances 0.000 description 8

- 229920001187 thermosetting polymer Polymers 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 5

- 239000003822 epoxy resin Substances 0.000 description 5

- -1 for example Substances 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- 229920000647 polyepoxide Polymers 0.000 description 5

- 229910000679 solder Inorganic materials 0.000 description 5

- 229910052718 tin Inorganic materials 0.000 description 5

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000009719 polyimide resin Substances 0.000 description 4

- 239000004695 Polyether sulfone Substances 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 239000005011 phenolic resin Substances 0.000 description 3

- 239000013034 phenoxy resin Substances 0.000 description 3

- 229920006287 phenoxy resin Polymers 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- 229920002492 poly(sulfone) Polymers 0.000 description 3

- 229920006393 polyether sulfone Polymers 0.000 description 3

- 229920001955 polyphenylene ether Polymers 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- 229920005992 thermoplastic resin Polymers 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N 2-Propenoic acid Natural products OC(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 239000004697 Polyetherimide Substances 0.000 description 2

- 239000004734 Polyphenylene sulfide Substances 0.000 description 2

- MCMNRKCIXSYSNV-UHFFFAOYSA-N Zirconium dioxide Chemical compound O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 239000000805 composite resin Substances 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 230000020169 heat generation Effects 0.000 description 2

- 150000003949 imides Chemical class 0.000 description 2

- 238000007733 ion plating Methods 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229920001601 polyetherimide Polymers 0.000 description 2

- 229920005672 polyolefin resin Polymers 0.000 description 2

- 229920000069 polyphenylene sulfide Polymers 0.000 description 2

- 229920012287 polyphenylene sulfone Polymers 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- XQUPVDVFXZDTLT-UHFFFAOYSA-N 1-[4-[[4-(2,5-dioxopyrrol-1-yl)phenyl]methyl]phenyl]pyrrole-2,5-dione Chemical compound O=C1C=CC(=O)N1C(C=C1)=CC=C1CC1=CC=C(N2C(C=CC2=O)=O)C=C1 XQUPVDVFXZDTLT-UHFFFAOYSA-N 0.000 description 1

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- JOYRKODLDBILNP-UHFFFAOYSA-N Ethyl urethane Chemical compound CCOC(N)=O JOYRKODLDBILNP-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- CERQOIWHTDAKMF-UHFFFAOYSA-N Methacrylic acid Chemical compound CC(=C)C(O)=O CERQOIWHTDAKMF-UHFFFAOYSA-N 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000005062 Polybutadiene Substances 0.000 description 1

- 229920000265 Polyparaphenylene Polymers 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- 229910004166 TaN Inorganic materials 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000008602 contraction Effects 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000004090 dissolution Methods 0.000 description 1

- 229920001971 elastomer Polymers 0.000 description 1

- 238000005566 electron beam evaporation Methods 0.000 description 1

- 238000000313 electron-beam-induced deposition Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 125000003700 epoxy group Chemical group 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920003192 poly(bis maleimide) Polymers 0.000 description 1

- 229920002857 polybutadiene Polymers 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 239000005060 rubber Substances 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229920002379 silicone rubber Polymers 0.000 description 1

- 239000004945 silicone rubber Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000001947 vapour-phase growth Methods 0.000 description 1

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/16—Printed circuits incorporating printed electric components, e.g. printed resistor, capacitor, inductor

- H05K1/162—Printed circuits incorporating printed electric components, e.g. printed resistor, capacitor, inductor incorporating printed capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4682—Manufacture of core-less build-up multilayer circuits on a temporary carrier or on a metal foil

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4688—Composite multilayer circuits, i.e. comprising insulating layers having different properties

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/145—Organic substrates, e.g. plastic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00011—Not relevant to the scope of the group, the symbol of which is combined with the symbol of this group

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0137—Materials

- H05K2201/0175—Inorganic, non-metallic layer, e.g. resist or dielectric for printed capacitor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0137—Materials

- H05K2201/0179—Thin film deposited insulating layer, e.g. inorganic layer for printed capacitor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09372—Pads and lands

- H05K2201/09436—Pads or lands on permanent coating which covers the other conductors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09509—Blind vias, i.e. vias having one side closed

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/09509—Blind vias, i.e. vias having one side closed

- H05K2201/09527—Inverse blind vias, i.e. bottoms outwards in multilayer PCB; Blind vias in centre of PCB having opposed bottoms

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/096—Vertically aligned vias, holes or stacked vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/108—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by semi-additive methods; masks therefor

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

- Y10T29/49158—Manufacturing circuit on or in base with molding of insulated base

- Y10T29/4916—Simultaneous circuit manufacturing

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Ceramic Engineering (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

【課題】実装信頼性が高い電子部品実装用基板を提供する。

【解決手段】支持層40の第1面上に形成されている有機絶縁層30と、上記有機絶縁層30の表面のうち上記支持層40の第1面に接する第2面上、又は、上記有機絶縁層30の第2面側の内部に形成されている第1導体回路31と、上記有機絶縁層30において上記第2面とは反対側に位置する第1面上に形成されている無機絶縁層20と、上記無機絶縁層20の内部に形成されている第2導体回路21と、上記電子部品を実装するためのパッド22と、上記有機絶縁層30の内部に形成されていて、上記第2導体回路21と上記第1導体回路31とを電気的に接続するビア導体32と、上記支持層40において上記第1面とは反対側に位置する第2面側に形成されている導体と、上記支持層40内に設けられており、上記第1導体回路31と上記導体とを電気的に接続する導体ポスト41と、からなる。

【選択図】図2

【解決手段】支持層40の第1面上に形成されている有機絶縁層30と、上記有機絶縁層30の表面のうち上記支持層40の第1面に接する第2面上、又は、上記有機絶縁層30の第2面側の内部に形成されている第1導体回路31と、上記有機絶縁層30において上記第2面とは反対側に位置する第1面上に形成されている無機絶縁層20と、上記無機絶縁層20の内部に形成されている第2導体回路21と、上記電子部品を実装するためのパッド22と、上記有機絶縁層30の内部に形成されていて、上記第2導体回路21と上記第1導体回路31とを電気的に接続するビア導体32と、上記支持層40において上記第1面とは反対側に位置する第2面側に形成されている導体と、上記支持層40内に設けられており、上記第1導体回路31と上記導体とを電気的に接続する導体ポスト41と、からなる。

【選択図】図2

Description

本発明は、電子部品実装用基板及び電子部品実装用基板の製造方法に関する。

ロジック、メモリなどの半導体素子が実装される中間基板として、インターポーザーと呼ばれる電子部品実装用基板が用いられている。

特許文献1には、シリコン基板上に微細配線が形成された半導体装置用基板が開示されている。特許文献1に記載の基板においては、シリコン基板中に、シリコン基板の表面と裏面との間を接続する実装端子が形成されている。

特許文献1に示された半導体装置用基板の実施形態では、異方性エッチングにより角錐形状の実装端子が形成され、角錐形状の実装端子の先端は半導体素子の電極端子に接続される。しかしながら、実装対象である半導体素子の電極がファインピッチになるに伴い、それに追従した実装端子の形成は困難となる。

また、半導体装置用基板をそのシリコン基板側でプリント配線基板に実装した場合、プリント配線基板とシリコン基板との熱膨張係数の差が大きいため、その差に起因して発生する応力により例えば接続端子(バンプ)にクラックが生じ、半導体素子の実装信頼性が低くなってしまうという問題があった。

また、シリコン基板を有する分だけ半導体装置用基板の厚さが厚くなってしまい、装置全体の高さが大きくなってしまうという問題があった。

また、半導体装置用基板をそのシリコン基板側でプリント配線基板に実装した場合、プリント配線基板とシリコン基板との熱膨張係数の差が大きいため、その差に起因して発生する応力により例えば接続端子(バンプ)にクラックが生じ、半導体素子の実装信頼性が低くなってしまうという問題があった。

また、シリコン基板を有する分だけ半導体装置用基板の厚さが厚くなってしまい、装置全体の高さが大きくなってしまうという問題があった。

本発明は、上記のような問題に鑑み、電極のピッチが狭い半導体素子を一方の面に実装することができ、かつ、他方の面でプリント配線基板に実装した場合の実装信頼性が高い電子部品実装用基板を提供することを目的とする。また、シリコン基板を有さず、実装高さを小さくすることができる電子部品実装用基板を提供することを目的とする。

また、上記特徴を有する電子部品実装用基板の製造方法を提供することを目的とする。

また、上記特徴を有する電子部品実装用基板の製造方法を提供することを目的とする。

すなわち、請求項1に記載の電子部品実装用基板は、プリント配線基板と電子部品との間に介在される電子部品実装用基板であって、

樹脂からなる支持層と、

上記支持層の第1面上に形成されている少なくとも1層の有機絶縁層と、

上記有機絶縁層の表面のうち上記支持層の第1面に接する第2面上、又は、上記有機絶縁層の第2面側の内部に形成されている第1導体回路と、

上記有機絶縁層において上記第2面とは反対側に位置する第1面上に形成されている無機絶縁層と、

上記無機絶縁層の内部に形成されている第2導体回路と、

上記無機絶縁層の内部に形成されていて、上記電子部品を実装するためのパッドと、

上記有機絶縁層の内部に形成されていて、上記第2導体回路と上記第1導体回路とを電気的に接続するビア導体と、

上記支持層において上記第1面とは反対側に位置する第2面側に形成されている導体と、上記支持層内に設けられており、上記第1導体回路と上記導体とを電気的に接続する導体ポストと、からなることを特徴とする。

樹脂からなる支持層と、

上記支持層の第1面上に形成されている少なくとも1層の有機絶縁層と、

上記有機絶縁層の表面のうち上記支持層の第1面に接する第2面上、又は、上記有機絶縁層の第2面側の内部に形成されている第1導体回路と、

上記有機絶縁層において上記第2面とは反対側に位置する第1面上に形成されている無機絶縁層と、

上記無機絶縁層の内部に形成されている第2導体回路と、

上記無機絶縁層の内部に形成されていて、上記電子部品を実装するためのパッドと、

上記有機絶縁層の内部に形成されていて、上記第2導体回路と上記第1導体回路とを電気的に接続するビア導体と、

上記支持層において上記第1面とは反対側に位置する第2面側に形成されている導体と、上記支持層内に設けられており、上記第1導体回路と上記導体とを電気的に接続する導体ポストと、からなることを特徴とする。

請求項1に記載の電子部品実装用基板においては、樹脂からなる支持層が設けられており、支持層内には導体ポストが設けられている。

そして、電子部品実装用基板の支持層の第2面側で、電子部品実装用基板をプリント配線基板に実装することができる。このため、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力が導体ポストにより緩和される。このため、例えば、電子部品実装用基板をプリント配線基板に実装する際に用いられるバンプに応力が集中することがほとんどなくなり、バンプにクラックが入ることを抑制することが可能となる。その結果、電子部品実装用基板の実装信頼性を確保することが可能となる。

一方、支持層の第1面側には有機絶縁層が設けられ、さらに有機絶縁層上には無機絶縁層が設けられている。そして、無機絶縁層の内部には電子部品を実装するためのパッドが設けられている。このパッドは無機絶縁層の内部に形成された第2導体回路を用いた微細配線により配線されたものであり、ファインピッチ化されている。

そのため、無機絶縁層の内部に形成されたパッドに電子部品、特にファインピッチの端子(電極)を有する半導体素子を実装させることができる。

そして、電子部品実装用基板の支持層の第2面側で、電子部品実装用基板をプリント配線基板に実装することができる。このため、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力が導体ポストにより緩和される。このため、例えば、電子部品実装用基板をプリント配線基板に実装する際に用いられるバンプに応力が集中することがほとんどなくなり、バンプにクラックが入ることを抑制することが可能となる。その結果、電子部品実装用基板の実装信頼性を確保することが可能となる。

一方、支持層の第1面側には有機絶縁層が設けられ、さらに有機絶縁層上には無機絶縁層が設けられている。そして、無機絶縁層の内部には電子部品を実装するためのパッドが設けられている。このパッドは無機絶縁層の内部に形成された第2導体回路を用いた微細配線により配線されたものであり、ファインピッチ化されている。

そのため、無機絶縁層の内部に形成されたパッドに電子部品、特にファインピッチの端子(電極)を有する半導体素子を実装させることができる。

また、無機絶縁層内部には微細配線を形成することができるため、無機絶縁層内部に第2導体回路を用いた微細配線を形成することによって、層数を増やして徐々に配線をファンアウトさせる必要がなく、少ない層数で電子部品の端子のファイン化に対応することが可能となる。

また、半導体素子等の電子部品は通常シリコン等の無機材料からなるため、電子部品が無機絶縁層に近接して電子部品実装用基板に実装された場合には、電子部品と電子部品実装用基板の間の熱膨張係数の差が小さく、実装信頼性が高くなる。

請求項2に記載の電子部品実装用基板では、上記導体ポストのアスペクト比は、4.0〜6.5である。

このような構成であると、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力を容易に緩和することが可能となる。

このような構成であると、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力を容易に緩和することが可能となる。

請求項3に記載の電子部品実装用基板では、第1導体回路は、第2導体回路よりも厚さが厚い。

また、請求項4に記載の電子部品実装用基板では、第1導体回路は、第2導体回路よりも断面積が大きい。

第1導体回路を構成する配線の厚さが厚いか、断面積が大きいと、第1導体回路の配線抵抗が第2導体回路と比較して小さくなる。このため、無機絶縁層内の第2導体回路のみで半導体素子とプリント配線基板との配線を行う場合と比較して、電子部品実装用基板全体の配線抵抗を小さくすることができる。

また、請求項4に記載の電子部品実装用基板では、第1導体回路は、第2導体回路よりも断面積が大きい。

第1導体回路を構成する配線の厚さが厚いか、断面積が大きいと、第1導体回路の配線抵抗が第2導体回路と比較して小さくなる。このため、無機絶縁層内の第2導体回路のみで半導体素子とプリント配線基板との配線を行う場合と比較して、電子部品実装用基板全体の配線抵抗を小さくすることができる。

請求項5に記載の電子部品実装用基板では、上記有機絶縁層のうち、最も無機絶縁層に近い側に位置する有機絶縁層の内部にはビア導体のみが形成されており、導体回路が形成されていない。

最も無機絶縁層に近い側に位置する有機絶縁層(最外層の有機絶縁層)は、電子部品の発熱に起因する熱履歴の影響を最も受けやすい。その結果、仮に最外層の有機絶縁層内に導体回路が存在する場合は、導体回路を形成する金属と有機絶縁層との間の熱膨張係数の差により、例えば導体回路のエッジ部分を起点として有機絶縁層内にクラックが入る可能性が高い。上記構成である場合には、最外層の有機絶縁層内に導体回路が形成されていない

ことから、そうしたクラックが生じることはほとんどない。

最も無機絶縁層に近い側に位置する有機絶縁層(最外層の有機絶縁層)は、電子部品の発熱に起因する熱履歴の影響を最も受けやすい。その結果、仮に最外層の有機絶縁層内に導体回路が存在する場合は、導体回路を形成する金属と有機絶縁層との間の熱膨張係数の差により、例えば導体回路のエッジ部分を起点として有機絶縁層内にクラックが入る可能性が高い。上記構成である場合には、最外層の有機絶縁層内に導体回路が形成されていない

ことから、そうしたクラックが生じることはほとんどない。

請求項6に記載の電子部品実装用基板において、上記ビア導体は、上記有機絶縁層の第2面から第1面に向かって断面積が小さくなるようにテーパした側面を有する。

このような構成であると、ビア導体の頂部は緩やか(鈍角)な形状となる。このため、例えば電子部品の発熱によって有機絶縁層に内部応力が発生したとしても、ビア導体の頂部に集中する応力は緩和される。その結果、ビア導体の頂部を基点として有機絶縁層内にクラックが生じることを効果的に抑制することができる。

このような構成であると、ビア導体の頂部は緩やか(鈍角)な形状となる。このため、例えば電子部品の発熱によって有機絶縁層に内部応力が発生したとしても、ビア導体の頂部に集中する応力は緩和される。その結果、ビア導体の頂部を基点として有機絶縁層内にクラックが生じることを効果的に抑制することができる。

請求項7に記載の電子部品実装用基板では、上記支持層は、その30℃におけるヤング率が10〜1000MPaである材料からなる。

支持層のヤング率が上記範囲内であると、支持層を設けることによって電子部品実装用基板の強度をより良好に保つことができる。

支持層のヤング率が上記範囲内であると、支持層を設けることによって電子部品実装用基板の強度をより良好に保つことができる。

請求項8に記載の電子部品実装用基板の製造方法は、支持基板上に無機絶縁層を形成すること、

上記無機絶縁層の内部に第2導体回路及びパッドを形成すること、

上記無機絶縁層上に少なくとも1層の有機絶縁層を形成すること、

上記有機絶縁層の内部又は上記有機絶縁層の上に第1導体回路を形成するとともに、上記第2導体回路と上記第1導体回路とを電気的に接続するビア導体を形成すること、

上記有機絶縁層の上に支持層を形成すること、

上記支持層上に導体を形成するとともに、上記支持層内に上記導体と上記第1導体回路とを電気的に接続する導体ポストを形成すること、

上記支持基板を剥離すること、

とからなることを特徴とする。

上記工程によると、一方の面にファインピッチの端子(電極)を有する半導体素子を実装することができ、かつ、他方の面にプリント配線基板を実装した場合の実装信頼性が高い電子部品実装用基板を製造することができる。

上記無機絶縁層の内部に第2導体回路及びパッドを形成すること、

上記無機絶縁層上に少なくとも1層の有機絶縁層を形成すること、

上記有機絶縁層の内部又は上記有機絶縁層の上に第1導体回路を形成するとともに、上記第2導体回路と上記第1導体回路とを電気的に接続するビア導体を形成すること、

上記有機絶縁層の上に支持層を形成すること、

上記支持層上に導体を形成するとともに、上記支持層内に上記導体と上記第1導体回路とを電気的に接続する導体ポストを形成すること、

上記支持基板を剥離すること、

とからなることを特徴とする。

上記工程によると、一方の面にファインピッチの端子(電極)を有する半導体素子を実装することができ、かつ、他方の面にプリント配線基板を実装した場合の実装信頼性が高い電子部品実装用基板を製造することができる。

請求項9に記載の電子部品実装用基板の製造方法では、上記第1導体回路をセミアディティブ法により形成する。

セミアディティブ法を用いることによって、第2導体回路よりも単位長さ当たりの配線抵抗が小さい第1導体回路を簡便且つ低コストで形成することができる。

セミアディティブ法を用いることによって、第2導体回路よりも単位長さ当たりの配線抵抗が小さい第1導体回路を簡便且つ低コストで形成することができる。

請求項10に記載の電子部品実装用基板の製造方法では、上記支持層の内部に上記第1導体回路の一部を露出させる開口を形成した後、上記開口内に導体ポストを形成する。

上記工程によると、アスペクト比の大きい導体ポストであっても良好に形成することができる。

上記工程によると、アスペクト比の大きい導体ポストであっても良好に形成することができる。

請求項11に記載の電子部品実装用基板の製造方法では、上記第2導体回路をダマシン法により形成する。

ダマシン法を用いることによって、微細な引き回しを行う第2導体回路を精度よく形成することができる。さらに、平坦性の高い配線を形成することが可能となる。

ダマシン法を用いることによって、微細な引き回しを行う第2導体回路を精度よく形成することができる。さらに、平坦性の高い配線を形成することが可能となる。

請求項12に記載の電子部品実装用基板は、プリント配線基板と電子部品との間に介在される電子部品実装用基板であって、

樹脂からなる支持層と、

上記支持層の第1面上に形成されている少なくとも1層の有機絶縁層と、

上記有機絶縁層の表面のうち上記支持層の第1面に接する第2面上、又は、上記有機絶縁層の第2面側の内部に形成されている第1導体回路と、

上記有機絶縁層において上記第2面とは反対側に位置する第1面上に形成されているキャパシタと、

上記支持層において上記第1面とは反対側に位置する第2面側に形成されている導体と、上記支持層内に設けられており、上記第1導体回路と上記導体とを電気的に接続する導体ポストと、を備え、

上記キャパシタは、開口部を有する下部電極と、上記下部電極上に形成された誘電体層と、上記誘電体層上に形成され開口部を有する上部電極とからなり、

上記下部電極及び上記上部電極の一方が半導体素子の電源ラインに接続されるとともに、他方がグランドラインに接続されることを特徴とする。

樹脂からなる支持層と、

上記支持層の第1面上に形成されている少なくとも1層の有機絶縁層と、

上記有機絶縁層の表面のうち上記支持層の第1面に接する第2面上、又は、上記有機絶縁層の第2面側の内部に形成されている第1導体回路と、

上記有機絶縁層において上記第2面とは反対側に位置する第1面上に形成されているキャパシタと、

上記支持層において上記第1面とは反対側に位置する第2面側に形成されている導体と、上記支持層内に設けられており、上記第1導体回路と上記導体とを電気的に接続する導体ポストと、を備え、

上記キャパシタは、開口部を有する下部電極と、上記下部電極上に形成された誘電体層と、上記誘電体層上に形成され開口部を有する上部電極とからなり、

上記下部電極及び上記上部電極の一方が半導体素子の電源ラインに接続されるとともに、他方がグランドラインに接続されることを特徴とする。

このような構成であると、半導体素子を実装した際にキャパシタが半導体素子の直下に位置することとなる。そのため、半導体素子に対して最短距離で瞬時に電源供給を行うことが可能となり、デカップリング効果が得られる。その結果、半導体素子の誤作動を防止することができる。

請求項13に記載の電子部品実装用基板は、上記下部電極の開口部を通過して上記上部電極に接続される第1導体と、上記上部電極の開口部を通過して上記下部電極に接続される第2導体とを備える。

請求項14に記載の電子部品実装用基板では、上記誘電体層は、単一金属酸化物よりなる。

(第一実施形態)

以下、本発明の実施形態を説明する。

図1は、本発明の電子部品実装用基板が用いられる態様の一例を模式的に示す断面図である。

本実施形態の電子部品実装用基板1は、図1に示すように、電子部品200(各電子部品は、ロジック及び/又はメモリ等の半導体素子を含む)とプリント配線基板100との間に配置されている。

電子部品200と電子部品実装用基板1は、例えばバンプ61を介して接続されている。電子部品実装用基板1とプリント配線板100は、例えばバンプ51を介して接続されている。

以下、本発明の実施形態を説明する。

図1は、本発明の電子部品実装用基板が用いられる態様の一例を模式的に示す断面図である。

本実施形態の電子部品実装用基板1は、図1に示すように、電子部品200(各電子部品は、ロジック及び/又はメモリ等の半導体素子を含む)とプリント配線基板100との間に配置されている。

電子部品200と電子部品実装用基板1は、例えばバンプ61を介して接続されている。電子部品実装用基板1とプリント配線板100は、例えばバンプ51を介して接続されている。

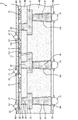

図2は、本発明の電子部品実装用基板の一例の一部分を模式的に示す断面図である。

本実施形態の電子部品実装用基板1は、図2の下側から、支持層40、有機絶縁層30、無機絶縁層20を有する。

なお、図2において支持層40、有機絶縁層30及び無機絶縁層20の上側の面をそれぞれの層の第1面ということとし、下側の面をそれぞれの層の第2面ということとする。

なお、図2において支持層40、有機絶縁層30及び無機絶縁層20の上側の面をそれぞれの層の第1面ということとし、下側の面をそれぞれの層の第2面ということとする。

支持層40の第1面側であって有機絶縁層30の第2面上(図2における下側)には第1導体回路31が形成されている。支持層40の第2面上(図2における下側)には導体57(図2では第3導体回路56及びパッド55)が形成されている。そして、支持層40の内部には導体ポスト41が設けられている。この導体ポスト41により、第1導体回路31と導体57とが電気的に接続されている。

保護膜50には、導体57の一部を露出する開口53が形成されていて、導体57のうち、開口53から露出される部分がパッド55として機能する。パッド55上には、バリアメタル層54が形成されている。そして、パッド55上には、バリアメタル層54を介してバンプ51が形成されている。このバンプ51を介して、電子部品実装用基板1がプリント配線基板100に実装されている(図3参照)。

保護膜50には、導体57の一部を露出する開口53が形成されていて、導体57のうち、開口53から露出される部分がパッド55として機能する。パッド55上には、バリアメタル層54が形成されている。そして、パッド55上には、バリアメタル層54を介してバンプ51が形成されている。このバンプ51を介して、電子部品実装用基板1がプリント配線基板100に実装されている(図3参照)。

無機絶縁層20は、SiO2(二酸化珪素)からなる。無機絶縁層20の内部には、電子部品を実装するためのパッド22及び第2導体回路21が設けられている。無機絶縁層2

0上に形成されているSi3N4層60は、保護膜として機能する層であり、Si3N4層60にはパッド22の一部を露出する開口64が形成されている。パッド22上には、バリアメタル層65が形成されている。そして、パッド22上には、バリアメタル層65を介してバンプ61が形成されている。このバンプ61を介して、電子部品200が電子部品実装用基板1に実装されている。(図3参照)。

また、第2導体回路21(パッド22)と第1導体回路31とは、有機絶縁層30の内部に設けられたビア導体32により電気的に接続されている。

0上に形成されているSi3N4層60は、保護膜として機能する層であり、Si3N4層60にはパッド22の一部を露出する開口64が形成されている。パッド22上には、バリアメタル層65が形成されている。そして、パッド22上には、バリアメタル層65を介してバンプ61が形成されている。このバンプ61を介して、電子部品200が電子部品実装用基板1に実装されている。(図3参照)。

また、第2導体回路21(パッド22)と第1導体回路31とは、有機絶縁層30の内部に設けられたビア導体32により電気的に接続されている。

以下、これら各部位の詳細について、図2を参照して、下側から順次説明する。

まず、支持層40及び導体ポスト41について説明する。

支持層40は、樹脂からなる層であり、支持層40の材料としては、エポキシ樹脂、イミド系樹脂、フェノール樹脂、シリコーン樹脂等の熱硬化性樹脂や、ポリオレフィン系樹脂、ビニル系樹脂、イミド系樹脂等の熱可塑性樹脂にゴム系成分(ポリブタジエン、シリコーンゴム、ウレタン、SBR、NBRなど)及びシリカ、アルミナ、ジルコニアなどの無機成分が分散したものが挙げられる。

また、支持層の材料である樹脂の30℃におけるヤング率は10〜1000MPaとなっている。

支持層40は、樹脂からなる層であり、支持層40の材料としては、エポキシ樹脂、イミド系樹脂、フェノール樹脂、シリコーン樹脂等の熱硬化性樹脂や、ポリオレフィン系樹脂、ビニル系樹脂、イミド系樹脂等の熱可塑性樹脂にゴム系成分(ポリブタジエン、シリコーンゴム、ウレタン、SBR、NBRなど)及びシリカ、アルミナ、ジルコニアなどの無機成分が分散したものが挙げられる。

また、支持層の材料である樹脂の30℃におけるヤング率は10〜1000MPaとなっている。

導体ポスト41は、支持層40内に形成された柱状の導体であり、銅めっき及び銅めっきの下のシード層141からなる。

一般的に有機材料からなるプリント配線基板と、一般的に無機材料からなる電子部品とを電子部品実装用基板のそれぞれの面に接続すると、上記有機材料と上記無機材料の熱膨張率差に起因して、温度変化による歪みが発生する。しかしながら、支持層内に柱状の導体ポストを設けることによってその歪みが緩和される。その結果、バンプに応力が集中することがほとんどなくなり、バンプにクラックが入ることを抑制することが可能となる。

一般的に有機材料からなるプリント配線基板と、一般的に無機材料からなる電子部品とを電子部品実装用基板のそれぞれの面に接続すると、上記有機材料と上記無機材料の熱膨張率差に起因して、温度変化による歪みが発生する。しかしながら、支持層内に柱状の導体ポストを設けることによってその歪みが緩和される。その結果、バンプに応力が集中することがほとんどなくなり、バンプにクラックが入ることを抑制することが可能となる。

導体ポストの高さ(厚さ)は、20〜400μmであることが望ましい。

導体ポストの高さが20μm以上であると、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力を緩和しやすくなる。

また、導体ポストの高さを400μm以下とすると、めっきにより導体ポストを容易に形成することができるために好ましい。

導体ポストの高さが20μm以上であると、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力を緩和しやすくなる。

また、導体ポストの高さを400μm以下とすると、めっきにより導体ポストを容易に形成することができるために好ましい。

導体ポストの径は、10〜200μmであることが望ましい。また、導体ポストのアスペクト比(高さ/径)は4.0〜6.5であることが望ましい。

なお、導体ポストの径は、導体ポストが円柱形状であるときはその底面の直径であり、他の形状のときはその形状の重心を通る最大の径として定める。

なお、導体ポストの径は、導体ポストが円柱形状であるときはその底面の直径であり、他の形状のときはその形状の重心を通る最大の径として定める。

次に、有機絶縁層30、第1導体回路31及びビア導体32について説明する。

本実施形態における有機絶縁層30は、有機材料よりなり、支持層40の第1面上に形成されている。この有機絶縁層30は、開口36を有し、開口36にはビア導体32が形成されている。さらに、有機絶縁層30の第2面(有機絶縁層30の面であって支持層40の第1面側の面)上には、第1導体回路31が形成されている。

本実施形態における有機絶縁層30は、有機材料よりなり、支持層40の第1面上に形成されている。この有機絶縁層30は、開口36を有し、開口36にはビア導体32が形成されている。さらに、有機絶縁層30の第2面(有機絶縁層30の面であって支持層40の第1面側の面)上には、第1導体回路31が形成されている。

有機絶縁層30は、熱硬化性樹脂、感光性樹脂、熱硬化性樹脂の一部に感光性基が付与された樹脂、熱可塑性樹脂、又は、これらの樹脂を含む樹脂複合体等からなる層である。

具体的には、感光性ポリイミド樹脂からなることが望ましい。

具体的には、感光性ポリイミド樹脂からなることが望ましい。

第1導体回路31及びビア導体32は、銅めっき及び銅めっきの下のシード層131からなる。シード層の構成の一例については本実施形態の電子部品実装用基板の製造方法の項

で説明する。

で説明する。

本実施形態において、第1導体回路31及びビア導体32は例えばセミアディティブ法によって形成されており、第1導体回路31を構成する配線のL/Sは後述する第2導体回路21を構成する配線のL/Sと比べて大きくなっている。本実施形態における第1導体回路を構成する配線のL/Sは、L/S=3μm/3μmだが、これに限定されるものではない。第1導体回路を構成する配線の本数及び第1導体回路が形成される領域の面積等に応じて適宜決定すればよい。

第1導体回路31は、第2導体回路21よりも厚さが大きい。本実施形態における第1導体回路31の厚さは、特に限定されるものではないが、2μmより大きく、30μm以下であることが好ましい。第1導体回路31の厚さがこの範囲の場合、電子部品実装用基板の反りを抑制しつつ、第1導体回路31の配線抵抗を低減させることが可能となる。加えて、電子部品実装用基板の厚さが増大することもない。なお、第1導体回路の厚さは、その長さ方向における任意の10箇所の断面に基づいて走査型電子顕微鏡を用いて測定して得られた各々の値の平均値を意味する。第2導体回路の厚さに関しても同様である。

また、第2導体回路の厚さに対する第1導体回路の厚さの割合(第1導体回路の厚さ/第2導体回路の厚さ)は、1より大きく15以下である。上記割合が1以下の場合は、電子部品実装用基板の剛性が充分に確保されず、電子部品と電子部品実装用基板との間の熱膨張係数の相違に起因して電子部品実装用基板に反りが生じる可能性がある。一方、上記割合が15を超える場合は、仮に配線幅が同じだと仮定すると第1導体回路のアスペクト比が大きくなってしまい、例えば熱履歴により有機絶縁層が膨張収縮した際にはその有機絶縁層の膨張収縮に第1導体回路が容易に追従してしまい、有機絶縁層に対する第1導体回路の密着性が低下する可能性がある。

また、第1導体回路31を構成する配線の断面積は、第2導体回路21を構成する配線の断面積に対して大きいことが望ましく、特に3〜10倍であることが望ましい。第1導体回路を構成する配線の断面積を大きくすることによって、第1導体回路の単位長さあたりの配線抵抗が小さくなる。

例えば、第2導体回路21を構成する配線と第1導体回路31を構成する配線のアスペクト比がともに1:1である場合に、第2導体回路を構成する配線のL/S=1μm/1μm、第1導体回路を構成する配線のL/S=3μm/3μmとすると、第1導体回路を構成する配線の断面積は第2導体回路を構成する配線の断面積の9倍となる。

例えば、第2導体回路21を構成する配線と第1導体回路31を構成する配線のアスペクト比がともに1:1である場合に、第2導体回路を構成する配線のL/S=1μm/1μm、第1導体回路を構成する配線のL/S=3μm/3μmとすると、第1導体回路を構成する配線の断面積は第2導体回路を構成する配線の断面積の9倍となる。

ビア導体32は、有機絶縁層の第2面(図2の下側)から第1面(図2の上側)に向かって断面積が小さくなるようにテーパした側面を有する。また、ビア導体32の第2面側の径は、第1面側の径よりも大きくなっている。

また、最も無機絶縁層20に近い側に位置する有機絶縁層は有機絶縁層30であり、有機絶縁層30の内部にはビア導体32のみが形成されており、導体回路が形成されていない。

次に、無機絶縁層20、第2導体回路21及びパッド22について説明する。

本実施形態における無機絶縁層20は、無機材料よりなり、有機絶縁層30の第1面上に形成されている。この無機絶縁層20の内部には第2導体回路21と電子部品を実装するためのパッド22が形成されている。

本実施形態における無機絶縁層20は、無機材料よりなり、有機絶縁層30の第1面上に形成されている。この無機絶縁層20の内部には第2導体回路21と電子部品を実装するためのパッド22が形成されている。

本実施形態における無機絶縁層20は、SiO2(二酸化珪素)等の無機材料よりなる層である。具体的な層構成の一例については本実施形態の電子部品実装用基板の製造方法の

項で説明するが、無機絶縁層20の構成は、SiO2層のみからなる構成に限定されるものではなく、Si3N4層からなる構成や、SiO2層、Si3N4層等の無機材料からなる層が複数種類、複数層積層された構成であってもよい。

項で説明するが、無機絶縁層20の構成は、SiO2層のみからなる構成に限定されるものではなく、Si3N4層からなる構成や、SiO2層、Si3N4層等の無機材料からなる層が複数種類、複数層積層された構成であってもよい。

第2導体回路21及びパッド22は、銅めっき及び銅めっきの下のシード層126からなる。シード層の構成の一例については本実施形態の電子部品実装用基板の製造方法の項で説明する。

本実施形態において、第2導体回路21及びパッド22はダマシン法によって形成されている。第2導体回路21を構成する配線のL/Sは第1導体回路31を構成する配線のL/Sと比べて小さくなっている。

なお、第2導体回路を構成する配線のL/Sは、特に限定されるものではなく、L/S=1μm/1μm程度であることが望ましいが、それよりもファインであってもよい。

この第2導体回路21の厚さは、第1導体回路の厚さよりも小さい。本実施形態における第2導体回路21の厚さは特に限定されるものではないが、2μm以下であることが好ましい。第2導体回路21の厚さが2μm以下の場合、配線のファイン化が可能となる。

なお、第2導体回路を構成する配線のL/Sは、特に限定されるものではなく、L/S=1μm/1μm程度であることが望ましいが、それよりもファインであってもよい。

この第2導体回路21の厚さは、第1導体回路の厚さよりも小さい。本実施形態における第2導体回路21の厚さは特に限定されるものではないが、2μm以下であることが好ましい。第2導体回路21の厚さが2μm以下の場合、配線のファイン化が可能となる。

パッド22は、電子部品を実装する際に電子部品の接続端子とバンプ等を介して接続される部位である。パッド22は、無機絶縁層20の第1面側でその表面が無機絶縁層20から露出しており、バンプ61と電気的に接続されている。

このバンプ61は電子部品を実装するために用いられるバンプである。

このバンプ61は電子部品を実装するために用いられるバンプである。

また、第2導体回路21及びパッド22はダマシン法によって形成されているため、無機絶縁層20、第2導体回路21及びパッド22からなる表面(無機絶縁層20の第2面側の面)は平坦になっている。

本実施形態の電子部品実装用基板の下側、すなわちプリント配線基板が実装される側に設けられる保護膜50について説明する。

保護膜50は、支持層40の第2面上(図2における下側)に形成されている。この保護膜50内にはパッド55及び第3導体回路56が設けられている。

パッド55及び第3導体回路56は、支持層の第2面上に位置する導体57に該当する。また、パッド55の上(図2における下側)には開口53が設けられ、この開口53にはバリアメタル層54を介してはんだよりなるバンプ51が形成されている。

保護膜50の材料は特に限定されるものではないが、樹脂からなる支持層40との

密着性の観点から、有機材料であることが好ましい。

保護膜50は、支持層40の第2面上(図2における下側)に形成されている。この保護膜50内にはパッド55及び第3導体回路56が設けられている。

パッド55及び第3導体回路56は、支持層の第2面上に位置する導体57に該当する。また、パッド55の上(図2における下側)には開口53が設けられ、この開口53にはバリアメタル層54を介してはんだよりなるバンプ51が形成されている。

保護膜50の材料は特に限定されるものではないが、樹脂からなる支持層40との

密着性の観点から、有機材料であることが好ましい。

本実施形態の電子部品実装用基板の上側、すなわち電子部品が実装される側に設けられる保護膜60について説明する。

保護膜60は、無機絶縁層20の第1面、第2導体回路21及びパッド22の上に形成されている。この保護膜60は、パッド22を部分的に露出させる開口64を有しており、この開口64にはバリアメタル層65を介してはんだよりなるバンプ61が形成されている。

このバンプ61に電子部品の接続端子を接続させることによって、電子部品を電子部品実装用基板を実装することができる。

保護膜60の材料は特に限定されるものではないが、Si3N4等の無機材料が用いられることが好ましい。

保護膜60は、無機絶縁層20の第1面、第2導体回路21及びパッド22の上に形成されている。この保護膜60は、パッド22を部分的に露出させる開口64を有しており、この開口64にはバリアメタル層65を介してはんだよりなるバンプ61が形成されている。

このバンプ61に電子部品の接続端子を接続させることによって、電子部品を電子部品実装用基板を実装することができる。

保護膜60の材料は特に限定されるものではないが、Si3N4等の無機材料が用いられることが好ましい。

図3は、図2に示す電子部品実装用基板に電子部品が実装され、さらにプリント配線基板に電子部品実装用基板が実装された形態の一例を模式的に示す断面図である。

図3に示す電子部品実装用基板1の第1面側には、電子部品200が実装されており、電

子部品200を実装させた電子部品実装用基板1は、その第2面側でプリント配線基板100に実装されている。

図3に示す電子部品実装用基板1の第1面側には、電子部品200が実装されており、電

子部品200を実装させた電子部品実装用基板1は、その第2面側でプリント配線基板100に実装されている。

電子部品実装用基板の第1面側では、バンプ61を介して電子部品200の接続端子(図示せず)が電子部品実装用基板と電気的に接続されている。

また、電子部品200と電子部品実装用基板1との間にはアンダーフィル樹脂62が充填されている。さらに、電子部品200は封止樹脂63により封止されている。

一方、電子部品実装用基板の第2面側では、バンプ51を介して電子部品実装用基板1がプリント配線基板100の接続端子(図示せず)と電気的に接続されている。

また、プリント配線基板100と電子部品実装用基板1との間にはアンダーフィル樹脂52が充填されている。

また、電子部品200と電子部品実装用基板1との間にはアンダーフィル樹脂62が充填されている。さらに、電子部品200は封止樹脂63により封止されている。

一方、電子部品実装用基板の第2面側では、バンプ51を介して電子部品実装用基板1がプリント配線基板100の接続端子(図示せず)と電気的に接続されている。

また、プリント配線基板100と電子部品実装用基板1との間にはアンダーフィル樹脂52が充填されている。

以下、本実施形態の電子部品実装用基板の製造方法について図面を用いて説明する。

図4(a)、図4(b)、図4(c)及び図4(d)は、第一実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

図4(a)、図4(b)、図4(c)及び図4(d)は、第一実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

まず、図4(a)に示すように、支持基板10の上に、保護膜となるSi3N4層60及び無機絶縁層20となるSiO2層20を成膜する。

本実施形態の支持基板10としてはシリコンウェハを用い、支持基板10の上面に、Si3N4層60及びSiO2層20をそれぞれCVD(化学気相成長)法によって成膜する。

本実施形態の支持基板10としてはシリコンウェハを用い、支持基板10の上面に、Si3N4層60及びSiO2層20をそれぞれCVD(化学気相成長)法によって成膜する。

次いで、このSiO2層20の所望の箇所にレジストを塗布し、露光・現像することによってSiO2層20に開口を形成する位置のレジストを除去し、さらにドライエッチングにより開口125を形成する(図4(b))。

このドライエッチングの際、Si3N4層60はストップ層の役割を果たす。

このドライエッチングの際、Si3N4層60はストップ層の役割を果たす。

次に、図4(c)に示すように、Si3N4層60の露出した表面及び無機絶縁層20の表面(SiO2層20の表面)にシード層126を、例えばスパッタリングにより形成する。本実施形態では、シード層126は、下から順にTiN、Ti、Cuのスパッタリング膜により構成されるが、これに限定されるものではない。

次に、シード層126を給電層として電解銅めっきを行い電解銅めっき層を形成する。電解銅めっきは、従来公知の方法により行えばよい。

さらに、CMP(化学機械研磨)を行って、電解銅めっき層、及び、SiO2層20表面のシード層126を除去する。

なお、CMPは従来のダマシン法において知られている方法及び装置を用いて行えばよい。

そして、CMPを行った後に残った電解銅めっき層が、第2導体回路21及びパッド22となる。

これまでの工程をまとめて図4(d)に示している。

以上の工程によって、無機絶縁層、第2導体回路及びパッドを形成することができる。

さらに、CMP(化学機械研磨)を行って、電解銅めっき層、及び、SiO2層20表面のシード層126を除去する。

なお、CMPは従来のダマシン法において知られている方法及び装置を用いて行えばよい。

そして、CMPを行った後に残った電解銅めっき層が、第2導体回路21及びパッド22となる。

これまでの工程をまとめて図4(d)に示している。

以上の工程によって、無機絶縁層、第2導体回路及びパッドを形成することができる。

図5(a)、図5(b)及び図5(c)並びに図6(a)、図6(b)及び図6(c)は、第一実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

まず、図5(a)に示すように、無機絶縁層20及び第2導体回路21の上に有機絶縁層30を形成し、図5(b)に示すように開口36を形成する。

有機絶縁層30を形成する方法としては、例えば未硬化の感光性ポリイミド樹脂をロールコーター等を用いて塗布する方法等を用いることができる。

開口36を形成する方法としては、露光現像処理を用いることができる。

まず、図5(a)に示すように、無機絶縁層20及び第2導体回路21の上に有機絶縁層30を形成し、図5(b)に示すように開口36を形成する。

有機絶縁層30を形成する方法としては、例えば未硬化の感光性ポリイミド樹脂をロールコーター等を用いて塗布する方法等を用いることができる。

開口36を形成する方法としては、露光現像処理を用いることができる。

次に、図5(c)に示すように有機絶縁層30の表面(開口36の壁面を含む)と、開口36より露出した第2導体回路21の上面にシード層131を形成する。

シード層131は、例えばスパッタリングにより形成され、本実施形態においてはTi及びCuよりなる。なお、シード層131の構造は、これに限定されるものではない。

シード層131は、例えばスパッタリングにより形成され、本実施形態においてはTi及びCuよりなる。なお、シード層131の構造は、これに限定されるものではない。

次に、図6(a)に示すように、めっきレジスト132を設け、めっきレジスト132をマスクを介して露光、現像することによって、第1導体回路を形成する位置のめっきレジスト132を除去する。

めっきレジストとしては、例えば感光性ドライフィルム等を使用することができる。

めっきレジストとしては、例えば感光性ドライフィルム等を使用することができる。

続いて、図6(b)に示すように、シード層131を給電層として電解銅めっきを行って、めっきレジスト132が除去された部位に銅めっきを施す。これにより有機絶縁層30内にビア導体32が形成される。

次に、図6(c)に示すように、残っためっきレジストを除去するとともに、除去しためっきレジストの下のシード層131をエッチングによって除去する。これにより、有機絶縁層30の上に第1導体回路31が形成される。なお、このシード層131をエッチングする方法としては特に限定されないが、電解銅めっきのオーバーエッチングを抑制するといった観点から、ドライエッチング(反応性イオンエッチング)が好ましい。

以上の工程により、有機絶縁層、第1導体回路及びビア導体を形成することができる。

以上の工程により、有機絶縁層、第1導体回路及びビア導体を形成することができる。

図7(a)及び図7(b)、図8(a)及び図8(b)、図9(a)及び図9(b)、並びに、図10(a)及び図10(b)は、第一実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

まず、有機絶縁層30上にさらに別の有機絶縁層を形成する。この新たに形成した有機絶縁層が支持層40となる。そして、支持層40の所定の位置に開口42を形成する。この開口42の形成方法としては、特に限定されず、レーザーやフォトリソグラフィが挙げられる。レーザーを採用する際には、有機絶縁層30上にアライメントマークが形成される。

これらの工程をまとめて図7(a)に示している。

まず、有機絶縁層30上にさらに別の有機絶縁層を形成する。この新たに形成した有機絶縁層が支持層40となる。そして、支持層40の所定の位置に開口42を形成する。この開口42の形成方法としては、特に限定されず、レーザーやフォトリソグラフィが挙げられる。レーザーを採用する際には、有機絶縁層30上にアライメントマークが形成される。

これらの工程をまとめて図7(a)に示している。

次に、図7(b)に示すように、支持層40に設けた開口42にシード層141を形成する。シード層141の構成及び形成方法としては、シード層131の構成及び形成方法と同様とすることができる。

次に、図8(a)に示すように、シード層141を給電層として電解銅めっきを行って、開口42内及び支持層40の上に電解銅めっき層142を形成する。

この工程によって形成された電解銅めっき層142のうち、開口42内に形成された部分は、導体ポスト41となる。

この工程によって形成された電解銅めっき層142のうち、開口42内に形成された部分は、導体ポスト41となる。

次に、図8(b)に示すように、電解銅めっき層142の所定の部位にレジスト151を形成する。

続いて、図9(a)に示すように、レジスト151が形成されていない部位の電解銅めっき層142及びその下のシード層141をエッチングを用いて除去する。

この工程によって支持層の上に残った電解銅めっき層が第3導体回路56及びパッド55となる。

さらに、図9(b)に示すように、第3導体回路56及びパッド55を覆うように保護膜50を形成する。

続いて、図9(a)に示すように、レジスト151が形成されていない部位の電解銅めっき層142及びその下のシード層141をエッチングを用いて除去する。

この工程によって支持層の上に残った電解銅めっき層が第3導体回路56及びパッド55となる。

さらに、図9(b)に示すように、第3導体回路56及びパッド55を覆うように保護膜50を形成する。

続いて、図10(a)に示すように、支持基板10を除去(剥離)する。支持基板を除去する方法は特に限定されるものではないが、研削とエッチングにより行うことができる。

まず、シリコンウェハからなる支持基板10の第1面側(支持基板の表面が露出している面、図9(b)の下側)を研削装置を用いて研削し、支持基板の厚さを薄くする。研削量は特に限定されるものではないが、支持基板の厚さが100μm程度になるまで研削することが望ましい。

研削装置としては、シリコンウェハを研削するための研削装置を好適に用いることができる。

研削装置としては、シリコンウェハを研削するための研削装置を好適に用いることができる。

続いて、研削によって薄くした支持基板10(シリコンウェハ)を水酸化カリウム等のエッチング液を用いてエッチングして全て除去する。エッチングに用いるエッチング液としては、シリコンウェハのエッチングに用いられるものであれば特に限定されるものではないが、例えば水酸化カリウム水溶液等を用いることができる。エッチングに用いる装置は、特に限定されるものではないが、シリコンウェハのウエットエッチングに用いられる装置を好適に用いることができる。

また、図4(a)において支持基板10(シリコンウェハ)上に無機絶縁層20を形成する前に、支持基板10の表面に剥離層を形成してもよい。この剥離層の材料としては、Cu、Ni等の金属であってもよく、或いは樹脂であってもよい。そうした場合、支持基板10を除去する際には、剥離層を介して電子部品実装用基板と支持基板とを容易に分離することが可能となる。その手法としては特に限定されないが、剥離層が金属の場合はエッチングが用いられる。剥離層が樹脂の場合は例えば、アルカリ溶解等が挙げられる。こうした場合、支持基板10(シリコンウェハ)を再度使用することができる。

また、図4(a)において支持基板10(シリコンウェハ)上に無機絶縁層20を形成する前に、支持基板10の表面に剥離層を形成してもよい。この剥離層の材料としては、Cu、Ni等の金属であってもよく、或いは樹脂であってもよい。そうした場合、支持基板10を除去する際には、剥離層を介して電子部品実装用基板と支持基板とを容易に分離することが可能となる。その手法としては特に限定されないが、剥離層が金属の場合はエッチングが用いられる。剥離層が樹脂の場合は例えば、アルカリ溶解等が挙げられる。こうした場合、支持基板10(シリコンウェハ)を再度使用することができる。

続いて、図10(b)に示すように、保護膜50に開口53を形成してパッド55を露出させる。

さらに、図10(b)に示すように、保護膜60(Si3N4層60)に開口64を形成する。

これらの開口の形成方法としては、特に限定されず、レーザーやフォトリソグラフィが挙げられる。

上述した工程によって、本実施形態の電子部品実装用基板1を製造することができる。

電子部品実装用基板1の第1面側(図10(b)の下側)には、パッド22の表面が露出し、パッド22には電子部品を実装することができる。

一方、電子部品実装用基板1の第2面側(図10(b)の上側)には、パッド55の表面が露出し、パッド55を介してプリント配線基板に電子部品実装用基板1を実装することができる。

さらに、図10(b)に示すように、保護膜60(Si3N4層60)に開口64を形成する。

これらの開口の形成方法としては、特に限定されず、レーザーやフォトリソグラフィが挙げられる。

上述した工程によって、本実施形態の電子部品実装用基板1を製造することができる。

電子部品実装用基板1の第1面側(図10(b)の下側)には、パッド22の表面が露出し、パッド22には電子部品を実装することができる。

一方、電子部品実装用基板1の第2面側(図10(b)の上側)には、パッド55の表面が露出し、パッド55を介してプリント配線基板に電子部品実装用基板1を実装することができる。

続いて、本実施形態の電子部品実装用基板に電子部品を実装し、さらに電子部品実装用基板をプリント配線基板に実装する工程について説明する。

図11(a)及び図11(b)は、第一実施形態の電子部品実装用基板に電子部品を実装し、さらに電子部品実装用基板をプリント配線基板に実装する工程を模式的に示す断面図である。

なお、図11(a)及び図11(b)では、図10(b)と上下の方向を逆にして示しており、図2及び図3と同様に各層の第1面を上に、各層の第2面を下に示している。

図11(a)には、電子部品実装用基板1の両面にバリアメタル層及びバンプを形成した様子を模式的に示している。

図11(a)及び図11(b)は、第一実施形態の電子部品実装用基板に電子部品を実装し、さらに電子部品実装用基板をプリント配線基板に実装する工程を模式的に示す断面図である。

なお、図11(a)及び図11(b)では、図10(b)と上下の方向を逆にして示しており、図2及び図3と同様に各層の第1面を上に、各層の第2面を下に示している。

図11(a)には、電子部品実装用基板1の両面にバリアメタル層及びバンプを形成した様子を模式的に示している。

まず、保護膜60に設けた開口64にバリアメタル層65を形成する。このバリアメタル層65は、例えば窒化タンタル及びタンタルを順次スパッタすることで形成される。なお、このバリアメタル層65の構成材料及び形成方法は特に限定されるものではない。また

、図示は省略するが、保護膜60の開口64から露出するバリアメタル層65の表面にNi/Auめっきを施す。これは、後述するはんだ接合を行ったときに、はんだとパッドとの密着性を確保するためである。

続いて、バリアメタル層65の上にはんだよりなるバンプ61を形成する。

、図示は省略するが、保護膜60の開口64から露出するバリアメタル層65の表面にNi/Auめっきを施す。これは、後述するはんだ接合を行ったときに、はんだとパッドとの密着性を確保するためである。

続いて、バリアメタル層65の上にはんだよりなるバンプ61を形成する。

電子部品実装用基板1の第2面側の保護膜50に設けられた開口53にも、上述した第1面側と同様にしてバリアメタル層54を形成し、バリアメタル層54にはんだよりなるバンプ51を形成する。

続いて、電子部品実装用基板1の第1面側に形成したバンプ61を介して電子部品200を電子部品実装用基板1上にフリップチップ実装する。次に、電子部品200と電子部品実装用基板1との間にアンダーフィル樹脂62を充填し、それを硬化させる。次いで、実装した電子部品200の周囲を封止樹脂63で封止する。

さらに、電子部品実装用基板1の第2面側に形成したバンプ51を介して電子部品実装用基板1をプリント配線基板100上に実装する。次に、プリント配線基板100と電子部品実装用基板1との間にアンダーフィル樹脂52を充填し、それを硬化させる。

これらの工程をまとめて図11(b)に示している。

なお、アンダーフィル樹脂及び封止樹脂としては、公知の樹脂を用いればよい。

このような工程によって、その第1面側に電子部品が実装され、その第2面側でプリント配線基板に実装された電子部品実装用基板とすることができる。

さらに、電子部品実装用基板1の第2面側に形成したバンプ51を介して電子部品実装用基板1をプリント配線基板100上に実装する。次に、プリント配線基板100と電子部品実装用基板1との間にアンダーフィル樹脂52を充填し、それを硬化させる。

これらの工程をまとめて図11(b)に示している。

なお、アンダーフィル樹脂及び封止樹脂としては、公知の樹脂を用いればよい。

このような工程によって、その第1面側に電子部品が実装され、その第2面側でプリント配線基板に実装された電子部品実装用基板とすることができる。

なお、支持基板としてシリコンウェハを用いて、シリコンウェハ上に電子部品実装用基板を形成した場合、電子部品実装用基板の寸法に対して充分大きいシリコンウェハを用いることによって、1枚のシリコンウェハ上に複数の電子部品実装用基板を形成することができる。

1枚のシリコンウェハ上に複数の電子部品実装用基板を形成した場合は、電子部品を実装する工程の前又は電子部品を実装する工程の後といった適切な時期に、ダイシング等の方法によってシリコンウェハを切断することによって電子部品実装用基板ごとに分割することができる。このようにすることによって、効率よく電子部品実装用基板を製造することができる。

1枚のシリコンウェハ上に複数の電子部品実装用基板を形成した場合は、電子部品を実装する工程の前又は電子部品を実装する工程の後といった適切な時期に、ダイシング等の方法によってシリコンウェハを切断することによって電子部品実装用基板ごとに分割することができる。このようにすることによって、効率よく電子部品実装用基板を製造することができる。

以下、本実施形態の電子部品実装用基板及び電子部品実装用基板の製造方法の作用効果について列挙する。

(1)本実施形態の電子部品実装用基板においては、樹脂からなる支持層が設けられており、支持層内には導体ポストが設けられている。

そして、電子部品実装用基板の支持層の第2面側で、電子部品実装用基板をプリント配線基板に実装することができる。このため、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力が導体ポストにより緩和される。このため、例えば、電子部品実装用基板をプリント配線基板に実装する際に用いられるバンプに応力が集中することがほとんどなくなり、バンプにクラックが入ることを抑制することが可能となる。その結果、電子部品実装用基板の実装信頼性を確保することが可能となる。

一方、支持層の第1面側には有機絶縁層が設けられ、さらに有機絶縁層上には無機絶縁層が設けられている。そして、無機絶縁層の内部には電子部品を実装するためのパッドが設けられている。このパッドは無機絶縁層の内部に形成された第2導体回路を用いた微細配線により配線されたものであり、ファインピッチ化されている。

そのため、無機絶縁層の内部に形成されたパッドに電子部品、特にファインピッチの端子(電極)を有する半導体素子を実装させることができる。

(1)本実施形態の電子部品実装用基板においては、樹脂からなる支持層が設けられており、支持層内には導体ポストが設けられている。

そして、電子部品実装用基板の支持層の第2面側で、電子部品実装用基板をプリント配線基板に実装することができる。このため、電子部品実装用基板とプリント配線基板との間の熱膨張係数の差に起因して発生する応力が導体ポストにより緩和される。このため、例えば、電子部品実装用基板をプリント配線基板に実装する際に用いられるバンプに応力が集中することがほとんどなくなり、バンプにクラックが入ることを抑制することが可能となる。その結果、電子部品実装用基板の実装信頼性を確保することが可能となる。

一方、支持層の第1面側には有機絶縁層が設けられ、さらに有機絶縁層上には無機絶縁層が設けられている。そして、無機絶縁層の内部には電子部品を実装するためのパッドが設けられている。このパッドは無機絶縁層の内部に形成された第2導体回路を用いた微細配線により配線されたものであり、ファインピッチ化されている。

そのため、無機絶縁層の内部に形成されたパッドに電子部品、特にファインピッチの端子(電極)を有する半導体素子を実装させることができる。

(2)無機絶縁層内部には微細配線を形成することができるため、無機絶縁層内部に第2導体回路を用いた微細配線を形成することによって、層数を増やして徐々に配線をファン

アウトさせる必要がなく、少ない層数で電子部品の端子のファイン化に対応することが可能となる。

アウトさせる必要がなく、少ない層数で電子部品の端子のファイン化に対応することが可能となる。

(3)本実施形態の電子部品実装用基板の第1面側には、無機絶縁層が設けられており、ファインピッチ半導体素子等の電子部品を無機絶縁層に近接させて電子部品実装用基板に実装させることができる。上記電子部品は通常シリコン等の無機材料からなるため、電子部品と電子部品実装用基板の間の熱膨張係数の差を小さくして実装信頼性を高くすることができる。

(4)有機絶縁層の第2面上(支持層側)に第1導体回路が形成されており、第1導体回路は一方で第2導体回路と電気的に接続されており、他方で導体ポストと電気的に接続されている。

そして、第1導体回路を用いて、第2導体回路による微細配線が必要でない部分の配線を行うことができる。微細配線でない配線は微細配線に比べて配線抵抗が小さいため、第1導体回路を設けることによって電子部品実装用基板全体の配線抵抗を小さくすることができる。

そして、第1導体回路を用いて、第2導体回路による微細配線が必要でない部分の配線を行うことができる。微細配線でない配線は微細配線に比べて配線抵抗が小さいため、第1導体回路を設けることによって電子部品実装用基板全体の配線抵抗を小さくすることができる。

(5)第1導体回路を構成する配線の厚さ及び断面積が、第2導体回路を構成する配線の厚さ及び断面積よりも大きくなっている。そのため、第1導体回路を構成する配線の配線抵抗が小さくなり、第1導体回路を設けることによって電子部品実装用基板全体の配線抵抗を小さくすることができる。

(6)最も無機絶縁層に近い側に位置する有機絶縁層の内部にはビア導体のみが形成されており、導体回路が形成されていない。最も無機絶縁層に近い側に位置する有機絶縁層(最外層の有機絶縁層)は、電子部品の発熱に起因する熱履歴の影響を最も受けやすいため、クラックが発生しやすい部位であるが、本実施形態の構成では最外層の有機絶縁層内に導体回路が形成されていないことから、有機絶縁層にクラックが生じることを防止することができる。

(7)本実施形態の電子部品実装用基板の製造方法では、一方の面にファインピッチの端子(電極)を有する半導体素子を実装することができ、かつ、他方の面でプリント配線基板に実装した場合の実装信頼性が高い電子部品実装用基板を製造することができる。

(8)本実施形態の電子部品実装用基板の製造方法では、第2導体回路をダマシン法によって形成し、第1導体回路をセミアディティブ法によって形成する。

これにより、第2導体回路を構成する配線を微細配線にして精度よく形成し、さらに、平坦性の高い配線を形成することができる。また、配線抵抗の低い第1導体回路を簡便に形成して電子部品実装用基板を製造することができる。

これにより、第2導体回路を構成する配線を微細配線にして精度よく形成し、さらに、平坦性の高い配線を形成することができる。また、配線抵抗の低い第1導体回路を簡便に形成して電子部品実装用基板を製造することができる。

(9)本実施形態の電子部品実装用基板の製造方法では、支持層の内部に第1導体回路の一部を露出させる開口を形成した後、上記開口内に導体ポストを形成する。

このような工程によると、アスペクト比の大きい導体ポストを良好に形成することができる。

このような工程によると、アスペクト比の大きい導体ポストを良好に形成することができる。

(第二実施形態)

本実施形態の電子部品実装用基板は、支持層の第2面上に位置する導体の形態が第一実施形態の電子部品実装用基板と異なる。

本実施形態の電子部品実装用基板は、支持層の第2面上に位置する導体の形態が第一実施形態の電子部品実装用基板と異なる。

図12は、本発明の電子部品実装用基板の別の一例の一部分を模式的に示す断面図である。

本実施形態の電子部品実装用基板2では、支持層40の第2面上に第3導体回路及びパッドが設けられていない。支持層40の第2面上には保護膜50が設けられている。

保護膜50には、開口53が設けられており、この開口53にはバリアメタル層54が形成され、さらにバンプ51が形成されている。

このバンプ51が形成された開口53の直下(図12の上側)には導体ポスト41の一方の端部が位置している。すなわち、本実施形態において支持層の第2面上に位置する導体はバンプ51(バリアメタル層54を含む)であり、このバンプ51と第1導体回路31とが導体ポスト41を介して電気的に接続されていることとなる。

このような構成であるとバンプ51を介して電子部品実装用基板2をプリント配線基板に実装することができる。

なお、図12において支持層40及び支持層40より上に位置する各層の構成は第一実施形態の電子部品実装用基板と同様であるであるため詳細な説明を省略する。

本実施形態の電子部品実装用基板2では、支持層40の第2面上に第3導体回路及びパッドが設けられていない。支持層40の第2面上には保護膜50が設けられている。

保護膜50には、開口53が設けられており、この開口53にはバリアメタル層54が形成され、さらにバンプ51が形成されている。

このバンプ51が形成された開口53の直下(図12の上側)には導体ポスト41の一方の端部が位置している。すなわち、本実施形態において支持層の第2面上に位置する導体はバンプ51(バリアメタル層54を含む)であり、このバンプ51と第1導体回路31とが導体ポスト41を介して電気的に接続されていることとなる。

このような構成であるとバンプ51を介して電子部品実装用基板2をプリント配線基板に実装することができる。

なお、図12において支持層40及び支持層40より上に位置する各層の構成は第一実施形態の電子部品実装用基板と同様であるであるため詳細な説明を省略する。

本実施形態の電子部品実装用基板の製造方法においては、第一実施形態において支持層40上に電解めっき膜を形成する工程までを行った基板に対し、CMPを行う。

図13(a)及び図13(b)並びに図14は、第二実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

まず、第一実施形態において第1導体回路31を形成する工程までを行った基板に対し、支持層40となる有機絶縁層を形成し、所定の位置に開口42を形成する。

以上の工程をまとめて図13(a)に示している。

次に、図13(b)に示すように、支持層40に設けた開口42にシード層141を形成し、さらにシード層141を給電層として電解銅めっきを行って、開口42内及び支持層40の上に電解銅めっき層142を形成する。

図13(a)及び図13(b)並びに図14は、第二実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

まず、第一実施形態において第1導体回路31を形成する工程までを行った基板に対し、支持層40となる有機絶縁層を形成し、所定の位置に開口42を形成する。

以上の工程をまとめて図13(a)に示している。

次に、図13(b)に示すように、支持層40に設けた開口42にシード層141を形成し、さらにシード層141を給電層として電解銅めっきを行って、開口42内及び支持層40の上に電解銅めっき層142を形成する。

次に、図14に示すように、CMPを行って、電解銅めっき層142及び支持層40表面のシード層141を除去する。電解銅めっき層142及びシード層141を除去する方法は、CMPに限定されるものではなく、エッチング等の他の方法を用いてもよい。

本実施形態の電子部品実装用基板には、図12に示すように、支持層40の第2面側にさらに保護膜50を設けて、保護膜50の所定の位置に開口53を形成し、開口53へのバリアメタル層54、バンプ51の形成を順次行うことができる。

また、支持基板10を除去した後に保護膜60の所定の位置に開口64を形成し、開口64へのバリアメタル層65、バンプ61の形成を順次行うことができる。上記工程によって、図12に示すような本実施形態の電子部品実装用基板を製造することができる。

本実施形態の電子部品実装用基板においては、第一実施形態において説明した効果(1)〜(9)を発揮することができ、さらに以下の効果を発揮することができる。

(10)本実施形態によれば、第一実施形態におけるランド55が設けられていないため、その分第3導体回路を引き回す領域が増す。その結果、第3導体回路の引き回しが容易となる。

また、支持基板10を除去した後に保護膜60の所定の位置に開口64を形成し、開口64へのバリアメタル層65、バンプ61の形成を順次行うことができる。上記工程によって、図12に示すような本実施形態の電子部品実装用基板を製造することができる。

本実施形態の電子部品実装用基板においては、第一実施形態において説明した効果(1)〜(9)を発揮することができ、さらに以下の効果を発揮することができる。

(10)本実施形態によれば、第一実施形態におけるランド55が設けられていないため、その分第3導体回路を引き回す領域が増す。その結果、第3導体回路の引き回しが容易となる。

(第三実施形態)

本実施形態の電子部品実装用基板には、複数の電子部品を実装することができ、複数の電子部品のうちの特定の電子部品の間が、第1導体回路及び第2導体回路を介して接続されるように構成されている。

図15は、本発明の電子部品実装用基板の別の一例の一部分を模式的に示す断面図である。

図15に示す電子部品実装用基板3には、複数の電子部品200、300を実装することができる。

本実施形態の電子部品実装用基板には、複数の電子部品を実装することができ、複数の電子部品のうちの特定の電子部品の間が、第1導体回路及び第2導体回路を介して接続されるように構成されている。

図15は、本発明の電子部品実装用基板の別の一例の一部分を模式的に示す断面図である。

図15に示す電子部品実装用基板3には、複数の電子部品200、300を実装することができる。

本実施形態で用いられる電子部品200及び電子部品300の機能、実装形態は、特に限

定されない。本実施形態では、電子部品200が電源レギュレータモジュールであり、電子部品300がCPUである。

定されない。本実施形態では、電子部品200が電源レギュレータモジュールであり、電子部品300がCPUである。

本実施形態の電子部品実装用基板においては、第一実施形態及び第二実施形態において説明した効果(1)〜(10)を発揮することができる。

(第四実施形態)

本実施形態の電子部品実装用基板では、有機絶縁層の第1面上にキャパシタが形成されている。

本実施形態の電子部品実装用基板では、有機絶縁層の第1面上にキャパシタが形成されている。

図16は、本発明の電子部品実装用基板の別の一例の一部分を模式的に示す断面図である。

本実施形態の電子部品実装用基板4では、有機絶縁層が2層(有機絶縁層30及び有機絶縁層30の第1面上に設けられた有機絶縁層80)設けられており、有機絶縁層80の第1面上にキャパシタ70が形成されている。

本実施形態の電子部品実装用基板4では、有機絶縁層が2層(有機絶縁層30及び有機絶縁層30の第1面上に設けられた有機絶縁層80)設けられており、有機絶縁層80の第1面上にキャパシタ70が形成されている。

キャパシタ70は、下部電極71、誘電体層72、上部電極73からなる。

下部電極71は、有機絶縁層80を貫通してグランド用(電源用でもよい)のバンプに接続される第2導体81を介して、有機絶縁層80の第2面上に設けられたランド85に電気的に接続されている。

上部電極73は、有機絶縁層80を貫通して電源用(グランド用でもよい)のバンプに接続される第1導体83を介して、有機絶縁層80の第2面上に設けられたランド85に電気的に接続されている。

ランド85は、有機絶縁層30の内部に設けられたビア導体32を介して第1導体回路31と電気的に接続されている。

すなわち、下部電極71、上部電極73のいずれも第1導体回路31と電気的に接続されている。

下部電極71は、有機絶縁層80を貫通してグランド用(電源用でもよい)のバンプに接続される第2導体81を介して、有機絶縁層80の第2面上に設けられたランド85に電気的に接続されている。

上部電極73は、有機絶縁層80を貫通して電源用(グランド用でもよい)のバンプに接続される第1導体83を介して、有機絶縁層80の第2面上に設けられたランド85に電気的に接続されている。

ランド85は、有機絶縁層30の内部に設けられたビア導体32を介して第1導体回路31と電気的に接続されている。

すなわち、下部電極71、上部電極73のいずれも第1導体回路31と電気的に接続されている。

上部電極73は、誘電体層72の上面に形成されたベタパターンであって、第2導体81及び信号用導体87を上部電極73と非接触の状態で通過させるための開口部74を有する。開口部74には誘電体層72と同じ材料からなる誘電体が充填されている。

上部電極73は、キャパシタ70の第1面上に形成されている保護膜90に設けられた開口93の直下に位置している。

保護膜90の開口93にはバリアメタル層94が形成され、さらにバンプ91が形成されている。このバンプ91には電子部品を実装させることができる。

上部電極73は、キャパシタ70の第1面上に形成されている保護膜90に設けられた開口93の直下に位置している。

保護膜90の開口93にはバリアメタル層94が形成され、さらにバンプ91が形成されている。このバンプ91には電子部品を実装させることができる。

下部電極71は、誘電体層72の下面に形成されたベタパターンであって、第1導体83を下部電極71と非接触の状態で通過させるための開口部75を有する。開口部75には有機絶縁層80と同じ材料からなる樹脂が充填されている。

下部電極71は有機絶縁層80の第1面上に形成されている。

下部電極71は有機絶縁層80の第1面上に形成されている。

下部電極71及び上部電極73の材質としては、TiN、TaN、Cu、Ni、Co、Ru、Ir、Au、Mo、W、Al、Ta及びTiからなる群から選択される少なくとも1種が挙げられる。下部電極71及び上部電極73の形成方法としては、スパッタリング、真空蒸着等が挙げられる。

誘電体層72は、上部電極73と下部電極71の間に設けられた層である。この誘電体層72を形成する材料としては、Ta2O5、ZrO2、HfO2等の単一金属酸化物や、SrTiO3、BaTiO3、PbTiO3等が挙げられる。この誘電体層72の形成方法としては、例えばCVDが挙げられる。これらの中でも、格子欠陥が少なく、上部電極

73と下部電極71との間のリーク電流を抑制できるといった点から、Ta2O5、ZrO2、HfO2等の単一金属酸化物が好ましい。

73と下部電極71との間のリーク電流を抑制できるといった点から、Ta2O5、ZrO2、HfO2等の単一金属酸化物が好ましい。

本実施形態における上部電極73と下部電極71の間の距離は10μm以下であって、上部電極73と下部電極71が短絡しない距離に設定されていることが望ましい。電極間距離が充分小さいと、キャパシタの静電容量を大きくすることができる。

また、本実施形態の電子部品実装用基板には、信号用電流が流れるための信号用導体87が形成されている。図16において信号用導体87は電子部品実装用基板4の左右両端に形成されている。信号用導体87は有機絶縁層80、開口部75、誘電体層72及び開口部74を貫通してバンプ91とランド85を電気的に接続している。

信号用導体87は上部電極73及び下部電極71と電気的に接続されていない。

信号用導体87は上部電極73及び下部電極71と電気的に接続されていない。

有機絶縁層80の材質は第一実施形態における有機絶縁層30と同様である。また、保護膜90の材料としては、無機絶縁層20や保護膜60と同様の材料(SiO2及び/又はSi3N4)を用いることができる。

また、有機絶縁層80を貫通する第2導体81、第1導体83、信号用導体87、並びに、有機絶縁層80の第2面上に設けられたランド85は銅めっき及び銅めっきの下のシード層からなる。

また、有機絶縁層80を貫通する第2導体81、第1導体83、信号用導体87、並びに、有機絶縁層80の第2面上に設けられたランド85は銅めっき及び銅めっきの下のシード層からなる。

また、図16において、有機絶縁層30及び有機絶縁層30より下に位置する各層の構成は第一実施形態の電子部品実装用基板と同様であるため詳細な説明を省略する。

以下、本実施形態の電子部品実装用基板の製造方法について図面を用いて説明する。

図17(a)、図17(b)及び図17(c)、図18(a)、図18(b)及び図18(c)並びに図19は、第四実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

図17(a)、図17(b)及び図17(c)、図18(a)、図18(b)及び図18(c)並びに図19は、第四実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

まず、図17(a)に示すように、支持基板10の上にSiO2層90を成膜する。SiO2層90は、保護膜90となる層である。

本実施形態の支持基板10としては、第一実施形態の電子部品実装用基板の製造方法と同様にシリコンウェハを用い、支持基板10の上面に、SiO2層90をCVD(化学気相成長)法によって成膜する。

さらに、上部電極73となる金属膜(TiN)を例えばスパッタリングによってSiO2層90の表面に成膜し、パターンニングを行って開口部74を形成し、SiO2層90の表面の一部を露出させる。

パターンニングは、例えばRIE等のドライエッチングや、所定のエッチング液を用いたウェットエッチングを用いて行うことができる。

本実施形態の支持基板10としては、第一実施形態の電子部品実装用基板の製造方法と同様にシリコンウェハを用い、支持基板10の上面に、SiO2層90をCVD(化学気相成長)法によって成膜する。

さらに、上部電極73となる金属膜(TiN)を例えばスパッタリングによってSiO2層90の表面に成膜し、パターンニングを行って開口部74を形成し、SiO2層90の表面の一部を露出させる。

パターンニングは、例えばRIE等のドライエッチングや、所定のエッチング液を用いたウェットエッチングを用いて行うことができる。

次に、図17(b)に示すように、Ta2O5、ZrO2、HfO2等の単一金属酸化物からなる層をCVD等の手法により成膜して誘電体層72を形成する。

さらに、図17(c)に示すように下部電極71となる金属膜(TiN)をスパッタリングによって誘電体層72の上に成膜し、パターンニングを行って開口部75を形成して誘電体層72の表面の一部を露出させる。

パターンニングは、例えばRIE等のドライエッチングや、所定のエッチング液を用いたウェットエッチングを用いて行うことができる。。

さらに、図17(c)に示すように下部電極71となる金属膜(TiN)をスパッタリングによって誘電体層72の上に成膜し、パターンニングを行って開口部75を形成して誘電体層72の表面の一部を露出させる。

パターンニングは、例えばRIE等のドライエッチングや、所定のエッチング液を用いたウェットエッチングを用いて行うことができる。。

次に、図18(a)に示すように、下部電極71と誘電体層72の上に有機絶縁層80を形成する。

さらに、図18(b)に示すようにレーザー又はRIEを用いて開口181、開口183

及び開口187を形成する。開口181及び開口187はSiO2層90が露出するように形成した開口であり、開口183は上部電極73が露出するように形成した開口である。

さらに、図18(b)に示すようにレーザー又はRIEを用いて開口181、開口183

及び開口187を形成する。開口181及び開口187はSiO2層90が露出するように形成した開口であり、開口183は上部電極73が露出するように形成した開口である。

次に、図18(c)に示すようにシード層185をスパッタリングにより形成する。シード層185としては、第一実施形態におけるシード層131と同様の構成のものを使用することができる。

続いて、第一実施形態において第1導体回路31を形成した工程と同様にしてメッキレジストの形成、露光及び現像、シード層185を給電層とした電解銅めっき、並びにメッキレジストの除去の工程をそれぞれ施し、第2導体81、第1導体83、信号用導体87及びランド85を形成する。

第2導体81は下部電極71と、第1導体83は上部電極73とそれぞれ電気的に接続される。信号用導体87は下部電極71、上部電極73のいずれにも電気的に接続されない。

続いて、第一実施形態において第1導体回路31を形成した工程と同様にしてメッキレジストの形成、露光及び現像、シード層185を給電層とした電解銅めっき、並びにメッキレジストの除去の工程をそれぞれ施し、第2導体81、第1導体83、信号用導体87及びランド85を形成する。

第2導体81は下部電極71と、第1導体83は上部電極73とそれぞれ電気的に接続される。信号用導体87は下部電極71、上部電極73のいずれにも電気的に接続されない。

以下、図19に示すように有機絶縁層30より上に位置する各層を形成する。この工程は第一実施形態において説明した工程と同様であるため詳細な説明を省略する。

続いて、支持基板10の除去、保護膜50及びSiO2層90(保護膜90)への開口の形成を行う。さらに、第1面側及び第2面側の各開口へのバンプの形成までの工程を行う。上記工程を経て図16に示すような電子部品実装用基板4を製造することができる。

これらの工程は第一実施形態において説明した工程と同様であるため詳細な説明を省略する。

これらの工程は第一実施形態において説明した工程と同様であるため詳細な説明を省略する。

本実施形態の電子部品実装用基板においては、第一実施形態及び第二実施形態において説明した効果(1)〜(10)を発揮することができ、さらに以下の効果を発揮することができる。

(11)本実施形態の電子部品実装用基板にはキャパシタが設けられており、半導体素子を実装した際にキャパシタが半導体素子の直下に位置することとなる。そのため、半導体素子に対して最短距離で瞬時に電源供給を行うことが可能となり、デカップリング効果が得られる。その結果、半導体素子の誤作動を防止することができる。

(11)本実施形態の電子部品実装用基板にはキャパシタが設けられており、半導体素子を実装した際にキャパシタが半導体素子の直下に位置することとなる。そのため、半導体素子に対して最短距離で瞬時に電源供給を行うことが可能となり、デカップリング効果が得られる。その結果、半導体素子の誤作動を防止することができる。

(12)本実施形態の電子部品実装用基板では、キャパシタの誘電体層がCVDによって形成されており、誘電体層の厚さが薄いために高容量の薄膜キャパシタとすることができる。

(第五実施形態)

本実施形態の電子部品実装用基板では、有機絶縁層の第1面上にキャパシタが形成されており、キャパシタの第1面上には無機絶縁層及び第2導体回路が形成されている。

本実施形態の電子部品実装用基板では、有機絶縁層の第1面上にキャパシタが形成されており、キャパシタの第1面上には無機絶縁層及び第2導体回路が形成されている。

図20は、本発明の電子部品実装用基板の別の一例の一部分を模式的に示す断面図である。

本実施形態の電子部品実装用基板5では、有機絶縁層80の第1面上にキャパシタ70が形成されている。有機絶縁層80とキャパシタ70の位置関係は第四実施形態の電子部品実装用基板と同様である。

そして、キャパシタ70の第1面上には無機絶縁層20、第2導体回路21及びパッド22a、22b、22cが設けられている。そして、無機絶縁層20の第1面側に位置するSi3N4層60は、保護膜として機能する層であり、Si3N4層60にはパッド22の一部を露出する開口93が形成されている。パッド22a、22b、22c上には、バリアメタル層94を介してバンプ91が形成されている。

無機絶縁層20、第2導体回路21の構成は第一実施形態の電子部品実装用基板と同様である。また、パッド22a、22b、22cの構成は第一実施形態の電子部品実装用基板のパッド22と同様である。

本実施形態の電子部品実装用基板5では、有機絶縁層80の第1面上にキャパシタ70が形成されている。有機絶縁層80とキャパシタ70の位置関係は第四実施形態の電子部品実装用基板と同様である。

そして、キャパシタ70の第1面上には無機絶縁層20、第2導体回路21及びパッド22a、22b、22cが設けられている。そして、無機絶縁層20の第1面側に位置するSi3N4層60は、保護膜として機能する層であり、Si3N4層60にはパッド22の一部を露出する開口93が形成されている。パッド22a、22b、22c上には、バリアメタル層94を介してバンプ91が形成されている。

無機絶縁層20、第2導体回路21の構成は第一実施形態の電子部品実装用基板と同様である。また、パッド22a、22b、22cの構成は第一実施形態の電子部品実装用基板のパッド22と同様である。

本実施形態の電子部品実装用基板では、上部電極73上に形成されているパッド22aが電源用のパッドとして機能する。また、この上部電極73とは絶縁されて開口部74の上に位置するパッド22bがグランド用のパッドとして機能する。

また、上部電極73、下部電極71のいずれとも絶縁されている、図20の両端に位置するパッド22cは信号用のパッドとして機能する。

また、上部電極73、下部電極71のいずれとも絶縁されている、図20の両端に位置するパッド22cは信号用のパッドとして機能する。

また、図20におけるその他の部位の構成は第一実施形態の電子部品実装用基板と同様であるため、その詳細な説明を省略する。

以下、本実施形態の電子部品実装用基板の製造方法について図面を用いて説明する。

図21(a)及び図21(b)は、第五実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

図21(a)及び図21(b)は、第五実施形態の電子部品実装用基板の製造工程の一部を模式的に示す断面図である。

図21(a)は、第一実施形態の図4(d)と同様の図面である。

本実施形態の電子部品実装用基板の製造方法では、まず、第一実施形態の電子部品実装用基板の製造方法と同様にして支持基板10の上にSi3N4層60、無機絶縁層20、第2導体回路21、パッド22a、パッド22b、22cを形成する。

本実施形態の電子部品実装用基板の製造方法では、まず、第一実施形態の電子部品実装用基板の製造方法と同様にして支持基板10の上にSi3N4層60、無機絶縁層20、第2導体回路21、パッド22a、パッド22b、22cを形成する。

次に、無機絶縁層20、第2導体回路21、パッド22a、パッド22b、22cの上に上部電極73となる金属膜(TiN)を成膜する工程を行い、以下、第四実施形態の電子部品実装用基板の製造方法においてキャパシタを形成した工程と同様にしてキャパシタ70を形成する。さらに、有機絶縁層80より上に位置する各層を形成する。ここまでの工程を図21(b)にまとめて示している。

以後、第四実施形態の電子部品実装用基板の製造方法と同様にして図20に示すような電子部品実装用基板5を製造することができる。

本実施形態の電子部品実装用基板においては、第一、第二及び第四実施形態において説明した効果(1)〜(12)を発揮することができる。

(その他の実施形態)

上述した本発明の各実施形態の電子部品実装用基板においては、第1導体回路は有機絶縁層の表面のうち支持層の第1面に接する第2面上に形成されていたが、第1導体回路は有機絶縁層の第2面側の内部に形成されていても良い。

「有機絶縁層の第2面側の内部」とは、有機絶縁層の内部であって有機絶縁層の第2面側の近傍の領域のことを指し、具体的には有機絶縁層の厚さの半分で切断した断面よりも第2面側に位置する領域のことを指す。

上述した本発明の各実施形態の電子部品実装用基板においては、第1導体回路は有機絶縁層の表面のうち支持層の第1面に接する第2面上に形成されていたが、第1導体回路は有機絶縁層の第2面側の内部に形成されていても良い。

「有機絶縁層の第2面側の内部」とは、有機絶縁層の内部であって有機絶縁層の第2面側の近傍の領域のことを指し、具体的には有機絶縁層の厚さの半分で切断した断面よりも第2面側に位置する領域のことを指す。

本発明の電子部品実装用基板においては、無機絶縁層の内部又は無機絶縁層の第2面上(最も無機絶縁層に近い側に位置する有機絶縁層の内部)に、電源層及びグランド層のうちの少なくとも一方が形成されていてもよい。

例えば無機絶縁層の内部にグランド層を形成した場合には、その直下に位置する第1導体回路とを含めてマイクロストリップ構造が形成される。その結果、特性インピーダンスを整合でき、信号の伝搬を安定化させることが可能となる。

例えば無機絶縁層の内部にグランド層を形成した場合には、その直下に位置する第1導体回路とを含めてマイクロストリップ構造が形成される。その結果、特性インピーダンスを整合でき、信号の伝搬を安定化させることが可能となる。

本発明の電子部品実装用基板においては、有機絶縁層及び/又は無機絶縁層が複数設けら

れていて、第1導体回路及び/又は第2導体回路が多層配線となっていてもよい。

特に、有機絶縁層が複数設けられている場合には、各有機絶縁層の内部にはビア導体及び/又は導体回路が形成されるが、最も無機絶縁層に近い側に位置する有機絶縁層の内部にはビア導体のみが形成されており、導体回路が形成されていないことが望ましい。

れていて、第1導体回路及び/又は第2導体回路が多層配線となっていてもよい。

特に、有機絶縁層が複数設けられている場合には、各有機絶縁層の内部にはビア導体及び/又は導体回路が形成されるが、最も無機絶縁層に近い側に位置する有機絶縁層の内部にはビア導体のみが形成されており、導体回路が形成されていないことが望ましい。

導体ポスト、第1導体回路、及び、第2導体回路を構成する材料は、導電性のある材料であれば、特に限定されるものではない。

銅の他にはタングステン、ニッケル、金、銀等が挙げられる。

銅の他にはタングステン、ニッケル、金、銀等が挙げられる。

有機絶縁層の種類としては、熱硬化性樹脂として、例えば、エポキシ樹脂、フェノール樹脂、ポリイミド樹脂、ポリエステル樹脂、ビスマレイミド樹脂、ポリオレフィン系樹脂、ポリフェニレンエーテル樹脂、ポリフェニレン樹脂、フッ素樹脂等が挙げられる。

また、感光性樹脂として、例えば、アクリル樹脂等が挙げられる。

また、感光性樹脂として、例えば、アクリル樹脂等が挙げられる。

熱硬化性樹脂の一部に感光性基が付与された樹脂としては、上記熱硬化性樹脂の熱硬化基とメタクリル酸やアクリル酸とをアクリル化反応させたもの等が挙げられる。

また、熱可塑性樹脂としては、例えば、フェノキシ樹脂、ポリエーテルスルフォン(PES)、ポリスルフォン(PSF)、ポリフェニレンスルフォン(PPS)、ポリフェニレンサルファイド(PPES)、ポリフェニレンエーテル(PPE)、ポリエーテルイミド(PI)等が挙げられる。

また、熱可塑性樹脂としては、例えば、フェノキシ樹脂、ポリエーテルスルフォン(PES)、ポリスルフォン(PSF)、ポリフェニレンスルフォン(PPS)、ポリフェニレンサルファイド(PPES)、ポリフェニレンエーテル(PPE)、ポリエーテルイミド(PI)等が挙げられる。

また、有機絶縁層として用いることのできる樹脂複合体の具体的な組み合わせとしては、例えば、フェノール樹脂/ポリエーテルスルフォン、ポリイミド樹脂/ポリスルフォン、エポキシ樹脂/ポリエーテルスルフォン、エポキシ樹脂/フェノキシ樹脂、アクリル樹脂/フェノキシ樹脂、エポキシ基の一部をアクリル化したエポキシ樹脂/ポリエーテルスルフォン等が挙げられる。

本発明の電子部品実装用基板に実装される電子部品の種類、機能は特に限定されるものでない。また、そうした電子部品の個数及び実装形態も特に限定されない。

また、複数の電子部品が積層された状態で実装されてもよい。この場合、例えば、各々の電子部品に設けられた貫通電極同士がバンプを介して接続される。

また、複数の電子部品が積層された状態で実装されてもよい。この場合、例えば、各々の電子部品に設けられた貫通電極同士がバンプを介して接続される。

本発明の電子部品実装用基板の製造方法において、ダマシン法により第2導体回路を形成する際に用いる、無機絶縁層の上に形成するレジストの種類、露光方法及び現像方法は、半導体製造工程で用いられるレジスト、露光方法、及び、現像方法であれば特に限定されるものでない。

無機絶縁層及び有機絶縁層の上にシード層を形成する方法としては、スパッタリングの他に、いわゆるPVD(物理気相成長)法と呼ばれる方法を用いることができ、具体的には、真空蒸着、イオンプレーティング、電子ビーム蒸着等の方法を用いることができる。

また、有機絶縁層の上にシード層を形成する方法としては、セミアディティブ法により導体回路を形成するために知られている従来公知の方法も用いることができる。

また、有機絶縁層の上にシード層を形成する方法としては、セミアディティブ法により導体回路を形成するために知られている従来公知の方法も用いることができる。

有機絶縁層を形成する方法としては、特に限定されるものではなく、スピンコーター、カーテンコーター等によって未硬化の樹脂を塗布する方法や、樹脂フィルムを熱圧着することにより樹脂層を形成する方法を用いることができる。

また、樹脂を硬化させる方法は、熱硬化に限定されるものではない。

また、樹脂を硬化させる方法は、熱硬化に限定されるものではない。

また、有機絶縁層に開口を形成する方法としては、露光現像処理やレーザー加工によって開口する方法を用いることができる。

レーザー加工の方法としては、エキシマーレーザー、UV−YAGレーザー、炭酸ガスレーザー等を用いる方法が挙げられる。

レーザー加工の方法としては、エキシマーレーザー、UV−YAGレーザー、炭酸ガスレーザー等を用いる方法が挙げられる。

なお、上記実施形態の説明においては支持基板としてSiを用いたが、これに代えて例えばガラス、セラミックス又は金属よりなる支持基板を用いてもよい。

第四実施形態及び第五実施形態において、上部電極73及び下部電極71を形成する方法としては、スパッタリングの他にMOCVD法を含む化学気相蒸着法、原子層蒸着法(ALD)及びPVD(物理気相成長)法(真空蒸着、イオンプレーティング、電子ビーム蒸着等)が挙げられる。

1〜5 電子部品実装用基板

10 支持基板

20 無機絶縁層

21 第2導体回路

22、22a、22b、22c パッド

30、80 有機絶縁層

31 第1導体回路

32 ビア導体

40 支持層

41 導体ポスト

42 開口

51 バンプ(支持層の第2面上に位置する導体)

55 パッド(支持層の第2面上に位置する導体)

56 第3導体回路(支持層の第2面上に位置する導体)

57 導体(支持層の第2面上に位置する導体)

70 キャパシタ

71 下部電極

72 誘電体層

73 上部電極

74、75 開口部

100 プリント配線基板

200、300 電子部品

10 支持基板

20 無機絶縁層

21 第2導体回路

22、22a、22b、22c パッド

30、80 有機絶縁層

31 第1導体回路

32 ビア導体

40 支持層

41 導体ポスト

42 開口

51 バンプ(支持層の第2面上に位置する導体)

55 パッド(支持層の第2面上に位置する導体)

56 第3導体回路(支持層の第2面上に位置する導体)

57 導体(支持層の第2面上に位置する導体)

70 キャパシタ

71 下部電極

72 誘電体層

73 上部電極

74、75 開口部

100 プリント配線基板

200、300 電子部品

Claims (14)

- プリント配線基板と電子部品との間に介在される電子部品実装用基板であって、

樹脂からなる支持層と、

前記支持層の第1面上に形成されている少なくとも1層の有機絶縁層と、

前記有機絶縁層の表面のうち前記支持層の第1面に接する第2面上、又は、前記有機絶縁層の第2面側の内部に形成されている第1導体回路と、

前記有機絶縁層において前記第2面とは反対側に位置する第1面上に形成されている無機絶縁層と、

前記無機絶縁層の内部に形成されている第2導体回路と、

前記無機絶縁層の内部に形成されていて、前記電子部品を実装するためのパッドと、

前記有機絶縁層の内部に形成されていて、前記第2導体回路と前記第1導体回路とを電気的に接続するビア導体と、

前記支持層において前記第1面とは反対側に位置する第2面側に形成されている導体と、前記支持層内に設けられており、前記第1導体回路と前記導体とを電気的に接続する導体ポストと、からなることを特徴とする電子部品実装用基板。 - 前記導体ポストのアスペクト比は、4.0〜6.5である請求項1に記載の電子部品実装用基板。

- 前記第1導体回路は、前記第2導体回路よりも厚さが厚い請求項1又は2に記載の電子部品実装用基板。

- 前記第1導体回路は、前記第2導体回路よりも断面積が大きい請求項1〜3のいずれかに記載の電子部品実装用基板。

- 前記有機絶縁層のうち、最も無機絶縁層に近い側に位置する有機絶縁層の内部にはビア導体のみが形成されており、導体回路が形成されていない請求項1〜4のいずれかに記載の電子部品実装用基板。

- 前記ビア導体は、前記有機絶縁層の第2面から第1面に向かって断面積が小さくなるようにテーパした側面を有する請求項1〜5のいずれかに記載の電子部品実装用基板。

- 前記支持層は、その30℃におけるヤング率が10〜1000MPaである材料からなる請求項1〜6のいずれかに記載の電子部品実装用基板。

- 支持基板上に無機絶縁層を形成すること、

前記無機絶縁層の内部に第2導体回路及びパッドを形成すること、

前記無機絶縁層上に少なくとも1層の有機絶縁層を形成すること、

前記有機絶縁層の内部又は前記有機絶縁層の上に第1導体回路を形成するとともに、前記第2導体回路と前記第1導体回路とを電気的に接続するビア導体を形成すること、

前記有機絶縁層の上に支持層を形成すること、

前記支持層上に導体を形成するとともに、前記支持層内に前記導体と前記第1導体回路とを電気的に接続する導体ポストを形成すること、

前記支持基板を剥離すること、

とからなることを特徴とする電子部品実装用基板の製造方法。 - 前記第1導体回路をセミアディティブ法により形成する請求項8に記載の電子部品実装用基板の製造方法。

- 前記支持層の内部に前記第1導体回路の一部を露出させる開口を形成した後、前記開口内に導体ポストを形成する請求項8又は9に記載の電子部品実装用基板の製造方法。

- 前記第2導体回路をダマシン法により形成する請求項8〜10のいずれかに記載の電子部品実装用基板の製造方法。

- プリント配線基板と電子部品との間に介在される電子部品実装用基板であって、

樹脂からなる支持層と、

前記支持層の第1面上に形成されている少なくとも1層の有機絶縁層と、

前記有機絶縁層の表面のうち前記支持層の第1面に接する第2面上、又は、前記有機絶縁層の第2面側の内部に形成されている第1導体回路と、

前記有機絶縁層において前記第2面とは反対側に位置する第1面上に形成されているキャパシタと、

前記支持層において前記第1面とは反対側に位置する第2面側に形成されている導体と、前記支持層内に設けられており、前記第1導体回路と前記導体とを電気的に接続する導体ポストと、を備え、

前記キャパシタは、開口部を有する下部電極と、前記下部電極上に形成された誘電体層と、前記誘電体層上に形成され開口部を有する上部電極とからなり、

前記下部電極及び前記上部電極の一方が半導体素子の電源ラインに接続されるとともに、他方がグランドラインに接続されることを特徴とする電子部品実装用基板。 - 前記下部電極の開口部を通過して前記上部電極に接続される第1導体と、

前記上部電極の開口部を通過して前記下部電極に接続される第2導体と、

を備える請求項12に記載の電子部品実装用基板。 - 前記誘電体層は、単一金属酸化物よりなる請求項12又は13に記載の電子部品実装用基板。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14113208P | 2008-12-29 | 2008-12-29 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010157690A true JP2010157690A (ja) | 2010-07-15 |

Family

ID=42539455

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009261724A Pending JP2010157690A (ja) | 2008-12-29 | 2009-11-17 | 電子部品実装用基板及び電子部品実装用基板の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8373069B2 (ja) |

| JP (1) | JP2010157690A (ja) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014154800A (ja) * | 2013-02-13 | 2014-08-25 | Shinko Electric Ind Co Ltd | 配線基板及びその製造方法 |

| JP2015026722A (ja) * | 2013-07-26 | 2015-02-05 | 新光電気工業株式会社 | バンプ構造、配線基板及び半導体装置並びにバンプ構造の製造方法 |

| JP2017084955A (ja) * | 2015-10-28 | 2017-05-18 | 大日本印刷株式会社 | インターポーザ及びインターポーザの製造方法 |

| WO2020105633A1 (ja) * | 2018-11-20 | 2020-05-28 | 凸版印刷株式会社 | 半導体パッケージ基板およびその製造方法 |

| JP2020129680A (ja) * | 2015-10-28 | 2020-08-27 | 大日本印刷株式会社 | インターポーザ及びインターポーザの製造方法 |

| JP2021114534A (ja) * | 2020-01-17 | 2021-08-05 | 凸版印刷株式会社 | 配線基板および配線基板の製造方法 |

| US11088081B2 (en) | 2018-10-02 | 2021-08-10 | Samsung Electronics Co., Ltd. | Semiconductor package having a connection structure with tapering connection via layers |

| JP2021168403A (ja) * | 2020-04-23 | 2021-10-21 | 大日本印刷株式会社 | インターポーザ及びインターポーザの製造方法 |

| US11177205B2 (en) | 2018-12-18 | 2021-11-16 | Samsung Electronics Co., Ltd. | Semiconductor package having multi-level and multi-directional shape narrowing vias |

| KR20230124459A (ko) * | 2022-02-17 | 2023-08-25 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 집적 회로 패키지 및 방법 |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5574639B2 (ja) * | 2009-08-21 | 2014-08-20 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JP5077324B2 (ja) * | 2009-10-26 | 2012-11-21 | 株式会社デンソー | 配線基板 |

| US9142533B2 (en) | 2010-05-20 | 2015-09-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Substrate interconnections having different sizes |

| US9425136B2 (en) | 2012-04-17 | 2016-08-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Conical-shaped or tier-shaped pillar connections |

| US9299674B2 (en) | 2012-04-18 | 2016-03-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Bump-on-trace interconnect |

| US9111817B2 (en) * | 2012-09-18 | 2015-08-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Bump structure and method of forming same |

| US20140115886A1 (en) * | 2012-10-26 | 2014-05-01 | Volex Plc | Method and system for marking substrate and placing components for high accuracy |

| JP6162458B2 (ja) * | 2013-04-05 | 2017-07-12 | 新光電気工業株式会社 | 配線基板、半導体装置及び配線基板の製造方法 |

| US9466554B2 (en) | 2014-02-13 | 2016-10-11 | Qualcomm Incorporated | Integrated device comprising via with side barrier layer traversing encapsulation layer |

| TWI566354B (zh) * | 2014-08-13 | 2017-01-11 | 矽品精密工業股份有限公司 | 中介板及其製法 |

| US9842825B2 (en) * | 2014-09-05 | 2017-12-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Substrateless integrated circuit packages and methods of forming same |

| JP6078765B1 (ja) * | 2015-03-11 | 2017-02-15 | 株式会社野田スクリーン | 薄膜キャパシタの製造方法、集積回路搭載基板、及び当該基板を備えた半導体装置 |

| US10643936B2 (en) * | 2017-05-31 | 2020-05-05 | Dyi-chung Hu | Package substrate and package structure |

| FR3076659B1 (fr) * | 2018-01-05 | 2020-07-17 | Stmicroelectronics (Grenoble 2) Sas | Entretoise isolante de reprise de contacts |

| CN110556356A (zh) * | 2018-06-01 | 2019-12-10 | 夏普株式会社 | 功率模块 |

| KR20220046134A (ko) | 2020-10-07 | 2022-04-14 | 삼성전자주식회사 | 반도체 패키지 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001185642A (ja) * | 1999-12-22 | 2001-07-06 | Sumitomo Metal Mining Co Ltd | 半導体実装用パッケージ基板 |

| JP2003031722A (ja) * | 2001-07-11 | 2003-01-31 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP2004152781A (ja) * | 2002-10-28 | 2004-05-27 | Kyocera Corp | 配線基板およびその製造方法 |

| JP2006066597A (ja) * | 2004-08-26 | 2006-03-09 | Ibiden Co Ltd | プリント配線板 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4044769B2 (ja) | 2002-02-22 | 2008-02-06 | 富士通株式会社 | 半導体装置用基板及びその製造方法及び半導体パッケージ |

-

2009

- 2009-11-17 JP JP2009261724A patent/JP2010157690A/ja active Pending

- 2009-12-24 US US12/647,015 patent/US8373069B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001185642A (ja) * | 1999-12-22 | 2001-07-06 | Sumitomo Metal Mining Co Ltd | 半導体実装用パッケージ基板 |

| JP2003031722A (ja) * | 2001-07-11 | 2003-01-31 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |