JP2008293648A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2008293648A JP2008293648A JP2008201883A JP2008201883A JP2008293648A JP 2008293648 A JP2008293648 A JP 2008293648A JP 2008201883 A JP2008201883 A JP 2008201883A JP 2008201883 A JP2008201883 A JP 2008201883A JP 2008293648 A JP2008293648 A JP 2008293648A

- Authority

- JP

- Japan

- Prior art keywords

- data

- write

- read

- memory

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Read Only Memory (AREA)

Abstract

【課題】不揮発性半導体記憶装置のデータ転送処理効率を改善する。

【解決手段】それぞれが複数の不揮発性メモリセルを有するメモリブロック(MB0−MB3)それぞれに対応してデータの書込/読出を行なうためのローカルバス(HB0−HB3)を設け、また各メモリブロックに対応してデータの書込/読出を行なうための回路(SA0−SA3,HSW0−HSW3)を設ける。さらに、これらのメモリブロックに共通に双方向でデータを転送するデータ転送線(BTX0,BTX1)と、メモリブロック間でデータ転送を行なうための転送スイッチゲート(TX0−TX3)を設ける。これらのメモリブロックをバンク(BNKA,BNKB)に分割し、メモリブロック個々にデータの書込/読出をバンク単位で行ない、書込/読出の並行実行および書込/読出と内部転送を行なう。

【選択図】図6

【解決手段】それぞれが複数の不揮発性メモリセルを有するメモリブロック(MB0−MB3)それぞれに対応してデータの書込/読出を行なうためのローカルバス(HB0−HB3)を設け、また各メモリブロックに対応してデータの書込/読出を行なうための回路(SA0−SA3,HSW0−HSW3)を設ける。さらに、これらのメモリブロックに共通に双方向でデータを転送するデータ転送線(BTX0,BTX1)と、メモリブロック間でデータ転送を行なうための転送スイッチゲート(TX0−TX3)を設ける。これらのメモリブロックをバンク(BNKA,BNKB)に分割し、メモリブロック個々にデータの書込/読出をバンク単位で行ない、書込/読出の並行実行および書込/読出と内部転送を行なう。

【選択図】図6

Description

この発明は、半導体記憶装置に関し、特に、データを不揮発的に記憶する不揮発性半導体記憶装置に関する。より特定的には、この発明は、同一ビット線に行方向において隣接する2列のメモリセルが接続するバーチャルグランドアレイを有する不揮発性半導体記憶装置のデータアクセスのための構成に関する。

データを不揮発的に記憶する不揮発性半導体記憶装置において、コントロールゲート下の絶縁膜に電荷をトラップして情報を記憶する絶縁膜電荷トラップ型メモリが知られている。

図25は、従来の絶縁膜電荷トラップ型メモリセルの断面構造を概略的に示す図である。図25において、絶縁膜電荷トラップ型メモリセルは、半導体基板領域900表面に形成される埋込拡散層901aおよび901bと、これらの埋込拡散層901aおよび901bの間の基板領域上に形成される多層絶縁膜903と、多層絶縁膜903上に形成される導電層904を含む。

埋込拡散層901aおよび901bは、列方向に延在して形成され、ビット線として用いられる。導電層904は、行方向に延在して形成され、ワード線として用いられて行選択信号を伝達し、また、メモリセルのコントロールゲートとして用いられる。

多層絶縁膜903は、導電層904と平行に、ワード線方向に延在して配置される。この多層絶縁膜903は、酸化膜903a、窒化膜903bおよび酸化膜903cの多層構造を有し、酸化膜903aおよび930cの間の窒化膜903bの領域に電荷を蓄積する。

なお、以下の説明においては、データのプログラムは、絶縁膜903bに電荷(電子)を蓄積する動作を示す。この状態においては、Hレベルのデータが書込まれるものとする。Lレベルデータ格納時においては、電子は蓄積されない。この絶縁膜電荷とラップ型メモリセルにおいては、電荷蓄積領域として、2つの領域、すなわち右ビット領域BT1と左ビット領域BT2が存在する。

右ビット領域BT1に対しプログラムを行なう場合には、コントロールゲート(ゲート電極層)904に、9Vの電圧を印加し、拡散ビット線領域(不純物領域)901bに4.5ないし6Vの電圧を印加する。拡散ビット線領域(不純物領域)901aを、接地電圧レベルに設定する。この状態においては、ゲート電極層904に印加される電圧に従って、基板領域900表面にチャネルが形成され、図25において左向きの矢印で示すように、拡散ビット線領域901bから拡散ビット線領域901aに電流Iが流れる。

このチャネル領域を流れる電流Iが、ゲート電極層904に印加される電圧に従って垂直方向に加速され、電子(チャネルホットエレクトロン)が窒化膜903bに格納され、右ビット領域BT1に電子が蓄積される。窒化膜903bにおいては、電子の移動度は小さいため、この右ビット領域BT1は、ドレイン領域近傍の領域においてのみ、このドレイン領域に対して自己整合的に形成される(チャネルホットエレクトロンが、ドレイン高電界により生成されて、次いで加速されて窒化膜903bに蓄積されるため)。

一方、左ビット領域BT2に電子を蓄積する場合には、拡散ビット線領域901aに、4.5から6Vの電圧を印加し、拡散ビット線領域901bを接地電圧れに設定する。ゲート電極層904に対しては、9Vの電圧を印加する。この場合には、図25において右向きの矢印で示すように、拡散ビット線領域901aから拡散ビット線領域901bに電流Iが流れ、ドレイン高電界により生成されたチャネルホットエレクトロンがゲート電極層904に印加される電圧により加速されて窒化膜903bに格納される。これにより、左ビット領域BT2に電子が蓄積される。

すなわち、プログラム動作時においては、チャネルホットエレクトロン(CHE)が生成されて窒化膜903bにトラップされる。この電荷蓄積領域に電子が注入された状態をプログラム状態(書込状態)と称する。このプログラム状態においては、実行電荷蓄積領域に電子が注入されているため、この領域においてメモリセルのトランジスタのしきい値電圧が高くなる。

データ読出時においては、図25において矢印に示すように、プログラム動作時と逆方向に電流Iをメモリセルに流す。すなわち、右ビット領域BT1の記憶データを読出す場合には、拡散ビット線領域901aに、たとえば、1.5から2Vの電圧を印加し、拡散ビット線領域901bを接地電圧レベルに設定する。ゲート電極層904へは、たとえば4Vの読出電圧を印加する。この場合、左ビット領域BT2においては、空乏層の広がりによりパンチスルーが生じており、この左ビット領域BT2の近傍領域におけるしきい値電圧は、読出電流に対しては何ら影響は及ぼさない。すなわち、データ読出動作時には、拡散ビット線領域901aから拡散ビット線領域901bに電流が流れるときに、右ビット領域BT1に蓄積される電子量に応じてこのチャネル領域を流れる電流量が決定される。この電流量を検出することにより、右ビット領域BT1に格納されたデータを読出すことができる。

一方、左ビット領域BT2に格納されたデータを読出す場合には、拡散ビット線領域901bに1.5から2Vの電圧を与え、拡散ビット線領域901aを接地電圧レベルに設定する。ゲート電極層904に対しては、4V程度の電圧を印加する。右ビット領域BT1の近傍領域においては、基板表面領域にパンチスルーが生じており、空乏層が広がっているだけであり、拡散ビット線901bおよび901aの間には、左ビット領域BT2に蓄積される電子の量に応じた電流が流れる。この電流量を検出することにより、左ビット領域BT2に格納されたデータを読出す。

通常、メモリセルにおいてプログラム時に電流が流れる方向をフォワード方向と称し、データ読出時に電流が流れる方向をリバース方向と称する。したがって、図25において矢印で示すように、右ビット領域BT1と左ビット領域BT2とでは、フォワード方向およびリバース方向が反対方向となる。

記憶データを消去する方法としては、種々の消去方法が提案されている。1つは、リバース方向に電流を流してチャネルホットホールを生成し、このチャネルホットホールを窒化まくに注入して、蓄積電子とホットホールとを再結合させて、蓄積電子を中性化する方法である。第2の方法は、窒化膜903bとゲート電極層904との間に電圧を印加し、窒化膜903bに蓄積された電子を、ゲート電極層904を介して引き抜く方法である。ゲート電極層904は、後に説明するように、ワード線を構成しており、図示しない行選択回路により駆動されるため、この第2の方法においては、行選択回路により電子が結果的に引き抜かれる。

第3の方法は、窒化膜903bとドレイン領域(拡散ビット線)との間で(バンド間)トンネリング電流により電流を流して、電子を窒化膜903bから引き抜く方法である。消去動作については、いずれの消去方法が用いられてもよい。この消去動作時においても、右ビット領域BT1および左ビット領域BT2それぞれにおいて個々に消去が実行される。

図26は、メモリセルの電気的等価回路およびプログラム動作時の印加電圧を示す図である。図26においては、2行3列に配列されるメモリセルを代表的に示す。図26において、メモリセルMCは、フローティングゲート型トランジスタで構成されるように示す。この絶縁膜電荷トラップ型メモリセルにおいては、フローティングゲート型トランジスタは、フローティングゲートが、ポリシリコンではなく窒化膜(903b)で形成される。

メモリセル行に対応してワード線WLaおよびWLbが配置され、それぞれに対応の行のメモリセルのゲート電極層(コントロールゲート)が接続される。メモリセル列に対応してビット線BLa−BLcがそれぞれ配置される。ビット線BLa−BLcは、それぞれ、行方向において隣接するメモリセルMCに共有される。

今、ワード線WLbとビット線BLbおよびBLcの交差部に対応して配置されるメモリセルMC1の右ビット領域BT1に対するプログラム動作を考える。データの書込(プログラム)は、フォワード方向に電流を流すことにより行なわれる。したがって、この場合には、ビット線BLcに、4.5から6Vの電圧が印加され、ビット線BLbは、接地電圧レベルに保持される。ビット線BLaはフローティング状態に維持される。ワード線WLaおよびWLbが、それぞれ、0Vおよび9Vに設定される。この状態においては、メモリセルMC1において、ビット線BLcからビット線BLbに電流が流れ、チャネルホットエレクトロンeが発生し、右ビット領域BT1に格納される。

メモリセルMC1に行方向において隣接するメモリセルMC3においては、ビット線BLaがフローティング状態にあり、チャネル電流が流れないため、チャネルホットエレクトロンは生成されず、プログラムは行なわれない。

また、メモリセルMC1に列方向において隣接するメモリセルMC3においては、ワード線WLaが接地電圧レベルに維持されており、メモリセルトランジスタが非導通状態を維持し、チャネル電流が流れず、プログラムは行なわれない。

したがって、ビット線が行方向において隣接するメモリセルにより共有される構成においても、正確にプログラム対象のメモリセルに対してのみプログラムを行なうことができる。

図27は、データ読出時の印加電圧を示す図である。図27において、メモリセルMC1の右ビット領域BT1に記憶されるデータを読出す場合には、ビット線BLbに、1.5から2Vの電圧が印加され、ビット線BLcが接地電圧レベルに維持される。ワード線WLaおよびWLbが、それぞれ、0Vおよび4Vに設定される。この状態においては、ビット線BLbからビット線BLcにメモリセルMC1の右ビット領域BT1に蓄積される電子量に応じた電流Iが流れる。この電流Iの大きさを検出して、右ビット領域BT1に格納されたデータを読出す。読出動作時において、ビット線BLaがフローティング状態であり、メモリセルMC2においては、ビット線BLbに読出電圧1.5から2Vが印加されても、メモリセルMC2には電流は流れず、正確に、メモリセルMC1の右ビット領域BT1に記憶されたデータに応じた大きさの電流Iを流すことができる。

メモリセルMC1の左ビット領域BT2のデータを読出す場合には、ビット線BLcに1.5から2Vの電圧が印加され、ビット線BLbに対し接地電圧が印加される。その場合、ビット線BLcの右側のビット線に対してフローティング状態に維持される。

図28は、従来の不揮発性半導体記憶装置のデータ読出部の構成を概略的に示す図である。図28において、データ読出部は、データ読出時、列選択ゲート915を介して選択列に対応するビット線BLに結合され、読出電圧を定電流IRとともに選択ビット線BLに供給する定電流源920と、定電流源920からの分流Isにより充電される容量素子921と、容量素子921の充電電圧に従って内部読出データRTを生成する増幅回路922を含む。この増幅回路922は、たとえば差動増幅回路で構成され、容量素子921の充電電圧を所定の基準電圧と比較し、2値読出データRDを生成する。

ビット線BLは、メモリセルMCを介して仮想ソース線VSLに接続される。この仮想ソース線VSLは、隣接列のビット線BLで構成され、データ読出時には、この仮想ソース線VSLは接地電圧レベルに維持される。列選択ゲート915へは、列選択線CSL上の列選択信号が与えられる。

この図28に示す内部データ読出部の構成においては、メモリセルMCの記憶データに応じて、このビット線BLから仮想ソース線VSLに流れる電流Ibの大きさが異なる応じて、容量素子912へ供給される電流Isの大きさも異なる。したがって、メモリセルMCの記憶データに応じて一定期間内での容量素子921の充電電圧が異なる。この容量素子921の充電電圧を増幅回路922で検知し増幅することにより内部読出データRDを生成する。

ここで、容量素子921は、図示しない放電スイッチを介して、データ読出前に、一旦、接地電圧レベルに放電される。

上述のように、ビット線が隣接メモリセルで共有される構成においては、プログラムモード時およびデータ読出モード時、選択メモリセルに応じて、ビット線が仮想ソース線として用いられて、接地電圧レベルに維持される。このようなアレイ構成を、「バーチャルGND(グラウンド)アレイ」構成と称する。

このようなバーチャルGNDアレイ構成においては、ビット線が行方向において隣接する2ビットのメモリセルにより共有されるため、プログラム時においては、プログラム高電圧が印加されるビット線に関して、フローティング状態のビット線と接地電圧状態のビット線が配置される。したがって、プログラム対象のメモリセルが接続するビット線を流れる電流が、隣接メモリセルを介してフローティング状態のビット線へ流れる可能性が生じる。このような場合、プログラム対象のメモリセルの絶縁膜(窒化膜)の電子注入量が不十分となり、正確にデータをプログラムすることができない。

また、確実にプログラムをするためにはプログラム期間を長くすることが考えられるが、この場合、不必要にフローティング状態のビット線に電流が流れ、消費電流が増大する可能性がある。

また、データ読出時においても、同様、読出電圧が印加されるビット線に関して接地電圧レベルのビット線とフローティング状態のビット線とが配置される。したがって、この状態においても、読出対象のメモリセルが接続するビット線からフローティング状態のビット線へ電流が流れる可能性が生じ、読出対象のメモリセルの記憶データが書込状態に対応するデータのとき、誤って消去状態にあると判定される可能性があり、正確なデータ読出を行なうことができなくなる可能性がある。

また、プログラム/リード対象のビット線が行方向において隣接するメモリセルにより共有されるため、プログラム/読出対象のビット線に関して接地電圧レベルおよびフローティング状態のビット線が対向して配置される。従って、1つのメモリブロックにおいては、1つのメモリセルに対しプログラム/データ読出を行なうことができるだけであり、高速でデータ書込/読出を行なうことができない。また、読出データビット幅が小さく、データバンド幅が小さく、効率的に処理を実行する処理システムを構築するのが困難になるという問題が生じる。

また、プログラム時においては、外部からのアクセスを禁止して内部でデータの書込に必要な電圧が生成されて、書込みが行われる。プログラムには絶縁膜に電荷を注入する必要があり、データ書込のサイクル時間は、データ読出のサイクル時間より長い。従って、データ書込のサイクルタイムが、この半導体記憶装置のアクセス時間を決定することになり、高速アクセスを実現することができない。

それゆえ、この発明の目的は、効率的にデータの書込および読出を行なうことのできる半導体記憶装置を提供することである。

この発明の他の目的は、データ転送効率の優れた半導体記憶装置を提供することである。

この発明のさらに他の目的は、データ処理効率の優れた処理システムを構築することのできる不揮発性半導体記憶装置を提供することである。

この発明の第1の観点に係る半導体記憶装置は、各々が複数の不揮発性メモリセルを有する複数のメモリブロックと、各メモリブロックに対応して配置され、各々が対応のメモリブロックに対するデータの書込および読出を行なうための電圧を伝達する複数のローカルバスと、複数のメモリブロックに共通に配置され、複数のメモリブロックの選択されたメモリブロック間でデータの転送を行なうためのデータ転送バスを備える。

好ましくは、複数のローカルバスの各々は、複数の信号線を含み、各メモリブロックにおいて複数の不揮発性メモリセルは行列状に配列され、各メモリブロックにおいては、メモリセル列に対応して、かつ隣接列のメモリセルに共有されるように配列され、各々に対応の列の不揮発性メモリセルが接続する複数のビット線と、メモリセル行に対応して配置され、各々に対応の行の不揮発性メモリセルが接続する複数のワード線とが設けられる。この構成において、好ましくは、さらに、各メモリブロックに対応して配置され、少なくともアドレス信号と動作モード指示信号と動作モード指示信号のデータ書込指示時の書込データとに従ってローカルバスの電圧を設定する電圧供給制御回路と、各メモリブロックに対応して配置され、少なくともアドレス信号に従ってローカルデータバスの選択された信号線のデータを検知して内部読出データを生成する内部読出回路と、各メモリブロックに対応して配置され、アドレス信号に従って対応のローカルバスの各信号線を対応のメモリブロックのビット線に結合するビット線選択回路とが設けられる。

好ましくは、データ転送バスは、各メモリブロックの電圧制御回路および読出回路に選択的に結合される。

好ましくは、複数のメモリブロックは、各々が、少なくとも1個のメモリブロックを含む複数のメモリ群に分割される。この構成において、電圧供給制御回路および内部読出回路およびビット線選択回路は、メモリ群単位で互いに独立に動作可能とされる。

メモリブロックに対応してローカルバスを配置し、複数のメモリブロックに共通にデータ転送バスを配置する。したがって、1つのメモリブロックにおいて書込またはデータ読出を行なっているときに、そのデータ転送バスを介してアクセス中のデータを別のメモリブロックへ転送することができ、データの退避およびバックアップを容易に行なうことができる。また、バンク構成を利用する場合、バンク間でデータ転送を行なうことにより、1バンクへの書込時、別バンクから転送データを読出すことにより、処理効率を改善することができる。

また、1または複数のメモリブロック単位で、データの書込/読出を行なうことにより、同時に、メモリブロックにおいてデータの書込または読出を行なうことができ、データビット幅を広くすることができ、転送データのバンド幅を拡張することができ、処理効率が改善される。

[実施の形態1]

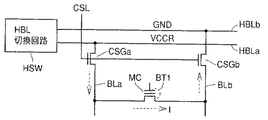

図1は、この発明の従う不揮発性半導体記憶装置の要部の基本的構成を概略的に示す図である。図1において、1つのメモリブロック内に配置されるビット線に共通に電位供給線HBLaおよびHBLbが配設される。この電位供給線HBLaおよびHBLbは、HBL切換回路HSWにより、その電圧レベルが設定される。HBL切換回路HSWは、アドレス信号、書込/読出指示信号、リバース/フォワード方向指示信号、および書込データに従って、電位供給線HBLaおよびHBLbの電圧レベルを設定する。

図1は、この発明の従う不揮発性半導体記憶装置の要部の基本的構成を概略的に示す図である。図1において、1つのメモリブロック内に配置されるビット線に共通に電位供給線HBLaおよびHBLbが配設される。この電位供給線HBLaおよびHBLbは、HBL切換回路HSWにより、その電圧レベルが設定される。HBL切換回路HSWは、アドレス信号、書込/読出指示信号、リバース/フォワード方向指示信号、および書込データに従って、電位供給線HBLaおよびHBLbの電圧レベルを設定する。

電位供給線HBLの数は、任意であるが、ここでは説明を簡単にするために、電位供給バスHBに含まれる電位供給線の数を2本とする。電位供給バスが、メモリブロック単位で配置される。このバスの配置については後に詳細に説明する。

電位供給線HBLaおよびHBLbに対応して設けられるメモリブロックにおいては、不揮発性メモリセルMCが行列状に配列される。図1においては、ビット線BLaおよびBLbの間に接続されるメモリセルMCを代表的に示す。このメモリセルMCは、絶縁膜電荷トラップ型メモリセルであり、2つの記憶領域(電荷蓄積領域)、すなわち右ビット領域BT1と左ビット領域BT2とを有する。図1においては、左ビット領域BT2を示す。

これらのビット線BLaおよびBLbは、ともに列選択線CSL上の列選択信号に従ってそれぞれ電位供給線HBLaおよびHBLbに結合される。所定数のビット線を組として、各組のビット線を同時に互いに異なる電位供給線に結合する。HBL切換回路HSWは、単に、この電位供給線HBLaおよびHBLbの電圧レベルを決定して設定するだけであり、各ビット線ごとに電圧を制御することは要求されないため、書込/読出時の電圧制御が容易となる。

図1においては、メモリセルMCの左ビット領域BT2に対するプログラム時の電流Iの流れを示す。このメモリセルMCの左ビット領域BT2に対するプログラム動作時においては、電位供給線HBLaおよびHBLbに、それぞれ書込高電圧VCCWおよび接地電圧GNDが与えられる。列選択ゲートCSGaおよびCSGbが、列選択信号CSLに従って導通し、ビット線BLaおよびBLbが、それぞれ電位供給線HBLaおよびHBLbに結合される。この状態においては、電位供給線HBLaからビット線BLa、メモリセルMCおよびビット線BLbを介して電位供給線HBLbに電流Iが流れる。したがって、メモリセルMCにおいては、この左ビット領域BT2に対しチャネルホットエレクトロンが蓄積され、プログラムが実行される。これにより、左ビット領域BT2においてHレベルデータが格納される。Lレベルデータ格納時においては、記憶領域は消去状態に維持される。

図2は、メモリセルMCの左ビット領域BT2の記憶データを読出す際の電流Iの流れを示す図である。この左ビット領域BT2の記憶データを読出す場合には、HBL切換回路HSWは、電位供給線HBLaおよびHBLbに、それぞれ、接地電圧GNDおよび読出電圧VCCRを供給する。列選択ゲートCSGaおよびCSGbが、列選択線CSL上の列選択信号に従って導通する。

この状態においては、電位供給線HBLbからビット線BLbを介してメモリセルMCに電流Iが供給され、このメモリセルMCの左ビット領域BT2の記憶データに応じた電流が、ビット線BLaを介して電位供給線HBLaに流れる。データ読出時においては、この読出電圧VCCRを受ける電位供給線HBLbを流れる電流量を図示しないセンスアンプにより検出する。このセンスアンプと電位供給線の接続も、HBL切換回路HSWにより実行される。この電流Iは、読出動作時においては、数十μA程度である。

図3は、メモリセルMCの右ビット領域BT1のプログラム時の電流Iの流れを示す図である。この右ビット領域BT1のプログラム時においては、電位供給線HBLaおよびHBLbが、それぞれ接地電圧GNDおよび書込高電圧VCCWに設定される。この状態においては、電位供給線HBLbからビット線BLbを介してメモリセルMCに電流Iが供給され、さらに電流Iがビット線BLaを介して電位供給線HBLaに流れる。したがって、このメモリセルMCにおけるチャネル電流により、ホットエレメントが生成されて、右ビット領域BT1に蓄積される。

図4は、メモリセルMCの右ビット領域BT1の蓄積データの読出時の電流Iの流れを示す図である。このメモリセルMCの右ビット領域BT1の記憶データ読出時においては、電位供給線HBLaおよびHBLbが、それぞれ読出電圧VCCRおよび接地電圧GNDに設定される。この状態においては、メモリセルMCの右ビット領域BT1においては、リバース方向に電流Iが流れ、右ビット領域BT1の格納データに応じた電流が電位供給線HBLbに流れる。図示しないセンスアンプにより、この電位供給線HBLaを流れる電流を検出して、メモリセルMCの右ビット領域BT1の記憶データを検出する。

この電位供給線HBLaおよびHBLbの電圧レベルを、HBL切換回路HSWにより、選択メモリセルの位置および動作モードに応じて設定することにより、ビット線BLaおよびBLbそれぞれにおいて、動作モードに応じて、接続される電位供給ノードを変更する構成に比べて、ビット線それぞれ電位ノード切換えのためのスイッチングトランジスタを配置する必要がなく、素子数を低減することができる。

図5は、この発明の実施の形態1に従う不揮発性半導体記憶装置の全体の構成を概略的に示す図である。この図5に示す不揮発性半導体記憶装置においては、2つのバンクBNKAおよびBNKBが設けられる。バンクBNKAは、メモリセルアレイ1aおよび周辺回路2aを含み、バンクBAKBは、メモリセルアレイ1bおよび周辺回路2bを含む。メモリセルアレイ1aおよび1bそれぞれにおいて、不揮発性メモリセルが行列状に配列される。

周辺回路2aおよび2bそれぞれは、メモリセル行を選択するための行選択回路、メモリセル列(ビット線)を選択するための列選択回路、データの書込/読出に必要な電圧を生成するHBL切換回路、およびデータの読出を行なうセンスアンプを含む。

バンクBNKAおよびBNKBの間で双方向でデータの転送を行なうための転送回路3が設けられる。転送回路3は、バンクBNKAおよびBNKBの一方のバンクへのデータアクセス時(書込/読出)、この一方のバンクのデータを他方のバンクに転送する。または、単に1つのバンクから他方のバンクへ内部でデータを転送する。

不揮発性半導体記憶装置は、さらに、外部からの動作モードを指示するコマンドCMDを受けるコマンドポート4と、読出アドレスRADDを受けかつ外部出力データQを出力するリードポート5と、書込アドレスRADDおよび書込データDを受けるライトポート6を含む。

コマンドポート4は、外部からのコマンドCMDを受けるコマンド入力回路4aを含む。コマンド入力回路4aは、コマンドCMDの形態に応じて、その回路構成が定められる。たとえばコマンドCMDが、複数の信号で与えられる場合、このコマンド入力回路4aは、与えられたコマンドをデコードするデコード回路を含み、このデコード結果に従って、内部動作モード指示信号を生成する。またコマンドCMDが、1つの信号により動作モードを指示する場合には、このコマンド入力回路4aは、バッファ回路で構成される。

リードポート5は、外部からのリードアドレスRADDを受けて内部リードバンクアドレス信号RBADを含む内部リードアドレスを生成するリードアドレス入力回路5aと、選択バンクから読出されたデータをバッファ処理して外部へ出力するデータ出力回路5bを含む。外部へ出力されるデータQは、複数ビットで構成される。

ライトポート6は、外部からのライトアドレス信号WADDを受けて内部ライトバンクアドレス信号WBADを含む内部ライトアドレス信号を生成するライトアドレス入力回路6aと、外部からの書込データDを受けて内部書込データを生成するデータ入力回路6bを含む。

リードポート5およびライトポート6を別々に設けることにより、1つのバンクに対し、データ書込を行なうのと並行して、データの読出を別バンクに対して実行する。比較的に長時間を要するデータの書込時に、別バンクにアクセスしてデータを読み出すことにより、データアクセス効率を改善する。

この不揮発性半導体記憶装置の内部動作を制御するために、コマンド入力回路4aからの内部コマンド(動作モード指示信号)と、リードポート5からのリードバンクアドレス信号RBADとライトポート6からのライトバンクアドレス信号WBADを受けるメイン制御回路7と、メイン制御回路7からの選択信号SELRに従って、バンクBNKAおよびBNKBから読出されたデータの一方を選択する選択回路8と、メイン制御回路7からの選択信号SELWに従ってライトポート6から与えられたデータをバンクBNKAおよびBNKBの一方へ伝達する選択回路9が設けられる。

リードポート5およびライトポート6からの内部アドレス信号は、それぞれバンクBNKAおよびBNKBに与えられる。このメイン制御回路7は、バンクアドレス信号RBADおよびWBADに従って、アドレス指定されたバンクに対し、コマンドポート4を介して与えられる内部動作モード指示信号に従って、選択されたバンクを活性化する。

図6は、図5に示すバンクBNKAおよびBNKBの構成の一例を示す図である。図6において、バンクBNKAのメモリアレイ1aは、2つのメモリブロックMB0およびMB1を含み、バンクBNKBのメモリアレイ1bは、メモリブロックMB2およびMB3を含む。メモリブロックMB0およびMB1それぞれにおいて、1つのメモリセルが選択され、またメモリブロックMB2およびMB3それぞれにおいて、1つのメモリセルが選択される。したがって、この図6に示す構成においては、選択バンクに対し2ビットのデータの書込/読出が行なわれる。

メモリブロックMB0−MB3それぞれに対応して電位供給バスHB0−HB3が設けられる。これらの電位供給バスHB0−HB3それぞれに対して、HBL切換回路HSW0−SW3が配置される。HBL切換回路HSW0およびHSW1が隣接して配置され、またHBL切換回路HSW2およびHSW3が隣接して配置されるように示す。しかしながら、これらの電位供給回路HSW0およびHSW1は、メモリブロックMB0およびMB1において反対方向に電流が流れるようにメモリブロックMB0およびMB1の対向端部に配置される。電位供給回路HSW2およびHSW3についても同様である。

これらのHBL切換回路HSW0−HSW3は、それぞれ、選択回路9に結合される。データ書込時においては、これらのHBL切換回路HSW0−HSW3は、書込データに応じて、対応の電位供給バスHB0−HB3の電圧レベルを設定する。これらのHBL切換回路HSW0−HSW3それぞれに対しては、図5に示すリードポート5およびライトポート6からのリードアドレスおよびライトアドレスが与えられ、また、メイン制御回路7からの制御信号が与えられる。

電位供給バスHB0−HB3それぞれに対応して、センスアンプSA0−SA3が設けられる。これらのセンスアンプSA0−SA3は、データ読出時、対応の電位供給バスHB0−HB3の読出電圧を受ける電位供給線に結合され、この電流量に従って内部読出データを生成する。センスアンプSA0−SA3は、選択回路8に結合されるセンスアンプSA0ないしSAと電位供給バスHB0ないしHB3の電位供給線との接続は、電位供給回路HSW0ないしHSW3に含まれるデコーダの出力信号に従って行われる。

図5に示す転送回路3として、メモリブロックMB0−MB3に共通に双方向データ転送線BTX0およびBTX1が設けられる。双方向データ転送線BTX0は、メモリブロックMB0に対して設けられる転送スイッチ回路TX0およびメモリブロックMB2に対して設けられる転送スイッチ回路TX2に結合される。双方向データ転送線BTX1は、メモリブロックMB1およびMB3にそれぞれ対して設けられる転送スイッチ回路TX1およびTX3に結合される。

これらの転送スイッチ回路TX0−TX3の各々は、対応のセンスアンプに接続されるリード転送スイッチTXRと、対応のHBL切換回路に結合されるライト転送スイッチTXWを含む。

書込動作時においては、入力データDが、選択バンクに分配され、選択バンクのメモリブロックに並行して書込まれる。データ読出動作時においては、選択バンクのメモリブロックから読出されたデータが、選択回路8により選択されて出力される。

図5に示すように、リードポート5およびライトポート6を別々に設け、リードアドレスRADDおよびライトアドレスWADDを与えており、データ書込期間中に、別のバンクに対し、リードアクセスを行ない、動作効率を改善する。これは、データ書込時においては、右ビット領域BT1または左ビット領域BT2に電子を注入する必要があり、データ読出時よりも、時間を要する。従って、この書込動作中に、データのリード動作を別バンクに対して行なうことにより、効率的に、データを外部の処理装置へ転送することができる。

HBL切換回路HSW0−HSW3が、メモリブロックMB0−MB3それぞれに対応して配置されているのは以下の理由による。メモリブロックMB0−MB3は、バーチャルGLDアレイ構成を有しており、行方向において隣接するメモリセルがビット線を共有している。したがって、選択メモリセルのアドレスに従って、ビット線がドレイン線およびソース線のいずれにもなり得る。ビット線がソース線であるかドレイン線であるかに応じて、ビット線に対するセンスアンプの接続、およびビット線の電位制御を行なう必要がある。また、書込時においてはプログラムの有無によって、ビット線の電位制御が異なる。メモリブロック単位で、これらのビット線とセンスアンプの接続およびビット線の供給電圧の設定を行なうことにより、メモリブロック単位で正確にデータの書込/読出を行なうことができる。

図7は、図6に示すメモリブロックMB0およびMB1および周辺部の構成を具体的に示す図である。図7において、メモリブロックMB0においては、複数のメモリセルMCが行列状に配列され、メモリブロックMB1においても、不揮発性メモリセルMCが行列状に配列される。図7においては、メモリブロックMB0において3行4列に不揮発性メモリセルMCが配列され、メモリブロックMB1において、不揮発性メモリセル(以下、単にメモリセルと称す)が3行5列に配列する部分を代表的に示す。

メモリブロックMB0においては、隣接列のメモリセルに共有されるようにメモリセル列に対応してビット線BL1ないしBL5が配置され、またメモリブロックMB1においては、隣接列のメモリセルにより共有されるように各メモリセル列に対応してビット線BL6ないしBL11が配列される。メモリブロックMB0およびMB1の境界領域においては、ダミーセル列が配列され、各メモリセル行に対応してダミーセルDMC1、DMC2、およびDMC3が配設される。ダミーセルDMCは、メモリブロックMB0およびMB1において境界領域のメモリセルにアクセスする際に、メモリブロック間でのビット線電圧の競合および電流の流入/流出を防止するための分離素子として用いられる。

このメモリブロックMB0およびMB1のメモリセル行それぞれに対応してワード線WL1ないしWL3が配列される。

メモリブロックMB0およびMB1それぞれに対応して、ビット線選択回路BS0およびBS1が設けられる。ビット線選択回路BS0およびBS1の各々は、ビット線BLそれぞれに対応して配置され、選択時、予め定められた電位供給線HBLに対応のビット線を接続するコラム選択スイッチSWと、このコラム選択スイッチの導通/非導通を制御するスイッチ制御回路30を含む。

スイッチ制御回路30は、コラムプリデコーダ101からのプリデコード信号AL0−ALnに従って4本のビット線を同時に選択するデコーダDCと、選択メモリセル位置を示す信号C0およびC1に従って選択的に隣接デコーダを活性化するANDゲートAGとを含む。

4つのコラム選択スイッチSWが、1つのデコーダDCに対して配置される。このコラム選択スイッチにより、デコーダDCの出力信号に従って、選択されたビット線を最大合計8本を、電位供給バスHBの電位供給線に1対1に結合する。

図7においては、ビット線選択回路BS0に含まれるスイッチ制御回路30において、デコーダDC1と、デコーダDC1の出力信号とメモリセル位置指示信号C0を受けるANDゲートAG1を代表的に示す。このANDゲートAG1は、デコーダDC1のデコード結果がHレベルの選択状態を示し、かつメモリセル位置指示信号C0が、選択メモリセルが、4つのメモリセルのうちの左半分に位置していることを示すときには、デコーダDC1に隣接するデコーダを活性化する。

電位供給バスHB0は、8本の電位供給線HBL1−HBL8を含み、HBL切換回路HSW0により、選択メモリセル位置情報および動作モードに応じて、それぞれの電圧レベルが設定される。これらの8本の電位供給線HBL1−HBL8に対し、選択的に8本のビット線が接続されるため、ビット線BL1−BL5それぞれに対応してコラム選択スイッチSW1−SW5が設けられる。メモリブロックMB0の端部を除いて、2つのデコーダDCの出力信号が選択状態となり、8本のビット線が、1対1対応で電位供給線HBL1−HBL8に結合される。ビット線BLが接続する電位供給線HBLは、コラム選択スイッチSWにより、一意的に定められる。

ビット線選択回路BS1においても、同様の構成が配置される。スイッチ制御回路31においては、ビット線BL6−BL9を同時に選択するデコーダDC2と、ビット線BL10−BL13(図示せず)を同時に選択するデコーダDC3と、デコーダDC2の出力信号とメモリ位置指示信号C1を受けてデコーダDC3を選択的に活性化するANDゲートAG2と、デコーダDC3の出力信号とメモリセル位置指示信号C0とを受けて、デコーダDC2を選択的に活性化するANDゲートAG3を代表的に示す。

ビット線選択回路BS1において、HBL切換回路HSW1から電位供給線HBL11−HBL18に動作モードおよび選択メモリセル位置に応じた電圧が伝達され、これらの電位供給線HBL11−HBL18が、メモリブロック端部領域をのぞいて、1対1にビット線に結合される。ビット線BLが接続する電位供給線HBLは、コラム選択スイッチSWにより一意的に定められている。

図7に示す構成において、メモリセルの列アドレスは、ブロック境界領域に関して対称的に配置される。また、ビット線BLと電位供給線HBLとの接続も、メモリブロックMB0およびMB1において、ブロック境界に関して対称的に行なわれる。この対称配置により、電流の流れる方向がメモリブロックMB0およびMB1においてブロック境界において対称的となる。

図8は、図7に示すHBL切換回路HSW0の構成を概略的に示す図である。図8において、HBL切換回路HSW0は、データ書込時、電位供給線HBL1−HBL8の電圧レベルを設定する書込電位供給回路41と、読出動作時に、この電位供給線HBL1−HBL8の電圧レベルを設定しかつセンスアンプSA0に、読出電圧が印加された電位供給線を結合する読出電位供給回路を含む。

書込電位供給回路41は、3ビットのアドレス信号AC−AC3とフォワード信号FWDと、リバース信号REVと、書込信号WITEとを受ける。アドレス信号AC1−AC3は、下位3ビットのコラムアドレス信号である。

フォワード信号FWDは、フォワードライトまたはフォワードリード時に、外部からのモード指示信号に従って生成される。リバース信号REVは、リバースライトまたはリバースリード時に、活性化される。これらのフォワード信号FWDおよびリバース信号REVは、外部からのモード指示信号に代えて、特定のコラムアドレスビットをデコードして活性化されてもよい。フォワード信号FWDおよびリバース信号REVがモード指示信号に従って生成される場合には、これらの信号は、メイン制御回路において生成される。特定のコラムアドレスビットに従ってこれらのフォワード信号FWDおよびリバース信号REVが生成される場合には、これらの信号は、コラムアドレスデコーダから生成されてもよく、また、周辺回路内の専用のフォワード/リバースデコード回路により生成されてもよい。

書込信号WITEは、データ書込動作時に、外部からのコマンドに従って、選択バンクに対して活性化される。

読出電位供給回路42は、同様、3ビットのアドレス信号AC1−AC3と、フォワード信号FWDと、リバース信号REVと読出信号REDとを受ける。読出信号READは、読出動作時に、外部からのコマンドに従って選択バンクに対して活性化される。

メモリブロックMB1に対して設けられるHBL切換回路HSW1の構成も、この図8に示すHBL切換回路HSW0の構成と同じである。

これらのHBL切換回路HSW0およびHSW1の構成においては、8本の電位供給線HBL1−HBL8およびHBL11−HBL18の電圧レベルが設定され、したがって、8本の連続するビット線を1つの単位として、それらの電位を制御する。したがって、ビット線選択回路BS0およびBS1の構成においては、デコーダに対応して配置される4本のビット線およびそれに隣接するビット線を単位として、8本の連続するビット線が電位供給線HBL1−HBL8に1対1対応で接続される。

仮に、電位供給線HBL1に、ビット線BL1が対応して配置され、電位供給線HBL2にビット線BL2が対応して配置される状態を考える。この場合、1つの電位供給線HBLn(nは自然数)に対して、メモリブロックMB0内の複数のビット線BL(8m+n)が選択的に結合される。書込電位供給回路41および読出電位供給回路42は、複数の電位供給線HBLを介して複数のビット線BLに電位を供給することができ、したがって、それらの回路構成を簡略化することができる。すなわち、書込電位供給回路41および読出電位供給回路42は、各ビット線BLごとの電位を制御する必要がなく、入力アドレス信号AC1−AC3に従ってビット線BLの数よりも少ない数の電位供給線を有する電位供給バスHBの電位を制御するだけで、各ビット線BLの電位を制御することができる。

以下、図7および図8を参照して、この不揮発性半導体記憶装置のデータ書込時のプログラム動作について説明する。

今、図7において、メモリブロックMB0のメモリセルMC10の記憶領域(左ビット領域)L1にHレベルのデータを書込み、メモリブロックMB1のメモリセルMC20の記憶領域L2に、Hレベルのデータを書込む場合について説明する。ここで、Hレベルのデータの書込とは、記憶領域に電子を注入する(プログラムする)動作を示す。Lレベルデータ書込時においては、消去が実行される。

まず、ビット線選択回路BS0内においてデコーダDC1が、コラムアドレスプリデコード信号を受け、その出力信号をHレベルに立上げる。同様、ビット線選択回路BS1においても、デコーダDC2が与えられたコラムプリデコード信号に従って、その出力信号をHレベルに立上げる。デコーダDC3では、デコーダDC2と異なる組合せのコラムプリデコード信号が与えられており、また、メモリセル位置指示信号C0もLレベルであり、ANDゲートAG2の出力信号もLレベルであり、その出力信号はLレベルである。

同様、ビット線選択回路BS1内においても、デコーダDC2から出力されるデコード信号に従って、コラム選択スイッチSW6からSW9が導通状態となる。応じて、ビット線BL6−BL9が、それぞれ、電位供給線HBL11−HBL14に結合される。電位供給線HBL15からHBL18はビット線から分離される。

続いて、HBL切換回路HSW0およびHSW1は、それぞれ所定の電位を、対応の電位供給線に供給する。具体的に、メモリブロックMB0に対しては、電位供給線HBL1およびHBL2に接地電位GNDが供給され、電位供給線HBL3およびHBL4に書込電位VCCWが供給される。それ以外の電位供給線HBL5−HBL8は、フローティング状態に維持される。

この結果、ビット線BL2およびBL3が、書込電位VCCWに維持され、ビット線BL4およびBL4が接地電位に維持される。ワード線WL1が選択されると、メモリセルMC10においてビット線BL3からビット線BL4へ電流が流れ、記憶領域(右ビット領域)L1に、Hレベルのデータが記憶される(電子が絶縁膜に注入される)。

このとき、ビット線BL2は、書込電位VCCWに維持されている。したがって、ビット線BLおよびBL3に接続されるメモリセルMC10に隣接したメモリセルMCにおいては電流は流れない。また、ビット線BL5の電位は接地電位GNDに維持される。したがって、メモリセルMC10に隣接するビット線BL4およびBL5に接続されるメモリセルMCにおいても電流は流れない。

メモリブロックMB1においては、HBL切換え回路HSW1より、電位供給線HBL11およびHBL12が接地電位GNDに維持され、電位供給線HBL13およびHBL14は、書込電位VCCWに維持される。それにより電位供給線HBL15からHBL18は、フローティング状態に維持される。したがって、ビット線BL8およびBL9が書込電位VCCWに維持され、ビット線BL6およびBL7は、接地電位GNDに維持される。

ワード線WL1が選択されると、メモリセルMC20のビット線BL8側からビット線BL7側に電流が流れ、記憶領域(右ビット領域)L2にHレベルのデータが格納される(プログラムが行なわれる)。メモリセルMC20に隣接するメモリセルの両端は、それぞれ書込電位VCCWまたは接地電位GNDに維持され、電流は流れない。

したがって、書込対象のメモリセルに対し書込動作を行なっても、書込対象のメモリセルに隣接するメモリセルにおいては電流は流れない。

なお、この書込動作において、メモリセルMC10が、単位を構成する4ビットのメモリセルにおいて右側に配置されており、メモリセル位置指示信号C0はLレベルであり、ANDゲートAG1の出力信号はデコーダDC1が出力信号HレベルとなってもLレベルを維持する。したがって、ビット線BL1に対して設けられるデコーダからの出力信号はLレベルであり、コラム選択スイッチSW1はオフ状態を維持する。

メモリブロックMB1に対しても、選択メモリセルMC20は、デコーダDC2に対して配置される4ビットのメモリセルのうち、左側に配置されており、ANDゲートAG2の出力信号はLレベルとなる。したがって、ビット線選択回路BS0およびBS1において境界領域に関して対称的に、ビット線と電位供給線の接続が形成されるようにコラム選択スイッチを配置することにより、この境界領域においてメモリセルが選択されても、正確にメモリセルに対する書込を行なうことができる。

境界領域と異なるメモリセルが選択された場合には、2つのデコーダが選択され、各ビット線がそれぞれ対応の電位供給線に結合される。この場合、4ビットのビット線に対しては電位供給線が、フローティング(FLAOTING)状態とされるため、電流の流れる経路は遮断され、選択メモリセルに対する書込動作に対して悪影響は生じない。

8本のビット線を単位として、電位供給線とビット線との接続を行っているのは以下の理由による。例えば、図7において、ビット線BL2とビット線BL1との間のメモリセルに対して書込みをする場合、ビット線BL1およびBL2の電位を書込みデータに応じて設定する必要がある。この場合、メモリセル位置指示信号C0がHレベルとなり、ANDゲートAG1の出力信号をHレベルに設定して、ビット線BL1を電位供給線HBL5に結合して、その電位を設定する。従って、1つのデコーダにより4本のビット線が選択される場合においても、その単位の端のビット線に接続するメモリセルに対してアクセスする場合には、隣接単位のビット線を選択して、電位供給線に接続して、その電位を設定する必要があり、8本の電位供給線が必要となる。

図9は、1つのメモリブロックにおける境界領域と異なる領域のビット線選択回路の構成を概略的に示す図である。図9において、ビット線選択回路は、それぞれ4ビットのビット線を選択するデコーダDECaおよびDECbを含む。このデコーダDECaのデコード結果は、両側に配置されるANDゲートAGaおよびAGbに与えられる。デコーダDECbのデコード結果は、その両側に配置されるANDゲートAGcおよびAGdへ与えられる。ANDゲートAGaおよびAGcは、メモリ位置指示信号C0を受け、またANDゲートAGbおよびAGdが、メモリ位置指示信号C1を受ける。

デコーダDECaおよびDECbそれぞれに対応して、メモリセルMC0−MC3が配置される。メモリセルMC0またはMC1が指定されたときには、メモリ位置指示信号C0がHレベルとなり、メモリセルMC2またはMC3が指定されたときには、メモリ位置指示信号C1がHレベルとなる。

デコーダDECaおよびDECbはそれぞれ、プリデコード信号AL0−ALnの所定の組合せを受けており、プリデコード信号AL0−ALnにより、1つのデコーダが選択される。このデコード結果が両側に配置されるANDゲートへ与えられる。したがって、たとえば、デコーダDECaが選択されたときには、その出力信号はHレベルとなる。そのとき、メモリセルMC2またはMC3が選択された場合には、メモリ位置指示信号C1がHレベルとなるため、ANDゲートAGbの出力信号はHレベルとなる。

デコーダDECbは、ANDゲートAGbの出力信号がHレベルのときには、その出力信号を強制的にHレベルに立下げる。一方、メモリ位置指示信号C0がこの状態ではLレベルであり、ANDゲートAGaの出力信号はLレベルである。したがって、デコーダDECaが選択され、メモリセルMC2またはMC3が選択されたときには、デコーダDECbが選択される。

一方、デコーダDECbの選択時においてメモリセルMC0またはMC1が選択された場合には、メモリ位置指示信号C0がHレベルとなる。したがって、デコーダDECbの出力信号がHレベルとなり、またANDゲートAGcの出力信号がHレベルとなり、応じてデコーダDECaの出力信号もHレベルとなる。したがって、境界領域と異なる領域においては、8本のビット線が同時に選択され、電位供給バスの電位供給線にそれぞれ結合される。

たとえばデコーダDECaが選択されかつメモリセルMC3が選択されたとき、このメモリセルMC3に接続するビット線に書込電圧を印加した場合、デコーダDECbに対応して配置されるメモリセルMC0に接続するビット線をフローティング状態に設定する。デコーダDECbに対応して配置されるメモリセルMC0に接続するビット線をフローティング状態に設定することにより、このメモリセルMC0を介して電流が、メモリセルMC3が接続するビット線から流れるのを確実に防止する。

これにより、選択メモリセルとビット線を共有するメモリセルが接続する他方側ビット線を、常にフローティング状態または一方ビット線と同一電位に設定することができ、電流が不必要に流れるのを防止することができる。すなわち、同一単位内においては、選択メモリセルとビット線を共有するメモリセルは、ソースおよびドレイン領域がともに同一電位とされ、電流が流れるのを防止される。単位外のメモリセルについては、フローティング状態または書込時の印加電圧が与えられる。いずれにおいても、非選択メモリセルの電流の経路は遮断される。個々のビット線ごとに電位を制御する必要がなく、隣接ビット線間の電圧を考慮するだけでよく、電位供給線において選択メモリセル位置に応じて電圧をサイクリックに印加するだけでよく、ビット線電位の制御が容易となる。

デコーダDECaにおいてメモリセルMC1が選択される場合、メモリセルMC2およびMC3に電流が流れないように、同一電圧およびフローティング状態に各ビット線が設定される。8本の電位供給線において、隣接する2本の電位供給線の組が、それぞれ同一電圧とされ、残りの4本の電位供給線がフローティング状態とされる。

次に、図7および図8に示す構成におけるデータ読出動作について、図10を参照して説明する。データ読出時において、ビット線選択回路BS0およびBS1のデコーダDC1からDC3およびコラム選択スイッチSW1ないしSW11の動作は、書込動作時のそれと同じであり、その説明は繰返さない。

読出動作時においては、読出信号READが活性化され、HBL切換回路HSW内の読出電位供給回路42が活性化され、電位供給線HBL1からHBL8に対して電位を供給する。書込信号WRITEはLレベルであり、書込電位供給回路41は非活性状態にある。

メモリセルMC10の記憶領域(左ビット領域)L1の記憶データを読出す場合には、読出電位供給回路42は、電位供給線HBL1およびHBL2に読出電位VCCRを供給し、電位供給線HBL3およびHBL4に接地電位GNDを供給する。その他の電位供給線HBL5からHBL8はフローティング状態に維持される。

したがって、ビット線BL2およびBL3が接地電位GNDに維持され、ビット線BL4およびBL5が読出電位VCCRに維持される。応じて、メモリセルMC10においては、ビット線BL4からビット線BL3方向に電流が流れ、記憶領域L1のデータをセンスアンプにより読出すことができる。

センスアンプ43は、電位供給線HBL3を流れる電流を受けて増幅することにより、内部読出データを生成する。センスアンプ43と電位供給線HBL3との接続は、読出電位供給回路42内のセンスデコーダにより電位供給線を選択することにより行なわれる。このセンスデコーダは、列アドレス信号AC1−AC3とフォワード信号FWDとリバース信号REVとに従って、選択メモリセルに対応して配置されるドレインビット線を選択する。3ビットの列アドレスAC1からAC3により、8個のメモリセルのうち1つのメモリセルを選択し、対応の2本の電位供給線を識別し、フォワード信号FWDおよびリバース信号REVにより、選択メモリセルのドレインビット線に接続する電位供給線を選択する。

これに代えて、列アドレス信号AC1からAC3の最下位ビットが、メモリセルの記憶領域、すなわち、右ビット領域および左ビット領域を特定する場合には、データ読出時においてはリバース方向に電流が流れるため、3ビットのアドレス信号AC1からAC3のデコード結果に従って電位供給線が選択されてセンスアンプに接続されてもよい。

ビット線BL2およびBL3は、接地電位に維持されており、ビット線BL4およびBL5が、読出電位VCCRに維持される。したがって、メモリセルアレイMC10に隣接するメモリセルにおいては、その両側の電位は同じであり、電流は流れない。

ビット線BL1はコラム選択スイッチSW1がオフ状態であり、フローティング状態にある。

メモリブロックMB1のメモリセルMC20の記憶領域(右ビット領域)L2のデータの読出動作についても同じである。

この場合、メモリブロックMB1においては、電位供給線HBL11およびHBL12に読出電位VCCRが、電位供給線HBL13およびHBL14に接地電位GNDがそれぞれHBL切換回路HSW1より供給される。ビット線BL6およびBL7が、読出電位VCCRに維持され、ビット線BL8およびBL9が接地電位GNDに維持される。したがって、メモリセルMC20においてはビット線BL7からビット線BL8方向に電流が流れ、記憶領域L2の記憶データが読出される。

ビット線BL10は対応のコラム選択スイッチSW10がオフ状態であり、フローティング状態にある。

メモリセルMC20の両側のメモリセルは、その導通ノードが読出電位VCCRまたは接地電位GNDに維持されており、電流は流れない。したがって、上述のようにHBL切換回路HSW0およびHSW1をそれぞれ設けることにより、各メモリブロックごとにメモリセルを選択して、同時に書込動作または読出動作を行なうことができる。

この場合、メモリブロックMB0およびMB1間においてはダミーセルDMC1からDM3が配置されており、これらのダミーセルDMCのソースおよびドレインが同一電位に維持されており、これらのダミーセルDMCにおいて電流が流れるのを防止することができ、メモリブロックMB0およびMB1それぞれにおいて正確にメモリセルのデータの読出を行うことができる。

特に、図7に示すメモリセルの配置においては、メモリブロックMB0およびMB1において、記憶領域を含めて対称的にメモリセルが選択され手電位供給線HBLに接続されるように、ビット線選択回路BS0およびBS1にそれぞれデコーダが配置されている。したがって、ビット線BL4およびBL5の間のメモリセルとビット線BL6およびBL7の間のメモリセルがともに選択される場合が存在する。

この場合、プログラム時において、たとえばビット線BL5に書込電圧VCCWが印加され、ビット線BL6に接地電位GNDが供給される場合が生じる。フォワード信号FWDおよびリバース信号REVは、これらのHBL切換回路HSW0およびHSW1に共通に与えられている。したがって、メモリブロックMB0およびMB1において、それぞれ、右ビット領域および左ビット領域へのアクセスが常に並行して行なわれることになる。したがって、ビット線BL5およびBL6においては、同じ電圧レベルの電圧が伝達され、ダミーセルDMC1−DMC3におけるリーク電流を確実に抑制することができ、ブロック間貫通電流が生じるのを防止することができる。

データ読出時において、ビット線BL2およびBL3に読出電圧VCCRが伝達され、ビット線BL4およびBL5に対して接地電圧GNDが伝達される場合において、読出電流がビット線BL3からビット線BL5へ流れることが考えられる。しかしながら、この場合においても、ビット線BL4およびBL5の間のメモリセルは、ソースおよびドレインがともに接地電圧レベルであり、また、ビット線BL5にはダミーセルが接続されるため、メモリブロックMB0からメモリブロックMB1に電流が流れこむのは確実に防止することができる。

メモリブロックMB1からメモリブロックMB0に流れる電流についても同様である。従って、メモリブロック単位で正確にメモリセルのデータの書込および読出を行うことができる。

[ビット線選択回路およびメモリブロックの構成の変更例]

図11は、この発明の実施の形態1に従う不揮発性半導体記憶装置のビット線選択回路およびメモリブロックの変更例の構成を示す図である。図11を参照して、メモリブロックMB0において、メモリセルMCが行列状に配列される。図11において、3行10列に配列されるメモリセルを代表的に示す。このメモリセル行に対応してワード線WL1−WL3が配設され、メモリセル列に対応して、隣接メモリセルに共有されるようにビット線BL1−BL10が配設される。

図11は、この発明の実施の形態1に従う不揮発性半導体記憶装置のビット線選択回路およびメモリブロックの変更例の構成を示す図である。図11を参照して、メモリブロックMB0において、メモリセルMCが行列状に配列される。図11において、3行10列に配列されるメモリセルを代表的に示す。このメモリセル行に対応してワード線WL1−WL3が配設され、メモリセル列に対応して、隣接メモリセルに共有されるようにビット線BL1−BL10が配設される。

このメモリアレイ構造において、さらに、1つのビット線を間においた2本のビット線に対応してメインビット線MBが配置される。図11において、ビット線BL1およびBL3に対応してメインビット線MB0が配置され、ビット線BL2およびBL4に対応してメインビット線MB1が配置される。ビット線BL5およびBL7に対応してメインビット線MB2が配置され、ビット線BL6およびBL8に対応してメインビット線MB3が配置される。ビット線BL9およびBL11に対応してメインビット線MB4が配置され、ビット線BL10および図示しないビット線BL12に対応して、図示しないメインビット線MB5が配置される。

このメモリアレイ構造において、4つのメモリセルを単位として、2つのメインビット線が配置される。このメインビット線により、4本のビット線の組から2つのビット線が選択されて、電位供給線LAおよびLBに結合される。

メインビット線MB0は、サブコラム選択スイッチSW53およびSW54を介してビット線BL1およびBL3に結合され、メインビット線MB1は、サブコラム選択ゲートSW46およびSW47を介してビット線BL2およびBL4にそれぞれ結合される。メインビット線MB2は、サブコラム選択スイッチSW55およびSW56を介してビット線BL5およびBL7に結合される。メインビット線MB3は、サブコラム選択スイッチSW48およびSW49を介してビット線BL6およびBL8に結合される。メインビット線MB4は、サブコラム選択スイッチSW57およびSW58を介してビット線BL9およびBL11へそれぞれ結合される。

メインビット線MB0、MB2およびMB4は、それぞれ、メインコラム選択スイッチMSC0、MSC2、およびMSC4を介して電位供給線LBに結合され、メインビット線MB1およびMB3がメインコラム選択スイッチMSC1およびMSC3を介して電位供給線LAに結合される。

これらのメインコラム選択スイッチMSC0−MSC4の導通および非導通を制御するために、スイッチ制御回路34が設けられる。このスイッチ制御回路34においては、メインコラム選択スイッチMSC0−MSC4それぞれに対応してデコーダDC20−DC24が設けられる。これらのデコーダDC20−DC24へは、プリデコード信号AL0−ALnの所定の組がそれぞれ与えられる。これらのプリデコード信号AL0−ALnは、3つのプリデコード信号により、2つのビット線を指定する。すなわち、プリデコード信号AL0−ALnにより1つのメインビット線が指定される。

2つのメインビット線を同時に選択するために、さらに、ANDゲートAG20−AG29が設けられる。ANDゲートAG20は、デコーダ20のデコード結果とメモリ位置指示信号LC1とを受け、その出力信号をデコーダDC21へ与える。ANDゲートAG21は、デコーダDC21のデコーダ結果とメモリ位置指示信号LC0とを受け、その出力信号をデコーダDC20へ与える。ANDゲートAG22は、デコーダDC21のデコーダ結果とメモリ位置指示信号LC1とを受け、その出力信号をデコーダDC22へ与える。ANDゲートAG23は、デコーダDC22のデコード結果とメモリ位置指示信号LC0とを受け、その出力信号をデコーダDC21へ与える。

ANDゲートAG24は、デコーダDC22のデコード結果とメモリ位置指示信号LC1とを受け、その出力信号をデコーダDC23へ与える。ANDゲートAG25は、デコーダDC23のデコード結果とメモリ位置指示信号LC0とを受け、その出力信号をデコーダDC22へ与える。

ANDゲートAG26は、メモリ位置指示信号LC1とデコーダDC23のデコード結果とを受け、その出力信号をデコードDC24へ与える。ANDゲートAG27は、デコーダDC24のデコード結果とメモリ位置指示信号LC0とを受け、その出力信号をデコーダDC23へ与える。ANDゲートAG28は、デコーダDC24のデコード結果とメモリ位置指示信号LC1とを受け、その出力信号を図示しないデコーダ(DC25)へ与える。ANDゲートAG29は、図示しないデコーダ(DC25)のデコード結果とメモリ位置指示信号LC0とを受け、その出力信号をデコーダDC24へ与える。

デコーダDC20−DC24は、その構成は、先の図7に示す構成におけるメモリセルデコーダDC1−DC3と同様であり、そのプリデコード信号の組が対応のメインビット線を指定するときには、デコード結果をHレベルとし、その両側に配置されたANDゲートの出力信号およびデコード結果のいずれかがHレベルとなると、その出力信号をHレベルに設定する。

メモリ位置指示信号LC1およびLC0は、最下位アドレス信号をプリデコードして生成される。2つの隣接メモリセルのうちの右および左のメモリセルのいずれをアクセスするかが、このメモリ位置指示信号LC0およびLC1により指定される。

電位供給線LBおよびLAへの電位供給およびメインビット線とビット線との接続を制御するために、HBL切換回路HSW11が設けられる。HBL切換回路HSW11は、書込動作時に、電位供給線LAおよびLBに書込電圧を供給する書込電位供給回路46と、読出動作時にこれらの電位供給線LAおよびLBに所定の電位を供給する読出電位供給回路47と、2ビットのアドレス信号AC1およびAC2をデコードして、スイッチ選択線SWL1−SWL4を駆動するデコーダDC30を含む。

書込電位供給回路46は、アドレス信号AC1およびAC2と、フォワード信号FWDと、リバース信号REVと、書込信号WRITEとを受ける。読出電位供給回路47は、アドレス信号AC1およびAC2と、フォワード信号FWVと、リバース信号REVと、読出信号REABとを受ける。

デコーダDC30は、アドレス信号AC1およびAC2に従って、スイッチ選択線SWL1およびSWL2の一方を選択状態、スイッチ選択線SWL3およびSWL4の一方を選択状態へ駆動する。このとき、4本のビット線に対して設けられる2本のメインビット線に、それぞれ、ビット線が1つ接続される。

メインコラム選択スイッチMSC0−MSC4それぞれには、デコーダDC20−DC24の出力信号が与えられる。サブコラム選択スイッチSW47およびSW49には、スイッチ選択線SWL1上のサブコラム選択信号が与えられる。サブコラム選択スイッチSW46およびSW48には、スイッチ選択線SWL2上のサブコラム選択信号が与えられる。スイッチ選択線SWL3上のサブコラム選択信号は、サブコラム選択スイッチSW54、SW56およびSW58へ与えられる。スイッチ選択線SWL4上のサブコラム選択信号は、サブコラム選択スイッチSW53、SW55およびSW57へ与えられる。次に、図11に示すビット線選択回路BS0の動作を、メモリブロックMB0内のメモリセルMC40の記憶領域(左ビット領域)L1にデータを書込む場合の動作について説明する。

まず、読出信号READはLレベルであり、書込信号WRITEがHレベルとなる。読出電位供給回路47は、動作が停止され、一方、書込電位供給回路46が電位供給線LAおよびLBに選択メモリセル位置に応じた書込電圧を供給する。メモリセルMC40の記憶領域L1にHレベルのデータを書込む(プログラムする)ときには、書込電位供給回路46は、電位供給線LAに接地電位GNDを供給し、電位供給線LBに書込電位VCCWを供給する。またデコーダDC30は、アドレス信号AC1およびAC2に従ってスイッチ選択線SWL1およびSWL3にHレベルの信号を伝達する。

スイッチ制御回路34内においては、デコーダDC21が選択されその出力信号がHレベルとなる。デコーダDC21のデコード結果が選択状態を示しており、また、メモリ位置指示信号LC0がHレベルであり、ANDゲートAG21の出力信号がHレベルとなり、応じて、デコーダDC20の出力信号がHレベルとなる。

メインコラム選択スイッチMSC0およびMSC1が、デコーダDC0およびDC21の出力信号に従って導通し、メインビット線MB0およびMB1がそれぞれ電位供給線LBおよびLAに結合される。メインビット線MB0に書込電圧VCCWが供給され、メインビット線MB1に接地電圧GNDが供給される。

スイッチ選択線SWL1およびSWL3がHレベルであるため、サブコラム選択スイッチSW54およびSW47が導通し、メインビット線MB0およびMB1がそれぞれビット線BL3およびBL4に結合され、これらのビット線BL3およびBL4に書込電圧VCCWおよび接地電位GNDが供給される。ビット線BL2は、サブコラム選択スイッチSW46が非導通状態であり、フローティング状態を維持する。

この状態においては、メインセルMC40に接続されるビット線BL3からビット線BL4に電流が流れ、その記憶領域L1にHレベルのデータを書込むことができる(プログラムすることができる)。この場合、ビット線BL2はフローティング状態であり、ビット線BL3の電流がビット線BL2へ流れ込むのを防止することができる。

したがって、同様の動作を行なうことにより、特定のメモリセルに対して書込動作を行なうことができる。書込電位供給回路46において、アドレス信号AC1およびAC2とフォワード信号FWDとリバース信号REVとに従って、電位供給線LAおよびLBの電位を順方向および逆方向のいずれかに設定する。書込電位供給回路46においては、書込データが与えられており、この書込データに従って電位供給線LAおよびLBに書込高電圧を印加するかの判定が行なわれる。Hレベルデータの書込時において書込高電圧が電位供給線LAまたはLBに印加される。

デコーダDC30は、アドレス信号AC1およびAC2に従って、4ビットのメモリセルから1つのメモリセルを選択し、この選択メモリセルが接続する2本のビット線を対応のメインビット線対にそれぞれ接続する。

読出動作時において、メモリセルMC40の記憶領域L1のデータを読出す場合には、ビット線BL4に読出電位VCCRが供給され、ビット線BL3が接地電位に供給保持される。読出電位供給回路47により、読出電圧レベルの電位供給線LAがセンスアンプSA0に結合される。この場合、メモリセルデータの読出を行なうためのメインビット線およびビット線の選択動作は書込時と同じである。

図11に示す構成の場合、メインビット線MBに、電位供給線HBLと同様の機能を持たせることができる。したがって、電位供給線とワード線とを平行に配置するだけでなく、メインビット線を利用して、電位供給線とビット線とを平行に配線することもできる。

メモリブロックにおいて、図11においては、メインビット線/ビット線の階層構造を用いている。しかしながら、ビット線は非階層構造であり、デコーダの動作により選択された4本のビット線を電位供給線により強制的にフローティング状態とする階層デコード構成の場合、ビット線の組がビット線4本で構成され、電位供給線の数は4本であってもよく、また電位供給線の数が6本の場合でも、同様に構成することができる。

したがって、メモリブロックの面積の許容範囲に応じて、電位供給線HBLの配置と、階層デコード方式または階層ビット線構造を適宜決定することができる。これにより、面積利用効率に優れた正確にデータの書込/読出をメモリセルブロック単位で実行することができる半導体記憶装置を実現することができる。

本実施の形態1において、このメモリブロックのデータ書込またはデータ読出時において、別バンクに対してデータアクセスを並行して実行する。

図12は、この発明の実施の形態1に従う不揮発性半導体記憶装置における第1のデータ転送処理態様におけるデータの流れを示す図である。図12においては、バンクBNKAに対してデータ書込を行ない、バンクBNKBにおいてはデータ読出を行なう。これらの動作を並行して実行する。第1のデータ転送処理態様において、バンクBNKAのHBL切換回路HSW0およびHSW1に対して、選択回路9を介して書込データが与えられる。HBL切換回路HSW0およびHSW1は、この書込データと、図示しないアドレス信号およびリバース/フォワード信号および書込指示信号に従って、電位供給バスHB0およびHB1に所定の電圧を供給し、メモリブロックMB0およびMB1の選択メモリセルへ並行してデータを書込む。

メモリブロックMB0からMB3の構成は先に示した構成のいずれが用いられてもよい。従って、電位供給バスHB0からHB3の構成もメモリブロックMB0からMB3の構成に応じて、適当に定められる。

一方、バンクBNKBにおいては、メモリブロックMB2およびMB3に対して、HBL切換回路HSW2およびHSW3により、読出電圧および接地電圧が電位供給バスHB2およびHB3を介して選択メモリセルに供給され、センスアンプSA2およびSA3により、選択メモリセルの記憶データが読出される。選択回路8は、これらのセンスアンプSA2およびSA3の読出データを選択して外部へリードポート5を介して出力する。

メモリブロックMB0−MB3に対し、それぞれセンスアンプSA0−SA3およびHBL切換回路HSW0−HSW3を配置しており、バンク単位でデータの書込およびデータの読出を並行して実行することができる。データ書込に要する時間が長い(たとえばバースト書込などの動作モードで大量のデータを書込む)場合、1つのバンクに対する書込を行なっている際に、別のバンクにアクセスしてデータを読出すことができ、データ処理効率が向上する。

また、ビット単位でデータの書込/読出が行なわれる場合においても、データの書込に要する時間は、絶縁膜に電荷を注入する必要があり、データ読出に要する時間より長い。従って、データ書込を指示するライトコマンドを与えた次のサイクルにおいてデータの読出を指示するリードコマンドを別バンクに与えることにより、ライトコマンド印加時の待ち時間を利用してデータの転送を行うことができ、データ転送効率を改善することができる。

図13は、図12に示す第1のデータ転送処理態様のシーケンスの一例を示す図である。図13において、システムクロックCLKに同期して、コマンドCMDが発行される場合を一例として示す。

サイクル0において、データ読出を示すリードコマンドREが、アドレス信号とともに与えられる。図13においては、バンクアドレスBADDを示す。サイクル0においては、バンクAに対するリードコマンドREが与えられる。バンクBNKAにおいては、リードコマンドREに従ってデータ読出動作が行なわれ、データQ0が出力される。

次のサイクル1において、データ書込を示すライトコマンドWRがバンクBNKBに対して与えられる。今、1例として、このデータ書込は、システムクロックCLKの2クロックサイクル期間必要とされ、またデータ読出は、1クロックサイクルで完了する場合を想定する。この場合、バンクBNKBにおいてサイクル1からサイクル2においてデータの書込が実行される。

サイクル2において、バンクBNKAに対し、データ書込を指示するライトコマンドWRが与えられる。したがって、この場合、バンクBNKAにおいては、リード動作は既に完了しているため、データの書込が実行される。

サイクル3において、バンクBに対するリードコマンドREが与えられる。サイクル3において、バンクBNKBからデータD1が読出される。このサイクル3においては、バンクBNKAにおいてはデータ書込が実行されている。

サイクル4において、バンクBNKAに対しライトコマンドWRが書込データD2とともに与えられ、またサイクル6において、バンクAに対しライトコマンドWRがそれぞれ書込データD2およびD3とともに与えられる。

サイクル7において、バンクBに対しリードコマンドREが与えられ、バンクBNKBにおいてデータ読出が行なわれ、データQ2がバンクBNKBから読出される。このサイクルにおいては、バンクBNKAにおいてはデータ書込が実行されている。

したがって、たとえばデータ書込に2クロックサイクルを要し、データ読出には1クロックサイクルで行なわれる場合、被書込状態のバンクと異なるバンクへリードアクセス(データの読出)を行なうことにより、効率的にデータを外部のプロセッサなどの処理装置との間で転送することができる。

図14は、図5に示すメイン制御回路7の構成の並列アクセスに関連する部分の構成の一例を示す図である。バンクBNKAおよびBNKBにおいては、それぞれ周辺回路2aおよび2bが設けられている。これらの周辺回路2aおよび2bは、先に説明したセンスアンプおよびHBL切換回路を、各メモリブロックごとに含む。周辺回路2aおよび2bは、内部での書込動作の実行中、書込活性化信号WACTAおよびWACTBを活性化する。書込活性化信号WACTAおよびWACTBの活性化中、対応のバンクに対する外部アクセスが禁止される。

これらの書込活性化信号WACTAおよびWACTBは、ポリシリコンフローティングゲートに電荷を蓄積するフラッシュメモリにおいて用いられているステータスレジスタに格納される書込状態指示フラグと同様にして生成されてもよい。また、単に、フリップフロップなどを用いて、バンクに対する書込信号WRITEの活性化に応答して書込完了まで活性状態に維持されてもよい。

メイン制御回路7は、図5に示すコマンド入力回路4aと、コマンドをデコードするコマンドデコーダ60と、コマンドデコーダ60からの動作モード指示信号OPMに従ってリードアドレス信号RADDおよびライトアドレス信号WADDの一方を選択するアドレス選択回路62と、アドレス選択回路62からのバンクアドレス信号BADと書込活性化信号WACTAおよびWACTBに従って、選択バンクへのアクセスの可否を判定する競合回避回路64を含む。

この競合回避回路64は、アクセス可能時においてはイネーブル信号ENAおよびENBを周辺回路2aおよび2bへそれぞれ与える。周辺回路2aおよび2bは、イネーブル信号ENAおよびENBの活性化時、コマンドデコーダ60から与えられるリード信号READ、ライト信号WRITE、リバース信号REV、およびフォワード信号FWDとアドレス選択回路62からのアドレス信号ADDに従ってメモリセルの選択およびデータの書込/読出を実行する。

コマンドデコーダ60へは、制御信号の組合せでコマンドが与えられてもよくまた、リードコマンドREAD、ライトコマンドWRETE、リバース信号REVおよびフォワード信号FWDがそれぞれ個々の信号として与えられてもよい。動作モード指示信号OPMは、データの読出を示すリードモード指示信号およびデータの書込を示すライトモード指示信号を含む。

アドレス選択回路62は、この動作モード指示信号OPMが指定する動作モードに応じたアドレス信号を、リードアドレス信号RADDおよびライトアドレス信号WADDから選択する。

この図14に示すメイン制御回路7の構成において、書込動作が行なわれているバンクに対するアクセスが禁止され、正確にデータ書込動作およびデータ読出動作を並行して実行することができる。

なお、この図14に示すメイン制御回路7の構成においては、コマンドデコーダ60がデータ書込モードおよびデータ読出モードに対して共通に設けられている。しかしながら、コマンドポートをリードポートおよびライトポートそれぞれに対応して設けた場合、同一サイクルに、リードコマンドおよびライトコマンドを異なるバンクBNKAおよびBNKBに対して並行して与えることができる。この構成の場合には、競合回避回路64において、同じサイクルにおいて与えられたリードアドレスおよびライトアドレスが異なるバンクを示していることを検出し、かつ各バンクがアクセス可能(書込活性化信号WACTの非活性状態)のときに、周辺回路を活性化する。ただし、この場合には、内部のコマンドを伝達する信号配線を、リードポート用およびライトポート用それぞれに設ける必要があり、図14に示す構成に比べて配線レイアウト面積が増大する。

図15は、この発明の実施の形態1に従う不揮発性半導体記憶装置における第2のデータ転送処理態様を示す図である。図15に示すデータ転送処理においては、バンクBNKAからデータQが読出され、かつバンクBNKAのメモリブロックMB0およびMB1から読出されたデータビットが、並行してバンクBNKBに転送されて書込まれる。

すなわち、バンクBNKAのメモリブロックMB0およびMB1それぞれに対して設けられたセンスアンプSA0およびSA1の出力する内部読出データが転送スイッチ回路TX0およびTX1のリード転送スイッチTXRを介して双方向データ転送線BTX0およびBTX1上に転送される。双方向データ転送線BTX0およびBTX1に転送されたデータは、転送スイッチ回路TX2およびTX3がライト転送スイッチTXWを介してHBL切換回路HSW2およびHSW3へそれぞれ与えられる。

HBL切換回路HSW2およびHSW3は、転送されたデータに従ってメイン供給バスHB2およびHB3へ書込データおよび選択メモリセルの位置に応じた電位を供給し、メモリブロックMB2およびMB3の選択メモリセルに転送データを書込む。この場合、アドレス信号としては、読出データと同一の内部アドレス信号が書込アドレス信号として用いられるても良く、また、転送動作時においては、リード/転送コマンドと同時に与えられるライトアドレス信号を、転送先アドレスとして用いてもよい。

この図15に示すデータ転送処理態様においては、バンクBNKAのデータを外部へ読出すと同時にバンクBNKBに退避させる。この場合、内部でデータの転送を行なってデータ退避を行なっており、外部へ一旦読出した後、再び外部から書込データを与えて退避させる必要はなく、処理効率が向上する。

また、ある処理シーケンスにおいて、バンクBNKAから読出したデータを外部の処理装置で加工し、加工後のデータをバンクBNKAの元の位置に書込みその後再び加工前のデータを用いて処理を行なう場合、バンクの切換だけで効率的に処理を行なうことができる。たとえば画像処理において、画像を重ね合わせるαブレンド演算などの処理を効率的に行なうことができる。

バンクBNKAからのデータ読出と並行してバンクBNKBにこの読出データを転送して書込む場合、書込時間がデータ読出時間よりも長いため、転送データを順次保持し、この保持転送データに従って書込を実行する。1つのバンクからデータを他方のバンクに転送させて退避させ、同一データを異なるバンクに位置付ける。この後、これらのバンクに対しデータの読出および書込を並行して行なうことにより、同一バンクに対するデータの書込および読出を等価的に同時に実行することができる。

図16は、この発明の実施の形態1における第3のデータ転送処理態様を概略的に示す図である。図16に示すデータ転送処理態様においては、バンクBNKAへのデータ書込時、この書込データをバンクBNKBに転送してバンクBNKBのメモリブロックMB2およびMB3にそれぞれ書込む。

すなわち、選択回路9から転送された書込データが、バンクBNKAに対して設けられたHBL切換回路HSW0およびHSW1に転送されて、メモリブロックMB0およびMB1に書込まれる。この選択回路9から転送された書込データは、転送スイッチ回路TX0およびTX1に含まれるライト転送スイッチTXWを介して双方向データ転送線BTX0およびBTX1上に転送される。この双方向データ転送線BTX0およびBTX1上の書込データは、転送スイッチ回路TX2およびTX3に含まれるライト転送スイッチTXWを介してHBL切換回路HSW2およびHSW3に与えられる。

HBL切換回路HSW2およびHSW3が、転送モード時活性化され、与えられたデータおよびアドレス信号に従って電位供給バスHB2およびHB3を駆動し、メモリブロックMB2およびMB3に転送データを書込む。転送先を指定するアドレスとしてはライトポートに与えられたアドレスが用いられる。この場合、バンクBNKAおよびBNKBの同一アドレスに同じデータが書込まれる。

したがって、第3のデータ転送処理態様においては、バンクBNKAおよびBNKBにおいては、同じデータが書込まれる。したがって、バンクBNKAおよびBNKBの一方にデータ書込が行なわれている場合、他方バンクからデータを読出すことができ、例えば、キャッシュメモリにおけるコピーバック動作時に、必要なデータを高速で転送することができる。

また、転送先のバンクをバックアップメモリとして利用することもできる。

図17は、第4のデータ転送処理態様を概略的に示す図である。この図17に示すデータ処理転送態様においては、内部でバンクBNKBからバンクBNKAへデータが転送されて格納される。すなわち、バンクBNKBにおいてメモリブロックMB2およびMB3の選択メモリセルの記憶データが、センスアンプSA2およびSA3により検出されて転送スイッチ回路TX2およびTX3へ与えられる。転送スイッチ回路TX2およびTX3において、リード転送スイッチTXRにより、これらのセンスアンプSA2およびSA3から読出されたデータが、双方向データ転送線BTX0およびBTX1上に伝達される。

図17は、第4のデータ転送処理態様を概略的に示す図である。この図17に示すデータ処理転送態様においては、内部でバンクBNKBからバンクBNKAへデータが転送されて格納される。すなわち、バンクBNKBにおいてメモリブロックMB2およびMB3の選択メモリセルの記憶データが、センスアンプSA2およびSA3により検出されて転送スイッチ回路TX2およびTX3へ与えられる。転送スイッチ回路TX2およびTX3において、リード転送スイッチTXRにより、これらのセンスアンプSA2およびSA3から読出されたデータが、双方向データ転送線BTX0およびBTX1上に伝達される。

この双方向データ転送線BTX0およびBTX1に与えられたデータは、転送スイッチ回路TX0およびTX1に含まれるライト転送スイッチTXWを介してHBL切換回路HSW0およびHSW1へ与えられる。HBL切換回路HSW0およびHSW1は、図示しないアドレス信号および転送データに従って対応の電位供給バスHB0およびHB1の電圧レベルを設定し、メモリブロックMB0およびMB1の選択メモリセルにデータを書込む。

バンクBNKAからバンクBNKBへのデータ転送は、上述のデータの流れを逆にして行なわれる。内部で、バンク間でデータを転送しており、外部へ一旦データを読出してから別バンクへ書込む必要がなく、データの退避を行なう場合に有効である。また、バンクBNKAおよびBNKB間のデータ転送が内部で実行され、外部のバスは用いられない。したがって、外部のバスに接続する他のデバイスの動作と並行して内部データ転送を行なうことができる。

図18は、メモリブロックMB0に対して設けられる転送スイッチ回路TX0の構成の一例を概略的に示す図である。転送スイッチ回路TX0は、センスアンプSA0に結合されるリード転送スイッチTXRと、HBL切換回路HSW0に結合されるライト転送スイッチTXWを含む。

リード転送スイッチTXRは、データ転送元指示信号SOURCEAの活性化に応答して活性化され、センスアンプSA0からのデータを双方向データ転送線BTX0に転送するトライステートバッファ80aを含む。センスアンプSA0の処理データは、選択回路9に含まれるトライステートバッファ回路89aへ与えられる。トライステートバッファ回路89aは、読出信号READAの活性化に応答して、センスアンプSA0の出力データをバッファ処理してリードポート5へ与える。読出信号READAは、バンクBNKAに対するリードコマンドが与えられたときに活性化される。データ転送元指示信号SOURCEAはバンクBNKAからバンクBNKBへデータを転送するときに活性化される。

ライト転送スイッチTXWは、データ転送先指示信号DESTIAの活性化に応答して双方向データ転送線DTX0上のデータを転送するトライステートバッファ82aと、トライステートバッファ82aの出力データを順次格納するファーストイン・ファーストアウト(FIFO)84aを含む。このFIFO84aの出力データは、HBL切換回路HSW0へ与えられる。HBL切換回路HSW0に対しては、またアドレスFIFO86aが設けられる。アドレスFIFO86aは、FIFO84aに格納されるデータそれぞれに対するアドレスを格納する。FIFO84aおよびアドレスFIFO86aを利用することにより、データ書込に長時間を要し、転送データが与えられる周期とデータ書込の周期が異なる場合に、転送データをバッファ処理して対応のメモリセルへ書込む。これにより、内部データ転送を、書込および読出の周期が異なる場合においても、外部アクセスに悪影響を及ぼすことなく行うことができる。

HBL切換回路HSW0には、選択回路8のトライステートバッファ回路88aの出力データがまた与えられる。このトライステートバッファ回路88aは、書込信号WRITEAの活性化に応答して活性化され、ライトポート6(図5参照)から与えられるデータをバッファ処理してHBL切換回路HSW0に転送する。ライト信号WRITEAは、バンクBNKAに対するライトコマンドが追加されたときに活性化される。

図19は、メモリブロックMB2に対して設けられる転送スイッチ回路TX2の構成を示す図である。この転送スイッチ回路TX2において、リード転送スイッチTXRは、データ転送元指示信号SOURCEBの活性化に応答して活性化され、センスアンプSA2の出力データをバッファ処理して双方向データ転送線BTX0に転送するトライステートバッファ80bを含む。データ転送元指示信号SOURCEBは、バンクBNKBからバンクBNKAへデータを転送するときに活性化される。

この転送スイッチ回路TX2のライト転送スイッチTXWは、データ転送先指示信号DESTIBの活性化に応答して双方向データ転送線BTX0上の信号をバッファ処理するトライステートバッファ82bと、トライステートバッファ82bの出力データを順次格納するFIFO84bを含む。データ転送先指示信号DESTIBは、バンクBNKBに対しデータの転送が行なわれるときに活性化される。このFIFO84bに対応して、HBL切換回路HSW2に対し、アドレスFIFO86bが設けられ、FIFO84bの格納データのアドレスが順次与えられる。

センスアンプSA2は、選択回路9に含まれるトライステートバッファ回路89bにその出力データを与える。トライステートバッファ回路89bは、読出信号READBの活性化に応答して活性化され、センスアンプSA2の出力データをバッファ処理してリードポート5へ与える。

読出信号READBは、バンクBNKBのデータ読出動作の活性化時、活性化される。すなわち、バンクBNKBに対してリードコマンドが与えられたときに活性化される。

HBL切換回路HSW2は、選択回路8に含まれるトライステートバッファ回路88bの出力データを受ける。このトライステートバッファ回路88bは、書込信号WRITEBの活性化に応答して活性化され、ライトポート6から与えられたデータをバッファ処理してHBL切換回路HSW2へ与える。書込信号WRITEBは、バンクBNKBに対するライトコマンドが与えられたときに活性化され、また、バンクBNKBに対するデータ転送および転送データの書込が行なわれるときに活性化される。

なお、この図18および図19に示す構成においては、トライステートバッファ回路88aおよび88bはライトポートに結合される選択回路8に含まれ、トライステートバッファ回路89aおよび89bはリードポートに結合される選択回路9に含まれている。しかしながら、これらのトライステートバッファ回路88aおよび88bは、選択回路8の外部に設けられ、選択回路8がトランスミッションゲートで構成されてもよい。同様、選択回路9も、トランスミッションゲートで構成され、これらのトライステートバッファ回路89aおよび89bが、バスドライバとして用いられてもよい。

図18および図19に示す読出信号READA、READBと、データ転送元指示信号SOURCEA、SOURCEBと、データ転送先指示信号DESTIBおよびDESTIAは、図5に示すメイン制御回路7から生成され、その基本的な構成としては先の図14に示す構成を用いられて、バンクに対するデータの書込、読出およびデータ転送が制御される。

図20は、バンク間データ転送を実現するメイン制御回路の処理内容を示す図である。メイン制御回路(図5に示すメイン制御回路7)は、コントローラなどの処理装置で構成され、個々の処理に応じた専用のロジック回路は用いられないため、図20においては、各処理内容をブロックで示す。

図20において、メイン制御回路は、動作モード指示が与えられると外部からのリードアドレスおよびライトアドレスからバンクアドレスを抽出するリードバンクアドレスの抽出処理SP1aおよびライトバンクアドレス抽出処理SP1bを行なう。また、この動作モードが与えられると、与えられた動作モードが読出モードであるのか書込モードであるのかを検出するため、それぞれリードコマンド(RE)の抽出処理SP2aおよびライトコマンド(WR)の抽出処理SP2bを実行する。同時に、外部からのコマンドに従って転送コマンドが与えられたか検出する(処理SP3)。

処理SP1aおよびSP2aの処理結果に従って、リードバンクアドレスおよびリードコマンドに従ってデータ読出を行なうリードバンクを検出する(処理SP4a)。また、処理SP1aにより抽出されたライトバンクアドレスと処理SP2bにより抽出されたライトコマンドWRとに従ってライトバンクの検出処理を行なう(SP4b)。これらの検出処理SP4aおよびSP4bにおいては、転送コマンドが印加されている場合には、検出されたコマンドとバンクアドレスとにしたがって、転送元のバンクおよび転送先のバンク、すなわちリードバンクおよびライトバンクが設定される。

リードバンクが検出された場合には、バンク書込活性化信号WACTAおよびWACTBの活性/非活性化に従って、アクセス競合が生じない場合、このデータ読出が指定されたバンクに対する読出信号READAまたはREADBを活性化する(処理SP6)。また、処理SP4bの処理結果に従って、選択バンクに対して書込が可能な場合に、指定されたバンクに対する書込信号WRITEAまたはWRITEBを活性化する(処理SP7)。

この書込時において、選択バンクが書込状態にある場合においては、書込データを書込データ専用のデータレジスタに格納してもよい。アドレス信号は図19および20に示すアドレスFIFOに格納する。データ専用のレジスタを、転送データ格納用のFIFOと共有してもよい。トライステートバッファ回路88aの出力とトライステートバッファ82aの出力を共通にFIFOに結合する。同様、トライステートバッファ回路88bの出力とトライステートバッファ82Bの出力を共通にFIFOに結合する。通常のデータ書込時においてバースト書込を実現することができる。

一方、処理SP2aおよびSP2bの処理結果に従って、リードコマンドのみが印加されたかの検出処理SP5a、ライトコマンドのみが印加されたかの検出処理SP5b、およびリードコマンドおよびライトコマンドの両コマンド印加なしの検出処理SP5cが実行される。これらの処理SP5a−SP5cの処理結果に従って、処理SP1aおよびSP1bにおいて検出されたバンクアドレスの選択処理SP8が行なわれる。

リードコマンドのみが印加されている場合には、処理SP5aの処理結果に従ってリードバンクアドレスが検出される。一方、ライトコマンドのみが印加されていると、処理SP5bにおいて検出された場合には、ライトバンクアドレスが選択される。一方、リードコマンドおよびライトコマンドの両コマンドが印加されていないことが検出された場合には、リードバンクアドレスが選択される。これは、外部の仕様において、内部転送時においては、リードアドレスポートのアドレスを転送元アドレスに設定するためである。この場合には、ライトポートのアドレスポートに、転送先のアドレスが設定される。

選択処理SP8の選択結果に従って、転送を行なう可能性があるアドレスを転送アドレスとして設定する処理SP9が行なわれる。次いで、処理SP3の処理結果に従ってデータ転送が行なわれる場合には、処理SP9において設定された転送アドレスを転送元アドレスとして設定する(処理SP10)。転送指示が印加されていない場合には、転送元アドレスの設定は行なわれず、転送動作は行なわれない。

処理SP10において転送元アドレスの設定が行なわれると、転送元アドレスに基いて、転送先指示信号SOURCEAおよびSOURCEBが選択的に活性化される(処理SP11)。一方、バンクは、バンクBNKAおよびBNKBの2つであるため、この転送元アドレスを反転することにより、転送先アドレスが設定される(処理SP10)。この処理SP10により、転送先バンクが設定され、処理SP10の処理結果に従って、転送先指示信号DESTIAまたはDESTIBが選択的に活性化される(処理SP12)。

転送コマンドが印加されたことが検出された場合には、処理SP4aおよびSP4bは、処理SP2aおよびSP2bの処理結果にかかわらず、処理SP1aおよびSP1bの処理結果に基づいてリードバンクおよびライトバンクを検出する。外部からリードコマンドと転送コマンドが与えられた場合、この転送先のバンクをライトアドレスポートに設定することにより、ライトバンク検出処理SP4bにおいて転送先のバンクを検出でき、正確に書込信号WRITEAまたはWRITEBを活性化することができる。また、ライトコマンドと転送コマンドのみが与えられた場合には、同様、リードアドレスポートに、転送先アドレスを設定することにより、この処理SP3の処理結果に従ってリードバンク検出処理SP4aを行なって、転送先のバンクを正確に検出することができる。

リードコマンドと転送コマンドが同時に印加される場合には、ライトアドレスポートに転送先アドレスを設定し、またライトコマンドと転送コマンドが印加される場合には、リードアドレスポートに、転送先アドレスを設定する。これにより、転送先のバンクの所望のアドレス領域にデータを転送することができる。しかしながら、このバンクへの書込または読出の内部データ転送を行なう場合、この書込または読出ポートに対してのみ、データおよびアドレスを設定することにより、バンクBNKAおよびBNKBの同一アドレス間で内部転送を行なうこともできる。以下この構成について簡単に説明する。

図21は、このメイン制御回路の処理回路を概略的に示す図である。この図21においては、先の図20に示す処理シーケンスに加えて、さらに、リードのみ指示の検出を行なう処理SP5aと転送コマンド印加を検出する処理SP3の処理結果に従って、リードコマンドおよび転送コマンド両者が印加されたと判定する処理SP20と、この処理SP20の判定結果が、リードコマンドおよび転送コマンド両者の印加を示しているときには、リードバンク検出処理SP4aにより設定されたリードバンクアドレスを反転する反転処理SP21が設けられる。この場合、ライトバンク検出処理SP4bにおいては、反転処理SP21の処理結果に基づいてライトバンクを設定する。

このメイン制御回路は、さらに、処理SP5bおよびSP3の処理結果に従って、ライトコマンドおよび転送コマンド両者が印加されたかを判定する判定処理SP22と、この判定処理SP22の判定結果が、ライトコマンドおよび転送コマンドが与えられたことを示している場合には、処理SP4bにより設定されたライトバンクアドレスを反転する処理SP23が実行される。この場合には、リードポートには、リードアドレスが与えられていないため、リードバンク検出処理SP4aにおいては、反転処理SP23の処理結果に従ってリードバンクが設定される。

このリードバンク検出処理SP4aおよびライトバンク検出処理SP4bにより、バンクが設定されたとし、図20に示す処理SP6およびSP7に従って読出信号READA/READBおよびWRITEA/WRITEBが選択的に活性化されて、データの書込/読出および内部転送が実行される。これにより、内部転送モード時および書込/内部転送モード時および読出/内部転送モード時において、外部からアクセスされるバンクに対してのみポートを用いてアクセスすることができ、内部転送モード時において、使用ポートを統一することができ、転送処理が容易となる。

図22は、バンクBNKAおよびBNKBに対するリードアドレスおよびライトアドレスを転送する処理を示す図である。図22において、破線ブロック内の処理がメイン制御回路において実行され、この破線ブロック外部の処理は、バンクの周辺回路で実行される。

図22において、メイン制御回路においては、まずリードアドレスの検出処理(SP30)およびライトアドレスの検出処理(SP32)が実行される。リードのみ指示の検出処理SP5aと転送コマンド印加の検出処理SP3の処理結果に従って、処理SP20において、リードコマンドのみと転送コマンドが印加されたかの判定が行なわれる。この判定処理SP20において、リードコマンドと転送コマンドが印加されたと判定されると、処理SP30において抽出されたリードアドレスが、ライトアドレスとして転送される。

処理SP22において、処理SP3が転送コマンドの印加を示し、また処理SP5bにおいてライトコマンドのみが印加されたことが検出されると、処理SP32により検出されたライトアドレスを、リードアドレスとして転送する。

したがって、この構成の場合には、転送動作時において各バンクに転送されるライトアドレスおよびリードアドレスは、同じアドレスとなる。

データアクセスが行なわれず、内部転送のみが指示された場合には、図20に示す処理にしたがってリードバンクおよびライトバンクが決定される。

バンクBNKAおよびBNKBの周辺回路において、このアドレスを選択する処理が実行される。まず処理SP40において、読出動作が指定されているか書込動作が指定されているかの判定が行なわれる。これは、読出信号READA(READB)およびWRITEA(WRITEB)のいずれが活性状態にあるかを見ることにより判定される。この処理SP40における判定結果に従って、ライトアドレスおよびリードアドレスの一方が選択される(選択処理SP42)。したがって、対応のバンクに対して読出信号READA(READB)が活性状態にある場合には、リードアドレスが、この処理SP40により選択され、書込信号WRITEA(WRITEB)が活性状態にある場合には、ライトアドレスが選択処理SP42により選択される。この選択処理SP40により選択されたアドレスは、対応のアドレスFIFOへ順次格納される(処理SP44)。この対応のアドレスFIFOにおいて空状態であるかをモニタし、書込活性化信号WACTA(WACTB)の活性/非活性の制御処理が実行される(処理SP46)。

内部転送コマンドの印加時において、転送元のバンクは、リードポートにアドレスにより設定され、リードバンクが設定される。従って、この場合には、処理SP33において、転送コマンドのみが印加され、ライトコマンドおよびリードコマンドが印加されない場合に、リードアドレスがライトアドレスバスにも転送される。処理SP5cと処理SP3の論理積の処理と処理SP20の論理和処理により、処理SP33のアドレス転送処理を実行する。

これらの処理により、リードコマンドおよび転送コマンドの印加時およびライトコマンドおよび転送コマンドの印加時および内部転送コマンド印加時において、1つのポートに与えられるアドレスを用いて内部転送用のアドレスを生成して、書込/読出を実行することができる。

なお、リードコマンドが印加されている場合には、アドレスFIFOにリードアドレスが格納される。しかしながら、アドレスFIFOは、先入・先出であり、1つのリードアドレスしか与えられない場合においても、即座に読出されて対応のHBL切換回路HSWへリードアドレスを与えることができる。

以上のように、この発明の実施の形態1に従えば、バンク間で内部データ転送を行なうことができるように構成しており、また、読出ポートおよび書込ポートを別々に設けており、バンクそれぞれに読出動作および書込動作を並行して行なうことができる。また内部データ転送と組合せることにより、効率的なデータ転送を実現することができ、システムのアプリケーションに応じたデータ記憶を実現することができる。

[実施の形態2]

図23は、この発明の実施の形態2に従う不揮発性半導体記憶装置のデータおよびアドレス入力部の構成を概略的に示す図である。この図23に示す構成においては、リードポート5およびライトポート6に共通にアドレス/データ入力ポートが設けられる。すなわち、アドレス入力ポート100にアドレス信号ADDが与えられ、データ入力ポート102にデータDQが与えられる。

図23は、この発明の実施の形態2に従う不揮発性半導体記憶装置のデータおよびアドレス入力部の構成を概略的に示す図である。この図23に示す構成においては、リードポート5およびライトポート6に共通にアドレス/データ入力ポートが設けられる。すなわち、アドレス入力ポート100にアドレス信号ADDが与えられ、データ入力ポート102にデータDQが与えられる。

リードポート5は、このアドレス入力ポート100からのアドレスをデータ読出モード時に取込み内部読出アドレス信号RADDを生成するリードアドレス入力回路5aと、データ入力ポート102へ、図6に示す選択回路8からのデータを出力するデータ出力回路5bを含む。

ライトポート6は、ホールド指示信号WHLDの活性化時、アドレス入力ポート100からのアドレスを取込みラッチし、内部書込アドレス信号WADDを生成するアドレスラッチ104と、ホールド指示信号WHLDの活性化時データ入出力ポート102からのデータをラッチし、ラッチデータを選択回路9へ与えるデータラッチ106を含む。これらのアドレスラッチ104およびデータラッチ106がラッチ状態のときには、外部のアドレスバスおよびデータバスから、これらの書込に関連するアドレスおよびデータは分離される。

ライトポートをラッチ状態にするために、書込/読出並列実行指示RWPLを生成するコマンドレジスタ108と、このコマンドレジスタ108からの指示RWPLとコマンド入力回路からの書込動作モード指示信号(またはライトコマンド)WRとに従ってホールド指示信号WHLDを生成するライトホールド処理部110が、メイン制御回路7内に設けられる。ライトホールド処理部110は、書込/読出並列実行指示RWPLの活性化時ライトコマンドWRが与えられるとホールド指示信号WHLDを生成する。このホールド指示信号WHLDが活性状態の間、書込信号WRITEを活性状態に維持し、また新たなライトコマンドWRの受付を禁止する。この新たなライトコマンドWRの受付禁止は、コマンド入力回路からのコマンドをデコードするコマンドデコーダの出力信号において、書込動作モード指示信号WRを、このホールド指示信号WHLDの活性状態の間または書込信号WRITEの活性状態の間強制的に非活性状態に維持することにより実現される。

コマンドレジスタ108は、コマンドレジスタセットモードコマンドと特定のアドレス信号ビットとに従って、その内容のセット/リセットが実行される。したがって、このコマンドレジスタ108を利用する場合には、リードコマンドおよびライトコマンド印加時と異なるサイクルにおいて、書込/読出並列実行指示を設定するコマンドが印加される。しかしながら、これに代えて、書込を指示するライトコマンドとして、この書込/読出並列実行指示を示す専用のコマンドが用いられてもよい。その場合には、コマンドレジスタ108は特に用いる必要がない。ライトホールド処理部110において、書込/読出並列実行機能付きライトコマンドが印加されると、ホールド指示信号WHLDを活性状態に設定する。しかしながら、コマンドレジスタを、この並列実行機能つきライトコマンドが印加されたときにセットしてもよい。この場合、書込動作が完了すると、コマンドレジスタがリセットされる構成とされてもよく、また、コマンドレジスタリセット用のコマンドが印加されてもよい。

この図23に示す構成の場合、データの書込にデータ読出に比べて長時間を要する場合、データ書込/ライトコマンド印加も、書込に関連する経路を外部のバスから分離する。したがってこの場合、ライトコマンドが印加された次のサイクルでリードコマンドを印加し、書込が行なわれているバンクと異なるバンクに対し、リードアクセスを行なうことができる。

この図23に示す構成の場合、リードポートおよびライトポートに共通にアドレス入力ポート100およびデータ入出力ポート102を設けており、リードポートおよびライトポートそれぞれ別々に、アドレス入力ポートおよびデータ入出力ポートを設ける構成に比べて外部バスに結合されるポート数を低減することができ、面積を低減することができる。

図23に示す構成の他の構成は、図5に示す構成と同じである。ポートの共有以外、データの転送およびデータアクセスを行う構成は同様である。

図24は、図23に示す構成におけるメイン制御回路7の動作を示すフロー図である。以下、図24を参照して、この図23に示す構成におけるメイン制御回路7の動作について説明する。

まず、メイン制御回路7において、コマンド入力回路の出力をモニタし、ライトコマンドが印加されたかを判定する(ステップST1)。ライトコマンドが印加されていない場合において、動作モード指示が与えられている場合には、リードコマンドまたは内部転送コマンドが印加されている状態であり、与えられたコマンドに従った動作が実行され、ライトコマンドの印加をモニタする。

ライトコマンドが印加されると、次に、コマンドレジスタ108において、書込/読出並列実行指示が設定されているかの判定を行なう。この場合、コマンドレジスタ108において、ライトコマンド印加前に、書込/読出並列実行の設定を行なう場合には、コマンドレジスタモードセットコマンドおよび特定のアドレスビットを用いて書込/読出並列実行が指定される。また、並列実行機能つきライトコマンドの場合には、コマンドのデコード結果に従って書込/読出並列実行の指示の判定を行う。

この書込/読出並列実行処理が指定されていない場合には、ライトホールド処理部110においては、ラッチ信号は生成せず、書込信号WRITEを活性化して、通常のデータ書込動作を実行する(ステップST3)。このときに、データ転送が指示されている場合には、書込データの内部転送および書込が、実施の形態1と同様にして実行される。

一方、コマンドレジスタ108において書込/読出並列実行処理が設定されている場合または、コマンドにより書込/読出並列実行が指定されている場合には、ライトホールド処理部110は、ホールド指示信号WHLDを活性状態に設定し、アドレスラッチ104およびデータラッチ106をラッチ状態に設定し、アドレス入力ポート100からのアドレス信号およびデータ入出力ポート102からのデータをそれぞれアドレスラッチ104およびデータラッチ106にラッチさせる。

また、ライトホールド処理部110は、そのホールド指示信号WHLDの活性化に伴って、書込信号WRITEを活性状態に維持し、また新たなライトコマンドの受付を禁止する(ステップST4)。したがって、このホールド指示信号WHLDが活性状態に設定されている場合には、内部で2バンクが設けられている場合においても、1つのバンクに対し書込動作を行なっている間、別バンクに対し外部からデータ書込を行なうことはできない。別バンクに対して外部からリードアクセスのみを行なうことができる。内部でのバンク間データ転送を行うことはできる。

次いで、アドレスラッチ104およびデータラッチ106に格納されたアドレス信号およびデータに従ってデータ書込を実行する(ステップST5)。次いで、書込時において所定の条件が成立したかの判定が行なわれる(ステップST6)。この所定の条件としては、データ書込時、書込活性化信号WACTが非活性状態に移行したかの判定、または所定のクロックサイクル期間が経過したかの判定またはコマンドレジスタ108のリセットのいずれであってもよい。データ書込時において、この所定条件が成立するまで、ライトポート6はラッチ状態を維持する。所定条件が成立すると、ライトホールド処理部110からのホールド指示信号WHLDが非活性状態とされ、アドレスラッチ104およびデータラッチ106はラッチ状態から解放される(ステップST7)。また、新たなライトコマンドWRの受付が許可される。

このステップST1からST7の一連の処理において、データ書込が完了する。したがって、データの書込時において、この書込を行なうバンクを外部バスから切離すことにより、別バンクに対し、リードアクセスを行なうことができ、アドレスおよびデータの入出力ポートを書込および読出両者に対し共通化しても、高速で、処理を行なうことができる。

また、並列実行機能付きライトコマンドを専用に設けた場合、連続的にライトコマンドを与えて書込データを、実施の形態1において示すアドレスFIFOに格納し、最終のライトコマンドとして、この並列実行処理機能付きライトコマンドを印加して、書込バンクを外部バスから分離することにより、効率的に、データの書込をバースト的に行ない、その間、別バンクに対しデータの読出を行なうことができ、データのバースト転送を行なうことができる。このバースト書込時において、コマンドレジスタ108において、バースト書込を行なう際のビット数を設定し、ライトホールド処理部110において、データビット数をカウントし、そのカウント値が設定されたバースト長に一致したときに、ホールド指示信号WHLDを活性状態に設定する構成が用いられてもよい。

また、各バンクの周辺回路において書込アドレス信号および書込データをラッチするラッチ回路を設けておけば、通常のデータ書込モードで連続的に交互にバンクBNKAおよびBNKBへデータの書込を行なうことができる。また、この書込時にラッチ回路を利用して、異なるバンクへ交互にデータ書込を行なう場合には、以下の構成が用いられればよい。バンクの周辺回路すなわちHBL切換回路において、書込アドレスおよび書込データをラッチするラッチ回路を設ける。メイン制御回路7において、1つのバンクに対する書込データ時において、別バンクに対するデータ書込が指示された場合には、このアドレスラッチ104やデータラッチ106へ、新たなデータおよびアドレス信号のラッチを行なわせる。これにより、2つのバンクで、それぞれの周辺回路のラッチ回路にラッチされたアドレス信号および書込データを用いて書込/読出を行なうことができる。このラッチ回路に代えてデータ転送用に準備されたデータFIFOおよびアドレスFIFOが用いられてもよい。

以上のように、この発明の実施の形態2に従えば、データ書込時においては、データ書込バンクを外部バスから分離しており、アドレスポートおよびデータポートをデータ書込およびデータ読出に共通に配置する構成においても、書込コマンド印加の次のサイクルでリードコマンドを印加して別バンクからデータの読出を行なうことができ、効率的なデータ転送を行なうことができる。また、アドレスポートおよびデータポートが書込および読出に対し共通化されており、外部バスのレイアウト面積を低減することができる。

なお、不揮発性半導体記憶装置としては、ゲート下の絶縁膜に電荷をトラップする絶縁膜電荷トラップ型メモリセルを示している。しかしながら、この不揮発性メモリセルの構造としては、相変化メモリ、強誘電体メモリおよび磁気メモリセルなどの他のメモリセル構造が用いられてもよい。

また、絶縁膜電荷とラップ型メモリセル構造において、メモリセルトランジスタは、PチャネルトランジスタおよびNチャネルトランジスタのいずれであってもよい。

また、1つのバンクにおいて、2つのメモリブロックが用いられる場合を一例として示している。しかしながら、1つのバンクに含まれるメモリブロックの数は、3以上であってもよい。各メモリブロックに対して、センスアンプおよびHBL切換回路を個々に設け、メモリブロックそれぞれにおいて同時にデータの書込/読出を実行する。

また、リードポートおよびライトポート両者を用いてデータ転送先およびデータ転送元を指定する構成を利用することにより、バンクの数を3以上に容易に拡張することができる。

以上のように、この発明に従えば、1つのメモリバンクにおいて複数のメモリブロックを設け個々にメモリブロックに対してデータアクセスを行ない、かつバンクに対し並行して、書込および読出を行なえるように構成しており、データ転送を効率的に行なうことができる。

また、バンクに共通に内部バスを、内部データ読出バスおよび内部データ書込バスと別に設けており、内部でバンク間でデータの転送を行なうことができる。

複数の不揮発性メモリブロックそれぞれに対応して書込/読出を行なうための電圧を伝達するローカルバスを配置し、またこれらの複数のメモリブロックに共通にメモリブロック間でデータ転送を行なうためのデータ転送バスを配置することにより、1つのメモリブロックへのデータアクセスと並行して、メモリブロック間でのデータ転送を行なうことができ、効率的なデータ転送を行なう半導体記憶装置を実現することができる。

また、各メモリブロックに対応して、ローカルバスの信号線の電圧を設定する電圧供給制御回路と、ローカルバスの選択された信号線のデータを検知して内部読出データを生成する内部読出回路と、ローカルバスの各信号線を各メモリブロックの選択ビット線に結合する構成を配置することにより、メモリブロック単位でデータの書込/読出を行なうことができ、複数ビットデータの書込/読出を行なうことができ、データ転送効率を改善することができる。

また、この複数のメモリブロック間に共通に配置されるデータ転送バスを各メモリブロックの電圧制御回路に結合することにより、容易に、1つのメモリブロックから別のメモリブロックへのデータ転送を行なって、別のメモリブロックにおいてデータの書込/読出を行なうことができる。

また、メモリブロックを複数のメモリ群に分割し、各メモリ群単位で個々に独立に動作させることにより、1つのメモリ群へのデータ書込時、別のメモリ群からデータの読出を行なうことができ、アクセス効率を改善するとこができる。

また、内部で、データ転送方向を決定して転送先および転送元情報を生成し、その転送先および転送元情報に従ってデータ転送バスとローカルバスの間で転送転送を行なうことにより、内部で正確にデータ転送を行なうことができる。

また、メモリブロックを複数メモリ群に分割し、メモリ群間でデータ転送を行なうことにより、1つのメモリ群へのアクセス時、他方のメモリ群へデータを待避させることができ、データの処理効率が改善される。

なお、バーチャルGNDアレイ構成の複数のメモリブロックに対してそれぞれローカルバスを配置し、各メモリブロック個々に、ローカルバスの電圧供給、データの内部読出、および対応のローカルバスの各信号線とメモリブロックのビット線との結合を行なうことにより、各メモリブロックにおいて並行してデータアクセスを行なうことができ、複数ビットデータの書込/読出を行なうことができる。

また、ブロック間でデータ転送を行なわせるこにとより、データアクセスと並行してデータ転送を別のメモリブロックに行なうことができ、データの退避などの処理を行なうことができ、データ処理効率を改善することができる。

また、特定の動作モード時においては、外部からの書込データおよび書込アドレス信号を取込み保持し、この保持アドレスおよび保持書込データを外部信号線から分離することにより、書込に時間が要する場合においても、書込動作と並行して、外部からデータ読出を指示して実行することができる。

この保持状態を、書込データの書込動作が完了するまで、維持することにより、ポートが共有される場合においても、別バンクに対してリードアクセスを行うことができる。

また、データ書込を指示するライトコマンドを保持状態に維持し、この保持ライトコマンドに従って選択メモリブロックでデータ書込を行なうことにより、正確に、データ書込を行なうことができる。

また、この書込アドレス信号を書込データおよび書込用コマンドを書込完了まで保持状態に維持し、次のライトコマンドの受付を禁止することにより、同一バンクに対するデータ書込の競合を回避することができる。

この発明は、情報を不揮発的に記憶する半導体記憶装置に適用することにより、高速処理システムを実現することのできる半導体記憶装置を得ることができる。

HSW,HSW0−HSW3 HBL切換回路、1a,1b メモリセルアレイ、2a,2b 周辺回路、3 転送回路、4 コマンドポート、4a コマンド入力回路、5 リードポート、5a リードアドレス入力回路、5b データ出力回路、6 ライトポート、6a ライトアドレス入力回路、6b データ入力回路、7 メイン制御回路、8,9 選択回路、HB0−HB3 電位供給バス、TX0−TX3 転送スイッチ回路、TXR リードタ転送スイッチ、TXW ライト転送スイッチ、MB0−MB3 メモリブロック、BNKA,BNKB バンク、80a,80b,82a,82b,88a,88b,89a,89b トライステートバッファ、84a,84b FIFO、86a,86b アドレスFIFO、SA0−SA3 センスアンプ、100 アドレス入力ポート、102 データ入出力ポート、104 アドレスラッチ、106 データラッチ、108 コマンドレジスタ、110 ライトホールド処理部。

Claims (4)

- 各々が複数の不揮発性メモリセルを有する複数のメモリブロック、

各前記メモリブロックに対応して配置され、各々が対応のメモリブロックに対するデータの書込および読出を行なうための電圧を伝達する複数のローカルバス、および

前記複数のメモリブロックに共通に配置され、前記複数のメモリブロックの選択されたメモリブロック間でデータの転送を行なうためのデータ転送バスを備える、半導体記憶装置。 - 前記複数のローカルバスの各々は、複数の信号線を含み、

各前記メモリブロックにおいて前記複数の不揮発性メモリセルは行列状に配列され、

各前記メモリブロックは、さらに、

メモリセル列に対応して、かつ各々が隣接列のメモリセルに共有されるように配列され、各々に対応の列の不揮発性メモリセルが接続する複数のビット線と、

各メモリセル行に対応して配置され、各々に対応の行の不揮発性メモリセルが接続する複数のワード線とを備え、

前記半導体記憶装置は、さらに、

各前記メモリブロックに対応して配置され、少なくともアドレス信号と動作モード指示信号と前記動作モード指示信号のデータ書込指示時に与えられる書込データとに従って対応のローカルバスの電圧を設定する電圧供給制御回路、および

各前記メモリブロックに対応して配置され、少なくとも前記アドレス信号に従って前記ローカルバスの選択された信号線のデータを検知して内部読出データを生成する内部読出回路、および

各前記メモリブロックに対応して配置され、前記アドレス信号に従って対応のローカルバスの信号線を対応のメモリブロックのビット線に結合するビット線選択回路を備える、請求項1記載の半導体記憶装置。 - 前記データ転送バスは、各前記メモリブロックの前記電圧供給制御回路および内部読出回路に選択的に結合される、請求項2記載の半導体記憶装置。

- 前記複数のメモリブロックは、各々が、少なくとも1個のメモリブロックを含む複数のメモリ群に分割され、

前記電圧供給制御回路および内部読出回路およびビット線選択回路は、前記メモリ群単位で互いに独立に動作可能である、請求項2記載の半導体記憶装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008201883A JP2008293648A (ja) | 2008-08-05 | 2008-08-05 | 半導体記憶装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008201883A JP2008293648A (ja) | 2008-08-05 | 2008-08-05 | 半導体記憶装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002229634A Division JP4225749B2 (ja) | 2002-08-07 | 2002-08-07 | 半導体記憶装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008293648A true JP2008293648A (ja) | 2008-12-04 |

Family

ID=40168206

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008201883A Pending JP2008293648A (ja) | 2008-08-05 | 2008-08-05 | 半導体記憶装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2008293648A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112767976A (zh) * | 2021-01-09 | 2021-05-07 | 深圳市德明利技术股份有限公司 | 平稳闪存写速度的方法、装置、存储介质和计算机设备 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS643899A (en) * | 1987-06-24 | 1989-01-09 | Sharp Kk | Nonvolatile semiconductor memory device |

| JPH0589686A (ja) * | 1991-09-27 | 1993-04-09 | Citizen Watch Co Ltd | 半導体不揮発性メモリとその書き込み方法 |

| JPH06181298A (ja) * | 1992-07-24 | 1994-06-28 | Sundisk Corp | セグメントコラムメモリアレイ |

| JPH07281952A (ja) * | 1994-04-12 | 1995-10-27 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JPH11176177A (ja) * | 1997-12-12 | 1999-07-02 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2001006379A (ja) * | 1999-06-16 | 2001-01-12 | Fujitsu Ltd | 複写、移動機能を有するフラッシュメモリ |

| JP2001344986A (ja) * | 2000-06-05 | 2001-12-14 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

-

2008

- 2008-08-05 JP JP2008201883A patent/JP2008293648A/ja active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS643899A (en) * | 1987-06-24 | 1989-01-09 | Sharp Kk | Nonvolatile semiconductor memory device |

| JPH0589686A (ja) * | 1991-09-27 | 1993-04-09 | Citizen Watch Co Ltd | 半導体不揮発性メモリとその書き込み方法 |

| JPH06181298A (ja) * | 1992-07-24 | 1994-06-28 | Sundisk Corp | セグメントコラムメモリアレイ |

| JPH07281952A (ja) * | 1994-04-12 | 1995-10-27 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JPH11176177A (ja) * | 1997-12-12 | 1999-07-02 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2001006379A (ja) * | 1999-06-16 | 2001-01-12 | Fujitsu Ltd | 複写、移動機能を有するフラッシュメモリ |

| JP2001344986A (ja) * | 2000-06-05 | 2001-12-14 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112767976A (zh) * | 2021-01-09 | 2021-05-07 | 深圳市德明利技术股份有限公司 | 平稳闪存写速度的方法、装置、存储介质和计算机设备 |

| CN112767976B (zh) * | 2021-01-09 | 2023-09-01 | 深圳市德明利技术股份有限公司 | 平稳闪存写速度的方法、装置、存储介质和计算机设备 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4225749B2 (ja) | 半導体記憶装置 | |

| US7936602B2 (en) | Use of data latches in cache operations of non-volatile memories | |

| KR101825232B1 (ko) | 반도체 메모리 디바이스에서 어레이 교란의 영향을 감소시키는 기술 | |

| JP3703951B2 (ja) | 不揮発性半導体メモリ装置 | |

| KR101468886B1 (ko) | 비휘발성 메모리를 위한 고속 감지 증폭기 어레이와 방법 | |

| TWI280582B (en) | Latched programming of memory and method | |

| CN100590741C (zh) | 用减少的相邻场误差编程非易失性存储器及方法 | |

| JP4814995B2 (ja) | 読み出し操作中にデータラッチでバックグラウンドキャッシングを行う不揮発性メモリとその方法 | |

| US6163048A (en) | Semiconductor non-volatile memory device having a NAND cell structure | |

| CN1698131B (zh) | 高度紧凑的非易失性存储器及其方法 | |

| JP4012150B2 (ja) | 不揮発性半導体記憶装置 | |

| US5999451A (en) | Byte-wide write scheme for a page flash device | |

| TWI360819B (ja) | ||

| JP3397404B2 (ja) | 半導体記憶装置 | |

| JPWO2003073433A1 (ja) | 不揮発性半導体記憶装置 | |

| US9099189B2 (en) | Methods and devices for memory reads with precharged data lines | |

| JP4712769B2 (ja) | 不揮発性半導体記憶装置 | |

| US6614691B2 (en) | Flash memory having separate read and write paths | |

| US6856549B2 (en) | Non-volatile semiconductor memory device attaining high data transfer rate | |

| US7843730B2 (en) | Non-volatile memory with reduced charge fluence | |

| JP2002279789A (ja) | 不揮発性半導体記憶装置とそのプログラム方法 | |

| US6839818B2 (en) | Electrically modifiable, non-volatile, semiconductor memory which can keep a datum stored until an operation to modify the datum is completed | |

| JP2008293648A (ja) | 半導体記憶装置 | |

| US20050146916A1 (en) | Series feram cell array | |

| KR100732633B1 (ko) | 비연속적인 비트라인 디코딩을 수행하는 플래시 메모리장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100602 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110215 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110802 |