JP2005159056A - 積層セラミック電子部品 - Google Patents

積層セラミック電子部品 Download PDFInfo

- Publication number

- JP2005159056A JP2005159056A JP2003396420A JP2003396420A JP2005159056A JP 2005159056 A JP2005159056 A JP 2005159056A JP 2003396420 A JP2003396420 A JP 2003396420A JP 2003396420 A JP2003396420 A JP 2003396420A JP 2005159056 A JP2005159056 A JP 2005159056A

- Authority

- JP

- Japan

- Prior art keywords

- dielectric layer

- porosity

- multilayer ceramic

- ceramic electronic

- electronic component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Ceramic Capacitors (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Abstract

【課題】焼成時の内部欠陥や、外部衝撃によるクラックを防止できる積層セラミック電子部品を提供する。

【解決手段】複数の第1誘電体層2aを間に内部電極3、4を介して積層するとともに、積層体1の両主面に第2誘電体層2bを被着・形成し、積層体1の端面に内部電極3、4に電気的に接続される外部電極5、6を被着・形成してなる積層セラミック電子部品であって、第1誘電体層2a及び第2誘電体層2bの空隙率が0.01%〜1.00%に設定されており、且つ第1誘電体層2aの空隙率が第2誘電体層2bの空隙率に比し高いことを特徴とする。

【選択図】図1

【解決手段】複数の第1誘電体層2aを間に内部電極3、4を介して積層するとともに、積層体1の両主面に第2誘電体層2bを被着・形成し、積層体1の端面に内部電極3、4に電気的に接続される外部電極5、6を被着・形成してなる積層セラミック電子部品であって、第1誘電体層2a及び第2誘電体層2bの空隙率が0.01%〜1.00%に設定されており、且つ第1誘電体層2aの空隙率が第2誘電体層2bの空隙率に比し高いことを特徴とする。

【選択図】図1

Description

本発明は、積層セラミック電子部品に関するものである。

代表的な積層セラミック電子部品として、積層セラミックコンデンサを例にとって説明する。

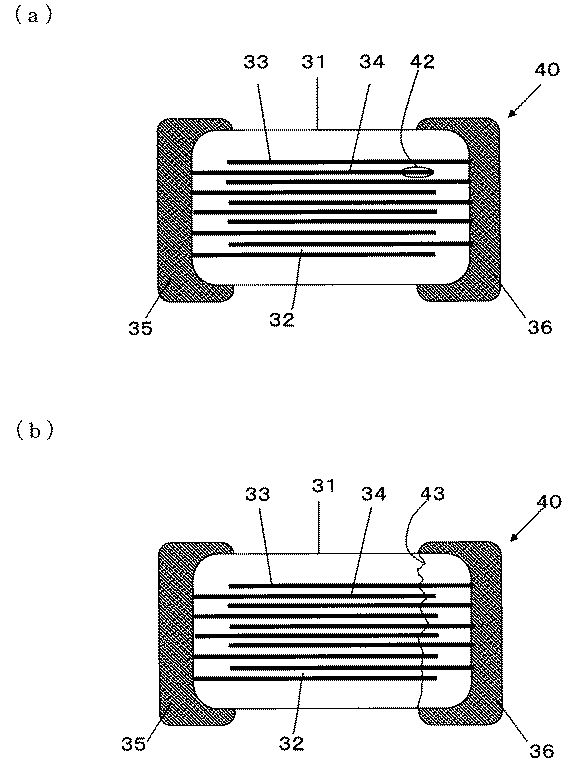

図4は、従来の積層セラミックコンデンサを示す断面図であり、同図において、積層セラミックコンデンサ30は、複数の誘電体層32を間に内部電極33、34を介して積層した積層体1と、積層体1の端面に被着・形成し、内部電極33、34に夫々電気的に接続される外部電極35、36とで構成されている。

かかる従来の積層セラミックコンデンサ10は以下の工程によって製作される。

まず、セラミックグリーンシート32上に、スクリーン印刷法などにより、Cu、Niなどの金属粉末、バインダ樹脂、溶剤などを混合した導体ペーストを薄膜状に塗布するとともに乾燥し、内部電極となる導体パターン33、34を形成する。

次に、導体パターン33、34が形成された複数のセラミックグリーンシート32を積層し、導体パターン33、34が形成されない複数のセラミックグリーンシート32を積層することにより大型積層体を形成する。

続いて、大型積層体を各素子領域毎に切断して未焼成状態の積層体31を形成し、次に未焼成状態の積層体31を焼成することによって積層体31を得、最後に、得られた積層体31の一対の端部に外部電極35、36を被着・形成することによって積層セラミックコンデンサ30が得られる。

特開平3−91218号公報

特許第2804325号

特許第3047706号公報

しかしながら、上述した従来の積層セラミックコンデンサ30においては、誘電体層32の空隙率が低い場合、図4(a)に示すように、焼成時に発生する内部応力を緩和する効果が低下するため、デラミネーション・クラックなどの内部欠陥42が発生するという問題点があった。一方、誘電体層32の空隙率が高い場合、図4(b)に示すように、外部からの衝撃により、積層体31にクラック43が発生するという問題点があった。

本発明は、上述の問題点に鑑みてなされたもので、その目的は、焼成時の内部欠陥や、外部衝撃によるクラックを防止できる積層セラミック電子部品を提供することにある。

本発明の積層セラミック電子部品は、複数の第1誘電体層を間に内部電極を介して積層するとともに、該積層体の両主面に第2誘電体層を被着・形成し、前記積層体の端面に前記内部電極に電気的に接続される外部電極を被着・形成してなる積層セラミック電子部品であって、前記第1誘電体層及び前記第2誘電体層の空隙率が0.01%〜1.00%に設定されており、且つ前記第1誘電体層の空隙率が前記第2誘電体層の空隙率に比し高いことをことを特徴とするものである。

また本発明の積層セラミック電子部品は、前記第1誘電体層の空隙率をP1、前記第2誘電体層の空隙率をP2とした場合、1<P1/P2≦10の範囲に設定されていることを特徴とするものである。

さらに本発明の積層セラミック電子部品は、前記第2誘電体層内の空隙率が第1誘電体層側に比し表層側で低くなっていることを特徴とするものである。

本発明によれば、第1誘電体層の空隙率が第2誘電体層の空隙率に比し高い。すなわち、第1誘電体層の空隙率を高くできることから、焼成時のデラミネーション、クラックなどの内部欠陥を防止でき、且つ第2誘電体層の空隙率を低くできることにより、積層体の機械的強度が向上し、外部衝撃によるクラックを防止できる。さらに、第1誘電体層及び第2誘電体層の空隙率が0.01%〜1.00%に設定されているため、上記焼成時のデラミネーション、クラックなどの内部欠陥を防止しつつ、第1誘電体層の厚みが10μm以下と薄型化した場合も、空隙を起点に内部電極間のショートに至ることがない。

また、第1誘電体層の空隙率をP1、第2誘電体層の空隙率をP2とした場合、1<P1/P2≦10の範囲に設定されているため、より効果的に、上記焼成時の内部欠陥や、外部衝撃によるクラックを防止しつつ、空隙を起点とする内部電極間のショートを防止できる。

さらに、第2誘電体層内の空隙率が第1誘電体層側に比し表層側で低くなっているため、第2誘電体層内の第1誘電体層側の空隙率を高くできることから、内部電極の有無による段差を緩和できる。

以下、本発明にかかる積層セラミック電子部品の製造方法を、積層セラミックコンデンサを製造する場合を例にとって説明する。

図1(a)は、本発明の一実施形態に係る積層セラミックコンデンサを示す外観斜視図、図1(b)は(a)の積層セラミックコンデンサの縦断面図、図2は図1の積層セラミックコンデンサの製造方法を示す図である。

本実施形態の積層セラミックコンデンサ10は、大略的に、積層体1と、積層体1の一対の端面に被着・形成された外部電極5、6とで構成されている。

積層体1は、間に内部電極3、4が形成されて積層された複数の誘電体層2aと、両主面に積層された第2誘電体層2bとからなり、内部電極3と外部電極5、内部電極4と外部電極6が夫々電気的に接続されている。

ここで、第1誘電体層2a及び第2誘電体層2bの空隙率が0.01%〜1.00%に設定されており、且つ第1誘電体層2aの空隙率が第2誘電体層2bの空隙率に比し高い。

また、第1誘電体層2aの空隙率をP1、第2誘電体層2bの空隙率をP2とした場合、1<P1/P2≦10の範囲に設定されている。

以下、本発明の積層セラミックコンデンサ10の製造方法について説明する。なお、図中の参照符は焼成の前後で区別することなく用いるものとする。

まず、チタン酸バリウム(BaTiO3)などの誘電体材料を主成分とするセラミック粉末、バインダ樹脂、溶剤、可塑剤、分散剤などを混合したセラミックスラリーを、ドクターブレード法、引き上げ法、ダイコーター、グラビアロールコータなどにより、シート状に成形するとともに乾燥し、第1誘電体層となるセラミックグリーンシート2a、第2誘電体層となるセラミックグリーンシート2bを形成する。

ここで、セラミックグリーンシート2aに含有されるバインダ樹脂の割合は、セラミックグリーンシート2bに含有されるバインダ樹脂の割合より高くする。例えば、セラミックグリーンシート2aに含有されるバインダ樹脂の割合が10%である場合、セラミックグリーンシート2bに含有されるバインダ樹脂の割合を8%にする。

次に、セラミックグリーンシート2a上に、スクリーン印刷法などにより、Cu、Niなどの金属粉末、バインダ樹脂、溶剤などを混合した導体ペーストを薄膜状に塗布するとともに乾燥し、内部電極となる導体パターン3、4を形成する。

次に、台板21上に、複数のセラミックグリーンシート2bを積層する。また、導体パターン3、4が形成されたセラミックグリーンシート2aを交互に積層する。さらに、複数のセラミックグリーンシート2bを積層することにより積層素体11を形成する。

次に、積層素体11を台板21上に形成した状態で加熱しつつ積層方向に加圧することにより、圧着積層体11を形成する。具体的には、図2に示すように、台板21上に形成した積層素体11の周囲を枠23で囲い、さらに積層素体11上に剛体板22を配置し、これらを可撓性袋24内に収納させて内部を脱気・密封した状態で静水圧プレス装置の加圧室内に投入する。このとき、圧着積層体11が可撓性袋24から剥離しやすいように、これらの間にPETフィルムなどを介在させても良い。

このとき、セラミックグリーンシート2aに含有されるバインダ樹脂の割合は、セラミックグリーンシート2bに含有されるバインダ樹脂の割合より高いため、セラミックグリーンシート2aに含有されるバインダ樹脂の割合を高くできることから、セラミックグリーンシート2aと導体パターン3、4間の層間剥離を防止でき、一方、セラミックグリーンシート2bに含有されるバインダ樹脂の割合を少なくできるため、セラミックグリーンシート2bが台板21や剛体板22に貼り付くことによる積層圧着体11の破損を防止できる。

次に、圧着積層体11を各素子領域毎に切断し、未焼成状態の積層体1を形成し、しかる後、未焼成状態の積層体1を焼成し、積層体1を得る。

このとき、セラミックグリーンシート2aに含有されるバインダ樹脂の割合は、セラミックグリーンシート2bに含有されるバインダ樹脂の割合より高いため、第1誘電体層の空隙率が前記第2誘電体層の空隙率に比し高くなる。

そして最後に、得られた積層体1の一対の端部に、外部電極5、6を被着・形成し、これによって図1に示す積層セラミックコンデンサ10が完成する。

以上のような本実施形態の積層セラミックコンデンサ10によれば、第1誘電体層2aの空隙率が第2誘電体層2bの空隙率に比し高い。すなわち、第1誘電体層2aの空隙率を高くできることから、焼成時のデラミネーション、クラックなどの内部欠陥42を防止でき、且つ第2誘電体層2bの空隙率を低くできることにより、積層体1の機械的強度が向上し、外部衝撃によるクラック43を防止できる。さらに、第1誘電体層2a及び第2誘電体層2bの空隙率が0.01%〜1.00%に設定されているため、上記焼成時のデラミネーション、クラックなどの内部欠陥42を防止しつつ、第1誘電体層2aの厚みが10μm以下と薄型化した場合も、空隙を起点に内部電極3−4間のショートに至ることがない。

また、第1誘電体層2aの空隙率をP1、第2誘電体層2bの空隙率をP2とした場合、1<P1/P2≦10の範囲に設定されているため、より効果的に、上記焼成時の内部欠陥42や、外部衝撃によるクラック43を防止しつつ、空隙を起点とする内部電極3−4間のショートを防止できる。

なお、本発明は上記の実施の形態例に限定されるものではなく、本発明の要旨を逸脱しない範囲内での種々の変更や改良などは何ら差し支えない。

図3は、本発明の他の実施の形態を示す縦断面図であり、同図に示すように、内部電極3、4が形成されない誘電体層2b1、2b2を積層するようにし、空隙率が2a<2b1<2aの関係となるようにしても良い。すなわち、誘電体層2b1の空隙率を誘電体層2b2より高くできるため、内部電極3、4の有無による段差を緩和できるという効果もある。

また、図2に示すように、積層素体11を台板21上に形成した状態で加熱しつつ積層方向に加圧することにより、圧着積層体11を形成する際に、セラミックグリーンシート2aと導体パターン3、4間の層間剥離や、セラミックグリーンシート2b2が台板21や剛体板22に貼り付くことによる積層圧着体11の破損を防止ししつ、セラミックグリーンシート2aが積層された部分とセラミックグリーンシート2b2が積層された部分の間の層間剥離も防止できる。

更に、上述した実施形態では、本発明を積層セラミックコンデンサ10の製造方法に適用した例について説明したが、本発明は、回路基板、積層圧電部品、半導体部品など、あらゆる積層セラミック電子部品10の製造方法に適用可能である。

本発明者は、セラミックグリーンシート2a、2bに含有されるバインダ樹脂の割合を変化させることにより、第1誘電体層2aの空隙率P1、第2誘電体層2aの空隙率P2を制御した積層セラミックコンデンサ10を作製した。

得られた積層セラミックコンデンサ10について、焼成時の内部欠陥42の発生率、実装時のクラック43の発生率を求めた。

焼成時の内部欠陥42の発生率は、100個の焼成後の積層体1を研磨し、金属顕微鏡で観察することにより、デラミネーション・クラックの発生率を求めた。

実装時のクラック43の発生率は、100個の積層セラミックコンデンサ10を1.6mm厚のガラスエポキシ基板(配線基板)上の配線パターンに、半田付けにより表面実装した後、金属顕微鏡で観察することにより、クラックの発生率を求めた。

表1に示すように、第1誘電体層2a及び第2誘電体層2bの空隙率が0.01%〜1.00%に設定されており、且つ1<P1/P2≦10の範囲にある本実施例(試料番号2〜7)は、焼成時の内部欠陥42の発生率、実装時のクラック43の発生率はともに0%だった。

これに対し、P1=P2=0.01%である比較例(試料番号1)は、焼成時の内部欠陥42が2%発生した。一方、P1=P2=1.00%である比較例(試料番号8)は、実装時のクラック43が1%発生した。

これらの結果から、本発明の積層セラミックコンデンサ10は、第1誘電体層2a及び第2誘電体層2bの空隙率が0.01%〜1.00%に設定されており、且つ1<P1/P2≦10の範囲にあるため、焼成時の内部欠陥42や、外部衝撃によるクラック43を防止できることがわかった。

10・・・・・・・積層セラミックコンデンサ

1・・・・・・・・積層体

2a・・・・・・・第1誘電体層(セラミックグリーンシート)

2b・・・・・・・第2誘電体層(セラミックグリーンシート)

3、4・・・・・・内部電極(導体パターン)

5、6・・・・・・外部電極

11・・・・・・・圧着積層体(積層素体)

21・・・・・・・台板

22・・・・・・・剛体板

23・・・・・・・枠

24・・・・・・・可撓性袋

1・・・・・・・・積層体

2a・・・・・・・第1誘電体層(セラミックグリーンシート)

2b・・・・・・・第2誘電体層(セラミックグリーンシート)

3、4・・・・・・内部電極(導体パターン)

5、6・・・・・・外部電極

11・・・・・・・圧着積層体(積層素体)

21・・・・・・・台板

22・・・・・・・剛体板

23・・・・・・・枠

24・・・・・・・可撓性袋

Claims (3)

- 複数の第1誘電体層を間に内部電極を介して積層するとともに、該積層体の両主面に第2誘電体層を被着・形成し、前記積層体の端面に前記内部電極に電気的に接続される外部電極を被着・形成してなる積層セラミック電子部品であって、

前記第1誘電体層及び前記第2誘電体層の空隙率が0.01%〜1.00%に設定されており、且つ前記第1誘電体層の空隙率が前記第2誘電体層の空隙率に比し高いことを特徴とする積層セラミック電子部品。 - 前記第1誘電体層の空隙率をP1、前記第2誘電体層の空隙率をP2とした場合、1<P1/P2≦10の範囲に設定されていることを特徴とする請求項1に記載の積層セラミック電子部品。

- 前記第2誘電体層内の空隙率が第1誘電体層側に比し表層側で低くなっていることを特徴とする請求項1または請求項2に記載の積層セラミック電子部品。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003396420A JP2005159056A (ja) | 2003-11-26 | 2003-11-26 | 積層セラミック電子部品 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003396420A JP2005159056A (ja) | 2003-11-26 | 2003-11-26 | 積層セラミック電子部品 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005159056A true JP2005159056A (ja) | 2005-06-16 |

Family

ID=34721872

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003396420A Pending JP2005159056A (ja) | 2003-11-26 | 2003-11-26 | 積層セラミック電子部品 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005159056A (ja) |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011198947A (ja) * | 2010-03-18 | 2011-10-06 | Tdk Corp | セラミック電子部品およびセラミック電子部品の製造方法 |

| KR101124091B1 (ko) * | 2009-12-10 | 2012-03-20 | 삼성전기주식회사 | 적층 세라믹 커패시터 |

| US8345405B2 (en) | 2009-12-10 | 2013-01-01 | Samsung Electronics Co., Ltd. | Multilayer ceramic capacitor |

| KR101508503B1 (ko) * | 2010-08-18 | 2015-04-07 | 다이요 유덴 가부시키가이샤 | 적층형 세라믹 전자 부품 |

| US9042081B2 (en) | 2013-04-08 | 2015-05-26 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor and method of manufacturing the same |

| US20150348712A1 (en) * | 2014-05-28 | 2015-12-03 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor, method of manufacturing the same, and board having the same |

| CN105761934A (zh) * | 2015-01-06 | 2016-07-13 | 三星电机株式会社 | 多层陶瓷电容器及具有该多层陶瓷电容器的板 |

| CN106098295A (zh) * | 2015-04-27 | 2016-11-09 | 株式会社村田制作所 | 电子部件及其制造方法 |

| JP2018186199A (ja) * | 2017-04-26 | 2018-11-22 | 京セラ株式会社 | コンデンサ |

| JP2019102655A (ja) * | 2017-12-04 | 2019-06-24 | 太陽誘電株式会社 | セラミックコンデンサおよびその製造方法 |

| JP2019175935A (ja) * | 2018-03-27 | 2019-10-10 | Tdk株式会社 | 積層セラミック電子部品 |

| CN115249586A (zh) * | 2021-04-28 | 2022-10-28 | Tdk株式会社 | 电子零件 |

| WO2025047707A1 (ja) * | 2023-08-28 | 2025-03-06 | 株式会社村田製作所 | 積層セラミックコンデンサ |

| WO2025047708A1 (ja) * | 2023-08-28 | 2025-03-06 | 株式会社村田製作所 | 積層セラミックコンデンサ |

-

2003

- 2003-11-26 JP JP2003396420A patent/JP2005159056A/ja active Pending

Cited By (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101124091B1 (ko) * | 2009-12-10 | 2012-03-20 | 삼성전기주식회사 | 적층 세라믹 커패시터 |

| US8345405B2 (en) | 2009-12-10 | 2013-01-01 | Samsung Electronics Co., Ltd. | Multilayer ceramic capacitor |

| US8390983B2 (en) | 2009-12-10 | 2013-03-05 | Samsung Electronics Co., Ltd. | Multilayer ceramic capacitor |

| JP2011198947A (ja) * | 2010-03-18 | 2011-10-06 | Tdk Corp | セラミック電子部品およびセラミック電子部品の製造方法 |

| KR101508503B1 (ko) * | 2010-08-18 | 2015-04-07 | 다이요 유덴 가부시키가이샤 | 적층형 세라믹 전자 부품 |

| US9042081B2 (en) | 2013-04-08 | 2015-05-26 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor and method of manufacturing the same |

| US20150348712A1 (en) * | 2014-05-28 | 2015-12-03 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor, method of manufacturing the same, and board having the same |

| JP2015226053A (ja) * | 2014-05-28 | 2015-12-14 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | 積層セラミックキャパシタ、積層セラミックキャパシタの製造方法、及び積層セラミックキャパシタの実装基板 |

| US9812259B2 (en) * | 2014-05-28 | 2017-11-07 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor, method of manufacturing the same, and board having the same |

| CN105761934A (zh) * | 2015-01-06 | 2016-07-13 | 三星电机株式会社 | 多层陶瓷电容器及具有该多层陶瓷电容器的板 |

| US10770233B2 (en) | 2015-01-06 | 2020-09-08 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor and board having the same |

| CN105761934B (zh) * | 2015-01-06 | 2019-09-06 | 三星电机株式会社 | 多层陶瓷电容器及具有该多层陶瓷电容器的板 |

| US10373762B2 (en) | 2015-01-06 | 2019-08-06 | Samsung Electro-Mechanics Co., Ltd. | Multilayer ceramic capacitor and board having the same |

| US10256029B2 (en) | 2015-04-27 | 2019-04-09 | Murata Manufacturing Co., Ltd. | Electronic component and method for manufacturing the same |

| CN106098295A (zh) * | 2015-04-27 | 2016-11-09 | 株式会社村田制作所 | 电子部件及其制造方法 |

| JP2018186199A (ja) * | 2017-04-26 | 2018-11-22 | 京セラ株式会社 | コンデンサ |

| JP2019102655A (ja) * | 2017-12-04 | 2019-06-24 | 太陽誘電株式会社 | セラミックコンデンサおよびその製造方法 |

| JP7032916B2 (ja) | 2017-12-04 | 2022-03-09 | 太陽誘電株式会社 | セラミックコンデンサおよびその製造方法 |

| JP2019175935A (ja) * | 2018-03-27 | 2019-10-10 | Tdk株式会社 | 積層セラミック電子部品 |

| JP7069935B2 (ja) | 2018-03-27 | 2022-05-18 | Tdk株式会社 | 積層セラミック電子部品 |

| CN115249586A (zh) * | 2021-04-28 | 2022-10-28 | Tdk株式会社 | 电子零件 |

| CN115249586B (zh) * | 2021-04-28 | 2024-05-28 | Tdk株式会社 | 电子零件 |

| WO2025047707A1 (ja) * | 2023-08-28 | 2025-03-06 | 株式会社村田製作所 | 積層セラミックコンデンサ |

| WO2025047708A1 (ja) * | 2023-08-28 | 2025-03-06 | 株式会社村田製作所 | 積層セラミックコンデンサ |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101823246B1 (ko) | 적층 세라믹 전자 부품 및 그 실장 기판 | |

| JPH08130160A (ja) | 積層セラミック電子部品の製造方法 | |

| JP2005159056A (ja) | 積層セラミック電子部品 | |

| JPWO2018216452A1 (ja) | 電子部品、及び、電子部品の製造方法 | |

| JP2002015939A (ja) | 積層型電子部品およびその製法 | |

| JP2002299148A (ja) | 積層セラミックコンデンサ及びその製造方法 | |

| US12080483B2 (en) | Method of producing multilayer ceramic electronic component, and multilayer ceramic electronic component | |

| JPH09190947A (ja) | 積層セラミック電子部品 | |

| JP2000340448A (ja) | 積層セラミックコンデンサ | |

| JP2003045740A (ja) | 積層型電子部品 | |

| KR101805074B1 (ko) | 세라믹 다층회로 기판의 제조방법 | |

| JP2000243650A (ja) | 積層セラミックコンデンサおよびその製造方法 | |

| JPH06283375A (ja) | 積層電子部品の製造方法 | |

| JP2002270459A (ja) | 積層セラミック電子部品の製造方法 | |

| JPH10112417A (ja) | 積層セラミック電子部品及びその製造方法 | |

| JP2004186343A (ja) | セラミック積層体及びその製法 | |

| JP7775891B2 (ja) | 積層シートの製造方法、積層電子部品の製造方法、及び積層シート | |

| JP3954792B2 (ja) | 積層セラミック電子部品の製造方法 | |

| JP2004186344A (ja) | セラミック積層体及びその製法 | |

| JPH09129482A (ja) | 積層セラミックコンデンサの製造方法 | |

| JPH08316093A (ja) | 積層セラミック電子部品の製造方法 | |

| JP2007053294A (ja) | 積層型セラミック電子部品の製造方法 | |

| JP2005136008A (ja) | 積層型電子部品の製法 | |

| JP4822725B2 (ja) | 積層体の製造方法 | |

| JP2005136126A (ja) | 積層セラミック電子部品の製造方法 |