CN113436664B - 一种阻变存储单元的电导线性对称调节方法 - Google Patents

一种阻变存储单元的电导线性对称调节方法 Download PDFInfo

- Publication number

- CN113436664B CN113436664B CN202110987676.4A CN202110987676A CN113436664B CN 113436664 B CN113436664 B CN 113436664B CN 202110987676 A CN202110987676 A CN 202110987676A CN 113436664 B CN113436664 B CN 113436664B

- Authority

- CN

- China

- Prior art keywords

- conductance

- resistive memory

- voltage

- pulse

- random access

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 39

- 230000015654 memory Effects 0.000 claims abstract description 43

- 230000008859 change Effects 0.000 claims abstract description 12

- 230000000630 rising effect Effects 0.000 claims description 18

- 230000007423 decrease Effects 0.000 claims description 10

- 230000001419 dependent effect Effects 0.000 claims description 3

- 230000033228 biological regulation Effects 0.000 abstract description 6

- 125000004122 cyclic group Chemical group 0.000 abstract description 3

- 230000008569 process Effects 0.000 abstract description 3

- 230000000737 periodic effect Effects 0.000 abstract description 2

- 238000010586 diagram Methods 0.000 description 21

- 230000000694 effects Effects 0.000 description 9

- 230000003247 decreasing effect Effects 0.000 description 6

- 230000009467 reduction Effects 0.000 description 6

- 238000004364 calculation method Methods 0.000 description 3

- 238000013528 artificial neural network Methods 0.000 description 2

- 230000001174 ascending effect Effects 0.000 description 2

- 230000004087 circulation Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000035772 mutation Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

Landscapes

- Semiconductor Memories (AREA)

Abstract

本发明属于非易失存储器技术领域,涉及一种阻变存储单元的电导线性对称调节方法,通过调节阻变存储单元晶体管的栅极电压来实现阻变存储单元的电导的线性对称调节,在一晶体管一阻变存储器件的阻变存储单元结构下,在晶体管源极和漏极施加电压时,通过控制晶体管的栅极电压,使得阻变存储单元的电导状态发生改变,在高阻向低阻转变过程中,当晶体管的栅极电压较大时,器件电阻处于高电导状态;当晶体管的栅极电压较小时,忆阻器处于低电导状态。本发明方法通过调节栅极电压,得到电导呈线性对称变化,在多个周期性的测试中都保持较大的窗口,多次循环操作的电导变化差异很小,耐久性较好,可以解决传统阻变存储器编程方案的电导精准调控难题。

Description

技术领域

本发明属于非易失存储器技术领域,涉及一种阻变存储单元的电导线性对称调节方法。

背景技术

阻变存储器作为一种新型的非易失存储器,在近几年来,受到学术界和产业界的广泛关注。由于其具有电导连续可调的特性,所以可以做成多值存储单元。由于其具有可微缩性较好的特点,所以可以做成大规模的阵列,并且它可以很好的与硅基半导体工艺兼容。除此之外,器件阵列在存储信息的同时能够利用欧姆定律和基尔霍夫定律完成乘累加运算,具有计算并行度高、功耗低、速度快的显著优势,被学术界广泛的应用于神经网络的研究。神经网络计算对阻变存储器的性能提出了很高的要求,其中,阻变存储器电导的线性对称调节是困扰学术界和产业界的巨大难题。

目前,阻变存储器电导的线性对称调节的方式主要有:(1)调节脉冲宽度。即在电导的上升阶段,施加连续的SET脉冲,每次施加在漏极上的脉冲宽度逐渐增大;在电导的下降阶段,施加连续的RESET脉冲,每次施加在源极上的脉冲宽度逐渐增大,最终实现电导的线性上升和下降调节。(2)调节脉冲个数。即在电导的上升阶段,施加多个连续的SET脉冲,每个脉冲的脉宽均相同。在电导的下降阶段,施加多个连续的RESET脉冲,每个脉冲的脉宽均相同,最终实现电导的线性上升和下降调节。(3)调节存储单元漏极和源极上的脉冲幅值。即在电导的上升阶段,施加连续的SET脉冲,每次施加在漏极上的脉冲幅值逐渐增大;在电导的下降阶段,施加连续的RESET脉冲,每次施加在源极上的脉冲幅值逐渐增大。(4)调节晶体管的栅压。即在电导的上升阶段,施加连续的SET脉冲,每次施加在栅极上的脉冲幅值逐渐增大;在电导的下降阶段,施加连续的RESET脉冲,每次施加在栅极上的脉冲幅值逐渐增大。最终实现电导的线性上升和下降。

上述方法在实际操作过程中,并不能很好地实现阻变存储器电导线性对称调节的效果,存在电导突变或缓变的情况。

发明内容

为了解决现有技术中存在的上述技术问题,本发明提出一种阻变存储单元的电导线性对称调节方法,通过调节阻变存储单元阵列中栅极上的电压以及漏极、源极上的电压实现电导的线性对称调节,其中,通过逐渐增加栅极上的电压使阻变存储单元的电导线性增加,RESET回初始电导后减小栅极上的电压使阻变存储单元的电导线性减小,其具体技术方案如下:

一种阻变存储单元的电导线性对称调节方法,采用的阻变存储单元为1T1R结构的阻变存储阵列,包括晶体管和阻变存储器,阻变存储器与晶体管串联方式连接,阻变存储器的下电极连接晶体管的漏极,上电极连接Vd电压线,该调节方法具体包括以下步骤:

步骤一,初始化操作:初始化阻变存储单元,后进行读操作,通过读取源极的电流I,得到阻变存储单元的阻值R1,并根据R1值判断完成初始化操作;

步骤二,RESET操作:对已完成初始化操作的阻变存储单元进行RESET操作,即在源极施加脉冲,阻变存储器的上电极接地,再进行与步骤一中相同的读操作,得到RESET后的阻变存储单元的阻值R3,并根据R3值判断进行下一步骤;

步骤三,电导线性上升阶段:在电导线性上升阶段,在存储单元的阻变存储器的上电极施加脉冲,源极接地,即进行SET操作,使得电导线性增加;

步骤四,电导线性下降阶段:在电导线性下降阶段,在存储单元的阻变存储器的上电极进行连续的SET操作,每次SET操作前进行与步骤二相同的RESET操作,使得电导的线性减小;

步骤五,多次循环调节:重复进行步骤三和步骤四,得到多个循环的电导数据,实现电导的线性对称调节。

进一步的,所述步骤一,具体包括:

步骤(1),对选取的阻变存储单元进行初始化操作,将源极接地,栅极施加偏置电压U,阻变存储器的上电极施加一个从0V开始的步进增加幅度电压值为U1的直流电压;

步骤(2),然后进行读操作,栅极保持电压U不变,在阻变存储器的上电极施加一个脉冲方波,源极接地,从源极端获取读出的电流I,用阻变存储器的上电极的脉冲电压除以I得到阻变存储单元的阻值R1,若阻值R1大于阈值R2,则再进行步骤(1)的初始化操作,在阻变存储器的上电极施加一个从0V开始的步进增加幅度电压值为U2的直流电压,U2>U1,其他条件不变;若阻值R1小于阈值R2,则初始化操作完成。

进一步的,所述步骤二,具体包括:

步骤(3),对已完成初始化操作的阻变存储单元进行RESET操作,即在选中的阻变存储单元的源极和栅极上施加脉冲电压U3,阻变存储器的上电极接地;

步骤(4),再进行与步骤(2)相同的读操作,得到RESET后的阻变存储单元的阻值R3,若阻值R3小于阈值R4,则再次进行与步骤(3)相同的RESET操作,反之进行下一步骤。

进一步的,所述步骤三,具体包括:

步骤(5),进入电导线性上升阶段,在漏极上施加一个脉冲电压,保持不变,源极接地,在栅极上施加从1V开始步进增加到U的脉冲电压,脉宽不变,即进行连续的SET操作,每施加一个SET脉冲,进行与步骤(2)相同的读操作,通过读出的电流值,计算并记录每次施加完SET脉冲后的电导Gp;

进一步的,所述步骤四,具体包括:

步骤(6),进入电导线性下降阶段,阻变存储器的上电极电压保持不变,源极接地,在栅极上施加从U开始步进减小到1V的脉冲电压,脉宽不变,即进行连续的SET操作,每次SET前进行与步骤(3)相同的RESET操作,每施加一个SET脉冲,进行与步骤(2)相同的读操作,通过读出的电流值,计算并记录每次施加完SET脉冲后的电导Gd。

进一步的,所述步骤五,具体包括:

步骤(7),重复进行步骤(5)和步骤(6)的操作,得到多个循环的电导数据,实现电导的线性对称,以该电导数据作为因变量,SET脉冲个数作为自变量作图,得到电导脉冲个数的增加呈线性对称的变化曲线图。

本发明的优点:

本发明方法简单易行,通过调节栅极电压,得到电导随栅压呈线性对称变化,并且高低电导差值很大,即窗口很大,多次循环操作的电导变化差异很小;在多个周期性的测试中都保持较大的窗口,耐久性较好,可以解决传统阻变存储器编程方案的电导精准调控难题。

附图说明

图1是1T1R存储单元的结构图;

图1a是现有电导线性上升阶段的调节脉宽的操作方法的示意图;

图1b是现有电导线性下降阶段的调节脉宽的操作方法的示意图;

图2是现有的调节脉宽时存储单元的电学性能的示意图;

图3a是现有电导线性上升阶段的调节脉冲个数的操作方法的示意图;

图3b是现有电导线性下降阶段的调节脉冲个数的操作方法的示意图;

图4是现有的调节脉冲个数时存储单元的电学性能的示意图;

图5a是现有电导线性上升阶段的调节漏极和源极上电压的操作方法的示意图;

图5b是现有电导线性下降阶段的调节漏极和源极上电压的操作方法的示意图;

图6是现有的调节漏极和源极上电压时存储单元的电学性能的示意图;

图7a是现有电导线性上升阶段的调节栅极上电压的操作方法的示意图;

图7b是现有电导线性下降阶段的调节栅极上电压的操作方法的示意图;

图8是现有的调节栅极上电压时存储单元的电学性能的示意图;

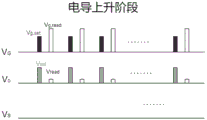

图9a是本发明提出的电导线性上升阶段调节单元的栅压的操作方法原理示意图;

图9b是本发明提出的电导线性下降阶段调节单元的栅压的操作方法原理示意图;

图10是本发明中通过调节栅压和初始电导使存储单元的电导呈线性对称变化的示意图。

具体实施方式

为了使本发明的目的、技术方案和技术效果更加清楚明白,以下结合说明书附图和实施例,对本发明作进一步详细说明。

一种阻变存储单元的电导线性对称调节方法,采用的阻变存储单元是1T1R结构的阻变存储阵列,该1T1R阻变存储阵列的基本单元包括一个晶体管和一个阻变存储器,阻变存储器的下电极和晶体管的漏极相连,通过调节晶体管栅压实现电导的线性对称变化,其中,通过增加栅压使阻变存储单元的电导线性增加,通过RESET后减小栅压,使阻变存储单元的电导线性减小,具体的,该方法包括以下步骤:

步骤(1),对选取的阻变存储单元进行初始化操作,即在栅极上施加2V的偏置电压,源极接地,阻变存储器的上电极的直流电压从0V以0.046V的步进增加到4.6V,直流施加的总时间为10毫秒。

步骤(2),读操作,在栅极上施加2V的电压,阻变存储器的上电极施加0.2V的2毫秒的方波,源极接地,从源极端获取读出的电流I,用0.2V除以I得到阻变存储单元的阻值R1,若阻值R1大于100K欧姆,则再进行步骤(1)的初始化操作,但阻变存储器的上电极的直流电压要从0V以0.047V的步进增加到4.7V,其他条件不变;若阻值R1小于100K欧姆,则初始化操作完成。

步骤(3),对已完成初始化操作的阻变存储单元进行RESET操作,即在选中存储单元的源极上施加3.7V的脉冲,阻变存储器的上电极接地,栅极上施加3.7V的脉冲,脉冲为脉宽5微秒的方波。

步骤(4),进行与步骤(2)相同的读操作,若阻变存储单元的阻值R3小于66K欧姆则再次进行步骤(3)的操作,反之进行下一步骤。

步骤(5),电导线性上升阶段,实现电导的线性增加,即在漏极上施加2.5V的脉冲,源极接地,栅极上的电压从1V以0.01V的步进增加到2V,脉冲为500微秒的方波,实现电导的线性增加。即进行连续的SET操作,每施加一个SET脉冲,进行步骤(2)的读操作,用读出电流除以电压0.2V,计算并记录每次施加完SET脉冲后的电导Gp。

步骤(6),电导线性下降阶段,实现电导的线性减小,分为RESET和SET两个操作,每次SET前进行步骤(3)的RESET操作;SET时,在阻变存储器的上电极施加2.5V的脉冲,源极接地,栅极上的电压从2V以0.01V的步进递减到1V,脉冲为500微秒的方波,每施加一个SET脉冲,进行步骤(2)的读操作,用读出电流除以电压0.2V,计算并记录每次施加完SET脉冲后的电导Gd。

步骤(7),重复进行步骤(5)和步骤(6)的操作,得到多个循环的电导数据,以该电导数据作为因变量,SET脉冲个数作为自变量作图,得到电导脉冲个数的增加呈线性对称的变化曲线图。

如图1所示,是1T1R阻变存储单元的结构图,VG是指施加在晶体管栅极的电压,VS是指施加在晶体管源极的电压,VD是指施加在阻变存储单元上电极的电压。

如图1a和图1b所示,是现有的调节脉宽的操作方法的示意图。在电导线性上升阶段,保持栅极上的电压不变,源极接地,逐渐增加漏极上脉冲的脉宽,脉冲幅度不变,实现电导的增加。在电导线性下降阶段,保持栅极上的电压不变,漏极接地,逐渐增加源极上脉冲的脉宽,脉冲幅度不变,实现电导的减小,最终实现电导线性上升阶段和电导线性下降阶段的电导线性对称调节。值得说明的是在所有附图中,Vg,set是指在SET操作时施加在栅极上的脉冲幅值,Vg,read是指在读操作时施加在栅极上的脉冲幅值,Vset是指在SET操作时施加在漏极上的脉冲幅值,Vread是指在读操作时施加在漏极上的脉冲幅值,Vg,reset是指在RESET操作时施加在栅极上的脉冲幅值,Vreset是指在RESET操作时施加在源极上的脉冲幅值。

如图2所示,是最优脉冲参数下实现的效果,该方法的RESET是突变的,并不能达到电导线性调节的效果。

如图3a和图3b所示,是现有的调节脉冲个数的操作方法的示意图。在电导线性上升阶段,保持栅极上的电压以及漏极上的电压不变,源极接地,脉宽不变,施加多个相同的SET脉冲,实现电导的增加;在电导线性下降阶段,保持栅极上的电压以及源极上的电压不变,漏极接地,脉宽不变,施加多个相同的RESET脉冲,实现电导的减小。

如图4所示,是最优脉冲参数下实现的效果,该方法的SET和RESET都是突变的,并不能达到电导线性调节的效果。

如图5a和图5b所示,是现有的调节漏极和源极上电压的操作方法的示意图。在电导线性上升阶段,保持栅极上的电压不变,源极接地,逐渐增加漏极上脉冲的幅度,脉宽不变,实现电导的增加;在电导线性下降阶段,保持栅极上的电压不变,漏极接地,逐渐增加源极上脉冲的幅度,脉宽不变,实现电导的减小。

如图6所示,是最优脉冲参数下实现的效果,虽然该方法电导变化具有一定的线性度,但这种方法的电导窗口太小。

如图7a和图7b所示,是现有的调节栅极上电压的操作方法的示意图。在电导线性上升阶段,保持漏极上的电压不变,源极接地,逐渐增加栅极上的电压,脉宽不变,实现电导的增加;在电导线性下降阶段,保持源极上的电压不变,漏极接地,逐渐增加栅极上的电压,脉宽不变,实现电导的减小。

如图8所示,是最优脉冲参数下实现的效果,虽然该方法窗口较大,但是线性度不高。

如图9a和图9b所示,是本发明提出的调节阻变存储单元的栅压的操作方法原理示意图。在电导线性上升阶段,保持阻变存储器的上电极的电压不变,源极接地,逐渐增加栅极上的电压,脉宽不变,实现电导的增加;在电导线性下降阶段分为SET和RESET操作,每次SET前进行一次RESET操作,将电导调回低导,SET时,保持阻变存储器的上电极的电压不变,源极接地,逐渐减小栅极上的电压,脉宽不变,实现电导的减小。

如图10所示,是最优脉冲参数下实现的效果。此方法可以实现电导的线性对称调节,并且多次循环操作的电导变化差异很小,高低电导差值很大,即窗口很大。

以上所述,仅为本发明的优选实施案例,并非对本发明做任何形式上的限制。虽然前文对本发明的实施过程进行了详细说明,对于熟悉本领域的人员来说,其依然可以对前述各实例记载的技术方案进行修改,或者对其中部分技术特征进行同等替换。凡在本发明精神和原则之内所做修改、同等替换等,均应包含在本发明的保护范围之内。

Claims (3)

1.一种阻变存储单元的电导线性对称调节方法,采用的阻变存储单元为1T1R结构的阻变存储阵列,包括晶体管和阻变存储器,阻变存储器与晶体管串联方式连接,阻变存储器的下电极连接晶体管的漏极,上电极连接Vd电压线,其特征在于,该调节方法具体包括以下步骤:

步骤一,初始化操作:初始化阻变存储单元,后进行读操作,通过读取源极的电流I,得到阻变存储单元的阻值R1,并根据R1值判断完成初始化操作;

步骤二,RESET操作:对已完成初始化操作的阻变存储单元进行RESET操作,即在源极施加脉冲,阻变存储器的上电极接地,再进行与步骤一中相同的读操作,得到RESET后的阻变存储单元的阻值R3,并根据R3值判断进行下一步骤;

步骤三,电导线性上升阶段:在电导线性上升阶段,在存储单元的阻变存储器的上电极施加脉冲,源极接地,即进行SET操作,使得电导线性增加;

步骤四,电导线性下降阶段:在电导线性下降阶段,在存储单元的阻变存储器的上电极进行连续的SET操作,每次SET操作前进行与步骤二相同的RESET操作,使得电导的线性减小;

步骤五,多次循环调节:重复进行步骤三和步骤四,得到多个循环的电导数据,实现电导的线性对称调节;

所述步骤一,具体包括:

步骤(1),对选取的阻变存储单元进行初始化操作,将源极接地,栅极施加偏置电压U,阻变存储器的上电极施加一个从0V开始的步进增加幅度电压值为U1的直流电压;

步骤(2),然后进行读操作,栅极保持电压U不变,在阻变存储器的上电极施加一个脉冲方波,源极接地,从源极端获取读出的电流I,用阻变存储器的上电极的脉冲电压除以I得到阻变存储单元的阻值R1,若阻值R1大于阈值R2,则再进行步骤(1)的初始化操作,在阻变存储器的上电极施加一个从0V开始的步进增加幅度电压值为U2的直流电压,U2>U1,其他条件不变;若阻值R1小于阈值R2,则初始化操作完成;

所述步骤二,具体包括:

步骤(3),对已完成初始化操作的阻变存储单元进行RESET操作,即在选中的阻变存储单元的源极和栅极上施加脉冲电压U3,阻变存储器的上电极接地;

步骤(4),再进行与步骤(2)相同的读操作,得到RESET后的阻变存储单元的阻值R3,若阻值R3小于阈值R4,则再次进行与步骤(3)相同的RESET操作,反之进行下一步骤;

所述步骤三,具体包括:

步骤(5),进入电导线性上升阶段,在漏极上施加一个脉冲电压,保持不变,源极接地,在栅极上施加从1V开始步进增加到U的脉冲电压,脉宽不变,即进行连续的SET操作,每施加一个SET脉冲,进行与步骤(2)相同的读操作,通过读出的电流值,计算并记录每次施加完SET脉冲后的电导Gp。

2.如权利要求1所述的一种阻变存储单元的电导线性对称调节方法,其特征在于,所述步骤四,具体包括:

步骤(6),进入电导线性下降阶段,阻变存储器的上电极电压保持不变,源极接地,在栅极上施加从U开始步进减小到1V的脉冲电压,脉宽不变,即进行连续的SET操作,每次SET前进行与步骤(3)相同的RESET操作,每施加一个SET脉冲,进行与步骤(2)相同的读操作,通过读出的电流值,计算并记录每次施加完SET脉冲后的电导Gd。

3.如权利要求2所述的一种阻变存储单元的电导线性对称调节方法,其特征在于,所述步骤五,具体包括:

步骤(7),重复进行步骤(5)和步骤(6)的操作,得到多个循环的电导数据,实现电导的线性对称,以该电导数据作为因变量,SET脉冲个数作为自变量作图,得到电导脉冲个数的增加呈线性对称的变化曲线图。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202110987676.4A CN113436664B (zh) | 2021-08-26 | 2021-08-26 | 一种阻变存储单元的电导线性对称调节方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202110987676.4A CN113436664B (zh) | 2021-08-26 | 2021-08-26 | 一种阻变存储单元的电导线性对称调节方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN113436664A CN113436664A (zh) | 2021-09-24 |

| CN113436664B true CN113436664B (zh) | 2021-12-14 |

Family

ID=77798052

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202110987676.4A Active CN113436664B (zh) | 2021-08-26 | 2021-08-26 | 一种阻变存储单元的电导线性对称调节方法 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN113436664B (zh) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102129886A (zh) * | 2010-01-12 | 2011-07-20 | 中芯国际集成电路制造(上海)有限公司 | 电阻随机存储器的初始化以及设置、复位方法 |

| WO2017151296A1 (en) * | 2016-03-04 | 2017-09-08 | Silicon Storage Technology, Inc. | Multi-step voltage for forming resistive random access memory (rram) cell filament |

| CN108878646A (zh) * | 2018-06-28 | 2018-11-23 | 北京大学 | 一种阻变器件多级稳定阻态实现方法及电子设备 |

| CN113191402A (zh) * | 2021-04-14 | 2021-07-30 | 华中科技大学 | 基于忆阻器的朴素贝叶斯分类器设计方法、系统及分类器 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102804278B (zh) * | 2010-03-30 | 2014-10-01 | 松下电器产业株式会社 | 电阻变化型非易失性存储元件的塑造方法及电阻变化型非易失性存储装置 |

| JP5915121B2 (ja) * | 2011-11-30 | 2016-05-11 | 凸版印刷株式会社 | 抵抗変化型不揮発性メモリ |

| CN104966779B (zh) * | 2015-07-31 | 2017-08-01 | 华中科技大学 | 基于数字双向脉冲对相变存储单元非晶态和晶态剪裁的方法 |

| US10903273B2 (en) * | 2019-01-04 | 2021-01-26 | International Business Machines Corporation | Phase change memory with gradual conductance change |

| CN109950394B (zh) * | 2019-03-29 | 2020-05-15 | 河南大学 | 无电形成过程阻变存储器实现量子电导效应的方法 |

-

2021

- 2021-08-26 CN CN202110987676.4A patent/CN113436664B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102129886A (zh) * | 2010-01-12 | 2011-07-20 | 中芯国际集成电路制造(上海)有限公司 | 电阻随机存储器的初始化以及设置、复位方法 |

| WO2017151296A1 (en) * | 2016-03-04 | 2017-09-08 | Silicon Storage Technology, Inc. | Multi-step voltage for forming resistive random access memory (rram) cell filament |

| CN108878646A (zh) * | 2018-06-28 | 2018-11-23 | 北京大学 | 一种阻变器件多级稳定阻态实现方法及电子设备 |

| CN113191402A (zh) * | 2021-04-14 | 2021-07-30 | 华中科技大学 | 基于忆阻器的朴素贝叶斯分类器设计方法、系统及分类器 |

Non-Patent Citations (1)

| Title |

|---|

| 基于氧化锌薄膜的忆阻器特性及神经突触仿生功能研究;王宫;《中国优秀硕士学位论文全文数据库工程科技Ⅰ辑》;20200815;1.1阻变存储器,第四章-第五章 * |

Also Published As

| Publication number | Publication date |

|---|---|

| CN113436664A (zh) | 2021-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Papandreou et al. | Programming algorithms for multilevel phase-change memory | |

| US11094377B2 (en) | Multi-level self-selecting memory device | |

| Wang et al. | A self-rectification and quasi-linear analogue memristor for artificial neural networks | |

| US8557654B2 (en) | Punch-through diode | |

| KR102014944B1 (ko) | 저항성 메모리 디바이스에 대한 기입 및 소거 방식 | |

| US20230274773A1 (en) | Non-volatile analog resistive memory cells implementing ferroelectric select transistors | |

| JP6884232B2 (ja) | メモリ・セルの時間ベースのアクセス | |

| CN101889312B (zh) | 存储装置及信息再记录方法 | |

| Milo et al. | Optimized programming algorithms for multilevel RRAM in hardware neural networks | |

| WO2021136394A1 (zh) | 阻变存储阵列及其操作方法、阻变存储器电路 | |

| CN111179991B (zh) | 阻变存储阵列及其操作方法、阻变存储器电路 | |

| WO2021136395A1 (zh) | 阻变存储阵列的操作方法 | |

| Yan et al. | Characteristic investigation of highly oriented Hf0. 5Zr0. 5O2 thin-film resistive memory devices | |

| CN113436664B (zh) | 一种阻变存储单元的电导线性对称调节方法 | |

| CN111640865B (zh) | 一种适用于神经形态计算的人工突触器件 | |

| JP2022542047A (ja) | メモリデバイスのための適応型書き込み動作 | |

| WO2020247277A1 (en) | Combinational resistive change elements | |

| US20120230098A1 (en) | Programming of phase-change memory cells | |

| WO2021083356A1 (zh) | 存算单元和芯片 | |

| Glukhov et al. | Statistical model of program/verify algorithms in resistive-switching memories for in-memory neural network accelerators | |

| CN115035934A (zh) | 存储器装置及其操作方法 | |

| US9472279B2 (en) | Memory cell dynamic grouping using write detection | |

| US9087574B2 (en) | Memory apparatus with gated phase-change memory cells | |

| Wang et al. | Uniformity improvements of low current 1T1R RRAM arrays through optimized verification strategy | |

| CN114970846A (zh) | 一种储备池计算网络的硬件实现方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |