CN101504618B - Multi-core processor oriented real-time thread migration method - Google Patents

Multi-core processor oriented real-time thread migration method Download PDFInfo

- Publication number

- CN101504618B CN101504618B CN2009100959582A CN200910095958A CN101504618B CN 101504618 B CN101504618 B CN 101504618B CN 2009100959582 A CN2009100959582 A CN 2009100959582A CN 200910095958 A CN200910095958 A CN 200910095958A CN 101504618 B CN101504618 B CN 101504618B

- Authority

- CN

- China

- Prior art keywords

- thread

- migration

- processor

- core

- operating system

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Memory System Of A Hierarchy Structure (AREA)

Abstract

本发明公开了一种面向多核处理器的实时线程迁移方法。本发明是充分利用了共享二级cache和内存的多核硬件体系架构的特点从而有效地实现了多核处理器上的实时线程迁移方法。本发明实现了硬件支持的线程迁移初始化和处理器核之间的线程迁移,在线程运行时不需要花任何时间来轮询系统变量,减少了线程迁移时处理器核之间的数据传输,明显提高了线程执行时的性能和缩短了线程迁移的时间。本发明可以用在各种多核处理器上。

The invention discloses a multi-core processor-oriented real-time thread migration method. The present invention makes full use of the characteristics of the multi-core hardware system framework of shared secondary cache and memory, thereby effectively realizing the real-time thread migration method on the multi-core processor. The present invention realizes hardware-supported thread migration initialization and thread migration between processor cores, does not need to spend any time polling system variables when threads are running, reduces data transmission between processor cores during thread migration, and obviously Improved thread execution performance and shortened thread migration time. The present invention can be used on various multi-core processors.

Description

技术领域technical field

本发明涉及多核硬件体系架构上处理器核之间进行线程迁移的方法。The invention relates to a thread migration method between processor cores on a multi-core hardware architecture.

背景技术Background technique

由于处理器时钟频率的增长,处理器能耗和温度的不断攀升,导致了处理器厂商在速度竞争上的极限。面临这种增长的极限,微处理器厂商纷纷投向了多核处理器技术的怀抱。多核处理器技术为处理器性能提升开辟了一个新的前景。有些公司就声称其生产的处理器将会全面使用多核体系架构。Due to the increase of processor clock frequency, the continuous rise of processor power consumption and temperature has led to the limit of processor manufacturers' competition in speed. Faced with the limit of this growth, microprocessor manufacturers have turned to the embrace of multi-core processor technology. Multi-core processor technology has opened up a new prospect for processor performance improvement. Some companies claim that the processors they produce will use multi-core architecture in an all-round way.

多核处理器芯片提供了比单核处理器芯片更好的并发性,更好的单位瓦特系统性能。并发性为控制系统,网络路由等设备提供了更高的性能扩展。这些系统如果充分利用多核处理器芯片提供的并发性,将能在性能上有很大的提升。然而,大多数的软件设计者和软件工程师对于这种并发编程模式缺少相应的经验和技术积累,因此这对于利用多核处理器技术的优势是一个很大的障碍。Multi-core processor chips provide better concurrency and better system performance per watt than single-core processor chips. Concurrency provides higher performance scaling for control systems, network routing, and other devices. If these systems take full advantage of the concurrency provided by multi-core processor chips, they will be able to greatly improve their performance. However, most software designers and software engineers lack corresponding experience and technology accumulation for this concurrent programming mode, so this is a big obstacle for taking advantage of multi-core processor technology.

这种技术上的障碍是很明显的,比如说多核芯片上的共享资源的管理就是一个很大的技术挑战。大多数情况下,多核芯片中的每个核有一个独立的一级缓存和共享的二级缓存,内存子系统,中断子系统和外围设备。这样,系统设计者就必须确保每个核互斥的访问某些资源。这种设计上的考虑就带来了更高的设计复杂性。比如说,在不同的核上运行的程序如果需要互相协作,那么就需要一个可行的进程间通讯机制,共享内存机制和保障共享资源的同步原语机制。操作系统的方方面面都需要针对多核体系进行改造才能充分利用多核技术带来的性能提升。This technical obstacle is obvious. For example, the management of shared resources on a multi-core chip is a great technical challenge. In most cases, each core in a multicore chip has an independent L1 cache and shared L2 cache, memory subsystem, interrupt subsystem, and peripherals. Thus, system designers must ensure that each core has exclusive access to certain resources. This design consideration brings higher design complexity. For example, if programs running on different cores need to cooperate with each other, then a feasible inter-process communication mechanism, a shared memory mechanism and a synchronization primitive mechanism to guarantee shared resources are needed. All aspects of the operating system need to be modified for the multi-core system in order to take full advantage of the performance improvement brought by the multi-core technology.

因此,操作系统对多核的支持能很大程度上减少多核技术带来的设计难度。一个支持多核的操作系统充分利用多核硬件平台的优势,关键在于操作系统对多核的支持。操作系统在线程级别对多核的支持可以带来更好的性能。Therefore, the operating system's support for multi-core can greatly reduce the design difficulty brought about by multi-core technology. An operating system that supports multi-core takes full advantage of the advantages of a multi-core hardware platform, the key lies in the support of the operating system for multi-core. The operating system's support for multi-core at the thread level can lead to better performance.

线程迁移在分布式系统中已经进行了大量的研究。分布式系统是通过协同各个节点来共同完成计算任务。通过事先的任务放置静态地分配负载难以达到负载平衡。在计算过程中,各个节点的负载会动态地发生改变,线程迁移是实现分布式系统动态负载平衡的方法之一。线程迁移是将在一个节点上运行的线程转移到另外的节点上运行。它可以保留在源节点上已经执行的结果而不必重新执行该线程。目前已实现的线程迁移机制当中,大部分是基于检查点保存重起机制来实现的,即在迁移进程之前,把进程的状态数据保存到检查点文件,然后该检查点文件转移到另外的节点上,待目标节点收到整个检查点文件后,再根据检查点文件重新恢复迁移线程。分布式系统中各个节点是不共享本地内存的,每次线程迁移都要传输大量的数据。Thread migration has been extensively studied in distributed systems. Distributed systems work together to complete computing tasks by cooperating with each node. Load balancing is difficult to achieve by statically distributing load through prior task placement. During the computing process, the load of each node will change dynamically, and thread migration is one of the methods to achieve dynamic load balancing in distributed systems. Thread migration is to transfer the threads running on one node to run on another node. It can retain the results of the execution on the source node without re-executing the thread. Most of the currently implemented thread migration mechanisms are implemented based on the checkpoint saving and restarting mechanism, that is, before migrating the process, the state data of the process is saved to the checkpoint file, and then the checkpoint file is transferred to another node. After the target node receives the entire checkpoint file, the migration thread will be resumed according to the checkpoint file. Each node in a distributed system does not share local memory, and a large amount of data must be transferred for each thread migration.

同样,为了实现多核处理器的动态负载平衡,或者是为了提高多核处理器的性能,降低多核处理器的能耗,有必要在处理器核之间进行线程迁移。Similarly, in order to realize the dynamic load balance of the multi-core processor, or to improve the performance of the multi-core processor and reduce the energy consumption of the multi-core processor, it is necessary to perform thread migration between processor cores.

发明内容Contents of the invention

本发明的目的在于提供一种面向多核处理器的实时线程迁移方法。The purpose of the present invention is to provide a multi-core processor-oriented real-time thread migration method.

本发明解决其技术问题采用的技术方案如下:The technical scheme that the present invention solves its technical problem adopts is as follows:

1)在处理器核之间进行线程迁移,所有的处理器核都有私有的一级cache,共享的二级cache和内存;1) Perform thread migration between processor cores, all processor cores have private first-level cache, shared second-level cache and memory;

2)硬件支持的线程迁移初始化:2) Thread migration initialization supported by hardware:

第一步,当每一个线程开始运行后,这个线程的所有的迁移点地址都记录在操作系统中;In the first step, when each thread starts running, all migration point addresses of this thread are recorded in the operating system;

第二步,操作系统把所有的迁移点地址保存到每个线程各自的一个数据结构中,并把每个处理器核上正在运行的线程的迁移点地址写到核上的调试寄存器中,当发生上下文切换时,操作系统就更新调试寄存器中的数据;In the second step, the operating system saves all migration point addresses into a data structure of each thread, and writes the migration point addresses of threads running on each processor core into the debug register on the core. When a context switch occurs, the operating system updates the data in the debug register;

第三步,当操作系统决定迁移一个线程的时候,操作系统就设置这个线程所在处理器核上的调试寄存器中的标志位来激活调试寄存器;In the third step, when the operating system decides to migrate a thread, the operating system sets the flag bit in the debug register on the processor core where the thread is located to activate the debug register;

第四步,当线程执行指令到达线程的迁移点地址时,就会产生一个硬件中断并开始线程迁移;In the fourth step, when the thread execution instruction reaches the migration point address of the thread, a hardware interrupt will be generated and the thread migration will start;

3)线程迁移方法:3) Thread migration method:

当开始线程迁移时,操作系统唤醒线程迁移的目标处理器核,接着根据源处理器核的指令执行结果对目标处理器核进行训练;当训练过程结束后,操作系统首先释放源处理器核上的线程并清空源处理器核的流水线,接着把源处理器核的一级cache中的数据写回到二级cache中,然后把源处理器核寄存器中的数据通过总线传输给目标处理器核。最后目标处理器核把接收到数据存储到寄存器中,然后开始执行在目标处理器核上产生的线程。When thread migration starts, the operating system wakes up the target processor core for thread migration, and then trains the target processor core according to the instruction execution results of the source processor core; when the training process ends, the operating system first releases the thread and clear the pipeline of the source processor core, then write the data in the first-level cache of the source processor core back to the second-level cache, and then transfer the data in the registers of the source processor core to the target processor core through the bus . Finally, the target processor core stores the received data into registers, and then starts executing the threads generated on the target processor core.

与现有技术相比,本发明的有益效果是:Compared with prior art, the beneficial effect of the present invention is:

(1)高效性。本发明实现了一种面向多核处理器的实时线程迁移方法,基于检查点的线程迁移方法在线程执行过程中要不断地轮询系统变量来确定是否要进行线程迁移,而硬件支持的线程迁移初始化方法不需要花任何时间来轮询系统变量,因此明显提高了线程执行时的性能。由于在多核处理器上线程迁移时的数据传输过程只需要把一级cache中的数据写回到二级cache中,然后把源处理器核上的寄存器中的数据通过总线传输到目标处理器核上,因此明显缩短了线程迁移的时间。(1) Efficiency. The present invention implements a real-time thread migration method for multi-core processors. The checkpoint-based thread migration method needs to continuously poll system variables to determine whether to perform thread migration during the thread execution process, and the thread migration initialization supported by hardware The method does not need to spend any time polling system variables, thus significantly improving the performance of thread execution. Since the data transmission process during thread migration on a multi-core processor only needs to write the data in the first-level cache back to the second-level cache, and then transfer the data in the registers on the source processor core to the target processor core through the bus. Therefore, the time for thread migration is significantly shortened.

(2)可靠性。本发明通过对分布式系统中线程迁移的过程进行仔细的分析,适当地更改了线程迁移的过程,仔细地设计了线程迁移初始化和线程迁移时源处理器核和目标处理器核之间的数据传输过程,保证了线程能够在处理器核之间正常地进行迁移,使线程迁移到目标处理器核上后能够继续正常运行。(2) Reliability. The present invention properly changes the process of thread migration by carefully analyzing the process of thread migration in a distributed system, and carefully designs the data between the source processor core and the target processor core during thread migration initialization and thread migration. The transmission process ensures that the thread can be normally migrated between processor cores, so that the thread can continue to run normally after being migrated to the target processor core.

(3)实用性。本发明提出的一种面向多核处理器的实时线程迁移方法,可以用在各种多核处理器上。(3) Practicality. A multi-core processor-oriented real-time thread migration method proposed by the present invention can be used on various multi-core processors.

附图说明Description of drawings

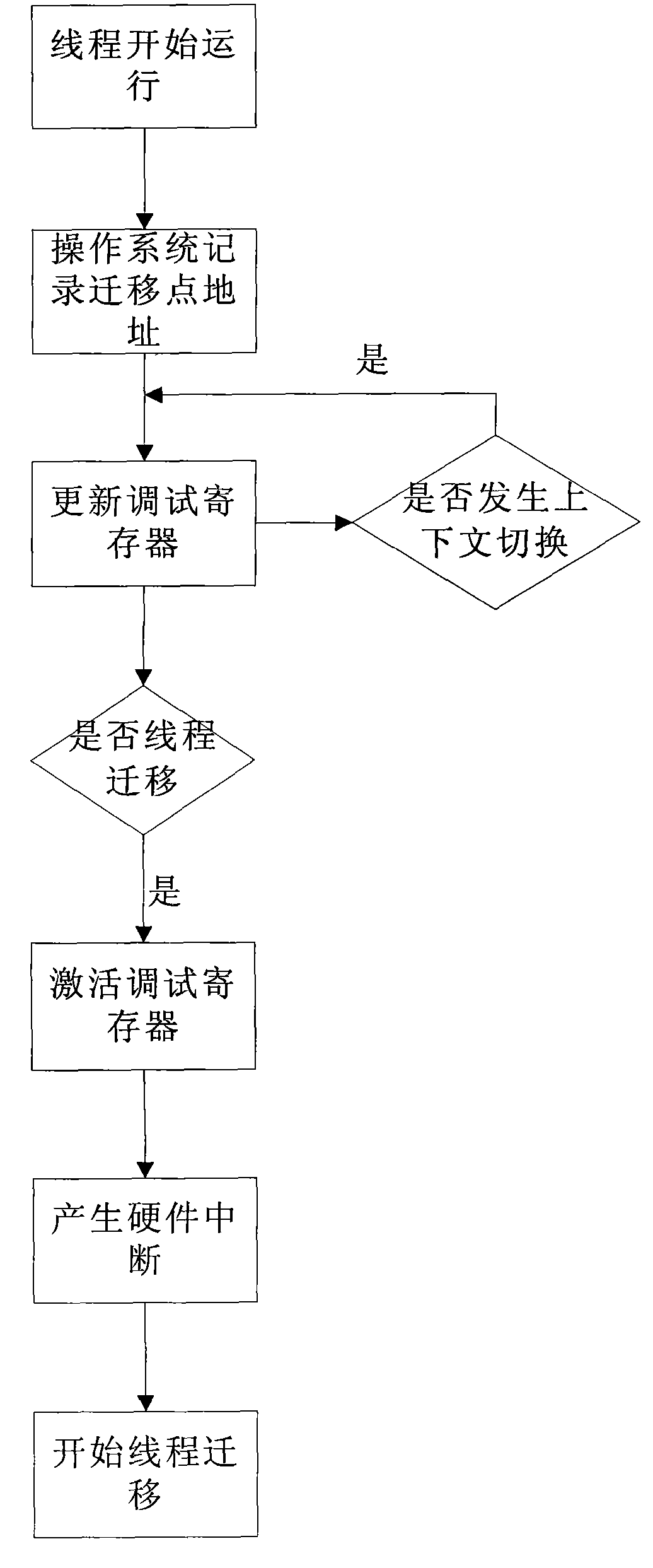

图1是硬件支持的线程迁移初始化过程的示意图。FIG. 1 is a schematic diagram of a thread migration initialization process supported by hardware.

图2是线程迁移过程的示意图。FIG. 2 is a schematic diagram of a thread migration process.

具体实施方式Detailed ways

1)在处理器核之间进行线程迁移,所有的处理器核都有私有的一级cache,共享的二级cache和内存:1) Thread migration between processor cores, all processor cores have private first-level cache, shared second-level cache and memory:

目前大多数的多核处理器体系架构中,处理器核都有私有的一级cache,并共享二级cache和内存。所有的处理器核都共享内存,因此线程迁移时不需要传输共享内存中的代码和数据。所有的处理器核都共享二级cache,线程迁移时源处理器核的一级cache中的数据只需写回到二级cache中而不用写回到内存中。In most current multi-core processor architectures, processor cores have a private L1 cache and share L2 cache and memory. All processor cores share memory, so there is no need to transfer code and data in shared memory during thread migration. All processor cores share the second-level cache. When threads migrate, the data in the first-level cache of the source processor core only needs to be written back to the second-level cache instead of being written back to the memory.

2)硬件支持的线程迁移初始化:2) Thread migration initialization supported by hardware:

大多数现代处理器都含有一系列的调试寄存器。PowerPC 405处理器包含4个32位的指令地址比较寄存器。当程序计数寄存器中的值等于一个被激活的指令地址比较寄存器中的值时就会产生一个硬件中断。同样地,在其它处理器中,当程序计数寄存器中的值等于一个被激活的调试寄存器中的值时也会产生一个硬件中断。利用这个机制的硬件支持的线程迁移初始化方法使得线程在执行过程中不需要花任何时间来轮询系统中的变量。硬件支持的线程迁移初始化方法,如图1所示,包含以下四个步骤:Most modern processors contain a series of debug registers. The PowerPC 405 processor contains four 32-bit instruction address compare registers. A hardware interrupt is generated when the value in the program count register equals the value in the address compare register of an activated instruction. Likewise, on other processors, a hardware interrupt is generated when the value in the program counter register equals the value in an enabled debug register. The hardware-supported thread migration initialization method using this mechanism makes the thread do not need to spend any time polling the variables in the system during execution. The hardware-supported thread migration initialization method, as shown in Figure 1, includes the following four steps:

第一步,当一个线程开始运行后,这个线程的所有的迁移点地址都记录在操作系统中;In the first step, when a thread starts running, all migration point addresses of this thread are recorded in the operating system;

第二步,操作系统把所有的迁移点地址保存到每个线程各自的一个数据结构中,并把每个处理器核上正在运行的线程的迁移点地址写到核上的调试寄存器中,当发生上下文切换时,操作系统就会用将要执行的线程的迁移点地址来更新调试寄存器中的数据;In the second step, the operating system saves all migration point addresses into a data structure of each thread, and writes the migration point addresses of threads running on each processor core into the debug register on the core. When a context switch occurs, the operating system will update the data in the debug register with the migration point address of the thread to be executed;

第三步,当操作系统根据资源管理器决定迁移一个线程到另外一个处理器核上的时候,操作系统就设置这个线程所在处理器核上的调试寄存器中的标志位来激活调试寄存器;In the third step, when the operating system decides to migrate a thread to another processor core according to the resource manager, the operating system sets the flag bit in the debug register on the processor core where the thread is located to activate the debug register;

第四步,当线程执行指令到达线程所在处理器核上被激活的调试寄存器中的迁移点地址时,就会产生一个硬件中断并开始线程迁移;In the fourth step, when the thread execution instruction reaches the migration point address in the activated debug register on the processor core where the thread is located, a hardware interrupt will be generated and the thread migration will start;

3)线程迁移方法:3) Thread migration method:

如图2所示,当开始线程迁移时,如果线程迁移的目标处理器核被关闭了,操作系统需要唤醒线程迁移的目标处理器核,接着根据源处理器核的指令执行结果对目标处理器核上的cache和预测器进行训练。当训练过程结束后,操作系统首先释放源处理器核上的线程并清空源处理器核的流水线,接着把源处理器核的一级cache中的数据写回到二级cache中。当源处理器核把一级cache中的数据写回到二级cache中,目标处理器核访问二级cache就可以获得正确的数据。然后操作系统把源处理器核寄存器中的数据通过总线传输存储到共享内存中,这样目标处理器核就能够访问这些数据。最后,操作系统在线程迁移的目标处理器核上创建一个新的线程,目标处理器核通过访问共享内存获得源处理器核寄存器中的数据,并把这些数据存储到自己的寄存器中,接着目标处理器核就开始执行新创建的线程。As shown in Figure 2, when the thread migration starts, if the target processor core of the thread migration is closed, the operating system needs to wake up the target processor core of the thread migration, and then execute the target processor according to the instruction execution result of the source processor core. The cache and predictor on the core are trained. When the training process is over, the operating system first releases the threads on the source processor core and clears the pipeline of the source processor core, and then writes the data in the primary cache of the source processor core back into the secondary cache. When the source processor core writes the data in the first-level cache back to the second-level cache, the target processor core can access the second-level cache to obtain the correct data. Then the operating system transfers and stores the data in the registers of the source processor core to the shared memory through the bus, so that the target processor core can access the data. Finally, the operating system creates a new thread on the target processor core of the thread migration. The target processor core obtains the data in the registers of the source processor core by accessing the shared memory, and stores these data in its own registers, and then the target processor core The processor core starts executing the newly created thread.

Claims (1)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN2009100959582A CN101504618B (en) | 2009-02-26 | 2009-02-26 | Multi-core processor oriented real-time thread migration method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN2009100959582A CN101504618B (en) | 2009-02-26 | 2009-02-26 | Multi-core processor oriented real-time thread migration method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101504618A CN101504618A (en) | 2009-08-12 |

| CN101504618B true CN101504618B (en) | 2011-04-27 |

Family

ID=40976873

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2009100959582A Expired - Fee Related CN101504618B (en) | 2009-02-26 | 2009-02-26 | Multi-core processor oriented real-time thread migration method |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN101504618B (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2502857A (en) * | 2013-03-05 | 2013-12-11 | Imagination Tech Ltd | Migration of register file caches in a parallel processing system |

| US11853809B2 (en) | 2016-01-15 | 2023-12-26 | Intel Corporation | Systems, methods and devices for determining work placement on processor cores |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101751295B (en) * | 2009-12-22 | 2012-08-29 | 浙江大学 | Method for realizing inter-core thread migration under multi-core architecture |

| CN102495762B (en) * | 2011-11-16 | 2014-04-02 | 华为技术有限公司 | Thread scheduling method, thread scheduling device and multi-core processor system |

| CN102981805B (en) * | 2012-11-02 | 2015-11-18 | 浪潮(北京)电子信息产业有限公司 | The response method of serialized software and system |

| CN105009086B (en) * | 2014-03-10 | 2019-01-18 | 华为技术有限公司 | A kind of method, computer and switching device for realizing processor switching |

| CN105868016B (en) * | 2015-01-20 | 2019-04-02 | 复旦大学 | A kind of thread transfer distribution method avoiding multi-core processor hot-spot |

| CN115100018A (en) | 2015-06-10 | 2022-09-23 | 无比视视觉技术有限公司 | Image processor and method for processing images |

| WO2017049592A1 (en) * | 2015-09-25 | 2017-03-30 | Intel Corporation | Method and apparatus to improve shared memory efficiency |

| US10083068B2 (en) * | 2016-03-29 | 2018-09-25 | Microsoft Technology Licensing, Llc | Fast transfer of workload between multiple processors |

| CN105930218A (en) * | 2016-04-18 | 2016-09-07 | 深圳市万普拉斯科技有限公司 | Computing resource frequency adjustment method and system |

| CN106776018B (en) * | 2016-12-01 | 2020-09-01 | 三星(中国)半导体有限公司 | Parallel processing method and device for master node and slave node of distributed system |

| CN108156207A (en) * | 2016-12-02 | 2018-06-12 | 航天星图科技(北京)有限公司 | A kind of data processing method of multi-node system |

| CN106850749A (en) * | 2016-12-26 | 2017-06-13 | 联想(北京)有限公司 | A kind of method and device, the electronic equipment of online updating kernel |

| CN109254849B (en) * | 2018-08-31 | 2021-03-30 | 北京小米移动软件有限公司 | Application program running method and device |

| CN109614220B (en) * | 2018-10-26 | 2020-06-30 | 阿里巴巴集团控股有限公司 | Multi-core system processor and data updating method |

| CN112395079B (en) * | 2019-08-19 | 2022-10-04 | 无锡江南计算技术研究所 | Operation core job migration method under heterogeneous many-core architecture |

| CN111338577A (en) * | 2020-02-21 | 2020-06-26 | 苏州浪潮智能科技有限公司 | Multi-core thread migration method and system of storage system and related components |

| CN112559176B (en) * | 2020-12-11 | 2024-07-19 | 广州橙行智动汽车科技有限公司 | Instruction processing method and device |

| CN115658569B (en) * | 2022-12-08 | 2023-04-14 | 井芯微电子技术(天津)有限公司 | Method, system and equipment for interrupting and sharing storage among AMP (amplifier) multi-core processors |

| CN116244229B (en) * | 2023-05-12 | 2023-08-04 | 苏州浪潮智能科技有限公司 | Hardware controller access method, device, storage medium and electronic equipment |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101201753A (en) * | 2007-12-13 | 2008-06-18 | 浪潮通信信息系统有限公司 | Method for configuring and managing multimode machine supervising engine |

| CN101256515A (en) * | 2008-03-11 | 2008-09-03 | 浙江大学 | Implementation method of multi-core processor operating system load balancing |

| CN101364189A (en) * | 2007-06-30 | 2009-02-11 | 英特尔公司 | Method and apparatus for runtime processor migration with operating system assistance |

-

2009

- 2009-02-26 CN CN2009100959582A patent/CN101504618B/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101364189A (en) * | 2007-06-30 | 2009-02-11 | 英特尔公司 | Method and apparatus for runtime processor migration with operating system assistance |

| CN101201753A (en) * | 2007-12-13 | 2008-06-18 | 浪潮通信信息系统有限公司 | Method for configuring and managing multimode machine supervising engine |

| CN101256515A (en) * | 2008-03-11 | 2008-09-03 | 浙江大学 | Implementation method of multi-core processor operating system load balancing |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2502857A (en) * | 2013-03-05 | 2013-12-11 | Imagination Tech Ltd | Migration of register file caches in a parallel processing system |

| GB2502857B (en) * | 2013-03-05 | 2015-01-21 | Imagination Tech Ltd | Migration of data to register file cache |

| US11853809B2 (en) | 2016-01-15 | 2023-12-26 | Intel Corporation | Systems, methods and devices for determining work placement on processor cores |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101504618A (en) | 2009-08-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101504618B (en) | Multi-core processor oriented real-time thread migration method | |

| TWI494850B (en) | Providing an asymmetric multicore processor system transparently to an operating system | |

| US10509576B2 (en) | Method, apparatus, and system for energy efficiency and energy conservation including autonomous hardware-based deep power down in devices | |

| CN115016907B (en) | Methods, devices, and instructions for pausing user-level threads | |

| US8954977B2 (en) | Software-based thread remapping for power savings | |

| CN109960398B (en) | Dynamic core selection for heterogeneous multi-core systems | |

| CN102495756B (en) | The method and system that operating system switches between different central processing units | |

| CN101387952B (en) | Single-chip multi-processor task scheduling and managing method | |

| Wang et al. | Run-time power-gating in caches of GPUs for leakage energy savings | |

| TW201337771A (en) | A method, apparatus, and system for energy efficiency and energy conservation including thread consolidation | |

| GB2547769A (en) | Method for booting a heterogeneous system and presenting a symmetric core view | |

| US9804876B2 (en) | Hypervisor-driven hibernation | |

| CN111008042B (en) | Efficient general-purpose processor execution method and system based on heterogeneous pipeline | |

| US9684541B2 (en) | Method and apparatus for determining thread execution parallelism | |

| CN101639814B (en) | Input-output system facing to multi-core platform and networking operation system and method thereof | |

| CN120179296B (en) | Pseudo-disordered instruction scheduling method based on branch jump | |

| WO2019153684A1 (en) | Method for automatically managing low-latency instruction scheduler | |

| Palomar et al. | Energy minimization at all layers of the data center: The ParaDIME project | |

| CN202711237U (en) | Opportunity multithreaded processor | |

| Chu | Dynamic Voltage and Frequency Scaling Optimization for | |

| Liu et al. | A HW/SW Co-design of Execution Migration for Shared-ISA Heterogeneous Chip Multiprocessors | |

| Le Sueur et al. | Operating System Support for the Heterogeneous OMAP4430 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20110427 Termination date: 20120226 |