WO1992020162A2 - Method and apparatus for resolving phase ambiguities in trellis coded modulated data - Google Patents

Method and apparatus for resolving phase ambiguities in trellis coded modulated data Download PDFInfo

- Publication number

- WO1992020162A2 WO1992020162A2 PCT/US1992/003656 US9203656W WO9220162A2 WO 1992020162 A2 WO1992020162 A2 WO 1992020162A2 US 9203656 W US9203656 W US 9203656W WO 9220162 A2 WO9220162 A2 WO 9220162A2

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- bit

- data

- output

- differential

- encoder

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/25—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM]

- H03M13/256—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM] with trellis coding, e.g. with convolutional codes and TCM

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/25—Error detection or forward error correction by signal space coding, i.e. adding redundancy in the signal constellation, e.g. Trellis Coded Modulation [TCM]

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/37—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35

- H03M13/39—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes

- H03M13/41—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes using the Viterbi algorithm or Viterbi processors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/18—Phase-modulated carrier systems, i.e. using phase-shift keying

- H04L27/186—Phase-modulated carrier systems, i.e. using phase-shift keying in which the information is carried by both the individual signal points and the subset to which the individual signal points belong, e.g. coset coding or related schemes

Definitions

- the present invention relates to data communications. More particularly, the present invention relates to a novel and improved method and apparatus for resolving phase ambiguities in trellis coded modulated data.

- the field of data communications is concerned with raising the data throughput of a transmission system with a limited signal to noise ratio (SNR).

- SNR signal to noise ratio

- the use of error correcting circuitry such as the Viterbi decoder allows system tradeoffs to be made with smaller SNRs or higher data rates to be used with the same bit error rate (BER).

- the decrease in the SNR needed is generally referred to as coding gain. Coding gain may be determined from simulated bit error performance curves. In a graph of simulated bit error performance curves the BER of uncoded and various code rate data is charted against E b /N 0 , where E b is the energy per bit and N o is the Gaussian White Noise energy per bit.

- the coding gain at any point along a bit error performance curve for a particular BER level is determined by subtracting the coded E b N D from the uncoded E b /N 0 .

- the coding rate and constraint length are used to define the Viterbi decoder.

- the coding rate (m/n) corresponds to the number of coding symbols produced (n) for a given number of input bits (m).

- the coding rate of 1/2 has become one of the most popular rates, although other code rates are also generally used.

- One class of codes with m ⁇ l are called punctured codes and are produced by discarding or erasing symbols from the rate 1/n code.

- the constraint length (K) is the length of the convolutional code used in the encoding of the data.

- the convolutional encoder can be thought of as an Finite Impulse Response (FIR) filter with binary coefficients and length K-l. This filter produces a symbol stream with 2 K_ 1 possible states.

- FIR Finite Impulse Response

- the basic principal of the Viterbi algorithm is to take a convolutionally encoded data stream that has been transmitted over a noisy channel and use the properties of the convolutional code to determine the transmitted bit stream.

- the Viterbi algorithm is a computationally efficient method of updating the conditional probabilities of the best state and the most probable bit sequence transmitted from the possible 2 K_1 states. In order to compute this probability, all 2 K*1 states for each bit must be computed. The resulting decision from each of these computations is stored as a single bit in a path memory.

- a chainback operation an inverse of the encoding operation, is performed in which the 2 K_l decision bits are used to select an output bit. After many states the most probable path will be selected with a high degree of certainty.

- the path memory depth must be sufficiently long to allow this probability to approach 1. For a rate 1/2 code, an exemplary path memory depth is about (5«K), or 35 states. For a rate 7/8 punctured code the optimal depth increases to 96 states.

- Constraint lengths of K less than 5 are too small to provide any substantial coding gain, while systems with K greater than 7 are typically too complex to implement as a parallel architecture on a single VLSI device.

- the constraint length increases, the number of interconnections in a fully parallel computation section increases as a function of (2 K_1 • L), where L is the number of bits of precision in the state metric computations. Therefore, where K is greater than 7, serial computation devices are generally used which employ large external random access memories (RAMs).

- Trellis coding is an attractive coding technique since it possesses an aspect which other coding techniques lack.

- the power of trellis coding lies in the fact that even though no apparent coding operation is performed on any other bit than the least significant bit of the input data, the decoder is able to provide error correction on all bits.

- TCM techniques to achieve efficient use of power-bandwidth resources has been limited to low speed applications in digital signal processor implementations.

- the use of PTCM techniques enable VLSI implementations of an encoder/decoder capable of operating at high rates.

- a decoder using PTCM techniques is capable of handling different modulation techniques, such as M-ary phase-shift keying (M-ary PSK) including Binary PSK (BPSK), Quadrature PSK (QPSK), 8-PSK, and 16-PSK.

- M-ary PSK phase-shift keying

- BPSK Binary PSK

- QPSK Quadrature PSK

- 8-PSK 8-PSK

- 16-PSK 16-PSK

- phase ambiguities in the transmitted data may occur in the transmission channel which must be resolved for proper decoding of the received data.

- phase ambiguities, or phase shifts, in the received data can be on the order of 2 ⁇ /M, 4 ⁇ /M, . . . , (M-l)(2 ⁇ /M).

- All phase ambiguities other than integer multiples 4 ⁇ /M can be resolved by known techniques, typically monitoring the growth rate of the state metrics in the Viterbi decoder. However, such techniques do not enable resolution of the phase ambiguities that are integer multiples 4 ⁇ /M. Therefore, the power of trellis coding has been unavailable to high speed data communication systems using M-ary PSK modulation.

- the present invention is a novel and improved method and apparatus which utilizes trellis coding in the encoding and decoding of data.

- an encoder and a decoder are disclosed which overcome the problems of transmission phase ambiguities in M-ary PSK modulation when using trellis coded data.

- the encoder receives sets of input data bits, differentially encodes one input data bit of each set and then convolutionally encodes the resultant bit to produce corresponding symbols.

- each set is comprised of two bits while in a 16-PSK modulation scheme each set is comprised of three bits.

- For 8-PSK modulation the other input data bit from each set of input data bits is directed onto one of two data paths in accordance with the state of the most significant symbol resulting from the convolutional encoding.

- 16-PSK modulation the other input data bits from each set of input data bits are directed onto one of two data paths in accordance with the state of the most significant symbol resulting from the convolutional encoding.

- the data on each data path are independently differentially encoded then remerged into a single output bit stream.

- the convolutional encoded symbols and the corresponding remerged bit, or bits in the case of 16-PSK modulation, form a signal or phase point used in carrier modulation.

- the least significant bits of the phase point is comprised of the convolutional encoder output while the more significant bits are comprised of the resultant multiplexed differential encoded bits.

- the decoder uses a Viterbi decoder and differential decoder to generate an error corrected estimate of the corresponding one bit of the original data.

- the Viterbi decoder uses branch metrics in the decoding process developed from information contained in the phase of the received signal.

- the Viterbi decoder output bit is also convolutionally encoded to produce corresponding symbols for use in the recovery of the other corresponding bits. In the case of 8-PSK modulation each most significant data bit is directed onto one of two data paths in accordance with the state of the most significant symbol of the convolutionally re- encoded symbol pair output.

- Figure 1 is a graph illustrating the signal space for 8-PSK modulation

- Figure 2 is a block diagram of an exemplary embodiment of the encoder of the present invention for 8-PSK modulation

- Figure 3 is a block diagram of an exemplary embodiment of the decoder of the present invention for data encoded by the encoder of Figure 2;

- Figure 4 is a graph illustrating the signal space for 16-PSK modulation;

- Figure 5 is a graph illustrating a data map of the two most significant bits of data in 16-PSK modulation

- Figure 6 is a block diagram of an exemplary embodiment of the encoder of the present invention for a 16-PSK modulation

- Figure 7 is a block diagram of an exemplary embodiment of the decoder of the present invention for data encoded by the encoder of Figure 5.

- Figure 1 illustrates the signal space for 8-PSK modulation for trellis coded data.

- the signals used in 8-PSK modulation are proportional to:

- each sector Zi in which the signal S ⁇ corresponds is represented by a three-bit sector value (a, b, c) representative of that sector according to the exemplary mapping scheme illustrated in Figure 1.

- bit value a which is the most significant bit of the sector value, bit a, identifies the half plane

- bits (b, c) identify the sector within the half plane.

- a three-bit sector value of 111 would be indicative of a signal corresponding to sector number 6 (Z & ) and would be transmitted as a carrier phase shift of 270°.

- a carrier signal received having a phase shift of 270° would also correspond to a sector value of 111, provided no phase shift is experienced in the transmission channel.

- each sector value corresponds to one sector, or wedge, of the IQ planes of Figures 1 and 4. It is critical to understand that the sector values are not the same as traditional "decision regions".

- the sector value for a given sector corresponds to the three-bit value for 8-PSK, or four-bit value for 16-PSK, mapped to the phase point bordering the sector on the side clockwise from the center of the sector. Decision regions are generally centered on the transmitted phase points, while in this discussion sectors are immediately counterclockwise from the phase points. Decision regions normally associated with PSK modem designs are not relevant to the present discussion.

- phase ambiguities in the received carrier may result from phase shifts in the transmission channel.

- phase ambiguities that are integer multiples ⁇ /2 need to be resolved by techniques previously unknown.

- the encoder and decoder as disclosed herein utilizes techniques which enable the resolution of such phase ambiguities.

- the receiver (decoder) phase can differ from the transmitter (encoder) phase, i.e. a phase shift in the transmitted data with respect to the received data, as discussed above.

- the receiver may differ from the transmitter phase by 0°, 45°, 90°, 135°, 180°, 225°, 270° or 315°.

- the phase shifts of 45°, 135°, 225° and 315° are detected by a Viterbi or convolutional decoder at the receiver since in these cases the effective error rate of the channel in the absence of noise is 50%.

- phase shifts of 90°, 180° and 270° are undetected by the Viterbi decoder and thus other means must be utilized to correct for these conditions.

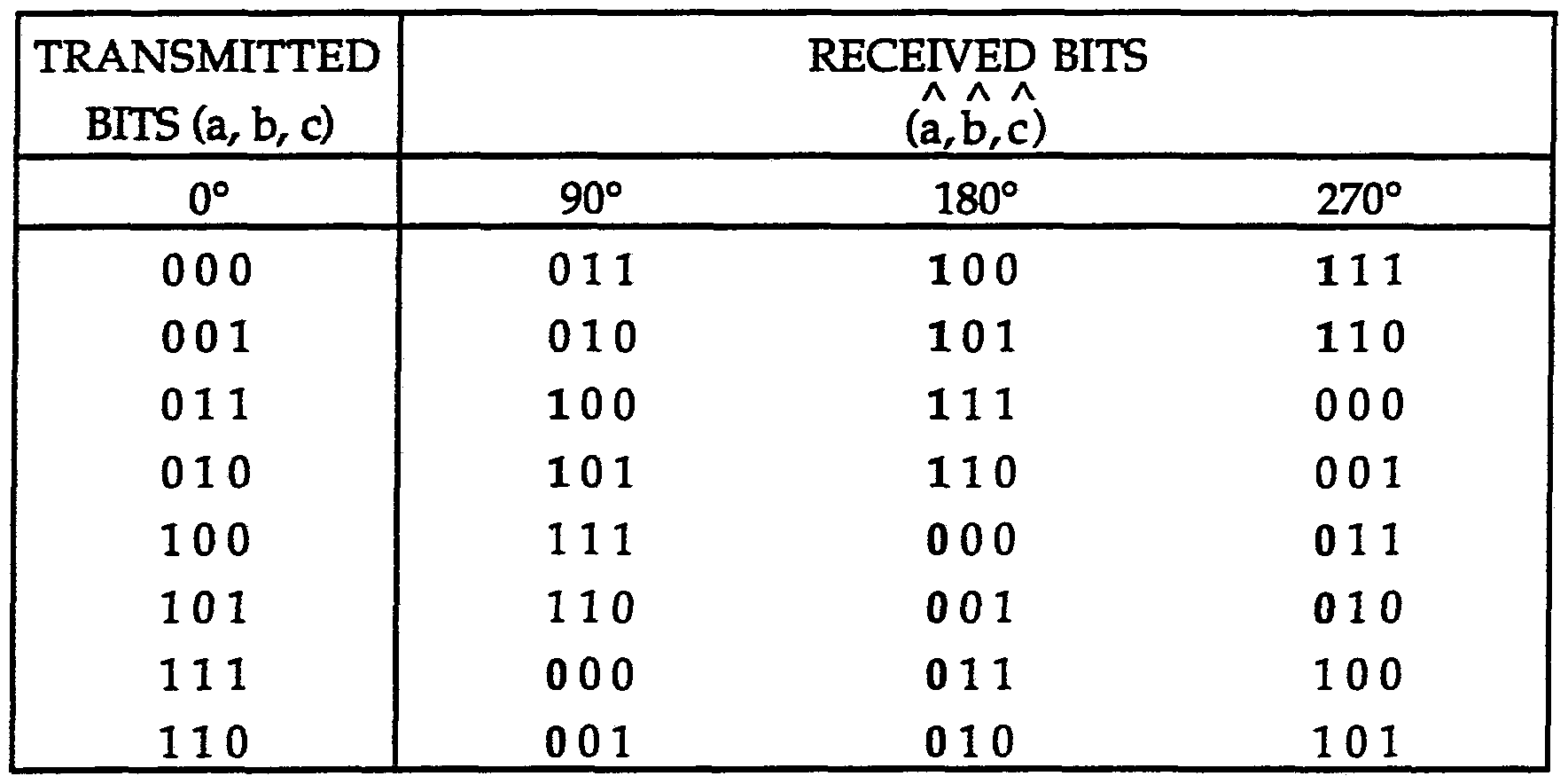

- Table I illustrates the transmitted data and corresponding received data for phase shifts in increments of 90°. Since only a phase shift of 90°, 180° and 270° and no other noise is assumed in this discussion, the

- ⁇ ⁇ ⁇ symbols (a,b,c) can be used to refer to either the received phase point or the corresponding sector value.

- bits b, and c which are coded with a transparent convolutional code are always either the right sense or inverted when a phase shift is experienced in the transmission channel.

- the use of a standard binary differential encoder just prior to the convolutional encoder in the TCM encoder and after the Viterbi decoder in the TCM decoder will correct the phase ambiguities in these two least significant bits.

- bit a is a more difficult problem to overcome, particularly for phase shifts of 90° and 270° where it is not complemented consistently.

- the Viterbi decoder For 8-PSK modulation, the Viterbi decoder produces an estimate a ' of the most significant bit a of the transmitted phase point along with the symbol ⁇ , an estimate of ⁇ discussed later herein.

- the manner of operation of the Viterbi decoder is the subject of a copending patent application entitled "Viterbi Decoder Bit Efficient Chainback Memory Method And Decoder Incorporating Same", filed , bearing U.S. Patent Application Serial

- a' is the same as a.

- bit a With respect to the case of a 180° phase shift the uncoded bit, bit a is always inverted with respect to the corresponding transmitted bit, while for phase shifts of 90° and 270° only certain ones of the uncoded bit a are inverted. For purposes of illustration in Table I, each occurrence of an inverted uncoded bit a is highlighted. Whether or not the uncoded ⁇ ⁇ bit a is inverted can be identified by the middle bit, bit b, of the three

- ⁇ ⁇ bit b is a "0".

- the uncoded bit a is unchanged when the error corrected version of the coded middle bit b is a "1".

- ⁇ ⁇ middle bit b is a "1".

- the uncoded bit a is unchanged when the error

- ⁇ corrected version of the coded middle bit b is a "0".

- Straight differential encoding of the uncoded bit a in the case of a phase shift of 180° will resolve the constant inversion. However, such a technique alone will not resolve inconsistent inversions in the uncoded

- the coded middle bit b preferably the error corrected version thereof, can therefore be used as an indicator of inversions as a supplement to differential encoding.

- the coded middle bit b is used to split the stream of bits ⁇ into two streams ⁇ i and ⁇ ⁇ .

- the coded middle bit b is then used to remerge the two differentially encoded bit streams ai and a 2 to produce each bit a.

- the coded bits b and c are decoded using a

- bit b ' is used to split the stream of most significant bits a * provided by the Viterbi decoder into two streams ai' and a 2 * .

- Each of the two streams of uncoded bits ai' and a ⁇ ' are differentially decoded with a standard binary differential decoder independently of each other to produce the corresponding bits streams ⁇ i and ⁇ ⁇ -

- the coded middle ⁇ bit b' is then used to remerge the two differentially encoded bit streams ⁇ i and ⁇ i to produce each bit ⁇ .

- FIG. 2 illustrates an exemplary embodiment of a trellis coded modulation (TCM) encoder 10 of the present invention configured for 8-PSK modulation where no phase reference is provided.

- Encoder 10 receives two bits of input data ( ⁇ , ⁇ ) and generates a corresponding three-bit phase point value (a, b, c).

- the phase point value is output from encoder 10 to an 8-PSK phase mapper or modem 12 where the phase of a carrier signal is shifted in accordance with the data sector mapping scheme of Figure 1.

- A is the signal amplitude (typically a constant)

- fc is the carrier frequency

- ⁇ is the phase offset corresponding to the sector value

- Modem 12 may be configured as a conventional phase shift keyed

- PSK phase shift techniques well known in the art.

- modem 12 is typically configured to transmit the carrier signal in the form according to equation (1).

- cos (x + y) (cos x • cos y) - (sin x • sin y) (5)

- a QPSK modem structure may be implemented using an I and Q constellation corresponding to Figure 1 to represent the carrier phase shift where :

- Modem 12 may also be configured to include circuitry for converting the baseband signal to RF frequencies, RF transmission circuitry and an antenna system as is well known in the art.

- Encoder 10 in an exemplary form is comprised of multiplexers 14 and 16; differential encoders 18, 20 and 22; and convolutional encoder 24.

- Encoder 10 is preferably of a VLSI construction with the elements thereof individually of conventional design.

- Data is input to encoder 10 two bits at a time, bits ( ⁇ , ⁇ ), with bit ⁇ input to multiplexer 14, and bit ⁇ input to differential encoder 20.

- bits ( ⁇ , ⁇ ) In each two-bit input of data, bits ( ⁇ , ⁇ ), the bit ⁇ is input to differential encoder 22 where it is differentially encoded.

- Techniques for the differential encoding of bit ⁇ , along with circuit designs for differential encoders are well known in the art.

- Each differentially encoded bit or symbol ( ⁇ ) corresponding to an input bit ⁇ is output from differential encoder 22 as an input to convolutional encoder 24.

- Techniques for the convolutional encoding of bit ⁇ , along with circuit designs for convolutional encoders, are well known in the art.

- the bits (b, c) output from encoder 10 are provided as inputs to modem 12.

- the most significant bit, bit b, of the bit pair (b, c) is also output from encoder 24 as a select signal to a select input to each of multiplexers 14 and 16.

- Multiplexer 14 is typically a 1:2 multiplexer which provides data presented at a data input thereof to a selected one of two outputs in accordance with the state of the select signal provided at the select input thereof.

- the data presented at the input of multiplexer 14 is the bit ⁇ of the current bit pair ( ⁇ , ⁇ ).

- bit ⁇ When the bit b state is in one logic state, for example a logical "0", the bit ⁇ is output from multiplexer 14 at a first output as the bit ⁇ i. Similarly, when the bit b state is in the other logic state, for example a logical "1", the bit ⁇ is output from multiplexer 14 at a second output as the bit a - In essence, the stream of bits ⁇ is broken into two bit streams according to the state of the most significant bit, bit b, of the bit pair (b, c) output from convolutional encoder 24.

- Each output of multiplexer 14 is coupled to a respective input of differential encoders 18 and 20.

- the bit ⁇ i is therefore provided to differential encoder 18 while the bit 0:2 is respectively to differential encoder 20.

- Differential encoders 18 and 20 each differentially encode the respectively received bit ⁇ i or ci2 with respect to a correspondingly previously received bit.

- the differential encoding of the bits ⁇ i and 0 * 2 can be accomplished by any of the techniques well known in the art. Differential encoders 18 and 20 are thus each exercised only when a new input bit is provided thereto.

- Each of differential encoders 18 and 20 respectively provide an output bit ai or a2 for each corresponding bit ⁇ i or 0.2 received.

- the bits ai or a2 are respectively provided from differential encoders 18 and 20 to separate data inputs of multiplexer 16.

- Multiplexer 16 is typically a 2:1 multiplexer which, in accordance with a select signal provided at a select input, provides data at an output selected from data presented at two inputs.

- the bits ai and a2 as presented at the inputs of multiplexer 16 are provided at the output of multiplexer 16, as the bit or symbol a.

- the bit a is determined in accordance with the state of the bit b generated from bit ⁇ of the current bit pair ( ⁇ , ⁇ ). In essence, the bit streams ai and a2 are merged into a single bit stream corresponding to the most significant bit, bit b, of the bit pair (b, c) output from convolutional encoder 24.

- the bit a is provided, along with the bits b and c, at respective inputs of modem 12.

- Modem 12 assembles the data bits a, b and c in order with the bits a and c respectively being the most significant and least significant bits of a three-bit phase point value.

- Modem 12 provides the shifted phase carrier signal (0) as discussed above.

- Figure 3 illustrates an exemplary embodiment of a modem 30 and

- TCM decoder 32 of the present invention configured for demodulation of an 8-PSK signal where no phase reference is provided.

- Modem 30 receives

- phase shifted carrier signal 0 which contains information in the form of the phase shift in the carrier.

- channel conditions may arise which can result in a phase shift in the transmitted signal ⁇ .

- the received signal ⁇ may be expressed by the following equation:

- Modem 30 converts the received signal ⁇ to quantized I and Q components where :

- the I and Q components are provided to decoder 32 where converted to a

- Modem circuitry and techniques well known in the art may be utilized to convert the phase of the received signal to I and Q components.

- Modem 30 may further include an antenna system, RF circuitry and frequency downconversion circuitry necessary to convert the received signal to baseband as is well known in the art.

- Modem 30 provides an output of the I and Q components to decoder 32 for decoding and error correction.

- Decoder 32 is comprised of branch metrics and sector determination circuitry 34; branch metrics and sector rotation circuitry 36; normalization rate detection circuitry 38; Viterbi decoder 40; multiplexers 42 and 44; differential decoders 46, 48 and 50; and convolutional encoder 52.

- decoder 32 is also preferably of a VLSI construction with the elements thereof of conventional design.

- circuitry 34 and 38 may also be provided on a single VLSI chip, it is preferred that these elements be provided separately to enable flexibility for the end user and be of a conventional design.

- convolutional encoder 52 may be integrated within Viterbi decoder 40.

- determination circuitry 34 typically includes an arctangent lookup table (not shown) typically

- ⁇ ⁇ implemented as a read only memory storing values of ⁇ .

- the value of ⁇ is provided to a sector value and branch metric lookup table (not shown), also typically a read only memory, which stores a three-bit sector value along with the branch metrics corresponding to each value of ⁇ .

- the sector value and branch metrics are output from determination circuitry 34 to rotation circuitry 36.

- Rotation circuitry 36 rotates the three-bit sector value and corresponding branch metrics in the event of a detection by detection circuitry 38 of an usually high normalization rate in Viterbi decoder 40. In the 8-PSK system, a rotation corresponding to a 45° shift in the sector value and related branch metrics is performed.

- Rotation circuitry 36 may again be configured as a lookup table which is responsive to a signal from detection circuitry 38 for shifting the sector value and branch metrics. Further details on this rotation is discussed below.

- Rotation circuitry 36 also contains a delay element (not shown) for providing a delay in the propagation of the sector value as output from rotation circuity 36 due to the computational time required by the Viterbi decoder 40.

- decoder 40 uses the branch metrics and the sector values (a, b, c ), rotated if necessary, decoder 40 produces best estimates of ⁇ and a, respectively

- ⁇ ⁇ denoted as ⁇ and a'.

- ⁇ and a' a simplification in the actual decoding may be used that is the subject of the previously mentioned copending application.

- Decoder 40 as previously mentioned also provides an output of normalization data which is used by normalization rate detection circuitry 38 to detect a high normalization rate indicative of channel phase shifts of 45°, 135°, 225° and 315°.

- detection circuitry 38 Upon detection of a high normalization rate, detection circuitry 38 provides a control signal to rotation circuitry 36 which in response thereto provides a shift in the branch metrics corresponding to a shift in the signal space of ⁇ /4, along with a

- Such a shift in the sector value results in the sector value corresponding to a phase shift of 0°, 90°, 180° and 270°.

- the Viterbi decoder is capable of recovering data.

- the Viterbi decoder is not capable of detecting that the data is in error as a result of a channel phase shift.

- the Viterbi decoder would therefore produce erroneous estimates of the original data.

- the present invention augments the Viterbi decoder so as to permit the resolution of phase ambiguity errors in the data caused by a channel phase shift.

- Decoder 40 provides an output of the bit ⁇ as an input to both differential decoder 50 and convolutional encoder 52. Since the bit ⁇ was differentially encoded prior to convolutional encoding on the transmit

- the bit ⁇ is an estimate of the originally encoded bit ⁇ .

- bit stream of a ' must be broken into two bit streams with each -bit stream independently differentially decoded then recombined into a single bit stream.

- the breaking of the bit stream into two bit streams and recombining is similar in manner to that of the encoder of Figure 2.

- Control over the separation and combining of the broken bit stream is provided by the middle bit of the sector value.

- this error since errors may occur in the middle bit position of the sector value as received, i.e. in bit b, it is preferred that this error be corrected prior to usage of the bit in

- ⁇ ⁇ bits (b 1 , c ') are estimates of the originally transmitted bits (b, c) that errors

- bit ⁇ output from decoder 40 is also provided as an input of convolutional encoder 52 so as to produce

- Multiplexer 42 is typically a 1:2 multiplexer which provides data presented at a data input thereof to a selected one of two outputs in accordance with the state of the select signal provided at the select input thereof. In this particular case, the data presented at the input of

- ⁇ multiplexer 42 is the bit a' from the Viterbi decoder. With the select signal

- bit b ' generated from bit ⁇ determines at which output of

- bit a ' is presented.

- bit b ' state is in one logic state, for example a logical "0"

- the bit a' is output from multiplexer 42 at a

- bit a ' A first output as the bit a ' ⁇ .

- bit b ' state is in the other logic state, for example a logical "1”

- the bit a ' is output from multiplexer 42 at a second output as the bit a '2-

- bit stream a ' is broken into two bit streams according to the state of the most

- bit b ' of the bit pair (b ', c ') output from convolutional encoder 52 Each output of multiplexer 42 is coupled to a respective input of differential decoders 46 and 48.

- the bit a ' ⁇ is therefore provided to decoder 46 while the bit a '2 is respectively to decoder 48.

- Differential decoders 46 and 48 each differentially decode the respectively received bit a' ⁇ or a '2 with respect to a correspondingly previously received bit.

- the differential decoding of the bits a' ⁇ and a '2 can be accomplished by any of the techniques well known in the art. Differential decoders 46 and 48 are thus each exercised only when a new input bit is provided thereto.

- ⁇ ⁇ differential decoders 46 and 48 respectively provide an output bit c or 0:2

- bits ⁇ i or 02 are respectively provided from differential decoders 46 and 48 to separate data inputs of multiplexer 44.

- Multiplexer 44 is typically a 2:1 multiplexer which, in accordance with a select signal provided at a select input, provides data at an output

- ⁇ ⁇ selected from data presented at two inputs.

- the bits ⁇ i and 0 2 as presented at the inputs of multiplexer 44 are provided at the output of multiplexer 44, as the bit ⁇ .

- the bit ⁇ i and (X 2 selected for output is

- bit stream c and CC 2 is merged into a single bit stream ⁇

- bit b ' of the bit pair (b ', c ') output from convolutional encoder 52.

- Figure 4 illustrates the signal space and corresponding data mapping.

- the signal space is defined by sixteen sectors with the signal falling at the beginning of a sector.

- each sector to which a signal corresponds is represented by a four-bit sector value (w, x, y, z).

- the receiver may differ from the transmitter phase by 0°, 22.5°, 45°, 67.5°, 90°, 112.5°, 135°, 157.5°, 180°, 202.5°, 225°, 247.5°, 270°, 292.5,° 315°, or 337.5°.

- Phase shifts of 22.5°, 67.5°, 112.5°, 157.5°, 202.5°, 247.5°, 292.5,° 315°, or 337.5° are detected at the receiver by a

- Viterbi decoder since in these cases the effective error rate of the channel in the absence of noise is again 50%. Again a technique used for detecting these particular phase shifts is monitoring the growth of the state metrics, i.e the normalization rate of the state metrics is abnormally high. Upon detecting this phase condition, correction may be made by shifting the branch metrics, such as by simply stepping ahead by ⁇ /8 in the signal space. However, phase shifts of 45°, 90°, 135°, 180°, 225°, 270° and 315° are undetected by the Viterbi decoder and thus other means must be utilized to correct for these conditions. Table II illustrates the transmitted data and corresponding received data for phase shifts in increments of 45°.

- phase point as received, bits w and x is a more difficult problem to overcome, particularly for phase shifts of 45°, 135°, 225° and 315° where one, both or neither of these bits are complemented.

- phase shifts of 90°, 180° and 270° the coded bits (y, z) are correct while for phase shifts of 45°, 135°, 225° and 315° the coded bits (y,z) are mapped to their inverse with respect to the corresponding transmitted bits.

- the use of a differential encoder in the encoder and decoder will ensure that the received bits (y, z) are correct.

- the Viterbi decoder produces an estimate (w', x') of the most significant bits (w, x) of the transmitted phase

- the uncoded bits bits (w, x) are both always shifted by a fixed amount of rotation with respect to the corresponding transmitted bits.

- the uncoded bits (w, x) may be represented by a Gray code.

- the uncoded bits are respectively rotated by a fixed amount, i.e. -90°, 180° and + 90°, according to the mapping scheme of Figure 5.

- a fixed amount of rotation is not present in the uncoded bits (w, x).

- each occurrence of a rotated pair of uncoded bits (w, x) is highlighted, hi the case of phase shifts of 90°, 180° and 270° the fixed rotation is corrected for by using four-phase (4 ⁇ ) differential encoding/ decoding.

- a rotation in the uncoded bits (w, x) occurs, a rotation of the bits according to the map of Figure 5, can be identified by the bit y of the four bits (w, x, y, z).

- bit y is preferably used, bit y ', Table II for purposes of illustration considers bit y to not need correction and be the same as the error corrected bit y '. Referring to Table II, in the case of a 45° phase shift the uncoded bits (w, x) are rotated by -90° when the error corrected version of the coded

- a ⁇ ⁇ bit y is a "1".

- the uncoded bits (w, x) are unchanged when the error corrected version of the coded bit y is a "0". In the case of a 90° phase shift

- the uncoded bits (w,x) are rotated by -90° regardless of the state of the error ⁇ corrected version of the coded bit y .

- the uncoded bits (w, x) are rotated by 180° when the error corrected version of

- a ⁇ ⁇ the coded bit y is a "1".

- the uncoded bits (w, x) are rotated by -90° when

- the error corrected version of the coded bit y is a "0".

- the uncoded bits (w, x) are rotated by 180° regardless of the state of the error corrected version of the coded bit y.

- the coded bit y is a "0".

- the uncoded bits (w, x) are rotated by +90° regardless of the state of the error corrected version of the coded bit y .

- the uncoded bits (w, x) are unchanged when the error corrected version of the

- a ⁇ ⁇ coded bit y is a "1". However,the uncoded bits (w, x) are rotated by +90

- the coded bit y preferably the error corrected version thereof (y'), can therefore be used as an indicator of rotation as a supplement to differential encoding.

- the coded bit y is used to split the stream of bit pairs ( ⁇ , ⁇ ), into a two separate streams of bit pairs ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ ) 2 -

- Each of the bit pair streams of uncoded bits ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ ) 2 are differentially encoded with a standard four-phase differential encoder independently of each other.

- the coded bit y is then used to remerge the two differentially encoded bit streams ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ ) 2 to produce the bits (w, x).

- the coded bits (y, z) are decoded using a Viterbi decoder for error detection and correction.

- the bit ⁇ , resulting from the Viterbi decoding, is then convolutional encoded to produce the

- the bit y ' is used to split the stream of paired bits (w 1 , x)', also output from the Viterbi decoder, into two streams, (w*, x' and (w', x') 2 -

- Each of the two streams of uncoded bits (w', x') ⁇ and (w', x') 2 are differentially decoded with a standard four-phase differential decoder independently of each other to produce the corresponding bits streams ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ ) 2 -

- the coded bit y * is then used to remerge the two differentially encoded bit streams ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ ) 2 to produce the bits ⁇ and ⁇ .

- ⁇ ⁇ selection permits rotations in the bit pair (w', x') to be resolved.

- Figure 6 illustrates an exemplary embodiment of a trellis coded modulation encoder 100 of the present invention configured for 16-PSK modulation where again no phase reference is provided.

- Encoder 100 receives three bits of input data ( ⁇ , ⁇ , p) and generates the corresponding four-bit phase point value (w, x, y, z).

- phase point value is output from encoder 100 to a 16-PSK mapper or modem 102 where the phase of a carrier signal is shifted in accordance with the the data sector mapping scheme of Figure 4.

- A is the signal amplitude (typically a constant)

- fc is the carrier frequency

- ⁇ is the phase offset corresponding to the sector value

- Modem 102 may be configured as a conventional phase shift keyed (PSK) digital transmission modem using phase shift techniques well known in the art.

- PSK phase shift keyed

- Encoder 100 in an exemplary form is comprised of multiplexers 104 and 106; four-phase differential encoders 108 and 110; binary differential encoder 112; and convolutional encoder 114.

- Encoder 100 is preferably of a

- Data is input to encoder 100 three bits at a time, bits ( ⁇ , ⁇ , p), with bits ( ⁇ , ⁇ ) input to multiplexer 104, and bit p input to differential encoder 112.

- each bit p is input to differential encoder 112 and differentially encoded with respect to a previously received bit p.

- Techniques for the differential encoding of bit p, along with circuit designs for differential encoders are well known in the art.

- Each differentially encoded bit or symbol ( ⁇ ) corresponding to an input bit p is output from differential encoder 112 as an input to convolutional encoder 114.

- Techniques for the convolutional encoding of bit ⁇ , along with circuit designs for convolutional encoders are well known in the art.

- the bits (y, z) output from encoder 100 are provided as inputs to modem 102.

- the most significant bit, bit y, of the bit pair (y, z) is also output from convolutional encoder 114 as a select signal to a select input to each of multiplexers 104 and 106.

- Multiplexer 104 is typically a 1:2 multiplexer which provides data presented at a data pair input thereof to a selected one of two data pair outputs in accordance with the state of the select signal provided at the select input thereof.

- the data presented at the data pair input of multiplexer 104 are the bits ( ⁇ , ⁇ ) of the current bit group ( ⁇ , ⁇ , p).

- the state of the bit y generated from bit p of the current bit group ( ⁇ , ⁇ , p) determines at which data pair output of multiplexer 104 the bit pair ( ⁇ , ⁇ ) are presented.

- the bit y state is in one logic state, for example a logical "0"

- the bit pair ( ⁇ , ⁇ ) are output from multiplexer 104 at a first output as the bit pair ( ⁇ , ⁇ ) ⁇ .

- bit pair ( ⁇ , ⁇ ) are output from multiplexer 104 at a second output as the bit pair ( ⁇ , ⁇ )2-

- bit pair ( ⁇ , ⁇ ) are broken into two bit streams according to the state of the most significant bit, bit y, of the bit pair (y, z) output from convolutional encoder 114.

- Each bit pair output of multiplexer 104 is coupled to a respective bit pair input of differential encoders 108 and 110.

- the bit pair ( ⁇ , ⁇ ) ⁇ is therefore provided to differential encoder 108 while the bit pair ( ⁇ , ⁇ )2 is respectively to differential encoder 110.

- Differential encoders 108 and 110 each differentially encode the respectively received bit pairs ( ⁇ , ⁇ ) ⁇ or ( ⁇ , ⁇ )2 with respect to a correspondingly previously received bit pair.

- the differential encoding of the bit pairs ( ⁇ , ⁇ ) ⁇ or ( ⁇ , ⁇ )2 can be accomplished by any of the techniques well known in the art. Differential encoders 108 and 110 are thus each exercised only when a new input bit pair is provided thereto.

- Each of differential encoders 108 and 110 respectively provide an output bit pair (w, x) ⁇ or (w, x)2 for each corresponding bit pair ( ⁇ , ⁇ ) ⁇ or ( ⁇ , )2 received.

- the bit pairs (w, x) ⁇ and (w, x)2 are respectively provided from differential encoders 108 and 110 to separate data pair inputs of multiplexer 106.

- Multiplexer 106 is typically a 2:1 multiplexer which, in accordance with a select signal provided at a select input, provides data at a data pair output selected from data presented at two data pair inputs.

- the bit pairs (w, x) ⁇ and (w, x)2 as presented at the data pair inputs of multiplexer 106 are provided at the data pair output of multiplexer 106, as the bit or symbol pair (w, x).

- the bit pair (w, x) is determined in accordance with the state of the bit y generated from bit p of the current bit group ( ⁇ , ⁇ , p).

- bit pair streams (w, x) ⁇ and (w, x)2 are merged into a single bit pair stream corresponding to the most significant bit, bit y, of the bit pair (y, z) output from convolutional encoder 114.

- the bit pair (w, x) is provided, along with the bit pair (y, z), at respective inputs of modem 102.

- Modem 102 assembles the data bits w, x, y and z with the bits ordered (w, x, y and z) from most significant to least significant bits of a four-bit phase point value.

- Modem 102 provides the shifted phase carrier signal ( ⁇ ) as discussed above.

- Figure 7 illustrates an exemplary embodiment of a modem 120 and

- TCM decoder 122 of the present invention configured for demodulation of an 16-PSK signal where no phase reference is provided.

- the received signal ⁇ again may be expressed by equation (10).

- Modem 120 converts the received signal ⁇ to quantized I and Q components according to equation (10).

- the I and Q components are provided to decoder 122 where converted to a four-bit sector

- Modem circuitry and techniques well known in the art may be utilized to convert the phase of the received signal to I and Q components.

- Modem 120 may further include an antenna system, RF circuitry and frequency downconversion circuitry necessary to convert the received signal to baseband as is well known in the art.

- Modem 120 provides an output of the I and Q components to decoder 122 for decoding and error correction.

- Decoder 122 is comprised of branch metrics and sector determination circuitry 124; branch metrics and sector rotation circuitry 126; normalization rate detection circuitry 128; Viterbi decoder 130; multiplexers 132 and 134; four-phase differential decoders 136 and 138; binary differential decoder 140; and convolutional encoder 142.

- decoder 122 is again also preferably of a VLSI construction with the elements thereof of conventional design.

- circuitry 124 and 128 may also be provided on a single VLSI chip, it is preferred that these elements be provided separately to enable flexibility for the end user and be of a conventional design.

- convolutional encoder 142 may be integrated within Viterbi decoder 130.

- the I and Q components are provided to determination circuitry 124 which typically includes an arctangent lookup table (not shown) typically implemented as a read only memory storing values of ⁇ .

- the value of ⁇ is provided to a sector value and branch metric lookup table (not shown), also typically a read only memory, which stores a four-bit sector value along with the branch metrics corresponding to each value of ⁇ .

- the sector value and branch metrics are output from determination circuitry 124 to rotation circuitry 126.

- Rotation circuitry 126 rotates the four-bit sector value and corresponding branch metrics in the event of a detection by detection circuitry 128 of an usually high normalization rate in Viterbi decoder 130. In the 16-PSK system, a rotation corresponding to a 22.5° shift in the sector value and related branch metrics is performed. Rotation circuitry 126 may again be configured as a lookup table which is responsive to a signal from detection circuitry 128 for shifting the sector value and branch metrics. Further details on this rotation is discussed below.

- Rotation circuitry 126 also contains a delay element (not shown) for providing a delay in the propagation of the sector value as output from rotation ⁇ rcuity 126 due to the computational time required by the Viterbi decoder 130.

- decoder 130 uses the branch metrics and the sector values (w, x,y, z), rotated if necessary, decoder 130 produces best estimates of ⁇ and (w, x), respectively

- Decoder 130 also provides an output of normalization data which is used by normalization rate detection circuitry 128 to detect a high normalization rate indicative of channel phase shifts of 22.5°, 67.5°, 112.5°, 157.5°, 202.5°, 247.5°, 292.5,° 315°, or 337.5°.

- detection circuitry 128 Upon detection of a high normalization rate, detection circuitry 128 provides a control signal to rotation circuitry 126 which in response thereto provides a shift in the branch metrics corresponding to a shift in the signal space of ⁇ /8, along with a corresponding shift in the sector value bits (w,x,y,z). Such a shift in the sector value results in the sector value corresponding to a phase shift of one of 0°, 45°, 90°, 135°, 180°,

- the Viterbi decoder is capable of recovering data.

- the Viterbi decoder is not capable of detecting that the data is in error as a result of a channel phase shift.

- the Viterbi decoder would therefore produce erroneous estimates of the original data.

- the present invention augments the Viterbi decoder so as to permit the resolution of phase ambiguity errors in the data caused by a channel phase shift.

- Decoder 130 provides an output of the bit ⁇ as an input to both differential decoder 140 and convolutional encoder 142. Since the bit ⁇ was differentially encoded prior to convolutional encoding on the transmit

- the bit p is an estimate of the originally encoded bit p.

- the stream of paired bits (w', x') must be broken into two two-bit streams with each bit stream independently four-phase differentially decoded then recombined into a single bit pair stream.

- the breaking of the bit pair stream into two bit pair streams and recombining is similar in manner to that of the encoder of Figure 6. Control over the separation and combining of the broken bit pair stream is provided by the bit y of the sector value. However, since errors may occur in this bit of the sector value as received, it is preferred that this error be corrected prior to

- bit ⁇ A usage of the bit in decoding the bit pair stream (w', x ')• Therefore the bit ⁇ , which corresponds indirectly to a corrected sector value, is convolutionally encoded to produce the bits (y ', z').

- bit ⁇ output from decoder 130 is also provided as an input of convolutional encoder 142 so as to produce bits (y ', z ') which are corrected estimates of the transmitted phase point bits (y, z).

- the most significant bit (y ') of the bit pair (y', z 1 ) is output from convolutional encoder 142 as a select signal to a select input of each of ⁇ multiplexers 132 and 134.

- bit z ' is also produced by convolutional encoder 142 this bit is not used.

- Multiplexer 132 is typically a 1:2 multiplexer which provides data presented at a data pair input thereof to a selected one of two data pair outputs in accordance with the state of the select signal provided at the select input thereof.

- the data presented at the input of multiplexer 132 is the bit pair (w', x ') from the Viterbi decoder.

- the select signal input coupled to the bit y' output of convolutional encoder 142, the state of the bit y ' generated from bit ⁇ determines at which data pair output of multiplexer 132 the bit pair (w 1 , x ') is presented.

- bit pair (w', x') When the bit y' state is in one logic state, for example a logical "0", the bit pair (w', x') is output from multiplexer 132 at a first data pair output as the bit pair (w 1 , x') ⁇ - Similarly, when the bit y ' state is in the other logic state, for example a logical "1", the bit pair (w', x ') is output from multiplexer 132 at a second data pair output as the bit pair (w 1 , x * )2- In essence, the bit pair stream (w 1 , x ') is broken into two bit pair streams according to the state of the most significant bit, bit y ' of the bit pair (y ', z') output from convolutional encoder 142.

- Each data pair output of multiplexer 132 is coupled to a respective input of four-phase differential decoders 136 and 138.

- the bit pair (w', x') ⁇ is therefore provided to decoder 136 while the bit pair (w', x')2 is respectively to decoder 138.

- Differential decoders 136 and 138 each differentially decode, using four-phase techniques, the respectively received bit pair (w 1 , x') ⁇ or (w', x')2 with respect to a correspondingly previously received bit pair.

- the differential decoding of the bit pair (w', x') ⁇ or (w, x')2 can be accomplished by any of the techniques well known in the art for four-phase differential decoding.

- Differential decoders 136 and 138 are thus each exercised only when a new input bit pair is provided thereto.

- Each of differential decoders 136 and 138 respectively provide an output bit pair ( ⁇ , ⁇ or ( ⁇ , ⁇ )2 for each corresponding input bit pair (w 1 , x ') ⁇ or (w, x ')2-

- the bit pairs ( ⁇ , ⁇ ) ⁇ or ( ⁇ , ⁇ )2 are respectively provided from differential decoders 136 and 138 to separate data inputs of multiplexer 134.

- Multiplexer 134 is typically a 2:1 multiplexer which, in accordance with a select signal provided at a select input, provides a data pair at a data pair output selected from data pairs presented at two data pair inputs.

- the bit pairs ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ )2 as presented at the data pair inputs of multiplexer 134 are provided at the data pair output of multiplexer 134, as the bit pair ( ⁇ , ⁇ ).

- the bit pair ( ⁇ , ⁇ ) ⁇ or ( ⁇ , ⁇ selected for output is

- bit pair stream ( ⁇ , ⁇ ) ⁇ and ( ⁇ , ⁇ )2 is merged into a single bit pair stream ( ⁇ , ⁇ ) corresponding to the most significant bit, bit y ', of the bit pair (y', z') output from convolutional encoder 142.

- the encoder and decoder may be formed in VLSI form on separate chips or preferably on a single chip. Furthermore, the encoder for both the 8-PSK and 16-PSK modulation may be integrally formed using a sharing of common elements, and similarly so for the decoder.

- encoders 24 and 114 would be configured as block encoders. In these alternate embodiments consideration must be given to the timing of data flowing through encoders 10 and 100.

- Block encoders need to have an entire input block of bits ⁇ or p to generate a corresponding output block. Since the output bits from the block encoders control the multiplexed encoding of the bits ⁇ and ( ⁇ , ⁇ ) it is necessary to insure coordination between the output of the block encoders with the input to the multiplexers of the corresponding bits ⁇ and ( ⁇ , ⁇ ).

- Circuitry such as a memory or shift register(s) prior to the input of multiplexers 14 and 104 would receive the ⁇ or ( ⁇ , ⁇ ) bits.

- the clocking of these bits out of the shift registers) would be in coordination with the output of the coded bits from the block encoder as provided by the appropriate addressing/timing logic. This technique would ensure that each bit in the block of encoded bits output from the block encoder would correspond to one of an input ⁇ or ( ⁇ , ⁇ ) bit(s) in controlling the multiplexed encoding of these bits.

- Viterbi decoders 40 and 130 would be replaced by corresponding block decoders with the least significant

- Encoders 52 and 142 would also be configured as block encoders identical respectively to the block encoders in the corresponding encoder 10 or 100. Again it is necessary to control the timing of the bits a and (w, x) through the multiplexed decoding circuitry. Circuitry such as a memory or shift registers) with the appropriate addressing/timing logic would again ensure mat each bit in the block of decoded bits output from the block decoder would correspond to one of a re-encoded estimate of the bits b or y that were used in controlling the original encoding of the ⁇ and ( ⁇ , ⁇ ) bits.

Landscapes

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Error Detection And Correction (AREA)

Abstract

Description

Claims

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US07/695,397 US5233630A (en) | 1991-05-03 | 1991-05-03 | Method and apparatus for resolving phase ambiguities in trellis coded modulated data |

| US695,397 | 1991-05-03 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| WO1992020162A2 true WO1992020162A2 (en) | 1992-11-12 |

| WO1992020162A3 WO1992020162A3 (en) | 1993-01-07 |

Family

ID=24792819

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/US1992/003656 Ceased WO1992020162A2 (en) | 1991-05-03 | 1992-05-01 | Method and apparatus for resolving phase ambiguities in trellis coded modulated data |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US5233630A (en) |

| CN (1) | CN1032104C (en) |

| AU (1) | AU2265892A (en) |

| IE (1) | IE80624B1 (en) |

| IL (1) | IL101752A (en) |

| MX (1) | MX9202041A (en) |

| MY (1) | MY109076A (en) |

| TW (1) | TW221838B (en) |

| WO (1) | WO1992020162A2 (en) |

| ZA (1) | ZA923193B (en) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0647046A1 (en) * | 1993-09-03 | 1995-04-05 | Siemens Telecomunicazioni S.P.A. | Procedure and device for phase ambiguity resolution in a trellis coded modulation system |

| EP0668682A1 (en) * | 1994-02-18 | 1995-08-23 | Alcatel Telspace | System of convolutional coding and Viterbi decoding, transparent to phase shifts of pi and pi/2 |

| WO1996017439A1 (en) * | 1994-11-23 | 1996-06-06 | At & T Wireless Services, Inc. | Cyclic trellis coded modulation |

| GB2305086A (en) * | 1995-08-23 | 1997-03-26 | Oki Electric Ind Co Ltd | Viterbi trellis decoder using branch metrics |

| FR2742611A1 (en) * | 1995-12-19 | 1997-06-20 | Alcatel Telspace | ENCODING / DECODING SYSTEM USING MULTI-LEVEL BLOCKS CODED 16-QAM MODULATION |

| GB2311913A (en) * | 1996-03-31 | 1997-10-08 | Fujitsu Ltd | A judging method and a precoding apparatus |

| US5838728A (en) * | 1994-11-23 | 1998-11-17 | At&T Wireless Services, Inc. | High rate reed-solomon concatenated trellis coded 16 star QAM system for transmission of data over cellular mobile radio |

| EP0887942A1 (en) * | 1997-06-23 | 1998-12-30 | Qualcomm Incorporated | High rate trellis coding and decoding method and apparatus |

| WO1998059424A1 (en) * | 1997-06-23 | 1998-12-30 | Qualcomm Incorporated | Trellis coding with punctured convolutional code |

| EP0763901A3 (en) * | 1995-09-14 | 1999-02-03 | Thomson Consumer Electronics, Inc. | A trellis demapper of a convolutional decoder |

| US6889356B1 (en) | 1994-11-23 | 2005-05-03 | Cingular Wireless Ii, Llc | Cyclic trellis coded modulation |

Families Citing this family (82)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5214675A (en) * | 1991-07-02 | 1993-05-25 | Motorola, Inc. | System and method for calculating channel gain and noise variance of a communication channel |

| JP2876497B2 (en) * | 1991-08-23 | 1999-03-31 | 松下電器産業株式会社 | Error correction code decoding method and apparatus |

| US5469452A (en) * | 1991-09-27 | 1995-11-21 | Qualcomm Incorporated | Viterbi decoder bit efficient chainback memory method and decoder incorporating same |

| US5329551A (en) * | 1992-04-16 | 1994-07-12 | At&T Bell Laboratories | Overlapped multilevel codes |

| JP2845705B2 (en) * | 1993-01-14 | 1999-01-13 | 日本電気株式会社 | Multi-level coded modulation communication device |

| US5428631A (en) * | 1993-02-01 | 1995-06-27 | Qualcomm Incorporated | Method and apparatus for resolving phase ambiguities in trellis coded modulated data |

| US5844922A (en) * | 1993-02-22 | 1998-12-01 | Qualcomm Incorporated | High rate trellis coding and decoding method and apparatus |

| US5402447A (en) * | 1993-03-05 | 1995-03-28 | Motorola, Inc. | Speech decoding in a zero BER environment |

| US5438590A (en) * | 1993-05-24 | 1995-08-01 | Comstream Corporation | Transmitting and receiving apparatus and method including punctured convolutional encoding and decoding |

| FR2713423B1 (en) * | 1993-11-30 | 1996-03-29 | Alcatel Telspace | Differential encoder and decoder for lattice-encoded MDP-8 modulation using the pragmatic approach. |

| US5473600A (en) * | 1994-05-20 | 1995-12-05 | Sierra Semiconductor Corporation | Efficient data storage arrangement for far-end echo canceller |

| US5754600A (en) * | 1994-08-29 | 1998-05-19 | Motorola, Inc. | Method and apparatus for optimum soft-decision viterbi decoding of convolutional-differential encoded QPSK data in coherent detection |

| US5450453A (en) * | 1994-09-28 | 1995-09-12 | Motorola, Inc. | Method, apparatus and system for decoding a non-coherently demodulated signal |

| CA2161467C (en) * | 1994-11-18 | 2001-01-30 | Kumar Ramaswamy | Apparatus for demodulating and decoding satellite, terrestrial and cable transmitted digital television data |

| US5497401A (en) * | 1994-11-18 | 1996-03-05 | Thomson Consumer Electronics, Inc. | Branch metric computer for a Viterbi decoder of a punctured and pragmatic trellis code convolutional decoder suitable for use in a multi-channel receiver of satellite, terrestrial and cable transmitted FEC compressed-digital television data |

| US6885652B1 (en) | 1995-06-30 | 2005-04-26 | Interdigital Technology Corporation | Code division multiple access (CDMA) communication system |

| ZA965340B (en) | 1995-06-30 | 1997-01-27 | Interdigital Tech Corp | Code division multiple access (cdma) communication system |

| US7123600B2 (en) | 1995-06-30 | 2006-10-17 | Interdigital Technology Corporation | Initial power control for spread-spectrum communications |

| US7020111B2 (en) | 1996-06-27 | 2006-03-28 | Interdigital Technology Corporation | System for using rapid acquisition spreading codes for spread-spectrum communications |

| US7929498B2 (en) | 1995-06-30 | 2011-04-19 | Interdigital Technology Corporation | Adaptive forward power control and adaptive reverse power control for spread-spectrum communications |

| DE19530063A1 (en) * | 1995-08-16 | 1997-02-20 | Bosch Gmbh Robert | Method for resolving phase ambiguity in trellis-coded modulation |

| US6356555B1 (en) | 1995-08-25 | 2002-03-12 | Terayon Communications Systems, Inc. | Apparatus and method for digital data transmission using orthogonal codes |

| US5805583A (en) * | 1995-08-25 | 1998-09-08 | Terayon Communication Systems | Process for communicating multiple channels of digital data in distributed systems using synchronous code division multiple access |

| US5793759A (en) * | 1995-08-25 | 1998-08-11 | Terayon Corporation | Apparatus and method for digital data transmission over video cable using orthogonal cyclic codes |

| US5991308A (en) * | 1995-08-25 | 1999-11-23 | Terayon Communication Systems, Inc. | Lower overhead method for data transmission using ATM and SCDMA over hybrid fiber coax cable plant |

| US6665308B1 (en) | 1995-08-25 | 2003-12-16 | Terayon Communication Systems, Inc. | Apparatus and method for equalization in distributed digital data transmission systems |

| US5768269A (en) * | 1995-08-25 | 1998-06-16 | Terayon Corporation | Apparatus and method for establishing frame synchronization in distributed digital data communication systems |

| US5745837A (en) * | 1995-08-25 | 1998-04-28 | Terayon Corporation | Apparatus and method for digital data transmission over a CATV system using an ATM transport protocol and SCDMA |

| US6307868B1 (en) | 1995-08-25 | 2001-10-23 | Terayon Communication Systems, Inc. | Apparatus and method for SCDMA digital data transmission using orthogonal codes and a head end modem with no tracking loops |

| GB2307152B (en) * | 1995-11-10 | 1999-04-07 | Motorola Ltd | Method and apparatus for enhanced communication capability while maintaining standard channel modulation compatibility |

| US5742622A (en) * | 1996-03-12 | 1998-04-21 | Discovision Associates | Error detection and correction system for a stream of encoded data |

| WO1998012818A1 (en) * | 1996-09-17 | 1998-03-26 | Philips Electronics N.V. | Transmission system with improved lock detection |

| GB9622540D0 (en) * | 1996-10-30 | 1997-01-08 | Discovision Ass | Trackback for viterbi decoder |

| US5938790A (en) * | 1997-03-04 | 1999-08-17 | Silicon Systems Research Ltd. | Sequence error event detection and correction using fixed block digital sum codes |

| US5995551A (en) * | 1997-08-15 | 1999-11-30 | Sicom, Inc. | Rotationally invariant pragmatic trellis coded digital communication system and method therefor |

| US5878085A (en) * | 1997-08-15 | 1999-03-02 | Sicom, Inc. | Trellis coded modulation communications using pilot bits to resolve phase ambiguities |

| US5910967A (en) * | 1997-10-20 | 1999-06-08 | Sicom, Inc. | Pragmatic encoder and method therefor |

| US6078625A (en) * | 1997-10-20 | 2000-06-20 | Sicom, Inc. | Pragmatic decoder and method therefor |

| US20020051434A1 (en) * | 1997-10-23 | 2002-05-02 | Ozluturk Fatih M. | Method for using rapid acquisition spreading codes for spread-spectrum communications |

| US6118822A (en) * | 1997-12-01 | 2000-09-12 | Conexant Systems, Inc. | Adaptive entropy coding in adaptive quantization framework for video signal coding systems and processes |

| WO1999031809A1 (en) * | 1997-12-16 | 1999-06-24 | Sicom, Inc. | Pragmatic trellis-coded modulation system and method therefor |

| US6005897A (en) * | 1997-12-16 | 1999-12-21 | Mccallister; Ronald D. | Data communication system and method therefor |

| US5909454A (en) * | 1998-01-20 | 1999-06-01 | General Instrument Corporation | Intermediate rate applications of punctured convolutional codes for 8PSK trellis modulation over satellite channels |

| AU3495099A (en) * | 1998-04-17 | 1999-11-08 | Tiernan Communications, Inc. | 45 degree phase ambiguity resolution for 8psk modulation |

| US6087969A (en) * | 1998-04-27 | 2000-07-11 | Motorola, Inc. | Sigma-delta modulator and method for digitizing a signal |

| US6236685B1 (en) | 1998-06-05 | 2001-05-22 | Sicom, Inc. | Pragmatic trellis-coded digital communication with multi-stage branch metrics |

| US6426978B1 (en) * | 1998-10-01 | 2002-07-30 | Ericsson Inc. | Digital communication systems and methods for differential and/or amplitude encoding and decoding secondary symbols |

| US6061408A (en) * | 1999-04-16 | 2000-05-09 | Tiernan Communications, Inc. | Method and apparatus for 45° phase ambiguity resolution for one coded bit per symbol 8PSK modulation |

| EP1091579B1 (en) * | 1999-09-07 | 2006-02-15 | Thomson Licensing | Trellis demapper for Trellis decoder |

| US6735734B1 (en) | 2000-04-28 | 2004-05-11 | John M. Liebetreu | Multipoint TDM data distribution system |

| US6697441B1 (en) | 2000-06-06 | 2004-02-24 | Ericsson Inc. | Baseband processors and methods and systems for decoding a received signal having a transmitter or channel induced coupling between bits |

| US6798852B2 (en) | 2000-06-06 | 2004-09-28 | Ericsson Inc. | Methods and systems for extracting a joint probability from a map decision device and processing a signal using the joint probability information |

| KR100672561B1 (en) | 2000-09-22 | 2007-01-23 | 엘지전자 주식회사 | Digital TV Communication System |

| KR100351829B1 (en) | 2000-09-26 | 2002-09-11 | 엘지전자 주식회사 | digital communication system |

| KR100351831B1 (en) * | 2000-10-02 | 2002-09-11 | 엘지전자 주식회사 | VSB transmission system |

| US6683915B1 (en) * | 2000-12-21 | 2004-01-27 | Arraycomm, Inc. | Multi-bit per symbol rate quadrature amplitude encoding |

| KR100673419B1 (en) * | 2000-12-28 | 2007-01-24 | 엘지전자 주식회사 | Transmission system and data processing method |

| KR100674423B1 (en) * | 2001-01-19 | 2007-01-29 | 엘지전자 주식회사 | Transmission / reception system and data processing method |

| US6947487B2 (en) * | 2001-04-18 | 2005-09-20 | Lg Electronics Inc. | VSB communication system |

| US7631340B2 (en) * | 2001-04-18 | 2009-12-08 | Lg Electronics Inc. | VSB communication system |

| KR100734351B1 (en) * | 2001-04-20 | 2007-07-03 | 엘지전자 주식회사 | Digital broadcast transmission system |

| KR100706508B1 (en) * | 2001-04-25 | 2007-04-11 | 엘지전자 주식회사 | Digital TV's VBS Communication System |

| KR100736500B1 (en) * | 2001-04-25 | 2007-07-06 | 엘지전자 주식회사 | Digital TV's VBS Communication System |

| KR100793766B1 (en) * | 2001-06-11 | 2008-01-10 | 엘지전자 주식회사 | Digital transmission system and method |

| KR100850932B1 (en) * | 2001-06-11 | 2008-08-12 | 엘지전자 주식회사 | Digital transmit system and method |

| KR100510679B1 (en) * | 2003-03-21 | 2005-08-31 | 엘지전자 주식회사 | Digital VSB transmitting system and enhanced data multiplexing method in a VSB transmitting system |

| US20030133519A1 (en) * | 2001-09-17 | 2003-07-17 | Manish Shah | Forward tracing decoder apparatus and method |

| US7161994B2 (en) * | 2001-09-17 | 2007-01-09 | Digeo, Inc. | System and method for shared decoding |

| US7167531B2 (en) * | 2001-09-17 | 2007-01-23 | Digeo, Inc. | System and method for shared decoding using a data replay scheme |

| KR100454398B1 (en) * | 2001-12-28 | 2004-10-26 | 한국전자통신연구원 | An adaptive modem, a pragmatic decoder and decoding method employed in the modem |

| US6973579B2 (en) | 2002-05-07 | 2005-12-06 | Interdigital Technology Corporation | Generation of user equipment identification specific scrambling code for the high speed shared control channel |

| KR100448884B1 (en) * | 2002-10-25 | 2004-09-18 | 한국전자통신연구원 | Apparatus of Generalized Phase Ambiguity Resolution for the Adaptive MODEM |

| GB0229320D0 (en) * | 2002-12-17 | 2003-01-22 | Koninkl Philips Electronics Nv | Signal processing method and apparatus |

| US7308025B2 (en) * | 2003-07-23 | 2007-12-11 | Intel Corporation | Transmitters providing cycle encoded signals |

| US7305023B2 (en) * | 2003-07-23 | 2007-12-04 | Intel Corporation | Receivers for cycle encoded signals |

| US7599348B2 (en) * | 2003-11-04 | 2009-10-06 | Lg Electronics Inc. | Digital E8-VSB reception system and E8-VSB data demultiplexing method |

| US8098773B1 (en) | 2005-09-19 | 2012-01-17 | Piesinger Gregory H | Communication method and apparatus |

| US9294321B2 (en) * | 2010-05-14 | 2016-03-22 | The Boeing Company | Bit signal structure for differentially encoded broadcasts |

| CN103229474B (en) * | 2010-12-06 | 2015-08-26 | 三菱电机株式会社 | Parallel differential coding circuit |

| US9041564B2 (en) * | 2013-01-11 | 2015-05-26 | Freescale Semiconductor, Inc. | Bus signal encoded with data and clock signals |

| US10135460B2 (en) | 2013-10-01 | 2018-11-20 | Texas Instruments Incorporated | Apparatus and method for multilevel coding (MLC) with binary alphabet polar codes |

| CN103840841A (en) * | 2014-02-11 | 2014-06-04 | 郭勇 | Method for designing PTCM+8PSK codec capable of overcoming seven kinds of phase ambiguity |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3789360A (en) * | 1972-10-13 | 1974-01-29 | Harris Intertype Corp | Convolutional decoder |

| JPS57155857A (en) * | 1981-03-23 | 1982-09-27 | Kokusai Denshin Denwa Co Ltd <Kdd> | Maximum likelihood method and apparatus for error |

| US4586182A (en) * | 1984-02-06 | 1986-04-29 | Codex Corporation | Source coded modulation system |

| US4823346A (en) * | 1986-04-16 | 1989-04-18 | Hitachi, Ltd. | Maximum likelihood decoder |

| US4993046A (en) * | 1988-06-24 | 1991-02-12 | Nippon Telegraph And Telephone Corporation | Coded modulation communication system |

| US5115453A (en) * | 1990-10-01 | 1992-05-19 | At&T Bell Laboratories | Technique for designing a multidimensional signaling scheme |

-

1991

- 1991-05-03 US US07/695,397 patent/US5233630A/en not_active Expired - Lifetime

-

1992

- 1992-04-30 ZA ZA923193A patent/ZA923193B/en unknown

- 1992-04-30 IL IL101752A patent/IL101752A/en not_active IP Right Cessation

- 1992-04-30 MX MX9202041A patent/MX9202041A/en not_active IP Right Cessation

- 1992-04-30 TW TW081103402A patent/TW221838B/zh not_active IP Right Cessation

- 1992-05-01 WO PCT/US1992/003656 patent/WO1992020162A2/en not_active Ceased

- 1992-05-01 AU AU22658/92A patent/AU2265892A/en not_active Abandoned

- 1992-05-02 MY MYPI92000761A patent/MY109076A/en unknown

- 1992-05-03 CN CN92104299A patent/CN1032104C/en not_active Expired - Fee Related

- 1992-07-01 IE IE921372A patent/IE80624B1/en not_active IP Right Cessation

Cited By (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0647046A1 (en) * | 1993-09-03 | 1995-04-05 | Siemens Telecomunicazioni S.P.A. | Procedure and device for phase ambiguity resolution in a trellis coded modulation system |

| US5555547A (en) * | 1994-02-18 | 1996-09-10 | Alcatel Telspace | Convolutional coding and viterbi decoding system transparent to phase skips of π and π/2, with applications in TDMA transmission |

| EP0668682A1 (en) * | 1994-02-18 | 1995-08-23 | Alcatel Telspace | System of convolutional coding and Viterbi decoding, transparent to phase shifts of pi and pi/2 |

| FR2716588A1 (en) * | 1994-02-18 | 1995-08-25 | Alcatel Telspace | Convolutional coding system and transparent viterbi decoding at pi and pi / 2 phase jumps, applicable in particular to TDMA transmissions. |

| WO1996017439A1 (en) * | 1994-11-23 | 1996-06-06 | At & T Wireless Services, Inc. | Cyclic trellis coded modulation |

| US8037396B2 (en) | 1994-11-23 | 2011-10-11 | At&T Mobility Ii Llc | Cyclic trellis coded modulation |

| US6889356B1 (en) | 1994-11-23 | 2005-05-03 | Cingular Wireless Ii, Llc | Cyclic trellis coded modulation |

| US6578173B2 (en) | 1994-11-23 | 2003-06-10 | At&T Wireless Services, Inc. | Cyclic trellis-coded modulation |

| US5675590A (en) * | 1994-11-23 | 1997-10-07 | At&T Wireless Services, Inc. | Cyclic trellis coded modulation |

| US5907565A (en) * | 1994-11-23 | 1999-05-25 | At&T Wireless Services, Inc. | Cyclic trellis coded modulation |

| US5784417A (en) * | 1994-11-23 | 1998-07-21 | At&T Wireless Services, Inc. | Cyclic trelles coded modulation |

| US5931965A (en) * | 1994-11-23 | 1999-08-03 | At&T Wireless Services, Inc. | Cyclic trellis coded modulation |

| US5838728A (en) * | 1994-11-23 | 1998-11-17 | At&T Wireless Services, Inc. | High rate reed-solomon concatenated trellis coded 16 star QAM system for transmission of data over cellular mobile radio |

| GB2305086B (en) * | 1995-08-23 | 1999-10-27 | Oki Electric Ind Co Ltd | Viterbi decoding method and apparatus with balance among memory and processing requirements |

| US5787127A (en) * | 1995-08-23 | 1998-07-28 | Oki Electric Industry Co., Ltd. | Viterbi decoding method and apparatus with balance among memory and processing requirements |

| GB2305086A (en) * | 1995-08-23 | 1997-03-26 | Oki Electric Ind Co Ltd | Viterbi trellis decoder using branch metrics |

| EP0763901A3 (en) * | 1995-09-14 | 1999-02-03 | Thomson Consumer Electronics, Inc. | A trellis demapper of a convolutional decoder |

| US6195396B1 (en) | 1995-12-19 | 2001-02-27 | Alcatel Telspace | Encoding/decoding system using 16-QAM modulation encoded in multi-level blocks |

| EP0780987A1 (en) * | 1995-12-19 | 1997-06-25 | Alcatel Telspace | Coding/decoding system using multilevel block coded MAQ-16 modulation |

| FR2742611A1 (en) * | 1995-12-19 | 1997-06-20 | Alcatel Telspace | ENCODING / DECODING SYSTEM USING MULTI-LEVEL BLOCKS CODED 16-QAM MODULATION |

| GB2311913A (en) * | 1996-03-31 | 1997-10-08 | Fujitsu Ltd | A judging method and a precoding apparatus |

| US6078624A (en) * | 1996-03-31 | 2000-06-20 | Fujitsu Limited | Judging method and a precoding apparatus |

| GB2311913B (en) * | 1996-03-31 | 2000-11-22 | Fujitsu Ltd | A judging method and a precoding apparatus |

| WO1998059424A1 (en) * | 1997-06-23 | 1998-12-30 | Qualcomm Incorporated | Trellis coding with punctured convolutional code |

| EP0887942A1 (en) * | 1997-06-23 | 1998-12-30 | Qualcomm Incorporated | High rate trellis coding and decoding method and apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| WO1992020162A3 (en) | 1993-01-07 |

| IE80624B1 (en) | 1998-10-21 |

| MY109076A (en) | 1996-11-30 |

| AU2265892A (en) | 1992-12-21 |

| US5233630A (en) | 1993-08-03 |

| CN1072302A (en) | 1993-05-19 |

| IL101752A0 (en) | 1992-12-30 |

| TW221838B (en) | 1994-03-21 |

| MX9202041A (en) | 1992-11-01 |

| ZA923193B (en) | 1993-04-28 |

| IL101752A (en) | 1997-11-20 |

| IE921372A1 (en) | 1992-11-04 |

| CN1032104C (en) | 1996-06-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5233630A (en) | Method and apparatus for resolving phase ambiguities in trellis coded modulated data | |

| US5469452A (en) | Viterbi decoder bit efficient chainback memory method and decoder incorporating same | |

| US5428631A (en) | Method and apparatus for resolving phase ambiguities in trellis coded modulated data | |

| US5535228A (en) | Device and method for achieving rotational invariance in a multi-level trellis coding system | |

| USRE38010E1 (en) | Trellis encoder and decoder based upon punctured rate ½ convolutional codes | |

| US5844922A (en) | High rate trellis coding and decoding method and apparatus | |

| JP3926499B2 (en) | Convolutional code soft decision decoding receiver | |

| US5408499A (en) | Multilevel code for transmission device | |

| US6195396B1 (en) | Encoding/decoding system using 16-QAM modulation encoded in multi-level blocks | |

| US6977972B1 (en) | Method of hybrid soft/hard decision demodulation of signals with multilevel modulation | |

| BRPI0315001B1 (en) | reception of a modulated signal according to a multilevel coding technique | |

| Pietrobon et al. | Rotationally invariant nonlinear trellis codes for two-dimensional modulation | |

| US5173926A (en) | Convolutionally-encoded quadrature frequency-modulation system | |

| EP0383632A2 (en) | Mapping digital data sequences | |

| US5848102A (en) | Method and apparatus for encoding/decoding QAM trellis coded data | |

| US5608763A (en) | Method and apparatus for decoding a radio frequency signal containing a sequence of phase values | |

| JP2001053816A (en) | Multi-chip data detector corresponding to symmetrical differential phase deviation keying (sdpsk) modulation format | |

| US20050008097A1 (en) | Coded modulation scheme for a wirelesss communication system and methods thereof | |

| US6118826A (en) | Method and apparatus for encoding/decoding QAM trellis coded data | |

| EP1326358B1 (en) | Scaling of Viterbi decoding based on channel and location information | |

| KR100524379B1 (en) | Pragmatic TCM Decoder and Its Method Using Coset Mapping | |

| IL119604A (en) | Method for encoding data as trellis coded data and apparatus for resolving phase ambiguities | |

| US20030123562A1 (en) | Adaptive modem, pragmatic decoder and decoding method | |

| US6061408A (en) | Method and apparatus for 45° phase ambiguity resolution for one coded bit per symbol 8PSK modulation | |

| JP4472132B2 (en) | Bit error rate measurement method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| AK | Designated states |

Kind code of ref document: A2 Designated state(s): AU BG BR CA CS FI HU JP KP KR NO PL RO RU |

|

| AL | Designated countries for regional patents |

Kind code of ref document: A2 Designated state(s): AT BE CH DE DK ES FR GB GR IT LU MC NL SE |

|

| AK | Designated states |

Kind code of ref document: A3 Designated state(s): AU BG BR CA CS FI HU JP KP KR NO PL RO RU |

|

| AL | Designated countries for regional patents |

Kind code of ref document: A3 Designated state(s): AT BE CH DE DK ES FR GB GR IT LU MC NL SE |

|

| DFPE | Request for preliminary examination filed prior to expiration of 19th month from priority date (pct application filed before 20040101) | ||

| EX32 | Extension under rule 32 effected after completion of technical preparation for international publication |

Ref country code: KZ |

|

| LE32 | Later election for international application filed prior to expiration of 19th month from priority date or according to rule 32.2 (b) |

Ref country code: KZ |

|

| NENP | Non-entry into the national phase |

Ref country code: CA |

|

| EX32 | Extension under rule 32 effected after completion of technical preparation for international publication |

Ref country code: UZ |

|

| LE32 | Later election for international application filed prior to expiration of 19th month from priority date or according to rule 32.2 (b) |

Ref country code: UZ |

|

| 122 | Ep: pct application non-entry in european phase | ||

| 122 | Ep: pct application non-entry in european phase |