KR20100138639A - Method and apparatus for tweed factor index generation in fast Fourier transform system - Google Patents

Method and apparatus for tweed factor index generation in fast Fourier transform system Download PDFInfo

- Publication number

- KR20100138639A KR20100138639A KR1020090057250A KR20090057250A KR20100138639A KR 20100138639 A KR20100138639 A KR 20100138639A KR 1020090057250 A KR1020090057250 A KR 1020090057250A KR 20090057250 A KR20090057250 A KR 20090057250A KR 20100138639 A KR20100138639 A KR 20100138639A

- Authority

- KR

- South Korea

- Prior art keywords

- factor

- data

- index

- digit

- radix

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F17/00—Digital computing or data processing equipment or methods, specially adapted for specific functions

- G06F17/10—Complex mathematical operations

- G06F17/14—Fourier, Walsh or analogous domain transformations, e.g. Laplace, Hilbert, Karhunen-Loeve, transforms

- G06F17/141—Discrete Fourier transforms

- G06F17/142—Fast Fourier transforms, e.g. using a Cooley-Tukey type algorithm

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/26—Systems using multi-frequency codes

- H04L27/2601—Multicarrier modulation systems

Landscapes

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Mathematical Analysis (AREA)

- Pure & Applied Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computational Mathematics (AREA)

- Data Mining & Analysis (AREA)

- Mathematical Optimization (AREA)

- Algebra (AREA)

- Discrete Mathematics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Databases & Information Systems (AREA)

- Software Systems (AREA)

- General Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Complex Calculations (AREA)

Abstract

본 발명은 고속 푸리에 변환 시스템에서 트위들 팩터 인덱스 생성 방법 및 장치에 관한 것으로서, 데이터가 입력되는 스테이지의 넘버(s)를 결정하여 출력하는 스테이지 넘버 카운터, 상기 입력되는 데이터에 대한 인덱스를 순차적으로 카운트하고, 카운트되는 데이터 인덱스를 r 진수로 출력하는 데이터 인덱스 카운터, 상기 r 진수의 데이터 인덱스를 구성하는 디지트 중, rs 자리수에 대응하는 디지트를 제1 인자로 선택하여 출력하는 선택기, 상기 r 진수의 데이터 인덱스를 구성하는 디지트 중, 상기 rs 자리수보다 상위 자리수에 해당하는 디지트를 선택하는 쉬프터, 상기 쉬프터에서 선택된 디지트를 비트 반전하여 제2 인자로 출력하는 비트 반전기, 상기 결정된 스테이지 넘버에 따라 스케일링을 위한 제3 인자를 생성하는 스케일러 및 상기 제1 인자와 상기 제2 인자와 상기 제3 인자를 서로 곱하여 상기 트위들 팩터 인덱스를 생성하는 곱셈기를 포함하는 것을 특징으로 한다. The present invention relates to a method and apparatus for generating a tween factor index in a fast Fourier transform system, comprising: a stage number counter for determining and outputting a number (s) of a stage into which data is input, and sequentially counting an index of the input data And a data index counter for outputting the counted data index in r-decimal number, a selector for selecting and outputting a digit corresponding to r s digits as a first factor among the digits constituting the data index in r-number, A shifter for selecting a digit higher than the r s digit among the digits constituting the data index, a bit inverter for bit inverting the digit selected by the shifter and outputting it as a second factor, scaling according to the determined stage number A scaler for generating a third factor for and the first factor And a multiplier for multiplying the second factor and the third factor to generate the tween factor index.

Description

본 발명은 고속 푸리에 변환 시스템에서 트위들 팩터 인덱스 생성 방법 및 장치에 관한 것이다. 보다 구체적으로, 본 발명은 반전된 순서(bit reverse order)로 입력되는 데이터 열에 대한 Radix-r의 n승 방식의 고속 푸리에 변환 수행 시 필요한 트위들 팩터 인덱스의 생성 방법 및 장치에 관한 것이다. The present invention relates to a method and apparatus for generating a tween factor index in a fast Fourier transform system. More specifically, the present invention relates to a method and apparatus for generating a tween factor index required for performing a Fast Fourier Transform of an n-square method of Radix-r on a data string input in a bit reverse order.

IEEE(Institute of Electrical and Electronics Engineers) 802.16, IEEE 802.111과 같은 무선 통신 시스템과, DMB(Digital Multimedia Broadcasting)과 같은 디지털 방송 등에서 직교 주파수 분할 다중(Orthogonal Frequency Division Multiplexing, 이하 'OFDM') 기술이 이용된다. 이 때, 상기 OFDM에서 가장 중요한 구성 요소 중 고속 푸리에 변환(FAST FOURIER TRANSFORM, 이하 'FFT') 프로세서가 있다. FFT는 이산 푸리에 변환(Discrete Fourier Transform, 이하 'DFT')을 고속으로 연산하기 위한 알고리즘으로, DFT에 대한 수식은 아래의 수학식 1과 같이 정의된다. Orthogonal Frequency Division Multiplexing (OFDM) technology is used in wireless communication systems such as Institute of Electrical and Electronics Engineers (IEEE) 802.16, IEEE 802.111, and digital broadcasting such as digital multimedia broadcasting (DMB). . At this time, one of the most important components of the OFDM is a FAST FOURIER TRANSFORM (FFT) processor. The FFT is an algorithm for computing the Discrete Fourier Transform (DFT) at high speed, and the equation for the DFT is defined as in

[수학식 1][Equation 1]

여기서 X(K)는 푸리에 변환의 결과이고, x(n)은 FFT의 입력 데이터열, WN은 트위들 팩터(Twiddle Factor)이며, 이들 값은 모두 복소수 형태를 가진다. 여기서, 상기 트위들 팩터는 시간 신호를 주파수 신호로 변환하기 위해 사용되는 주기함수이다. Where X (K) is the result of the Fourier transform, x (n) is the input data string of the FFT, W N is the Twiddle Factor, and all of these values have a complex form. Here, the tweet factor is a periodic function used for converting a time signal into a frequency signal.

FFT를 구현함에 있어서, 널리 사용되는 방식 중 하나인 Radix-4 방식은 Radix-2 방식에 비해 곱셈의 효율 면에서 우수하다. 반면, Radix-2 방식의 경우, 버터플라이 구조가 Radix-4 보다 간단하기 때문에 사용하기 쉽다는 장점이 있다. 여기서, Radix-4 방식과 Radix-2 방식의 장점만을 결합한 방식이 'Shousheng He'에 의해 Radix-2의 2승(Radix-22, 이하 동일하다) DIF FFT가 고안되었다. In implementing the FFT, the Radix-4 method, which is one of the widely used methods, is superior in terms of multiplication efficiency to the Radix-2 method. On the other hand, the Radix-2 method has the advantage that the butterfly structure is easier to use because it is simpler than the Radix-4. Here, Radix-4 method and system which combines the advantages of only Radix-2 scheme (the same Radix-2. 2, below) the square of the Radix-2 by 'Shousheng He' DIF FFT is designed.

그런데, 상기 Radix 2의 2승 DIF FFT는 순차적(natural order)으로 데이터 열을 입력받아 FFT 연산을 수행하고, 반전된 순서로 데이터 열을 출력한다. 한편, 최근의 OFDM 방식의 모뎀 수신기에서는 (I)FFT를 수신된 OFDM 신호의 복조 뿐만 아니라 등화기, 채널 추정 등에서도 폭 넓게 사용한다. 이 경우, 복조를 위한 FFT와 이후 수행되는 등화기 등에서의 (I)FFT를 구현함에 있어서, 종래의 Radix 2의 2승 DIF FFT 알고리즘을 동일하게 적용하는 경우에는 반전된 순서로 출력되는 데이터를 이후 수행될 (I)FFT 연산을 위하여 순서대로 재정렬하는 과정을 거쳐야 한다. 이러한 재정렬 동작에는 FFT 크기에 해당하는 메모리가 필요하고, 심볼들에 대해 시간 지연이 발생한다는 문제점이 있다. However, the quadratic DIF FFT of Radix 2 receives a data sequence in a natural order, performs an FFT operation, and outputs the data sequence in an inverted order. On the other hand, modern modem modem receivers use (I) FFT not only for demodulation of received OFDM signals but also for equalizers and channel estimation. In this case, in implementing the (I) FFT in the FFT for demodulation and the equalizer to be performed later, when the conventional Radix 2 power DIF FFT algorithm is applied in the same way, the data outputted in the reversed order will be In order for the (I) FFT operation to be performed, the process must be rearranged in order. This realignment operation requires a memory corresponding to the FFT size, and there is a problem that a time delay occurs for symbols.

본 발명은 상기와 같은 문제점을 해결하기 위하여 안출된 것으로서, 반전된 순서로 입력되는 데이터 열에 대한 Radix-r 방식의 고속 푸리에 변환 수행 시 필요한 트위들 팩터의 생성 방법을 제안하는데 그 목적이 있다. The present invention has been made to solve the above problems, and an object of the present invention is to propose a method for generating a tween factor required for performing a Fast Fourier Transform of a Radix-r method on a data sequence inputted in an inverted order.

상기와 같은 문제점을 해결하기 위한 본 발명의 Radix-r의 n승 방식의 고속 푸리에 변환 프로세서의 트위들 팩터 인덱스 생성 장치는 데이터가 입력되는 스테이지의 넘버(s)를 결정하여 출력하는 스테이지 넘버 카운터, 상기 입력되는 데이터에 대한 인덱스를 순차적으로 카운트하고, 카운트되는 데이터 인덱스를 r 진수로 출력하는 데이터 인덱스 카운터, 상기 r 진수의 데이터 인덱스를 구성하는 디지트 중, rs 자리수에 대응하는 디지트를 제1 인자로 선택하여 출력하는 선택기, 상기 r 진수의 데이터 인덱스를 구성하는 디지트 중, 상기 rs 자리수보다 상위 자리수에 해당하는 디지트를 선택하는 쉬프터, 상기 쉬프터에서 선택된 디지트를 비트 반전하여 제2 인자로 출력하는 비트 반전기, 상기 결정된 스테이지 넘버에 따라 스케일링을 위한 제3 인자를 생성하는 스케일러 및 상기 제1 인자와 상기 제2 인자와 상기 제3 인자를 서로 곱하여 상기 트위들 팩터 인덱스를 생성하는 곱셈기를 포함하는 것을 특징으로 한다. In order to solve the above problems, a tweed factor index generating device of the Radix-r n-type fast Fourier transform processor according to the present invention includes a stage number counter for determining and outputting a number s of a stage into which data is input; A first index corresponding to r s digits of a data index counter that sequentially counts the indexes of the input data and outputs the counted data indexes in r numbers, and digits constituting the r data indexes; A selector for selecting and outputting a digit, a shifter for selecting a digit corresponding to a higher digit than the r s digits among the digits constituting the data index of the r-number, and outputting the bit selected by the shifter as a second factor. A bit inverter, generating a third factor for scaling according to the determined stage number Multiplied by a scalar, and the third factor and the second factor from the first factor to each other characterized in that it comprises a multiplier for generating the twiddle factor index.

또한, 상기와 같은 문제점을 해결하기 위한 본 발명의 Radix-r의 n승 방식의 고속 푸리에 변환 프로세서의 트위들 팩터 인덱스 생성 방법은 데이터가 입력되는 스테이지의 넘버(s)를 결정하여 출력하는 단계, 상기 입력되는 데이터에 대한 인덱스를 순차적으로 카운트하고, 카운트되는 데이터 인덱스를 r 진수로 출력하는 단계, 상기 r 진수의 데이터 인덱스를 구성하는 디지트 중, rs 자리수에 대응하는 디지트를 제1 인자로 선택하여 출력하는 단계, 상기 r 진수의 데이터 인덱스를 구성하는 디지트 중, 상기 rs 자리수보다 상위 자리수에 해당하는 디지트를 선택하는 단계, 상기 쉬프터에서 선택된 디지트를 비트 반전하여 제2 인자로 출력하는 단계, 상기 결정된 스테이지 넘버에 따라 스케일링을 위한 제3 인자를 생성하는 단계 및 상기 제1 인자와 상기 제2 인자와 상기 제3 인자를 서로 곱하여 상기 트위들 팩터 인덱스를 생성하는 단계를 포함하는 것을 특징으로 한다. In addition, in order to solve the above problems, a method of generating a tween factor index of the n-th order fast Fourier transform processor of the Radix-r of the present invention includes determining and outputting a number s of a stage into which data is input; Sequentially counting the indices of the input data and outputting the counted data indexes in r numbers; selecting a digit corresponding to r s digits among the digits constituting the r data index as the first factor Selecting a digit corresponding to a higher digit than the r s digit among the digits constituting the data index of the r base, outputting the selected digit by the bit shifter as a second factor, Generating a third factor for scaling according to the determined stage number and the first factor and the second factor And multiplying a factor by the third factor to generate the tweet factor index.

본 발명에서는 비트 반전된 순서로 입력되는 데이터 열에 대한 Radix-r의 n승 방식의 고속 푸리에 변환 수행 시 필요한 트위들 팩터의 생성 방법을 제안한다. 이에 따라, OFDM 방식의 모뎀 수신부에서 등화기 등을 구성함에 있어서, 복조를 위한 FFT 이후, 별도의 재정렬 과정 없이 채널 등화를 위한 (I)FFT를 수행할 수 있다. 따라서 재정렬 과정으로 인하여 요구되는 메모리 및 시간 증가를 방지할 수 있다. The present invention proposes a method of generating a tween factor required for performing a Fast Fourier Transform of the n-th power method of Radix-r on a data sequence inputted in bit inverted order. Accordingly, in configuring an equalizer in an OFDM modem modem receiver, after the FFT for demodulation, (I) FFT for channel equalization may be performed without a separate reordering process. Therefore, the memory and time increase required by the reordering process can be prevented.

이하에서 기술되는 본 발명의 요지는 Radix-2의 2승 방식의 고속 푸리에 변 환을 예시로 설명할 것이지만, Radix-r의 n승 방식의 고속 푸리에 변환 수행시에 적용될 수 있다. The gist of the present invention described below will be described as an example of Radix-2 quadratic fast Fourier transform, but may be applied when performing Radix-r fast Fourier transform of n-square.

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시 예들을 상세히 설명한다. 이 때, 첨부된 도면에서 동일한 구성 요소는 가능한 동일한 부호로 나타내고 있음에 유의해야 한다. 또한 본 발명의 요지를 흐리게 할 수 있는 공지 기능 및 구성에 대한 상세한 설명은 생략할 것이다. Hereinafter, exemplary embodiments of the present invention will be described in detail with reference to the accompanying drawings. Note that, in the drawings, the same components are denoted by the same reference symbols as possible. Further, the detailed description of well-known functions and constructions that may obscure the gist of the present invention will be omitted.

도 1은 종래 N=64에 대한 Radix-2의 2승 DIF FFT의 신호 흐름 그래프(Signal Flow Graph, SFG)를 도시하는 도면이다. FIG. 1 is a diagram illustrating a signal flow graph (SFG) of a Radix-2 quadratic DIF FFT for N = 64.

상기한 Radix-2의 2승 DIF FFT는 Radix-4 방식과 Radix-2 방식의 장점만을 결합한 방식으로서, MDC(Multi-Path Delay Commutator), SDF(Single-path Delay Feedback) 등과 같은 다양한 파이프라인 방식의 FFT 구조에 적용될 수 있다. The Radix-2 quadratic DIF FFT combines only the advantages of the Radix-4 and Radix-2 schemes, and includes various pipeline schemes such as Multi-Path Delay Commutator (MDC) and Single-path Delay Feedback (SDF). Can be applied to the FFT structure.

상기 도 1에 도시된 Radix-2의 2승 DIF FFT 알고리즘을 이용하여 구현된 SDF 방식의 FFT 프로세서가 도 2에 도시된다. 도 2에 도시된 FFT 프로세서는 Radix-2의 간단한 버터플라이 구조와 Radix-4의 곱셈 횟수를 유지하여 기능의 효율성과 구현의 용이성 때문에 최적의 FFT 구현 방식으로 널리 사용된다.The SDF FFT processor implemented using the Radix-2 quadratic DIF FFT algorithm shown in FIG. 1 is shown in FIG. 2. The FFT processor shown in FIG. 2 is widely used as an optimal FFT implementation method because of maintaining the simple butterfly structure of Radix-2 and the number of multiplications of Radix-4, because of the efficiency of functions and the ease of implementation.

상기 도 2에 도시된 바와 같이, FFT 프로세서는 복수 개의 스테이지(stage)로 구성되며, 각 스테이지의 출력 데이터열에 트위들 팩터 'W(n)'이 각각 곱해진다. 그리고 모든 스테이지를 거친 입력 데이터열 x(n)은 X(K)로 출력된다.As shown in FIG. 2, the FFT processor includes a plurality of stages, and the tween factor 'W (n)' is multiplied by the output data string of each stage. The input data string x (n) having passed through all stages is output as X (K).

그리고 상기 도 2에 도시된 임의의 스테이지의 세부 구조가 도 3에서 도시된다. 도 3에서 도시되는 바와 같이, Radix-2의 2승 DIF FFT 프로세서의 임의의 스테 이지는 제1 버퍼(310), 제2 버퍼(320), 제1 Radix-2 버터플라이 연산자(330), 제2 Radix-2 버터플라이 연산자(340), I/Q 교환기(350), 트위들 팩터 승산기(360), 및 트위들 팩터 생성기(370)를 포함한다. And the detailed structure of any stage shown in FIG. 2 is shown in FIG. As shown in FIG. 3, any stage of the Radix-2 quadratic DIF FFT processor may include a

스테이지에 따라 각각 다른 크기를 갖는 제1 버퍼(310) 및 제2 버퍼(320)는 FIFO(First-In First-Out)으로 동작하고, 버터플라이 연산자의 입출력을 정렬해주는 기능을 수행한다. The

버터플라이 유닛으로 입력된 데이터는 제1 버퍼(310)에 순서대로 저장된다. 그리고 상기 제1 버퍼(310)에서 가장 처음으로 저장된 데이터가 출력하는 시점부터 가장 마지막에 저장된 데이터가 출력될 때까지, 초기 또는 이전 스테이지에서 입력되는 데이터와 제1 버퍼(310)에서 출력되는 데이터를 이용하여 첫 번째 Radix-2 버터플라이 연산을 수행한다. 여기서, 상기 Radix-2 버터플라이 연산은 당업자에게 자명한 기술 사항으로서, 두 개의 데이터에 대해 가산 및 감산을 수행하는 연산이다. Data input to the butterfly unit is stored in the

제1 Radix-2 버터플라이 연산자(330)의 출력 중 가산 결과는 곧바로 I/Q 교환기(350)에 입력된다. 반면, 상기 제1 Radix-2 버터플라이 연산자(330)의 출력 중 감산 결과는 제1 버퍼(310)에 저장된 후 버퍼 크기만큼의 지연을 거친 후 I/Q 교환기(350)에 입력된다. The addition result of the output of the first Radix-2

I/Q 교환기(350) 역시 실질적으로 트위들 팩터를 곱해주는 역할을 수행하는 블록인데, Radiz-2의 2승 분해에 따라 '-j' 또는 '1' 만의 값을 갖는 단순 승산(Trivial Multiplication)으로 단순화되기 때문에 I의 부호를 바꾼 뒤 I/Q 데이 터를 서로 바꾸어 주는 것만으로도 간단하게 구현할 수 있다. The I /

I/Q 교환기(350)를 거친 데이터는 제2 버퍼(320)에 저장된 후, 제1 버퍼(310)에서와 마찬가지로 가장 먼저 입력된 데이터가 출력되는 시점부터 두 번째 Radix-2 버터플라이 연산이 수행된다. 그리고 제2 Radix-2 버터플라이 연산자(340)에 의해 출력은 순서대로 트위들 팩터 승산기(360)에 입력된다. After passing through the I /

이 때 곱해지는 트위들 팩터는 트위들 팩터 생성기(370)에 의해 생성되며, Radix-2의 2승 분해 과정에 따라 아래의 수학식 2와 같이 도출된다.The tween factor factor multiplied at this time is generated by the

[수학식 2][Equation 2]

여기서, N은 FFT의 크기, n3은 [0~N/4-1], k1=(0,1), k2=(0,1)이다. Here, N is the size of the FFT, n 3 is [0 ~ N / 4-1], k1 = (0,1), k2 = (0,1).

n3은 데이터 입력과 함께 매 클럭 증가하는 카운터 값이고, (k2, k1) 은 N/4 주기로 (0,0), (1,0), (0,1), (1,1)로 변하는 값이다. n 3 is a counter value that increases every clock with the data input, and (k2, k1) changes to (0,0), (1,0), (0,1), (1,1) in N / 4 periods. Value.

도 4는 N=16에 대해 생성된 트위들 팩터의 인덱스를 도시하는 도면이다. 4 is a diagram illustrating the index of the tween factor generated for N = 16.

도 4에서는 N=16인 경우, 입력 데이터열에 대응하는 n3, k2, k1 값에 따라 계산된 트위들 팩터 인덱스를 도시한다. 이와 같이 생성된 트위들 팩터 값과 복소 승산된 데이터는 다음 스테이지의 버터플라이 유닛으로 전달된다. Radix-2의 2승 SDF 방식의 FFT 프로세서는 파이프라인 방식으로 동작하므로, 상기 버터플라이 유닛을 FFT 사이즈에 따라 결정되는 스테이지 수만큼을 연결하고 각 스테이지를 제어 한다. FIG. 4 illustrates a tween factor index calculated according to n 3 , k 2 , and

그런데, 상기한 Radix 2의 2승 DIF FFT는 순차적(natural order)으로 데이터 열을 입력받아 FFT 연산을 수행하고, 반전된 순서로 데이터 열을 출력한다. 한편, 최근의 OFDM 방식의 모뎀 수신기에서는 (I)FFT를 수신된 OFDM 신호의 복조 뿐만 아니라 등화기, 채널 추정 등에서도 폭 넓게 사용한다. 이 경우, 복조를 위한 FFT와 이후 수행되는 등화기 등에서의 (I)FFT를 구현함에 있어서, 종래의 Radix 2의 2승 DIF FFT 알고리즘을 동일하게 적용하는 경우에는 반전된 순서로 출력되는 데이터를 이후 수행될 (I)FFT 연산을 위하여 순서대로 재정렬하는 과정을 거쳐야 한다. 이러한 재정렬 동작에는 FFT 크기에 해당하는 메모리가 필요하고, 심볼들에 대해 시간 지연이 발생한다는 문제점이 있다. However, the quadratic DIF FFT of Radix 2 receives a data sequence in a natural order, performs an FFT operation, and outputs the data sequence in an inverted order. On the other hand, modern modem modem receivers use (I) FFT not only for demodulation of received OFDM signals but also for equalizers and channel estimation. In this case, in implementing the (I) FFT in the FFT for demodulation and the equalizer to be performed later, when the conventional Radix 2 power DIF FFT algorithm is applied in the same way, the data outputted in the reversed order will be In order for the (I) FFT operation to be performed, the process must be rearranged in order. This realignment operation requires a memory corresponding to the FFT size, and there is a problem that a time delay occurs for symbols.

따라서, 반전된 순서로 입력되는 데이터 열에 대한 Radix-2의 2승 방식의 고속 푸리에 변환 수행 시 필요한 트위들 팩터를 생성할 필요가 있다. Accordingly, it is necessary to generate a tween factor necessary for performing a Fast Fourier Transform of the Radix-2 quadratic method on the data strings input in the inverted order.

상기와 같은 목적을 달성하기 위한 본 발명에서는 반전된 순서로 입력되는 데이터에 대해 Radix-2의 2승 FFT 알고리즘을 적용하기 위해, 각 스테이지에서 사용되는 트위들 팩터 인덱스(i=n3(k1+2k2)) 순서를 재정렬한다. 이를 위해, 본 발명에서는 입력 데이터 열이 비트 반전되어 있는 점을 고려하여 n3를 비트 반전 시키고, k1과 k2의 동작 주기를 바꾸어 줌으로써 트위들 팩터의 순서가 반전되는 효과를 얻을 수 있다. 이를 구현하기 위한 구체적인 방법은 이하에서 상술하도록 한다. In the present invention for achieving the above object, in order to apply the Radix-2 quadratic FFT algorithm to the data input in the inverted order, the tweed factor index (i = n 3 (k1 +) used in each stage 2k2)) Reorder. To this end, in the present invention, in consideration of the fact that the input data string is bit inverted, n 3 is bit inverted and the order of the tweed factor is reversed by changing the operation periods of k1 and k2. A detailed method for implementing this will be described below.

도 5는 본 발명의 실시예에 따른 FFT 프로세서의 내부 구조를 도시하는 블록 도이다. 본 발명의 FFT 프로세서는 제1 버퍼(510), 제2 버퍼(520), 제1 Radix-2 버터플라이 연산자(530), 제2 Radix-2 버터플라이 연산자(540), I/Q 교환기(550), 트위들 팩터 승산기(560), 및 트위들 팩터 생성기(570)를 포함한다. 5 is a block diagram illustrating an internal structure of an FFT processor according to an embodiment of the present invention. The FFT processor of the present invention includes a

상기 도 5에 도시된 제1 Radix-2 버터플라이 연산자(530), 제2 Radix-2 버터플라이 연산자(540), 트위들 팩터 승산기(560)의 기능은 도 3에서 상술한 바 있으므로 자세한 설명은 생략하기로 한다. The functions of the first Radix-2

스테이지에 따라 각각 다른 크기를 갖는 제1 버퍼(310) 및 제2 버퍼(320)는 FIFO(First-In First-Out)으로 동작하고, 버터플라이 연산자의 입출력을 정렬해주는 기능을 수행한다. 한편, 본 발명의 실시예에 따라, 반전된 순서로 입력되는 Radix-2의 2승의 Signal Flow Graph인 도8을 참고하면, 각 stage의 두 번째 Radix-2 버터플라이 연산에 사용되는 2개의 입력 데이터 간의 거리가 첫 번째 Radix-2 버터플라이 연산에 사용되는 2개의 데이터간의 거리가 보다 2배 긴 것을 확인할 수 있다. 두 데이터간의 거리가 2배 길다는 것은 Radix-2 버퍼플라이 연산자의 두 입력 중에서 하나의 데이터가 입력된 이후 다음 데이터가 입력되기까지 걸리는 시간이 2배 길어짐을 뜻한다. 제1 버퍼와 제2 버퍼의 기능이 두 개의 입력 데이터 간에 발생하는 시간차를 맞추어 두 데이터를 동시에 Radix-2 버터플라이 연산자로 입력하기 위한 것이므로 종래에는 제1 버퍼의 크기가 제2 버퍼의 2배 크기를 갖는 것과는 반대로 본 발명에서는 제2 버퍼가 제1 버퍼의 크기의 2배 크기를 갖는 것을 특징으로 한다. The

I/Q 교환기(550)는 I/Q 교환기의 스위치가 'ON'이면 (-j)를 곱해주는 것과 동일한 동작인 I의 부호를 바꾼 뒤 I와 Q의 데이터를 교환하는 동작을 하고 스위치가 'OFF'이면 그대로 출력한다. 이 스위치의 동작 주기는 스테이지에 따라 달라지는데, 본 발명에서처럼 입력 데이터가 반전된 순서로 들어오는 경우에는 [OFF:ON]가 [3:1]의 형태로 이루어지는 것은 종래와 동일하나, 스위칭의 주기와 ON이 유지되는 구간이 이전 스테이지에 비해 4배로 길어지는 규칙을 따른다. N=64인 경우 I/Q 교환기의 스위칭 동작 타이밍을 도10에 예시하였다. 최초의 스테이지에서는 4개의 데이터가 한 주기가 되어 3개의 데이터 구간동안 OFF를 유지하고 1개의 데이터 구간에서 ON이 되는 형태로 16번 반복한다. 두 번째 스테이지에서는 4배 길어진 16개의 데이터를 한 주기로 하여 12개의 데이터 구간동안 OFF를 유지하고 4개의 데이터 구간에서 ON이 되는 형태로 4번 반복한다. 마지막 스테이지 역시 이전과 동일한 원리로 64개의 데이터를 한 주기로 하여 48개의 데이터 구간동안 OFF를 유지하고 16개의 데이터 구간동안 ON을 유지하는 형태로 동작한다. The I /

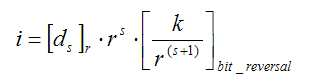

트위들 팩터 인덱스 생성기(570)는 본 발명의 실시예에 따라, 비트 반전된 순서로 입력되는 데이터 열에 대한 Radix-r 방식의 고속 푸리에 변환 수행 시 필요한 트위들 팩터 인덱스를 생성한다. FFT 크기를 NFFT라 하고, 데이터 인덱스(k)를 r-진수(22의 경우 r=4)로 표현하고, 스테이지 넘버를 's'로 표시할 때, 상기 트위들 팩터 인덱스 생성기(570)에서 생성되는 트위들 팩터 인덱스 'i' 는 아래의 수학식 3과 같이 표현할 수 있다. The tween

[수학식 3]&Quot; (3) "

(여기서, r=22, n=logrNFFT)Where r = 2 2 and n = log r N FFT

이하에서는, 상기 수학식 3을 실제 로직으로 구현하기 위한 트위들 팩터 인덱스 생성기(570)의 구조를 제시하도록 한다. Hereinafter, a structure of a tween

도 6은 상기 트위들 팩터 인덱스 생성기(570)의 구체적인 구조를 도시하는 도면이다. FIG. 6 is a diagram illustrating a detailed structure of the tween

도 6에 도시된 바와 같이, 본 발명의 트위들 팩터 생성기(570)는 스테이지 넘버 카운터(605), 데이터 인덱스 카운터(610), 쉬프터(620), 비트 반전기(630), 선택기(640), 스케일러(650), 곱셈기(660)를 구비할 수 있다. As shown in FIG. 6, the

스테이지 넘버 카운터(605)는 데이터열이 입력되는 현재 스테이지의 넘버를 결정하여 그 결과 값을 출력한다. 스테이지 넘버 카운터(605)는 상기 수학식 3의 's' 값을 계산하는 블록에 대응한다. The

데이터 인덱스 카운터(610)는 각 스테이지별 버터플라이 유닛으로 데이터가 입력될 때마다 카운터 값(k)을 1 씩 증가시켜 r-진수 디지트로 출력한다. 그리고 상기 데이터 인덱스 카운터(610)는 NFFT의 데이터가 모두 입력되면 인덱스가 0으로 초기화 되도록 동작한다. 본 발명의 일 실시예에 따르면, 상기 데이터 인덱스 카운터(610)는 2n 비트의 카운터일 수 있다. 데이터 인덱스 카운터(610)는 상기 수학식 3의 'k' 값을 계산하는 블록에 대응한다. 예를 들어, r=22인 경우, 첫 번째 입력되는 데이터의 인덱스는 [000]4이며, 두 번째 입력되는 데이터의 인덱스는 [001]4로 표현할 수 있으며, 상기 데이터 인덱스는 순차적으로 증가한다. The

쉬프터(620)는 상기 수학식 3의 k/r(s+1)에 해당하는 부분을 계산하기 위한 것으로, 상기 데이터 인덱스 카운터(610) 출력 값의 4진수-디지트(Quarternary digit)를 쉬프트 시킨다. 상기 쉬프터(620)는 4진수로 표현된 데이터의 인덱스를 해당 스테이지의 넘버에 따라 라이트 쉬프트(right shift)시키는 블록이다. 이 블록의 동작을 살펴보면, 첫 번째 스테이지(s=0)에서는 데이터 인덱스(000, 001, 002, 003, 010, 011, ..., 330, 331, 332, 333) 가 입력되면 (s+1)개의 디지트, 즉, 1개의 디지트를 라이트 쉬프트(right-shift)시켜서 (00, 00, 00, 00, 01, 01, ... , 33, 33, 33, 33)을 출력한다. 동일한 인덱스에 대해서 두번째 스테이지(s=1)의 경우를 살펴보면, 데이터 인덱스 데이터 인덱스(000, 001, 002, 003, 010, 011, ..., 330, 331, 332, 333)가 입력되고 2개의 디지트를 라이트 쉬프트(right-shift)시켜서 (0, 0, 0, 0, 0, 0, ..., 3, 3, 3, 3)을 출력한다. 정리하면, 상기 쉬프터(620)는 스테이지 넘버에 따라 디지트(4진수, 2비트)를 각각 1개 4 진수-디지트(00, 00, 00, 01, ..., 33)와, 2개의 4진수-디지트(00, 00, 00, 00, 01, ..., 33)를 라이트 쉬프트(right shift)(0, 0, 0, 0, 0, ..., 3) 시킨다. The

상기한 과정은 쉬프터(620)가 데이터 인덱스 카운터(610)로부터 출력되는 4진수의 데이터 인덱스 중, 4s(rs) 자리수보다 상위 자리수에 해당하는 디지트를 선택하는 과정으로 설명될 수 있다. The above process may be described as a process in which the

비트 반전기(630)는 상기 쉬프터(620)의 출력 값을 비트(bit) 단위로 반전시키고 10진수로 변환하여 트위들 팩터 인덱스 생성을 위한 제2 인자를 출력한다. 여기서, 비트 반전이란 임의의 값을 최하위비트(LSB)에서 최상위비트(MSB) 순서로 읽어나가는 것을 말한다. 예를 들어, '0001'의 비트 반전 결과는 '1000'이고 , '0101'의 비트 반전 결과는 '1010' 이다. The

선택기(640)는 수학식 3의 [dS]r를 계산하기 위한 블록이다. 선택기(640)는 데이터 인덱스 카운터(610)에서 출력되는 데이터 인덱스 값 중 현재 스테이지 넘버에 따라 설정된 4진수-디지트(일반화 하면 r진수-디지트, 이하 동일하다)를 트위들 팩터 인덱스를 생성하기 위한 제1 인자로 선택하여 출력한다. 다시 말해, 상기 선택기(640)는 데이터 인덱스 카운터(610)의 출력을 4진수로 간주하고, 4진수로 표현된 데이터 인덱스(000, 001, 002, 003, 010, ...) 중이서 스테이지 0의 경우, 40 자리수인 d0(0, 1, 2, 3, 0, ...)을 제1 인자로 선택하고, 스테이지 1의 경우, 41 자리수인 d1(0, 0, 0, 0, 1, ...)를 제1 인자로 선택한다. 이를 일반화하면, 선택 기(640)는 r 진수의 데이터 인덱스 값에서 rs 자리수에 해당하는 디지트를 트위들 팩터 인덱스를 생성하기 위한 제1 인자로 선택하여 출력한다고 정리할 수 있다.The

보다 구체적인 예시를 들어 설명하면, 상기 선택기(640)는 스테이지 0에서, 두 번째 입력되는 데이터에 대한 데이터 인덱스가 [001]4 인 경우, 스테이지 0의 선택기는 [001]4의 40 자리수인 '1'을 제1 인자로 선택하여 출력한다. 반면, 스테이지 1에서, 두 번째 입력되는 데이터에 대한 데이터 인덱스가 [001]인 경우, 스테이지 1의 선택기는 [001]4의 41 자리수인 '0'을 제1 인자로 선택하여 출력한다.For example, when the data index for the second input data is [001] 4 in

스케일러(650)는 상기 스테이지 넘버 카운터(605)로부터 출력되는 스테이지 넘버(s)를 전달받아 트위들 팩터 인덱스 생성을 위한 제3 인자를 생성한다. 본 발명의 실시예에 따르면, 상기 제3 인자는 rS 일 수 있다. The

곱셈기(660)는 상기 선택기(640)에서 선택된 제1 인자, 비트 반전기(630)에서 출력되는 제2 인자, 스케일러(650)에서 출력되는 제3 인자를 서로 곱하여 트위들 팩터 인덱스를 생성하여 출력한다. The

본 발명의 트위들 팩터 인덱스 생성기(570)에 의해 생성된 트위들 팩터 인덱스에 대한 예시가 도 7에 도시된다. 여기서 NFFT=64임을 가정한다. An example of the tween factor index generated by the tween

이하에서는 데이터 인덱스가 7 인 경우를 예를 들어 트위들 팩터 인덱스 생성 과정에 대해 구체적으로 설명하도록 한다.Hereinafter, a case where the data index is 7 will be described in detail with reference to a tween factor index generation process.

우선, 스테이지 0인 경우, 스테이지 넘버 카운터(605)는 데이터 열이 입력되는 현재 스테이지의 넘버인 0을 결정하여 출력한다. 그리고 데이터 인덱스 카운터(610)는 입력되는 데이터열에 대한 인덱스를 순차적으로 카운트 하여 r 진수(4진수)로 출력하는데, 본 예시에서는 7([013]4)임을 가정하였다. First, in the case of

그러면 선택기(640)는 상기 데이터 인덱스 카운터(610)로부터 출력되는 4 진수의 데이터 인덱스 중, 40(rs) 자리수에 대응하는 디지트인 '3'을 제1 인자로 선택하여 출력한다. Then, the

한편, 쉬프터(620)는 상기 데이터 인덱스 카운터(610)로부터 출력되는 4진수의 데이터 인덱스 중, 40(rs) 자리수보다 상위 자리수에 해당하는 디지트인 '01'을 선택하고, 이를 2진수로 변경하여 출력하는데, 그 값은 '0001'이다. Meanwhile, the

그리고 비트 반전기(630)는 상기 쉬프터(620)로부터 출력되는 값인 '0001'을 수신하고, 이를 비트 반전 하여 '1000'을 생성한다. 그리고 비트 반전기(630)는 상기 생성된 '1000'을 10 진수로 변환하여 제2 인자인 '8'을 출력한다. The

한편, 스케일러(650)는 스테이지 넘버 카운터(605)로부터 스테이지 넘버인 0을 수신하여 제3 인자로서 '1'(rs)를 출력한다. Meanwhile, the

그러면, 곱셈기(660)는 선택기(640), 비트 반전기(630), 스케일러(650)로부터 출력되는 값인 제1 인자('3'), 제2 인자('8'), 제3 인자('1')를 각각 수신하고, 이들을 서로 곱하여 트위들 팩터 인덱스인 '24'를 생성하여 출력한다. Then, the

정리하면, 스테이지 0에서, 데이터 인덱스 7인 데이터에 대한 트위들 팩터 인덱스는 24이다. In summary, at

그리고 스테이지 1인 경우, 스테이지 넘버 카운터(605)는 데이터 열이 입력되는 현재 스테이지의 넘버인 1을 결정하여 출력한다. 그리고 데이터 인덱스 카운터(610)는 입력되는 데이터열에 대한 인덱스를 순차적으로 카운트 하여 r 진수(4진수)로 출력하는데, 본 예시에서는 7([013]4)임을 가정하였다. In the case of

그러면 선택기(640)는 상기 데이터 인덱스 카운터(610)로부터 출력되는 4 진수의 데이터 인덱스 중, 41(rs) 자리수에 대응하는 디지트인 '1'을 제1 인자로 선택하여 출력한다. Then, the

한편, 쉬프터(620)는 상기 데이터 인덱스 카운터(610)로부터 출력되는 4진수의 데이터 인덱스 중, 41(rs) 자리수보다 상위 자리수에 해당하는 디지트인 '0'을 선택하고, 이를 2진수로 변경하여 출력하는데, 그 값은 '00'이다. Meanwhile, the

그리고 비트 반전기(630)는 상기 쉬프터(620)로부터 출력되는 값인 '00'을 수신하고, 이를 비트 반전 하여 '00'을 생성한다. 그리고 비트 반전기(630)는 상기 생성된 '00'을 10 진수로 변환하여 제2 인자인 '0'을 출력한다. The

한편, 스케일러(650)는 스테이지 넘버 카운터(605)로부터 스테이지 넘버인 0을 수신하여 제3 인자로서 '4'(rs)를 출력한다. Meanwhile, the

그러면, 곱셈기(660)는 선택기(640), 비트 반전기(630), 스케일러(650)로부 터 출력되는 값인 제1 인자('1'), 제2 인자('0'), 제3 인자('4')를 각각 수신하고, 이들을 서로 곱하여 트위들 팩터 인덱스인 '0'를 생성하여 출력한다. The

정리하면, 스테이지 1에서, 데이터 인덱스 7인 데이터에 대한 트위들 팩터 인덱스는 0이다. In summary, in

도 8은 NFFT=64에 대해 상기한 수학식 3을 적용한 데이터 흐름도(Signal Flow Graph)를 도시하는 도면이다. FIG. 8 is a diagram showing a data flow graph (Signal Flow Graph) to which

도 9는 본 발명의 실시예에 따라 트위들 팩터 인덱스를 생성하는 과정을 도시하는 순서도이다. 9 is a flowchart illustrating a process of generating a tween factor index according to an embodiment of the present invention.

우선, S910 단계에서 스테이지 넘버 카운터(605)는 데이터 열이 입력되는 현재 스테이지의 넘버를 결정하여 출력한다. 그리고 S920 단계에서, 데이터 인덱스 카운터(610)는 입력되는 데이터열에 대한 인덱스를 순차적으로 카운트 하고, S930 단계에서 상기 카운트되는 데이터 인덱스를 r 진수로 출력한다.First, in step S910, the

그리고 S940 단계에서, 선택기(640)는 상기 데이터 인덱스 카운터(610)로부터 출력되는 r 진수의 데이터 인덱스 중, rs 자리수에 대응하는 디지트를 제1 인자로 선택하여 출력한다. In operation S940, the

그리고 S950 단계에서, 쉬프터(620)는 상기 데이터 인덱스 카운터(610)로부터 출력되는 r 진수 데이터 인덱스 중, rs 자리수보다 상위 자리수에 해당하는 디지트를 선택하고, 이를 비트 반전하여 제2 인자로서 출력한다. 여기서 비트 반전된 상기 제2 인자는 10진수로 표현된다. In operation S950, the

한편, 스케일러는 S960 단계에서, 스테이지 넘버 카운터로부터 스테이지 넘버를 수신하여 제3 인자로서 rs를 출력한다. In operation S960, the scaler receives the stage number from the stage number counter and outputs r s as a third factor.

그러면, 곱셈기(660)는 S970 단계에서, 선택기(640), 비트 반전기(630), 스케일러(650)로부터 출력되는 제1 인자, 제2 인자, 제3 인자를 각각 수신하고, 이들을 서로 곱하여 트위들 팩터 인덱스를 생성하여 출력한다. Then, the

본 명세서와 도면에 개시 된 본 발명의 실시예들은 본 발명의 기술 내용을 쉽게 설명하고 본 발명의 이해를 돕기 위해 특정 예를 제시한 것일 뿐이며, 본 발명의 범위를 한정하고자 하는 것은 아니다. 여기에 개시된 실시예들 이외에도 본 발명의 기술적 사상에 바탕을 둔 다른 변형 예들이 실시 가능하다는 것은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 자명한 것이다.The embodiments of the present invention disclosed in the present specification and drawings are merely illustrative of specific embodiments of the present invention and are not intended to limit the scope of the present invention in order to facilitate understanding of the present invention. It will be apparent to those skilled in the art that other modifications based on the technical idea of the present invention can be carried out in addition to the embodiments disclosed herein.

도 1은 종래 N=64에 대한 Radix-2의 2승 DIF FFT의 신호 흐름 그래프(Signal Flow Graph, SFG)를 도시하는 도면.1 shows a signal flow graph (SFG) of a Radix-2 power of two DIF FFTs for a conventional N = 64.

도 2는 도 1에 도시된 Radix-2의 2승 DIF FFT 알고리즘을 이용하여 구현된 FFT 프로세서 구조를 도시하는 도면.FIG. 2 illustrates an FFT processor structure implemented using Radix-2's quadratic DIF FFT algorithm shown in FIG.

도 3은 도 2에 도시된 임의의 스테이지의 세부 구조를 도시하는 도면.FIG. 3 shows a detailed structure of any stage shown in FIG.

도 4는 N=16에 대해 생성된 트위들 팩터의 인덱스를 도시하는 도면.4 illustrates the index of the tween factor generated for N = 16.

도 5는 본 발명의 실시예에 따른 FFT 프로세서의 내부 구조를 도시하는 블록도.5 is a block diagram illustrating an internal structure of an FFT processor according to an embodiment of the present invention.

도 6은 상기 트위들 팩터 인덱스 생성기(570)의 구체적인 구조를 도시하는 도면.6 illustrates a detailed structure of the tweed

도 7은 본 발명의 트위들 팩터 인덱스 생성기(570)에 의해 생성된 트위들 팩터 인덱스에 대한 예시를 도시하는 도면.FIG. 7 shows an example of the tween factor index generated by the tween

도 8은 NFFT=64에 대해 상기한 수학식 3을 적용한 데이터 흐름도(Signal Flow Graph)를 도시하는 도면.FIG. 8 is a diagram showing a data flow graph to which

도 9는 본 발명의 실시예에 따라 트위들 팩터 인덱스를 생성하는 과정을 도시하는 순서도.9 is a flowchart illustrating a process of generating a tween factor index according to an embodiment of the present invention.

도 10은 본 발명의 실시예에 따라 I/Q 변환기의 스위칭 주기를 도시하는 도면.10 illustrates a switching period of an I / Q converter in accordance with an embodiment of the present invention.

Claims (4)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090057250A KR20100138639A (en) | 2009-06-25 | 2009-06-25 | Method and apparatus for tweed factor index generation in fast Fourier transform system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090057250A KR20100138639A (en) | 2009-06-25 | 2009-06-25 | Method and apparatus for tweed factor index generation in fast Fourier transform system |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20100138639A true KR20100138639A (en) | 2010-12-31 |

Family

ID=43512085

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090057250A Withdrawn KR20100138639A (en) | 2009-06-25 | 2009-06-25 | Method and apparatus for tweed factor index generation in fast Fourier transform system |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR20100138639A (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170061054A (en) * | 2015-11-25 | 2017-06-02 | 한국전자통신연구원 | Fully parallel fast fourier transform device |

| CN119854091A (en) * | 2024-12-30 | 2025-04-18 | 重庆邮电大学 | FPGA-based low-complexity OCDM modulation and demodulation implementation method |

-

2009

- 2009-06-25 KR KR1020090057250A patent/KR20100138639A/en not_active Withdrawn

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20170061054A (en) * | 2015-11-25 | 2017-06-02 | 한국전자통신연구원 | Fully parallel fast fourier transform device |

| CN119854091A (en) * | 2024-12-30 | 2025-04-18 | 重庆邮电大学 | FPGA-based low-complexity OCDM modulation and demodulation implementation method |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP0855657B1 (en) | Fast fourier transforming apparatus and method | |

| WO2005022794A2 (en) | Combined inverse fast fourier transform and guard interval processing for efficient implementation of ofdm based systems | |

| RU2007100349A (en) | MATRIX VALUES AND DEVICE FOR PROCESSING SIGNALS | |

| CN100558020C (en) | Multi-carrier transmission system and method for subcarrier relocation and guard interval insertion | |

| CN101937423B (en) | Streamline FFT/IFFT processing system | |

| US9735996B2 (en) | Fully parallel fast fourier transformer | |

| US9727531B2 (en) | Fast fourier transform circuit, fast fourier transform processing method, and program recording medium | |

| KR20100138639A (en) | Method and apparatus for tweed factor index generation in fast Fourier transform system | |

| KR101229648B1 (en) | Circular fast fourier transform | |

| KR100602272B1 (en) | Fast Fourier Transform Device and Method for Processing Data at High Speed | |

| JP3065979B2 (en) | Fast Fourier transform apparatus and method, variable bit reverse circuit, inverse fast Fourier transform apparatus and method, and OFDM reception and transmission apparatus | |

| KR100720949B1 (en) | Fast fourier transform processor in ofdm system and transform method thereof | |

| KR100892292B1 (en) | Quadratic Fast Fourier Transform Processor of Radii 2 Using Parallel Structure and Pipeline Method | |

| CN111291315A (en) | Data processing method, device and equipment | |

| Oh et al. | Implementation of Orthogonal Frequency Division Multiplexing Modem Using Radix-N Pipeline Fast Fourier Transform (FFT) Processor | |

| JP4995987B2 (en) | Signal receiving apparatus and communication system | |

| JP6779226B2 (en) | Transmitter, communication device, transmission signal generation method, receiver and demodulation method | |

| KR20070061357A (en) | Memory address calculation method of fast Fourier transform system and tweed factor generation device using same | |

| KR20040110338A (en) | 3780-point DFT processor using CORDIC algorithm | |

| KR102505022B1 (en) | Fully parallel fast fourier transform device | |

| JP5131346B2 (en) | Wireless communication device | |

| CN101490671A (en) | Folds input data values onto a transformation function | |

| KR100230847B1 (en) | Orthogonal Frequency Division Multiplexing Receiving System | |

| Ahmad et al. | implementation and performance evaluation of three reconfigurable FFT cores for application in software defined radio system | |

| JP5776986B2 (en) | Addition / subtraction hardware computing unit, processor, and mobile communication terminal including the processor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20090625 |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |