KR20090085877A - Vertical structure semiconductor light emitting device manufacturing method - Google Patents

Vertical structure semiconductor light emitting device manufacturing method Download PDFInfo

- Publication number

- KR20090085877A KR20090085877A KR20080011776A KR20080011776A KR20090085877A KR 20090085877 A KR20090085877 A KR 20090085877A KR 20080011776 A KR20080011776 A KR 20080011776A KR 20080011776 A KR20080011776 A KR 20080011776A KR 20090085877 A KR20090085877 A KR 20090085877A

- Authority

- KR

- South Korea

- Prior art keywords

- nitride semiconductor

- type nitride

- layer

- semiconductor layer

- etch stop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Led Devices (AREA)

Abstract

본 발명은 수직구조 반도체 발광소자 제조방법에 관한 것으로서, 본 발명의 바람직한 실시 형태는, 반도체 단결정 성장용 기판 상에 개구부를 갖는 식각저지층을 형성하는 단계와, 상기 개구부를 통하여 상기 반도체 단결정 성장용 기판 및 상기 식각저지층 상에 n형 질화물 반도체층, 활성층 및 p형 질화물 반도체층을 순차적으로 성장시키는 단계와, 상기 p형 질화물 반도체층 상에 도전성 기판을 형성하는 단계와, 상기 반도체 단결정 성장용 기판을 상기 n형 질화물 반도체층으로부터 제거하는 단계와, 상기 식각저지층의 개구부를 통하여 노출된 상기 n형 질화물 반도체층을 식각하여 요철 구조를 형성하는 단계 및 상기 n형 질화물 반도체층과 전기적으로 연결되도록 n형 전극을 형성하는 단계를 포함하는 수직구조 반도체 발광소자 제조방법을 제공한다.The present invention relates to a method for manufacturing a vertical semiconductor light emitting device, and a preferred embodiment of the present invention includes forming an etch stop layer having an opening on a substrate for semiconductor single crystal growth, and for growing the semiconductor single crystal through the opening. Sequentially growing an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer on the substrate and the etch stop layer, forming a conductive substrate on the p-type nitride semiconductor layer, and growing the semiconductor single crystal Removing the substrate from the n-type nitride semiconductor layer, etching the n-type nitride semiconductor layer exposed through the opening of the etch stop layer to form an uneven structure, and electrically connecting the n-type nitride semiconductor layer It provides a vertical structure semiconductor light emitting device manufacturing method comprising the step of forming an n-type electrode to The.

본 발명에 따르면, 광 방출 면 상에 요철 구조를 형성함에 있어서, 반도체 단결정의 결정성을 해치지 않으면서도 그 크기와 형상을 용이하게 제어할 수 있는 수직구조 반도체 발광소자의 제조방법을 얻을 수 있다.According to the present invention, in the formation of the uneven structure on the light emitting surface, it is possible to obtain a manufacturing method of the vertical structure semiconductor light emitting device which can easily control the size and shape without compromising the crystallinity of the semiconductor single crystal.

Description

본 발명은 수직구조 반도체 발광소자 제조방법에 관한 것으로서, 특히 광 방출 면에 요출 구조를 형성하는 단계를 포함하는 수직구조 반도체 발광소자 제조방법에 관한 것이다.The present invention relates to a method for manufacturing a vertical semiconductor light emitting device, and more particularly, to a method for manufacturing a vertical semiconductor light emitting device including forming a concave structure on a light emitting surface.

반도체 발광소자(Light Emitting Diode, LED)는 전류가 가해지면 p,n형 반도체의 접합 부분에서 전자와 정공의 재결합에 기하여, 다양한 색상의 빛을 발생시킬 수 있는 반도체 장치이다. 이러한 LED는 필라멘트에 기초한 발광소자에 비해 긴 수명, 낮은 전원, 우수한 초기 구동 특성, 높은 진동 저항 및 반복적인 전원 단속에 대한 높은 공차 등의 여러 장점을 갖기 때문에 그 수요가 지속적으로 증가하고 있다. 특히, 최근에는, 청색 계열의 단파장 영역에서 발광이 가능한 III족 질화물 반도체가 각광을 받고 있다. BACKGROUND A light emitting diode (LED) is a semiconductor device capable of generating light of various colors based on recombination of electrons and holes at a junction portion of a p and n type semiconductor when current is applied thereto. The demand for these LEDs continues to increase because of their advantages such as long life, low power, excellent initial drive characteristics, high vibration resistance, and high tolerance for repetitive power interruptions. In particular, in recent years, group III nitride semiconductors capable of emitting light in a blue short wavelength region have been in the spotlight.

이러한 III족 질화물 반도체를 이용한 발광소자를 구성하는 질화물 단결정은 사파이어 또는 SiC 기판과 같이 특정의 단결정 성장용 기판 상에서 형성된다. 하지 만, 사파이어와 같이 절연성 기판을 사용하는 경우에는 전극의 배열에 큰 제약을 받게 된다. 즉, 종래의 질화물 반도체 발광소자는 전극이 수평방향으로 배열되는 것이 일반적이므로, 전류흐름이 협소 해지게 된다. 이러한 협소한 전류 흐름으로 인해, 발광소자의 동작 전압(Vf)이 증가하여 전류효율이 저하되며, 이와 더불어 정전기 방전(Electrostatic discharge)에 취약해지는 문제가 있다. 이러한 문제를 해결하기 위해서, 수직구조를 갖는 반도체 발광소자가 요구된다. The nitride single crystal constituting the light emitting device using the group III nitride semiconductor is formed on a specific single crystal growth substrate, such as a sapphire or SiC substrate. However, when an insulating substrate such as sapphire is used, the arrangement of the electrodes is greatly limited. That is, in the conventional nitride semiconductor light emitting device, since the electrodes are generally arranged in the horizontal direction, the current flow becomes narrow. Due to such a narrow current flow, the operating voltage (Vf) of the light emitting device is increased, the current efficiency is lowered, and at the same time, there is a problem of being vulnerable to electrostatic discharge. In order to solve this problem, a semiconductor light emitting device having a vertical structure is required.

수직구조 반도체 발광소자의 경우, 활성층에서 발생된 광은 공기/GaN 계면에 입사 시 입사각에 따라 반사 정도가 달라진다. 이 경우, 이론적으로 입사각이 26° 이상인 경우, 활성층에서 발생된 광은 모두 내부 전반사 된다. 따라서, 이러한 문제를 최소화하여 외부 광추출효율을 향상시키기 위해, 광이 외부로 투과되는 면에 요철 구조를 형성할 수 있다.In the case of the vertical semiconductor light emitting device, the light generated in the active layer has a different degree of reflection depending on the incident angle when incident on the air / GaN interface. In this case, theoretically, when the incident angle is 26 ° or more, all light generated in the active layer is totally internally reflected. Therefore, in order to minimize such a problem and improve the external light extraction efficiency, the concave-convex structure can be formed on the surface through which light is transmitted to the outside.

당 기술 분야에서 알려진 실험 결과에 따르면, 요철 구조가 없는 경우에 비하여 요철 패턴이 있는 경우 광 추출효율이 향상되며, 요철 구조의 단면이 사각형인 경우보다, 삼각형 또는 사다리꼴인 경우 광 추출효율이 약간 더 높은 것이 일반적이다. 나아가, 상기 요철 구조는 그 크기가 작을수록(나노사이즈) 광 추출효율 향상에 더 유리할 수 있다.According to experimental results known in the art, light extraction efficiency is improved when there is an uneven pattern, and when the cross-section of the uneven structure is rectangular, but slightly triangular or trapezoidal, the light extraction efficiency is slightly higher. High is common. Further, the uneven structure may be more advantageous in improving light extraction efficiency as the size thereof is smaller (nano size).

한편, 수직구조 반도체 발광소자에서는 요철 구조 형성을 위하여, n형 질화물 반도체층에 반응성 이온 식각(RIE) 등을 적용하는 것이 일반적이나, 이 경우, 요철 구조 주변 영역은 플라즈마 손상을 입어 광 추출효율이 저하되는 문제가 있다.On the other hand, in the vertical semiconductor light emitting device, reactive ion etching (RIE) or the like is generally applied to the n-type nitride semiconductor layer in order to form the uneven structure, but in this case, the region around the uneven structure suffers plasma damage, resulting in high light extraction efficiency. There is a problem of deterioration.

따라서, 당 기술 분야에서는, 요철 구조를 형성함에 있어, 반도체 단결정의 결정성을 해치지 않으면서도 그 크기와 형상을 용이하게 제어할 수 있는 기술의 개발이 요구된다.Therefore, in the art, it is required to develop a technology that can easily control the size and shape of the uneven structure without compromising the crystallinity of the semiconductor single crystal.

본 발명은 상기와 같은 문제점을 해결하기 위한 것으로, 본 발명의 일 목적은 광 방출 면 상에 요철 구조를 형성함에 있어서, 반도체 단결정의 결정성을 해치지 않으면서도 그 크기와 형상을 용이하게 제어할 수 있는 수직구조 반도체 발광소자의 제조방법을 제공하는 데에 있다.The present invention is to solve the above problems, an object of the present invention is to form an uneven structure on the light emitting surface, it is possible to easily control the size and shape of the semiconductor single crystal without compromising the crystallinity The present invention provides a method for manufacturing a vertical semiconductor light emitting device.

상기한 목적을 달성하기 위해서, 본 발명의 바람직한 실시 형태는,In order to achieve the above object, a preferred embodiment of the present invention,

반도체 단결정 성장용 기판 상에 개구부를 갖는 식각저지층을 형성하는 단계와, 상기 개구부를 통하여 상기 반도체 단결정 성장용 기판 및 상기 식각저지층 상에 n형 질화물 반도체층, 활성층 및 p형 질화물 반도체층을 순차적으로 성장시키는 단계와, 상기 p형 질화물 반도체층 상에 도전성 기판을 형성하는 단계와, 상기 반도체 단결정 성장용 기판을 상기 n형 질화물 반도체층으로부터 제거하는 단계와, 상기 식각저지층의 개구부를 통하여 노출된 상기 n형 질화물 반도체층을 식각하여 요철 구조를 형성하는 단계 및 상기 n형 질화물 반도체층과 전기적으로 연결되도록 n형 전극을 형성하는 단계를 포함하는 수직구조 반도체 발광소자 제조방법을 제공한다.Forming an etch stop layer having an opening on the semiconductor single crystal growth substrate, and forming an n-type nitride semiconductor layer, an active layer, and a p-type nitride semiconductor layer on the semiconductor single crystal growth substrate and the etch stop layer through the openings; Sequentially growing; forming a conductive substrate on the p-type nitride semiconductor layer; removing the semiconductor single crystal growth substrate from the n-type nitride semiconductor layer; and openings of the etch stop layer And forming an uneven structure by etching the exposed n-type nitride semiconductor layer and forming an n-type electrode to be electrically connected to the n-type nitride semiconductor layer.

바람직하게는, 상기 n형 질화물 반도체층을 식각하여 요철 구조를 형성하는 단계는 습식 식각에 의해 실행될 수 있으며, 이 경우, KOH 용액을 이용할 수 있다.Preferably, the step of forming the uneven structure by etching the n-type nitride semiconductor layer may be performed by wet etching, in this case, KOH solution may be used.

특히, 상기 n형 질화물 반도체층에서 습식 식각에 의해 제거된 영역은 피라미드 형상을 갖는 것이 바람직하다. 또한, 상기 요철 구조를 이루는 상기 n형 질화물 반도체층 면은 (11-2-2) 결정면일 수 있다.In particular, the region removed by wet etching in the n-type nitride semiconductor layer preferably has a pyramid shape. In addition, the n-type nitride semiconductor layer surface forming the uneven structure may be a (11-2-2) crystal surface.

본 발명의 바람직한 실시 형태에서, 상기 식각저지층을 형성하는 단계 전에 상기 반도체 단결정 성장용 기판 상에 언도프 질화물 반도체층을 성장시키는 단계를 더 포함하며, 상기 n형 질화물 반도체층을 식각하여 요철 구조를 형성하는 단계는 상기 언도프 질화물 반도체층을 제거하는 단계를 포함할 수 있다.In a preferred embodiment of the present invention, further comprising the step of growing an undoped nitride semiconductor layer on the semiconductor single crystal growth substrate before forming the etch stop layer, by etching the n-type nitride semiconductor layer uneven structure The step of forming may include removing the undoped nitride semiconductor layer.

또한, 상기 n형 질화물 반도체층을 식각하여 요철 구조를 형성하는 단계 후에, 상기 식각저지층을 제거하는 단계를 더 포함할 수 있다.The method may further include removing the etch stop layer after etching the n-type nitride semiconductor layer to form an uneven structure.

바람직하게는, 상기 식각저지층은 금속산화물, 실리콘산화물 및 실리콘질화물으로 구성된 그룹으로부터 선택된 물질을 적어도 하나 포함할 수 있다.Preferably, the etch stop layer may include at least one material selected from the group consisting of metal oxides, silicon oxides and silicon nitrides.

또한, 상기 식각저지층의 두께는 10 ~ 500㎚인 것이 바람직하다.In addition, the thickness of the etch stop layer is preferably 10 ~ 500nm.

상기 식각저지층은 격자 패턴 구조를 갖는 것이 바람직하며, 이 경우, 상기 식각저지층을 이루는 격자 패턴은 각 패턴의 직경이 100 ~ 500㎚이고, 격자 패턴의 주기는 200 ~ 500㎚인 것이 바람직하다.The etch stop layer preferably has a lattice pattern structure. In this case, the lattice pattern forming the etch stop layer preferably has a diameter of 100 to 500 nm, and a period of the lattice pattern is 200 to 500 nm. .

한편, 상기 p형 질화물 반도체층을 성장시키는 단계와 상기 도전성 기판을 형성하는 단계 사이에, 상기 p형 질화물 반도체층의 상면 및 측면을 덮도록 반사금 속층을 형성하는 단계를 더 포함할 수 있다. 이 경우, 상기 반사금속층은 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt 및 Au으로 이루어진 그룹으로부터 선택된 적어도 하나의 물질을 포함할 수 있다.On the other hand, between the step of growing the p-type nitride semiconductor layer and the step of forming the conductive substrate, forming a reflective metal layer to cover the upper surface and the side of the p-type nitride semiconductor layer. In this case, the reflective metal layer may include at least one material selected from the group consisting of Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, and Au.

또한, 상기 반도체 단결정 성장용 기판을 제거하는 단계는 레이저 리프트 오프 공정에 의해 실행될 수 있다.In addition, the removing of the semiconductor single crystal growth substrate may be performed by a laser lift-off process.

상술한 바와 같이, 본 발명에 따르면, 광 방출 면 상에 요철 구조를 형성함에 있어서, 반도체 단결정의 결정성을 해치지 않으면서도 그 크기와 형상을 용이하게 제어할 수 있는 수직구조 반도체 발광소자의 제조방법을 얻을 수 있다.As described above, according to the present invention, in forming a concave-convex structure on the light emitting surface, a method of manufacturing a vertical structure semiconductor light emitting device which can easily control the size and shape of the semiconductor single crystal without harming the crystallinity. Can be obtained.

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시형태들을 설명한다. 다만, 본 발명의 실시형태는 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 이하 설명하는 실시형태로 한정되는 것은 아니다. 또한, 본 발명의 실시형태는 당업계에서 평균적인 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있으며, 도면상의 동일한 부호로 표시되는 요소는 동일한 요소이다.Hereinafter, preferred embodiments of the present invention will be described with reference to the accompanying drawings. However, embodiments of the present invention may be modified in various other forms, and the scope of the present invention is not limited to the embodiments described below. In addition, the embodiments of the present invention are provided to more completely explain the present invention to those skilled in the art. Accordingly, the shape and size of elements in the drawings may be exaggerated for clarity, and the elements denoted by the same reference numerals in the drawings are the same elements.

도 1a 내지 도 1h는 본 발명의 일 실시 형태에 따른 수직구조 반도체 발광소자의 제조 방법을 설명하기 위한 공정별 단면도이다.1A to 1H are cross-sectional views illustrating processes for manufacturing a vertical structure semiconductor light emitting device according to one embodiment of the present invention.

우선, 도 1a와 같이, 사파이어 기판(11) 상에 식각저지층(Etch Stop Layer, 12)을 형성한다.First, as shown in FIG. 1A, an

상기 사파이어 기판(11)은, 육각-롬보형(Hexa-Rhombo R3c) 대칭성을 갖는 결정체로서 c축 방향의 격자상수가 13.001Å, a축 방향으로는 4.765Å의 격자 간 거리를 가지며, 사파이어 면방향(orientation plane)으로는 C(0001)면, A(1120)면, R(1102)면 등을 갖는다. 이러한 사파이어 기판(11)의 C면은 비교적 질화물 박막의 성장이 용이하며, 고온에서 안정하기 때문에 질화물 성장용 기판으로 주로 사용된다. 다만, 본 발명에서 단결정 성장용 기판으로 사파이어만을 사용할 수 있는 것은 아니며, SiC, MgAl2O4, MgO, LiAlO2, LiGaO2 등으로 이루어진 기판도 채용이 가능하다.The

사파이어 기판(11) 상에 형성되는 식각저지층(12)은 상기 사파이어 기판(11) 상면의 소정 영역을 노출시키는 개구부를 갖도록 패턴 구조를 이룬다. 상기 식각저지층(12)은 후술할 바와 같이, n형 질화물 반도체층에 요철 구조 형성을 위한 습식 식각 과정에서 요철 구조가 원하는 형상이 되도록 n형 질화물 반도체층의 일부 영역이 식각 되지 않도록 한다. 이를 위해, 상기 식각저지층(12)은 습식 식각 용액(예컨대, KOH)에 식각 되지 않는 물질이 채용되며, 구체적으로, 금속산화물, 실리 콘 산화물, 실리콘 질화물 등을 사용할 수 있다. 금속산화물로 식각저지층(12)을 형성하는 경우에는 투광성과 전기전도성을 모두 갖는 TCO, ZnO 등을 사용하는 것이 바람직하다. 상기 식각저지층(12)의 높이(t)는 원하는 요철 구조의 크기·형상에 따라 조절될 수 있으며, 다만, 적절한 높이(t)는 10 ~ 500㎚이다.The

한편, 도시하지는 않았으나, 상기 식각저지층(12)은 당 기술분야에서 공지된 방법을 이용하여 형성할 수 있으며, 예를 들어, 포토리소그래피(Photolithography), 임프린트, 홀로리소그래피(Hololithography) 등의 방법으로 마스크를 형성한 후 원하는 식각저지층(12) 패턴을 제외한 나머지 영역을 제거하는 방법을 이용하여 형성할 수 있다.Although not shown, the

이어서, 도 1b와 같이, 개구부에 의해 노출된 사파이어 기판(11) 상면을 통하여 n형 질화물 반도체층(13)을 성장시켜, 상기 사파이어 기판(11) 및 식각저지층(12)을 덮도록 한다. 다음으로, 도 1c와 같이, n형 질화물 반도체층(13) 상에 활성층(14)과 p형 질화물 반도체층(15)을 성장시킨다. Next, as shown in FIG. 1B, the n-type

상기 n형 및 p형 질화물 반도체층(13, 15)은 AlxInyGa(1-x-y)N 조성식(여기서, 0≤x≤1, 0≤y≤1, 0≤x+y≤1임)을 갖고, 각각 n형 불순물 및 p형 불순물이 도핑된 반도체 물질로 이루어질 수 있으며, 대표적으로, GaN, AlGaN, InGaN이 있다. 또한, 상기 n형 불순물로 Si, Ge, Se, Te 또는 C 등이 사용될 수 있으며, 상기 p형 불순물로는 Mg, Zn 또는 Be 등이 대표적이다.The n-type and p-type

상기 활성층(14)은 전자와 정공의 재결합에 의해 빛이 발생하는 층으로서, 단일 또는 다중 양자 웰 구조를 갖는 질화물 반도체층으로 구성된다. 상기 n형 질화물 반도체층, 활성층 및 p형 질화물 반도체층(13, 14, 15)은 유기금속 기상증착법(MOCVD), 분자빔성장법(MBE) 및 하이브리드 기상증착법(HVPE)등으로 성장될 수 있다.The

이어서, 도 1d와 같이, p형 질화물 반도체층(15) 상에 도전성 기판(16)을 형성한다.Subsequently, as illustrated in FIG. 1D, the

상기 도전성 기판(16)은 최종 수직구조 발광소자에 포함되는 요소로서, p측 전극 역할과 함께 상기 발광구조물을 지지하는 지지체의 역할을 수행한다. 특히, 후술할 레이저리프트 오프 공정 등으로 상기 사파이어 기판(11)을 제거할 시에, 상기 도전성 기판(16)에 의해 상대적으로 두께가 얇은 상기 발광구조물을 보다 용이하게 다룰 수 있다.The

한편, 상기 도전성 기판(16)이 금속인 경우에는 도금, 증착, 스퍼터링 등의 공정이 가능 하나, 공정 효율상 도금 공정이 바람직하다. 상기 도금 공정은 전해도금, 비전해도금, 증착도금 등 금속층을 형성하는데 사용되는 공지의 도금 공정을 포함하며, 이 중에서, 도금 시간이 적게 소요되는 전해도금법을 이용하는 것이 바람직하다. 다만, 본 발명에서 상기 도전성 기판의 형성 방법은 이에 제한되지 않으며, 웨이퍼 본딩을 통하여 상기 도전성 기판(16)을 접합시킬 수도 있다.On the other hand, when the

다음으로, 레이저 리프트오프(Laser Lift Off, LLO) 공정에 의해 사파이어 기판(11)을 제거한다. 이를 위해, 상기 사파이어 기판(11) 하면으로 레이저빔을 조사한다. 이 경우, 레이저빔은 사파이어 기판(11)의 전면에 조사되는 것보다는, 상기 사파이어 기판(11) 상에 형성된 최종 발광소자의 크기로 분리될 수 있도록 발광구조물 각각에 복수 회 조사되는 것이 바람직하다. Next, the

한편, 사파이어 기판(11)을 제거하는 단계는 본 실시 형태와 같이 레이저 리프트오프 공정이 바람직하나, 본 발명은 이에 제한되지 않으며, 다른 기계적 또는 화학적 공정을 통하여서도 제거가 가능하다. 도 1e에서는 사파이어 기판이 제거된 상태를 도시하였으며, 도 1e에 도시된 바와 같이, 사파이어 기판과 접촉하고 있던 n형 질화물 반도체층(13)의 면은 외부로 노출된다.Meanwhile, the step of removing the

다음으로, 도 1f와 같이, 상기 n형 질화물 반도체층(13)의 노출면을 식각하여 요철 구조(P)를 형성한다. 본 실시 형태의 경우, 상기 요철 구조(P)는 습식 식각, 상세하게는, KOH 용액을 이용하여 형성될 수 있다. 이에 따라, RIE와 같은 건식 식각을 이용한 경우에 비하여 요철 구조 주변 영역에서 반도체 단결정의 손상을 최소화할 수 있다. 나아가, 패턴 구조를 갖는 식각저지층(12)에 의해 원하는 형상의 요철 구조를 용이하게 형성할 수 있다. 요철 구조 형성에 관한 보다 상세한 사항을, 도 2, 도 3 및 도 4를 참조하여 설명한다.Next, as shown in FIG. 1F, the exposed surface of the n-type

도 2는 사파이어 기판 상에 형성된 식각저지층을 위에서 바라본 평면도이며, 도 3은 n형 질화물 반도체층이 식각되어 요철 구조가 생기는 모습을 나타내는 평면 도이며, 도 4는 식각저지층의 패턴 간 거리에 따른 요철 구조의 변화를 나타내는 단면도이다. FIG. 2 is a plan view from above of an etch stop layer formed on a sapphire substrate, and FIG. 3 is a plan view showing an uneven structure formed by etching an n-type nitride semiconductor layer, and FIG. 4 is a distance between patterns of the etch stop layer. It is sectional drawing which shows the change of the uneven structure along.

우선, 도 2를, 본 실시 형태에서 식각저지층(12)은 격자 패턴 구조, 더욱 상세하게는, 육각(Hexagonal) 격자 패턴 구조를 가지며, 식각저지층(12)이 형성되지 않은 영역에서 사파이어 기판(11)은 외부로 노출된다. 상기 식각저지층(12)의 패턴 형상은 n형 질화물 반도체층에 형성되는 요철 구조의 형상과 크기를 결정할 수 있다. 즉, 상기 패턴의 주기(s)와 직경(d)은 요철 구조 각각의 폭과 높이를 결정한다.2, in the present embodiment, the

도 3 및 도 4에 도시된 바와 같이, n형 질화물 반도체층(13)에 형성되는 요철 구조(P)는 식각저지층(12)의 서로 인접한 패턴 사이 영역이 제거됨으로써 생긴다. 또한, 그 제거된 영역은 피라미드 구조 또는 이와 유사한 형상을 가지며, 상기 요철 구조(P)는 육각 격자 패턴을 따라 형성된다.As shown in FIGS. 3 and 4, the uneven structure P formed in the n-type

즉, KOH 용액 등과 같은 식각 용액이 노출된 n형 질화물 반도체층(13) 상면에 적용되면, 상기 n형 질화물 반도체층(13)은 특정한 결정면, 예를 들어, (11-2-2) 면을 갖는 요철 구조가 형성될 수 있다. 이 경우, 상기 밀러 지수 (11-2-2) 중의 [-2]은 [2] 위에 바(bar)가 붙은 것을 나타낸다. 이와 같이, 상기 n형 질화물 반도체층(13)은 특정한 결정면이 노출되기 전까지만 식각 용액에 의해 제거되며, 식각저지층(13)의 패턴 구조를 적절히 조절함으로써 요철 구조의 형상과 크기를 용이하게 제어할 수 있다.That is, when an etching solution such as a KOH solution or the like is applied to the exposed upper surface of the n-type

이 경우, 도 4에 도시된 바와 같이, 식각저지층(12) 패턴의 간격이 커질수록 요철 구조의 높이(h)는 커지므로, 상술한 바와 같이, 식각저지층(12) 패턴 구조는 적절히 조절될 필요가 있다. 바람직한 형태를 예로 들면, 상기 식각저지층(12) 패턴의 직경(d)은 100 ~ 500㎚이며, 그 주기(s)는 200 ~ 5000㎚이다. 이와 같이, 본 실시 형태에서 제안된 요철 구조 형성 공정은 식각저지층 패턴의 크기와 간격을 적절하게 배치함으로써 원하는 요철 형상을 정교하게 제어할 수 있으며, 나아가, n형 질화물 반도체층의 결정 손상을 줄일 수 있다.In this case, as shown in FIG. 4, as the distance between the

n형 질화물 반도체층에 요철 구조를 형성한 후에는, 도 1g와 같이, 식각저지층을 제거한 후, 도 1h와 같이, n형 질화물 반도체층(13)의 요철 구조에 n형 전극(17)을 형성한다. 상기 n형 전극(17)은 APCVD, LPCVD, PECVD 등을 이용한 금속박막증착 등으로 형성될 수 있으며, Ni/Au 등으로 이루어진 물질이 채용될 수 있다. n형 전극까지 형성된 최종 소자의 구조는 도 2에 도시된 것과 같다. 한편, 실시 형태에 따라서는, 식각저지층을 제거하지 않고, 최종 소자에 포함되도록 할 수도 있을 것이다.After the uneven structure is formed in the n-type nitride semiconductor layer, the etch stop layer is removed as shown in FIG. 1G, and then the n-

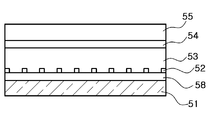

도 5 및 도 6은 도 1에 도시된 실시 형태에서 변형된 실시 형태에 따른 수직구조 반도체 발광소자의 제조방법을 설명하기 위한 단면도이다.5 and 6 are cross-sectional views illustrating a method of manufacturing a vertical structure semiconductor light emitting device according to an embodiment modified from the embodiment shown in FIG. 1.

우선, 도 5에 도시된 실시 형태의 경우는 식각저지층(52)을 형성하기 전에, 사파이어 기판(51) 상면에 언도프 질화물 반도체층(58)을 성장시킨다. 상기 언도프 질화물 반도체층(58)은 그 위에 순차적으로 성장되는 n형 질화물 반도체층(53), 활 성층(54), p형 질화물 반도체층(55)의 결정 품질을 향상시키는 버퍼층으로 기능할 수 있으며, 요철 구조 형성을 위한 식각 공정에서는 제거된다. First, in the embodiment shown in FIG. 5, the undoped

다음으로, 도 6에 도시된 실시 형태는, 도전성 기판(66)을 형성하는 단계이전에, p형 질화물 반도체층(65) 상에 반사금속층(69)을 형성하는 단계를 더 포함한다. 반사금속층(69)은 수직구조의 발광소자에서, 활성층(64)으로부터 방출된 빛을 n형 질화물 반도체층(63) 및 n형 전극(67) 방향으로 반사하는 기능과 p형 질화물 반도체층(65)과의 오믹 콘택 기능을 할 수 있다. 이러한 반사금속층(69)의 반사와 오믹콘택 기능을 고려하였을 때, 상기 반사금속층(69)은 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au 등의 물질을 포함하여 이루어질 수 있다. 한편, 상기 반사금속층(69)은 통상적인 금속층 형성방법인 증착법 또는 스퍼터링(sputtering) 공정에 의해 형성될 수 있다. 다만, 상기 반사금속층(69)은 광추출효율을 보다 향상시키기 위해 채용되는 것으로서 본 발명에서 필수적인 요소는 아니므로, 다른 실시 형태에서는 채용되지 않을 수 있다.Next, the embodiment shown in FIG. 6 further includes forming the

본 발명은 상술한 실시 형태 및 첨부된 도면에 의해 한정되는 것이 아니며, 첨부된 청구범위에 의해 한정하고자 한다. 따라서, 청구범위에 기재된 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 당 기술분야의 통상의 지식을 가진 자에 의해 다양한 형태의 치환, 변형 및 변경이 가능할 것이며, 이 또한 본 발명의 범위에 속한다고 할 것이다.The present invention is not limited by the above-described embodiment and the accompanying drawings, but is intended to be limited by the appended claims. Accordingly, various forms of substitution, modification, and alteration may be made by those skilled in the art without departing from the technical spirit of the present invention described in the claims, which are also within the scope of the present invention. something to do.

도 1a 내지 도 1h는 본 발명의 일 실시 형태에 따른 수직구조 반도체 발광소자의 제조 방법을 설명하기 위한 공정별 단면도이다.1A to 1H are cross-sectional views illustrating processes for manufacturing a vertical structure semiconductor light emitting device according to one embodiment of the present invention.

도 2는 사파이어 기판 상에 형성된 식각저지층을 위에서 바라본 평면도이며, 도 3은 n형 질화물 반도체층이 식각되어 요철 구조가 생기는 모습을 나타내는 평면도이며, 도 4는 식각저지층의 패턴 간 거리에 따른 요철 구조의 변화를 나타내는 단면도이다. FIG. 2 is a plan view from above of an etch stop layer formed on a sapphire substrate, and FIG. 3 is a plan view showing an uneven structure formed by etching an n-type nitride semiconductor layer, and FIG. It is sectional drawing which shows the change of uneven structure.

도 5 및 도 6은 도 1에 도시된 실시 형태에서 변형된 실시 형태에 따른 수직구조 반도체 발광소자의 제조방법을 설명하기 위한 단면도이다.5 and 6 are cross-sectional views illustrating a method of manufacturing a vertical structure semiconductor light emitting device according to an embodiment modified from the embodiment shown in FIG. 1.

<도면의 주요부분에 대한 부호의 설명><Description of the symbols for the main parts of the drawings>

11: 사파이어 기판 12: 식각저지층11: sapphire substrate 12: etch stop layer

13: n형 질화물 반도체층 14: 활성층13: n-type nitride semiconductor layer 14: active layer

15: p형 질화물 반도체층 16: 도전성 기판15: p-type nitride semiconductor layer 16: conductive substrate

17: n형 전극 58: 언도프 질화물 반도체층17: n-type electrode 58: undoped nitride semiconductor layer

69: 반사금속층69: reflective metal layer

Claims (15)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020080011776A KR100930187B1 (en) | 2008-02-05 | 2008-02-05 | Vertical structure semiconductor light emitting device manufacturing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020080011776A KR100930187B1 (en) | 2008-02-05 | 2008-02-05 | Vertical structure semiconductor light emitting device manufacturing method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20090085877A true KR20090085877A (en) | 2009-08-10 |

| KR100930187B1 KR100930187B1 (en) | 2009-12-07 |

Family

ID=41205694

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020080011776A Expired - Fee Related KR100930187B1 (en) | 2008-02-05 | 2008-02-05 | Vertical structure semiconductor light emitting device manufacturing method |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100930187B1 (en) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8698125B2 (en) | 2009-11-02 | 2014-04-15 | Lg Innotek Co., Ltd. | Light emitting device including second conductive type semiconductor layer and method of manufacturing the light emitting device |

| KR101436548B1 (en) * | 2013-05-28 | 2014-10-30 | 코닝정밀소재 주식회사 | Light extraction substrate, and method of fabricating light extraction substrate for oled |

| WO2015072751A1 (en) * | 2013-11-13 | 2015-05-21 | 코닝정밀소재 주식회사 | Light extraction substrate for organic light emitting element, method for manufacturing same, and organic light emitting element comprising same |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101692410B1 (en) | 2010-07-26 | 2017-01-03 | 삼성전자 주식회사 | Light emitting device and method of manufacturing the same |

| KR101229063B1 (en) * | 2011-01-21 | 2013-02-04 | 포항공과대학교 산학협력단 | Method of manufacturing light emitting diode and light emitting diode manufacured by the method |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100730537B1 (en) * | 2004-06-25 | 2007-06-20 | 학교법인 성균관대학 | Light emitting diode with vertical structure and method manufacturing for the same |

| JP2006049855A (en) | 2004-06-28 | 2006-02-16 | Matsushita Electric Ind Co Ltd | Semiconductor light emitting device and manufacturing method thereof |

| KR100638730B1 (en) * | 2005-04-14 | 2006-10-30 | 삼성전기주식회사 | Manufacturing method of vertical group III nitride light emitting device |

-

2008

- 2008-02-05 KR KR1020080011776A patent/KR100930187B1/en not_active Expired - Fee Related

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8698125B2 (en) | 2009-11-02 | 2014-04-15 | Lg Innotek Co., Ltd. | Light emitting device including second conductive type semiconductor layer and method of manufacturing the light emitting device |

| KR101436548B1 (en) * | 2013-05-28 | 2014-10-30 | 코닝정밀소재 주식회사 | Light extraction substrate, and method of fabricating light extraction substrate for oled |

| WO2015072751A1 (en) * | 2013-11-13 | 2015-05-21 | 코닝정밀소재 주식회사 | Light extraction substrate for organic light emitting element, method for manufacturing same, and organic light emitting element comprising same |

| US10454071B2 (en) | 2013-11-13 | 2019-10-22 | Corning Precision Materials Co., Ltd. | Light extraction substrate for organic light emitting element, method for manufacturing same, and organic light emitting element comprising same |

Also Published As

| Publication number | Publication date |

|---|---|

| KR100930187B1 (en) | 2009-12-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101341374B1 (en) | Photonic crystal light emitting device and manufacturing method of the same | |

| US8791483B2 (en) | High efficiency light emitting diode and method for fabricating the same | |

| US20140246647A1 (en) | Nanostructure light emitting device and method of manufacturing the same | |

| KR100638732B1 (en) | Manufacturing method of vertical structure nitride semiconductor light emitting device | |

| CN103794686B (en) | Light emitting semiconductor device and its manufacturing method | |

| KR20090027329A (en) | Vertical structure semiconductor light emitting device and its manufacturing method | |

| KR100982988B1 (en) | Vertical structure semiconductor light emitting device and its manufacturing method | |

| KR100930187B1 (en) | Vertical structure semiconductor light emitting device manufacturing method | |

| KR100887111B1 (en) | Vertical structure semiconductor light emitting device manufacturing method | |

| KR20090076163A (en) | Nitride semiconductor light emitting device manufacturing method and nitride semiconductor light emitting device manufactured thereby | |

| JP5165668B2 (en) | Semiconductor light emitting device and manufacturing method thereof | |

| US8735923B2 (en) | Semiconductor light emitting device and manufacturing method thereof | |

| KR20110085726A (en) | Semiconductor light emitting device and method for manufacturing same | |

| CN111697114B (en) | A vertical structure LED chip and preparation method thereof | |

| KR20110132161A (en) | Semiconductor light emitting device and manufacturing method thereof | |

| KR100982983B1 (en) | Vertical semiconductor light emitting device and manufacturing method of the same | |

| KR20110093006A (en) | Nitride semiconductor light emitting device | |

| KR101068864B1 (en) | Semiconductor light emitting device and manufacturing method thereof | |

| KR20110121176A (en) | Semiconductor light emitting device and manufacturing method thereof | |

| KR100826395B1 (en) | Vertical structure nitride semiconductor light emitting device manufacturing method | |

| KR20120010351A (en) | Manufacturing method of semiconductor light emitting device | |

| KR100856267B1 (en) | Vertical structure nitride semiconductor light emitting device and manufacturing method | |

| KR20100054594A (en) | Nitride semiconductor light emitting device and manufacturing method of the same | |

| KR101181018B1 (en) | Light emitting device with periodic deflector embedded structure and fabrication method thereof | |

| KR20110085727A (en) | Semiconductor light emitting device and method for manufacturing same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| FPAY | Annual fee payment |

Payment date: 20121031 Year of fee payment: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20131031 Year of fee payment: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20141128 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20141128 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |