KR101311527B1 - 영상처리장치 및 영상처리방법 - Google Patents

영상처리장치 및 영상처리방법 Download PDFInfo

- Publication number

- KR101311527B1 KR101311527B1 KR1020120020035A KR20120020035A KR101311527B1 KR 101311527 B1 KR101311527 B1 KR 101311527B1 KR 1020120020035 A KR1020120020035 A KR 1020120020035A KR 20120020035 A KR20120020035 A KR 20120020035A KR 101311527 B1 KR101311527 B1 KR 101311527B1

- Authority

- KR

- South Korea

- Prior art keywords

- transform

- blocks

- quantization

- unit

- block

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/12—Selection from among a plurality of transforms or standards, e.g. selection between discrete cosine transform [DCT] and sub-band transform or selection between H.263 and H.264

- H04N19/122—Selection of transform size, e.g. 8x8 or 2x4x8 DCT; Selection of sub-band transforms of varying structure or type

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/102—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the element, parameter or selection affected or controlled by the adaptive coding

- H04N19/124—Quantisation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/10—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding

- H04N19/169—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding

- H04N19/17—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being an image region, e.g. an object

- H04N19/176—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using adaptive coding characterised by the coding unit, i.e. the structural portion or semantic portion of the video signal being the object or the subject of the adaptive coding the unit being an image region, e.g. an object the region being a block, e.g. a macroblock

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Discrete Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

Abstract

Description

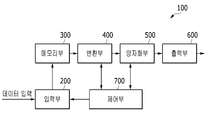

도 2는 본 발명의 한 실시예에 따른 영상처리장치의 상세 블록도이다.

도 3은 본 발명의 다른 실시예에 따른 영상처리장치의 상세 블록도이다.

도 4는 본 발명의 한 실시예에 따른 변환 변환 기저 벡터를 설명하는 도면이다.

도 5는 본 발명의 한 실시예에 따른 버터플라이 연산부를 설명하는 도면이다.

도 6은 본 발명의 한 실시예예에 따른 양자화처리에 관계된 블록도이다.

도 7은 본 발명의 한 실시예에 따른 변환 및 양자화에 관계된 타이밍도이다.

도 8은 본 발명의 한 실시예에 따른 영상처리방법의 흐름도이다.

| HEVC High Efficiency | HEVC Low Complexity |

| Prediction uints ( N= 4, 8, 16, 32, shapes : 2Nx2N, NxN for smallest) | |

| Transforms can cross prediction unit boundaries for intra; not for inter | |

| TU tree Structure ( Max 3 Levels ) | TU Tree Structure (Max 2 Levels ) |

| Transform Block size of 4x4 to 32x32 Samples (always Square) | |

Claims (8)

- 변환 및 양자화 처리를 수행하는 영상처리장치로서,

복수의 변환블록을 포함하고, 상기 복수의 변환블록은 병렬로 구성되며, 각 변환블록은 입력받은 데이터를 변환하는 변환부, 그리고

상기 복수의 변환블록 각각에 대응하는 복수의 양자화블록을 포함하고, 각 양자화블록은 대응하는 변환블록으로부터 전달된 데이터를 양자화하는 양자화부

를 포함하고,

상기 복수의 변환블록과 상기 복수의 양자화블록 중에서, 변환유닛(transform unit)의 크기에 따라 일부 블록은 활성화되고 나머지 블록은 비활성화되는 영상처리장치. - 제1항에서,

상기 변환부에서 처리하는 변환유닛(transform unit)의 크기를 기초로 상기 복수의 변환블록과 상기 복수의 양자화블록 중 일정 개수를 활성화시키는 제어부

를 더 포함하는 영상처리장치. - 제1항에서,

듀얼 메모리로 구성되며, 데이터를 병렬로 출력하여 상기 복수의 변환블록으로 전달하는 메모리부

를 더 포함하는 영상처리장치. - 제1항에서,

상기 변환부는

일부 정보가 반복되는 패턴으로 구성되어, 상기 일부 정보를 기초로 변환처리에 필요한 나머지 정보를 예측하도록 값이 설정된 변환 기저 벡터를 이용하는 영상처리장치. - 제1항에서,

상기 변환부는 부분 버터플라이 연산기를 이용하는 영상처리장치. - 영상처리장치가 변환 및 양자화 처리를 수행하는 방법으로서,

병렬로 구성된 복수의 변환블록 중에서 변환유닛(transform unit)의 크기를 기초로 변환처리에 이용할 제1 활성화 블록 그룹을 결정하는 단계,

상기 복수의 변환블록에 각각 대응하는 복수의 양자화블록 중에서, 상기 제1 활성화 블록에 대응하는 제2 활성화 블록 그룹을 결정하는 단계,

상기 제1 활성화 블록 그룹과 상기 제2 활성화 블록 그룹을 활성화하는 단계,

상기 제1 활성화 블록 그룹으로 데이터를 병렬로 입력하여 변환하는 단계, 그리고

상기 제1 활성화 블록 그룹의 출력 데이터를 대응하는 상기 제2 활성화 블록 그룹으로 각각 입력하여 양자화하는 단계

를 포함하는 영상처리방법. - 제6항에서,

상기 변환블록은

일부 정보가 반복되는 패턴으로 구성되어, 상기 일부 정보를 기초로 변환처리에 필요한 나머지 정보를 예측하도록 값이 설정된 변환 기저 벡터를 이용하여 변환하는 영상처리방법. - 제6항에서,

상기 변환블록은

부분 버터플라이 연산기를 이용하는 영상처리방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120020035A KR101311527B1 (ko) | 2012-02-28 | 2012-02-28 | 영상처리장치 및 영상처리방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120020035A KR101311527B1 (ko) | 2012-02-28 | 2012-02-28 | 영상처리장치 및 영상처리방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20130098480A KR20130098480A (ko) | 2013-09-05 |

| KR101311527B1 true KR101311527B1 (ko) | 2013-09-25 |

Family

ID=49450262

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020120020035A Expired - Fee Related KR101311527B1 (ko) | 2012-02-28 | 2012-02-28 | 영상처리장치 및 영상처리방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR101311527B1 (ko) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20040011359A (ko) * | 2002-07-30 | 2004-02-05 | 톰슨 라이센싱 소시에떼 아노님 | 디스플레이 디바이스 위에 디스플레이하기 위해 비디오데이터를 처리하는 방법 및 장치 |

| KR20050093819A (ko) * | 2003-01-10 | 2005-09-23 | 톰슨 라이센싱 소시에떼 아노님 | 디스플레이 디바이스 상에 디스플레이하기 위해 비디오데이터를 처리하기 위한 방법 및 디바이스 |

| KR20100105745A (ko) * | 2008-01-04 | 2010-09-29 | 돌비 인터네셔널 에이비 | 오디오 인코더 및 디코더 |

-

2012

- 2012-02-28 KR KR1020120020035A patent/KR101311527B1/ko not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20040011359A (ko) * | 2002-07-30 | 2004-02-05 | 톰슨 라이센싱 소시에떼 아노님 | 디스플레이 디바이스 위에 디스플레이하기 위해 비디오데이터를 처리하는 방법 및 장치 |

| KR20050093819A (ko) * | 2003-01-10 | 2005-09-23 | 톰슨 라이센싱 소시에떼 아노님 | 디스플레이 디바이스 상에 디스플레이하기 위해 비디오데이터를 처리하기 위한 방법 및 디바이스 |

| KR20100105745A (ko) * | 2008-01-04 | 2010-09-29 | 돌비 인터네셔널 에이비 | 오디오 인코더 및 디코더 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20130098480A (ko) | 2013-09-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12375735B2 (en) | Simplified context selection for entropy coding of transform coefficient syntax elements | |

| US11812041B2 (en) | Fast motion estimation for hierarchical coding structures | |

| US11558614B2 (en) | Transform and quantization architecture for video coding and decoding | |

| KR102622465B1 (ko) | 영상 코딩 시스템에서 인트라 예측에 따른 영상 디코딩 방법 및 장치 | |

| US20220060748A1 (en) | Luma-based chroma intra-prediction for video coding | |

| US20170195670A1 (en) | Virtual Boundary Processing Simplification for Adaptive Loop Filtering (ALF) in Video Coding | |

| EP2533539A2 (en) | Image encoding/decoding method for rate-distortion optimization and apparatus for performing same | |

| KR102801981B1 (ko) | Vvc에서의 컬러 변환을 위한 방법 및 장치 | |

| US11889088B2 (en) | Intra-prediction estimation using approximate reconstructed samples | |

| KR20150058324A (ko) | 차세대 비디오용 콘텐츠 적응적 엔트로피 코딩 | |

| JP7733083B2 (ja) | 予測ブロック生成装置、画像符号化装置、画像復号装置、及びプログラム | |

| Atapattu et al. | Real time all intra HEVC HD encoder on FPGA | |

| JP2022538968A (ja) | ビデオデータの変換スキップ残差符号化 | |

| KR20100079037A (ko) | 비디오 영상 부호화 방법 및 장치 | |

| JP7704475B2 (ja) | 符号化及び復号化方法並びに装置 | |

| JP2021500818A (ja) | 画像データ符号化及び復号化 | |

| KR20220138001A (ko) | 디코딩, 인코딩, 인코딩/디코딩 방법, 장치 및 그 기기 | |

| US10462461B2 (en) | Coding device and decoding device which allow encoding of non-square blocks | |

| WO2016194380A1 (ja) | 動画像符号化装置、動画像符号化方法および動画像符号化プログラムを記憶する記録媒体 | |

| Hamzaoglu et al. | An efficient H. 264 intra frame coder system | |

| KR101311527B1 (ko) | 영상처리장치 및 영상처리방법 | |

| Wang et al. | An effective TU size decision method for fast HEVC encoders | |

| Aparna | Efficient Architectures for Planar and DC modes of Intra Prediction in HEVC | |

| El Ansari et al. | An efficient VLSI architecture design for integer DCT in HEVC standard | |

| Do et al. | High throughput area-efficient SoC-based forward/inverse integer transforms for H. 264/AVC |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20161108 Year of fee payment: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| P14-X000 | Amendment of ip right document requested |

St.27 status event code: A-5-5-P10-P14-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20170918 Year of fee payment: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20180906 Year of fee payment: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| P14-X000 | Amendment of ip right document requested |

St.27 status event code: A-5-5-P10-P14-nap-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20191017 Year of fee payment: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20210917 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| K11-X000 | Ip right revival requested |

St.27 status event code: A-6-4-K10-K11-oth-X000 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20210917 |

|

| PR0401 | Registration of restoration |

St.27 status event code: A-6-4-K10-K13-oth-PR0401 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| R401 | Registration of restoration | ||

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 10 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 11 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 12 |