JP4057473B2 - 化合物半導体発光素子及びその製造方法 - Google Patents

化合物半導体発光素子及びその製造方法 Download PDFInfo

- Publication number

- JP4057473B2 JP4057473B2 JP2003167906A JP2003167906A JP4057473B2 JP 4057473 B2 JP4057473 B2 JP 4057473B2 JP 2003167906 A JP2003167906 A JP 2003167906A JP 2003167906 A JP2003167906 A JP 2003167906A JP 4057473 B2 JP4057473 B2 JP 4057473B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- type

- light emitting

- cladding layer

- thickness

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

- Led Devices (AREA)

Description

【発明の属する技術分野】

本発明は、青色領域で発光可能な半導体レーザおよび発光ダイオードの実現が可能な化合物半導体発光素子およびその製造方法に関する。

【0002】

【従来の技術】

従来、V族元素を窒素(N)とするIII−V族化合物半導体はエネルギーギャップが広いことから可視および紫外域の発光材料として注目されている。そのうち、AlGaN系材料を用いて、青色領域で発光可能な半導体レーザおよび発光ダイオード等の発光素子が検討されている。

【0003】

図3に、従来のAlGaN系半導体レーザ[または発光ダイオード]の断面模式図を示す。なお、[]内は発光ダイオードの場合である。

【0004】

この素子は、サファイア基板101上に、薄層のGaNまたはAlNからなるバッファ層102が形成され、その上に、n型GaN層103、n型AlGaN下部クラッド層104、ノンドープAlGaInN系活性層[ZnをドープしたAlGaInN系発光層]105、p型AlGaN上部クラッド層107、p型GaNキャップ層108が積層形成されている。

【0005】

p型GaNキャップ層108の上にはp型電極90が形成されている。また、n型GaN層103の上部が一部露出するように、その上側のn型下部クラッド層104、活性層[または発光層]105、p型上部クラッド層107およびp型キャップ層108は部分的に除去され、露出したn型GaN層103の部分の上にn型電極100が形成されている。

【0006】

この半導体レーザ[または発光ダイオード]の製造は、以下のようにして行われる。

【0007】

まず、有機金属気相成長法(MOCVD法)により、サファイア基板101を約1050℃で表面処理し、次に、基板温度を約500℃に下げて薄層のGaNまたはAlNからなるバッファ層102を成長させる。

【0008】

次に、基板温度を約1020℃に上げてn型GaN層103を形成し、引き続いてn型AlGaN下部クラッド層104を約1μm成長させる。

【0009】

続いて、基板温度を約800℃に下げてノンドープAlGaInN活性層[またはZnドープ発光層]105を約100オングストローム〜500オングストローム成長させる。

【0010】

その後、基板温度を約1020℃に上げてp型AlGaN上部クラッド層107を約1μm成長させ、引き続いてp型GaNキャップ層108を成長させる。

【0011】

【発明が解決しようとする課題】

上記従来の半導体レーザ[または発光ダイオード]において、光を活性層およびクラッド層に有効に閉じ込め、注入電流を活性層に有効に閉じ込めるためには、上部クラッド層107および下部クラッド層104の層厚は約1μm程度必要である。

【0012】

しかし、従来の半導体レーザ[または発光ダイオード]の素子構造および作製方法では、図4および図5に示すように、AlGaN下部クラッド層104を約1μm程度成長させた場合、表面にクラック109が発生し、良質なクラッド層を得ることが困難であった。

【0013】

本発明は、このような従来技術の課題を解決するためになされたものであり、表面状態が良好でクラックの無い良質なクラッド層が得られ、電気特性および光学特性が良好な半導体レーザおよび発光ダイオードの実現が可能な化合物半導体発光素子およびその製造方法を提供することを目的とする。

【0014】

【課題を解決するための手段】

本発明の化合物半導体発光素子は、基板上に、少なくとも下部クラッド層と、活性層または発光層と、上部クラッド層とが基板側からこの順に形成され、該下部クラッド層中および上部クラッド層中に、緩衝層が単層または複数層形成されており、そのことにより上記目的が達成される。

【0015】

前記緩衝層はAlxGa1-xN(0≦x≦1)からなり、前記下部クラッド層および上部クラッド層を構成するクラッド層はAlyGa1-yN(0<y<1)からなり、前記活性層または発光層はAlwGazIn1-w-zN(0≦w≦1、0≦z≦1からなるものを用いることができる。

【0016】

本発明の化合物半導体発光素子の製造方法は、基板上に、少なくとも下部クラッド層と、活性層または発光層と、上部クラッド層とがこの順に形成された化合物半導体発光素子の製造方法において、該下部クラッド層中および上部クラッド層中に、クラッド層の成長温度よりも低い成長温度で、GaNからなる緩衝層を単層または複数層成長させており、そのことにより上記目的が達成される。

【0017】

本発明の化合物半導体発光素子の製造方法は、基板上に、少なくとも下部クラッド層と、活性層または発光層と、上部クラッド層とがこの順に形成された化合物半導体発光素子の製造方法において、該下部クラッド層中および上部クラッド層中に、クラッド層の成長温度と同じ温度またはクラッド層の成長温度よりも高い成長温度で、AlNまたはAlxGa1-xN(0<x<1)からなる緩衝層を単層または複数層成長させており、そのことにより上記目的が達成される。

【0018】

以下に本発明の作用につき説明する。

本発明にあっては、下部クラッド層中および上部クラッド層中に、緩衝層が単層または複数層形成されている。クラッド層/緩衝層を繰り返して成長することにより、表面モフォロジーが良好でクラックの無い良質な上部クラッド層および下部クラッド層を所望の厚みに成長できる。

【0019】

例えば、AlyGa1-yN(0<y<1)クラッド層とAlxGa1-xN(0≦x≦1)緩衝層を繰り返して成長することにより、下部クラッド層および上部クラッド層の厚みを約1μm程度にすることが可能である。

【0020】

このように良質で厚膜の上部クラッド層および下部クラッド層を用い、AlwGazIn1-w-zN(0≦w≦1、0≦z≦1を活性層または発光層として、AlGaInN系半導体レーザ素子および発光ダイオードが実現可能である。

【0021】

GaNからなる緩衝層は、AlGaNクラッド層の成長温度またはクラッド層の成長温度よりも高い成長温度で成長させてもよいが、クラッド層の成長温度よりも低い成長温度で成長させると緩衝層の蒸発による影響がなく、より良好なクラッド層が得られる。

【0022】

AlNまたはAlxGa1-xN(0<x<1)からなる緩衝層は、AlGaNクラッド層の成長温度よりも低い成長温度で成長させてもよいが、緩衝層の蒸発を考慮する必要が無いのでクラッド層の成長温度と同じ温度またはクラッド層の成長温度よりも高い成長温度で成長させることができ、製造が容易である。

【0023】

【発明の実施の形態】

以下、本発明の実施形態について図面を参照しながら説明する。尚、以下の図において、同一の機能を有する部分は同一の番号で示している。

【0024】

(実施形態1)

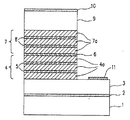

図1は、本発明の一実施形態であるAlGaN/InGaN/AlGaN系半導体レーザ[または発光ダイオード]を示す断面図である。

【0025】

この素子は、サファイア基板1上に、薄層のGaNまたはAlNからなるバッファ層2が形成され、その上に、n型GaN層3、n型下部クラッド層4、ノンドープまたはSiドープAlwGazIn1-w-zN(0≦w≦1、0≦z≦1)活性層[または発光層]6、p型上部クラッド層7およびp型GaNキャップ層9が積層形成されている。

【0026】

n型下部クラッド層4中には、n型AlyGa1-yN(0<y<1)クラッド層4aと薄層のn型AlxGa1-xN(0≦x≦1)緩衝層5とが交互に積層形成され、下部クラッド層4の厚みは約1μm程度にされている。また、p型上部クラッド層7中には、p型AlyGa1-yN(0<y<1)クラッド層7aと薄層のp型AlxGa1-xN(0≦x≦1)緩衝層8とが交互に積層形成されて、上部クラッド層7の厚みは約1μm程度にされている。

【0027】

p型キャップ層9の上にはp型電極10が形成されている。また、n型GaN層3の上部が一部露出するように、その上側のn型下部クラッド層4、活性層[または発光層]6、p型上部クラッド層7、p型緩衝層8およびp型キャップ層9は部分的に除去され、露出したn型GaN層3の部分の上にn型電極11が形成されている。

【0028】

この実施形態1では、厚み約0.15〜0.3μmのn型Al0.1Ga0.9Nクラッド層4aと厚み約200オングストロームのn型GaN緩衝層5とを繰り返し成長して約1μmとしている。また、厚み約0.15〜0.3μmのp型Al0.1Ga0.9Nクラッド層7aと厚み約200オングストロームのp型GaN緩衝層8とを繰り返し成長して下部クラッド層4および上部クラッド層7の厚みを約1μmとしている。また、活性層[または発光層]6としては、厚み約200オングストロームのノンドープまたはSiドープGa0.2In0.8N層を形成している。

【0029】

この半導体レーザ[または発光ダイオード]の製造は、以下のようにして行われる。

【0030】

各半導体層の成長はMOCVD法により行い、基板としてサファイア(0001)C面を用いる。III族ガス源としてはトリメチルガリウム(TMG)、トリメチルアルミニウム(TMA)、トリメチルインジウム(TMI)を用い、V族ガス源としてはアンモニア(NH3)を用いる。n型ドーパント源としてはモノシラン(SiH4)を用い、p型ドーパント源としてはビスシクロペンタディエニルマグネシウム(Cp2Mg)を用いる。また、キャリアガスとしてはH2を用いる。

【0031】

まず、MOCVD装置内にサファイア基板1を導入して、H2中で基板温度約1050℃で基板を熱することにより、基板の表面処理を行う。次に、基板温度を約500℃に下げてGaNまたはAlNからなるバッファ層2を成長させる。GaNからなるバッファ層の厚みは250オングストローム、AlNからなるバッファ層の厚みは500オングストロームとする。

【0032】

次に、基板温度を約1020℃に上げてn型GaN層3を厚み約4μm成長させる。

【0033】

続いて、同じ基板温度でn型Al0.1Ga0.9Nクラッド層4aを約0.15μm〜0.3μm成長させ、その後、基板温度を約500℃に下げてn型GaN緩衝層5を約200オングストローム成長させる。さらに、上記n型クラッド層4a/n型緩衝層5の成長を繰り返して、下部クラッド層4の厚みを約1μmとする。

【0034】

次に、基板温度を約800℃にしてノンドープまたはSiドープIn0.2Ga0.8N活性層[または発光層]6を厚み約200オングストローム成長させる。

【0035】

続いて、基板温度を約1020℃に上げてp型Al0.1Ga0.9Nクラッド層7aを約0.15μm〜0.3μm成長させ、その後、基板温度を約500℃に下げてp型GaN緩衝層8を約200オングストローム成長させる。さらに、上記p型クラッド層7a/p型緩衝層8の成長を繰り返して、上部クラッド層7の厚みを約1μmにする。

【0036】

引き続いて、p型GaNキャップ層9を厚み約1μm成長させる。

成長後のウェハーに対して約700℃、N2雰囲気中で熱アニーリングを行うことにより、p型緩衝層8、p型クラッド層7aおよびp型キャップ層9を高濃度のp型層に変化させる。

【0037】

その後、n型電極11形成のためにn型GaN層3が露出するまでエッチングを行い、これにより露出されたn型GaN層3上にn型電流11を形成し、p型キャップ層9の上にp型電流10を形成する。

【0038】

なお、GaN緩衝層の成長は、約1000℃または約1200℃等、クラッド層と同じかまたは高い成長温度で行ってもよいが、GaN緩衝層の蒸発を考慮すれば、約500℃程度のクラッド層よりも低い成長温度で行うのが好ましい。

【0039】

この実施形態1においては、AlGaNクラッド層の間にGaN緩衝層が形成されているので、表面状態が良好でクラックの無い良質なAlGaNクラッド層の結晶成長が可能であった。このように良質で厚膜のクラッド層が得られるので、量産性に優れ、電気特性および光学特性が良好なAlGaInN系半導体レーザおよび発光ダイオードの実現が可能となる。

【0040】

(実施形態2)

この実施形態2では、厚み約0.15〜0.3μmのn型Al0.3Ga0.7Nクラッド層4aと厚み約200オングストロームのn型GaN緩衝層5とを繰り返し成長して下部クラッド層4の厚みを約1μmとし、厚み約0.15〜0.3μmのp型Al0.3Ga0.7NNクラッド層7aと厚み約200オングストロームのp型GaN緩衝層8とを繰り返し成長して上部クラッド層7の厚みを約1μmとしている。また、活性層[または発光層]6としては、実施形態1と同様に、厚み約200オングストロームのノンドープまたはSiドープGa0.2In0.8N層を形成している。その他の構造は、実施形態1と同様である。

【0041】

この半導体レーザ[または発光ダイオード]の製造は、以下のようにして行われる。

【0042】

各半導体層の成長は実施形態1と同様にMOCVD法により行い、基板としてサファイア(0001)C面を用いる。III族ガス源、V族ガス源、n型ドーパント源、p型ドーパント源およびキャリアガスとしては実施形態1と同様のものを用いる。

【0043】

まず、実施形態1と同様にして、サファイア基板1上にバッファ層2およびn型GaN層3を成長させる。

【0044】

続いて、n型GaN層3と同じ約1020℃の基板温度でn型Al0.3Ga0.7Nクラッド層4aを約0.15μm〜0.3μm成長させ、その後、基板温度を約500℃に下げてn型GaN緩衝層5を約200オングストローム成長させる。さらに、上記n型クラッド層4a/n型緩衝層5の成長を繰り返して、下部クラッド層4の厚みを約1μmにする。

【0045】

次に、実施形態1と同様にして活性層[または発光層]6を成長させる。

続いて、基板温度を約1020℃に上げてp型Al0.3Ga0.7Nクラッド層7aを約0.15μm〜0.3μm成長させ、その後、基板温度を約500℃に下げてp型GaN緩衝層8を約200オングストローム成長させる。さらに、上記p型クラッド層7a/p型緩衝層8の成長を繰り返して、上部クラッド層7の厚みを約1μmとする。

【0046】

引き続いて、実施形態1と同様にしてp型キャップ層9を成長させ、p型緩衝層8、p型クラッド層7a、p型キャップ層9を高濃度のp型層に変化させる。その後、実施形態1と同様にしてp型電極10およびn型電極11を形成する。

【0047】

なお、GaN緩衝層の成長は、約1000℃または約1200℃等、クラッド層と同じかまたは高い成長温度で行ってもよいが、GaN緩衝層の蒸発を考慮すれば、約500℃程度のクラッド層よりも低い成長温度で行うのが好ましい。

【0048】

この実施形態2においても、AlGaNクラッド層の間にGaN緩衝層が形成されているので、表面状態が良好でクラックの無い良質なAlGaNクラッド層の結晶成長が可能であった。このように良質で厚膜のクラッド層が得られるので、量産性に優れ、電気特性および光学特性が良好なAlGaInN系半導体レーザおよび発光ダイオードの実現が可能となる。

【0049】

(実施形態3)

この実施形態3では、厚み約0.15〜0.3μmのn型Al0.1Ga0.9Nクラッド層4aと厚み約200オングストロームのn型AlN緩衝層5とを繰り返し成長して下部クラッド層4の厚みを約1μmとし、厚み約0.15〜0.3μmのp型Al0.1Ga0.9Nクラッド層7aと厚み約200オングストロームのp型AlN緩衝層8とを繰り返し成長して上部クラッド層7の厚みを約1μmとしている。また、活性層[または発光層]6としては、実施形態1と同様に、厚み約200オングストロームのノンドープまたはSiドープGa0.2In0.8N層を形成している。その他の構造は、実施形態1と同様である。

【0050】

この半導体レーザ[または発光ダイオード]の製造は、以下のようにして行われる。

【0051】

各半導体層の成長は実施形態1と同様にMOCVD法により行い、基板としてサファイア(0001)C面を用いる。III族ガス源、V族ガス源、n型ドーパント源、p型ドーパント源およびキャリアガスとしては実施形態1と同様のものを用いる。

【0052】

まず、実施形態1と同様にして、サファイア基板1上にバッファ層2およびn型GaN層3を成長させる。

【0053】

続いて、n型GaN層3と同じ約1020℃の基板温度でn型Al0.1Ga0.9Nクラッド層4aを約0.15μm〜0.3μm成長させ、その後、基板温度を約1000℃または約1200℃にしてn型AlN緩衝層5を約200オングストローム成長させる。さらに、上記n型クラッド層4a/n型緩衝層5の成長を繰り返して、下部クラッド層4の厚みを約1μmにする。

【0054】

次に、実施形態1と同様にして活性層[または発光層]6を成長させる。

続いて、基板温度を約1020℃に上げてp型Al0.1Ga0.9Nクラッド層7aを約0.15μm〜0.3μm成長させ、その後、基板温度を約500℃に下げてp型AlN緩衝層8を約200オングストローム成長させる。さらに、上記p型クラッド層7a/p型緩衝層8の成長を繰り返して、上部クラッド層7の厚みを約1μmにする。

【0055】

引き続いて、実施形態1と同様にしてp型キャップ層9を成長させ、p型緩衝層8、p型上部クラッド層7、p型キャップ層9を高濃度のp型層に変化させる。

【0056】

その後、実施形態1と同様にしてp型電極10およびn型電極11を形成する。

【0057】

なお、AlN緩衝層の成長温度は、約500℃程度の低温でもよいが、AlN緩衝層はその蒸発を考慮しなくてよく、約1000℃または約1200℃等の高温の方が好ましい。また、成長中に温度を下げることなく成長を行い得るため製造が容易になる。

【0058】

この実施形態3においては、AlGaNクラッド層の間にAlN緩衝層が形成されているので、表面状態が良好でクラックの無い良質なAlGaNクラッド層の結晶成長が可能であった。このように良質で厚膜のクラッド層が得られるので、量産性に優れ、電気特性および光学特性が良好なAlGaInN系半導体レーザおよび発光ダイオードの実現が可能となる。

【0059】

(実施形態4)

この実施形態4では、厚み約0.15〜0.3μmのn型Al0.3Ga0.7Nクラッド層4aと厚み約200オングストロームのn型Al0.05Ga0.95N緩衝層5とを繰り返し成長して下部クラッド層4の厚みを約1μmとし、厚み約0.15〜0.3μmのp型Al0.3Ga0.7Nクラッド層7aと厚み約200オングストロームのp型Al0.05Ga0.95N緩衝層8とを繰り返し成長して上部クラッド層7aの厚みを約1μmとしている。また、活性層[または発光層]6としては、実施形態1と同様に、厚み約200オングストロームのノンドープまたはSiドープGa0.2In0.8N層を形成している。その他の構造は、実施形態1と同様である。

【0060】

この半導体レーザ[または発光ダイオード]の製造は、以下のようにして行われる。

【0061】

各半導体層の成長は実施形態1と同様にMOCVD法により行い、基板としてサファイア(0001)C面を用いる。III族ガス源、V族ガス源、n型ドーパント源、p型ドーパント源およびキャリアガスとしては実施形態1と同様のものを用いる。

【0062】

まず、実施形態1と同様にして、サファイア基板1上にバッファ層2およびn型GaN層3を成長させる。

【0063】

続いて、n型GaN層3と同じ約1020℃の基板温度でn型Al0.3Ga0.7Nクラッド層4aを約0.15μm〜0.3μm成長させ、その後、基板温度を約1000℃または約1200℃にしてn型Al0.05Ga0.95N緩衝層5を約200オングストローム成長させる。さらに、上記n型クラッド層4a/n型緩衝層5の成長を繰り返して、下部クラッド層4の厚みを約1μmにする。

【0064】

次に、実施形態1と同様にして活性層[または発光層]6を成長させる。

続いて、基板温度を約1020℃に上げてp型Al0.3Ga0.7Nクラッド層7aを約0.15μm〜0.3μm成長させ、その後、基板温度を約1000℃または約1200℃にしてp型Al0.05Ga0.95N緩衝層8を約200オングストローム成長させる。さらに、上記p型クラッド層7a/p型緩衝層8の成長を繰り返して、上部クラッド層7の厚みを約1μmにする。

【0065】

引き続いて、実施形態1と同様にしてp型キャップ層9を成長させ、p型緩衝層8、p型クラッド層7a、p型キャップ層9を高濃度のp型層に変化させる。その後、実施形態1と同様にしてp型電極10およびn型電極11を形成する。

【0066】

なお、AlN緩衝層の成長温度は、約500℃程度の低温でもよいが、AlN緩衝層はその蒸発を考慮しなくてよく、約1000℃または約1200℃等の高温の方が好ましい。また、成長中に温度を下げることなく成長を行い得るため製造が容易になる。

【0067】

この実施形態4においては、AlGaNクラッド層の間にAlGaN緩衝層が形成されているので、表面状態が良好でクラックの無い良質なAlGaNクラッド層の結晶成長が可能であった。このように良質で厚膜のクラッド層が得られるので、量産性に優れ、電気特性および光学特性が良好なAlGaInN系半導体レーザおよび発光ダイオードの実現が可能となる。

【0068】

(実施形態5)

図2は、本発明の他の実施形態であるAlGaN/InGaN/AlGaN系半導体レーザ[または発光ダイオード]を示す断面図である。

【0069】

この素子は、サファイア基板1上に、薄層のGaNまたはAlNからなるバッファ層2が形成され、その上に、n型GaN層3、n型下部クラッド層4、ノンドープまたはSiドープAlwGazIn1-w-zN(0≦w≦1、0≦z≦1)活性層[または発光層]6、p型上部クラッド層7およびp型GaNキャップ層9が積層形成されている。

【0070】

n型下部クラッド層4中には、n型AlyGa1-yN(0<y<1)クラッド層4aと薄層のn型AlxGa1-xN(0≦x≦1)緩衝層5が積層形成され、p型上部クラッド層7中には、p型AlyGa1-yN(0<y<1)クラッド層7aと薄層のp型AlxGa1-xN(0≦x≦1)緩衝層8が積層形成されて、下部クラッド層4および上部クラッド層7の厚みが約1μm程度にされている。

【0071】

p型キャップ層9の上にはp型電極10が形成されている。また、n型下部クラッド層4、活性層[または発光層]6、p型上部クラッド層7、p型緩衝層8およびp型キャップ層9は、n型GaN層3が一部露出するように部分的に除去され、そのn型GaN3の露出部上にn型電極11が形成されている。

【0072】

この実施形態5では、下部クラッド層4は、厚み約0.3μmのn型Al0.1Ga0.9Nクラッド層4a、厚み約200オングストロームのn型GaN緩衝層5、厚み約0.25μmのn型Al0.1Ga0.9Nクラッド層4a、厚み約200オングストロームのn型GaN緩衝層5および厚み約0.15μmのn型Al0.1Ga0.9Nクラッド層4aを順次成長している。また、上部クラッド層7は、厚み約0.15μmのp型Al0.1Ga0.9Nクラッド層7a、厚み約200オングストロームのp型GaN緩衝層8、厚み約0.25μmのp型Al0.1Ga0.9Nクラッド層7a、厚み約200オングストロームのp型GaN緩衝層8および厚み約0.3μmのp型Al0.1Ga0.9Nクラッド層7aを順次成長している。さらに、活性層[または発光層]6としては、実施形態1と同様に、厚み約200オングストロームのノンドープまたはSiドープGa0.2In0.8N

層を形成している。その他の構造は、実施形態1と同様である。

【0073】

この半導体レーザ[または発光ダイオード]の製造は、以下のようにして行われる。

【0074】

各半導体層の成長は実施形態1と同様にMOCVD法により行い、基板としてサファイア(0001)C面を用いる。III族ガス源、V族ガス源、n型ドーパント源、p型ドーパント源およびキャリアガスとしては実施形態1と同様のものを用いる。

【0075】

まず、実施形態1と同様にして、サファイア基板1上にバッファ層2およびn型GaN層3を成長させる。

【0076】

続いて、n型GaN層3と同じ約1020℃の基板温度でn型Al0.3Ga0.7Nクラッド層4aを約0.3μm成長させ、その後、基板温度を約500℃に下げてn型GaN緩衝層5を約200オングストローム成長させる。次に、約1020℃の基板温度でn型Al0.3Ga0.7Nクラッド層4aを約0.25μm成長させ、その後、基板温度を約500℃に下げてn型GaN緩衝層5を約200オングストローム成長させる。さらに、約1020℃の基板温度でn型Al0.3Ga0.7Nクラッド層4aを約0.15μm成長させる。

【0077】

次に、実施形態1と同様にして活性層[または発光層]6を成長させる。

続いて、基板温度を約1020℃に上げてp型Al0.3Ga0.7Nクラッド層7aを約0.15μm成長させ、その後、基板温度を約500℃に下げてp型GaN緩衝層8を約200オングストローム成長させる。次に、約1020℃の基板温度でp型Al0.3Ga0.7Nクラッド層7aを約0.25μm成長させ、その後、基板温度を約500℃に下げてp型GaN緩衝層8を約200オングストローム成長らはる。さらに、約1020℃の基板温度でp型Al0.3Ga0.7Nクラッド層7aを約0.3μm成長させる。

【0078】

引き続いて、実施形態1と同様にしてp型キャップ層9を成長させ、p型緩衝層8、p型クラッド層7a、p型キャップ層9を高濃度のp型層に変化させる。その後、実施形態1と同様にしてp型電極10およびn型電極11を形成する。

【0079】

なお、GaN緩衝層の成長は、約1000℃または約1200℃等、クラッド層と同じかまたは高い成長温度で行ってもよいが、GaN緩衝層の蒸発を考慮すれば、約500℃程度のクラッド層よりも低い成長温度で行うのが好ましい。

【0080】

この実施形態5においては、AlGaNクラッド層の間にGaN緩衝層が形成されているので、表面状態が良好でクラックの無い良質なAlGaNクラッド層の結晶成長が可能であった。また、活性層[または発光層]に近付くにつれてAlGaNクラッド層を薄くしているので、クラッド層の結晶状態をさらに良好にすることができた。このように良質で厚膜なクラッド層が得られるので、量産性に優れ、電気特性および光学特性が良好なAlGaInN系半導体レーザおよび発光ダイオードの実現が可能となる。

【0081】

尚、本発明は上記実施形態に限定されるものではなく、成長条件、有機金属化合物ガスの種類、使用材料等は上記実施形態に示した以外のものを用いることができる。

【0082】

【発明の効果】

以上の説明から明らかなように、本発明によれば、下部クラッド層中および上部クラッド層中に、緩衝層を単層または複数層形成されており、クラッド層/緩衝層を繰り返して成長することにより、表面状態が良好でクラックの無い良質なクラッド層を所望の厚みに成長できる。

【0083】

AlyGa1-yN(0<y<1)クラッド層の場合、AlxGa1-xN(0≦x≦1)緩衝層とクラッド層とを繰り返して成長することにより、上部クラッド層および下部クラッド層を約1μm程度成長することが可能である。この上部クラッド層、下部クラッド層およびAlwGazIn1-w-zN(0≦w≦1、0≦z≦1活性層[または発光層]により、AlGaInN系半導体レーザ素子および発光ダイオードが実現可能である。

【0084】

このように良質で厚膜なクラッド層が得られるので、量産性に優れ、電気特性および光学特性が良好な半導体レーザおよび発光ダイオードの実現が可能となる。

【図面の簡単な説明】

【図1】本発明の一実施形態である半導体レーザ[または発光ダイオード]を示す断面模式図である。

【図2】本発明の他の実施形態である半導体レーザ[または発光ダイオード]を示す断面模式図である。

【図3】従来の半導体レーザ[または発光ダイオード]を示す断面模式図である。

【図4】従来の半導体レーザにおけるAlGaNクラッド層表面を示す平面模式図である。

【図5】従来の半導体レーザにおけるAlGaNクラッド層の作製工程を示す断面模式図である。

【符号の説明】

1 サファイア(0001)基板

2 GaNまたはAlNバッファ層

3 n型GaN層

4 下部クラッド層

4a n型AlyGa1-yN(0<y<1)クラッド層

5 薄層n型AlxGa1-xN(0≦x≦1)緩衝層

6 ノンドープまたはSiドープAlwGazIn1-w-zN(0≦w≦1、0≦z≦1)活性層または発光層

7 上部クラッド層

7a p型AlyGa1-yN(0<y<1)クラッド層

8 薄層p型AlxGa1-xN(0≦x≦1)緩衝層

9 p型GaNキャップ層

10 p型電極

11 n型電極

Claims (13)

- 基板と、この基板上に順次設けられた、少なくとも、下部クラッド層と、活性層または発光層と、上部クラッド層とを備える化合物半導体発光素子において、前記下部クラッド層はAlyGa1-yN(0<y<1)からなり、その中に、単層または複数層のAlxGa1-xN(0≦x≦1、x ≠ y)からなる緩衝層を含み、前記緩衝層により分割された前記下部クラッド層の各層の厚みより前記緩衝層の個々の厚みが薄いことを特徴とする化合物半導体発光素子。

- 前記基板と前記下部クラッド層との間にはGaNからなる層が存在することを特徴とする請求項1に記載の化合物半導体発光素子。

- 前記下部クラッド層と前記GaNからなる層とは互いに接していることを特徴とする請求項2に記載の化合物半導体発光素子。

- 前記基板と前記下部クラッド層との間にはGaNからなる層が存在し、前記緩衝層を含んだ前記下部クラッド層の厚みは1μm程度であることを特徴とする請求項1に記載の化合物半導体発光素子。

- 前記下部クラッド層と前記GaNからなる層とは互いに接していることを特徴とする請求項4に記載の化合物半導体発光素子。

- 基板と、この基板上に順次設けられた、少なくとも、下部クラッド層と、活性層または発光層と、上部クラッド層とを備える化合物半導体発光素子の下部クラッド層の形成方法において、AlyGa1-yN(0<y<1)からなる層と緩衝層としてのAlxGa1-xN(0≦x≦1、x ≠ y)からなる層とを交互に積層して前記下部クラッド層を形成するとともに、前記Al y Ga 1-y N(0<y<1)からなる層の厚みより前記Al x Ga 1-x N(0≦x≦1、 x ≠ y )からなる層の厚みを薄く形成する工程を具備することを特徴とする化合物半導体発光素子の下部クラッド層の形成方法。

- 前記基板と前記下部クラッド層との間にGaNからなる層を形成する工程を具備することを特徴とする請求項6に記載の化合物半導体発光素子の下部クラッド層の形成方法。

- 前記下部クラッド層と前記GaNからなる層とは互いに接して形成されることを特徴とする請求項7に記載の化合物半導体発光素子の下部クラッド層の形成方法。

- 前記緩衝層を含んだ前記下部クラッド層の厚みは1μm程度であることを特徴とする請求項6に記載の化合物半導体発光素子の下部クラッド層の形成方法。

- 前記緩衝層を含んだ前記下部クラッド層の厚みは1μm程度であることを特徴とする請求項7または8に記載の化合物半導体発光素子の下部クラッド層の形成方法。

- 前記緩衝層は、前記AlyGa1-yN(0<y<1)からなる層の形成温度と異なる温度で形成されることを特徴とする請求項6に記載の化合物半導体発光素子の下部クラッド層の形成方法。

- 前記下部クラッド層、前記活性層または発光層および前記上部クラッド層はMOCVD法により形成されることを特徴とする請求項8に記載の化合物半導体発光素子の下部クラッド層の形成方法。

- 前記緩衝層を含んだ前記下部クラッド層の厚みは1μm程度であることを特徴とする請求項12に記載の化合物半導体発光素子の下部クラッド層の形成方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003167906A JP4057473B2 (ja) | 2003-06-12 | 2003-06-12 | 化合物半導体発光素子及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003167906A JP4057473B2 (ja) | 2003-06-12 | 2003-06-12 | 化合物半導体発光素子及びその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001128662A Division JP3456980B2 (ja) | 2001-04-26 | 2001-04-26 | 化合物半導体層の形成方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007279842A Division JP2008047940A (ja) | 2007-10-29 | 2007-10-29 | 化合物半導体発光素子 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004006916A JP2004006916A (ja) | 2004-01-08 |

| JP4057473B2 true JP4057473B2 (ja) | 2008-03-05 |

Family

ID=30438291

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003167906A Expired - Lifetime JP4057473B2 (ja) | 2003-06-12 | 2003-06-12 | 化合物半導体発光素子及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4057473B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010027002A1 (ja) | 2008-09-05 | 2010-03-11 | 塩野義製薬株式会社 | Pi3k阻害活性を有する縮環モルホリン誘導体 |

-

2003

- 2003-06-12 JP JP2003167906A patent/JP4057473B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004006916A (ja) | 2004-01-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7687294B2 (en) | Nitride semiconductor device and method of manufacturing the same | |

| JP3728332B2 (ja) | 化合物半導体発光素子 | |

| EP2164115A1 (en) | Nitride semiconductor light emitting element and method for manufacturing nitride semiconductor | |

| JP3606015B2 (ja) | 3族窒化物半導体素子の製造方法 | |

| JP2002198314A (ja) | 窒化物半導体の製造方法、窒化物半導体素子の製造方法及びそれを用いた窒化物半導体素子 | |

| JP3269344B2 (ja) | 結晶成長方法および半導体発光素子 | |

| JP2007134507A (ja) | 半導体発光素子、および半導体発光素子を作製する方法 | |

| JP2006332258A (ja) | 窒化物半導体装置及びその製造方法 | |

| JP4743989B2 (ja) | 半導体素子およびその製造方法ならびに半導体基板の製造方法 | |

| JP6319975B2 (ja) | 窒化物半導体混晶の製造方法 | |

| JP2007201099A (ja) | 窒化物半導体発光素子を作製する方法 | |

| JP3763701B2 (ja) | 窒化ガリウム系半導体発光素子 | |

| JP3219231B2 (ja) | 化合物半導体発光素子およびその製造方法 | |

| JP3753369B2 (ja) | 窒化物系半導体発光素子 | |

| JP3642199B2 (ja) | 窒化ガリウム系化合物半導体発光素子の製造方法 | |

| JPH10303502A (ja) | 窒化ガリウム系化合物半導体発光素子及びその製造方法 | |

| JPH11224972A (ja) | 窒化物半導体発光素子 | |

| JP4057473B2 (ja) | 化合物半導体発光素子及びその製造方法 | |

| JP2002094113A (ja) | Iii−v族窒化物系半導体発光素子の製造方法 | |

| KR100728132B1 (ko) | 전류 확산층을 이용한 발광 다이오드 | |

| JP3615386B2 (ja) | 半導体素子及びその製造方法 | |

| JP3456980B2 (ja) | 化合物半導体層の形成方法 | |

| JP4198003B2 (ja) | 窒化物半導体発光素子 | |

| JP2008047940A (ja) | 化合物半導体発光素子 | |

| JP3556593B2 (ja) | 化合物半導体発光素子およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060411 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060609 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20060704 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060831 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20060908 |

|

| A912 | Removal of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20061201 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071029 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071213 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101221 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101221 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111221 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111221 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121221 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121221 Year of fee payment: 5 |

|

| EXPY | Cancellation because of completion of term |