JP2014229711A - Semiconductor device - Google Patents

Semiconductor device Download PDFInfo

- Publication number

- JP2014229711A JP2014229711A JP2013107381A JP2013107381A JP2014229711A JP 2014229711 A JP2014229711 A JP 2014229711A JP 2013107381 A JP2013107381 A JP 2013107381A JP 2013107381 A JP2013107381 A JP 2013107381A JP 2014229711 A JP2014229711 A JP 2014229711A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- wiring

- insulating film

- metal pattern

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

【課題】容量素子を有する半導体装置の信頼性や性能を向上させる。【解決手段】半導体基板上に形成した複数の配線層のうちのいずれかの配線層に、容量素子C1の下部電極LEを設け、下部電極LEが形成された配線層よりも2つ上層の配線層において、下部電極LEの上方に容量素子C1の上部電極UEを設ける。そして、下部電極LEが形成された配線層よりも1つ上層の配線層において、下部電極LEと上部電極UEとの間に位置する浮遊電極FEを設ける。【選択図】図8The reliability and performance of a semiconductor device having a capacitor element are improved. A lower electrode LE of a capacitor element C1 is provided in any one of a plurality of wiring layers formed on a semiconductor substrate, and two wirings higher than the wiring layer in which the lower electrode LE is formed. In the layer, the upper electrode UE of the capacitive element C1 is provided above the lower electrode LE. Then, the floating electrode FE located between the lower electrode LE and the upper electrode UE is provided in the wiring layer one layer above the wiring layer in which the lower electrode LE is formed. [Selection] Figure 8

Description

本発明は、半導体装置に関し、例えば、容量素子を有する半導体装置に好適に利用できるものである。 The present invention relates to a semiconductor device, and can be suitably used for a semiconductor device having a capacitor, for example.

半導体基板上に、MISFET(Metal Insulator Semiconductor Field Effect Transistor)や容量素子などを形成し、各素子間を配線で結線することで種々の半導体装置が製造される。半導体基板上に形成される容量素子には、MIM(Metal Insulator Metal)型容量素子がある。 Various semiconductor devices are manufactured by forming MISFETs (Metal Insulator Semiconductor Field Effect Transistors), capacitive elements, and the like on a semiconductor substrate and connecting the elements with wiring. As a capacitive element formed on a semiconductor substrate, there is a MIM (Metal Insulator Metal) type capacitive element.

特開2009−33029号公報(特許文献1)には、DRAMの配線に関する技術が記載されている。 Japanese Unexamined Patent Application Publication No. 2009-33029 (Patent Document 1) describes a technique related to wiring of a DRAM.

特開2005−183739号公報(特許文献2)には、櫛型状に配列された複数の配線をもつ電極により容量素子を形成する技術が記載されている。 Japanese Patent Laying-Open No. 2005-183739 (Patent Document 2) describes a technique in which a capacitor element is formed by electrodes having a plurality of wirings arranged in a comb shape.

特開2009−224637号公報(特許文献3)には、櫛型形状の金属パターンで電極を形成したMIM型の容量素子に関する技術が記載されている。 Japanese Patent Laying-Open No. 2009-224737 (Patent Document 3) describes a technique related to an MIM type capacitive element in which electrodes are formed with a comb-shaped metal pattern.

容量素子を有する半導体装置においても、できるだけ信頼性を向上させることが望まれる。または、できるだけ性能を向上させることが望まれる。若しくは、信頼性を向上させ、かつ、性能を向上させることが望まれる。 Even in a semiconductor device having a capacitor element, it is desired to improve the reliability as much as possible. Alternatively, it is desired to improve the performance as much as possible. Alternatively, it is desirable to improve reliability and improve performance.

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。 Other problems and novel features will become apparent from the description of the specification and the accompanying drawings.

一実施の形態によれば、半導体基板上に形成した複数の配線層のうちのいずれかの配線層に、容量素子の第1電極を設け、前記第1電極が形成された配線層よりも2つ上層の配線層において、前記第1電極の上方に前記容量素子の第2電極を設け、前記第1電極が形成された配線層よりも1つ上層の配線層において、前記第1電極と前記第2電極との間に浮遊電極を設ける。 According to one embodiment, the first electrode of the capacitive element is provided in any one of the plurality of wiring layers formed on the semiconductor substrate, and is 2 rather than the wiring layer in which the first electrode is formed. In the upper wiring layer, the second electrode of the capacitive element is provided above the first electrode. In the wiring layer one layer higher than the wiring layer on which the first electrode is formed, the first electrode and the A floating electrode is provided between the second electrode.

また、一実施の形態によれば、半導体基板上に形成した複数の配線層のうちのいずれかの配線層に第1金属パターンおよび第2金属パターンを設け、前記第1金属パターンおよび第2金属パターンが形成された配線層よりも1つ上層の配線層に、第3金属パターンおよび第4金属パターンを設ける。前記第1金属パターンと前記第3金属パターンは、互いに電気的に接続されて容量素子の一方の電極を形成し、前記第2金属パターンと前記第4金属パターンは、互いに電気的に接続されて前記容量素子の他方の電極を形成する。前記第1金属パターンは、第1方向にそれぞれ延在する複数の第1電極部を含んでおり、前記第2金属パターンは、前記第1方向にそれぞれ延在する複数の第2電極部を含んでおり、前記第1電極部と前記第2電極部とは、前記第1方向と交差する第2方向に交互に並んでいる。前記第3金属パターンは、前記第1方向にそれぞれ延在する複数の第3電極部を含んでおり、前記第4金属パターンは、前記第1方向にそれぞれ延在する複数の第4電極部を含んでおり、前記第3電極部と前記第4電極部とは、前記第2方向に交互に並んでいる。前記複数の第1電極部のそれぞれは、平面視において、前記第2方向に隣り合う前記第3電極部と前記第4電極部との間に配置されており、前記複数の第2電極部のそれぞれは、平面視において、前記第2方向に隣り合う前記第3電極部と前記第4電極部との間に配置されている。 According to one embodiment, the first metal pattern and the second metal pattern are provided on any one of the plurality of wiring layers formed on the semiconductor substrate, and the first metal pattern and the second metal pattern are provided. A third metal pattern and a fourth metal pattern are provided in a wiring layer one layer above the wiring layer on which the pattern is formed. The first metal pattern and the third metal pattern are electrically connected to each other to form one electrode of a capacitive element, and the second metal pattern and the fourth metal pattern are electrically connected to each other. The other electrode of the capacitive element is formed. The first metal pattern includes a plurality of first electrode portions extending in a first direction, and the second metal pattern includes a plurality of second electrode portions extending in the first direction. The first electrode portions and the second electrode portions are alternately arranged in a second direction intersecting the first direction. The third metal pattern includes a plurality of third electrode portions extending in the first direction, and the fourth metal pattern includes a plurality of fourth electrode portions extending in the first direction. The third electrode portion and the fourth electrode portion are alternately arranged in the second direction. Each of the plurality of first electrode portions is disposed between the third electrode portion and the fourth electrode portion adjacent to each other in the second direction in a plan view, and the plurality of second electrode portions Each is disposed between the third electrode portion and the fourth electrode portion adjacent in the second direction in plan view.

また、一実施の形態によれば、半導体基板上に形成した複数の配線層のうちのいずれかの配線層に、容量素子の一方の電極を形成する第1金属パターンと、前記容量素子の他方の電極を形成する第2金属パターンとを設ける。前記第1金属パターンは、第1方向にそれぞれ延在する複数の第1電極部を含んでおり、前記第2金属パターンは、前記第1方向にそれぞれ延在する複数の第2電極部を含んでおり、前記第1電極部と前記第2電極部とは、前記第1方向と交差する第2方向に交互に並んでいる。前記第1金属パターンおよび第2金属パターンが形成された配線層において、前記第2方向に隣り合う前記第1電極部と前記第2電極部との間に浮遊電極が形成されている。 According to one embodiment, the first metal pattern for forming one electrode of the capacitive element on any one of the plurality of wiring layers formed on the semiconductor substrate, and the other of the capacitive elements And a second metal pattern for forming the electrode. The first metal pattern includes a plurality of first electrode portions extending in a first direction, and the second metal pattern includes a plurality of second electrode portions extending in the first direction. The first electrode portions and the second electrode portions are alternately arranged in a second direction intersecting the first direction. In the wiring layer in which the first metal pattern and the second metal pattern are formed, a floating electrode is formed between the first electrode portion and the second electrode portion adjacent to each other in the second direction.

一実施の形態によれば、半導体装置の信頼性を向上させることができる。 According to one embodiment, the reliability of a semiconductor device can be improved.

または、半導体装置の性能を向上させることができる。 Alternatively, the performance of the semiconductor device can be improved.

若しくは、半導体装置の信頼性を向上させ、かつ、半導体装置の性能を向上させることができる。 Alternatively, the reliability of the semiconductor device can be improved and the performance of the semiconductor device can be improved.

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。 In the following embodiments, when it is necessary for the sake of convenience, the description will be divided into a plurality of sections or embodiments. However, unless otherwise specified, they are not irrelevant to each other. There are some or all of the modifications, details, supplementary explanations, and the like. Further, in the following embodiments, when referring to the number of elements (including the number, numerical value, quantity, range, etc.), especially when clearly indicated and when clearly limited to a specific number in principle, etc. Except, it is not limited to the specific number, and may be more or less than the specific number. Further, in the following embodiments, the constituent elements (including element steps and the like) are not necessarily indispensable unless otherwise specified and apparently essential in principle. Needless to say. Similarly, in the following embodiments, when referring to the shapes, positional relationships, etc. of the components, etc., the shapes are substantially the same unless otherwise specified, or otherwise apparent in principle. And the like are included. The same applies to the above numerical values and ranges.

以下、実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。 Hereinafter, embodiments will be described in detail with reference to the drawings. Note that components having the same function are denoted by the same reference symbols throughout the drawings for describing the embodiments, and the repetitive description thereof will be omitted. In the following embodiments, the description of the same or similar parts will not be repeated in principle unless particularly necessary.

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。 In the drawings used in the embodiments, hatching may be omitted even in a cross-sectional view so as to make the drawings easy to see. Further, even a plan view may be hatched to make the drawing easy to see.

(実施の形態1)

<半導体装置の構造について>

本実施の形態の半導体装置を図面を参照して説明する。本実施の形態の半導体装置は、容量素子を有する半導体装置である。

(Embodiment 1)

<Structure of semiconductor device>

The semiconductor device of the present embodiment will be described with reference to the drawings. The semiconductor device of this embodiment is a semiconductor device having a capacitor.

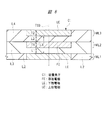

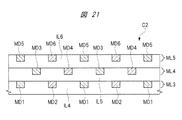

図1は、本実施の形態の半導体装置の要部断面図であり、図2〜図5は、本実施の形態の半導体装置の要部平面図である。図1には、本実施の形態の半導体装置におけるMISFET形成領域およびキャパシタ形成領域の断面図が示され、図2〜図5には、本実施の形態の半導体装置におけるキャパシタ形成領域の平面図が示されている。 FIG. 1 is a cross-sectional view of main parts of the semiconductor device of the present embodiment, and FIGS. 2 to 5 are plan views of main parts of the semiconductor device of the present embodiment. 1 is a cross-sectional view of a MISFET formation region and a capacitor formation region in the semiconductor device of the present embodiment, and FIGS. 2 to 5 are plan views of the capacitor formation region in the semiconductor device of the present embodiment. It is shown.

図1におけるキャパシタ形成領域の断面図は、図2〜図5のA1−A1線の位置での断面にほぼ対応している。但し、図1の断面図では、絶縁膜IL6および絶縁膜IL6に埋め込まれた配線M5よりも上層の構造は、図示を省略している。また、図1におけるMISFET形成領域とキャパシタ形成領域とは、同じ半導体装置(同じ半導体基板SB)における互いに異なる平面領域に対応している。図1におけるMISFET形成領域とキャパシタ形成領域とは、互いに隣り合っていても、隣り合っていなくてもよいが、理解を簡単にするために、図1の断面図においては、MISFET形成領域の断面図の隣にキャパシタ形成領域の断面図を示している。 1 substantially corresponds to the cross section taken along the line A1-A1 in FIGS. However, in the cross-sectional view of FIG. 1, the illustration of the insulating film IL6 and the structure above the wiring M5 embedded in the insulating film IL6 is omitted. Further, the MISFET formation region and the capacitor formation region in FIG. 1 correspond to different planar regions in the same semiconductor device (the same semiconductor substrate SB). The MISFET formation region and the capacitor formation region in FIG. 1 may or may not be adjacent to each other, but for the sake of easy understanding, the cross-sectional view of FIG. A sectional view of the capacitor formation region is shown next to the figure.

また、図2〜図5には、同じ半導体装置(半導体基板SB)における同じ平面領域(ここではキャパシタ形成領域)が示されているが、図2〜図5では、示される層が相違している。すなわち、図3には、キャパシタ形成領域における上部電極UEが形成された層(すなわち配線層ML3)の平面レイアウトが示され、図4には、キャパシタ形成領域における浮遊電極FEが形成された層(すなわち配線層ML2)の平面レイアウトが示され、図5には、キャパシタ形成領域における下部電極LEが形成された層(すなわち配線層ML1)の平面レイアウトが示されている。また、図2には、図3〜図5を重ね合わせた平面レイアウトが示されている。 2 to 5 show the same planar region (capacitor formation region here) in the same semiconductor device (semiconductor substrate SB), but the layers shown in FIGS. 2 to 5 are different. Yes. That is, FIG. 3 shows a planar layout of the layer in which the upper electrode UE is formed in the capacitor formation region (that is, the wiring layer ML3), and FIG. 4 shows the layer in which the floating electrode FE is formed in the capacitor formation region ( That is, a planar layout of the wiring layer ML2) is shown, and FIG. 5 shows a planar layout of the layer in which the lower electrode LE is formed in the capacitor formation region (that is, the wiring layer ML1). Further, FIG. 2 shows a planar layout in which FIGS.

本実施の形態の半導体装置は、MISFET形成領域にMISFET(Metal Insulator Semiconductor Field Effect Transistor)が形成され、MISFET形成領域とは異なる領域(平面領域)であるキャパシタ形成領域に容量素子C1が形成されている。本実施の形態の半導体装置の具体的な構成を図1〜図5を参照して説明する。 In the semiconductor device of this embodiment, a MISFET (Metal Insulator Semiconductor Field Effect Transistor) is formed in a MISFET formation region, and a capacitor element C1 is formed in a capacitor formation region that is a region (planar region) different from the MISFET formation region. Yes. A specific configuration of the semiconductor device of the present embodiment will be described with reference to FIGS.

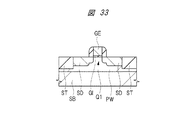

図1に示されるように、本実施の形態の半導体装置を構成する半導体基板SBは、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる。本実施の形態の半導体装置を形成する半導体基板SBは、容量素子C1が形成されたキャパシタ形成領域と、MISFETのような電界効果トランジスタが形成されたMISFET形成領域とを有しており、図1には、このキャパシタ形成領域とMISFET形成領域の断面図が示されている。 As shown in FIG. 1, the semiconductor substrate SB constituting the semiconductor device of the present embodiment is made of, for example, p-type single crystal silicon having a specific resistance of about 1 to 10 Ωcm. The semiconductor substrate SB forming the semiconductor device of the present embodiment has a capacitor forming region in which the capacitor element C1 is formed and a MISFET forming region in which a field effect transistor such as a MISFET is formed. FIG. 2 shows a cross-sectional view of the capacitor formation region and the MISFET formation region.

図1に示されるように、半導体基板SBの主面には、素子分離領域STが形成されている。素子分離領域STは、半導体基板SBに形成された溝(素子分離用の溝)に酸化シリコンなどの絶縁膜を埋め込んだものである。すなわち、素子分離領域STは、半導体基板SBに形成されかつ絶縁膜が埋め込まれた溝からなる。素子分離領域STは、STI(Shallow Trench Isolation)法により形成することができる。 As shown in FIG. 1, an element isolation region ST is formed on the main surface of the semiconductor substrate SB. The element isolation region ST is formed by embedding an insulating film such as silicon oxide in a groove (element isolation groove) formed in the semiconductor substrate SB. That is, the element isolation region ST is formed of a trench formed in the semiconductor substrate SB and embedded with an insulating film. The element isolation region ST can be formed by an STI (Shallow Trench Isolation) method.

素子分離領域STによって活性領域が規定される。活性領域は、半導体基板SBの基板領域であり、半導体基板SBの主面において素子分離領域STが形成されていない領域に対応する。 An active region is defined by the element isolation region ST. The active region is a substrate region of the semiconductor substrate SB and corresponds to a region where the element isolation region ST is not formed on the main surface of the semiconductor substrate SB.

図1に示されるように、MISFET形成領域の半導体基板SBにp型ウエル領域PWが形成されており、このp型ウエル領域PW上には、nチャネル型のMISFET(Metal Insulator Semiconductor Field Effect Transistor:MIS型電界効果トランジスタ)Q1が形成されている。MISFETQ1は、p型ウエル領域PWの表面に形成されたゲート絶縁膜GIと、ゲート絶縁膜GI上に形成されたゲート電極GEと、p型ウエル領域PW内に形成されたソース・ドレイン用のn型半導体領域SDとを有している。すなわち、ゲート電極GEは、p型ウエル領域PW上にゲート絶縁膜GIを介して形成されている。また、ソース・ドレイン用のn型半導体領域SDは、半導体基板SB(p型ウエル領域PW)において、ゲート電極GEの両側の領域に形成されている。半導体基板SB(p型ウエル領域PW)における、ゲート電極GEの下の領域が、MISFETQ1のチャネルが形成される領域、すなわちチャネル形成領域となる。一対のn型半導体領域SDが、チャネル形成領域を間に挟んでゲート電極GEのゲート長方向に対向している。 As shown in FIG. 1, a p-type well region PW is formed in a semiconductor substrate SB in a MISFET formation region, and an n-channel type MISFET (Metal Insulator Semiconductor Field Effect Transistor :) is formed on the p-type well region PW. MIS type field effect transistor) Q1 is formed. The MISFET Q1 includes a gate insulating film GI formed on the surface of the p-type well region PW, a gate electrode GE formed on the gate insulating film GI, and n for source / drain formed in the p-type well region PW. Type semiconductor region SD. That is, the gate electrode GE is formed on the p-type well region PW via the gate insulating film GI. The source / drain n-type semiconductor regions SD are formed in regions on both sides of the gate electrode GE in the semiconductor substrate SB (p-type well region PW). A region under the gate electrode GE in the semiconductor substrate SB (p-type well region PW) is a region where a channel of the MISFET Q1 is formed, that is, a channel formation region. A pair of n-type semiconductor regions SD are opposed to each other in the gate length direction of the gate electrode GE with the channel formation region interposed therebetween.

ゲート絶縁膜GIは、例えば酸化シリコン膜などからなり、ゲート電極GEは、例えば、不純物を導入した多結晶シリコン膜などからなる。n型半導体領域SDは、LDD(Lightly doped Drain)構造とすることもでき、この場合、ゲート電極GEの側壁上には、サイドウォールスペーサとも称される側壁絶縁膜が形成される。 The gate insulating film GI is made of, for example, a silicon oxide film, and the gate electrode GE is made of, for example, a polycrystalline silicon film into which impurities are introduced. The n-type semiconductor region SD may have an LDD (Lightly doped Drain) structure. In this case, a sidewall insulating film, also referred to as a sidewall spacer, is formed on the sidewall of the gate electrode GE.

ゲート電極GEおよびn型半導体領域SDの表面(表層部分)には、サリサイド(Salicide:Self Aligned Silicide)技術などにより、それぞれ金属シリサイド層(図示せず)を形成することもできる。この金属シリサイド層としては、例えばコバルトシリサイド層またはニッケルシリサイド層などを用いることができる。 Metal silicide layers (not shown) can also be formed on the surfaces (surface layer portions) of the gate electrode GE and the n-type semiconductor region SD by a salicide (Salicide: Self Aligned Silicide) technique, respectively. As this metal silicide layer, for example, a cobalt silicide layer or a nickel silicide layer can be used.

また、半導体基板SBの主面にnチャネル型のMISFETQ1を形成した場合について図示および説明したが、導電型を反対にして、pチャネル型のMISFETを形成することもできる。また、半導体基板SBの主面に、nチャネル型のMISFETとpチャネル型のMISFETの両方を形成することもできる。半導体基板SBの主面に形成するMISFETの数は、種々変更可能である。また、MISFET以外の半導体素子を半導体基板SBの主面に形成することもできる。 Further, although the case where the n-channel type MISFET Q1 is formed on the main surface of the semiconductor substrate SB has been illustrated and described, a p-channel type MISFET can be formed by reversing the conductivity type. In addition, both an n-channel MISFET and a p-channel MISFET can be formed on the main surface of the semiconductor substrate SB. The number of MISFETs formed on the main surface of the semiconductor substrate SB can be variously changed. Further, a semiconductor element other than the MISFET can be formed on the main surface of the semiconductor substrate SB.

また、図1では、キャパシタ形成領域における半導体基板SBの主面には、半導体素子を形成していない場合が示されており、キャパシタ形成領域における半導体基板SBの主面には、素子分離領域STが形成されている。他の形態として、キャパシタ形成領域の半導体基板SBの主面に、例えばMISFETまたはMOS(Metal Oxide Semiconductor)型容量素子などの半導体素子を形成することもできる。 FIG. 1 shows a case where no semiconductor element is formed on the main surface of the semiconductor substrate SB in the capacitor formation region, and an element isolation region ST is formed on the main surface of the semiconductor substrate SB in the capacitor formation region. Is formed. As another form, a semiconductor element such as a MISFET or a MOS (Metal Oxide Semiconductor) type capacitive element can be formed on the main surface of the semiconductor substrate SB in the capacitor formation region.

図1に示されるように、半導体基板SBの主面(主面全面)上に、ゲート電極GEを覆うように、絶縁膜(層間絶縁膜)IL1が形成されている。絶縁膜IL1は、窒化シリコン膜(下層側)とそれよりも厚い酸化シリコン膜(上層側)との積層膜、あるいは酸化シリコン膜の単体膜などにより形成されている。 As shown in FIG. 1, an insulating film (interlayer insulating film) IL1 is formed on the main surface (entire main surface) of the semiconductor substrate SB so as to cover the gate electrode GE. The insulating film IL1 is formed of a laminated film of a silicon nitride film (lower layer side) and a thicker silicon oxide film (upper layer side), or a single film of a silicon oxide film.

絶縁膜IL1を成膜したときには、下地の段差(例えばゲート電極GEの段差など)に起因して絶縁膜IL1の上面に凹凸形状が形成されるが、絶縁膜IL1の成膜後に絶縁膜IL1の上面(表面)をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨するなどして、絶縁膜IL1の上面は平坦化されている。このため、絶縁膜IL1よりも上の構造(後述の配線M1〜M5を含む多層配線構造)は、絶縁膜IL1の平坦な上面(表面)上に形成されている。 When the insulating film IL1 is formed, an uneven shape is formed on the upper surface of the insulating film IL1 due to a base step (for example, a step of the gate electrode GE). The upper surface of the insulating film IL1 is flattened by polishing the upper surface (surface) by a CMP (Chemical Mechanical Polishing) method. Therefore, the structure above the insulating film IL1 (a multilayer wiring structure including wirings M1 to M5 described later) is formed on the flat upper surface (front surface) of the insulating film IL1.

絶縁膜IL1には、絶縁膜IL1を貫通するコンタクトホール(開口部、孔、貫通孔)が形成されており、コンタクトホール内には、タングステン(W)膜を主体とする導電膜などからなるプラグ(導体部、接続用導体部)PGが形成されて埋め込まれている。MISFET形成領域において、コンタクトホールおよびそれを埋めるプラグPGは、n型半導体領域SDの上部やゲート電極GEの上部などに形成されている。 The insulating film IL1 has contact holes (openings, holes, through holes) penetrating the insulating film IL1, and plugs made of a conductive film mainly composed of a tungsten (W) film are formed in the contact holes. (Conductor part, connecting conductor part) PG is formed and embedded. In the MISFET formation region, the contact hole and the plug PG filling the contact hole are formed above the n-type semiconductor region SD, the top of the gate electrode GE, and the like.

図1に示されるように、絶縁膜IL1上には、配線M1〜M5を含む複数の配線層、すなわち多層配線構造が形成されている。 As shown in FIG. 1, a plurality of wiring layers including wirings M1 to M5, that is, a multilayer wiring structure is formed on the insulating film IL1.

すなわち、プラグPGが埋め込まれた絶縁膜IL1上には、絶縁膜(層間絶縁膜)IL2が形成されており、この絶縁膜IL2には配線用の溝とこの溝に埋め込まれた配線M1とが形成されている。絶縁膜IL2は、単層の絶縁膜、あるいは、複数の絶縁膜の積層膜とすることができる。配線M1は、ダマシン(Damascene)技術(ここではシングルダマシン技術)を用いて形成することができ、銅を主成分とする銅配線(ダマシン銅配線、埋込銅配線)とすることができる。 That is, an insulating film (interlayer insulating film) IL2 is formed on the insulating film IL1 in which the plug PG is embedded, and a wiring groove and a wiring M1 embedded in the groove are formed in the insulating film IL2. Is formed. The insulating film IL2 can be a single-layer insulating film or a stacked film of a plurality of insulating films. The wiring M1 can be formed using a damascene technology (here, a single damascene technology), and can be a copper wiring (damascene copper wiring, embedded copper wiring) containing copper as a main component.

配線M1は、多層配線構造における最下層の配線層(すなわち配線層ML1)の配線である。ここで、半導体基板SB上(すなわち絶縁膜IL1上)に形成された多層配線構造において、最下層の配線層を、符号ML1を付して配線層ML1と称することとする。また、半導体基板SB上(すなわち絶縁膜IL1上)に形成された多層配線構造において、配線層ML1よりも1つ上層の配線層を、符号ML2を付して配線層ML2と称し、配線層ML2よりも1つ上層の配線層を、符号ML3を付して配線層ML3と称することとする。また、半導体基板SB上(すなわち絶縁膜IL1上)に形成された多層配線構造において、配線層ML3よりも1つ上層の配線層を、符号ML4を付して配線層ML4と称し、配線層ML4よりも1つ上層の配線層を、符号ML5を付して配線層ML5と称することとする。従って、配線M1は、配線層ML1の配線であり、後述の配線M2は、配線層ML2の配線であり、後述の配線M3は、配線層ML3の配線であり、後述の配線M4は、配線層ML4の配線であり、後述の配線M5は、配線層ML5の配線である。 The wiring M1 is a wiring of the lowermost wiring layer (that is, the wiring layer ML1) in the multilayer wiring structure. Here, in the multilayer wiring structure formed on the semiconductor substrate SB (that is, on the insulating film IL1), the lowermost wiring layer is denoted by a reference numeral ML1 and is referred to as a wiring layer ML1. In the multilayer wiring structure formed on the semiconductor substrate SB (that is, on the insulating film IL1), the wiring layer that is one layer above the wiring layer ML1 is referred to as a wiring layer ML2 with a reference numeral ML2, and the wiring layer ML2 The wiring layer that is one layer higher than that is denoted by a reference numeral ML3 and is referred to as a wiring layer ML3. In the multilayer wiring structure formed on the semiconductor substrate SB (that is, on the insulating film IL1), the wiring layer that is one layer above the wiring layer ML3 is referred to as a wiring layer ML4 with a reference numeral ML4, and the wiring layer ML4. The wiring layer that is one layer higher than that is denoted by the reference numeral ML5 and is referred to as a wiring layer ML5. Accordingly, the wiring M1 is a wiring of the wiring layer ML1, a wiring M2 described later is a wiring of the wiring layer ML2, a wiring M3 described later is a wiring of the wiring layer ML3, and a wiring M4 described later is a wiring layer. ML4 is a wiring, and a wiring M5 described later is a wiring of the wiring layer ML5.

なお、図1には符号ML1〜ML5は示していないが、図1において、配線M1および下部電極LEが形成されている層が配線層ML1に対応し、配線M2および浮遊電極FEが形成されている層が配線層ML2に対応し、配線M3および上部電極UEが形成されている層が配線層ML3に対応している。また、図1において、配線M4が形成されている層が配線層ML4に対応し、配線M5が形成されている層が配線層ML5に対応している。 In FIG. 1, reference numerals ML1 to ML5 are not shown. In FIG. 1, the layer in which the wiring M1 and the lower electrode LE are formed corresponds to the wiring layer ML1, and the wiring M2 and the floating electrode FE are formed. The layer in which the wiring M3 and the upper electrode UE are formed corresponds to the wiring layer ML3. In FIG. 1, the layer in which the wiring M4 is formed corresponds to the wiring layer ML4, and the layer in which the wiring M5 is formed corresponds to the wiring layer ML5.

図1〜図5に示されるように、キャパシタ形成領域においては、下部電極LEが、配線M1と同層に同工程で形成されている。すなわち、配線M1と下部電極LEとは、同じ配線層ML1に形成されている。このため、配線M1と下部電極LEとは、どちらもダマシン技術を用いて同工程で形成されており、絶縁膜IL2に埋め込まれている。具体的には、配線M1と下部電極LEとは、それぞれ、絶縁膜IL2に形成された溝(または開口部)に埋め込まれている。下部電極LEと配線M1とは、同じ導電材料からなる。また、下部電極LEには、配線M1が一体的に接続されており、この下部電極LEに接続された配線M1などを介して、下部電極LEに所定の電位が供給できるようになっている。 As shown in FIGS. 1 to 5, in the capacitor formation region, the lower electrode LE is formed in the same layer as the wiring M1 in the same process. That is, the wiring M1 and the lower electrode LE are formed in the same wiring layer ML1. For this reason, both the wiring M1 and the lower electrode LE are formed in the same process using the damascene technique, and are embedded in the insulating film IL2. Specifically, the wiring M1 and the lower electrode LE are embedded in grooves (or openings) formed in the insulating film IL2. The lower electrode LE and the wiring M1 are made of the same conductive material. In addition, a wiring M1 is integrally connected to the lower electrode LE, and a predetermined potential can be supplied to the lower electrode LE through the wiring M1 connected to the lower electrode LE.

図1に示されるように、配線M1および下部電極LEが埋め込まれた絶縁膜IL2上には、絶縁膜(層間絶縁膜)IL3が形成されている。絶縁膜IL3は、単層の絶縁膜、あるいは、複数の絶縁膜の積層膜とすることができる。 As shown in FIG. 1, an insulating film (interlayer insulating film) IL3 is formed on the insulating film IL2 in which the wiring M1 and the lower electrode LE are embedded. The insulating film IL3 can be a single-layer insulating film or a stacked film of a plurality of insulating films.

絶縁膜IL3には、配線用の溝とその溝に埋め込まれた配線M2とが形成されている。配線M2は、ダマシン技術(ここではデュアルダマシン技術)を用いて形成することができ、銅を主成分とする銅配線(ダマシン銅配線、埋込銅配線)とすることができる。配線M2は、配線層ML2の配線である。配線M2の底面は、絶縁膜IL3の厚みの途中に位置している。 In the insulating film IL3, a trench for wiring and a wiring M2 embedded in the trench are formed. The wiring M2 can be formed using a damascene technology (here, dual damascene technology), and can be a copper wiring containing copper as a main component (damascene copper wiring, embedded copper wiring). The wiring M2 is a wiring of the wiring layer ML2. The bottom surface of the wiring M2 is located in the middle of the thickness of the insulating film IL3.

配線M2は、配線M2と一体的に形成されたビア部V2を介して、配線M1と電気的に接続されている。すなわち、ビア部V2は、配線M2と配線M1との間に配置されており、ビア部V2の上面は、配線M2の下面と一体的に接続されており、ビア部V2の下面(底面)は配線M1の上面に接している。ビア部V2は配線M2と同じ導電膜により一体的に形成されており、デュアルダマシン(Dual-Damascene)技術により配線M2を形成する際に配線M2と一緒にビア部V2も形成される。ビア部V2や後述のビア部V3,V4,V5は、異なる層の配線間に配置されかつ異なる層の配線間を接続する導電性の接続部材である。 The wiring M2 is electrically connected to the wiring M1 through a via portion V2 formed integrally with the wiring M2. That is, the via portion V2 is disposed between the wiring M2 and the wiring M1, the upper surface of the via portion V2 is integrally connected to the lower surface of the wiring M2, and the lower surface (bottom surface) of the via portion V2 is It is in contact with the upper surface of the wiring M1. The via portion V2 is integrally formed of the same conductive film as the wiring M2, and the via portion V2 is formed together with the wiring M2 when the wiring M2 is formed by the dual damascene technique. A via portion V2 and via portions V3, V4, and V5, which will be described later, are conductive connection members that are arranged between wirings of different layers and connect wirings of different layers.

また、ビア部V2は、配線M2とは別工程で形成することもでき、その場合、ビア部V2はプラグPGと同様の工程により形成され、配線M2はシングルダマシン技術により形成され、ビア部V2の下面(底面)は配線M1の上面に接し、ビア部V2の上面は配線M2の下面に接することになる。 The via portion V2 can also be formed in a separate process from the wiring M2. In this case, the via portion V2 is formed by the same process as the plug PG, the wiring M2 is formed by a single damascene technique, and the via portion V2 is formed. The bottom surface (bottom surface) of the contact portion is in contact with the top surface of the wiring M1, and the top surface of the via portion V2 is in contact with the bottom surface of the wiring M2.

図1〜図5に示されるように、キャパシタ形成領域においては、浮遊電極FEが、配線M2と同層に同工程で形成されている。すなわち、配線M2と浮遊電極FEとは、同じ配線層ML2に形成されている。つまり、配線M2および浮遊電極FEは、配線M1および下部電極LEが形成された配線層ML1よりも1つ上層の配線層ML2に形成されている。このため、配線M2と浮遊電極FEとは、どちらもダマシン技術を用いて同工程で形成されており、絶縁膜IL3に埋め込まれている。具体的には、配線M2と浮遊電極FEとは、それぞれ、絶縁膜IL3に形成された溝(または開口部)に埋め込まれている。浮遊電極FEと配線M2とは、同じ導電材料からなる。浮遊電極FEの底面(下面)は、絶縁膜IL3の厚みの途中に位置している。浮遊電極FEの底面(下面)の高さ位置と、配線M2の底面(下面)の高さ位置とは、概ね同じである。なお、絶縁膜に溝を形成する際には、その平面寸法が大きいほど溝の深さは深くなるため、浮遊電極FEの寸法(辺の寸法)が配線M2の幅よりも大きいことを反映して、浮遊電極FEの底面の高さ位置が、配線M2の底面の高さ位置より低くなる場合もある。 As shown in FIGS. 1 to 5, in the capacitor formation region, the floating electrode FE is formed in the same layer as the wiring M2 in the same process. That is, the wiring M2 and the floating electrode FE are formed in the same wiring layer ML2. That is, the wiring M2 and the floating electrode FE are formed in the wiring layer ML2 that is one layer higher than the wiring layer ML1 in which the wiring M1 and the lower electrode LE are formed. For this reason, both the wiring M2 and the floating electrode FE are formed in the same process using the damascene technique, and are embedded in the insulating film IL3. Specifically, the wiring M2 and the floating electrode FE are each embedded in a groove (or opening) formed in the insulating film IL3. The floating electrode FE and the wiring M2 are made of the same conductive material. The bottom surface (lower surface) of the floating electrode FE is located in the middle of the thickness of the insulating film IL3. The height position of the bottom surface (lower surface) of the floating electrode FE and the height position of the bottom surface (lower surface) of the wiring M2 are substantially the same. Note that when the trench is formed in the insulating film, the depth of the trench becomes deeper as the planar dimension is larger, which reflects that the dimension (side dimension) of the floating electrode FE is larger than the width of the wiring M2. Thus, the height position of the bottom surface of the floating electrode FE may be lower than the height position of the bottom surface of the wiring M2.

浮遊電極FEは、浮遊電位とされている。すなわち、浮遊電極FEは、電気的に浮遊状態(フローティング状態)とされている。浮遊電極FEは、下部電極LEと導体では繋がっておらず、また、後述の上部電極UEと導体では繋がっていない。このため、浮遊電極FEにはビア部V2は接続されておらず、浮遊電極FEの下にはビア部V2は配置されていない。 The floating electrode FE is set to a floating potential. That is, the floating electrode FE is in an electrically floating state (floating state). The floating electrode FE is not connected to the lower electrode LE by a conductor, and is not connected to an upper electrode UE, which will be described later, by a conductor. For this reason, the via part V2 is not connected to the floating electrode FE, and the via part V2 is not disposed under the floating electrode FE.

下部電極LEおよび上部電極UEのうちの一方に、下部電極LEおよび上部電極UEのうちの他方よりも高い電位(電圧)が印加(供給)されることにより、容量素子C1に電荷が蓄積される。すなわち、容量素子C1に電荷を蓄積する際には、配線などの導体を通じて下部電極LEと上部電極UEとに互いに異なる電圧が印加される。つまり、容量素子C1に電荷を蓄積する際には、下部電極LEよりも上部電極UEが高電位(高電圧)とされるか、あるいは、上部電極UEよりも下部電極LEが高電位(高電圧)とされる。しかしながら、浮遊電極FEは、浮遊電位とされており、容量素子C1に電荷を蓄積する際に、配線などの導体を通じた電圧印加は浮遊電極FEに対しては行われない。このため、浮遊電極FEは、ダミー電極とみなすこともできる。 When a potential (voltage) higher than the other of the lower electrode LE and the upper electrode UE is applied (supplied) to one of the lower electrode LE and the upper electrode UE, charges are accumulated in the capacitive element C1. . That is, when accumulating charges in the capacitive element C1, different voltages are applied to the lower electrode LE and the upper electrode UE through a conductor such as a wiring. That is, when accumulating charges in the capacitive element C1, the upper electrode UE is set to a higher potential (high voltage) than the lower electrode LE, or the lower electrode LE is set to a higher potential (high voltage) than the upper electrode UE. ). However, the floating electrode FE is at a floating potential, and voltage is not applied to the floating electrode FE through a conductor such as a wiring when charges are accumulated in the capacitor C1. For this reason, the floating electrode FE can also be regarded as a dummy electrode.

図1に示されるように、配線M2および浮遊電極FEが埋め込まれた絶縁膜IL3上には、絶縁膜(層間絶縁膜)IL4が形成されている。絶縁膜IL4は、単層の絶縁膜、あるいは、複数の絶縁膜の積層膜とすることができる。 As shown in FIG. 1, an insulating film (interlayer insulating film) IL4 is formed on the insulating film IL3 in which the wiring M2 and the floating electrode FE are embedded. The insulating film IL4 can be a single-layer insulating film or a stacked film of a plurality of insulating films.

絶縁膜IL4には、配線用の溝とその溝に埋め込まれた配線M3とが形成されている。配線M3は、ダマシン技術(ここではデュアルダマシン技術)を用いて形成することができ、銅を主成分とする銅配線(ダマシン銅配線、埋込銅配線)とすることができる。配線M3は、配線層ML3の配線である。配線M3の底面は、絶縁膜IL4の厚みの途中に位置している。 In the insulating film IL4, a trench for wiring and a wiring M3 embedded in the trench are formed. The wiring M3 can be formed using a damascene technique (here, dual damascene technique), and can be a copper wiring (a damascene copper wiring or a buried copper wiring) containing copper as a main component. The wiring M3 is a wiring of the wiring layer ML3. The bottom surface of the wiring M3 is located in the middle of the thickness of the insulating film IL4.

配線M3は、配線M3と一体的に形成されたビア部V3を介して、配線M2と電気的に接続されている。すなわち、ビア部V3は、配線M3と配線M2との間に配置されており、ビア部V3の上面は、配線M3の下面と一体的に接続されており、ビア部V3の下面(底面)は配線M2の上面に接している。ビア部V3は配線M3と同じ導電膜により一体的に形成されており、デュアルダマシン技術により配線M3を形成する際に配線M3と一緒にビア部V3も形成される。 The wiring M3 is electrically connected to the wiring M2 through a via portion V3 formed integrally with the wiring M3. That is, the via portion V3 is disposed between the wiring M3 and the wiring M2, the upper surface of the via portion V3 is integrally connected to the lower surface of the wiring M3, and the lower surface (bottom surface) of the via portion V3 is It is in contact with the upper surface of the wiring M2. The via portion V3 is integrally formed of the same conductive film as the wiring M3. When the wiring M3 is formed by the dual damascene technique, the via portion V3 is also formed together with the wiring M3.

また、ビア部V3は、配線M3とは別工程で形成することもでき、その場合、ビア部V3はプラグPGと同様の工程により形成され、配線M3はシングルダマシン技術により形成され、ビア部V3の下面(底面)は配線M2の上面に接し、ビア部V3の上面は配線M3の下面に接することになる。 The via portion V3 can also be formed in a separate process from the wiring M3. In that case, the via portion V3 is formed by the same process as the plug PG, the wiring M3 is formed by a single damascene technique, and the via portion V3. The bottom surface (bottom surface) of the contact portion is in contact with the top surface of the wiring M2, and the top surface of the via portion V3 is in contact with the bottom surface of the wiring M3.

図1〜図5に示されるように、キャパシタ形成領域においては、上部電極UEが、配線M3と同層に同工程で形成されている。すなわち、配線M3と上部電極UEとは、同じ配線層ML3に形成されている。つまり、配線M3および上部電極UEは、配線M2および浮遊電極FEが形成された配線層ML2よりも1つ上層の配線層ML3に形成されている。このため、配線M3と上部電極UEとは、どちらもダマシン技術を用いて同工程で形成されており、絶縁膜IL4に埋め込まれている。具体的には、配線M3と上部電極UEとは、それぞれ、絶縁膜IL4に形成された溝(または開口部)に埋め込まれている。上部電極UEと配線M3とは、同じ導電材料からなる。上部電極UEの底面(下面)は、絶縁膜IL4の厚みの途中に位置している。上部電極UEの底面(下面)の高さ位置と、配線M3の底面(下面)の高さ位置とは、概ね同じである。なお、絶縁膜に溝を形成する際には、その平面寸法が大きいほど溝の深さは深くなるため、上部電極UEの寸法(辺の寸法)が配線M3の幅よりも大きいことを反映して、上部電極UEの底面の高さ位置が、配線M3の底面の高さ位置より低くなる場合もある。また、上部電極UEには、配線M3が一体的に接続されており、この上部電極UEに接続された配線M3などを介して、上部電極UEに所定の電位が供給できるようになっている。 As shown in FIGS. 1 to 5, in the capacitor formation region, the upper electrode UE is formed in the same layer as the wiring M3 in the same process. That is, the wiring M3 and the upper electrode UE are formed in the same wiring layer ML3. That is, the wiring M3 and the upper electrode UE are formed in the wiring layer ML3 that is one layer higher than the wiring layer ML2 in which the wiring M2 and the floating electrode FE are formed. For this reason, the wiring M3 and the upper electrode UE are both formed in the same process using the damascene technique, and are embedded in the insulating film IL4. Specifically, the wiring M3 and the upper electrode UE are each embedded in a groove (or an opening) formed in the insulating film IL4. The upper electrode UE and the wiring M3 are made of the same conductive material. The bottom surface (lower surface) of the upper electrode UE is located in the middle of the thickness of the insulating film IL4. The height position of the bottom surface (lower surface) of the upper electrode UE and the height position of the bottom surface (lower surface) of the wiring M3 are substantially the same. Note that, when the trench is formed in the insulating film, the depth of the trench becomes deeper as the planar dimension is larger, which reflects that the dimension (side dimension) of the upper electrode UE is larger than the width of the wiring M3. Thus, the height position of the bottom surface of the upper electrode UE may be lower than the height position of the bottom surface of the wiring M3. Further, a wiring M3 is integrally connected to the upper electrode UE, and a predetermined potential can be supplied to the upper electrode UE through the wiring M3 connected to the upper electrode UE.

キャパシタ形成領域において、下部電極LEの上方に浮遊電極FEが配置され、浮遊電極FEの上方に上部電極UEが配置されている。上部電極UEと浮遊電極FEとは、導体では接続されていない。すなわち、上部電極UEと浮遊電極FEとの間には、直流電流は流れないようになっている。また、下部電極LEと浮遊電極FEとは、導体では接続されていない。すなわち、下部電極LEと浮遊電極FEとの間には、直流電流は流れないようになっている。また、上部電極UEと下部電極LEとは、導体では接続されていない。すなわち、上部電極UEと下部電極LEとの間には、直流電流は流れないようになっている。このため、上部電極UEと浮遊電極FEとの間には、上部電極UEと浮遊電極FEとを電気的に接続するビア部V3は配置されておらず、また、下部電極LEと浮遊電極FEとの間には、下部電極LEと浮遊電極FEとを電気的に接続するビア部V2は配置されていない。 In the capacitor formation region, the floating electrode FE is disposed above the lower electrode LE, and the upper electrode UE is disposed above the floating electrode FE. The upper electrode UE and the floating electrode FE are not connected by a conductor. That is, no direct current flows between the upper electrode UE and the floating electrode FE. Further, the lower electrode LE and the floating electrode FE are not connected by a conductor. That is, no direct current flows between the lower electrode LE and the floating electrode FE. Further, the upper electrode UE and the lower electrode LE are not connected by a conductor. That is, no direct current flows between the upper electrode UE and the lower electrode LE. For this reason, the via portion V3 that electrically connects the upper electrode UE and the floating electrode FE is not disposed between the upper electrode UE and the floating electrode FE, and the lower electrode LE and the floating electrode FE Between these, the via portion V2 that electrically connects the lower electrode LE and the floating electrode FE is not disposed.

なお、本願において、導体からなる複数の部材(電極または配線などに対応)の接続関係をいうときに、「導体では接続されていない」または「導体では繋がっていない」と表現するときは、導体でつながる導電経路が部材間に形成されていないことを意味している。 In this application, when referring to the connection relationship of a plurality of members made of conductors (corresponding to electrodes or wirings), when expressing as “not connected by a conductor” or “not connected by a conductor” This means that the conductive path connected by is not formed between the members.

下部電極LEと、上部電極UEと、下部電極LEと上部電極UEとの間の絶縁膜IL3,IL4とにより、容量素子(キャパシタ)C1が形成されている。下部電極LEは、容量素子C1の一方の電極であり、上部電極UEは、容量素子C1の他方の電極であり、下部電極LEと上部電極UEとの間に介在する絶縁膜IL3,IL4が、容量素子C1の容量絶縁膜(誘電体膜)として機能する。容量素子C1は、MIM(Metal Insulator Metal)型の容量素子である。 A capacitive element (capacitor) C1 is formed by the lower electrode LE, the upper electrode UE, and the insulating films IL3 and IL4 between the lower electrode LE and the upper electrode UE. The lower electrode LE is one electrode of the capacitive element C1, the upper electrode UE is the other electrode of the capacitive element C1, and the insulating films IL3 and IL4 interposed between the lower electrode LE and the upper electrode UE include It functions as a capacitive insulating film (dielectric film) of the capacitive element C1. The capacitive element C1 is a MIM (Metal Insulator Metal) type capacitive element.

但し、容量素子C1においては、下部電極LEと上部電極UEとの間に、浮遊電極FEが配置されている。このため、下部電極LEと浮遊電極FEとの間に介在する絶縁膜IL3と、上部電極UEと浮遊電極FEとの間に介在する絶縁膜IL4とが、容量素子C1の容量絶縁膜(誘電体膜)として機能することになる。キャパシタ形成領域に、下部電極LEと浮遊電極FEと上部電極UEとが下から順に形成されることで、容量素子C1を形成することができる。 However, in the capacitive element C1, the floating electrode FE is disposed between the lower electrode LE and the upper electrode UE. For this reason, the insulating film IL3 interposed between the lower electrode LE and the floating electrode FE and the insulating film IL4 interposed between the upper electrode UE and the floating electrode FE form a capacitive insulating film (dielectric material) of the capacitive element C1. Film). The capacitor element C1 can be formed by forming the lower electrode LE, the floating electrode FE, and the upper electrode UE in this order from the bottom in the capacitor formation region.

下部電極LEは、図5に示されるように、例えば矩形状の平面形状とすることができ、また、浮遊電極FEは、図4に示されるように、例えば矩形状の平面形状とすることができ、上部電極UEは、図3に示されるように、例えば矩形状の平面形状とすることができる。また、下部電極LEと上部電極UEとで、平面形状および平面寸法(平面積)を同じにして、平面視で下部電極LEと上部電極UEとが重なる(一致する)ようにすることもでき、そうすることで、容量素子C1の占有面積を抑えながら容量素子C1の容量値を増やすことができる。 As shown in FIG. 5, the lower electrode LE can have a rectangular planar shape, for example, and the floating electrode FE can have a rectangular planar shape as shown in FIG. In addition, the upper electrode UE can have, for example, a rectangular planar shape as shown in FIG. In addition, the lower electrode LE and the upper electrode UE can have the same planar shape and planar dimensions (planar area) so that the lower electrode LE and the upper electrode UE overlap (match) in plan view. By doing so, the capacitance value of the capacitive element C1 can be increased while suppressing the area occupied by the capacitive element C1.

なお、「平面視」または「平面的に見て」と言うときは、半導体基板SBの主面に平行な平面で見た場合を言うものとする。 Note that “plan view” or “view in plan” refers to the case of viewing in a plane parallel to the main surface of the semiconductor substrate SB.

図1に示されるように、配線M3および上部電極UEが埋め込まれた絶縁膜IL4上には、絶縁膜(層間絶縁膜)IL5が形成されている。絶縁膜IL5は、単層の絶縁膜、あるいは、複数の絶縁膜の積層膜とすることができる。 As shown in FIG. 1, an insulating film (interlayer insulating film) IL5 is formed on the insulating film IL4 in which the wiring M3 and the upper electrode UE are embedded. The insulating film IL5 can be a single-layer insulating film or a stacked film of a plurality of insulating films.

絶縁膜IL5には、配線用の溝とその溝に埋め込まれた配線M4とが形成されている。配線M4は、ダマシン技術(ここではデュアルダマシン技術)を用いて形成することができ、銅を主成分とする銅配線(ダマシン銅配線、埋込銅配線)とすることができる。配線M4は、配線層ML4の配線である。配線M4の底面(下面)は、絶縁膜IL5の厚みの途中に位置している。 In the insulating film IL5, a trench for wiring and a wiring M4 embedded in the trench are formed. The wiring M4 can be formed using a damascene technique (here, dual damascene technique), and can be a copper wiring (a damascene copper wiring or a buried copper wiring) containing copper as a main component. The wiring M4 is a wiring of the wiring layer ML4. The bottom surface (lower surface) of the wiring M4 is located in the middle of the thickness of the insulating film IL5.

配線M4は、配線M4と一体的に形成されたビア部V4を介して、配線M3と電気的に接続されている。すなわち、ビア部V4は、配線M4と配線M3との間に配置されており、ビア部V4の上面は、配線M4の下面と一体的に接続されており、ビア部V4の下面(底面)は配線M3の上面に接している。ビア部V4は配線M4と同じ導電膜により一体的に形成されており、デュアルダマシン技術により配線M4を形成する際に配線M4と一緒にビア部V4も形成される。 The wiring M4 is electrically connected to the wiring M3 through a via portion V4 formed integrally with the wiring M4. That is, the via portion V4 is disposed between the wiring M4 and the wiring M3, the upper surface of the via portion V4 is integrally connected to the lower surface of the wiring M4, and the lower surface (bottom surface) of the via portion V4 is It is in contact with the upper surface of the wiring M3. The via portion V4 is integrally formed of the same conductive film as the wiring M4. When the wiring M4 is formed by the dual damascene technique, the via portion V4 is also formed together with the wiring M4.

また、ビア部V4は、配線M4とは別工程で形成することもでき、その場合、ビア部V4はプラグPGと同様の工程により形成され、配線M4はシングルダマシン技術により形成され、ビア部V4の下面(底面)は配線M3の上面に接し、ビア部V4の上面は配線M4の下面に接することになる。 The via portion V4 can also be formed in a separate process from the wiring M4. In that case, the via portion V4 is formed by the same process as the plug PG, the wiring M4 is formed by a single damascene technique, and the via portion V4. The lower surface (bottom surface) of the contact portion contacts the upper surface of the wiring M3, and the upper surface of the via portion V4 contacts the lower surface of the wiring M4.

配線M4が埋め込まれた絶縁膜IL5上には、絶縁膜(層間絶縁膜)IL6が形成されている。絶縁膜IL6は、単層の絶縁膜、あるいは、複数の絶縁膜の積層膜とすることができる。 An insulating film (interlayer insulating film) IL6 is formed over the insulating film IL5 in which the wiring M4 is embedded. The insulating film IL6 can be a single-layer insulating film or a stacked film of a plurality of insulating films.

絶縁膜IL6には、配線用の溝とその溝に埋め込まれた配線M5とが形成されている。配線M5は、ダマシン技術(ここではデュアルダマシン技術)を用いて形成することができ、銅を主成分とする銅配線(ダマシン銅配線、埋込銅配線)とすることができる。配線M5は、配線層ML5の配線である。配線M5の底面(下面)は、絶縁膜IL6の厚みの途中に位置している。 In the insulating film IL6, a trench for wiring and a wiring M5 embedded in the trench are formed. The wiring M5 can be formed using damascene technology (here, dual damascene technology) and can be copper wiring (damascene copper wiring, embedded copper wiring) containing copper as a main component. The wiring M5 is a wiring of the wiring layer ML5. The bottom surface (lower surface) of the wiring M5 is located in the middle of the thickness of the insulating film IL6.

配線M5は、配線M5と一体的に形成されたビア部V5を介して、配線M4と電気的に接続されている。すなわち、ビア部V5は、配線M5と配線M4との間に配置されており、ビア部V5の上面は、配線M5の下面と一体的に接続されており、ビア部V5の下面(底面)は配線M4の上面に接している。ビア部V5は配線M5と同じ導電膜により一体的に形成されており、デュアルダマシン技術により配線M5を形成する際に配線M5と一緒にビア部V5も形成される。 The wiring M5 is electrically connected to the wiring M4 through a via portion V5 formed integrally with the wiring M5. That is, the via portion V5 is disposed between the wiring M5 and the wiring M4, the upper surface of the via portion V5 is integrally connected to the lower surface of the wiring M5, and the lower surface (bottom surface) of the via portion V5 is It is in contact with the upper surface of the wiring M4. The via portion V5 is integrally formed of the same conductive film as the wiring M5. When the wiring M5 is formed by the dual damascene technique, the via portion V5 is also formed together with the wiring M5.

また、ビア部V5は、配線M5とは別工程で形成することもでき、その場合、ビア部V5はプラグPGと同様の工程により形成され、配線M5はシングルダマシン技術により形成され、ビア部V5の下面(底面)は配線M4の上面に接し、ビア部V5の上面は配線M5の下面に接することになる。 The via portion V5 can also be formed in a separate process from the wiring M5. In that case, the via portion V5 is formed by the same process as the plug PG, the wiring M5 is formed by a single damascene technique, and the via portion V5. The bottom surface (bottom surface) of the contact portion contacts the top surface of the wiring M4, and the top surface of the via portion V5 contacts the bottom surface of the wiring M5.

配線M5が埋め込まれた絶縁膜IL6上に、必要に応じて更に上層の絶縁膜、配線、ボンディングパッドおよび最上層の保護膜などが形成されるが、ここではその図示および説明は省略する。 On the insulating film IL6 in which the wiring M5 is embedded, an upper insulating film, wiring, bonding pad, uppermost protective film, and the like are further formed as necessary, but illustration and description thereof are omitted here.

本実施の形態では、下部電極LEが配線M1と同層に形成され、浮遊電極FEが配線M2と同層に形成され、上部電極UEが配線M3と同層に形成されている。他の形態として、下部電極LEを配線M2と同層に形成し、浮遊電極FEを配線M3と同層に形成し、上部電極UEを配線M4と同層に形成することもでき、また、更に他の形態として、下部電極LEを配線M3と同層に形成し、浮遊電極FEを配線M4と同層に形成し、上部電極UEを配線M5と同層に形成することもできる。つまり、下部電極LEを形成する配線層は変更可能であるが、下部電極LEがいずれの配線層に形成された場合も、浮遊電極FEは、下部電極LEが形成された配線層よりも1つ上層の配線層に形成し、上部電極UEは、浮遊電極FEが形成された配線層よりも1つ上層の配線層に形成する。また、配線M1〜M5だけでなく配線M5よりも上層の配線も形成している場合(すなわち配線層が6層以上の場合)は、下部電極LEを配線M3よりも上層の配線層に形成することも可能であり、その場合においても、浮遊電極FEは、下部電極LEが形成された配線層よりも1つ上層の配線層に形成し、上部電極UEは、浮遊電極FEが形成された配線層よりも1つ上層の配線層に形成する。 In the present embodiment, the lower electrode LE is formed in the same layer as the wiring M1, the floating electrode FE is formed in the same layer as the wiring M2, and the upper electrode UE is formed in the same layer as the wiring M3. As another form, the lower electrode LE may be formed in the same layer as the wiring M2, the floating electrode FE may be formed in the same layer as the wiring M3, and the upper electrode UE may be formed in the same layer as the wiring M4. As another form, the lower electrode LE may be formed in the same layer as the wiring M3, the floating electrode FE may be formed in the same layer as the wiring M4, and the upper electrode UE may be formed in the same layer as the wiring M5. That is, the wiring layer for forming the lower electrode LE can be changed, but when the lower electrode LE is formed in any wiring layer, the floating electrode FE is one more than the wiring layer in which the lower electrode LE is formed. The upper electrode UE is formed in a wiring layer one layer higher than the wiring layer in which the floating electrode FE is formed. Further, when not only the wirings M1 to M5 but also wirings higher than the wiring M5 are formed (that is, when the wiring layer has six or more layers), the lower electrode LE is formed in a wiring layer above the wiring M3. In this case as well, the floating electrode FE is formed in a wiring layer one layer higher than the wiring layer in which the lower electrode LE is formed, and the upper electrode UE is a wiring in which the floating electrode FE is formed. The wiring layer is formed one layer above the layer.

つまり、半導体基板SBの上方には、複数の配線層を含む配線構造(多層配線構造)が形成されるが、本実施の形態では、その複数の配線層のうちの連続する任意の3層の配線層に、下部電極LEと浮遊電極FEと上部電極UEとを形成すればよい。このとき、浮遊電極FEは、下部電極LEが形成された配線層よりも1つ上層の配線層に形成し、上部電極UEは、浮遊電極FEが形成された配線層よりも1つ上層の配線層に形成する必要がある。本実施の形態では、3層の配線層に下部電極LEと浮遊電極FEと上部電極UEとを形成するため、半導体基板SBの上方に形成する配線構造(多層配線構造)は、少なくとも3層の配線層を含んでいる必要がある。 That is, a wiring structure (multilayer wiring structure) including a plurality of wiring layers is formed above the semiconductor substrate SB. In this embodiment, any three consecutive layers of the plurality of wiring layers are formed. The lower electrode LE, the floating electrode FE, and the upper electrode UE may be formed in the wiring layer. At this time, the floating electrode FE is formed in a wiring layer one layer higher than the wiring layer in which the lower electrode LE is formed, and the upper electrode UE is a wiring layer one layer higher than the wiring layer in which the floating electrode FE is formed. It is necessary to form a layer. In the present embodiment, since the lower electrode LE, the floating electrode FE, and the upper electrode UE are formed in the three wiring layers, the wiring structure (multilayer wiring structure) formed above the semiconductor substrate SB has at least three layers. It is necessary to include a wiring layer.

<検討例について>

次に、本発明者が検討した検討例について説明する。

<About study example>

Next, a study example studied by the present inventors will be described.

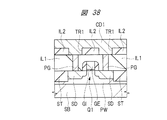

図6は、本発明者が検討した第1検討例の半導体装置の要部断面図であり、図7は、本発明者が検討した第2検討例の半導体装置の要部断面図であり、図8は、本実施の形態の半導体装置の要部断面図である。図6〜図8には、キャパシタ形成領域における、絶縁膜IL2,IL3,IL4およびそれに埋め込まれた電極(容量素子用の電極)が示されており、絶縁膜IL1およびそれよりも下層の構造と、絶縁膜IL5およびそれよりも上層の構造については、図示を省略している。すなわち、上記図1において、キャパシタ形成領域における絶縁膜IL2,IL3,IL4およびそこに埋め込まれた電極(下部電極LEと浮遊電極FEと上部電極UE)を抜き出して示したものが、図8に対応しており、図6および図7は、第1検討例および第2検討例の場合の、この図8に相当する領域が示されたものである。 FIG. 6 is a cross-sectional view of the main part of the semiconductor device of the first study example studied by the present inventors, and FIG. 7 is a cross-sectional view of the main part of the semiconductor device of the second study example studied by the present inventor. FIG. 8 is a fragmentary cross-sectional view of the semiconductor device of the present embodiment. 6 to 8 show the insulating films IL2, IL3, and IL4 and electrodes (capacitance element electrodes) embedded in the capacitor formation region. The insulating film IL1 and the structure below it are shown in FIGS. The illustration of the insulating film IL5 and the structure above it is omitted. That is, in FIG. 1, the insulating films IL2, IL3, and IL4 in the capacitor formation region and the electrodes embedded therein (lower electrode LE, floating electrode FE, and upper electrode UE) are extracted and shown in FIG. FIG. 6 and FIG. 7 show regions corresponding to FIG. 8 in the case of the first study example and the second study example.

図6に示される第1検討例では、キャパシタ形成領域において、電極DE1が、上記配線M1と同層に同工程で形成され、また、電極DE2が、上記配線M2と同層に同工程で形成され、また、電極DE3が、上記配線M3と同層に同工程で形成されている。このため、電極DE1は、絶縁膜IL2に形成された溝(開口部)に埋め込まれており、電極DE2は、絶縁膜IL3に形成された溝(開口部)に埋め込まれており、電極DE3は、絶縁膜IL4に形成された溝(開口部)に埋め込まれている。 In the first study example shown in FIG. 6, in the capacitor formation region, the electrode DE1 is formed in the same layer as the wiring M1 in the same process, and the electrode DE2 is formed in the same layer as the wiring M2 in the same process. In addition, the electrode DE3 is formed in the same layer as the wiring M3 in the same process. Therefore, the electrode DE1 is embedded in a groove (opening) formed in the insulating film IL2, the electrode DE2 is embedded in a groove (opening) formed in the insulating film IL3, and the electrode DE3 is And embedded in a groove (opening) formed in the insulating film IL4.

電極DE2の底面は、絶縁膜IL3の厚みの途中に位置しており、電極DE1と電極DE2との間には絶縁膜IL3(電極DE2の底面よりも下に位置する部分の絶縁膜IL3)が介在している。また、電極DE3の底面は、絶縁膜IL4の厚みの途中に位置しており、電極DE2と電極DE3との間には絶縁膜IL4(電極DE3の底面よりも下に位置する部分の絶縁膜IL4)が介在している。 The bottom surface of the electrode DE2 is located in the middle of the thickness of the insulating film IL3, and the insulating film IL3 (the insulating film IL3 in a portion located below the bottom surface of the electrode DE2) is between the electrode DE1 and the electrode DE2. Intervene. The bottom surface of the electrode DE3 is located in the middle of the thickness of the insulating film IL4. Between the electrode DE2 and the electrode DE3, the insulating film IL4 (the insulating film IL4 in a portion positioned below the bottom surface of the electrode DE3) is provided. ) Is present.

電極DE2と電極DE1とは、導体では接続されておらず、また、電極DE2と電極DE3とは、導体では接続されていない。しかしながら、電極DE3と電極DE1とは、導体で接続されている。すなわち、図示はしないけれども、電極DE3と電極DE1とは、電極DE3と一体的に形成された上記配線M3と、電極DE1と一体的に接続された上記配線M1と、上記配線M2と、上記ビア部V2,V3とを介して、電気的に接続されている。このため、電極DE3と電極DE1とには、同電位が供給されるようになっている。 The electrode DE2 and the electrode DE1 are not connected by a conductor, and the electrode DE2 and the electrode DE3 are not connected by a conductor. However, the electrode DE3 and the electrode DE1 are connected by a conductor. That is, although not shown, the electrode DE3 and the electrode DE1 are the wiring M3 formed integrally with the electrode DE3, the wiring M1 connected integrally with the electrode DE1, the wiring M2, and the via. They are electrically connected via the parts V2 and V3. For this reason, the same potential is supplied to the electrode DE3 and the electrode DE1.

図6の第1検討例の場合、電極DE1と、電極DE2と、電極DE3と、電極DE1と電極DE2との間の絶縁膜IL3と、電極DE3と電極DE2との間の絶縁膜IL4とにより、容量素子C101が形成されている。電極DE2が、容量素子C101の一方の電極であり、電極DE1と電極DE3とが、容量素子C101の他方の電極であり、電極DE1と電極DE2との間に介在する絶縁膜IL3と、電極DE3と電極DE2との間に介在する絶縁膜IL4とが、容量素子C101の容量絶縁膜(誘電体膜)として機能する。 In the case of the first study example of FIG. 6, the electrode DE1, the electrode DE2, the electrode DE3, the insulating film IL3 between the electrode DE1 and the electrode DE2, and the insulating film IL4 between the electrode DE3 and the electrode DE2. The capacitor element C101 is formed. The electrode DE2 is one electrode of the capacitive element C101, the electrode DE1 and the electrode DE3 are the other electrode of the capacitive element C101, the insulating film IL3 interposed between the electrode DE1 and the electrode DE2, and the electrode DE3 And the insulating film IL4 interposed between the electrode DE2 function as a capacitive insulating film (dielectric film) of the capacitive element C101.

図6の第1検討例の場合、容量素子C101の容量値を大きくしやすい。しかしながら、本発明者の検討によれば、次のような課題が生じることが分かった。 In the case of the first study example in FIG. 6, the capacitance value of the capacitive element C101 can be easily increased. However, according to the study of the present inventors, it has been found that the following problems arise.

すなわち、近年、半導体装置の小型化や薄型化が進んでおり、それに伴って、多層配線構造を形成するための層間絶縁膜の厚みが薄くなってきている。層間絶縁膜の厚みが薄くなることは、図6の第1検討例の場合、絶縁膜IL3,IL4の各厚みが薄くなることに相当している。 That is, in recent years, semiconductor devices have been reduced in size and thickness, and accordingly, the thickness of an interlayer insulating film for forming a multilayer wiring structure has been reduced. The reduction in the thickness of the interlayer insulating film corresponds to the reduction in the thickness of each of the insulating films IL3 and IL4 in the first study example of FIG.

容量素子においては、一方の電極と他方の電極とに異電位を印加することで、一方の電極と他方の電極との間に電位差を生じさせて、容量素子に電荷を蓄積する。すなわち、容量素子においては、一方の電極に対して低電圧を印加し、それよりも高電圧を他方の電極に対して印加することで、容量素子に電荷を蓄積する。 In a capacitor element, by applying different potentials to one electrode and the other electrode, a potential difference is generated between one electrode and the other electrode, and electric charge is accumulated in the capacitor element. That is, in a capacitor element, a low voltage is applied to one electrode, and a higher voltage than that is applied to the other electrode, whereby charges are accumulated in the capacitor element.

図6の第1検討例の場合、容量素子C101に電荷を蓄積する際には、電極DE2に低電圧を印加し、それよりも高電圧を電極DE1および電極DE3に印加するか、あるいは、低電圧を電極DE1および電極DE3に印加し、それよりも高電圧を電極DE2に印加することになる。このとき、電極DE1と電極DE2との間と電極DE3と電極DE2との間には、所定の電位差(電極DE2に印加した電圧と電極DE1,DE3に印加した電圧との電位差)が生じることになる。このため、絶縁膜IL3,IL4の厚みが薄くなると、電極DE1と電極DE2との間に介在する絶縁膜IL3の厚みと、電極DE3と電極DE2との間に介在する絶縁膜IL4の厚みとが薄くなることに繋がるため、容量素子C101の耐圧やTDDB(Time Dependent Dielectric Breakdown)寿命が低下することになる。また、電極DE1,DE3と電極DE2との間に印加する電圧が高い場合、例えば12V以上の場合などには、電極DE1,DE3と電極DE2との間に介在する絶縁膜の厚みが薄いと、耐圧やTDDB寿命を確保しづらくなる。 In the case of the first study example of FIG. 6, when accumulating charges in the capacitive element C101, a low voltage is applied to the electrode DE2, and a higher voltage is applied to the electrodes DE1 and DE3, or a low voltage is applied. A voltage is applied to the electrode DE1 and the electrode DE3, and a higher voltage is applied to the electrode DE2. At this time, a predetermined potential difference (potential difference between the voltage applied to the electrode DE2 and the voltage applied to the electrodes DE1 and DE3) is generated between the electrode DE1 and the electrode DE2 and between the electrode DE3 and the electrode DE2. Become. Therefore, when the thickness of the insulating films IL3 and IL4 is reduced, the thickness of the insulating film IL3 interposed between the electrode DE1 and the electrode DE2 and the thickness of the insulating film IL4 interposed between the electrode DE3 and the electrode DE2 are reduced. This leads to a reduction in thickness, and thus the withstand voltage and TDDB (Time Dependent Dielectric Breakdown) life of the capacitive element C101 are reduced. In addition, when the voltage applied between the electrodes DE1, DE3 and DE2 is high, for example, when the voltage is 12 V or more, the insulating film interposed between the electrodes DE1, DE3 and the electrode DE2 is thin. It is difficult to ensure a breakdown voltage and a TDDB life.

そこで、容量素子の耐圧を向上させるために、図7の第2検討例を適用することが考えられる。 Therefore, in order to improve the breakdown voltage of the capacitive element, it is conceivable to apply the second study example of FIG.

図7に示される第2検討例では、キャパシタ形成領域において、下部電極LE201が、上記配線M1と同層に同工程で形成され、また、上部電極UE201が、上記配線M3と同層に同工程で形成されている。このため、下部電極LE201は、絶縁膜IL2に形成された溝(開口部)に埋め込まれており、上部電極UE201は、絶縁膜IL4に形成された溝(開口部)に埋め込まれている。上部電極UE201の底面(下面)は、絶縁膜IL4の厚みの途中に位置しており、下部電極LE201と上部電極UE201との間には、絶縁膜IL4(上部電極UE201の底面よりも下に位置する部分の絶縁膜IL4)と絶縁膜IL3(絶縁膜IL3の全厚み分)とが介在している。下部電極LE201と上部電極UE201とは、導体では接続されていない。 In the second study example shown in FIG. 7, in the capacitor formation region, the lower electrode LE201 is formed in the same layer as the wiring M1, and the upper electrode UE201 is formed in the same layer as the wiring M3. It is formed with. For this reason, the lower electrode LE201 is embedded in a groove (opening) formed in the insulating film IL2, and the upper electrode UE201 is embedded in a groove (opening) formed in the insulating film IL4. The bottom surface (lower surface) of the upper electrode UE201 is located in the middle of the thickness of the insulating film IL4, and the insulating film IL4 (lower than the bottom surface of the upper electrode UE201) is positioned between the lower electrode LE201 and the upper electrode UE201. Insulating film IL4) and insulating film IL3 (for the entire thickness of insulating film IL3) are interposed. The lower electrode LE201 and the upper electrode UE201 are not connected by a conductor.

図7の第2検討例の場合、下部電極LE201と、上部電極UE201と、下部電極LE201と上部電極UE201との間の絶縁膜IL3,IL4とにより、容量素子C201が形成されている。下部電極LE201が、容量素子C201の一方の電極であり、上部電極UE201が、容量素子C201の他方の電極であり、下部電極LE201と上部電極UE201との間に介在する絶縁膜IL3,IL4が、容量素子C201の容量絶縁膜(誘電体膜)として機能する。 In the case of the second study example in FIG. 7, the capacitive element C201 is formed by the lower electrode LE201, the upper electrode UE201, and the insulating films IL3 and IL4 between the lower electrode LE201 and the upper electrode UE201. The lower electrode LE201 is one electrode of the capacitive element C201, the upper electrode UE201 is the other electrode of the capacitive element C201, and the insulating films IL3 and IL4 interposed between the lower electrode LE201 and the upper electrode UE201 are It functions as a capacitive insulating film (dielectric film) of the capacitive element C201.

図7の第2検討例の場合、容量素子C201の電極を、上記配線M1と同層の下部電極LE201と、上記配線M3と同層の上部電極UE201とにより構成している。このため、図6の第1検討例の場合に比べて、図7の第2検討例の場合は、容量素子の電極の間隔が大きいため、容量素子の耐圧やTDDB寿命を向上させることができる。 In the case of the second study example of FIG. 7, the electrode of the capacitive element C201 is constituted by the lower electrode LE201 in the same layer as the wiring M1 and the upper electrode UE201 in the same layer as the wiring M3. For this reason, in the case of the second study example in FIG. 7, the spacing between the electrodes of the capacitor element is larger than in the case of the first study example in FIG. 6, so that the breakdown voltage and the TDDB life of the capacitor element can be improved. .

すなわち、図6の第1検討例の場合は、容量素子の電極の間隔は、電極DE1と電極DE2との間の間隔(距離)L101と、電極DE2と電極DE3との間の間隔(距離)L102とに対応している。この電極DE1と電極DE2との間の間隔L101は、配線層ML1と配線層ML2との間の間隔により規定され、電極DE2と電極DE3との間の間隔L102は、配線層ML2と配線層ML3との間の間隔により規定されることになる。一方、図7の第2検討例の場合は、容量素子の電極の間隔は、下部電極LE201と上部電極UE201との間の間隔(距離)L201に対応しているが、この下部電極LE201と上部電極UE201との間の間隔L201は、配線層ML1と配線層ML3との間の間隔により規定されることになる。このため、図7の第2検討例における下部電極LE201と上部電極UE201との間の間隔L201は、図6の第1検討例における電極DE1と電極DE2との間の間隔L101や電極DE2と電極DE3との間の間隔L102よりも大きくなる(すなわちL201>L101かつL201>L102)。容量素子における高電位が印加される電極と低電位が印加される電極との間の間隔が大きくなるほど、容量素子の耐圧やTDDB寿命は向上する。このため、図6の第1検討例の場合に比べて、図7の第2検討例の場合の方が、容量素子の電極の間隔が大きいことで、容量素子の耐圧やTDDB寿命を向上させることができる。 That is, in the case of the first study example of FIG. 6, the distance between the electrodes of the capacitive element is the distance (distance) L101 between the electrode DE1 and the electrode DE2, and the distance (distance) between the electrode DE2 and the electrode DE3. Corresponding to L102. The distance L101 between the electrode DE1 and the electrode DE2 is defined by the distance between the wiring layer ML1 and the wiring layer ML2, and the distance L102 between the electrode DE2 and the electrode DE3 is the wiring layer ML2 and the wiring layer ML3. Will be defined by the interval between. On the other hand, in the second study example of FIG. 7, the distance between the electrodes of the capacitive element corresponds to the distance (distance) L201 between the lower electrode LE201 and the upper electrode UE201. The distance L201 between the electrode UE201 is defined by the distance between the wiring layer ML1 and the wiring layer ML3. Therefore, the distance L201 between the lower electrode LE201 and the upper electrode UE201 in the second study example of FIG. 7 is the distance L101 between the electrode DE1 and the electrode DE2 in FIG. It becomes larger than the distance L102 between DE3 (that is, L201> L101 and L201> L102). As the distance between the electrode to which the high potential is applied and the electrode to which the low potential is applied in the capacitor is increased, the withstand voltage and the TDDB life of the capacitor are improved. For this reason, compared with the case of the first study example of FIG. 6, the case of the second study example of FIG. 7 improves the withstand voltage and the TDDB life of the capacitor element because the gap between the electrodes of the capacitor element is larger. be able to.

しかしながら、図7の第2検討例の場合は、下部電極LE201と上部電極UE201との間の間隔L201が大きくなった分、容量素子C201の容量値が小さくなってしまう。すなわち、図7の第2検討例の場合は、下部電極LE201と上部電極UE201との間に介在する絶縁膜IL3,IL4が、容量素子C201の容量絶縁膜として機能し、下部電極LE201と上部電極UE201との間の間隔L201が、容量絶縁膜の厚みに等しくなる。このため、図7の第2検討例の場合は、容量絶縁膜の厚みは、配線層ML1と配線層ML3との間の間隔により規定されることになる。従って、図7の第2検討例の場合は、容量素子C201において、下部電極LE201と上部電極UE201との間の間隔L201が大きく、容量絶縁膜の厚みが厚いことで、容量素子C201の容量値が小さくなってしまう。容量素子C201の容量値を確保するためには、下部電極LE201および上部電極UE201の面積を増大させることが必要になるため、半導体装置において、容量素子C201を形成するのに必要な面積の増大を招き、半導体装置の面積の増大を招いてしまう。これは、半導体装置の小型化(小面積化)に不利となる。 However, in the case of the second study example in FIG. 7, the capacitance value of the capacitive element C201 becomes smaller by the increase in the distance L201 between the lower electrode LE201 and the upper electrode UE201. That is, in the case of the second study example of FIG. 7, the insulating films IL3 and IL4 interposed between the lower electrode LE201 and the upper electrode UE201 function as a capacitive insulating film of the capacitive element C201, and the lower electrode LE201 and the upper electrode A distance L201 between the UE 201 and the UE 201 is equal to the thickness of the capacitive insulating film. For this reason, in the case of the second study example in FIG. 7, the thickness of the capacitive insulating film is defined by the distance between the wiring layer ML1 and the wiring layer ML3. Therefore, in the case of the second study example in FIG. 7, in the capacitive element C201, since the gap L201 between the lower electrode LE201 and the upper electrode UE201 is large and the capacitive insulating film is thick, the capacitance value of the capacitive element C201 is large. Will become smaller. In order to secure the capacitance value of the capacitive element C201, it is necessary to increase the areas of the lower electrode LE201 and the upper electrode UE201. Therefore, in the semiconductor device, the area required to form the capacitive element C201 is increased. This leads to an increase in the area of the semiconductor device. This is disadvantageous for downsizing (smaller area) of the semiconductor device.

<主要な特徴と効果について>

本実施の形態の半導体装置は、半導体基板SBと、半導体基板SB上に形成されかつ複数の配線層を含む配線構造(多層配線構造)と、その配線構造(多層配線構造)に形成された容量素子C1とを有する半導体装置であり、配線構造(多層配線構造)の複数の配線層は、第1の配線層と、第1の配線層よりも1つ上層の第2の配線層と、第2の配線層よりも1つ上層の第3の配線層とを含んでいる。そして、第1の配線層に容量素子C1の第1電極(ここでは下部電極LE)が形成され、第3の配線層に容量素子C1の第2電極(ここでは上部電極UE)が形成され、第2電極(上部電極UE)は第1電極(下部電極LE)の上方に配置されており、第2の配線層に、第1電極(下部電極LE)と第2電極(上部電極UE)との間に位置する浮遊電極FEが形成されている。

<Main features and effects>

The semiconductor device of this embodiment includes a semiconductor substrate SB, a wiring structure (multilayer wiring structure) formed on the semiconductor substrate SB and including a plurality of wiring layers, and a capacitance formed in the wiring structure (multilayer wiring structure). The plurality of wiring layers of the wiring structure (multilayer wiring structure) includes a first wiring layer, a second wiring layer that is one layer above the first wiring layer, And a third wiring layer that is one layer above the second wiring layer. Then, the first electrode (here, the lower electrode LE) of the capacitive element C1 is formed in the first wiring layer, and the second electrode (here, the upper electrode UE) of the capacitive element C1 is formed in the third wiring layer. The second electrode (upper electrode UE) is arranged above the first electrode (lower electrode LE), and the second wiring layer includes a first electrode (lower electrode LE), a second electrode (upper electrode UE), and A floating electrode FE located between the two is formed.

上記図6の第1検討例のように、ある配線層とそれよりも1つ上層の配線層とに、容量素子における異なる電位を印加する電極を配置した場合には、容量素子の耐圧やTDDB寿命が低下する虞がある。また、上記図7の第2検討例のように、ある配線層とそれよりも2つ上層の配線層とに、容量素子における異なる電位を印加する電極を配置すると、容量素子の耐圧やTDDB寿命を向上させることはできるが、容量素子の容量値が小さくなり、回路構成上必要とされる容量値を確保しにくくなってしまう。 As shown in the first study example of FIG. 6 described above, in the case where electrodes for applying different potentials in the capacitive element are arranged in a certain wiring layer and a wiring layer one layer above it, the breakdown voltage of the capacitive element and the TDDB Life may be reduced. Further, as shown in the second study example of FIG. 7 described above, when electrodes for applying different potentials in the capacitive element are arranged in a certain wiring layer and the wiring layer two layers above it, the breakdown voltage and TDDB life of the capacitive element are arranged. However, the capacitance value of the capacitive element becomes small, and it becomes difficult to secure the capacitance value required for the circuit configuration.

それに対して、本実施の形態では、半導体基板SB上に形成された複数の配線層のうちのいずれかの配線層に容量素子C1の下部電極LEを形成し、それよりも1つ上層の配線層に浮遊電極FEを形成し、それよりも1つ上層の配線層に容量素子C1の上部電極UEを形成している。具体的には、上記図1および図8に示されるように、配線M1と同層に(すなわち配線層ML1に)下部電極LEが形成され、配線M2と同層に(すなわち配線層ML1より1つ上層の配線層ML2に)浮遊電極FEが形成され、配線M3と同層に(すなわち配線層ML2より1つ上層の配線層ML3に)上部電極UEが形成されている。 On the other hand, in the present embodiment, the lower electrode LE of the capacitive element C1 is formed in any one of the plurality of wiring layers formed on the semiconductor substrate SB, and the wiring one layer higher than that is formed. The floating electrode FE is formed in the layer, and the upper electrode UE of the capacitive element C1 is formed in the wiring layer one layer higher than the floating electrode FE. Specifically, as shown in FIGS. 1 and 8, the lower electrode LE is formed in the same layer as the wiring M1 (that is, in the wiring layer ML1), and in the same layer as the wiring M2 (that is, 1 from the wiring layer ML1). The floating electrode FE is formed in the upper wiring layer ML2, and the upper electrode UE is formed in the same layer as the wiring M3 (that is, in the wiring layer ML3 one layer higher than the wiring layer ML2).

本実施の形態では、下部電極LEを形成した配線層(図8の場合は配線層ML1)よりも2つ上層の配線層(図8の場合は配線層ML3)に上部電極UEを形成しているため、上記図6の第1検討例の場合に比べて、容量素子の電極の間隔を大きくすることができるため、容量素子C1の耐圧やTDDB寿命を向上させることができる。 In the present embodiment, the upper electrode UE is formed in the wiring layer (wiring layer ML3 in the case of FIG. 8) two layers above the wiring layer (wiring layer ML1 in the case of FIG. 8) on which the lower electrode LE is formed. Therefore, as compared with the case of the first study example of FIG. 6, the interval between the electrodes of the capacitive element can be increased, so that the breakdown voltage and the TDDB life of the capacitive element C1 can be improved.

すなわち、図6の第1検討例の場合は、容量素子において異なる電位が印加される電極間に介在する絶縁膜(すなわち容量絶縁膜として機能する絶縁膜)の厚みは、電極DE1と電極DE2との間に介在する絶縁膜IL3の厚みか、あるいは、電極DE2と電極DE3との間に介在する絶縁膜IL4の厚みに対応している。それに対して、本実施の形態では、容量素子において異なる電位が印加される電極間に介在する絶縁膜(すなわち容量絶縁膜として機能する絶縁膜)の厚みは、下部電極LEと浮遊電極FEとの間に介在する絶縁膜IL3の厚みと、浮遊電極FEと上部電極UEとの間に介在する絶縁膜IL4の厚みとの合計となる。このため、上記図6の第1検討例の場合に比べて、本実施の形態では、容量素子において異なる電位が印加される電極間に介在する絶縁膜(すなわち容量絶縁膜として機能する絶縁膜)の厚みを、厚くすることができる。容量素子において異なる電位が印加される電極間に介在する絶縁膜(すなわち容量絶縁膜として機能する絶縁膜)の厚みが厚い方が、容量素子の耐圧は高くなり、また、容量素子のTDDB寿命も長くなる。従って、上記図6の第1検討例の場合に比べて、本実施の形態の方が、容量素子において異なる電位が印加される電極間に介在する絶縁膜(すなわち容量絶縁膜として機能する絶縁膜)の厚みが厚くなることで、容量素子の耐圧を高くすることができ、また、容量素子のTDDB寿命を長くすることができる。このため、容量素子を有する半導体装置の信頼性を向上することができる。 That is, in the case of the first study example in FIG. 6, the thickness of the insulating film interposed between the electrodes to which different potentials are applied in the capacitive element (that is, the insulating film functioning as the capacitive insulating film) is the same as that of the electrode DE1 and the electrode DE2. This corresponds to the thickness of the insulating film IL3 interposed between the electrodes DE2 and DE3, or the thickness of the insulating film IL4 interposed between the electrodes DE2 and DE3. On the other hand, in the present embodiment, the thickness of the insulating film interposed between the electrodes to which different potentials are applied in the capacitor element (that is, the insulating film functioning as the capacitor insulating film) is the same as that of the lower electrode LE and the floating electrode FE. This is the sum of the thickness of the insulating film IL3 interposed therebetween and the thickness of the insulating film IL4 interposed between the floating electrode FE and the upper electrode UE. For this reason, compared with the case of the first study example of FIG. 6 described above, in this embodiment, an insulating film interposed between electrodes to which different potentials are applied in the capacitor element (that is, an insulating film functioning as a capacitor insulating film). The thickness of can be increased. When the insulating film interposed between electrodes to which different potentials are applied in the capacitor element (that is, the insulating film functioning as a capacitor insulating film) is thicker, the withstand voltage of the capacitor element is higher, and the TDDB life of the capacitor element is also increased. become longer. Therefore, as compared with the case of the first study example in FIG. 6, the present embodiment has an insulating film interposed between electrodes to which different potentials are applied in the capacitive element (that is, an insulating film functioning as a capacitive insulating film). ) Is increased, the breakdown voltage of the capacitor can be increased, and the TDDB life of the capacitor can be increased. For this reason, the reliability of the semiconductor device having a capacitor can be improved.

また、本実施の形態では、下部電極LEを形成した配線層(図8の場合は配線層ML1)よりも2つ上層の配線層(図8の場合は配線層ML3)に上部電極UEを形成するとともに、下部電極LEを形成した配線層(図8の場合は配線層ML1)よりも1つ上層の配線層(図8の場合は配線層ML2)に浮遊電極FEを形成している。すなわち、下部電極LEを形成した配線層(図8の場合は配線層ML1)と上部電極UEを形成した配線層(図8の場合は配線層ML3)との間の配線層(図8の場合は配線層ML2)に浮遊電極FEを形成している。そして、この浮遊電極FEを、下部電極LEと上部電極UEとの間に配置している。本実施の形態では、浮遊電極FEを下部電極LEと上部電極UEとの間に配置したことで、浮遊電極FEを設けない上記図7の第2検討例の場合に比べて、容量素子C1の容量値を大きくすることができる。 In the present embodiment, the upper electrode UE is formed in the wiring layer (wiring layer ML3 in the case of FIG. 8) two layers above the wiring layer (wiring layer ML1 in the case of FIG. 8) on which the lower electrode LE is formed. At the same time, the floating electrode FE is formed in the wiring layer (wiring layer ML2 in the case of FIG. 8) one layer above the wiring layer (wiring layer ML1 in the case of FIG. 8) on which the lower electrode LE is formed. That is, the wiring layer (in the case of FIG. 8) between the wiring layer (in the case of FIG. 8 the wiring layer ML1) in which the lower electrode LE is formed and the wiring layer in which the upper electrode UE is formed (the wiring layer ML3 in FIG. 8). Forms a floating electrode FE in the wiring layer ML2). The floating electrode FE is disposed between the lower electrode LE and the upper electrode UE. In the present embodiment, since the floating electrode FE is disposed between the lower electrode LE and the upper electrode UE, the capacitance element C1 is compared with the second study example of FIG. 7 in which the floating electrode FE is not provided. The capacity value can be increased.

すなわち、図7の第2検討例の場合は、下部電極LE201と上部電極UE201との間の間隔L201(すなわち下部電極LE201の上面から上部電極UE201の下面までの距離)が、そのまま容量絶縁膜の厚みになるため、容量絶縁膜の厚みが厚いことで、容量素子C201の容量値が小さくなってしまう。それに対して、本実施の形態では、下部電極LEと上部電極UEとの間に浮遊電極FEを配置したことで、浮遊電極FEの厚みの分だけ、容量絶縁膜の実効的な厚みを小さくすることができる。 That is, in the case of the second study example in FIG. 7, the distance L201 between the lower electrode LE201 and the upper electrode UE201 (that is, the distance from the upper surface of the lower electrode LE201 to the lower surface of the upper electrode UE201) is the same as that of the capacitor insulating film. Since the thickness is increased, the capacitance value of the capacitive element C201 is reduced by increasing the thickness of the capacitive insulating film. On the other hand, in this embodiment, the floating electrode FE is disposed between the lower electrode LE and the upper electrode UE, so that the effective thickness of the capacitive insulating film is reduced by the thickness of the floating electrode FE. be able to.