JP2009230590A - Arithmetic device for executing distributed processing, server and distributed processing method - Google Patents

Arithmetic device for executing distributed processing, server and distributed processing method Download PDFInfo

- Publication number

- JP2009230590A JP2009230590A JP2008076904A JP2008076904A JP2009230590A JP 2009230590 A JP2009230590 A JP 2009230590A JP 2008076904 A JP2008076904 A JP 2008076904A JP 2008076904 A JP2008076904 A JP 2008076904A JP 2009230590 A JP2009230590 A JP 2009230590A

- Authority

- JP

- Japan

- Prior art keywords

- calculation

- server

- distributed processing

- time step

- arithmetic

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Hardware Redundancy (AREA)

Abstract

【課題】分散処理システムの演算を一時停止させても該分散処理システムを構成する演算装置の演算結果にズレが生じない同期制御を行う。

【解決手段】サーバから分散処理の一時停止の要求を受信したとき、演算装置を停止させる演算処理一時停止部と、分散処理が停止したときに、サーバから演算装置ごとに設けられた分散処理の演算進度をカウントするカウンタの値を参照する演算タイムステップ参照通知に基づいて、カウンタ値を取得しサーバに送信する演算タイムステップ参照部と、演算装置ごとの演算タイムステップ参照部から取得したカウンタ値から最大値を検出して検出したカウンタ値の最大値に1カウント加算したタイムステップ最大値をサーバから取得してレジスタに記録する演算終了タイムステップ更新部と、停止状態から分散処理を再開する演算再開部と、を備え、分散処理を再開してタイムステップ最大値まで進めてから再度分散処理を停止する。

【選択図】図1Synchronous control is performed such that even if computation of a distributed processing system is temporarily stopped, a computation result of a computing device constituting the distributed processing system does not shift.

When a request for suspension of distributed processing is received from a server, an arithmetic processing suspension unit that stops the arithmetic device and a distributed processing provided for each arithmetic device from the server when the distributed processing stops. Based on the calculation time step reference notification that refers to the value of the counter that counts the calculation progress, the counter value acquired from the calculation time step reference unit that acquires the counter value and transmits it to the server, and the calculation time step reference unit for each calculation device An operation end time step update unit that obtains from the server the time step maximum value obtained by adding 1 count to the maximum counter value detected by detecting the maximum value from the server and records it in the register, and an operation that resumes the distributed processing from the stopped state A resuming unit, and resumes the distributed processing to advance to the time step maximum value, and then stops the distributed processing again.

[Selection] Figure 1

Description

本発明は、分散処理装置のタイムステップの同期制御の技術に関する。 The present invention relates to a technique for synchronous control of time steps of a distributed processing apparatus.

近年、分散処理システム環境下においてSPMD(単一プログラム複数データ)型プログラムなどのプログラムを実行する際、実行後の途中経過を確認してから、再度実行を継続するために、同期して停止させたいというニーズがある。 In recent years, when executing a program such as an SPMD (single program multiple data) type program in a distributed processing system environment, after confirming the progress after execution, the program is stopped synchronously in order to continue execution. There is a need to want.

従来は、SPMD型プログラムを同期して停止させる場合には、汎用OS(Operating System)搭載の計算機(サーバ)により、計算機同士によるメッセージパッシングや同期関数などを用いることにより実現していた。 Conventionally, when an SPMD type program is stopped synchronously, it has been realized by using a message passing or a synchronization function between computers by a computer (server) equipped with a general-purpose OS (Operating System).

図7は、従来の各計算機(サーバ)間のやり取りで同期を実現する場合の分散処理システムの構成を示す図である。分散処理システム70は4台のサーバA(71a)、サーバB(71b)、サーバC(71c)、サーバD(71d)から構成されている。各サーバA〜D(71a〜71d)はCPU72(72a〜72d)とOS74(74a〜74d)を有し、各CPUは演算部73(73a〜73d)を有している。演算部73は演算処理を実行し、OS74はサーバA〜D(71a、71b、71c、71d)自身の制御および、各サーバ同士の制御を行っている。

FIG. 7 is a diagram showing a configuration of a distributed processing system in the case where synchronization is realized by exchange between conventional computers (servers). The

各サーバA〜D(71a〜71d)には、それぞれSPMD型プログラムP0(P1、P2、P3、P4)が実装され、外部から入力されるデータD1〜D3を用いてサーバ71b、71c、71dがそれぞれに割り当てられた演算を実行する。また、サーバA(71a)は親サーバとして、他のサーバB〜D(71b、71c、71d)との通信を行い、命令およびデータの送受信をする。他のサーバB〜D(71b、71c、71d)間でも通信を行う。

SPMD type programs P0 (P1, P2, P3, P4) are respectively installed in the servers A to D (71a to 71d), and the

通常、上記のような構成の分散処理システムでは、利用者が演算の途中経過を確認する場合に、利用者が親サーバであるサーバA(71a)のOS74aから演算一時停止命令を出力する。各サーバB〜D(71b、71c、71d)のOS74b、74c、74dに対して送信される。その後、演算一時停止命令を受信した各サーバA〜D(71a、71b、71c、71d)は一時停止の準備後、演算を停止させる。

Normally, in the distributed processing system configured as described above, when the user confirms the progress of the computation, the user outputs a computation suspension command from the OS 74a of the server A (71a) which is the parent server. It is transmitted to the

図8は、図7に示した分散処理システムの動作を説明する図である。

ステップS81では、サーバA(71a)がサーバB(71b)に演算の開始を指示する(サーバB演算開始通知)。ステップS82では、サーバB(71b)がサーバB演算開始通知を受信して、ステップS83のタイミングからプログラムP0の実行を開始する。

FIG. 8 is a diagram for explaining the operation of the distributed processing system shown in FIG.

In step S81, the server A (71a) instructs the server B (71b) to start computation (server B computation start notification). In step S82, the server B (71b) receives the server B calculation start notification and starts executing the program P0 from the timing of step S83.

次に、ステップS84では、サーバA(71a)がサーバC(71c)に演算の開始を指示する(サーバC演算開始通知)。ステップS85では、サーバC(71c)がサーバC演算開始通知を受信して、ステップS86のタイミングからプログラムP0の実行を開始する。 Next, in step S84, the server A (71a) instructs the server C (71c) to start computation (server C computation start notification). In step S85, the server C (71c) receives the server C calculation start notification and starts executing the program P0 from the timing of step S86.

同様に、ステップS87では、サーバA(71a)がサーバD(71d)に演算の開始を指示する(サーバD演算開始通知)。ステップS88では、サーバD(71d)がサーバD演算開始通知を受信して、ステップS89のタイミングからプログラムP0の実行を

開始する。

Similarly, in step S87, server A (71a) instructs server D (71d) to start computation (server D computation start notification). In step S88, the server D (71d) receives the server D calculation start notification, and starts executing the program P0 from the timing of step S89.

ステップS810のタイミングでは、サーバA(71a)は他のサーバB〜D(71b〜71d)の演算が終了するまで待機状態になる。

ステップS814ではサーバB(71b)の演算が終了し、サーバB(71b)からサーバB演算終了通知が送信される。ステップS815のタイミングでサーバA(71a)はサーバB演算終了通知を受信する。次に、ステップS816ではサーバC(71c)の演算が終了し、サーバC(71c)からサーバC演算終了通知が送信される。ステップS817のタイミングでサーバA(71a)はサーバC演算終了通知を受信する。同様に、ステップS818ではサーバD(71d)の演算が終了し、サーバD(71d)からサーバD演算終了通知が送信される。ステップS819のタイミングでサーバA(71a)はサーバD演算終了通知を受信する。

At the timing of step S810, the server A (71a) is in a standby state until the calculations of the other servers B to D (71b to 71d) are completed.

In step S814, the calculation of the server B (71b) ends, and a server B calculation end notification is transmitted from the server B (71b). At the timing of step S815, the server A (71a) receives the server B calculation end notification. Next, in step S816, the calculation of the server C (71c) ends, and a server C calculation end notification is transmitted from the server C (71c). At the timing of step S817, the server A (71a) receives a server C calculation end notification. Similarly, in step S818, the calculation of server D (71d) ends, and a server D calculation end notification is transmitted from server D (71d). At the timing of step S819, the server A (71a) receives the server D calculation end notification.

ステップS820のタイミングでは、サーバA(71a)は他のサーバB〜D(71b〜61d)の演算が終了したことを判断して待機状態から抜ける。ステップS821では次のプログラムが実行される。 At the timing of step S820, the server A (71a) determines that the computations of the other servers B to D (71b to 61d) have ended, and exits the standby state. In step S821, the following program is executed.

しかしながら、上記のようにOS(ソフトウェア)によりSPMD型プログラムの実行を制御している場合に、各サーバA〜D(71a〜71d)に演算を一時停止させると、各サーバA〜D(71a〜71d)の実行した演算結果にズレが生じてしまうという問題がある。 However, when the execution of the SPMD type program is controlled by the OS (software) as described above, if each of the servers A to D (71a to 71d) pauses the computation, each of the servers A to D (71a to 71a) There is a problem that a deviation occurs in the calculation result executed in 71d).

また、特許文献1、特許文献2にはFPGAを使ったサーバ間での同期処理が提案されている。

分散処理装置の演算を一時停止させても該分散処理装置を構成する演算装置の演算結果にズレが生じない同期制御を行うことを目的とする。 It is an object of the present invention to perform synchronous control that does not cause a deviation in the calculation results of the calculation devices constituting the distributed processing device even if the calculation of the distributed processing device is temporarily stopped.

態様のひとつであるサーバと接続される分散処理を実行する複数の演算装置であって、前記サーバから前記分散処理の一時停止の要求を受信したとき、前記演算装置を停止させる演算処理一時停止部と、分散処理が停止したときに、前記サーバから前記演算装置ごとに設けられた分散処理の演算進度をカウントするカウンタの値を参照する演算タイムステップ参照通知に基づいて、前記カウンタ値を取得し前記サーバに送信する演算タイムステップ参照部と、前記演算装置ごとの前記演算タイムステップ参照部から取得した前記カウンタ値から最大値を検出して前記検出した前記カウンタ値の最大値に少なくとも1カウント加算したタイムステップ最大値を前記サーバから取得してレジスタに記録する演算終了タイムステップ更新部と、停止状態から前記分散処理を再開する演算再開部と、を備え、前記分散処理を再開して前記タイムステップ最大値まで進めてから再度分散処理を停止する。 An arithmetic processing pause unit that is a plurality of arithmetic devices that execute distributed processing connected to a server that is one of the aspects, and that stops the arithmetic device when a request for suspension of the distributed processing is received from the server And when the distributed processing is stopped, the counter value is acquired based on a calculation time step reference notification that refers to the value of the counter that counts the calculation progress of the distributed processing provided for each of the arithmetic devices from the server. An arithmetic time step reference unit to be transmitted to the server, and a maximum value is detected from the counter value acquired from the arithmetic time step reference unit for each arithmetic device, and at least one count is added to the detected maximum value of the counter value An operation end time step update unit that obtains the maximum value of the time step obtained from the server and records it in a register, and a stop And a resuming operation resumption section the distributed processing from the state, stopping the dispersion treatment resumed to re-dispersion treatment from advancing to the time step maximum value.

上記のように専用ハードハードウェアである演算装置を設けることにより、演算装置にOSなどが不要となる。また、サーバからの指示により演算装置が演算を実行するためシステム全体の整合をとることが容易にできる。 By providing an arithmetic device that is dedicated hardware as described above, an OS or the like is not required for the arithmetic device. In addition, since the arithmetic unit executes an arithmetic operation according to an instruction from the server, it is possible to easily match the entire system.

分散処理装置の演算を一時停止させても該分散処理装置を構成する演算装置の演算結果にズレが生じない同期制御を行うことができる。 Even when the computation of the distributed processing apparatus is temporarily stopped, it is possible to perform synchronous control that does not cause a deviation in the computation results of the computing apparatus constituting the distributed processing apparatus.

以下図面に基づいて、本発明の実施形態について詳細を説明する。

(実施例1)

図1は、1台の計算機(サーバ:ホストPC等)と複数台の専用ハードウェアにより構成された分散処理システムの構成を示す図である。図1に示す分散処理システム1は、サーバ2と、複数の演算装置3(3a、3b、3c〜:専用ハードウェア)から構成されている。そして、図1に示す分散処理システム1を用いてSPMDプログラムなどの分散処理をする場合の演算一時停止時の同期ズレを防止する。

Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings.

Example 1

FIG. 1 is a diagram showing a configuration of a distributed processing system including one computer (server: host PC or the like) and a plurality of dedicated hardware. A

図2を用いてSPMDプログラムの同期ズレについて説明する。例えば、流体の動きをシミュレーションする場合について説明する。図2Aは、流体の動きを8つの空間に分け、演算装置(ハード1〜ハード4)4台を用いて分散処理を行う場合について示している。ハード1は3つの空間の演算を担当し、ハード2は1つの空間の演算を担当し、ハード3は3つの空間の演算を担当し、ハード4は1つの空間の演算を担当する。

The synchronization deviation of the SPMD program will be described with reference to FIG. For example, the case of simulating fluid movement will be described. FIG. 2A shows a case where the movement of the fluid is divided into eight spaces and distributed processing is performed using four arithmetic devices (

図2Bに示す縦軸は演算装置の名称を示し、横軸はシミュレーションにおける進度を示す(カウント値:タイムステップ)。例えば、流体が1秒後、2秒後・・・にどのような状態になるかを示している。 The vertical axis shown in FIG. 2B indicates the name of the arithmetic device, and the horizontal axis indicates the progress in the simulation (count value: time step). For example, it shows what state the fluid will be after 1 second, 2 seconds, and so on.

ハード1〜4が分散処理を同時にスタートし(カウント値=0、実時間=0秒)、カウント値3で停止させる場合、担当する空間が多い演算装置の演算の進みは遅くなる。図2Bではハード2がカウント値3まで演算を進めていれば、ハード1は空間の担当している量がハード2の3倍なので進度は1/3になる。つまり、実時間で停止するとハード1とハード2のカウント値にズレがでてしまう。

When the

そこで、ハード1〜ハード4までの全てのカウント値が同じになるまで演算を実行して同期ズレをなくす。

図3にサーバ2の構成を示す。サーバ2は通信部33と、OS34(Operating System)、演算部35、演算データ設定指示部36、演算終了タイムステップ設定指示部37、演算開始指示部38、演算一時停止指示部39、演算タイムステップ参照指示部310、演算終了タイムステップ更新指示部311、演算再開指示部312、リスタートデータ取得指示部313を搭載している。

Therefore, the calculation is executed until all the count values from

FIG. 3 shows the configuration of the

通信部33は、各演算装置3(3a〜3c)との通信を行う。

演算部35は、SPMD(単一プログラム複数データ)型プログラムなどを含むプログラムを実行する。また、演算部35は最大値タイムステップ演算部314を有している。ここで、図1においてサーバ2が実行するSPMDプログラムは、図7、図8を用いて説明したプログラムP0のうちプログラムP1に関する部分である。また、サーバ2は、各演算装置3に対してSPMDプログラムに用いる演算データを送信する。図1では、SPMDプログラムのうちプログラムP2〜P4に用いる演算データD1〜D3が送信される。また、サーバ2はSPMDプログラムを実行する指示も各演算装置3に転送する。

The

The

演算データ設定指示部36は、サーバ2に接続された入力装置(不図示)から入力された演算データを各演算装置3に設定する指示を生成する。

演算終了タイムステップ設定指示部37は、分散処理により演算するシミュレーションを終了するタイムステップを各演算装置3に設定する指示を生成する。

The arithmetic data setting

The calculation end time step setting

演算開始指示部38は、各演算装置3に演算開始を指示するために演算開始通知を生成する。

演算一時停止指示部39は、分散処理により演算中のシミュレーションを一時停止するときに各演算装置3に指示をするための演算一時停止通知を生成する。

The calculation start

The calculation

演算タイムステップ参照指示部310は、各演算装置3の分散処理中のシミュレーションなどの演算がどこまで進んでいるかを参照するときに用いる演算タイムステップ参照通知を生成する。

The calculation time step

演算終了タイムステップ更新指示部311は、各演算装置3に後述する最大値タイムステップ演算部314の演算した最大値タイムステップまで演算を進めるために各演算装置3の演算終了タイムステップレジスタ6の値を更新する演算タイムステップ更新通知を生成する。

The calculation end time step

演算再開指示部312は、一時停止を解除して再度演算を開始する通知を生成する。

リスタートデータ取得指示部313は、演算の再開時に必要な演算データを含むデータを取得するための通知を生成する。

The calculation restart instruction unit 312 generates a notification for releasing the temporary stop and starting the calculation again.

The restart data

演算装置3は、演算部4(4a〜4c)、カウンタ5(5a〜5c)、演算終了タイムステップレジスタ6(6a〜6c)などを含んでいる。例えば、演算装置3はプログラム可能な集積回路などを用いて上記演算部4(4a〜4c)、カウンタ5(5a〜5c)、演算終了タイムステップレジスタ6(6a〜6c)を構築し、構築した各部を制御する。ここで、プログラム可能な集積回路とはFPGA(Field Programmable Gate Array)、CPLD(Complex Programmable Logic Device)などのことであるが、これらのデバイスに限定するものではない。

The

また、演算装置3にはそれぞれ割り当てられるプログラムがあり、そのプログラムに基づいて回路が構築される。図1では演算装置3aにはプログラムP2、演算装置3bにはプログラムP3、演算装置3cにはプログラムP4が割り当てられている。例えば、FPGAを用いる場合は、外部装置(PCなど)から各演算装置3にプログラムP2、P3、P4に基づいて生成された回路構築のためのデータをメモリに格納して、コンフィギュレーション時に回路を構築する。また、サーバ2から送信されたデータD1、D2、D3を、そのデータに対応する演算装置3が受信して、そのデータを用いて演算を実行する。

The

カウンタ5(5a〜5c)はサーバ2、演算装置3の同期を制御するために設けられたカウンタであり、予め設定された一定時間ごとにカウントをするカウンタである。ここで、カウンタ5がカウントする一定時間は、CPUに供給されるシステムクロックなどにより実際に時間計測するものでない。例えば、流体の動きを0〜100秒の間1秒間隔でシミュレーションする場合に、流体の10秒後の動きと、11秒後の動きが異なれば演算量も異なる。流体の動きが10秒後より11秒後の方が複雑であれば11秒後の演算量の方が10秒後の演算量より増える。つまり、カウンタ5は予め設定された時間に対応する演算が終了するごとにカウントをするカウンタである。

The counter 5 (5a to 5c) is a counter provided for controlling the synchronization of the

演算終了タイムステップレジスタ6(6a〜6c)は、例えば、シミュレーションを行う場合に、演算を終了するカウンタ5のカウント値をセットするためのレジスタである。演算終了タイムステップレジスタ6にセットするデータ(演算終了タイムステップ)はサーバ2から入力する。

The calculation end time step register 6 (6a to 6c) is a register for setting the count value of the

図4は、演算装置3の構成を示す図である。

演算装置3は、演算部4、カウンタ5、演算終了タイムステップレジスタ6、通信部7

、制御部8、メモリ9、演算データ設定部10、演算終了タイムステップ設定部11、演算開始部12、演算一時停止部13、演算タイムステップ参照部14、演算終了タイムステップ更新部15、演算再開部16、リスタートデータ取得部17を備えている。

FIG. 4 is a diagram illustrating a configuration of the

The

,

通信部7は、サーバ2との間で送受信される、演算データ(各演算装置3が演算に用いるデータ)、制御データ(演算装置3自身の制御するための通知および演算を制御するための通知)を含むデータの通信制御を行う。

The communication unit 7 transmits / receives computation data (data used by each

制御部8は、通信部7から受信した演算データ、制御データに基づいて演算装置3を構成する各部(図4に示す4〜7、9〜17を含む)の制御を行う。メモリ9は、演算データや演算結果などのデータを記録する。

The

演算データ設定部10は、演算データの設定と、該設定された演算データを制御部8を介して演算部4に転送する。演算データの演算データ設定部10への設定は、分散処理(SPMD型プログラムなど)に必要な演算データを、サーバ2に接続される入力装置(不図示)から入力し、通信部7と制御部8を介して演算データ設定部10に転送されたのち設定される。例えば、演算データ設定部10に設けられたメモリに演算データを記録する。また、演算データ設定部10は、演算が開始されると、必要に応じて制御部8から送信される上記設定した演算データを演算部4に転送するための要求通知を受け取る。その後、その要求通知に基づいて演算データを制御部8を介して演算部4へ転送する。

The calculation

演算終了タイムステップ設定部11は、演算終了タイムステップレジスタ6にサーバ2および各演算装置3が分散処理を終了するタイムステップを示す演算終了タイムステップデータを設定するための制御を行う。ここで、タイムステップとは上記説明したカウンタ5がカウントする値に相当する。演算終了タイムステップデータは、サーバ2から入力され通信部7と制御部8を介して演算終了タイムステップ設定部11に転送される。その後、演算終了タイムステップ設定部11は、演算終了タイムステップレジスタ6に演算終了タイムステップデータを記録する。また、制御部8は演算終了タイムステップレジスタ6に記録された演算終了タイムステップデータを参照して演算部4の演算を終了させる。

The calculation end time

演算開始部12は分散処理の演算を開始するときに用いる。サーバ2から演算開始通知を受信したら全ての演算装置3の演算部4を開始する。演算開始通知は、サーバ2から送信され通信部7により受信され、通信部7から制御部8を介して演算開始部12に送信される。例えば、演算開始部12に演算開始フラグを設けて、演算開始通知の内容が演算開始を示していれば演算開始フラグを開始中の状態に遷移させ、演算部4で分散処理の演算を開始する。なお、演算開始時に演算開始部12を参照して開始状態に遷移したことを検出して、上記カウンタ5の値を初期状態にしてもよい。

The calculation start

演算一時停止部13は、分散処理の演算途中に一時停止するときに用いる。サーバ2から演算一時停止通知を受信したら全ての演算装置3の演算部4を即時停止する。演算一時停止通知は、サーバ2から送信され通信部7により受信され、通信部7から制御部8を介して演算一時停止部13に送信される。例えば、演算一時停止部13に演算一時停止フラグを設けて、分散処理の一時停止通知の内容が演算一時停止を示していれば演算一時停止フラグを一時停止中の状態に遷移させ、演算部4を即時停止する。また、演算部4で演算された演算結果もメモリ9などに保持しておく。

The

演算タイムステップ参照部14は、カウンタ5の値を参照して現在どのタイムステップまで演算が実行されているかを検出する。演算タイムステップ参照部14は、カウンタ5の値を取得して制御部8に転送する。そして、通信部7は、制御部8を介して一時停止したタイムステップの示す値をサーバ2に送信する。

The calculation time

演算終了タイムステップ更新部15は、各演算装置3から送信された一時停止したときのタイムステップの値に基づいて生成されたタイムステップ最大値を受信する。演算終了タイムステップ更新部15は、タイムステップ最大値通知を受信すると、演算終了タイムステップ設定部11を介して演算終了タイムステップレジスタにタイムステップ最大値通知の示すタイムステップを設定する。タイムステップ最大値はサーバ2で生成される。サーバ2が収集した各演算装置3の一時停止時のタイムステップのうち最大のタイムステップを選択し、選択した最大のタイムステップにさらに少なくとも1タイムステップを追加したものである。例えば、演算装置3aの一時停止時のタイムステップT1、演算装置3bの停止時のタイムステップT2、演算装置3cの停止時のタイムステップT3のうち、最大の停止時のタイムステップがT1であればT1+1をタイムステップ最大値にし、タイムステップ最大値通知に含めて通知をする。

The calculation end time

演算再開部16は、一時停止した演算を再開させタイムステップ最大値になるまで演算を実行する。演算再開部16は、演算終了タイムステップレジスタ6を参照してタイムステップ最大値の取得と、制御部8を介して演算部4に演算再開の通知をするとともに、メモリに一時保存した演算結果などのデータを演算部に転送するように通知をする。

The

リスタートデータ取得部17は、一時停止(同期ズレのない一時停止)後に、一時停止を解除して再び演算を開始するために必要なデータを取得する。

(動作説明)

図5を用いて図1に示す分散処理装置の動作を説明する。ただし、便宜上図5ではサーバ2、演算装置3a(ハード1)、演算装置3b(ハード2)の構成を用いて説明する。

The restart

(Description of operation)

The operation of the distributed processing apparatus shown in FIG. 1 will be described with reference to FIG. However, for the sake of convenience, FIG. 5 will be described using the configuration of the

ステップS1からステップS2では、サーバ2の有するOSとプログラムが、分散処理を行うために実行される。ここで、プログラムとはSPMD(単一プログラム複数データ)型プログラムを含むプログラムである。

In step S1 to step S2, the OS and program of the

ステップS3では、サーバ2に接続されている入力装置から演算データが設定され、演算データを演算装置3aに送信する。このとき演算データとともに演算装置3aを識別する演算装置識別データを送信する。

In step S3, calculation data is set from the input device connected to the

ステップS4では、サーバ2から送信された演算データを演算装置3aの通信部7が受信して演算装置3aの演算データ設定部10に設定する。

ステップS5、ステップS6ではステップS3、S4と同様に演算装置3bの演算データ設定部10に演算データを設定する。

In step S4, the calculation data transmitted from the

In steps S5 and S6, calculation data is set in the calculation

ステップS7では、サーバ2に接続されている入力装置から分散処理の演算を終了する演算終了タイムステップ(T1_end)が設定され、演算終了タイムステップを演算装置3aに送信する。このとき演算終了タイムステップ設定通知とともに演算装置3aを識別する演算装置識別データを送信する。

In step S7, a computation end time step (T1_end) for finishing the computation of the distributed processing is set from the input device connected to the

ステップS8では、サーバ2から送信された演算終了タイムステップを演算装置3aの通信部7が受信して演算装置3aの演算終了タイムステップ設定部11に設定する。

ステップS9、ステップS10ではステップS7、S8と同様に演算装置3bの演算終了タイムステップ設定部11に演算終了タイムステップを設定する。

In step S8, the calculation end time step transmitted from the

In step S9 and step S10, the calculation end time step is set in the calculation end time

例えば、T1_endに「100」を設定するとタイムステップ(カウンタ5のカウント)が100になると演算装置3aは分散処理を終了する。

ステップS11では、サーバ2に接続されている入力装置から分散処理の演算開始をす

る演算開始通知が設定され、演算開始通知を演算装置3aに送信する。このとき演算開始通知とともに演算装置3aを識別する演算装置識別データを送信する。

For example, when “100” is set in T1_end, when the time step (count of the counter 5) reaches 100, the

In step S11, a calculation start notification for starting calculation of distributed processing is set from the input device connected to the

ステップS12では、サーバ2から送信された演算開始通知を演算装置3aの通信部7が受信して演算装置3aの演算開始部12に演算が開始された状態であることを設定して演算部4の演算を開始する。また、カウンタ5のカウンタ値を0にする。

In step S12, the communication unit 7 of the

ステップS13、ステップS14ではステップS11、S12と同様に演算装置3bの演算開始部12に演算が開始された状態であることを設定する。

次に、サーバ2は演算一時停止イベントを検出する。例えば、演算一時停止イベントは分散処理の途中の演算結果を確認するために演算を一時停止するイベントである。

In steps S13 and S14, as in steps S11 and S12, the

Next, the

ステップS15では、サーバ2に演算一時停止イベントに基づいて分散処理を一時停止するため演算一時停止通知が設定され、演算一時停止通知を演算装置3aに送信する。このとき演算一時停止通知とともに演算装置3aを識別する演算装置識別データを送信する。

In step S15, a calculation pause notification is set in the

ステップS16では、サーバ2から送信された演算一時停止通知を演算装置3aの通信部7が受信して演算装置3aの演算一時停止部13に演算が一時停止された状態であることを設定する。また、演算装置3aの演算を停止させる。また、カウンタ5のカウントを停止させる。

In step S16, the communication unit 7 of the

ステップS17、ステップS18ではステップS15、S16と同様に演算装置3bの演算一時停止部13に演算が一時停止された状態であることを設定する。また、演算装置3aの演算を停止させる。

In steps S17 and S18, as in steps S15 and S16, the

このとき、演算装置3aのカウント値は6であり、演算装置3bのカウント値は8である。

ステップS19では、サーバ2に一時停止したときのタイムステップを確認するために演算タイムステップ参照通知が設定され、演算タイムステップ参照通知を演算装置3aに送信する。このとき演算タイムステップ参照通知とともに演算装置3aを識別する演算装置識別データを送信する。

At this time, the count value of the

In step S19, the calculation time step reference notification is set to confirm the time step when the

ステップS20では、サーバ2から送信された演算タイムステップ参照通知を演算装置3aの通信部7が受信して演算装置3aの演算タイムステップ参照部14が、カウンタ5のカウンタ値を取得する。

In step S <b> 20, the communication unit 7 of the

ステップS21では、演算装置3aの通信部7からカウント値をサーバ2に送信する。本例では、カウント値として6を送信する。

ステップS22では、サーバ2の通信部が演算装置3aのカウント値を取得する。

In step S21, the count value is transmitted to the

In step S22, the communication unit of the

ステップS23、ステップS24、ステップS25、ステップS26では、ステップS19〜S22と同様にサーバ2が演算装置3bの一時停止時のカウント値を取得する。本例では、サーバ2はカウント値として8を取得する。

In step S23, step S24, step S25, and step S26, the

ステップS27からステップS28では、サーバ2は各演算装置3a、3bから取得したカウンタ値(一時停止時のタイムステップ)から最大値を検出する。本例では、演算装置3aのカウンタ値6より演算装置3bのカウンタ値8の方が大きいためカウント値8を選択する。そして、カウント値8に1を加算してタイムステップ最大値を算出する(Tend=8+1)。ここで、タイムステップに1を加算しているのは演算途中で演算が停止

しているためである。

In steps S27 to S28, the

ステップS29では、サーバ2の通信部からタイムステップ最大値を演算装置3aに送信する。このときタイムステップ最大値とともに演算装置3aを識別する演算装置識別データを送信する。

In step S29, the maximum time step value is transmitted from the communication unit of the

ステップS30では、サーバ2から送信されたタイムステップ最大値を演算装置3aの通信部7が受信し、演算終了タイムステップ更新部15が演算終了タイムステップレジスタ6にタイムステップ最大値を設定する。なお、本例では、タイムステップ最大値を演算終了タイムステップレジスタ6に設定しているが、演算終了タイムステップレジスタ6にせず他にレジスタを設けてもよい。

In step S30, the communication unit 7 of the

ステップS31、ステップS32ではステップS29、S30と同様に、サーバ2からの送信により、演算装置3bにタイムステップ最大値を取得させる。

ステップS33では、サーバ2からタイムステップ最大値までの演算を再開するための演算再開通知を演算装置3aに送信する。このとき演算再開通知とともに演算装置3aを識別する演算装置識別データを送信する。

In steps S31 and S32, as in steps S29 and S30, the time step maximum value is acquired by the computing device 3b by transmission from the

In step S33, a computation resumption notification for resuming computation from the

ステップS34では、演算装置3aの通信部7により演算再開通知を受信し、演算再開部16により一時停止した演算を再開させタイムステップ最大値になるまで演算を実行する。

In step S34, the calculation restart notification is received by the communication unit 7 of the

ステップS35、ステップS36では、ステップS33、S34と同様に、サーバ2からの通知により、演算装置3bでもタイムステップ最大値になるまで演算を実行させる。

演算装置3a、3bはタイムスタンプ最大値まで演算をして自動停止する。ここで、演算装置3aと演算装置3bの実際に停止する時刻は、演算量の違いによって異なる。

In steps S35 and S36, as in steps S33 and S34, calculation is executed by the notification from the

The

ステップS37では、サーバ2がタイムスタンプ最大値までの演算をして停止していることを確認する。サーバ2には、再停止したときのタイムステップを確認するために演算タイムステップ参照通知が設定され、演算タイムステップ参照通知を演算装置3aに送信する。このとき演算タイムステップ参照通知とともに演算装置3aを識別する演算装置識別データを送信する。

In step S37, it is confirmed that the

ステップS38では、サーバ2から送信された演算タイムステップ参照通知を演算装置3aの通信部7が受信して演算装置3aの演算タイムステップ参照部14が、カウンタ5のカウンタ値を取得する。

In step S38, the communication unit 7 of the

ステップS39では、演算装置3aの通信部7からカウント値をサーバ2に送信する。本例では、カウント値として9を送信する。

ステップS40では、サーバ2の通信部が演算装置3aのカウント値を取得する。

In step S39, the count value is transmitted to the

In step S40, the communication unit of the

ステップS41、ステップS42、ステップS43、ステップS44では、ステップS37〜S40と同様にサーバ2が演算装置3bの再停止時のカウント値を取得する。本例では、サーバ2はカウント値として9を取得する。

In step S41, step S42, step S43, and step S44, the

ステップS45では、サーバ2は演算装置3aから演算結果を取得するためにリスタートデータ取得通知を演算装置3aに送信する。このときリスタートデータ取得通知とともに演算装置3aを識別する演算装置識別データを送信する。

In step S45, the

ステップS46では、演算装置3aがリスタートデータ取得通知を受信する。そして、

リスタートデータ取得通知に基づいてリスタートデータ取得部17により再停止時の演算結果を収集してステップS47でサーバ2へ送信する。ステップS48では、サーバ2が演算結果を取得する。

In step S46, the

Based on the restart data acquisition notification, the restart

ステップS49、ステップS50、ステップS51、ステップS52では、ステップS45〜S48と同様にサーバ2が演算装置3bの再停止時の演算結果を取得するための処理を実行する。

In step S49, step S50, step S51, and step S52, similarly to steps S45 to S48, the

ステップS53からステップS54ではサーバ2はプログラムを終了する。

ステップS55からステップS56では、サーバ2は分散処理プログラムを再停止時に取得した演算結果を用いて演算を再開する。本例では、タイムステップが100になるまで各演算装置3a、3bが演算を行う。または、タイムステップ0から演算を再び行う。

In steps S53 to S54, the

In steps S55 to S56, the

例えばFPGAなどにおいては、専用ハードウェアの回路面積や消費電力、メモリ搭載量の制限などにより、割り込み等のイベント通知機能を実装できない場合があるが、上記説明した分散処理システムにより、サーバ(汎用OS搭載計算機)から演算装置(専用ハードウェア)間の同期を制御し、同期停止を実現することができる。 For example, in an FPGA or the like, there are cases where an event notification function such as an interrupt cannot be implemented due to restrictions on the circuit area, power consumption, and memory mounting capacity of dedicated hardware. The synchronization between the computing device (dedicated hardware) can be controlled from the on-board computer, and the synchronization stop can be realized.

(実施例2)

一時停止後の分散処理をより早く実行するために、サーバ2は各演算装置3へ演算再開通知をする際、一時停止時に取得したタイムステップを比較してタイムスタンプが小さかった演算装置3から優先的に実行させるようにする。

(Example 2)

In order to execute the distributed processing after the suspension earlier, the

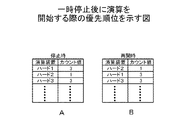

図6A(一時停止時の各演算装置3のタイムステップを示す図)は、演算装置3(ハード1)のカウント値が3、演算装置3(ハード2)のカウント値が1、演算装置3(ハード3)のカウント値が3であため、図6B(演算再開時のタイムステップが小さい順に並び替えことを示す図)である。

FIG. 6A (a diagram showing the time step of each

なお、本発明は、上記説明したSPMD型プログラムだけでなく、複数プログラムを分散処理する場合にも適用することができる。例えば、演算装置3a〜3cに流体の演算を担当させ、その他の演算装置3に流体の動きに基づいた温度の演算をさせる。

The present invention can be applied not only to the above-described SPMD type program but also to a case where a plurality of programs are distributedly processed. For example, the

上記構成された分散処理システムにおいて、1台のサーバから、仮停止と本停止の2段階停止命令でプログラムの演算停止を同期させることができる。

また、本発明は、上記実施の形態に限定されるものでなく、本発明の要旨を逸脱しない。

In the distributed processing system configured as described above, it is possible to synchronize the stop of program operation from a single server using a two-stage stop command of temporary stop and main stop.

Further, the present invention is not limited to the above embodiment, and does not depart from the gist of the present invention.

1 分散処理システム

2 サーバ

3 演算装置

4 演算部

5 カウンタ

6 演算終了タイムステップレジスタ

7 通信部

8 制御部

9 メモリ

10 演算データ設定部

11 演算終了タイムステップ設定部

12 演算開始部

13 演算一時停止部

14 演算タイムステップ参照部

15 演算終了タイムステップ更新部

16 演算再開部

17 リスタートデータ取得部

33 通信部

34 OS

35 演算部

36 演算データ設定指示部

37 演算終了タイムステップ設定指示部

38 演算開始指示部

39 演算一時停止指示部

310 演算タイムステップ参照指示部

311 演算終了タイムステップ更新指示部

312 演算再開指示部

313 リスタートデータ取得指示部

314 最大値タイムステップ演算部

70 分散処理システム

71 サーバ

72 CPU

73 演算部

74 OS

DESCRIPTION OF

35

73 Calculation unit 74 OS

Claims (6)

前記サーバから前記分散処理の一時停止の要求を受信したとき、前記演算装置を停止させる演算処理一時停止部と、

分散処理が停止したときに、前記サーバから前記演算装置ごとに設けられた分散処理の演算進度をカウントするカウンタの値を参照する演算タイムステップ参照通知に基づいて、前記カウンタ値を取得し前記サーバに送信する演算タイムステップ参照部と、

前記演算装置ごとの前記演算タイムステップ参照部から取得した前記カウンタ値から最大値を検出して前記検出した前記カウンタ値の最大値に少なくとも1カウント加算したタイムステップ最大値を前記サーバから取得してレジスタに記録する演算終了タイムステップ更新部と、

停止状態から前記分散処理を再開する演算再開部と、を備え、

前記分散処理を再開して前記タイムステップ最大値まで進めてから再度分散処理を停止することを特徴とする演算装置。 A plurality of arithmetic devices that execute distributed processing connected to a server,

When receiving a request for suspension of the distributed processing from the server, an arithmetic processing suspension unit for stopping the arithmetic device;

When the distributed processing is stopped, the server acquires the counter value based on a calculation time step reference notification that refers to the value of a counter that counts the calculation progress of the distributed processing provided for each arithmetic device from the server. A computation time step reference section to be transmitted to

A maximum time step value obtained by detecting a maximum value from the counter value acquired from the calculation time step reference unit for each arithmetic device and adding at least one count to the maximum value of the detected counter value is acquired from the server. An operation end time step update unit to be recorded in a register;

An operation restarting unit that restarts the distributed processing from a stopped state,

An arithmetic unit, wherein the distributed processing is resumed and advanced to the maximum value of the time step, and then the distributed processing is stopped again.

分散処理が停止したときの前記演算装置ごとの分散処理の演算進度をカウントするカウンタの値から最大値を検出し、前記検出した前記カウンタ値の最大値に少なくとも1カウント加算したタイムステップ最大値を算出して前記演算装置に送信することを特徴とするサーバ。 A server connected to the arithmetic device according to claim 1 or 2,

The maximum value of the time step is obtained by detecting the maximum value from the value of the counter that counts the calculation progress of the distributed processing for each arithmetic device when the distributed processing is stopped, and adding at least one count to the detected maximum value of the counter value. A server that calculates and transmits to the arithmetic device.

前記サーバが、前記分散処理の一時停止の要求をし、

前記演算装置が、前記要求を受信して前記演算装置ごとに処理を一時停止し、

前記サーバが、分散処理の停止時に前記演算装置ごとに設けられた分散処理の演算進度をカウントするカウンタの値を参照する演算タイムステップ参照通知を送信し、

前記演算装置が、前記演算タイムステップ参照通知に基づいて、前記カウンタ値を取得し前記サーバに送信し、

前記サーバが、前記演算装置から取得した前記カウンタ値から最大値を検出し、前記検出した前記カウンタ値の最大値に少なくとも1カウント加算したタイムステップ最大値を算出して前記演算装置に送信し、

前記演算装置が、前記タイムステップ最大値をレジスタに記録し、

前記サーバが、停止状態から前記分散処理を再開する通知を前記演算装置に送信し、

前記演算装置が、停止状態から前記分散処理を再開する通知に基づいて前記分散処理を再開して前記タイムステップ最大値まで分散処理を進めて停止する、

ことを特徴とする分散処理方法。 A distributed processing method for a plurality of arithmetic devices connected to a server,

The server requests the suspension of the distributed processing,

The computing device receives the request and pauses processing for each computing device,

The server transmits a calculation time step reference notification that refers to the value of a counter that counts the calculation progress of the distributed processing provided for each of the arithmetic devices when the distributed processing is stopped,

The arithmetic unit acquires the counter value based on the arithmetic time step reference notification and transmits the counter value to the server,

The server detects a maximum value from the counter value acquired from the arithmetic device, calculates a time step maximum value obtained by adding at least one count to the detected maximum value of the counter value, and transmits the time step maximum value to the arithmetic device,

The arithmetic unit records the time step maximum value in a register,

The server sends a notification to resume the distributed processing from a stopped state to the arithmetic device,

The arithmetic unit restarts the distributed processing based on a notification to restart the distributed processing from a stopped state, advances the distributed processing to the maximum time step, and stops.

A distributed processing method.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008076904A JP5181762B2 (en) | 2008-03-25 | 2008-03-25 | Arithmetic apparatus and server for executing distributed processing, and distributed processing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008076904A JP5181762B2 (en) | 2008-03-25 | 2008-03-25 | Arithmetic apparatus and server for executing distributed processing, and distributed processing method |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009230590A true JP2009230590A (en) | 2009-10-08 |

| JP5181762B2 JP5181762B2 (en) | 2013-04-10 |

Family

ID=41245873

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008076904A Expired - Fee Related JP5181762B2 (en) | 2008-03-25 | 2008-03-25 | Arithmetic apparatus and server for executing distributed processing, and distributed processing method |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5181762B2 (en) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012160655A1 (en) * | 2011-05-24 | 2012-11-29 | 富士通株式会社 | Data processing method and data processing system |

| JP2014021774A (en) * | 2012-07-19 | 2014-02-03 | Fujitsu Ltd | Arithmetic processing unit and arithmetic processing method |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01258057A (en) * | 1987-11-09 | 1989-10-16 | Tandem Comput Inc | Synchronous method and apparatus for a plurality of processors |

| JPH02105961A (en) * | 1988-10-14 | 1990-04-18 | Nippon Telegr & Teleph Corp <Ntt> | Multiprocessor synchronization system |

| JP2004046599A (en) * | 2002-07-12 | 2004-02-12 | Nec Corp | Fault tolerant computer apparatus, resynchronization method and resynchronization program |

| JP2005209029A (en) * | 2004-01-23 | 2005-08-04 | Tm T & D Kk | Application management system, application management method and program for performing the same |

-

2008

- 2008-03-25 JP JP2008076904A patent/JP5181762B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01258057A (en) * | 1987-11-09 | 1989-10-16 | Tandem Comput Inc | Synchronous method and apparatus for a plurality of processors |

| JPH02105961A (en) * | 1988-10-14 | 1990-04-18 | Nippon Telegr & Teleph Corp <Ntt> | Multiprocessor synchronization system |

| JP2004046599A (en) * | 2002-07-12 | 2004-02-12 | Nec Corp | Fault tolerant computer apparatus, resynchronization method and resynchronization program |

| JP2005209029A (en) * | 2004-01-23 | 2005-08-04 | Tm T & D Kk | Application management system, application management method and program for performing the same |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012160655A1 (en) * | 2011-05-24 | 2012-11-29 | 富士通株式会社 | Data processing method and data processing system |

| US9189301B2 (en) | 2011-05-24 | 2015-11-17 | Fujitsu Limited | Data processing method and data processing system |

| JP2014021774A (en) * | 2012-07-19 | 2014-02-03 | Fujitsu Ltd | Arithmetic processing unit and arithmetic processing method |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5181762B2 (en) | 2013-04-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8190941B2 (en) | Field control system | |

| JP6152920B2 (en) | Programmable controller system, its controller | |

| CN107066300B (en) | Firmware upgrading method of storage device and storage device | |

| US11089454B2 (en) | Systems and methods for upgrading firmware in multiple devices of a wireless fire detection system | |

| US20180365307A1 (en) | Webpage data synchronization | |

| JP2009245317A (en) | Virtual machine management program, management server device, and virtual machine management method | |

| JP6879625B2 (en) | Programmable controller, management device and control system | |

| CN103870324A (en) | Efficient execution of human machine interface applications in a heterogeneous multiprocessor environment | |

| JP5181762B2 (en) | Arithmetic apparatus and server for executing distributed processing, and distributed processing method | |

| CN110291474A (en) | controller | |

| JP4289293B2 (en) | Start control method, duplex platform system, and information processing apparatus | |

| KR20150080356A (en) | remote update method for home automatic system | |

| KR20160112787A (en) | Test system and control method thereof | |

| JP2017037606A (en) | Drive control system and abnormality monitoring device | |

| CN110188491B (en) | Processing method and device for improving calculation efficiency in simulation calculation process | |

| JP5662909B2 (en) | User terminal and communication method | |

| CN115878145B (en) | Electronic device, system upgrading method thereof and computer readable storage medium | |

| US20150282193A1 (en) | Method and apparatus for avoiding communication interference in wireless communication system | |

| JP6357806B2 (en) | Controller redundancy system, its controller | |

| JP2017016250A (en) | Barrier synchronization device, barrier synchronization method, and program | |

| JP2005107757A (en) | Program runaway detection method and program runaway detection device | |

| JP2012053805A (en) | Progress information display control system | |

| CN116185676B (en) | Job recovery methods and computing equipment | |

| JP2014134989A (en) | Computer system and computer management method | |

| JP2006302081A (en) | Service restart device and service restart program |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101119 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120221 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120731 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121231 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160125 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |