JP2009033175A - 低雑音フリップチップ・パッケージ及びそのフリップ・チップ - Google Patents

低雑音フリップチップ・パッケージ及びそのフリップ・チップ Download PDFInfo

- Publication number

- JP2009033175A JP2009033175A JP2008192724A JP2008192724A JP2009033175A JP 2009033175 A JP2009033175 A JP 2009033175A JP 2008192724 A JP2008192724 A JP 2008192724A JP 2008192724 A JP2008192724 A JP 2008192724A JP 2009033175 A JP2009033175 A JP 2009033175A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- circuit

- flip chip

- circuit portion

- connection

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W72/20—

-

- H10W70/60—

-

- H10W70/635—

-

- H10W70/65—

-

- H10W70/685—

-

- H10W72/00—

-

- H10W42/20—

-

- H10W90/724—

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Geometry (AREA)

Abstract

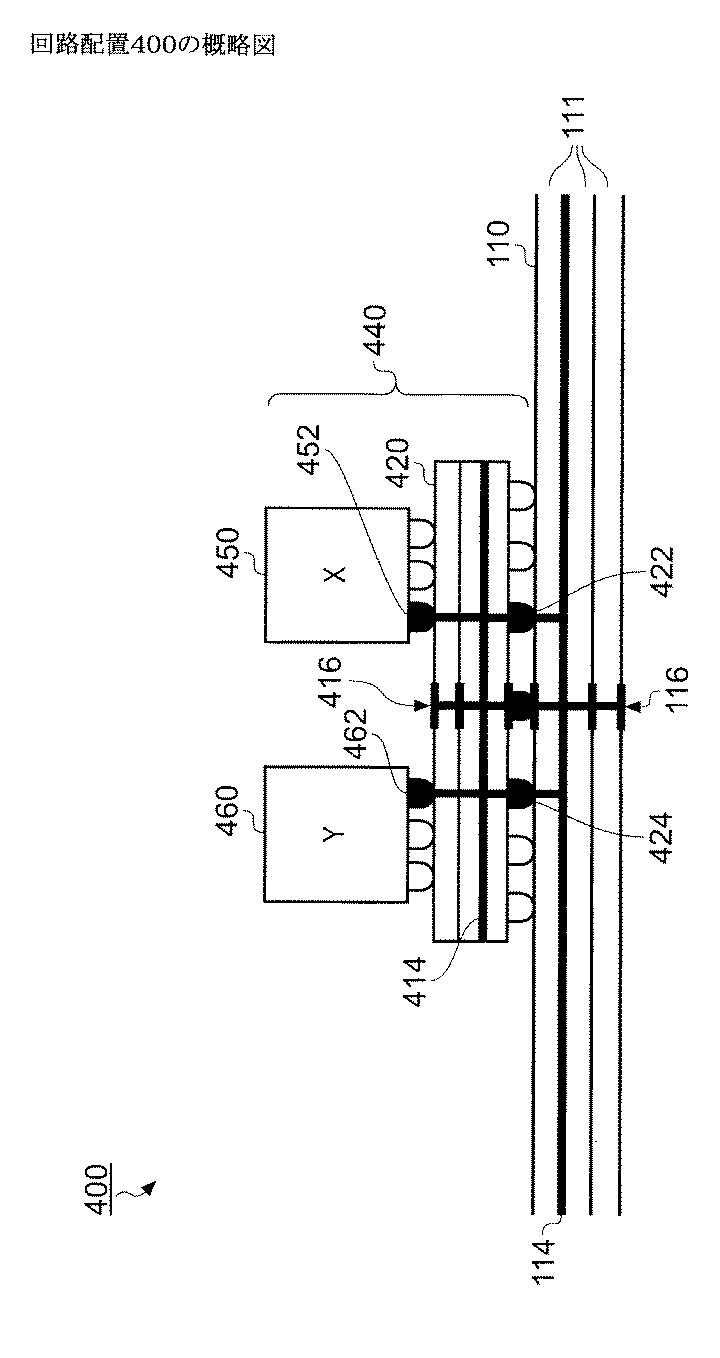

【解決手段】低雑音フリップチップ・パッケージ840は、対向する第1の主面及び第2の主面を有するキャリア基板110と、接続アレイ424を介してキャリア基板の第1の主面に対して下に向けて接続されたフリップ・チップ基板620とを備え、フリップ・チップ基板は、互いに間隔が空けられた少なくとも第1の回路部分及び第2の回路部分を備え、フリップ・チップ基板は、第1の回路部分と第2の回路部分との間に配置された基板接触境界416を備え、第1の回路部分、第2の回路部分、及び基板接触境界はそれぞれ、外部回路における共通信号参照エレメントへの接続のために接続アレイの個別の接続を介して、キャリア基板を通って、キャリア基板の第2の主面における個別の電気接触116まで延びるそれ自身の別個の信号参照接続を有する。

【選択図】図8

Description

の値は、

(付記1)

対向する第1の主面及び第2の主面を有するキャリア基板と、

接続アレイを介して前記キャリア基板の前記第1の主面に対して、下に向けて接続されたフリップ・チップ基板とを備え、

前記フリップ・チップ基板は、第1の回路部分及び第2の回路部分と、前記第1の回路部分と前記第2の回路部分との間に配置された基板接触境界を備え、

前記第1の回路部分、前記第2の回路部分、及び前記基板接触境界はそれぞれ、前記接続アレイの個別の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における個別の電気接触まで延びる別個の信号参照接続を有することを特徴とするフリップチップ・パッケージ。

(付記2)前記信号参照接続が接地電源接続であることを特徴とする、付記1記載のフリップチップ・パッケージ。

(付記3)前記基板接触境界の前記信号参照接続は、共通信号参照エレメントへの接続のために、前記接続アレイの複数の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における複数の電気接触まで延びる境界を形成することを特徴とする、付記1又は2に記載のフリップチップ・パッケージ。

(付記4)前記第1の回路部分及び前記第2の回路部分はそれぞれ、外部回路における対応する電源への接続のために、前記接続アレイの個別の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における個別の電気接触まで延びるそれ自身の別個の電源接続を有することを特徴とする、付記1、2又は3に記載のフリップチップ・パッケージ。

(付記5)前記基板接触境界が、単一の基板接触を備えることを特徴とする、付記1乃至4の何れか一項に記載のフリップチップ・パッケージ。

(付記6)前記基板接触境界が、少なくとも2つの基板接触を備えることを特徴とする、付記1乃至4の何れか一項に記載のフリップチップ・パッケージ。

(付記7)前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、前記基板接触境界の前記基板接触も、前記離隔方向において互いに間隔が空けられていることを特徴とする、付記6記載のフリップチップ・パッケージ。

(付記8)前記基板接触境界の少なくとも1つの基板接触は、別個に、その他の前記信号参照接続から前記接続アレイの接続を介して前記キャリア基板を通って、前記共通信号参照エレメントに接続するために、前記キャリア基板の前記第2の主面にある個別の電気接触まで延びるそれ自身の信号参照接続を有することを特徴とする、付記6又は7記載のフリップチップ・パッケージ。

(付記9)前記基板接触境界の各基板接触は、別個に、その他の前記信号参照接続から前記接続アレイの接続を介して前記キャリア基板を通って、前記共通信号参照エレメントに接続するために、前記キャリア基板の前記第2の主面にある個別の電気接触まで延びるそれ自身の信号参照接続を有することを特徴とする、付記8記載のフリップチップ・パッケージ。

(付記10)各基板接触の前記信号参照接続は、前記共通信号参照エレメントへの接続のために、前記接続アレイの複数の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における複数の電気接触まで延びる境界を形成することを特徴とする、付記9記載のフリップチップ・パッケージ。

(付記11)前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、

前記フリップ・チップ基板は厚さTを有し、

前記基板接触又は前記基板接触それぞれは、前記離隔方向において幅Wを有し、

前記幅W、又は幅Wの組み合わせCは好ましくは、使用中、前記基板接触境界が、厚さTと比較して、回路部分間でかなりの雑音遮断を設けるように十分大きいことを特徴とする、付記1乃至10の何れか一項に記載のフリップチップ・パッケージ。

(付記12)W又はC≧Tであり、好ましくは、W又はC≧2Tであり、より好ましくは、W又はC≧4Tであることを特徴とする、付記11記載のフリップチップ・パッケージ。

(付記13)前記基板、又は前記基板それぞれは、ほぼ細長くて回路部分間に壁を形成することを特徴とする、付記1乃至12の何れか一項に記載のフリップチップ・パッケージ。(付記14)前記第1の回路部分及び前記第2の回路部分の一方はアナログ回路部分であり、回路部分の他方はディジタル回路部分であることを特徴とする、付記1乃至13の何れか一項に記載のフリップチップ・パッケージ。

(付記15)

厚さTを有する基板と、

前記基板に形成された第1の回路部分及び第2の回路部分とを備え、

前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、

基板接触境界が、前記基板において前記第1の回路部分と前記第2の回路部分との間に形成され、

前記基板接触境界は、前記厚さTより大きな幅Wを前記離隔方向において有する基板接触を備えることを特徴とするフリップ・チップ。

(付記16)W≧Tであり、好ましくは、W≧2Tであり、より好ましくは、W≧4Tであることを特徴とする、付記15記載のフリップ・チップ。

(付記17)前記基板接触は第1の基板接触であり、

前記幅Wは幅W1であり、

前記基板接触境界は、前記基板において前記第1の回路部分と前記第2の回路部分との間に形成された第2の基板接触を備え、

前記第2の基板接触は前記離間方向において幅W2を有し、

前記幅W1及び前記幅W2の組み合わせCは、前記厚さTより大きいことを特徴とする、付記15又は16に記載のフリップ・チップ。

(付記18)C≧Tであり、好ましくは、C≧2Tであり、より好ましくは、C≧4Tであることを特徴とする、付記17記載のフリップ・チップ。

(付記19)前記第1の基板接触及び前記第2の基板接触は前記離隔方向において互いに間隔が空けられていることを特徴とする、付記17又は18の何れかに記載のフリップ・チップ。

(付記20)前記第1の基板接触及び前記第2の基板接触は、前記離隔方向において、幅W1と幅W2との和より小さい離隔幅SWで互いに間隔が空けられていることを特徴とする、付記19記載のフリップ・チップ。

(付記21)前記幅W1は、前記幅W2は実質的に同じであることを特徴とする、付記17乃至20の何れか記載のフリップ・チップ。

(付記22)前記基板、又は前記基板の両方は、回路部分間に壁を形成することを特徴とする、付記15乃至21の何れか一項に記載のフリップ・チップ。

(付記23)低雑音フリップ・チップであって、

基板と、

前記基板に形成された第1の回路部分及び第2の回路部分とを備え、

前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、

少なくとも2つの基板接触を備えた基板接触境界が前記基板において前記第1の回路部分と前記第2の回路部分との間に、前記2つの基板接触が前記離隔方向において互いに間隔が空けられるように形成されることを特徴とする低雑音フリップ・チップ。

(付記24)前記基板は厚さTを有し、

前記基板接触のうちの第1の基板接触は、前記離隔方向において幅W1を有し、

前記基板接触のうちの第2の基板接触は、前記離隔方向において幅W2を有し、

前記幅W1及び前記幅W2の組み合わせCは、前記厚さTより大きいことを特徴とする、付記23記載のフリップ・チップ。

(付記25)C≧Tであり、好ましくは、C≧2Tであり、より好ましくは、C≧4Tであることを特徴とする、付記24記載のフリップ・チップ。

(付記26)前記第1の基板接触及び前記第2の基板接触は、前記離隔方向において、幅W1と幅W2との和より小さい離隔幅SWで互いに間隔が空けられていることを特徴とする、付記24又は25に記載のフリップ・チップ。

(付記27)前記幅W1は、前記幅W2と実質的に同じであることを特徴とする、付記24乃至26の何れかに記載のフリップ・チップ。

(付記28)前記基板接触の一方又は両方は、回路部分間に壁を形成することを特徴とする、付記23乃至27の何れか一項に記載のフリップ・チップ。

620 ラミネート基板

732 回路部分

734 回路部分

800 回路配置

830 フリップ・チップ

860 基板接触

Claims (10)

- 対向する第1の主面及び第2の主面を有するキャリア基板と、

接続アレイを介して前記キャリア基板の前記第1の主面に対して、下に向けて接続されたフリップ・チップ基板とを備え、

前記フリップ・チップ基板は、第1の回路部分及び第2の回路部分と、前記第1の回路部分と前記第2の回路部分との間に配置された基板接触境界を備え、

前記第1の回路部分、前記第2の回路部分、及び前記基板接触境界はそれぞれ、前記接続アレイの個別の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における個別の電気接触まで延びる別個の信号参照接続を有することを特徴とするフリップチップ・パッケージ。 - 前記信号参照接続が接地電源接続であることを特徴とする、請求項1記載のフリップチップ・パッケージ。

- 前記基板接触境界の前記信号参照接続は、共通信号参照エレメントへの接続のために、前記接続アレイの複数の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における複数の電気接触まで延びる境界を形成することを特徴とする、請求項1又は2に記載のフリップチップ・パッケージ。

- 前記第1の回路部分及び前記第2の回路部分はそれぞれ、外部回路における対応する電源への接続のために、前記接続アレイの個別の接続を介して、前記キャリア基板を通って、前記キャリア基板の前記第2の主面における個別の電気接触まで延びるそれ自身の別個の電源接続を有することを特徴とする、請求項1、2又は3に記載のフリップチップ・パッケージ。

- 前記基板接触境界が、単一の基板接触を備えることを特徴とする、請求項1乃至4の何れか一項に記載のフリップチップ・パッケージ。

- 前記基板接触境界が、少なくとも2つの基板接触を備えることを特徴とする、請求項1乃至4の何れか一項に記載のフリップチップ・パッケージ。

- 前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、

前記基板接触境界の前記基板接触も、前記離隔方向において互いに間隔が空けられていることを特徴とする、請求項6記載のフリップチップ・パッケージ。 - 前記基板接触境界の少なくとも1つの基板接触は、別個に、その他の前記信号参照接続から前記接続アレイの接続を介して前記キャリア基板を通って、前記共通信号参照エレメントに接続するために、前記キャリア基板の前記第2の主面にある個別の電気接触まで延びるそれ自身の信号参照接続を有することを特徴とする、請求項6又は7記載のフリップチップ・パッケージ。

- 厚さTを有する基板と、

前記基板に形成された第1の回路部分及び第2の回路部分とを備え、

前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、

基板接触境界が、前記基板において前記第1の回路部分と前記第2の回路部分との間に形成され、

前記基板接触境界は、前記厚さTより大きな幅Wを前記離隔方向において有する基板接触を備えることを特徴とするフリップ・チップ。 - 低雑音フリップ・チップであって、

基板と、

前記基板に形成された第1の回路部分及び第2の回路部分とを備え、

前記第1の回路部分及び前記第2の回路部分は、離隔方向において互いに間隔が空けられており、

少なくとも2つの基板接触を備えた基板接触境界が前記基板において前記第1の回路部分と前記第2の回路部分との間に、前記2つの基板接触が前記離隔方向において互いに間隔が空けられるように形成されることを特徴とする低雑音フリップ・チップ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP07113378.9 | 2007-07-27 | ||

| EP20070113378 EP2019427B1 (en) | 2007-07-27 | 2007-07-27 | Low-noise flip-chip packages and flip chips thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009033175A true JP2009033175A (ja) | 2009-02-12 |

| JP5428233B2 JP5428233B2 (ja) | 2014-02-26 |

Family

ID=38668979

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008192724A Active JP5428233B2 (ja) | 2007-07-27 | 2008-07-25 | フリップチップ・パッケージ、及び上記フリップチップ・パッケージを含むシステム |

Country Status (4)

| Country | Link |

|---|---|

| US (6) | US8178979B2 (ja) |

| EP (1) | EP2019427B1 (ja) |

| JP (1) | JP5428233B2 (ja) |

| DE (1) | DE602007009375D1 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011151367A (ja) * | 2009-12-25 | 2011-08-04 | Sony Corp | 回路基板積層モジュール及び電子機器 |

| JP2015173140A (ja) * | 2014-03-11 | 2015-10-01 | 三菱電機株式会社 | 高周波パッケージ |

| JP2016500198A (ja) * | 2012-09-25 | 2016-01-07 | ザイリンクス インコーポレイテッドXilinx Incorporated | ノイズ減衰壁 |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2019427B1 (en) * | 2007-07-27 | 2010-09-22 | Fujitsu Semiconductor Limited | Low-noise flip-chip packages and flip chips thereof |

| EP2019486B1 (en) | 2007-07-27 | 2014-12-10 | Fujitsu Semiconductor Limited | RF transmitters |

| US8555230B2 (en) * | 2008-09-19 | 2013-10-08 | The Boeing Company | Isolation method and package using a high isolation differential ball grid array (BGA) pattern |

| US9070700B2 (en) * | 2011-11-04 | 2015-06-30 | Broadcom Corporation | Apparatus for electrostatic discharge protection and noise suppression in circuits |

| US9054722B2 (en) | 2013-09-12 | 2015-06-09 | Fujitsu Semiconductor Limited | Circuitry and methods for use in mixed-signal circuitry |

| EP2849344B1 (en) | 2013-09-12 | 2019-11-06 | Socionext Inc. | Circuitry and methods for use in mixed-signal circuitry |

| EP2849543B1 (en) | 2013-09-12 | 2021-02-24 | Socionext Inc. | Components and circuits for output termination |

| US8976050B1 (en) | 2013-09-12 | 2015-03-10 | Fujitsu Semiconductor Limited | Circuitry and methods for use in mixed-signal circuitry |

| EP3062189B1 (en) | 2013-09-12 | 2020-06-24 | Socionext Inc. | Circuitry useful for clock generation and distribution |

| EP2849346B1 (en) | 2013-09-12 | 2019-08-21 | Socionext Inc. | Mixed-signal circuitry |

| EP2849345B1 (en) | 2013-09-12 | 2020-11-04 | Socionext Inc. | Circuitry and methods for use in mixed-signal circuitry |

| EP2849021B1 (en) | 2013-09-12 | 2020-01-01 | Socionext Inc. | Signal-alignment circuitry and methods |

| US9201813B2 (en) | 2013-09-12 | 2015-12-01 | Socionext Inc. | Signal distribution circuitry |

| US10748854B2 (en) | 2016-03-16 | 2020-08-18 | Intel Corporation | Stairstep interposers with integrated shielding for electronics packages |

| CN111048492B (zh) * | 2019-12-30 | 2021-10-15 | 中国电子科技集团公司第十三研究所 | 一种限幅低噪声放大器芯片结构 |

| US20220310497A1 (en) | 2021-03-25 | 2022-09-29 | Dialog Semiconductor (Uk) Limited | Partially Staggered Ball Array for Reduced Noise Injection |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1155145A (ja) * | 1997-08-06 | 1999-02-26 | Sony Corp | 送受信機用集積回路 |

| JP2004179255A (ja) * | 2002-11-25 | 2004-06-24 | Sony Corp | 半導体集積回路 |

| JP2005150248A (ja) * | 2003-11-12 | 2005-06-09 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| JP2005167276A (ja) * | 2005-01-26 | 2005-06-23 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP2006261543A (ja) * | 2005-03-18 | 2006-09-28 | Fuji Xerox Co Ltd | 半導体装置実装パッケージ及び中継プリント配線基板 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR0150206B1 (ko) | 1989-02-21 | 1998-12-15 | 오가 노리오 | 디지탈/아날로그 변환기 |

| US6294407B1 (en) * | 1998-05-06 | 2001-09-25 | Virtual Integration, Inc. | Microelectronic packages including thin film decal and dielectric adhesive layer having conductive vias therein, and methods of fabricating the same |

| US6239485B1 (en) * | 1998-11-13 | 2001-05-29 | Fujitsu Limited | Reduced cross-talk noise high density signal interposer with power and ground wrap |

| US6121827A (en) | 1999-04-15 | 2000-09-19 | Lucent Technologies, Inc. | Digital noise reduction in integrated circuits and circuit assemblies |

| US6775150B1 (en) * | 2000-08-30 | 2004-08-10 | Intel Corporation | Electronic assembly comprising ceramic/organic hybrid substrate with embedded capacitors and methods of manufacture |

| TW511414B (en) * | 2001-04-19 | 2002-11-21 | Via Tech Inc | Data processing system and method, and control chip, and printed circuit board thereof |

| US6936502B2 (en) * | 2003-05-14 | 2005-08-30 | Nortel Networks Limited | Package modification for channel-routed circuit boards |

| EP2019427B1 (en) * | 2007-07-27 | 2010-09-22 | Fujitsu Semiconductor Limited | Low-noise flip-chip packages and flip chips thereof |

-

2007

- 2007-07-27 EP EP20070113378 patent/EP2019427B1/en active Active

- 2007-07-27 DE DE200760009375 patent/DE602007009375D1/de active Active

-

2008

- 2008-07-25 JP JP2008192724A patent/JP5428233B2/ja active Active

- 2008-07-25 US US12/180,212 patent/US8178979B2/en active Active

-

2012

- 2012-01-10 US US13/347,394 patent/US8334600B2/en active Active

- 2012-03-29 US US13/434,473 patent/US8648475B2/en active Active

- 2012-08-03 US US13/566,581 patent/US8637999B2/en active Active

-

2014

- 2014-01-10 US US14/152,609 patent/US9136238B2/en active Active

-

2015

- 2015-08-12 US US14/824,967 patent/US9490227B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1155145A (ja) * | 1997-08-06 | 1999-02-26 | Sony Corp | 送受信機用集積回路 |

| JP2004179255A (ja) * | 2002-11-25 | 2004-06-24 | Sony Corp | 半導体集積回路 |

| JP2005150248A (ja) * | 2003-11-12 | 2005-06-09 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| JP2005167276A (ja) * | 2005-01-26 | 2005-06-23 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP2006261543A (ja) * | 2005-03-18 | 2006-09-28 | Fuji Xerox Co Ltd | 半導体装置実装パッケージ及び中継プリント配線基板 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011151367A (ja) * | 2009-12-25 | 2011-08-04 | Sony Corp | 回路基板積層モジュール及び電子機器 |

| JP2016500198A (ja) * | 2012-09-25 | 2016-01-07 | ザイリンクス インコーポレイテッドXilinx Incorporated | ノイズ減衰壁 |

| JP2015173140A (ja) * | 2014-03-11 | 2015-10-01 | 三菱電機株式会社 | 高周波パッケージ |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2019427B1 (en) | 2010-09-22 |

| US8178979B2 (en) | 2012-05-15 |

| EP2019427A1 (en) | 2009-01-28 |

| US8637999B2 (en) | 2014-01-28 |

| US20120326335A1 (en) | 2012-12-27 |

| US8334600B2 (en) | 2012-12-18 |

| US20090057920A1 (en) | 2009-03-05 |

| US20140124930A1 (en) | 2014-05-08 |

| US20120106094A1 (en) | 2012-05-03 |

| US9136238B2 (en) | 2015-09-15 |

| US8648475B2 (en) | 2014-02-11 |

| US9490227B2 (en) | 2016-11-08 |

| US20120187579A1 (en) | 2012-07-26 |

| JP5428233B2 (ja) | 2014-02-26 |

| DE602007009375D1 (de) | 2010-11-04 |

| US20160043052A1 (en) | 2016-02-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5428233B2 (ja) | フリップチップ・パッケージ、及び上記フリップチップ・パッケージを含むシステム | |

| KR102870744B1 (ko) | 고밀도 3d 상호연결 구성 | |

| US6770963B1 (en) | Multi-power ring chip scale package for system level integration | |

| US8243465B2 (en) | Semiconductor device with additional power supply paths | |

| US6703714B2 (en) | Methods for fabricating flip-chip devices and preventing coupling between signal interconnections | |

| KR20100003237A (ko) | 장치, 칩 및 집적 회로 패키지 | |

| CN110088896B (zh) | 集成电路封装中的信号路由 | |

| JP7616964B2 (ja) | フリップ・チップ・トポロジーを有するトランジスタおよび該トランジスタを有する電力増幅器 | |

| JP2002190568A (ja) | 半導体チップ,半導体チップ群及びマルチチップモジュール | |

| JP3730625B2 (ja) | フリップチップボンディングのための有機基板 | |

| US6725443B1 (en) | Integrated circuit template cell system and method | |

| US5172471A (en) | Method of providing power to an integrated circuit | |

| US6841886B2 (en) | Layout structure for a flip chip semiconductor integrated circuit | |

| CN100468735C (zh) | 集成电路的电源地网络及其布置方法 | |

| US20240332304A1 (en) | Semiconductor integrated circuit device | |

| US20100164052A1 (en) | High power integrated circuit device | |

| JP2002170920A (ja) | フリップチップ装置 | |

| US11621259B2 (en) | Semiconductor chip | |

| US12107048B2 (en) | Layouts for conductive layers in integrated circuits | |

| JP2900555B2 (ja) | 半導体集積回路 | |

| JP4889667B2 (ja) | 半導体装置 | |

| US8669593B2 (en) | Semiconductor integrated circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090826 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110407 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121204 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130725 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131105 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131118 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5428233 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |