DE102017118975B4 - SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY AND METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY - Google Patents

SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY AND METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY Download PDFInfo

- Publication number

- DE102017118975B4 DE102017118975B4 DE102017118975.0A DE102017118975A DE102017118975B4 DE 102017118975 B4 DE102017118975 B4 DE 102017118975B4 DE 102017118975 A DE102017118975 A DE 102017118975A DE 102017118975 B4 DE102017118975 B4 DE 102017118975B4

- Authority

- DE

- Germany

- Prior art keywords

- semiconductor body

- doping

- concentration

- semiconductor

- field stop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H10P36/00—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

- H10D12/031—Manufacture or treatment of IGBTs

- H10D12/032—Manufacture or treatment of IGBTs of vertical IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/411—Insulated-gate bipolar transistors [IGBT]

- H10D12/441—Vertical IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/129—Cathode regions of diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/50—Physical imperfections

- H10D62/53—Physical imperfections the imperfections being within the semiconductor body

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/60—Impurity distributions or concentrations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

-

- H10P30/204—

-

- H10P30/208—

Landscapes

- Electrodes Of Semiconductors (AREA)

Abstract

Verfahren zum Herstellen einer Halbleitervorrichtung, umfassend:

Reduzieren einer Konzentration von Sauerstoff in einem ersten Teil (102) eines CZ-Halbleiterkörpers (100) durch eine thermische Behandlung, wobei der erste Teil (102) an eine erste Oberfläche (103) des Halbleiterkörpers (100) grenzt;

Bearbeiten des Halbleiterkörpers (100) an der ersten Oberfläche (103);

Reduzieren einer Dicke des Halbleiterkörpers (100) durch Abdünnen des Halbleiterkörpers (100) an einer der ersten Oberfläche (103) gegenüberliegenden zweiten Oberfläche (105); und danach

Ausbilden einer Feldstoppzone (1121, 1122) in dem Halbleiterkörper (100) durch Protonenimplantation durch die zweite Oberfläche (105) und Ausheilen des Halbleiterkörpers (100), wobei die Feldstoppzone zumindest teilweise in dem ersten Teil (102) des CZ-Halbleiterkörpers (100) ausgebildet wird, und wobei die Feldstoppzone (1121, 1122) Dotierungsspitzen in verschiedenen vertikalen Distanzen von der zweiten Oberfläche (105) umfasst und wobei eine Sauerstoffkonzentration bei der Dotierungsspitze mit einer größten vertikalen Distanz von der zweiten Oberfläche (105) unter den Dotierungsspitzen der Feldstoppzone auf weniger als 98 % der Sauerstoffkonzentration bei der Dotierungsspitze mit einer kleinsten vertikalen Distanz von der zweiten Oberfläche (105) unter den Dotierungsspitzen der Feldstoppzone (1121, 1122) eingestellt wird.

A method of manufacturing a semiconductor device, comprising:

reducing a concentration of oxygen in a first part (102) of a CZ semiconductor body (100) by a thermal treatment, the first part (102) adjoining a first surface (103) of the semiconductor body (100);

processing the semiconductor body (100) on the first surface (103);

reducing a thickness of the semiconductor body (100) by thinning the semiconductor body (100) on a second surface (105) opposite the first surface (103); and then

Forming a field stop zone (1121, 1122) in the semiconductor body (100) by proton implantation through the second surface (105) and annealing the semiconductor body (100), wherein the field stop zone is formed at least partially in the first part (102) of the CZ semiconductor body (100), and wherein the field stop zone (1121, 1122) has doping tips at different vertical distances from the second surface (10 5) and wherein an oxygen concentration at the doping tip with a greatest vertical distance from the second surface (105) among the doping tips of the field stop zone is set to less than 98% of the oxygen concentration at the doping tip with a smallest vertical distance from the second surface (105) among the doping tips of the field stop zone (1121, 1122).

Description

HINTERGRUNDBACKGROUND

In Halbleitervorrichtungen, zum Beispiel Bipolartransistoren mit isoliertem Gate (IGBTs), Feldeffekttransistoren mit isoliertem Gate (IGFETs) oder Dioden, dient eine niedrige Dotierungskonzentration eines Substratmaterials, zum Beispiel eines CZ-(Czochralski-)Siliziumwafers, dazu, eine gewünschte Gleichspannungs-Sperranforderung der Halbleitervorrichtung zu realisieren. In diesem Zusammenhang wird beispielhaft verwiesen auf den Offenbarungsgehalt in den Druckschriften

Es ist wünschenswert, eine Genauigkeit der Einstellung einer Dotierungskonzentration eines dotierten Halbleitergebiets in einem CZ-Halbleiterkörper zu verbessern.It is desirable to improve an accuracy of setting a doping concentration of a doped semiconductor region in a CZ semiconductor body.

ZUSAMMENFASSUNGSUMMARY

Die vorliegende Offenbarung bezieht sich auf ein Verfahren zum Herstellen einer Halbleitervorrichtung, das ein Reduzieren einer Konzentration von Sauerstoff in einem ersten Teil eines CZ-Halbleiterkörpers durch eine thermische Behandlung umfasst. Der erste Teil grenzt an eine erste Oberfläche des Halbleiterkörpers. Der Halbleiterkörper wird an der ersten Oberfläche bearbeitet. Eine Dicke des Halbleiterkörpers wird reduziert, indem der Halbleiterkörper an einer der ersten Oberfläche gegenüberliegenden zweiten Oberfläche abgedünnt wird. Danach wird eine Feldstoppzone im Halbleiterkörper durch Protonenimplantationen durch die zweite Oberfläche und Ausheilen des Halbleiterkörpers gebildet. Die Feldstoppzone wird zumindest teilweise im ersten Teil des CZ-Halbleiterkörpers ausgebildet.The present disclosure relates to a method of manufacturing a semiconductor device that includes reducing a concentration of oxygen in a first part of a CZ semiconductor body by a thermal treatment. The first part borders on a first surface of the semiconductor body. The semiconductor body is processed on the first surface. A thickness of the semiconductor body is reduced by the semiconductor body being thinned on a second surface opposite the first surface. Thereafter, a field stop zone is formed in the semiconductor body by proton implantations through the second surface and annealing of the semiconductor body. The field stop zone is formed at least partially in the first part of the CZ semiconductor body.

Die vorliegende Offenbarung bezieht sich auch auf eine Halbleitervorrichtung mit einem CZ-Halbleiterkörper mit gegenüberliegenden ersten und zweiten Oberflächen. Die Halbleitervorrichtung umfasst ferner eine Feldstoppzone in dem CZ-Halbleiterkörper. Die Feldstoppzone umfasst eine Vielzahl von Dotierungsspitzen in verschiedenen vertikalen Distanzen von der zweiten Oberfläche. Eine Sauerstoffkonzentration bei einer ersten Dotierungsspitze der Vielzahl von Dotierungsspitzen, die in einer größten vertikalen Distanz von der zweiten Oberfläche gelegen ist, beträgt weniger als 98 % oder weniger als 95 % oder weniger als 90 % oder weniger als 80 % oder weniger als 70 % oder sogar weniger als 50 % der Sauerstoffkonzentration bei einer zweiten Dotierungsspitze der Vielzahl von Dotierungsspitzen, die in einer kürzesten vertikalen Distanz von der zweiten Oberfläche gelegen ist.The present disclosure also relates to a semiconductor device having a CZ semiconductor body with opposing first and second surfaces. The semiconductor device further includes a field stop zone in the CZ semiconductor body. The field stop zone includes a plurality of doping peaks at different vertical distances from the second surface. An oxygen concentration at a first doping peak of the plurality of doping peaks located at a greatest vertical distance from the second surface is less than 98% or less than 95% or less than 90% or less than 80% or less than 70% or even less than 50% of the oxygen concentration at a second doping peak of the plurality of doping peaks located at a shortest vertical distance from the second surface.

Figurenlistecharacter list

Die beigefügten Zeichnungen sind beigeschlossen, um ein weiteres Verständnis der Erfindung zu liefern, und sie sind in diese Beschreibung einbezogen und bilden einen Teil von ihr. Die Zeichnungen veranschaulichen die Ausführungsformen und dienen zusammen mit der Beschreibung zum Erläutern der Prinzipien der Erfindung. Andere Ausführungsformen der Erfindung und beabsichtigte Vorteile werden sofort gewürdigt, da sie unter Hinweis auf die folgende detaillierte Beschreibung besser verstanden werden.

-

1 ist ein Flussdiagramm, das ein Beispiel einer Herstellung einer Halbleitervorrichtung veranschaulicht. -

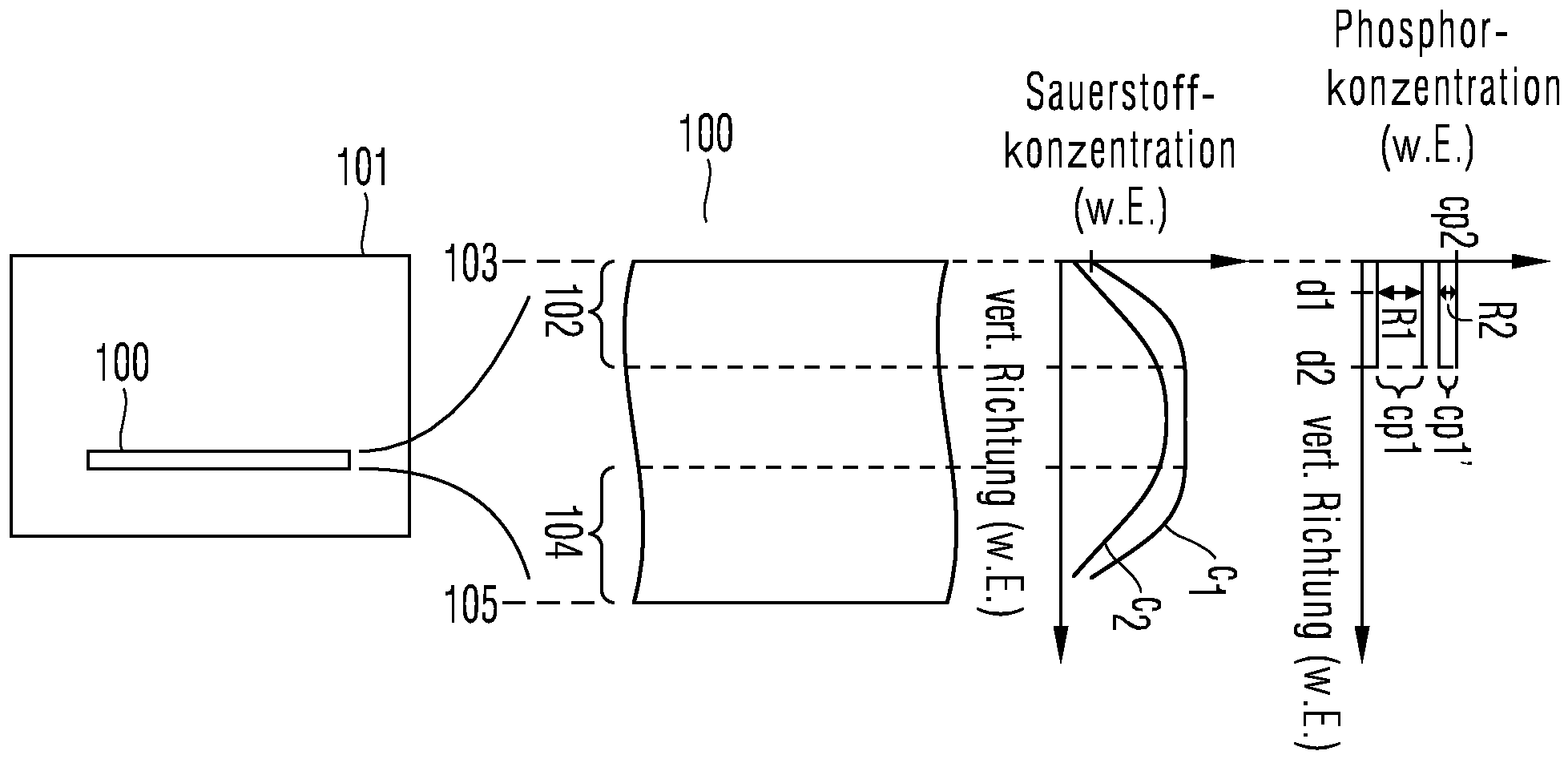

2A zeigt Ansichten, um einen Prozess zum Reduzieren einer Sauerstoffkonzentration in einem ersten Teil eines CZ-Halbleiterkörpers durch eine thermische Behandlung zu veranschaulichen. -

2B ist eine schematische Querschnittsansicht des in2A dargestellten Halbleiterkörpers nach einer Bearbeitung des Halbleiterkörpers an der ersten Oberfläche. -

2C ist eine schematische Querschnittsansicht des in2B dargestellten Halbleiterkörpers nach einem Reduzieren einer Dicke des Halbleiterkörpers durch Abdünnen des Halbleiterkörpers von einer der ersten Oberfläche gegenüberliegenden zweiten Oberfläche aus. -

2D ist eine schematische Querschnittsansicht des in2C dargestellten Halbleiterkörpers nach Ausbilden einer Feldstoppzone in dem Halbleiterkörper durch Protonenimplantationen durch die zweite Oberfläche und Ausheilen des Halbleiterkörpers. -

3 ist eine schematische Querschnittsansicht eines Halbleiterkörpers, um Beispiele von Halbleitervorrichtungen zu veranschaulichen, die eine Feldstoppzone enthalten, die durch ein Verfahren wie in1 dargestellt hergestellt wurde. -

4 ist eine schematische graphische Darstellung, die Profile von Dotierungskonzentrationen entlang einer vertikalen Richtung durch eine Driftzone und eine Feldstoppzone veranschaulicht.

-

1 FIG. 14 is a flowchart illustrating an example of manufacturing a semiconductor device. -

2A FIG. 12 shows views to illustrate a process of reducing an oxygen concentration in a first part of a CZ semiconductor body by a thermal treatment. -

2 B is a schematic cross-sectional view of FIG2A illustrated semiconductor body after processing of the semiconductor body on the first surface. -

2C is a schematic cross-sectional view of FIG2 B illustrated semiconductor body after reducing a thickness of the semiconductor body by thinning the semiconductor body from a second surface opposite the first surface. -

2D is a schematic cross-sectional view of FIG2C illustrated semiconductor body after forming a field stop zone in the semiconductor body by proton implantations through the second surface and annealing the semiconductor body. -

3 Fig. 12 is a schematic cross-sectional view of a semiconductor body to illustrate examples of semiconductor devices including a field stop zone formed by a method as in Fig1 shown. -

4 FIG. 12 is a schematic diagram illustrating profiles of doping concentrations along a vertical direction through a drift region and a field stop region.

DETAILBESCHREIBUNGDETAIL DESCRIPTION

Die Zeichnungen sind nicht maßstabsgetreu und dienen lediglich zu Veranschaulichungszwecken. Zur Klarheit sind die gleichen Elemente mit entsprechenden Bezugszeichen in den verschiedenen Zeichnungen versehen, falls nicht etwas anderes festgestellt wird.The drawings are not to scale and are for illustrative purposes only. For clarity, the same elements have been given corresponding reference numerals in the different drawings unless otherwise noted.

Die Begriffe „haben“, „enthalten“, „umfassen“, „aufweisen“ und dergleichen sind offene Begriffe, und die Begriffe geben das Vorhandensein der festgestellten Strukturen, Elemente oder Merkmale an, schließen jedoch das Vorhandensein von zusätzlichen Elementen oder Merkmalen nicht aus.The terms "having," "including," "comprising," "comprising," and the like are open-ended terms, and the terms indicate the presence of the noted structures, elements, or features, but do not exclude the presence of additional elements or features.

Der Begriff „elektrisch verbunden“ beschreibt eine permanente niederohmige Verbindung zwischen elektrisch verbundenen Elementen, beispielsweise einen direkten Kontakt zwischen den betreffenden Elementen oder eine niederohmige Verbindung über ein Metall und/oder einen hochdotierten Halbleiter. Die Figuren veranschaulichen relative Dotierungskonzentrationen durch Angabe von „-“ oder „+“ neben dem Dotierungstyp „n“ oder „p“. Beispielsweise bedeutet „n-“ eine Dotierungskonzentration, die niedriger als die Dotierungskonzentration eines „n“-Dotierungsgebiets ist, während ein „n+“-Dotierungsgebiet eine höhere Dotierungskonzentration als ein „n“-Dotierungsgebiet hat. Dotierungsgebiete der gleichen relativen Dotierungskonzentration haben nicht notwendigerweise die gleiche absolute Dotierungskonzentration. Beispielsweise können zwei verschiedene „n“-Dotierungsgebiete die gleichen oder verschiedene absolute Dotierungskonzentrationen haben.The term "electrically connected" describes a permanent low-impedance connection between electrically connected elements, for example a direct contact between the relevant elements or a low-impedance connection via a metal and/or a highly doped semiconductor. The figures illustrate relative doping concentrations by specifying " - " or " + " next to the "n" or "p" doping type. For example, " n- " means a doping concentration that is lower than the doping concentration of an "n" doping region, while an "n + " doping region has a higher doping concentration than an "n" doping region. Doping regions of the same relative doping concentration do not necessarily have the same absolute doping concentration. For example, two different "n" doping regions can have the same or different absolute doping concentrations.

Der Begriff „horizontal“, wie dieser in der vorliegenden Beschreibung verwendet ist, soll eine Orientierung im Wesentlichen parallel zu einer ersten oder Hauptoberfläche eines Halbleitersubstrats oder -körpers beschreiben. Diese kann beispielsweise die Oberfläche eines Wafers oder eines Die bzw. eines Chips sein.The term "horizontal" as used in the present specification intends to describe an orientation substantially parallel to a first or main surface of a semiconductor substrate or body. This can be the surface of a wafer or a die or a chip, for example.

Der Begriff „vertikal“, wie dieser in der vorliegenden Beschreibung verwendet wird, soll eine Orientierung beschreiben, die im Wesentlichen senkrecht zu der ersten Oberfläche, d.h. parallel zur Normalenrichtung der ersten Oberfläche, des Halbleitersubstrats oder Halbleiterkörpers angeordnet ist.The term "vertical" as used in the present specification intends to describe an orientation that is essentially perpendicular to the first surface, i.e. parallel to the normal direction of the first surface, the semiconductor substrate or semiconductor body.

In dieser Beschreibung wird eine zweite Oberfläche eines Halbleitersubstrats oder Halbleiterkörpers als durch die untere oder rückseitige Oberfläche gebildet angesehen, während die erste Oberfläche als durch die obere, Vorderseite oder Hauptoberfläche des Halbleitersubstrates gebildet betrachtet wird. Die Ausdrücke „oberhalb“ und „unterhalb“, wie diese in der vorliegenden Beschreibung verwendet werden, sollen daher eine relative Lage eines strukturellen Merkmals zu einem anderen beschreiben.In this description, a second surface of a semiconductor substrate or semiconductor body is considered to be formed by the bottom or back surface, while the first surface is considered to be formed by the top, front or main surface of the semiconductor substrate. The terms "above" and "below" as used in the present specification are therefore intended to describe a relative location of one structural feature to another.

In dieser Beschreibung bezieht sich n-dotiert auf einen ersten Leitfähigkeitstyp, während p-dotiert auf einen zweiten Leitfähigkeitstyp bezogen ist. Alternativ dazu können die Halbleitervorrichtungen mit entgegengesetzten Dotierungsbeziehungen gebildet werden, so dass der erste Leitfähigkeitstyp p-dotiert und der zweite Leitfähigkeitstyp n-dotiert sein können.In this description, n-doped refers to a first conductivity type, while p-doped refers to a second conductivity type. Alternatively, the semiconductor devices can be formed with opposite doping relationships, such that the first conductivity type can be p-doped and the second conductivity type can be n-doped.

Es versteht sich, dass, während das Verfahren 1000 im Folgenden als eine Reihe von Schritten oder Ereignissen veranschaulicht und beschrieben wird, die veranschaulichte Reihenfolge solcher Schritte oder Ereignisse nicht in einem beschränkenden Sinn zu interpretieren ist. Beispielsweise können einige Schritte in verschiedenen Reihenfolgen und/oder gleichzeitig mit anderen Schritten oder Ereignissen abgesehen von jenen, die hierin veranschaulicht und/oder beschrieben werden, erfolgen. Außerdem mögen nicht alle Schritte erforderlich sein, um einen oder mehrere Aspekte von Ausführungsformen der Offenbarung hierin zu implementieren. Auch können ein oder mehrere der hierin dargestellten Schritte in einen oder mehrere separate Teilschritte und/oder Phasen unterteilt werden.It should be understood that while the

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Die Oxidschicht kann beispielsweise vor oder während einer Bearbeitung des Halbleiterkörpers an der ersten Oberfläche vollständig oder teilweise entfernt werden.The oxide layer can be completely or partially removed, for example, before or during processing of the semiconductor body on the first surface.

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

Bezug nehmend auf

In einer oder mehreren Ausführungsformen wird eine Dotierungskonzentration der Dotierungsspitze mit einer größten vertikalen Distanz von der zweiten Oberfläche in einem Bereich von 2 × 1013 cm-3 bis 1 × 1015 cm-3 oder in einem Bereich von 5 × 1013 cm-3 bis 5 × 1014 cm-3 eingestellt. In einer oder mehreren Ausführungsformen können eine Protonenimplantationsenergie und eine Protonenimplantationsdosis zum Ausbilden der Dotierungsspitze unter den Spitzen der Feldstoppzone, die die größte Distanz zur zweiten Oberfläche aufweist, beispielsweise von 1600 keV bis 400 keV und von 2 × 1012 cm-2 bis 2 × 1014 cm-2 oder von 5 × 1012 cm-2 bis 5 × 1013 cm-2 reichen. In einer oder mehreren Ausführungsformen kann eine vertikale Distanz zwischen der Dotierungsspitze unter den Dotierungsspitzen der Feldstoppzone, die eine größte vertikale Distanz von der zweiten Oberfläche aufweist, und der Dotierungsspitze unter den Dotierungsspitzen der Feldstoppzone, die eine kleinste vertikale Distanz von der zweiten Oberfläche aufweist, beispielsweise von 3 µm bis 45 µm oder von 5 µm bis 25 µm reichen. Somit kann ein glattes Dotierungskonzentrationsprofil in der Feldstoppzone infolge einer tolerierbaren unerwünschten Störung eines Ziel-Dotierungsprofils durch sauerstoffbasierte Dotierungskomplexe eingerichtet werden, wodurch beispielsweise ein sanfterer Abschaltprozess von Halbleiter-Leistungsvorrichtungen ermöglicht wird.In one or more embodiments, a doping concentration of the doping peak having a greatest vertical distance from the second surface is set in a range from 2×10 13 cm -3 to 1×10 15 cm -3 or in a range from 5×10 13 cm -3 to 5×10 14 cm -3 . In one or more embodiments, a proton implantation energy and a proton implantation dose for forming the doping peak under the peaks of the field stop zone having the greatest distance to the second surface can range, for example from 1600 keV to 400 keV and from 2×10 12 cm -2 to 2×10 14 cm -2 or from 5×10 12 cm -2 to 5×10 13 cm -2 . In one or more embodiments, a vertical distance between the doping peak among the doping peaks of the field stop zone that has a greatest vertical distance from the second surface and the doping peak among the doping peaks of the field stop zone that has a smallest vertical distance from the second surface can range, for example, from 3 μm to 45 μm or from 5 μm to 25 μm. Thus, a smooth dopant concentration profile can be established in the field stop zone due to tolerable undesired perturbation of a target dopant profile by oxygen-based dopant complexes, thereby enabling a smoother turn-off process of semiconductor power devices, for example.

In einer oder mehreren Ausführungsformen ist die Halbleitervorrichtung eine vertikale Leistungs-Halbleitervorrichtung, und das Verfahren umfasst ferner ein Ausbilden eines ersten Lastanschlusskontakts, der mit der ersten Oberfläche des Halbleiterkörpers elektrisch verbunden ist, und ein Ausbilden eines zweiten Lastanschlusskontakts, der mit der zweiten Oberfläche des Halbleiterkörpers elektrisch verbunden ist. Der erste Lastanschlusskontakt kann beispielsweise Kontaktstecker oder Kontaktleitungen, Metallverdrahtungsleitungen und Kontaktflächen oder Kontaktpads umfassen. Der erste Lastanschlusskontakt kann Teil eines Verdrahtungsgebiets sein, das an die erste Oberfläche des Halbleiterkörpers grenzt. Das Verdrahtungsgebiet kann eine, zwei, drei oder sogar mehr Verdrahtungs- oder Metallebenen umfassen. In einer oder mehreren Ausführungsformen ist eine äußerste Verdrahtungsebene eine Leistungsmetallisierung, zum Beispiel eine Kupferschicht mit einer Dicke von mehr als 5 µm oder mehr als 10 µm oder sogar mehr als 15 µm. Der erste Lastanschlusskontakt kann beispielsweise ein Anodenkontakt sein, der mit einem Anodengebiet einer Leistungsdiode elektrisch verbunden ist, oder ein Sourcekontakt, der mit Source/Bodygebieten von Zellen mit Bipolartransistoren mit isoliertem Gate (IGBT-Zellen) oder Zellen mit Feldeffekttransistoren mit isoliertem Gate (IGFET-Zellen) elektrisch verbunden ist. Der zweite Lastanschlusskontakt kann beispielsweise Kontaktstecker oder Kontaktleitungen, Metallverdrahtungsleitungen und Kontaktflächen oder Kontaktpads umfassen. Der zweite Lastanschlusskontakt kann Teil eines Verdrahtungsgebiets sein, das an die zweite Oberfläche des Halbleiterkörpers grenzt. Das Verdrahtungsgebiet kann eine, zwei, drei oder sogar mehr Verdrahtungs- oder Metallebenen umfassen. In einer oder mehreren Ausführungsformen ist eine äußerste Verdrahtungsebene eine Leistungsmetallisierung, zum Beispiel eine Kupferschicht mit einer Dicke von mehr als 5 µm oder mehr als 10 µm oder sogar mehr als 15 µm. Der zweite Lastanschlusskontakt kann zum Beispiel ein Kathodenkontakt sein, der mit einem Kathodengebiet einer Leistungsdiode elektrisch verbunden ist, oder ein rückseitiger Emitterkontakt, der mit einem rückseitigen Emittergebiet von Zellen mit Bipolartransistoren mit isoliertem Gate (IGBT-Zellen) elektrisch verbunden ist, oder ein Drainkontakt, der mit einem Draingebiet von Zellen von Feldeffekttransistoren mit isoliertem Gate (IGFET-Zellen) wie etwa Leistungs-Metalloxid-Halbleiter-Feldeffekttransistoren (Leistungs-MOSFETs), elektrisch verbunden ist.In one or more embodiments, the semiconductor device is a vertical power semiconductor device, and the method further comprises forming a first load terminal contact electrically connected to the first surface of the semiconductor body and forming a second load terminal contact electrically connected to the second surface of the semiconductor body. The first load terminal contact may include, for example, contact plugs or contact lines, metal wiring lines, and contact surfaces or contact pads. The first load terminal contact may be part of a wiring region that borders the first surface of the semiconductor body. The wiring area may include one, two, three or even more levels of wiring or metal. In one or more embodiments, an outermost wiring level is a power metallization, for example a copper layer with a thickness of more than 5 μm or more than 10 μm or even more than 15 μm. The first load terminal contact may be, for example, an anode contact electrically connected to an anode region of a power diode, or a source contact electrically connected to source/body regions of insulated gate bipolar transistor (IGBT) cells or insulated gate field effect transistor (IGFET) cells. The second load connection contact can, for example, contact plugs or contact lines, metal wiring lines, and contact pads. The second load terminal contact may be part of a wiring region that borders the second surface of the semiconductor body. The wiring area may include one, two, three or even more levels of wiring or metal. In one or more embodiments, an outermost wiring level is a power metallization, for example a copper layer with a thickness of more than 5 μm or more than 10 μm or even more than 15 μm. The second load terminal contact may be, for example, a cathode contact that is electrically connected to a cathode region of a power diode, or a back emitter contact that is electrically connected to a back emitter region of insulated gate bipolar transistor (IGBT) cells, or a drain contact that is electrically connected to a drain region of insulated gate field effect transistor (IGFET) cells, such as power metal-oxide semiconductor field effect transistors (power MOSFETs).

Das oben beschriebene Verfahren 1000 ermöglicht ein Entfernen unerwünschter Dotierstoffe, zum Beispiel donatorartiger Komplexe wie etwa CiOiHn, aus dem Halbleiterkörper durch Ausdiffusion von Sauerstoff- und/oder Kohlenstoffverunreinigungen aus dem Halbleiterkörper. Dies erlaubt es, eine Dotierungskonzentration von funktionalen Halbleitergebieten wie etwa Feldstoppzonen im Halbleiterkörper präzise einzustellen.The

Die Ansichten von

Ein Vorhandensein oder Fehlen einer Oxidschicht auf der ersten Oberfläche während einer thermischen Behandlung ermöglicht es, ein Profil einer Phosphorkonzentration in Richtung der ersten Oberfläche einzustellen. Wenn die Oxidschicht weggelassen wird, kann eine erste Phosphorkonzentration cp1 in dem Halbleiterkörper in einer ersten vertikalen Distanz d1 von 1 µm zur ersten Oberfläche in einem ersten Bereich R1 von 10 % bis 50 % einer zweiten Phosphorkonzentration cp2 in dem Halbleiterkörper in einer zweiten vertikalen Distanz d2 von 10 µm zur ersten Oberfläche eingestellt werden. Die Oxidschicht kann eine Ausdiffusion von Phosphor behindern, und eine erste Phosphorkonzentration cp1' im Halbleiterkörper in einer ersten vertikalen Distanz d1 von 1 µm zur ersten Oberfläche kann in einem zweiten Bereich R2 von 95 % bis 100 % einer zweiten Phosphorkonzentration cp2 im Halbleiterkörper in einer zweiten vertikalen Distanz d2 von 10 µm zur ersten Oberfläche eingestellt werden.A presence or absence of an oxide layer on the first surface during a thermal treatment makes it possible to adjust a profile of a phosphorus concentration towards the first surface. If the oxide layer is omitted, a first phosphorus concentration cp1 in the semiconductor body at a first vertical distance d1 of 1 µm to the first surface can be set in a first region R1 of 10% to 50% of a second phosphorus concentration cp2 in the semiconductor body at a second vertical distance d2 of 10 µm to the first surface. The oxide layer can prevent out-diffusion of phosphorus, and a first phosphorus concentration cp1' in the semiconductor body at a first vertical distance d1 of 1 µm from the first surface can be adjusted in a second range R2 from 95% to 100% of a second phosphorus concentration cp2 in the semiconductor body at a second vertical distance d2 of 10 µm from the first surface.

Die Querschnittsansicht von

Die Querschnittsansicht von

Die Querschnittsansicht von

In dem linken eingekreisten Teil des bearbeiteten Bereichs 107 ist ein erster Lastkontakt L1 einer Leistungsdiode, zum Beispiel ein Anodenelektrodenkontakt, mit einem p+-dotierten Anodengebiet 125 elektrisch verbunden. Das p+-dotierte Anodengebiet 125 kann zum Beispiel gebildet werden, wenn Prozessmerkmal S110 ausgeführt wird.In the left circled part of the machined area 107 a first load contact L1 of a power diode, for example an anode electrode contact, is electrically connected to a p + -doped

In dem rechten eingekreisten Teil des bearbeiteten Bereichs 107 ist ein erster Lastkontakt L1 eines Bipolartransistors mit isoliertem Gate, zum Beispiel ein Sourceelektrodenkontakt, mit einem p-dotierten Bodygebiet 126 und mit einem n+-dotierten Sourcegebiet 127 elektrisch verbunden. Überdies ist mit einer Gateelektrode 128 ein Steuerelektrodenkontakt C, zum Beispiel ein Gateelektrodenkontakt, elektrisch verbunden. Ein Gatedielektrikum 129 ist zwischen der Gateelektrode 128 und einer Driftzone 113 angeordnet. Der erste Lastkontakt L1, das p-dotierte Bodygebiet 126, das n+-dotierte Sourcegebiet 127, die Gateelektrode 128 und das Gatedielektrikum 129 können zum Beispiel gebildet werden, wenn Prozessmerkmal S110 von

In dem linken eingekreisten Teil an der Unterseite des Halbleiterkörpers 100 ist ein zweiter Lastkontakt L2, zum Beispiel ein Kathodenelektrodenkontakt, mit einem n+-dotierten Kathodengebiet 130 elektrisch verbunden. Das n+-dotierte Kathodengebiet 130 kann nach Abdünnen des Halbleiterkörpers 100 durch einen Dotierungsprozess gebildet werden und kann an eine Feldstoppzone 112 grenzen, die beispielsweise durch das in

In dem rechten eingekreisten Teil an der Unterseite des Halbleiterkörpers 100 ist ein zweiter Lastkontakt L2, zum Beispiel ein rückseitiger Emitterelektrodenkontakt, mit einem p+-dotierten rückseitigen Emittergebiet 131 elektrisch verbunden. Das p+-dotierte rückseitige Emittergebiet 131 kann beispielsweise nach Abdünnen des Halbleiterkörpers 100 durch einen Dotierungsprozess oder vorher durch eine Schichtabscheidung und -dotierung gebildet werden.In the right circled part on the underside of the

In einer oder mehreren Ausführungsformen nimmt ein Dotierungskonzentrationsprofil der Feldstoppzone entlang der vertikalen Richtung von ersten Oberfläche zur zweiten Oberfläche von der Dotierungsspitze mit der größten vertikalen Distanz von der zweiten Oberfläche unter den Dotierungsspitzen der Feldstoppzone, zum Beispiel der in

In einer oder mehreren Ausführungsformen wird eine Dotierungskonzentration der Dotierungsspitze mit einer größten vertikalen Distanz von der zweiten Oberfläche, zum Beispiel die Konzentration cDP1 der Dotierungsspitze, in einem Bereich von 8 x 1013 cm-3 bis 2 × 1015 cm-3 eingestellt.In one or more embodiments, a doping concentration of the doping tip having a greatest vertical distance from the second surface, for example the concentration cDP1 of the doping tip, is set in a range from 8×10 13 cm -3 to 2×10 15 cm -3 .

Eine Störung der präzisen Einstellung einer Dotierungskonzentration durch eine unerwünschte Dotierung, die durch Verunreinigungen in einem Basismaterial, zum Beispiel Sauerstoffkomplexe in CZ-Silizium, erzeugt wird, kann durch das in

Claims (23)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102017118975.0A DE102017118975B4 (en) | 2017-08-18 | 2017-08-18 | SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY AND METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY |

| JP2018152796A JP7193267B2 (en) | 2017-08-18 | 2018-08-15 | Semiconductor device including CZ semiconductor body and method of manufacturing semiconductor device including CZ semiconductor body |

| CN201810941686.2A CN109411344B (en) | 2017-08-18 | 2018-08-17 | Semiconductor device including a CZ semiconductor body and method of manufacturing a semiconductor device including a CZ semiconductor body |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102017118975.0A DE102017118975B4 (en) | 2017-08-18 | 2017-08-18 | SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY AND METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| DE102017118975A1 DE102017118975A1 (en) | 2019-02-21 |

| DE102017118975B4 true DE102017118975B4 (en) | 2023-07-27 |

Family

ID=65234743

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| DE102017118975.0A Active DE102017118975B4 (en) | 2017-08-18 | 2017-08-18 | SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY AND METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP7193267B2 (en) |

| CN (1) | CN109411344B (en) |

| DE (1) | DE102017118975B4 (en) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019181852A1 (en) | 2018-03-19 | 2019-09-26 | 富士電機株式会社 | Semiconductor device and method for manufacturing semiconductor device |

| WO2021070539A1 (en) | 2019-10-11 | 2021-04-15 | 富士電機株式会社 | Semiconductor device and method for producing semiconductor device |

| CN113875016B (en) * | 2019-12-17 | 2025-04-22 | 富士电机株式会社 | Semiconductor devices |

| JP7334849B2 (en) * | 2020-03-17 | 2023-08-29 | 信越半導体株式会社 | Method for controlling donor concentration in silicon single crystal substrate |

| JP7264100B2 (en) * | 2020-04-02 | 2023-04-25 | 信越半導体株式会社 | Method for controlling donor concentration in silicon single crystal substrate |

| DE102020110072A1 (en) * | 2020-04-09 | 2021-10-14 | Infineon Technologies Ag | VERTICAL POWER SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD |

| JP7446212B2 (en) | 2020-12-07 | 2024-03-08 | 三菱電機株式会社 | Semiconductor device and its manufacturing method |

| WO2024122541A1 (en) * | 2022-12-08 | 2024-06-13 | 富士電機株式会社 | Semiconductor device and method for manufacturing semiconductor device |

| JPWO2025028573A1 (en) * | 2023-08-01 | 2025-02-06 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20110042791A1 (en) | 2006-01-20 | 2011-02-24 | Infineon Technologies Austria Ag | Method for treating an oxygen-containing semiconductor wafer, and semiconductor component |

| US20160093690A1 (en) | 2014-09-30 | 2016-03-31 | Infineon Technologies Ag | Soft switching semiconductor device and method for producing thereof |

| US20180012762A1 (en) | 2015-09-16 | 2018-01-11 | Fuji Electric Co., Ltd. | Semiconductor device and method of manufacturing semiconductor device |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06168887A (en) * | 1992-11-30 | 1994-06-14 | Sony Corp | Thermal oxidation of semiconductor wafer |

| JP3729955B2 (en) * | 1996-01-19 | 2005-12-21 | 株式会社半導体エネルギー研究所 | Method for manufacturing semiconductor device |

| US6893907B2 (en) * | 2002-06-05 | 2005-05-17 | Applied Materials, Inc. | Fabrication of silicon-on-insulator structure using plasma immersion ion implantation |

| JP5188673B2 (en) * | 2005-06-09 | 2013-04-24 | 株式会社Sumco | Silicon wafer for IGBT and method for manufacturing the same |

| DE102006002903A1 (en) * | 2006-01-20 | 2007-08-02 | Infineon Technologies Austria Ag | Treatment of oxygen-containing semiconductor wafer, comprises irradiating second side of wafer with high-energy particles to produce crystal defects in second semiconductor region of wafer, and heating wafer |

| JP2008177296A (en) * | 2007-01-17 | 2008-07-31 | Toyota Central R&D Labs Inc | Semiconductor device, PN diode, IGBT, and manufacturing method thereof |

| US7879699B2 (en) * | 2007-09-28 | 2011-02-01 | Infineon Technologies Ag | Wafer and a method for manufacturing a wafer |

| JPWO2009151077A1 (en) * | 2008-06-10 | 2011-11-17 | 株式会社Sumco | Manufacturing method of silicon single crystal wafer and silicon single crystal wafer |

| JP2011054655A (en) * | 2009-08-31 | 2011-03-17 | Sumco Corp | Silicon wafer for high-frequency device and manufacturing method thereof |

| EP2793266B1 (en) * | 2011-12-15 | 2020-11-11 | Fuji Electric Co., Ltd. | Method for manufacturing a semiconductor device |

| CN104205293B (en) * | 2012-03-30 | 2017-09-12 | 帝人株式会社 | Manufacturing method of semiconductor device |

| CN103730356A (en) * | 2013-12-31 | 2014-04-16 | 上海集成电路研发中心有限公司 | Method for manufacturing back face of power semiconductor device |

| US10211325B2 (en) * | 2014-01-28 | 2019-02-19 | Infineon Technologies Ag | Semiconductor device including undulated profile of net doping in a drift zone |

| WO2016051973A1 (en) * | 2014-10-03 | 2016-04-07 | 富士電機株式会社 | Semiconductor device and semiconductor device manufacturing method |

| DE102014114683B4 (en) * | 2014-10-09 | 2016-08-04 | Infineon Technologies Ag | METHOD FOR PRODUCING A SEMICONDUCTOR WAFERS WITH A LOW CONCENTRATION OF INTERSTITIAL OXYGEN |

| CN105206516B (en) * | 2015-08-21 | 2018-01-12 | 中国东方电气集团有限公司 | A kind of method for forming field cutoff layer in the semiconductor device |

-

2017

- 2017-08-18 DE DE102017118975.0A patent/DE102017118975B4/en active Active

-

2018

- 2018-08-15 JP JP2018152796A patent/JP7193267B2/en active Active

- 2018-08-17 CN CN201810941686.2A patent/CN109411344B/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20110042791A1 (en) | 2006-01-20 | 2011-02-24 | Infineon Technologies Austria Ag | Method for treating an oxygen-containing semiconductor wafer, and semiconductor component |

| US20160093690A1 (en) | 2014-09-30 | 2016-03-31 | Infineon Technologies Ag | Soft switching semiconductor device and method for producing thereof |

| US20180012762A1 (en) | 2015-09-16 | 2018-01-11 | Fuji Electric Co., Ltd. | Semiconductor device and method of manufacturing semiconductor device |

Non-Patent Citations (2)

| Title |

|---|

| SHUI, Q. [et. al.]: Intrinsic gettering of Czochralski silicon annealed in argon. In: Physica B, Vol. 307, 2001, S. 40 - 44 |

| SHUI, Q. [et. al.]: Intrinsic gettering of Czochralski silicon annealed in argon. In: Physica B, Vol. 307, 2001, S. 40 - 44. |

Also Published As

| Publication number | Publication date |

|---|---|

| CN109411344A (en) | 2019-03-01 |

| JP2019062189A (en) | 2019-04-18 |

| JP7193267B2 (en) | 2022-12-20 |

| DE102017118975A1 (en) | 2019-02-21 |

| CN109411344B (en) | 2024-01-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| DE102017118975B4 (en) | SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY AND METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A CZ SEMICONDUCTOR BODY | |

| DE102013107632B4 (en) | Process for manufacturing semiconductor devices by ion implantation | |

| DE102012102341B4 (en) | Semiconductor component and substrate with chalcogen-doped area | |

| DE102016120771B3 (en) | A method of fabricating semiconductor devices and semiconductor device containing hydrogen-correlated donors | |

| DE102012209429B4 (en) | POWER SEMICONDUCTOR DEVICES WITH HIGH VOLTAGE WITHSTANDING ELEMENTS AND PROCESS FOR THEIR MANUFACTURE | |

| DE102013225320B4 (en) | Method for producing a semiconductor device | |

| DE102013111792B4 (en) | METHOD FOR PROCESSING A SEMICONDUCTOR CARRIER | |

| DE102015112648B4 (en) | METHOD OF FORMING A WAFER STRUCTURE, METHOD OF FORMING A SEMICONDUCTOR COMPONENT AND A WAFER STRUCTURE | |

| EP0025854B1 (en) | Method of making bipolar transistors | |

| DE102018215731B4 (en) | Semiconductor device and method of manufacturing same | |

| DE102017102127B4 (en) | Method of manufacturing semiconductor devices using epitaxy and semiconductor devices with a lateral structure | |

| DE102016119799B4 (en) | INTEGRATED CIRCUIT CONTAINING A CURVED CAVE AND PRODUCTION METHOD | |

| DE102014117538A1 (en) | A method of manufacturing semiconductor devices using light ion implantation and semiconductor device | |

| DE112014001208B4 (en) | Method for manufacturing a semiconductor device | |

| DE102006055068A1 (en) | Semiconductor device with improved insulated gate bipolar transistor and method for its production | |

| DE112014005614T5 (en) | Method for producing a semiconductor device | |

| US5872047A (en) | Method for forming shallow junction of a semiconductor device | |

| US6703294B1 (en) | Method for producing a region doped with boron in a SiC-layer | |

| DE102017121693B4 (en) | doping process | |

| DE112014004395T5 (en) | A method of manufacturing a silicon carbide semiconductor device | |

| DE102017128247A1 (en) | A method of manufacturing a semiconductor device having first and second field stop zone regions | |

| DE112012001986B4 (en) | Bipolar punch-through semiconductor component and method for producing such a semiconductor component | |

| DE102016122217B4 (en) | METHOD OF THINNING SUBSTRATES | |

| DE102015121890A1 (en) | Process for processing a semiconductor wafer | |

| DE112006001791B4 (en) | Non-punch-through high voltage IGBT for switching power supplies and method of making same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| R012 | Request for examination validly filed | ||

| R016 | Response to examination communication | ||

| R016 | Response to examination communication | ||

| R018 | Grant decision by examination section/examining division | ||

| R020 | Patent grant now final | ||

| R082 | Change of representative | ||

| R079 | Amendment of ipc main class |

Free format text: PREVIOUS MAIN CLASS: H01L0021322000 Ipc: H10P0095400000 |