CN112367088B - Encoding method and device based on index matrix - Google Patents

Encoding method and device based on index matrix Download PDFInfo

- Publication number

- CN112367088B CN112367088B CN202011166798.9A CN202011166798A CN112367088B CN 112367088 B CN112367088 B CN 112367088B CN 202011166798 A CN202011166798 A CN 202011166798A CN 112367088 B CN112367088 B CN 112367088B

- Authority

- CN

- China

- Prior art keywords

- matrix

- index matrix

- check

- sub

- calculating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000011159 matrix material Substances 0.000 title claims abstract description 204

- 238000000034 method Methods 0.000 title claims abstract description 16

- 238000012795 verification Methods 0.000 claims description 4

- 238000010276 construction Methods 0.000 claims description 3

- 238000005516 engineering process Methods 0.000 abstract description 4

- 238000010586 diagram Methods 0.000 description 5

- 238000004891 communication Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2703—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques the interleaver involving at least two directions

- H03M13/2707—Simple row-column interleaver, i.e. pure block interleaving

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/11—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits using multiple parity bits

- H03M13/1102—Codes on graphs and decoding on graphs, e.g. low-density parity check [LDPC] codes

- H03M13/1148—Structural properties of the code parity-check or generator matrix

- H03M13/116—Quasi-cyclic LDPC [QC-LDPC] codes, i.e. the parity-check matrix being composed of permutation or circulant sub-matrices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2735—Interleaver using powers of a primitive element, e.g. Galois field [GF] interleaver

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/27—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes using interleaving techniques

- H03M13/2742—Irregular interleaver wherein the permutation pattern is not obtained by a computation rule, e.g. interleaver based on random generators

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Probability & Statistics with Applications (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Computing Systems (AREA)

- Error Detection And Correction (AREA)

- Detection And Correction Of Errors (AREA)

Abstract

The embodiment of the invention discloses an encoding method and device based on an index matrix. The method comprises the following steps: determining a check code type of the low-density parity check code according to the service parameters; determining a Galois field according to the check code pattern, and calculating to obtain all elements in the Galois field; calculating to obtain a pseudo-random interleaving sequence according to all the elements; determining a matrix configuration of an index matrix to be constructed; assigning the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration to construct and obtain an index matrix; and performing iterative coding on each subblock based on the registers with the same number of subblocks in the index matrix to generate a coded code word. The embodiment of the invention can greatly reduce the storage requirement on a hardware system and solve the problems of limited hardware resources and difficult realization of the high-performance LDPC code in the space mission. Meanwhile, the encoding speed can be improved by adopting the parallel encoding technology based on the index matrix.

Description

Technical Field

The present invention relates to the field of coding technologies, and in particular, to an index matrix-based coding method and apparatus.

Background

Quasi-cyclic low-density parity-check (QC-LDPC) codes are one of the new air interface (5G-NR) standard codes of the fifth generation mobile communication technology. The performance of the LDPC code is related to the code length and the code rate, the longer the code length, the better the performance, in an aerospace task, the LDPC code with excellent performance can effectively reduce the weight, the volume and the power consumption of a radio frequency system, however, the LDPC code with excellent performance also means that a large amount of hardware storage space is needed, and the difficulty of on-orbit implementation is higher.

Disclosure of Invention

The technical problem solved by the invention is as follows: the defects of the prior art are overcome, and an encoding method and device based on an index matrix are provided.

In order to solve the above technical problem, an embodiment of the present invention provides an encoding method based on an index matrix, including:

determining a check code type of the low-density parity check code according to the service parameters;

determining a Galois field according to the check code pattern, and calculating to obtain all elements in the Galois field;

calculating to obtain a pseudo-random interleaving sequence according to all the elements;

determining a matrix configuration of an index matrix to be constructed;

assigning the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration to construct and obtain an index matrix;

and performing iterative coding on each subblock based on the registers with the same number of subblocks in the index matrix to generate a coded code word.

Optionally, the determining a check code pattern of the low density parity check code according to the service parameter includes:

and determining the check code type of the low-density parity check code according to the information bit length, the bit error rate and the bit signal to noise ratio.

Optionally, determining a galois field according to the check code pattern, and calculating to obtain all elements in the galois field, including:

determining the size of a sub-matrix in a check matrix according to the check code pattern;

calculating to obtain the Galois field according to the size of the submatrix and a preset formula;

and expanding the Galois field to obtain all elements in the Galois field.

Optionally, the calculating a pseudo-random interleaving sequence according to all the elements includes:

inquiring a bias factor and a skip factor corresponding to each non-zero submatrix in a matrix to be constructed according to a preset standard;

and generating the pseudo-random interleaving sequence according to the bias factor and the skip factor.

Optionally, the assigning the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration to construct an index matrix, where the assigning includes:

acquiring a sub-matrix position corresponding to the pseudo-random interleaving sequence in the index matrix to be constructed according to the matrix configuration;

storing the elements in the pseudo-random interleaving sequence into the position of the sub-matrix one by one according to columns;

and repeatedly executing the step of storing the elements in the pseudo-random interleaving sequence into the positions of the sub-matrixes one by one according to columns until all the positions of the sub-matrixes are filled, and then generating the index matrix.

Optionally, the performing iterative encoding on each subblock based on the same number of registers of the subblocks in the index matrix to generate an encoded codeword includes:

dividing the index matrix into sub-blocks according to rows to obtain a plurality of sub-blocks;

respectively calculating by utilizing each subblock to obtain verification information;

repeatedly executing the step of respectively calculating and obtaining the check information by utilizing each subblock to obtain a check sequence and an information sequence;

and combining the check sequence and the information sequence to form the coding code word.

In order to solve the above technical problem, an embodiment of the present invention further provides an encoding apparatus based on an index matrix, including:

the check code type determining module is used for determining the check code type of the low-density parity check code according to the service parameters;

the all-element calculation module is used for determining a Galois field according to the check code type and calculating all elements in the Galois field;

the interleaving sequence calculation module is used for calculating to obtain a pseudo-random interleaving sequence according to all the elements;

the matrix configuration determining module is used for determining the matrix configuration of the index matrix to be constructed;

the index matrix construction module is used for carrying out assignment on the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration to construct and obtain an index matrix;

and the code word generating module is used for executing iterative coding on each subblock based on the registers with the same number of subblocks in the index matrix to generate a code word.

Optionally, the check code pattern determining module includes:

and the check code character determining unit is used for determining the check code type of the low-density parity check code according to the information bit length, the bit error rate and the bit signal to noise ratio.

Optionally, the all elements calculation module includes:

the sub-matrix size determining unit is used for determining the size of a sub-matrix in the check matrix according to the check code pattern;

the Galois field calculating unit is used for calculating to obtain the Galois field according to the size of the submatrix and a preset formula;

and the all-element acquisition unit is used for expanding the Galois field to obtain all the elements in the Galois field.

Optionally, the interleaving sequence calculating module includes:

the offset factor query unit is used for querying an offset factor and a skip factor corresponding to each non-zero submatrix in the matrix to be constructed according to a preset standard;

and the interleaving sequence generating unit is used for generating the pseudo-random interleaving sequence according to the bias factor and the skip factor.

Optionally, the index matrix building module includes:

a matrix position obtaining unit, configured to obtain, according to the matrix configuration, a sub-matrix position corresponding to the pseudorandom interleaving sequence in the index matrix to be constructed;

an element storage position unit, which is used for storing the elements in the pseudo-random interleaving sequence into the position of the sub-matrix one by one according to columns;

and the index matrix generating unit is used for repeatedly executing the element storage position unit until all the sub-matrix positions are filled, and then generating the index matrix.

Optionally, the code word generating module includes:

a plurality of subblock obtaining units, configured to divide the index matrix into subblocks according to rows to obtain a plurality of subblocks;

the check information calculation unit is used for calculating by using each subblock to obtain check information;

a check sequence obtaining unit for repeatedly executing the check information calculating unit to obtain a check sequence and an information sequence;

and the code word forming unit is used for combining the check sequence and the information sequence to form the code word.

Compared with the prior art, the invention has the advantages that:

the embodiment of the invention adopts the index matrix to replace the check matrix, can greatly reduce the storage requirement on a hardware system, and solves the problems of limited hardware resources and difficult realization of the high-performance LDPC code in the space mission. Meanwhile, the encoding speed can be improved by adopting the parallel encoding technology based on the index matrix.

Drawings

Fig. 1 is a flowchart illustrating steps of an encoding method based on an index matrix according to an embodiment of the present invention;

FIG. 2 is a schematic diagram of a base matrix according to an embodiment of the present invention;

FIG. 3 is a schematic diagram of an index matrix configuration according to an embodiment of the present invention;

FIG. 4 is a diagram illustrating parallel encoding based on an index matrix according to an embodiment of the present invention;

fig. 5 is a schematic structural diagram of an encoding apparatus based on an index matrix according to an embodiment of the present invention.

Detailed Description

Example one

Referring to fig. 1, a flowchart illustrating steps of an encoding method based on an index matrix according to an embodiment of the present invention is shown, and as shown in fig. 1, the encoding method based on the index matrix may specifically include the following steps:

step 101: and determining the check code type of the low-density parity check code according to the service parameters.

The embodiment of the invention can be applied to a scene of coding based on the index matrix.

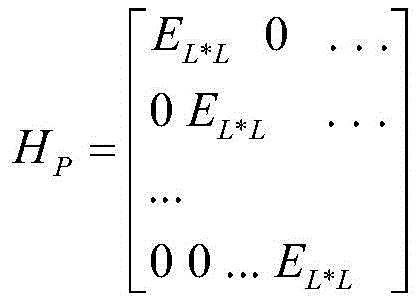

The method mainly comprises two parts of constructing an index matrix and implementing parallel coding. The first part is to construct an index matrix according to actual requirements, the check matrix of QC-LDPC is composed of submatrices with similar structures, and the check matrix of LDPC is set as H (N-K)*N (N is the codeword length and K is the information sequence length), the size of the sub-matrix is L x L, and the matrix can be decomposed into

H=[H S H P ]

Wherein, the matrix H P Is a known dual diagonal matrix

Matrix H S Is a matrix to be solved and is also composed of similar sub-matrices

In the above formula, H i,j (i=1...m b ,j=1...k b ) Both row weight and column weight of 1,m b And k b The number of rows and columns of the sub-matrix, respectively.

The service parameter refers to a service parameter for determining a code pattern of the low density parity check code, and in this example, the service parameter may include parameters such as an information bit length, a bit error rate, and a bit signal to noise ratio.

Selecting a Code type of an LDPC (Low Density Parity Check Code) Code according to actual requirements, wherein the actual requirements comprise: information bit length, bit error rate, bit signal to noise ratio, etc. For example: bit error rate requirement of 10 -6 The information bit length is 1016, the signal-to-noise ratio of the device is not less than 2.12, and a code (2032,1016) with a code rate of 0.5 can be selected.

After the check pattern is determined, step 102 is performed.

Step 102: and determining a Galois field according to the check code pattern, and calculating to obtain all elements in the Galois field.

After the check code pattern is obtained, the galois field may be determined according to the check code pattern, and all elements in the galois field are obtained through calculation, which may be specifically described in detail in conjunction with the following specific implementation manner.

In a specific implementation of the present invention, the step 102 may include:

substep A1: determining the size of a sub-matrix in a check matrix according to the check code pattern;

substep A2: calculating to obtain the Galois field according to the size of the submatrix and a preset formula;

substep A3: and unfolding the Galois field to obtain all elements in the Galois field.

In an embodiment of the invention, a galois field is determined and all the elements in the field are calculated according to the selected code pattern. Verification can be determined according to LDPC code patternSub-matrix size (L x L) in the matrix, galois field GF (2) m ) Can be calculated from the following formula;

L=2 m -1

according to the Galois field GF (2) m ) The generator polynomial of (c) may compute all the elements in the domain. For example: the sub-matrix size of the (2032,1016) code is 127 × 127, and the galois field is GF (2) 7 ) Expanding the galois field yields all 128 elements in the field as shown in table 1:

table 1:

after all elements in the galois field are computed, step 103 is performed.

Step 103: and calculating to obtain a pseudo-random interleaving sequence according to all the elements.

After all elements in the galois field are computed, the pseudo-random interleaving sequence can be computed from all elements, and in particular, the following detailed description can be incorporated.

In another specific implementation manner of the present invention, the step 103 may include:

substep B1: inquiring a bias factor and a skip factor corresponding to each non-zero submatrix in a matrix to be constructed according to a preset standard;

substep B2: and generating the pseudo-random interleaving sequence according to the bias factor and the skip factor.

In the embodiment of the invention, the H is queried according to the GJB7296-2011 standard S Bias factors theta and jump factors rho corresponding to each non-zero submatrix, and each group of bias factors theta and jump factors rho can generate a pseudo-random interleaving sequence pointing to the matrix H S All non-zero elements in the neutron matrix. Biasing by Table 1The factor theta and the jump factor rho are respectively expressed by Galois field elements i, j;

f(α i )=(θ) d

f(α j )=(ρ) d

wherein the function f () represents the mapping relationship of a Galois field element to a decimal number ") d Indicating that the number in parentheses is decimal. Then a pseudo-random interleaving sequence may be generated:

f(α i ,(α j ) 0 ),f(α i ,(α j ) 1 ),...,f(α i ,(α j ) L-1 )

thus, the position of a non-zero element in a sub-matrix may be represented as

(1,f(α i ,(α j ) 0 )),(2,f(α i ,(α j ) 1 )),...,(L,f(α i ,(α j ) L-1 ))

(1,f(α i ,(α j ) 0 )),(2,f(α i ,(α j ) 1 )),...,(L,f(α i ,(α j ) L-1 ))

After the pseudo-random interleaving sequence is calculated, step 104 is performed.

Step 104: and determining the matrix configuration of the index matrix to be constructed.

The matrix configuration refers to the configuration of an index matrix to be constructed.

After the pseudo-random interleaving sequence is obtained through calculation, the matrix configuration of the index matrix to be constructed may be determined, and specifically, in order to obtain good communication performance, the check matrix is usually large, for example: the check matrix size of the (2032,1016) code is 1016 × 2032, and the requirement on hardware system storage is high. The index matrix is configured as follows:

(1) And querying a basic matrix of the GJB7296-2011 standard construction code pattern, wherein the basic matrix is a simplified check matrix, and a sub-matrix is used as an element of the basic matrix. Taking (2032,1016) code as an example, the basic matrix is shown in fig. 2, where each element in the matrix represents a sub-matrix with a size of L × L, and the value of the element represents the row weight (column weight) of the sub-matrix.

(2) And constructing an index matrix configuration. Calculating H in the basis matrix S Number m of non-zero elements of each line of the part s The configuration of the index matrix is shown in fig. 3. The red part is the part of the check matrix, of which the submatrix corresponds to the index matrix. The column number of the index matrix is greatly reduced by m compared to the check matrix s N is less than or equal to N. For example: the (2032,1016) code has a check matrix size of 1016 × 2032, but has an index matrix size of 1016 × 5.

After the matrix configuration is determined, step 105 is performed.

Step 105: and assigning the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration to construct and obtain the index matrix.

After the matrix configuration is determined, the index matrix to be constructed may be assigned based on the pseudo-random interleaving sequence and the matrix configuration to construct an index matrix, which may be described in detail in conjunction with the following specific implementation manner.

In another specific implementation manner of the present invention, the step 105 may include:

substep C1: acquiring a sub-matrix position corresponding to the pseudo-random interleaving sequence in the index matrix to be constructed according to the matrix configuration;

and a substep C2: storing the elements in the pseudo-random interleaving sequence into the position of the sub-matrix one by one according to columns;

substep C3: and repeatedly executing the step of storing the elements in the pseudo-random interleaving sequence into the positions of the sub-matrixes one by one according to columns until all the positions of the sub-matrixes are filled, and generating the index matrix.

In the embodiment of the invention, the index matrix is assigned one by taking the submatrix as a unit, and firstly, the position of the corresponding submatrix of the pseudo-random interleaving sequence in the step 3 is determined; then, storing the elements in the pseudo-random interleaving sequence into an index matrix one by one according to columns; repeating the above steps until all the positions of the index matrix are filled.

After the index matrix is constructed, step 106 is performed.

Step 106: and performing iterative coding on each subblock based on the registers with the same number of subblocks in the index matrix to generate a coded code word.

After the index matrix is constructed, iterative encoding may be performed on each subblock based on the registers with the same number of subblocks in the index matrix to generate an encoded codeword, which may be described in detail in conjunction with the following specific implementation manner.

In another specific implementation manner of the present invention, the step 106 may include:

substep D1: dividing the index matrix into sub-blocks according to rows to obtain a plurality of sub-blocks;

substep D2: respectively calculating by utilizing each subblock to obtain verification information;

substep D3: repeatedly executing the step of respectively calculating and obtaining the check information by utilizing each subblock to obtain a check sequence and an information sequence;

substep D4: and combining the check sequence and the information sequence to form the coding code word.

In the embodiment of the present invention, the parallel encoding is implemented by using (N-K)/L registers to encode the sub-matrices at the same time, as shown in fig. 4. The specific steps of each sub-matrix encoding are as follows:

step 1: the index matrix is divided into (N-K)/L subblocks according to rows, the subblocks are independently encoded, and the subblocks can be simultaneously encoded in parallel by adopting (N-K)/L registers.

And 2, step: calculating check information by using subblocks of the index matrix respectively, and specifically comprising the following steps of:

(1) Taking the 0 th row element of the i (i = 0., (N-K)/L-1) sub-block, calculating the i x L position of the check information as follows:

in the above formula, I (I) represents the ith bit of the information to be transmitted, ID (I, j) represents the element in the ith row and jth column in the index matrix, and the operation symbolIs a modulo two addition.

(2) Taking the 1 st row element of the ith sub-block, and calculating the ith x L +1 bit of the check information as

(3) And (5) repeating the step (2), and iterating to obtain other check information bits. The i × L + j bits ((j = 1., (L-1)) of the parity information may be calculated from the j row element of the i sub-block and the i × L + j-1 bit of the parity information:

and combining the calculated check sequence and the information sequence to form a complete code word. The sequence of codewords can be represented as:

C=[m sg ,P]

in the above formula, m sg Is an information sequence and P is a check sequence.

Example two

Referring to fig. 5, a schematic structural diagram of an encoding apparatus based on an index matrix according to an embodiment of the present invention is shown, and as shown in fig. 5, the encoding apparatus based on the index matrix may specifically include the following modules:

a check code pattern determining module 510, configured to determine a check code pattern of the low-density parity check code according to the service parameter;

a all-element calculating module 520, configured to determine a galois field according to the check code pattern, and calculate all elements in the galois field;

an interleaving sequence calculation module 530, configured to calculate a pseudo-random interleaving sequence according to all the elements;

a matrix configuration determining module 540, configured to determine a matrix configuration of an index matrix to be constructed;

an index matrix constructing module 550, configured to assign a value to the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration, and construct an index matrix;

and an encoded codeword generating module 560, configured to perform iterative encoding on each sub-block based on the same number of registers in the sub-blocks in the index matrix, so as to generate an encoded codeword.

Optionally, the check pattern determining module 510 includes:

and the check code character determining unit is used for determining the check code type of the low-density parity check code according to the information bit length, the bit error rate and the bit signal to noise ratio.

Optionally, the all elements calculating module 520 includes:

the sub-matrix size determining unit is used for determining the size of a sub-matrix in the check matrix according to the check code pattern;

the Galois field calculating unit is used for calculating to obtain the Galois field according to the size of the submatrix and a preset formula;

and the all-element acquisition unit is used for expanding the Galois field to obtain all the elements in the Galois field.

Optionally, the interleaving sequence calculating module 530 includes:

the bias factor query unit is used for querying a bias factor and a skip factor corresponding to each non-zero sub-matrix in the matrix to be constructed according to a preset standard;

and the interleaving sequence generating unit is used for generating the pseudo-random interleaving sequence according to the bias factor and the skip factor.

Optionally, the index matrix building module 550 includes:

a matrix position obtaining unit, configured to obtain, according to the matrix configuration, a sub-matrix position corresponding to the pseudorandom interleaving sequence in the index matrix to be constructed;

an element storage position unit, which is used for storing the elements in the pseudo-random interleaving sequence into the position of the sub-matrix one by one according to columns;

and the index matrix generating unit is used for repeatedly executing the element storage position unit until all the sub-matrix positions are filled, and then generating the index matrix.

Optionally, the code codeword generating module 560 includes:

the multiple subblock obtaining units are used for dividing the index matrix into subblocks according to rows to obtain multiple subblocks;

the check information calculation unit is used for calculating by using each subblock to obtain check information;

a check sequence obtaining unit for repeatedly executing the check information calculating unit to obtain a check sequence and an information sequence;

and the code word forming unit is used for combining the check sequence and the information sequence to form the code word.

The invention is not described in detail in the specification of the invention, which belongs to the common general knowledge of the skilled person.

Claims (8)

1. An index matrix-based encoding method, comprising:

according to the service parameters: determining the check code type of the low-density parity check code according to the information bit length, the bit error rate and the bit signal to noise ratio;

determining a Galois field according to the check code pattern, and calculating to obtain all elements in the Galois field;

calculating to obtain a pseudo-random interleaving sequence according to all the elements;

determining a matrix configuration of an index matrix to be constructed;

assigning the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration, and constructing to obtain an index matrix, wherein the method comprises the following steps:

acquiring a sub-matrix position corresponding to the pseudo-random interleaving sequence in the index matrix to be constructed according to the matrix configuration;

storing the elements in the pseudo-random interleaving sequence into the position of the sub-matrix one by one according to columns;

repeatedly executing the step of storing the elements in the pseudo-random interleaving sequence into the positions of the sub-matrixes one by one according to columns until all the positions of the sub-matrixes are filled, and generating the index matrix;

and performing iterative coding on each subblock based on the registers with the same number of subblocks in the index matrix to generate a coded code word.

2. The encoding method according to claim 1, wherein the determining a galois field and calculating all elements in the galois field according to the check code pattern comprises:

determining the size of a sub-matrix in a check matrix according to the check code pattern;

calculating to obtain the Galois field according to the size of the submatrix and a preset formula;

and expanding the Galois field to obtain all elements in the Galois field.

3. The encoding method according to claim 1, wherein said calculating a pseudo-random interleaving sequence according to all the elements comprises:

inquiring a bias factor and a skip factor corresponding to each non-zero submatrix in a matrix to be constructed according to a preset standard;

and generating the pseudo-random interleaving sequence according to the bias factor and the skip factor.

4. The encoding method of claim 1, wherein the iteratively encoding each sub-block based on the same number of registers of the sub-blocks in the index matrix to generate an encoded codeword comprises:

dividing the index matrix into sub-blocks according to rows to obtain a plurality of sub-blocks;

respectively calculating by utilizing each subblock to obtain verification information;

repeatedly executing the step of respectively calculating and obtaining the check information by utilizing each subblock to obtain a check sequence and an information sequence;

and combining the check sequence and the information sequence to form the coding code word.

5. An apparatus for encoding based on an index matrix, comprising:

a check code pattern determining module, configured to: determining the check code type of the low-density parity check code according to the information bit length, the bit error rate and the bit signal to noise ratio;

the all-element calculation module is used for determining a Galois field according to the check code type and calculating all elements in the Galois field;

the interleaving sequence calculation module is used for calculating to obtain a pseudo-random interleaving sequence according to all the elements;

the matrix configuration determining module is used for determining the matrix configuration of the index matrix to be constructed;

the index matrix construction module is used for assigning the index matrix to be constructed based on the pseudo-random interleaving sequence and the matrix configuration and constructing to obtain an index matrix; the index matrix building module comprises:

a matrix position obtaining unit, configured to obtain, according to the matrix configuration, a sub-matrix position corresponding to the pseudorandom interleaving sequence in the index matrix to be constructed;

an element storage position unit, which is used for storing the elements in the pseudo-random interleaving sequence into the position of the sub-matrix one by one according to columns;

the index matrix generating unit is used for repeatedly executing the element storage position unit until all the sub-matrix positions are filled, and then generating the index matrix;

and the code word generating module is used for executing iterative coding on each subblock based on the registers with the same number of subblocks in the index matrix to generate a code word.

6. The encoding apparatus of claim 5, wherein the all elements calculation module comprises:

the sub-matrix size determining unit is used for determining the size of a sub-matrix in the check matrix according to the check code pattern;

the Galois field calculating unit is used for calculating to obtain the Galois field according to the size of the submatrix and a preset formula;

and the all-element acquisition unit is used for expanding the Galois field to obtain all the elements in the Galois field.

7. The encoding apparatus as claimed in claim 5, wherein the interleaving sequence calculating module comprises:

the bias factor query unit is used for querying a bias factor and a skip factor corresponding to each non-zero sub-matrix in the matrix to be constructed according to a preset standard;

and the interleaving sequence generating unit is used for generating the pseudo-random interleaving sequence according to the bias factor and the skip factor.

8. The encoding apparatus as claimed in claim 5, wherein the code word generating module comprises:

the multiple subblock obtaining units are used for dividing the index matrix into subblocks according to rows to obtain multiple subblocks;

the check information calculation unit is used for calculating by using each subblock to obtain check information;

a check sequence obtaining unit for repeatedly executing the check information calculating unit to obtain a check sequence and an information sequence;

and the code word forming unit is used for combining the check sequence and the information sequence to form the code word.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202011166798.9A CN112367088B (en) | 2020-10-27 | 2020-10-27 | Encoding method and device based on index matrix |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202011166798.9A CN112367088B (en) | 2020-10-27 | 2020-10-27 | Encoding method and device based on index matrix |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN112367088A CN112367088A (en) | 2021-02-12 |

| CN112367088B true CN112367088B (en) | 2023-03-21 |

Family

ID=74510959

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202011166798.9A Active CN112367088B (en) | 2020-10-27 | 2020-10-27 | Encoding method and device based on index matrix |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN112367088B (en) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113296999B (en) * | 2021-05-20 | 2022-11-11 | 山东云海国创云计算装备产业创新中心有限公司 | A RAID6 encoding method and encoding circuit |

| CN121308766A (en) * | 2024-07-09 | 2026-01-09 | 华为技术有限公司 | An encoding method, a decoding method, and related apparatus |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1558556A (en) * | 2004-02-09 | 2004-12-29 | 清华大学 | System code design method and communication system of irregular low-density parity-check code |

| CN101465655A (en) * | 2009-01-20 | 2009-06-24 | 清华大学 | Method for encoding ultra short code length density parity check code |

| CN101510782A (en) * | 2009-03-20 | 2009-08-19 | 华为技术有限公司 | Decoding method and system |

| CN102386933A (en) * | 2011-11-11 | 2012-03-21 | 中国科学院上海微系统与信息技术研究所 | Construction method for quasi-cyclic low density parity check (LDPC) code check matrix |

| CN105720990A (en) * | 2014-10-30 | 2016-06-29 | 北京邮电大学 | Four-ring search method and device for LDPC code verification matrix |

| CN107408950A (en) * | 2015-03-02 | 2017-11-28 | 三星电子株式会社 | Transmitter and its even-odd check method of replacing |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2003256588A1 (en) * | 2002-07-03 | 2004-01-23 | Hughes Electronics Corporation | Bit-interleaved coded modulation using low density parity check (ldpc) codes |

| CN114679185A (en) * | 2017-08-11 | 2022-06-28 | 中兴通讯股份有限公司 | Data encoding method and device |

-

2020

- 2020-10-27 CN CN202011166798.9A patent/CN112367088B/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1558556A (en) * | 2004-02-09 | 2004-12-29 | 清华大学 | System code design method and communication system of irregular low-density parity-check code |

| CN101465655A (en) * | 2009-01-20 | 2009-06-24 | 清华大学 | Method for encoding ultra short code length density parity check code |

| CN101510782A (en) * | 2009-03-20 | 2009-08-19 | 华为技术有限公司 | Decoding method and system |

| CN102386933A (en) * | 2011-11-11 | 2012-03-21 | 中国科学院上海微系统与信息技术研究所 | Construction method for quasi-cyclic low density parity check (LDPC) code check matrix |

| CN105720990A (en) * | 2014-10-30 | 2016-06-29 | 北京邮电大学 | Four-ring search method and device for LDPC code verification matrix |

| CN107408950A (en) * | 2015-03-02 | 2017-11-28 | 三星电子株式会社 | Transmitter and its even-odd check method of replacing |

Non-Patent Citations (3)

| Title |

|---|

| Nonbinary low-density-parity-check (NB-LDPC) code outperforms their binary counterpart in terms of error-correcting performance and error-floor property when the code length is moderate. However, the drawback of NB-LDPC decoders is high complexity and the;Huyen Pham Thi等;《IEEE》;20200109;全文 * |

| 准循环LDPC码的编译码技术研究与FPGA实现;董侃;《中国优秀硕士学位论文全文数据库 (信息科技辑)》;20151215;全文 * |

| 卫星突发通信用LDPC编译码器的研究与实现;童焦龙;《中国优秀硕士学位论文全文数据库 信息科技辑》;20180815;全文 * |

Also Published As

| Publication number | Publication date |

|---|---|

| CN112367088A (en) | 2021-02-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1866751B (en) | Construction method and device for low density parity codes | |

| CN104579576B (en) | Code modulating method and system | |

| JP5551209B2 (en) | LDPC encoding and decoding of variable size packets | |

| CN103731160B (en) | Packet space coupling low density parity check coding method | |

| CN101924565B (en) | LDPC encoders, decoders, systems and methods | |

| CN101741396B (en) | Method and device for coding or decoding low-density parity-check (LDPC) codes with variable code length, coder and decoder | |

| CN102035556B (en) | Method and system for encoding and decoding data | |

| CN111416625A (en) | Information processing method and communication device | |

| CN108270448B (en) | Quasi-cyclic low-density parity check coding method and device | |

| CN116054844B (en) | Check matrix construction method, system, electronic equipment and computer storage medium | |

| WO2013026291A1 (en) | Encoding method and encoder for block interleaved quasi-cyclic expanding parallel coding of ldpc code | |

| CN112367088B (en) | Encoding method and device based on index matrix | |

| CN101162907B (en) | A method and device for realizing encoding by using low-density parity-check code | |

| CN104779961A (en) | LDPC (Low Density Parity Check) structure, codeword, corresponding coder, decoder and coding method | |

| CN101252360A (en) | A Structural Construction Method of Multi-ary LDPC Codes with High Girth and Low Code Rate | |

| CN101465655B (en) | Method for encoding ultra short code length density parity check code | |

| CN107947802B (en) | Rate-compatible low-density parity-check code coding and decoding method and codec | |

| CN102891686B (en) | Irregular quasi-cyclic low-density parity check code construction method | |

| CN101764620B (en) | Apparatus and method for decoding using channel code | |

| CN102142929B (en) | Forward error correction method, device and system | |

| CN113708776B (en) | Encoding method, system, medium and device based on LDPC code | |

| CN104426553B (en) | The coding method of low-density parity check (LDPC) matrix | |

| CN101577552B (en) | Method for coding high code-rate repeat-accumulate codes with low complexity | |

| CN101789795A (en) | Encoding method based on multi-rate protograph low density parity check code and encoder | |

| CN102386932A (en) | LDPC code constitution method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |