CN102055485A - Quasi-cyclic low-density parity-check (QC-LDPC) code and correcting and linear coding method thereof - Google Patents

Quasi-cyclic low-density parity-check (QC-LDPC) code and correcting and linear coding method thereof Download PDFInfo

- Publication number

- CN102055485A CN102055485A CN2010106058385A CN201010605838A CN102055485A CN 102055485 A CN102055485 A CN 102055485A CN 2010106058385 A CN2010106058385 A CN 2010106058385A CN 201010605838 A CN201010605838 A CN 201010605838A CN 102055485 A CN102055485 A CN 102055485A

- Authority

- CN

- China

- Prior art keywords

- vector

- check matrix

- check

- code

- matrix

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 26

- 239000011159 matrix material Substances 0.000 claims abstract description 122

- 239000013598 vector Substances 0.000 claims abstract description 72

- 125000004122 cyclic group Chemical group 0.000 claims description 11

- 238000004364 calculation method Methods 0.000 claims description 8

- 150000002678 macrocyclic compounds Chemical class 0.000 claims description 5

- 230000001419 dependent effect Effects 0.000 claims 1

- 238000012986 modification Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000010276 construction Methods 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000008030 elimination Effects 0.000 description 1

- 238000003379 elimination reaction Methods 0.000 description 1

Images

Landscapes

- Error Detection And Correction (AREA)

Abstract

准循环低密度奇偶校验码及其修正和线性编码方法,该低密度校验码维度大于2的变量节点都是信息节点,而维度为2的变量节点在二分图上形成一个首尾相连的大环。其修正方法实施步骤包括:在维度为2的大环上任选一条边,将其截去,也即在低密度校验矩阵的相应位置填0,从而得到该编码一种修正结构。修正后的线性编码方法实施步骤包括:首先利用输入信息矢量s,与校验矩阵的列重大于2的部分做矢量与矩阵的相乘运算得到中间矢量u;变量节点维度为1的编码矢量直接截取中间矢量u的相应位置得到;变量节点维度为2的编码矢量则通过其在二分图上的大环特性由启动位开始逐比特计算可得,将两部分编码矢量拼合起来最终形成编码矢量。

The quasi-cyclic low-density parity-check code and its correction and linear coding method, the variable nodes with a dimension greater than 2 in the low-density check code are all information nodes, and the variable nodes with a dimension of 2 form a large end-to-end connection on the bipartite graph ring. The implementation steps of the correction method include: selecting a side on the large ring with a dimension of 2 and truncating it, that is, filling 0 in the corresponding position of the low-density parity check matrix, so as to obtain a correction structure of the code. The implementation steps of the modified linear coding method include: firstly, using the input information vector s, multiplying the vector and the matrix with the part of the check matrix whose column weight is greater than 2 to obtain the intermediate vector u; the coding vector with variable node dimension 1 It is obtained by directly intercepting the corresponding position of the intermediate vector u; the coded vector whose variable node dimension is 2 Then it can be calculated bit by bit from the start bit through its large cycle characteristics on the bipartite graph, and the two parts of the coded vector are combined to form the coded vector .

Description

技术领域technical field

本发明为低密度奇偶校验码的编码方法,属于信道纠错编码的编码构造及编码方法领域。The invention relates to an encoding method of a low-density parity check code, and belongs to the field of encoding structures and encoding methods of channel error correction encoding.

背景技术Background technique

在低密度奇偶校验(Low-Density Parity-Check,简称LDPC)码的编码方法当中,Richardson在文献(T.J. Richardson and R.L. Urbanke, “Efficient encoding of low-density parity-check codes,” IEEE Trans. Inform. Theory, vol.47, no.2, pp. 638-656, Feb. 2001.)中提出了基于类下三角形校验矩阵的编码方法。但是如果校验阵无法调整成理想的类下三角形矩阵形式,则编码的复杂度还是很高。从LDPC编译码器硬件实现的角度而言,无结构的LDPC码不利于硬件实现。为此,具有准循环(Quasi-Cyclic, 简称QC)结构的LDPC码得到了学术界和工业界的广泛青睐,QC结构反映到LDPC码的校验矩阵上具有以下特点:校验矩阵由循环移位子阵组成,而循环移位子阵则是单位矩阵经循环移位所得到的方阵,因此循环移位矩阵在矩阵大小给定的前提下完全决定于移位系数。研究发现,QC结构能简化编码器的设计,很多QC-LDPC码的编码器可以利用循环移位寄存器来有效实现。然而,QC结构简化编码器也存在着严重的制约关系:校验矩阵必须存在一个由循环子阵构成的满秩子矩阵。在实际构造中,该条件并不容易满足。 Among the encoding methods of Low-Density Parity-Check (LDPC) codes, Richardson in the literature (T.J. Richardson and R.L. Urbane, "Efficient encoding of low-density parity-check codes," IEEE Trans. Inform . Theory, vol.47, no.2, pp. 638-656, Feb. 2001.) An encoding method based on the class lower triangular check matrix is proposed. However, if the check matrix cannot be adjusted into an ideal lower triangular matrix form, the coding complexity is still very high. From the point of view of LDPC codec hardware implementation, unstructured LDPC codes are not conducive to hardware implementation. For this reason, LDPC codes with a quasi-cyclic (Quasi-Cyclic, QC for short) structure have been widely favored by academia and industry. The QC structure is reflected in the check matrix of LDPC codes and has the following characteristics: The cyclic shift sub-array is a square matrix obtained by cyclically shifting the unit matrix, so the cyclic shift matrix is completely determined by the shift coefficient under the premise of a given matrix size. It is found that the QC structure can simplify the design of encoders, and many encoders of QC-LDPC codes can be effectively implemented by using circular shift registers. However, the QC structure simplifies the encoder and there are serious constraints: the parity check matrix must have a full-rank sub-matrix composed of cyclic sub-matrixes. In actual construction, this condition is not easy to satisfy. the

在低码率LDPC码构造中,为提高性能,一般需要引入隐含变量节点,则相当于在LDPC码的校验矩阵中引入更多的列(1个变量节点对应于校验矩阵中的1列),也即对应的编码比特并不发送到信道上,因而称之为具有隐含节点的LDPC码,例如文献(T. Richardson and R. Urbanke, “Multi-Edge type LDPC Codes,” http://lthcwww.epfl.ch/)提出的多边型LDPC码或者文献(A. Abbasfar, D. Divsalar, and K. Yao, “Accumulate Repeat Accumulate Codes,” in IEEE International Symposium on Information Theory, (Chicago, Illinois), June 2004.)中提出的累加-重复-累加码(Accumulate-Repeat-Accumulate, 简称ARA)码。In the construction of low code rate LDPC codes, in order to improve performance, it is generally necessary to introduce hidden variable nodes, which is equivalent to introducing more columns in the parity check matrix of LDPC codes (1 variable node corresponds to 1 in the parity check matrix column), that is, the corresponding coded bits are not sent to the channel, so it is called an LDPC code with hidden nodes, such as literature (T. Richardson and R. Urbanke, “Multi-Edge type LDPC Codes,” http: //lthcwww.epfl.ch/) proposed polygonal LDPC codes or literature (A. Abbasfar, D. Divsalar, and K. Yao, "Accumulate Repeat Accumulate Codes," in IEEE International Symposium on Information Theory, (Chicago, Illinois ), the Accumulate-Repeat-Accumulate (ARA) code proposed in June 2004.).

为便于实现,具有隐含节点的LDPC码也应采用准循环结构,也即所谓的具有隐含节点准循环低密度奇偶校验码。但是,这种准循环结构经常找不到很好的编码方法,这是由于准循环结构使得校验矩阵中找到由循环移位子矩构成的信息长度大小的子阵是满秩的可能性并不大。为此,本发明对具有隐含节点准循环低密度奇偶校验码的结构进行调整,并以此为基础给出了一种线形编码方法。For the convenience of realization, the LDPC codes with hidden nodes should also adopt the quasi-cyclic structure, that is, the so-called quasi-cyclic low density parity-check codes with hidden nodes. However, this quasi-cyclic structure often cannot find a good encoding method, because the quasi-cyclic structure makes it possible to find a sub-matrix with a size of information length composed of cyclically shifted sub-moments in the parity check matrix that is full-ranked. not big. For this reason, the present invention adjusts the structure of the quasi-cyclic low-density parity-check code with hidden nodes, and provides a linear coding method based on this.

发明内容Contents of the invention

技术问题:本发明的目的是提供一种准循环低密度奇偶校验码的修正及其线性编码方法,解决该类低密度奇偶校验码线形复杂度编码难以设计的问题。 Technical problem: The purpose of the present invention is to provide a correction of quasi-cyclic low-density parity-check code and its linear coding method, so as to solve the problem that the linear complexity coding of this type of low-density parity-check code is difficult to design.

技术方案:本发明的准循环低密度奇偶校验码变量节点的维度分为3类:维度为1、维度为2以及维度大于2;维度大于2的变量节点都是信息节点,对应于待编码信息比特位,由于一般不发送到信道上,因而称之为隐含节点;维度为2的变量节点正好在相应的低密度校验矩阵对应的二分图上形成一个首尾相连的大环。 Technical solution: The dimensions of the quasi-cyclic low-density parity-check code variable nodes of the present invention are divided into three categories: dimension 1, dimension 2, and dimension greater than 2; variable nodes with dimension greater than 2 are information nodes, corresponding to the Information bits are generally not sent to the channel, so they are called hidden nodes; variable nodes with a dimension of 2 just form a large ring connected end to end on the bipartite graph corresponding to the corresponding low-density check matrix.

本发明的的准循环低密度奇偶校验码的修正方法为:在所述的维度为2的大环上任选一条边,将其截去,也即在低密度校验矩阵的相应位置填0,从而得到该编码一种修正结构;校验矩阵中填0操作所在的行作为编码开始启动的位置,称为编码启动行。The correction method of the quasi-cyclic low-density parity-check code of the present invention is: select an edge on the large ring whose dimension is 2, cut it off, that is, fill in the corresponding position of the low-

所述修正结构体现在对低密度奇偶校验码的校验矩阵的修改,修改操作对象是校验矩阵中构成大环的列重为2的列,任取其中一列的“1”将其置成“0”,置换发生的行称为启动行,该修正结构结合校验矩阵的定义具体表述为:The correction structure is embodied in the modification of the check matrix of the low-density parity-check code. The object of the modification operation is a column whose column weight is 2 to form a large ring in the check matrix. becomes "0", the line where the replacement occurs is called the start line, and this correction structure is specifically expressed in combination with the definition of the parity check matrix:

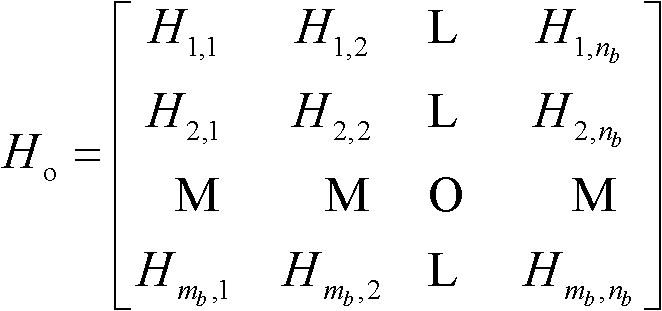

定义:一类具有隐含节点准循环低密度奇偶校验码的校验矩阵: Definition: A check matrix for a class of quasi-cyclic low-density parity-check codes with hidden nodes:

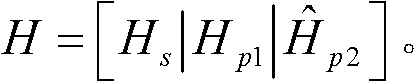

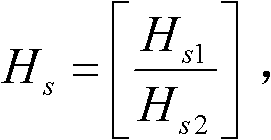

其中,是大小为的循环移位置换子矩阵,该矩阵完全取决于循环移位偏移量,为校验矩阵中循环移位置换子矩阵占的行数,为校验矩阵中循环移位置换子矩阵占的列数,该矩阵的大小为;为方便编码,此类校验矩阵分为3个部分:in, is the size of The cyclic shift permutation submatrix of , which depends entirely on the cyclic shift offset, is the number of rows occupied by the cyclic shift replacement sub-matrix in the parity check matrix, is the number of columns occupied by the cyclic shift replacement sub-matrix in the parity check matrix, the The size of the matrix is ; For the convenience of coding, this kind of check matrix is divided into 3 parts:

,其中,对应于完整码字的信息比特部分,大小为;单维度校验矩阵对应于码字单维度列重为1的校验比特部分,大小为;双维度校验矩阵对应于码字双维度列重为2的校验比特部分,大小为;编码的总长度为;由于对应的编码码字信息位部分并不发送到信道上,因而是具有隐含节点的低密度校验码;所述双维度校验矩阵所有的“1”构成一个大环,设双维度校验矩阵中的“1”依大环的逆时针顺序在该矩阵中的坐标依次为。 ,in, Corresponding to the information bit part of the complete codeword, the size is ;Single-dimensional check matrix Corresponding to the parity bit part of the single-dimensional column weight of the codeword is 1, the size is ;Two-dimensional parity check matrix Corresponding to the parity bit part of the double-dimensional column weight of the codeword is 2, the size is ; The total length of the code is ;because The corresponding encoded codeword information bit part is not sent to the channel, so it is a low-density check code with hidden nodes; the two-dimensional check matrix All "1" form a large ring, and a two-dimensional parity check matrix is set The coordinates of "1" in the matrix in the counterclockwise order of the macrocycle are .

所述双维度校验矩阵中任意制定其中的一个“1”,将其置为“0”,修改后的双维度校验矩阵记为,最终修正结构的低密度校验码具有校验矩阵:The two-dimensional parity check matrix Arbitrarily formulate one of the "1" in it, and set it to "0", and the modified two-dimensional check matrix is recorded as , the low-density check code of the final modified structure has a check matrix:

。 .

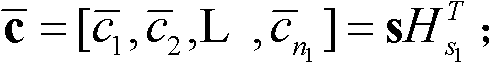

本发明的准循环低密度奇偶校验码的线性编码方法在于:利用修正结构的低密度校验矩阵及输入信息比特矢量计算编码位:首先利用输入信息矢量s,与校验矩阵的列重大于2的部分做矢量与矩阵的相乘运算得到中间矢量u;变量节点维度为1的编码矢量直接截取中间矢量u的相应位置得到;变量节点维度为2的编码矢量则通过其在二分图上的大环特性由启动位开始逐比特计算可得,将两部分编码矢量拼合起来最终形成编码输出矢量。The linear coding method of the quasi-cyclic low-density parity-check code of the present invention is: utilize the low-density check matrix of revised structure and input information bit vector to calculate coding bit: at first utilize input information vector s , and the column weight of check matrix is greater than The part of 2 is multiplied by the vector and the matrix to get the intermediate vector u ; the coded vector whose dimension of the variable node is 1 It is obtained by directly intercepting the corresponding position of the intermediate vector u ; the coded vector whose variable node dimension is 2 Then it can be calculated bit by bit from the start bit through its large ring characteristics on the bipartite graph, and the two parts of the encoded vector are combined to form the encoded output vector .

7.根据权利要求6所述的准循环低密度奇偶校验码的线性编码方法,其特征在于所述编码矢量分成两部分进行,一部分对应于校验矩阵列重为1的列,通过信息矢量直接编码而得;另一部分对应于校验矩阵列重为2的列,相应的编码矢量可通过大环特性逐比特计算而得,该编码算法具体表述为按如下顺序执行的几个步骤:定义: 设编码器的输入矢量为,其中;编码器的输出为编码码字,记为;如果信息位对应隐含节点,则信息位并不发送,编码器输出为,其中,对应于单维度校验矩阵的编码矢量,其大小设为;对应于双维度校验矩阵的编码矢量,其大小设为;将矩阵写成分块矩阵,其中的大小为,的大小为,且;步骤1:利用输入信息比特矢量以及校验矩阵,相乘直接计算;步骤2∶利用输入信息比特矢量以及校验矩阵,相乘直接计算;步骤3:利用中间结果矢量及校验矩阵中输入信息比特矢量以及校验矩阵中的大环特性,计算码字矢量如下所示:7. the linear coding method of quasi-cyclic low-density parity-check code according to claim 6, it is characterized in that described coding vector is divided into two parts and carries out, and a part is corresponding to the column that check matrix column weight is 1, passes information vector It is directly encoded; the other part corresponds to the column with a check matrix column weight of 2, and the corresponding encoding vector can be calculated bit by bit through the macrocycle characteristic. The encoding algorithm is specifically expressed as several steps executed in the following order: Definition : Let the input vector of the encoder be ,in ; The output of the encoder is the encoded codeword, denoted as ; If the information bit corresponds to the hidden node, the information bit is not sent, and the output of the encoder is ,in, An encoding vector corresponding to a single-dimensional parity check matrix whose size is set to ; The encoding vector corresponding to the two-dimensional parity check matrix, whose size is set to ; the matrix write block matrix ,in is of size , is of size ,and ; Step 1: Use the input information bit vector and check matrix , directly calculate by multiplying ; Step 2: Using the input information bit vector and check matrix , directly calculate by multiplying ; Step 3: Utilize the intermediate result vector and the input information bit vector in the parity check matrix and check matrix middle The macrocyclic properties of the calculation codeword vector As follows:

步骤4::将步骤1与步骤3的结果合并,最终得到编码码字。 Step 4: : Merge the results of step 1 and step 3, and finally get the encoded codeword .

有益效果:本发明的主要创新点在于根据维度为2的变量节点构成大环的特点,在大环上任意选取一变量节点并截取其一条边,这样使得编码可以完全根据校验矩阵的联接关系来直接计算完成。 Beneficial effects: the main innovation of the present invention is that according to the characteristics of the large ring formed by variable nodes with a dimension of 2, a variable node is arbitrarily selected on the large ring and one of its edges is intercepted, so that the encoding can be completely based on the connection relationship of the parity check matrix to complete the calculation directly.

主要体现在以下几个方面:It is mainly reflected in the following aspects:

1) 结构修正后的LDPC码相比于原有的LDPC码改动小,截除一条边1) Compared with the original LDPC code, the modified LDPC code has little change, and one side is cut off

的操作使得性能基本没有变化,而译码设计仍可沿用准循环结构来有效—4—The operation makes the performance basically unchanged, and the decoding design can still use the quasi-circular structure to be effective—4—

进行;conduct;

2) 无需对校验矩阵进行高斯消除变化即能编码,由于LDPC码校验矩阵的低密度特性,使得编码复杂度低。2) It can be encoded without Gaussian elimination of the parity check matrix. Due to the low-density characteristics of the parity check matrix of the LDPC code, the encoding complexity is low.

附图说明Description of drawings

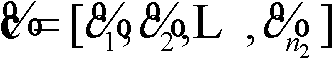

图1是一类准循环LDPC码校验矩阵中由变量维度为2的子矩阵形成的大环结构。Fig. 1 is a large ring structure formed by sub-matrices with a variable dimension of 2 in the parity check matrix of a class of quasi-cyclic LDPC codes.

所有的符号注解:All symbol annotations:

LDPC:Low-Density Parity-Check的缩写,低密度奇偶校验码;LDPC: the abbreviation of Low-Density Parity-Check, low-density parity check code;

:原始LDPC码的校验矩阵; : check matrix of the original LDPC code;

:结构修正后LDPC码的校验矩阵; : check matrix of LDPC code after structure modification;

:LDPC码校验矩阵对应于信息比特的子矩阵; : The LDPC code check matrix corresponds to the sub-matrix of the information bits;

:对应于码字单维度(列重为1)校验比特部分; : Corresponding to the single-dimensional codeword (column weight is 1) parity bit part;

:对应于码字双维度(列重为2)校验比特部分; : Corresponding to the codeword double-dimensional (column weight is 2) parity bit part;

:修改后的双维度校验矩阵; : Modified two-dimensional check matrix;

:编码器的输入矢量; : the input vector of the encoder;

:编码器的输出,编码码字矢量; : the output of the encoder, the encoded codeword vector;

:对应于单维度校验矩阵的编码矢量; : Corresponding to the encoding vector of the single-dimensional parity check matrix;

:对应于双维度校验矩阵的编码矢量; : Corresponding to the encoding vector of the double-dimensional parity check matrix;

:中的“1”所处的位置,依大环的逆时针顺序在该矩阵中的坐标。 : The position of "1" in is the coordinates in the matrix in the counterclockwise order of the macrocycle.

具体实施方式Detailed ways

本发明的准循环低密度奇偶校验码在维度为2的大环上任选一条边,将其截去,也即在低密度校验矩阵的相应位置填0,从而得到该编码一种修正结构。设原始编码的校验矩阵可以分为3个部分:In the quasi-cyclic low-density parity-check code of the present invention, one side is randomly selected on the large ring with a dimension of 2, and it is truncated, that is, 0 is filled in the corresponding position of the low-density check matrix, thereby obtaining a correction of the code structure. Suppose the check matrix of the original code can be divided into three parts:

,且双维度校验矩阵所有的“1”构成一个大环。设中的“1”依大环的逆时针顺序在该矩阵中的坐标依次为。结构修正方法具体步骤为:任意制定双维度校验矩阵中的一个“1”,将其置为“0”,修改后的双维度校验矩阵记为,最终结构修改的低密度校验码具有校验矩阵: , and the two-dimensional check matrix All "1"s form a big ring. set up The coordinates of "1" in the matrix in the counterclockwise order of the macrocycle are . The specific steps of the structure correction method are as follows: arbitrarily formulate a two-dimensional check matrix A "1" in it, set it to "0", and the modified two-dimensional check matrix is recorded as , the final modified low-density check code has a check matrix:

。 .

准循环低密度奇偶校验码的线性编码方法,利用低密度校验矩阵及输入信息比特矢量直接计算编码位。首先利用输入信息矢量,与校验矩阵的列重(也即变量节点维度)大于2的部分做矢量与矩阵的相乘运算得到中间矢量;变量节点维度为1的编码矢量直接截取中间矢量的相应位置得到;变量节点维度为2的编码矢量则通过其在二分图上的大环特性由启动位开始逐比特计算可得,将两部分编码矢量拼合起来最终形成编码矢量。准循环低密度奇偶校验码的线性编码方法可以表述为按照如下顺序执行的步骤:The linear coding method of the quasi-cyclic low-density parity-check code uses the low-density check matrix and the input information bit vector to directly calculate coded bits. First use the input information vector , with the column weight of the check matrix (that is, the dimension of the variable node) greater than 2, do the multiplication operation of the vector and the matrix to obtain the intermediate vector ;Coding vector of variable node dimension 1 Intercept the intermediate vector directly The corresponding position is obtained; the code vector of variable node dimension is 2 Then it can be calculated bit by bit from the start bit through its large cycle characteristics on the bipartite graph, and the two parts of the coded vector are combined to form the coded vector . The linear coding method of the quasi-cyclic LDPC code can be expressed as steps performed in the following order:

步骤1:利用输入信息比特矢量以及校验矩阵,相乘直接计算; Step 1: Utilize the input information bit vector and check matrix , directly calculate by multiplying ;

步骤2∶利用输入信息比特矢量以及校验矩阵,相乘直接计算; Step 2: Use the input information bit vector and check matrix , directly calculate by multiplying ;

步骤3:利用中间结果矢量及校验矩阵中输入信息比特矢量以及校验矩阵中的大环特性,计算码字矢量如下所示: Step 3: Utilize the intermediate result vector and the input information bit vector in the parity check matrix and check matrix middle The macrocyclic properties of the calculation codeword vector As follows:

步骤4::将步骤1与步骤3的结果合并,最终得到编码码字。 Step 4: : Merge the results of step 1 and step 3, and finally get the encoded codeword .

例:本发明的一种准循环低密度奇偶校验码的修正及其线性编码方法可以通过Example: the correction of a kind of quasi-cyclic low-density parity-check code of the present invention and its linear coding method can pass

以下实例来说明。设一个码长为6,信息长度为2,码率为1/3的具有隐含节点的准循环LDPC码的原始校验矩阵如下:The following examples to illustrate. The original check matrix of a quasi-cyclic LDPC code with hidden nodes with a code length of 6, an information length of 2, and a code rate of 1/3 is as follows:

。 .

该校验矩阵可以分解成3个部分,其中,The check matrix can be decomposed into 3 parts ,in,

,,。 , , .

对应于完整码字的信息比特部分,大小为,在本例子中并不发送到信道上,因而是所谓的隐含节点部分;对应于码字维度为1的校验比特部分,大小为;对应于码字维度为2的校验比特部分,大小为;参数,。该校验矩阵的对应的节点构成一个大环,如图1所示。 Corresponding to the information bit part of the complete codeword, the size is , which is not sent to the channel in this example, so it is the so-called hidden node part; Corresponding to the parity bit part of codeword dimension 1, the size is ; Corresponding to the parity bit part of codeword dimension 2, the size is ;parameter , . The parity check matrix The corresponding nodes form a large ring, as shown in Figure 1.

本发明的结构修正是在该大环上选取一点截去一条边,也即校验矩阵相应位置的“1” 填 “0”,如图1画圈的位置置成“0”,因而修正后的可以写成:The structural modification of the present invention is to select a point on the large ring to cut off a side, that is, to fill the "1" in the corresponding position of the parity check matrix with "0", as shown in Figure 1. of can be written as:

, ,

因而结构修改后的LDPC码校验矩阵可以写成:Therefore, the structure-modified LDPC code check matrix can be written as:

。 .

结构修改后LDPC码的线性编码算法其具体步骤如下: The specific steps of the linear coding algorithm of the LDPC code after structure modification are as follows:

步骤1:利用输入信息比特矢量以及校验矩阵,相乘直接计算; Step 1: Utilize the input information bit vector and check matrix , directly calculate by multiplying ;

步骤2∶利用输入信息比特矢量以及校验矩阵,相乘直接计算; Step 2: Use the input information bit vector and check matrix , directly calculate by multiplying ;

步骤3:利用中间结果矢量以及校验矩阵中的大环特性,计算码字矢量如下逐步计算所示(,): Step 3: Utilize the intermediate result vector and check matrix middle The macrocyclic properties of the calculation codeword vector Step-by-step calculations are shown below ( , ):

,,,; , , , ;

步骤4::将步骤1与步骤3的结果合并,最终得到编码码字。 Step 4: : Merge the results of step 1 and step 3, and finally get the encoded codeword .

the

图1是一种准循环LDPC码校验矩阵中由变量维度为2的子矩阵的大环结构。环各点在矩阵中的坐标为, 其中,。Fig. 1 is a macrocyclic structure of a sub-matrix whose variable dimension is 2 in the parity check matrix of a quasi-cyclic LDPC code. The coordinates of each point of the ring in the matrix are , in , .

Claims (7)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN2010106058385A CN102055485A (en) | 2010-12-24 | 2010-12-24 | Quasi-cyclic low-density parity-check (QC-LDPC) code and correcting and linear coding method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN2010106058385A CN102055485A (en) | 2010-12-24 | 2010-12-24 | Quasi-cyclic low-density parity-check (QC-LDPC) code and correcting and linear coding method thereof |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN102055485A true CN102055485A (en) | 2011-05-11 |

Family

ID=43959473

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2010106058385A Pending CN102055485A (en) | 2010-12-24 | 2010-12-24 | Quasi-cyclic low-density parity-check (QC-LDPC) code and correcting and linear coding method thereof |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN102055485A (en) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105281835A (en) * | 2015-09-14 | 2016-01-27 | 哈尔滨工业大学 | Visible light communication method based on LDPC code |

| CN107094025A (en) * | 2011-05-18 | 2017-08-25 | 松下电器产业株式会社 | Bit Interleave method, bit interleaver, signal processing method and signal processing apparatus |

| CN107094023A (en) * | 2011-05-18 | 2017-08-25 | 松下电器产业株式会社 | Bit Interleave method, bit interleaver and signal processing method, signal processing apparatus |

| CN107733438A (en) * | 2011-05-18 | 2018-02-23 | 松下电器产业株式会社 | Parallel bit interleaver |

| CN108777605A (en) * | 2018-05-24 | 2018-11-09 | 西安电子科技大学 | Multichain SC-LDPC coding methods suitable for bulk nanometer materials |

| WO2021146967A1 (en) * | 2020-01-21 | 2021-07-29 | 华为技术有限公司 | Low density parity check code encoding method and encoder |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101488761A (en) * | 2009-02-27 | 2009-07-22 | 北京交通大学 | LDPC constructing method with short ring or low duplicate code |

| CN101826878A (en) * | 2010-04-26 | 2010-09-08 | 杨磊 | QC-LDPC (Quasi-Cyclic Low Density Parity Check) code constructing method |

-

2010

- 2010-12-24 CN CN2010106058385A patent/CN102055485A/en active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101488761A (en) * | 2009-02-27 | 2009-07-22 | 北京交通大学 | LDPC constructing method with short ring or low duplicate code |

| CN101826878A (en) * | 2010-04-26 | 2010-09-08 | 杨磊 | QC-LDPC (Quasi-Cyclic Low Density Parity Check) code constructing method |

Non-Patent Citations (1)

| Title |

|---|

| 黄炜: "准循环LDPC码的构造及编解码方法研究", 《复旦大学硕士学位论文》 * |

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107733438B (en) * | 2011-05-18 | 2020-10-30 | 松下电器产业株式会社 | Parallel Bit Interleaver |

| US11362680B2 (en) | 2011-05-18 | 2022-06-14 | Panasonic Holdings Corporation | Parallel bit interleaver |

| CN107094023A (en) * | 2011-05-18 | 2017-08-25 | 松下电器产业株式会社 | Bit Interleave method, bit interleaver and signal processing method, signal processing apparatus |

| US10886946B2 (en) | 2011-05-18 | 2021-01-05 | Panasonic Corporation | Parallel bit interleaver |

| CN107733438A (en) * | 2011-05-18 | 2018-02-23 | 松下电器产业株式会社 | Parallel bit interleaver |

| US12052036B2 (en) | 2011-05-18 | 2024-07-30 | Panasonic Holdings Corporation | Parallel bit interleaver |

| CN107094025B (en) * | 2011-05-18 | 2020-07-07 | 松下电器产业株式会社 | Bit interleaving method, bit interleaver, signal processing method, and signal processing apparatus |

| CN107094023B (en) * | 2011-05-18 | 2020-07-10 | 松下电器产业株式会社 | Bit interleaving method, bit interleaver, signal processing method, and signal processing apparatus |

| CN107094025A (en) * | 2011-05-18 | 2017-08-25 | 松下电器产业株式会社 | Bit Interleave method, bit interleaver, signal processing method and signal processing apparatus |

| US11070236B2 (en) | 2011-05-18 | 2021-07-20 | Panasonic Corporation | Parallel bit interleaver |

| US11894861B2 (en) | 2011-05-18 | 2024-02-06 | Panasonic Holdings Corporation | Parallel bit interleaver |

| US11671118B2 (en) | 2011-05-18 | 2023-06-06 | Panasonic Holdings Corporation | Parallel bit interleaver |

| US11115060B2 (en) | 2011-05-18 | 2021-09-07 | Panasonic Corporation | Parallel bit interleaver |

| US11496157B2 (en) | 2011-05-18 | 2022-11-08 | Panasonic Holdings Corporation | Parallel bit interleaver |

| CN105281835A (en) * | 2015-09-14 | 2016-01-27 | 哈尔滨工业大学 | Visible light communication method based on LDPC code |

| CN105281835B (en) * | 2015-09-14 | 2017-11-07 | 哈尔滨工业大学 | Visible light communication method based on LDPC code |

| CN108777605A (en) * | 2018-05-24 | 2018-11-09 | 西安电子科技大学 | Multichain SC-LDPC coding methods suitable for bulk nanometer materials |

| CN114946144A (en) * | 2020-01-21 | 2022-08-26 | 华为技术有限公司 | Low density parity check code coding method and coder |

| WO2021146967A1 (en) * | 2020-01-21 | 2021-07-29 | 华为技术有限公司 | Low density parity check code encoding method and encoder |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11323134B2 (en) | Encoding method and device and decoding method and device for structured LDPC | |

| ES3031114T3 (en) | Encoding method, decoding method, encoding device and decoding device for structured qc-ldpc codes | |

| CN101141133B (en) | Method of encoding structured low density check code | |

| JP4602418B2 (en) | Parity check matrix generation method, encoding method, decoding method, communication apparatus, encoder, and decoder | |

| KR100641052B1 (en) | LDPC encoder and decoder, and method for LDPC encoding and decoding | |

| US7178082B2 (en) | Apparatus and method for encoding a low density parity check code | |

| US20190334559A1 (en) | Efficiently decodable qc-ldpc code | |

| CN100550655C (en) | A low-density parity-check code encoder/decoder and its generation method | |

| CN102394660B (en) | Encoding method and encoder for block interleaved quasi-cyclic extended parallel encoding LDPC code | |

| CN101567697B (en) | Coder and method for coding rate-compatible low-density parity-check codes | |

| US20080168324A1 (en) | Basic Matrix Based on Irregular Ldpc, Codec and Generation Method Thereof | |

| CN112204888B (en) | QC-LDPC code with high-efficiency coding and good error code layer characteristics | |

| CN102055485A (en) | Quasi-cyclic low-density parity-check (QC-LDPC) code and correcting and linear coding method thereof | |

| CN102394659A (en) | Low density parity check (LDPC) code check matrix construction method and corresponding matrix multiply operation device | |

| Tazoe et al. | Efficient termination of spatially-coupled codes | |

| Xie et al. | Design of rate-compatible protograph-based LDPC codes with mixed circulants | |

| WO2017193614A1 (en) | Encoding method and device and decoding method and device for structured ldpc | |

| WO2011144161A1 (en) | Method, device and system for forward error correction | |

| CN106953644A (en) | A Construction Method of Multivariate QC‑LDPC Code Based on Hamming Code | |

| CN105871385A (en) | LDPC convolutional code construction method | |

| Yoon et al. | Arbitrary bit generation and correction technique for encoding QC-LDPC codes with dual-diagonal parity structure | |

| EP2285004A1 (en) | Method for pseudo-puncturing exponent matrixes of LDPC codes to comply with different code-rates | |

| Yoon et al. | A hardware efficient LDPC encoding scheme for exploiting decoder structure and resources | |

| Li et al. | Performance analysis of QC-LDPC construction based on distance graph | |

| Kumar et al. | Performance evaluation and complexity analysis of re-jagged AR4JA code over AWGN channel |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Application publication date: 20110511 |