8x PLL Clock Multiplier IP on the Google-Skywater 130nm node.

Tested through spice simulations on skywater 130nm tt corner at room termperature

Generates 8x Multiplied Clock

Pre-Layout:

Frequency Obtained for 5Mhz input: 40MHz

Frequency Obtained for 12.5Mhz input: 100MHz

Duty Cycle obtained: 46% at 40MHz and 40.6% at 100MHz

Lock-in starts at ~80us for 100MHz and ~120us for 40Mhz

3rd-Order Loop Filter used [c1, c2, c3, r1, r2, r3]: 355fF, 350fF, 345fF, 490, 490, 490.

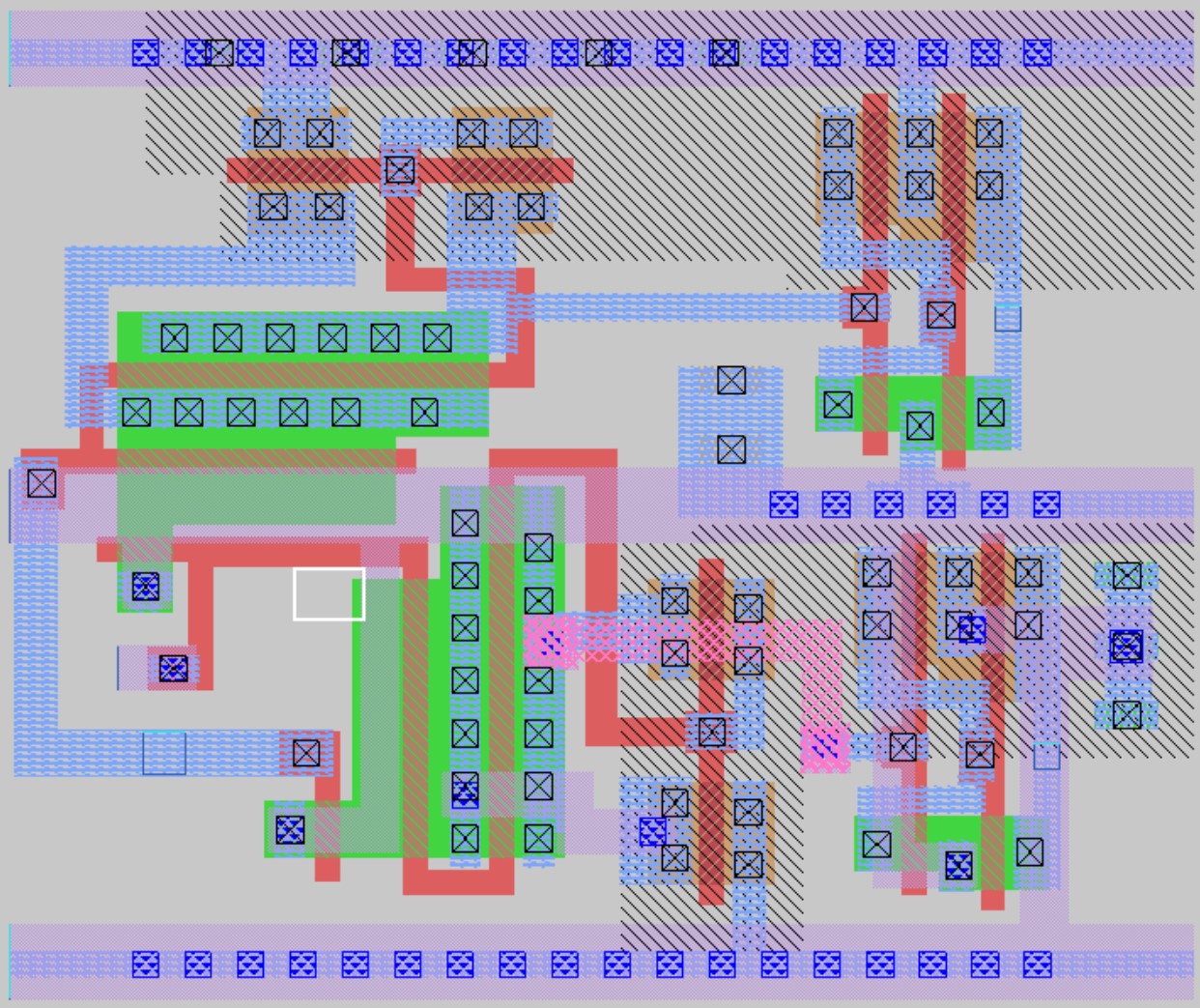

Post-Layout:

Frequency Obtained for 5Mhz input: 40MHz

Frequency Obtained for 12.5Mhz input: 100MHz

Duty Cycle obtained: 52.7% at 40MHz and 50% at 100MHz

Lock-in starts at ~22us for 100MHz and ~37us for 40Mhz

3rd-Order Loop Filter used [c1, c2, c3, r1, r2, r3]: 295fF, 300fF, 305fF, 490, 490, 490.

- Google-SkyWater 130nm PDK

- Specifications

- Pre-Layout Simulations

- Layout

- Post-Layout Simulations

- Instructions

- EDA tools used

- Preparing your IP for Tapeout

- References

- Future Scope

- Acknowlegements

- Contact

This PLL circuit is built on the Google-Skywater 130nm node. It is a mature 180nm-130nm hybrid technology originally developed internally by Cypress Semiconductor. The SkyWater Open Source PDK is a collaboration between Google and SkyWater Technology Foundry to provide a fully open source Process Design Kit and related resources, which can be used to create manufacturable designs at SkyWater’s facility.

| Parameter | Description | min | typ | max | Unit | Conditions |

|---|---|---|---|---|---|---|

| VDD | Digital Supply | - | 1.8 | - | V | T = 27C |

| FCLKREF | Reference | 5 | - | 12.5 | MHz | T = 27C |

| FCLKOUT | Output Clock | 40 | - | 100 | MHz | PLL Mode, T = 27C |

| FCLKOUT | Output Clock | - | - | - | MHz | VCO Mode, T = 27C |

| JRMS | Jitter (rms) | - | - | - | ps | PLL_Mode |

| DC | Duty Cycle | 52.7 | - | 50 | % | T = 27C |

| TSET | Settling Time | ~37 | - | ~22 | ns | T = 27C |

| CL | Load Capacitance | - | - | - | fF | T = 27C |

| IDD | Supply Current | - | - | - | fF | T = 27C |

Red: Reference Clock

Blue: Output Clock Divided by 8

Yellow: Down Signal

Brown: Up Signal

Pink (at top): ChargePump output

Blue constantly overlapping Red indicating locked state

Blue constantly overlapping Red indicating locked state

100Mhz Output:

Blue constantly overlapping Red indicating lock

Blue constantly overlapping Red indicating lock

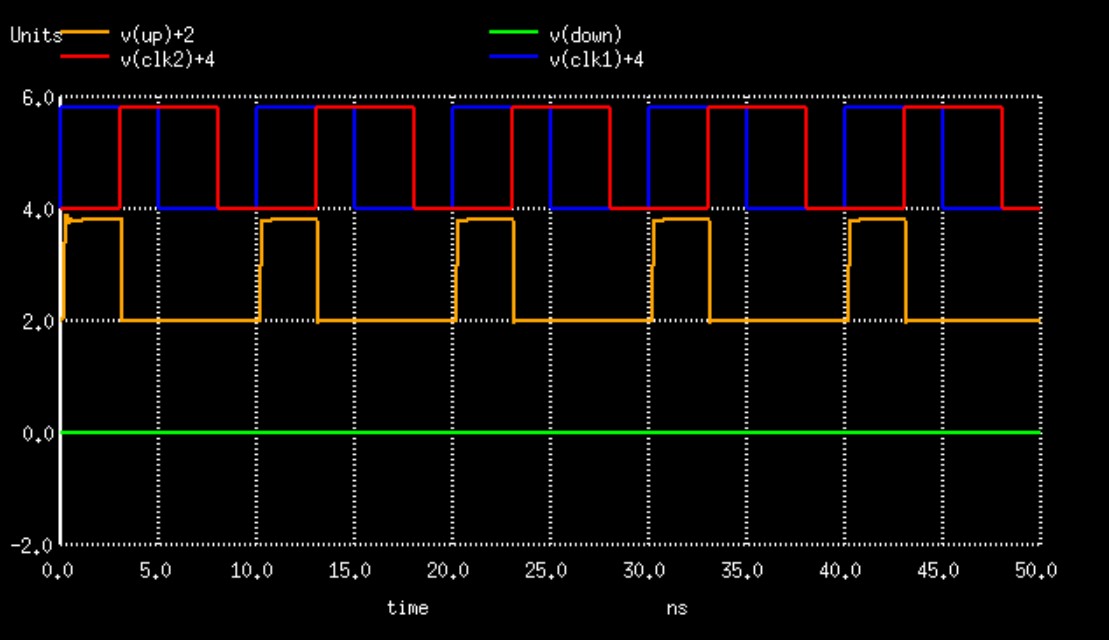

Red: Clock 2

Blue: Clock 1

Orange: Up Signal

Green: Down Signal

Red: Clock 2

Blue: Clock 1

Orange: Up Signal

Green: Down Signal

Red: Charge Pump Output Voltage

Red: Charge Pump Output Voltage

Red: Charge Pump Output Voltage

Leakage: 40uV increase every 1us

Red: Output Clock

Blue: Input Clock

*These above circuits were custom selected to improve stability and reduce area/power consumption.

Area: 29.92um square

Area: 49.09um square

Area: 12.12um square

Area: 132.29um square

Area: 57.73um square

Area: 496.03um square

Red: Reference Clock

Blue: Output Clock Divided by 8

Yellow: Down Signal

Brown: Up Signal

Pink (at top): ChargePump output

40Mhz Output:

Blue constantly overlapping Red indicating locked state

Blue constantly overlapping Red indicating locked state

100Mhz Output:

Blue constantly overlapping Red indicating locked state

Blue constantly overlapping Red indicating locked state

Red: Clock 1

Blue: Clock 2

Orange: Up Signal

Green: Down Signal

Red: Clock1 2

Blue: Clock 2

Orange: Up Signal

Green: Down Signal

Orange: Charge Pump Output Voltage

Red: Up Signal

Blue: Down Signal

Orange: Charge Pump Output Voltage

Red: Up Signal

Blue: Down Signal

Orange: Charge Pump Output Voltage

Red: Up Signal

Blue: Down Signal

Leakage: < 0.05V in 100us

Red: Input Clock

Blue: Output Clock

-

8000

- Get magic v8.3.82 or above from here

- Place the tech file sky130.tech in the folder where you'll be using magic

- Open magic using the command:

magic -T sky130

- Get ngspice from here or for ubuntu users, just use this command:

sudo apt-get install ngspice - Place the sky130nm.lib file and the Sky130_Primitives folder in the location where you'll be running ngspice

- Run the simulation:

ngspice circuitname.cir

For any design to be tapeout ready there are more requirements than just having a finished and tested IP Layout.

For Example, a proper GPIO (cells that enable the IP to be interfaced with external world) is needed for connecting the IP pins to the package (the final DIP or Surface Mount case in which the IC comes in from the Fab)

To meet these requirements either we need to take care of them individually by ourself (which may get complicated and time consuming) or,

we can choose a vehicle for enabling our IP to meet the requirements to go through the fabrication process.

Here we will be using Efabless Caravel SoC template as the Vehicle.

Before we start, this is the datasheet of the Caravel SoC from Efabless,

and these are the parts involved in it:

The Mega Project Area (MPRJ) or 'user_project_wrapper' or in other words 'the container' is where we will place and route our IP.

The Mega Project Area (MPRJ) or 'user_project_wrapper' or in other words 'the container' is where we will place and route our IP.

- Initial setup.

- Place and Route the IP inside the container (keep in mind to not have any DRCs).

- Verify Connectivity.

- Integrate the container onto the Caravel SoC.

- Check if everything is as expected including DRC (Precheck).

Getting it ready is as direct as this. We will see in detail the steps involved in context of Caravel SoC and Google-Skywater OpenShuttle.

Steps:

- Fork and clone Caravel

- Uncompress files

- Install PDK

-> Fork and 'git clone' the Caravel SoC.

Select the 'Fork' option on the top right of the Caravel Github repo.

Specify a name for your fork and then clone it (somewhere on your system where you want to integrate the design onto the Caravel SoC):

git clone <url of your fork>

Here we can see the content of the Caravel Repo. Each type of file is placed in it's respective folder.

Our main focus is the 'gds' folder which contains all the Layout GDS files.

We can see that several files have '.gz' extension. All these files are compressed files. This compression is in place to meet the Github size limit on individual files.

They need to be uncompressed for working on them.

-> This can be done the right way by moving to the root folder (the folder which is the local clone of the forked caravel repo) and giving:

make uncompress

Now we need to setup the Google-Skywater PDK on the machine on which this integration is to be performed.

-> The entire PDK installation is provided as a two step process:

export PDK_ROOT=<location where you want to install it>

You would want to install it outside the local clone of the caravel repo since finally it has to be pushed back to Github.

-> Move to the root folder and give:

make pdk

This downloads and installs the pdks in the location specified earlier (It takes a significant amount of time).

There are two ways to place and route:

- Automatically (Openlane) - commonly used in large digital designs.

- Manually - good for designs that aren't having too many pins to interface.

Here in context of the PLL IP, we will be proceeding along the Manual method of placing and routing the IP.

For more information on the automatic method follow this link.

For placing and routing the IP manually the magic layout tool can be used:

-

export the PDK_ROOT variable with the location of the PDK installation.

-

cd to the 'mag' folder and open magic layout tool (this is since the .magicrc configuration file is in this folder).

This is how to open magic with the right configuration for Caravel with the installed PDK:

-

Select File -> Read GDS and open user_project_wrapper.gds from 'gds' folder (this is the container where we are going to place the IP).

-

Select Cell -> Place Instance and select the mag file of the IP you want to insert (this allows you to place your IP inside this container).

- After Placing the IP by seeing a location with the right I/O pins, manually route the IP pins to the appropriate pins on the container (refer to the datasheet mentioned earlier). Keep in mind to avoid DRC errors.

- Select File -> Write GDS and write out the GDS file for the modified container (remember that the final container in which the IP is placed should be named user_project_wrapper.gds and it should be inside 'gds' folder, this is required for the integration step using 'make' to work).

In context of the a manual connectivity check for it's connectivity to the container pins is performed. You may want to have an automated process if your design has a large number of pins.

The connectivity check can be done through the simple yet effective net tracing feature of the magic layout tool:

- Select any part of the net you wish to trace using the 's' key.

Reference net or Input clock net can be seen selected in this image:

- Press 's' multiple times to see the net being traced till it's endpoints.

Now the fully highlighted net enables us to see which pin is connected where.

This way we can do the same for all nets interfacing the IP to the container to verify the connectivity.

The Caravel Repo uses a simple 'make' based method to integrate the container onto the Caravel SoC.

All that needs to be done, once all the place, route and verification is completed,

is to move to the root folder (the folder which is the local clone of the forked caravel repo) and,

give the 'make' command. This integrates the container onto the Caravel SoC (takes about 10-15mins usually).

We can see that in 'gds' folder a 'caravel.gds' file is generated.

This is the final gds file which is to be used by the Fab for fabricating the IC.

The precheck is provided as a separate repo by Efabless. This was the precheck for Google-Skywater-Efabless open MPW shuttle 2020, on which this guide will be based. It would be different for different tapeout runs and you would need to find the one for the specific tapeout run that you are tagetting.

Efabless Caravel Precheck is designed to run on docker (a container for software, kind of like Virtual Machine). Follow this link to know how to install docker.

Clone the Efabless precheck repo and follow these steps to run the precheck on your finished Caravel:

- Fetch their open_mpw_precheck docker

sh build-docker.sh

docker pull efabless/open_mpw_precheck:latest

- Load the precheck docker (assuming the PDK is already installed from the Caravel repo as mentioned earlier in the initial setup step)

export PDK_ROOT=< location where the PDK was installed >

export TARGET_PATH=< location where you have the forked and cloned Caravel repo where the completed caravel exists >

docker run -it -v $(pwd):/usr/local/bin -v $TARGET_PATH:$TARGET_PATH -v $PDK_ROOT:$PDK_ROOT -e TARGET_PATH=$TARGET_PATH -e PDK_ROOT=$PDK_ROOT -u $(id -u $USER):$(id -g $USER) efabless/open_mpw_precheck:latest

After docker loads you should see 'bash $' indication on the terminal.

- Run the precheck

python3 open_mpw_prechecker.py [-h] --target_path < the target path given earlier > --pdk_root < the pdk location given earlier > --waive_fuzzy_checks

This image shows how to load docker and run the precheck:

This should run the precheck and tell you which of the checks failed, which passed and whether there are any DRC violations.

Contact the organisation facilitating the tapeout run you are interested in and enquire what other steps are required to ensure tapeout readiness.

And you are done!

[1] K.K. Abdul Majeed, Binsu J. Kailath, A Novel Phase Frequency Detector for a High Frequency PLL Design, Procedia Engineering, Volume 64, 2013, Pages 377-384, ISSN 1877-7058,

doi: 10.1016/j.proeng.2013.09.110.

[2] X. Liu and A. N. Willson, "A pA-leakage CMOS charge pump for low-supply PLLs," 2010 53rd IEEE International Midwest Symposium on Circuits and Systems, Seattle, WA, 2010, pp. 1037-1040, doi: 10.1109/MWSCAS.2010.5548821.

[3] Suman, Shruti & Sharma, Krishna. (2018). An Improved Performance Ring VCO: Analysis and Design. Ciência e Técnica Vitivinícola. 33. 254-0223.

[4] Karbalaei Mohammad Ali, M., Hashemipour, O. A simple and high performance charge pump based on the self-cascode transistor. Analog Integr Circ Sig Process 100, 633–638 (2019). doi: 10.1007/s10470-019-01478-y

[5] Y. -. Choi and D. -. Han, "Gain-Boosting Charge Pump for Current Matching in Phase-Locked Loop," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 53, no. 10, pp. 1022-1025, Oct. 2006, doi: 10.1109/TCSII.2006.882122.

[6] Agrawal, Abhishek and Nikhil Saxena. “Comparative Analysis of High Speed FBB TSPC and E-TSPC Frequency Divider at 32 nm CMOS process,” International Journal of Trend in Research and Development (2017), Volume 4(1), ISSN: 2394-9333.

- Incorporation of Trimmer Codes.

- Incorporation of PVT compensation circuit.

- I thank Mr. Kunal Ghosh, co-founder VSD, for providing me the opportunity to work on this wonderful project.

- I thank Google, Skywater and Efabless for bringing this wonderful opportunity to the world and making this project tapeout possible.

- Lakshmi S (Author), MS ECE - lakshmi.sathi96@gmail.com

- Kunal Ghosh, Co-founder, VSD Corp. Pvt. Ltd. - kunalghosh@gmail.com