Power10 is a superscalar, multithreading, multi-core microprocessor family, based on the open source Power ISA, and announced in August 2020 at the Hot Chips conference; systems with Power10 CPUs. Generally available from September 2021 in the IBM Power10 Enterprise E1080 server.

Power10 SCM | |

| General information | |

|---|---|

| Launched | 2021 |

| Designed by | IBM, OpenPower partners |

| Common manufacturer | |

| Performance | |

| Max. CPU clock rate | +3.5 GHz to +4 GHz |

| Cache | |

| L1 cache | 48+32 KB per core |

| L2 cache | 2 MB per core |

| L3 cache | 120 MB per chip |

| Architecture and classification | |

| Technology node | 7 nm |

| Microarchitecture | P10 |

| Instruction set | Power ISA (Power ISA v.3.1) |

| Physical specifications | |

| Cores |

|

| Package |

|

| Socket |

|

| History | |

| Predecessor | POWER9 |

The processor is designed to have 15 cores available, but a spare core will be included during manufacture to cost-effectively allow for yield issues.

Power10-based processors will be manufactured by Samsung using a 7 nm process with 18 layers of metal and 18 billion transistors on a 602 mm2 silicon die.[1][2][3][4]

The main features of Power10 are higher performance per watt and better memory and I/O architectures, with a focus on artificial intelligence (AI) workloads.[5]

Design

editEach Power10 core has doubled up on most functional units compared to its predecessor POWER9. The core is eight-way multithreaded (SMT8) and has 48 KB instruction and 32 KB data L1 caches, a 2 MB large L2 cache and a very large translation lookaside buffer (TLB) with 4096 entries.[3] Latency cycles to the different cache stages and TLB has been reduced significantly. Each core has eight execution slices each with one floating-point unit (FPU), arithmetic logic unit (ALU), branch predictor, load–store unit and SIMD-engine, able to be fed 128-bit (64+64) instructions from the new prefix/fuse instructions of the Power ISA v.3.1. Each execution slice can handle 20 instructions each, backed up by a shared 512-entry instruction table, and fed to 128-entry-wide (64 single-threaded) load queue and 80-entry (40 single-threaded) wide store queue. Better branch prediction features have doubled the accuracy. A core has four matrix math assist (MMA) engines,[6] for better handling of SIMD code, especially for matrix multiplication instructions where AI inference workloads have a 20-fold performance increase.[7]

The processor has two "hemispheres" with eight cores each, sharing a 64 MB L3 cache for a total of 16 cores and 128 MB L3 caches. Due to yield issues, at least one core is always disabled, reducing L3 cache by 8 MB to a usable total of 15 cores and 120 MB L3 cache. Each chip also has eight crypto accelerators offloading common algorithms such as AES and SHA-3.

Increased clock gating and reworked microarchitecture at every stage, together with the fuse/prefix instructions enabling more work with fewer work units, and smarter cache with lower memory latencies and effective address tagging reducing cache misses, enables the Power10 core to consume half the power as POWER9. Combined with the improvements in the compute facilities by up to 30% makes the whole processor perform 2.6× better per watt than its predecessor. And in the case of mounting two cores on the same module, up to 3 times as fast in the same power budget.

As the cores can act like eight logical processors each the 15-core processor looks like 120 cores to the operating system. On a dual-chip module, that becomes 240 simultaneous threads per socket.

I/O

editThe chips have completely reworked memory and I/O architectures, using the open Coherent Accelerator Processor Interface (OpenCAPI) and Open Memory Interface (OMI). Using serial memory communications to off chip controllers reduces signaling lanes to and from the chip, increases the bandwidth and allows the processor to be flexible in its memory technology,.[4]

Power10 supports a wide range of memory types, including DDR3 through DDR5, GDDR, HBM, or Persistent Storage Memory. These configurations can be changed by the customer to best fit the use case intended for the system.

- DDR4 – support for up to 16 TB RAM, 410 GB/s, 10 ns latency

- GDDR6 – up to 800 GB/s

- Persistent storage – up to 2 PB

Power10 enables encrypting of data with no performance penalty at every stage from RAM, across accelerators and cluster nodes to data at rest.

Power10 comes with PowerAXON facility enabling chip to chip, system to system and OpenCAPI bus for accelerators, I/O and other high performance cache coherent peripherals. It manages the communications between nodes in a 16x socket single chip module (SCM) cluster or a 4x socket dual chip module (DCM) cluster. It also manages the memory semantics for clustering of systems enabling load/store access from the core up to 2 PB of RAM on the entire Power10 cluster. IBM calls this feature Memory Inception.

Both OMI and PowerAXON can handle 1 TB/s communications off the chip.

Power10 includes PCIe 5. The SCM has 32x and the DCM has 64x PCIe 5 lanes. The decision to remove NVLink support from Power10 was made due to PCIe 5.0's bandwidth capabilities rendering NVLink support obsolete for the use cases that Power10 was designed for.[3] Support for NVLink on-chip was previously a unique selling point for POWER8 and POWER9.

Variants

editThe Power10 chip is available in two variants, defined by firmware in the packaging. Even though the chips are physically identical and the difference is set in firmware, it cannot be changed by the user nor IBM after manufacturing.[8]

- 15× SMT8 cores

- Optimized for high throughput but less compute intensive applications

- 30× SMT4 cores

- Optimized for highly compute intensive applications that require complex instruction sets and multiple cycles for information loaded into cache

Modules

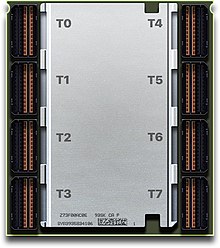

editThe Power10 comes in three flip-chip plastic land grid array (FC-PLGA) packages: one single chip module (SCM) and two dual-chip modules (DCM and eSCM).

- SCM, single chip module – 3.6-4.15 GHz, up to 15 SMT8 cores. Can be clustered up to 16 sockets. x32 PCIe 5 lanes. Module size: 68.5×77.5 mm. The module has a unique configuration with 8 connectors on the substrate (OTF) for symmetric multiprocessing (SMP) cables directly connecting other Power10 SCM modules.

- DCM, dual chip module – 3.4-4.0 GHz, up to 24 SMT8 cores. Can be clustered up to four sockets. x64 PCIe 5 lanes. The DCM is in the same thermal range as previous offerings. Module size: 74.5×85.75 mm. The DCM comes in four variants.[9]

- EPEU - 12 cores, 3.36-4.0 GHz

- EPEV - 18 cores, 3.2-4.0 GHz

- EPGW - 24 cores, 2.95-3.9 GHz

- EHC8 - 24 cores, 2.95-3.9 GHz (for North American healthcare)

- eSCM, entry single chip module – 3.0-3.9 GHz, up to 8 SMT8 cores. It combines two Power10 chips. The first chip is fully functional with 4-8 active cores. The other chip only uses the PCIe functionality acting as a IO switch with plenty of more PCIe lanes. These eSCM modules can be clustered up to four sockets. Module size: 74.5×85.75 mm. The eSCM is also called the "ioscm".[10][11]

Systems

editEnterprise

editThe IBM Power E1080, codename Denali, is the top end Power10 computer by IBM. It's made of 1-4× Central Electronics Complex (CEC) nodes, each one taking up 5Us of space. Each node has 4× Power10 SCM, configurable with 10, 12, or 15 SMT8 cores per processor, and up to 16 TB OMI-DDR4 RAM. The Power E1080 natively runs PowerVM running AIX, IBM i and little-endian Linux.[12] An E1080 system also needs a 2U high System Control Unit for monitoring and configuration.

The Power E1080 also supports up to sixteen I/O expansion drawers, four per CEC node. Each expansion drawer is connected to the respective CEC node by two PCIe fanout modules, and has twelve FHFL PCIe slots. Four of these slots are PCIe 3.0 x16, while the remaining eight are PCIe 3.0 x8. A maximum specification configuration allows the Power E1080 to support 192 single slot PCIe cards across a 16 socket system.[13]

Mid-range

edit- IBM Power E1050 - 4U case. 2-4× CPU sockets for 2-4× DCM modules, 24-96 cores. 64× OMI memory slots which support up to 16 TB RAM. 11× PCIe slots, 8× gen.5 and 3× gen.4. 10 slots for up to 64 TB of NVMe based SSDs. Run a mix of Linux, AIX or IBM i operating systems.[9]

Scale-out

editThe S-models can run Linux, IBM i and AIX. The L-models are made for Linux, but are allowed to run AIX and IBM i on up to 25% of available CPU cores.[10]

- IBM Power S1024 & L1024 - 4U case. 1-2× CPU sockets for 1-2× DCM modules, 24-48 cores. 32× OMI memory slots which support up to 8 TB RAM. 10× PCIe slots, 8× gen.5 and 2× gen.4. 16 slots for up to 102 TB of NVMe based SSDs.

- IBM Power S1022 & L1022 - 2U case. 1-2× CPU sockets for 1-2× DCM modules, 24-40 cores. 32× OMI memory slots which support up to 4 TB RAM. 10× PCIe slots, 8× gen.5 and 2× gen.4. 8 slots for up to 51 TB of NVMe based SSDs.

- IBM Power S1022s - 2U case. 1-2× CPU sockets for 1-2× eSCM modules, 4-16 cores. 16× OMI memory slots which support up to 2 TB RAM. 10× PCIe slots, 8× gen.5 and 2× gen.4. 8 slots for up to 51 TB of NVMe based SSDs.

- IBM Power S1014 - 4U case or a deskside tower. 1× Power10 eSCM module with 4 or 8 cores. 8× OMI memory slots which support up to 1 TB RAM. 5× PCIe slots, 4× gen.5 and 1× gen.4. 16 slots for up to 102 TB of NVMe based SSDs.

- IBM Power S1012 - 2U, half-wide case or a deskside tower. 1× Power10 eSCM module with 1, 4 or 8 cores. 4× OMI memory slots which support up to 256 GB RAM. 4× PCIe slots, 4× gen.5. 4 slots for up to 6.4 TB of NVMe based SSDs.

Operating system support

editComparison with earlier POWER CPUs

editThe change to a 7-nm fabrication process results in significantly higher performance per watt.

The PowerAXON facility now extends all the way to 2 PB of unified clustered memory space, shared across multiple cluster nodes, and includes support for PCIe 5.

New SIMD instructions and new data types including bfloat16, INT4(INTEGER) and INT8(BIGINT).[16][17] are aimed at improving AI workloads.

Unlike earlier POWER9 and POWER8 CPUs, Power10 requires closed source, third party firmware in security sensitive areas of the CPU module, along with additional closed source, third party firmware in the required off-module memory controller.[18]

Branding

editPower10 is unusual in that its name is not capitalised like POWER9 and all other previous POWER processors are. This change is one part in IBM's rebranding of their Power Systems offering, which beginning with Power10 is now just "Power". Power10 also has a logo.[19]

See also

editReferences

edit- ^ Dr. Cutress, Ian (August 17, 2020). "Hot Chips 2020 Live Blog: IBM's POWER10 Processor on Samsung 7nm". AnandTech.

- ^ Quach, Katyanna (August 17, 2020). "IBM takes Power10 processors down to 7nm with Samsung, due to ship by end of 2021". The Register.

- ^ a b c Schilling, Andreas (August 17, 2020). "IBM Power10 offers 30 cores with SMT8, PCIe 5.0 and DDR5". Hardware LUXX (in German).

- ^ a b Kennedy, Patrick (August 17, 2020). "IBM POWER10 Searching for the Holy Grail of Compute". ServeTheHome.

- ^ "IBM Reveals Next-Generation IBM POWER10 Processor". IBM. August 17, 2020.

- ^ Jose Moreira, Puneeth Bhat A H and Satish Kumar Sadasivam (April 15, 2021). Matrix-Multiply Assist Best Practices Guide.

- ^ Russell, John (August 17, 2020). "IBM Debuts Power10; Touts New Memory Scheme, Security, and Inferencing". HPCwire.

- ^ Prickett Morgan, Timothy (August 31, 2020). "IBM's Possible Designs For Power10 Systems". IT Jungle.

- ^ a b Giuliano Anselmi, Marc Gregorutti, Stephen Lutz, Michael Malicdem, Guido Somers, Tsvetomir Spasov (July 11, 2022). "IBM Power E1050 Technical Overview and Introduction" (PDF).

{{cite web}}: CS1 maint: multiple names: authors list (link) - ^ a b Giuliano Anselmi, Young Hoon Cho, Andrew Laidlaw, Armin Röll, Tsvetomir Spasov (July 19, 2022). "IBM Power S1014, S1022s, S1022, and S1024 Technical Overview and Introduction" (PDF).

{{cite web}}: CS1 maint: multiple names: authors list (link) - ^ GitHub/OpenPower/Rainier source

- ^ This is what the most powerful server in the world looks like

- ^ Giuliano Anselmi, Manish Arora, Ivaylo Bozhinov, Dinil Das, Turgut Genc, Bartlomiej Grabowski, Madison Lee, Armin Röll (December 9, 2021). "IBM Power E1080 Technical Overview and Introduction" (PDF).

{{cite web}}: CS1 maint: multiple names: authors list (link) - ^ Larabel, Michael (August 9, 2020). "Linux 5.9 Brings More IBM POWER10 Support, New/Faster SCV System Call ABI". Phoronix.

- ^ a b Prickett Morgan, Timothy (August 6, 2019). "Talking High Bandwidth with IBM's POWER10 Architect". The Next Platform.

- ^ Patrizio, Andy (August 18, 2020). "IBM details next-gen POWER10 processor". Network World.

- ^ "Data type aliases". IBM. August 26, 2020.

- ^ "It's not just OMI that's the trouble with POWER10". September 8, 2021.

- ^ No More Shouting The Name “Power” (Well, Except In Our Title Here)