(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第4523303号 (P4523303)

(45) 発行日 平成22年8月11日(2010.8.11)

(24) 登録日 平成22年6月4日(2010.6.4)

| (51) Int.Cl. |        |           | FΙ   |        |      |

|--------------|--------|-----------|------|--------|------|

| G06F         | 13/36  | (2006.01) | GO6F | 13/36  | 310E |

| G06F         | 3/00   | (2006.01) | GO6F | 3/00   | F    |

| G06F         | 13/24  | (2006.01) | GO6F | 13/24  | 330  |

| G06F         | 13/362 | (2006.01) | G06F | 13/362 | 510D |

請求項の数 1 (全 13 頁)

(21) 出願番号 特願2004-64987 (P2004-64987) (22) 出願日 平成16年3月9日 (2004.3.9)

(65) 公開番号 特開2005-258502 (P2005-258502A)

(43) 公開日 平成17年9月22日 (2005. 9. 22) 審査請求日 平成19年2月28日 (2007. 2. 28) ||(73)特許権者 000001122

株式会社日立国際電気

東京都千代田区外神田四丁目14番1号

||(74)代理人 100093104

弁理士 船津 暢宏

(74)代理人 100092772

弁理士 阪本 清孝

(72) 発明者 内川 信幸

東京都中野区東中野三丁目14番20号

株式会社日立国際電気内

審査官 鈴村 理絵子

最終頁に続く

(54) 【発明の名称】情報処理ボード

## (57)【特許請求の範囲】

## 【請求項1】

MPUが接続された第1のローカルバスと、LANコントローラ等の外部周辺デバイスが接続された第2のローカルバスとを備え、前記MPUと前記外部周辺デバイスとの間でデータの送受を行う情報処理ボードであって、

前記第1のローカルバスと、前記第2のローカルバスとの間に設けられ、前記第1のローカルバスと前記第2のローカルバスとの接続/非接続を行うゲートと、

前記ゲートの接続/非接続の制御を行うと共に、前記MPU又は前記外部周辺デバイスから、前記第2のローカルバスにデータを送出する権利としてのバス権の付与の要求があると、前記バス権を前記要求元のデバイスに付与する制御を行い、前記外部周辺デバイスから前記MPUへの割込みが発生すると、前記割込み<u>を前</u>記MPUに出力する外部制御デバイスとを備え、

10

前記外部制御デバイスは、前記外部周辺デバイスから複数の割込み要求があった場合に、前記外部周辺デバイス毎に、受信割込みと受信以外の割込みに分類し、前記受信割込みを優先順位の高い割込みとし、前記受信以外の割込みを優先順位の低い割込みとして、前記受信割込みを前記MPUに出力し、前記受信割込み又は前記統合された割込みを前記MPUに出力する際に、前記ゲートを接続状態にする外部制御デバイスであり、

前記MPUは、<u>入力された割込みの優先順位に応じて順次割込み処理を行い、</u>前記第2のローカルバスにデータを送出する権利としてのバス権の付与を要求する際に、前記ゲー

トを接続状態にするMPUであることを特徴とする情報処理ボード。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、分散処理システムにおいて用いられ、MPUと外部周辺デバイスとがローカルバスにより接続された情報処理ボードに係り、特に外部周辺デバイスとのデータのやり取りに伴うバス権の制御や外部割り込みに伴うMPUの負荷を低減することができる情報処理ボードに関する。

#### 【背景技術】

## [0002]

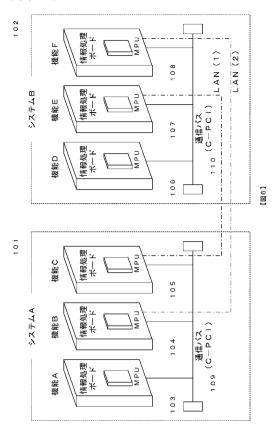

情報処理ボードが用いられる分散情報処理システムについて図 6 を用いて説明する。図 6 は、一般的な分散情報処理システムの概略構成図である。

図6に示すように、分散情報処理システムは、複数のシステムの間で、音声、テレタイプといったデータのやり取りをリアルタイムに行うものであり、図6の例ではシステムA101と、システムB102との間で、データの送受信が行われる。システムAには、当該システムで行われる機能A、機能B、機能Cを実行する情報処理ボード103、104、105が搭載されている。また、同様に、システムBには、当該システムで行われる機能D、機能E、機能Fを実行する情報処理ボード106、107、108が搭載されている。

## [0003]

## [0004]

また、図 6 の例では、システム A 1 0 1 の情報処理ボード 1 0 5 とシステム B 1 0 2 の情報処理ボード 1 0 6 との間は L A N ( 1 ) で接続され、システム A 1 0 1 の情報処理ボード 1 0 4 とシステム B 1 0 2 の情報処理ボード 1 0 7 との間は L A N ( 2 ) で接続されており、互いにデータのやり取りを行うようになっている。

## [0005]

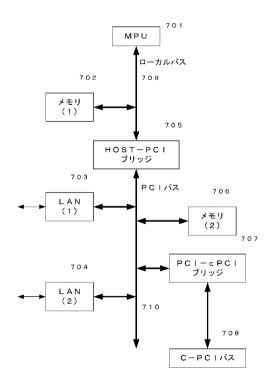

次に、情報処理ボードの構成について図7を用いて説明する。図7は、一般的な情報処理ボードの構成を示す構成プロック図である。

図 7 に示すように、一般的な情報処理ボードは、M P U (Micro Processor Unit) 7 0 1 と、メモリ(1) 7 0 2 と、ローカルバス 7 0 9 と、H O S T - P C I ブリッジ 7 0 5 と、L A N (1) 7 0 3 と、L A N (2) 7 0 4 と、メモリ(2) 7 0 6 と、P C I ア C I ブリッジ 7 0 7 と、P C I バス 7 1 0 と、C - P C I バス 7 0 8 とから構成されている。

## [0006]

各構成部分について具体的に説明する。

MPU701は、各ボード毎に搭載されるCPUであり、ボードに実装されているプログラムを起動して、機能を実現する処理を実行する制御部である。また、MPU701は、LANドライバを備え、LAN(1)703、LAN(2)704を介したデータの送受信を行うものである。また、MPU701は、LAN(1)703、LAN(2)704からの割込みを受け付け、割込みに応じた処理を行うものである。

#### [0007]

メモリ(1)702は、M P U 701の処理に伴うデータを記憶するメモリであり、M P U 701が管理し、使用する。

ローカルバス709は、MPU701とメモリ(1)702とを接続し、データの伝送 を行うバスである。

## [0008]

10

20

30

40

LAN(1)703は、図6に示したLAN(1)を介してデータの送受信を行うコントローラ部分であり、同様に、LAN(2)704は、図6に示したLAN(2)を介してデータの送受信を行うコントローラ部分である。LAN(1)703及びLAN(2)704は、内部に送信データ又は受信データを一時的に格納する記憶部(FIFO)を備えている。尚、図6において各LANに接続されていない情報処理ボードにもLANコントローラとしてのLAN(1)703及びLAN(2)704が設けられている。

#### [0009]

メモリ(2)706は、LAN(1)703又はLAN(2)704で受信したデータ が転送されて、一時蓄積されるメモリ(バッファ)である。

P C I バス 7 1 0 は、 L A N ( 1 ) 7 0 3、 L A N ( 2 ) 7 0 4、 メモリ( 2 ) 7 0 6を接続すると共に、 P C I - c P C I ブリッジ 7 0 7を介して別の情報処理ボードに接続するバスである。

#### [0010]

HOST-PCIブリッジ 705は、ローカルバス 709とPCIバス 710とを接続して信号変換するブリッジである。

また、 P C I - c P C I ブリッジ 7 0 7 は、 P C I バス 7 1 0 と、システム内の情報処理ボード間に設けられた C - P C I バス 7 0 8 とを接続するブリッジである。

#### [0011]

尚、上記構成においては、ローカルバス709及びPCIバス710を介してデータを 流す権利(バス権)の制御は、MPU701が行うようになっている。

### [0012]

次に、上記一般的な情報処理ボードにおけるLANを介した送信処理について説明する

まず、MPU701においてアプリケーション処理が動作している際に送信指示が入力されると、アプリケーションは、カーネルのシステムコール関数群を呼び出して起動し、データを渡す。

## [0013]

次に、MPU701はソケット関数の処理で、受け取ったデータを通信プロトコルに応じて変換し、LANドライバの送信関数の処理を起動してソケットバッファとしてデータを渡す。

## [0014]

そして、MPU701は、LANドライバの送信関数の処理で、ソケットバッファとして受け取ったデータを簡単にチェックし、LAN(1)703又はLAN(2)704のLANコントローラに対して、受け取ったデータ分の記憶領域を確保するメモリ確保要求を出力する。

## [0015]

LANコントローラは、メモリが確保できると、メモリ確保完了割込みをMPU701 に出力する。MPU701は、LANコントローラのデバイス送信関数の処理を起動して データを渡し、LANコントローラが送信関数の処理で実際にデータを送信する。

## [0016]

全てのデータを送信完了すると、LANコントローラは完了通知としてMPU701に「送信完了割込み」を通知する。

MPU701は、「送信完了割込み」を受信すると、送信完了割込みの処理を行って一連の送信処理を終了する。

#### [0017]

尚、送信処理においては、送信が成功した場合にはLANコントローラからMPU70 1に対して「送信完了割込み(送信EMPTY割込み)」が通知され、送信が失敗した場合には、「送信エラー割込み」が通知される。

## [0018]

次に、上記一般的な情報処理ボードにおける受信処理について説明する。

20

10

40

30

まず、LAN(1)又はLAN(2)を介してデータを受信すると、LANコントローラLAN(1)703又はLAN(2)704は、内部のFIFOに受信データを蓄積する。

## [0019]

データがFIFOに一定値以上蓄積されると、LANコントローラがMPU701に対して、「データ受信割込み」を通知する。

MPU701は、「データ受信割込み」を受信すると、LANコントローラのFIFOから、MPU701のカーネル領域のメモリにデータを転送し、更にそこからユーザ領域のメモリへとデータを転送し、MPU701上で起動しているアプリケーションへとデータが渡る。

## [0020]

受信処理においては、LANコントローラからMPU701に対して「データ受信割込み」、「受信オーバーランエラー割込み」、「その他の受信関連のエラー割込み」が通知されるものである。

## [0021]

また、従来のマイクロプロセッサシステムの技術としては、マイクロプロセッサと、それとデータの送受を行う周辺デバイスとの間のバス調停を一括して行うバスー括調停手段を設けて、マイクロプロセッサと周辺デバイス間のバスサイジング用インタフェース回路の小規模化を図るものがあった(特許文献 1 参照)。

#### [0022]

【特許文献 1 】特開平 5 - 4 6 5 3 4 号公報 ( 第 3 - 6 頁 )

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0023]

しかしながら、従来の情報処理ボードでは、ローカルバスとPCIバスの制御をMPUが行うので、MPUの負荷が大きくなってしまい、特に、リアルタイムのプロセスを行っている場合にはMPUの負荷の増大がシステム全体に影響を及ぼすおそれがあるという問題があった。

また、LAN等の外部周辺デバイスからの割込みが頻発するとMPUの負荷が更に増大してしまうという問題点があった。

## [0024]

本発明は上記実情に鑑みて為されたもので、バス権の制御の一部を担う制御デバイスを設け、更に、当該制御デバイスが LAN等の外部周辺デバイスからの割込みの制御を行って、バス権の制御や割込みによるMPUの負荷を低減することができる情報処理ボードを提供することを目的とする。

【課題を解決するための手段】

## [0025]

上記従来の問題点を解決するための本発明は、MPUが接続された第1のローカルバスと、LANコントローラ等の外部周辺デバイスが接続された第2のローカルバスとを備え、MPUと外部周辺デバイスとの間でデータの送受を行う情報処理ボードであって、第1のローカルバスと、第2のローカルバスとの間に設けられ、第1のローカルバスと第2のローカルバスとの接続/非接続を行うゲートと、ゲートの接続/非接続の制御を行うと共に、MPU又は外部周辺デバイスから、第2のローカルバスにデータを送出する権利としてのバス権の付与の要求があると、バス権を要求元のデバイスに付与する制御を行い、外部周辺デバイスからMPUへの割込みが発生すると、割込みをMPUに出力する外部制御デバイスとを備え、外部制御デバイスは、外部周辺デバイスから複数の割込み要求があった場合に、外部周辺デバイス毎に、受信割込みと受信以外の割込みに分類し、受信割込みを優先順位の高い割込みとし、受信以外の割込みを優先順位の低い割込みとして、受信割込み又は統合された割込みをMPUに出力する際に、ゲートを接続状態にする外部制御デバイスであ

10

20

30

40

<u>り、MPUは、入力された割込みの優先順位に応じて順次割込み処理を行い、</u>第2のローカルバスにデータを送出する権利としてのバス権の付与を要求する際に、ゲートを接続状態にするMPUであ<u>る情</u>報処理ボードとしており、従来のPCIバスを用いた回路に比べて回路構成を簡易にしてコストを低減することができ、また、バス権の制御の一部と、外部周辺デバイスからの割込み制御を外部制御デバイスが行うことにより、MPUの負荷を低減することができる。

#### 【発明の効果】

## [0026]

本発明によれば、MPUが接続された第1のローカルバスと、LANコントローラ等の 外部周辺デバイスが接続された第2のローカルバスとの接続/非接続を行うゲートと、ゲ ートの接続 / 非接続の制御を行うと共に、MPU又は外部周辺デバイスから、第 2 のロー カルバスのバス権の付与の要求があると、バス権を要求元のデバイスに付与する制御を行 い、外部周辺デバイスからMPUへの割込みが発生すると、割込みをMPUに出力する外 部制御デバイスとを備え、外部制御デバイスは、外部周辺デバイスから複数の割込み要求 があった場合に、外部周辺デバイス毎に、受信割込みと受信以外の割込みに分類し、受信 割込みを優先順位の高い割込みとし、受信以外の割込みを優先順位の低い割込みとして分 類し、受信割込みをMPUに出力し、受信以外の割込みを統合してMPUに出力し、受信 割込み又は統合された割込みをMPUに出力する際に、ゲートを接続状態にする外部制御 デバイスであり、MPUは、入力された割込みの優先順位に応じて順次割込み処理を行い 、第2のローカルバスにデータを送出する権利としてのバス権の付与を要求する際に、ゲ -トを接続状態にするMPUである情報処理ボードとしているので、従来のPCIバスを 用いた回路に比べて回路構成を簡易にしてコストを低減することができ、また、バス権の 制御の一部と、外部周辺デバイスからの割込み制御を外部制御デバイスが行うことにより MPUの負荷を低減することができ、システム全体としての処理効率を向上させること ができる効果がある。

【発明を実施するための最良の形態】

## [0027]

本発明の実施の形態について図面を参照しながら説明する。

本発明の情報処理ボードは、LAN等の外部周辺デバイスを第2のローカルバスによって接続し、MPUに接続する第1のローカルバスとの間にデータの入出力を制御するゲートを設け、外部周辺デバイス側の第2のローカルバスに、外部周辺デバイスの一種であるFPGA(Field Programmable Gate Alley)を接続し、該FPGAが、第2のローカルバスのバス権の制御と、ゲートの制御を行うと共に、LAN等の外部周辺デバイスからの割込みを統括してMPUに対する割込みを少なくし、MPUの負荷を低減することができるものである。

## [0028]

本発明の実施の形態に係る情報処理ボードについて説明する。

本発明の実施の形態に係る情報処理ボードは、図6に示した分散処理システムと同様のシステムにおいて用いられるものであるため、システム全体の説明は省略する。そして、図6と同様に、システム内の情報処理ボード間はPCIバスによって接続され、システム間はLANによって接続されている。

#### [0029]

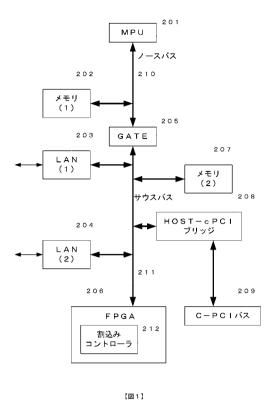

図1は、本発明の実施の形態に係る情報処理ボード(本装置)の構成ブロック図である

図1に示すように、本発明の実施の形態に係る情報処理ボードの構成は、図7に示した一般的な情報処理ボードの構成とほぼ同様であり、情報処理ボード全体の制御を行うMPU201と、MPU201のワークメモリとしてのメモリ(1)202と、ゲート(GATE)205と、LANコントローラとローラとしてのLAN(1)203及びLAN(2)204と、バッファとしてのメモリ(2)207と、HOST-PCIブリッジ208と、第1のローカルバスとしてのリースバス210と、第2のローカルバスとしてのサ

10

20

30

40

ウスバス 2 1 1 と、外部制御デバイスである F P G A 2 0 6 と、システム内の情報処理ボード同士を接続する C - P C I バス 2 0 9 とから構成されている。

#### [0030]

上記構成部分の内、メモリ(1)202、メモリ(2)207、ノースバス210は図 7に示した一般的な情報処理ボードと同様のものであるため、説明は省略する。

#### [0031]

本装置の特徴としては、外部周辺デバイスのLAN(1)203、LAN(2)204、メモリ(2)207及びHOST-PCIブリッジ208を接続するバスとして、従来のPCIバスの代わりに第2のローカルバスを用いている点と、更に当該第2のローカルバスにデータを送出する権利としてのバス権を管理し、第1のローカルバスと第2のローカルバスの間に設けられたゲート205の開閉を制御する外部周辺デバイスとしてFPGA206を設けている点である。

## [0032]

本装置の特徴部分について具体的に説明する。

M P U (Micro Processor Unit) 2 0 1 は、図 7 に示した M P U 7 0 1 と同様に装置全体の制御を行うものであり、L A N (1) 2 0 3、L A N (2) 2 0 4 を介したデータの送受信や、外部周辺デバイスから F P G A 2 0 6 を介して入力された割込みを受け付けて割込みに応じた処理を行うものである。また、本装置では、M P U 2 0 1 は、後述する F P G A 2 0 6 に対してサウスバス権の要求を出力する際に、ゲート 2 0 5 を接続状態にする制御を行うものである。

### [0033]

本装置の特徴として、MPU201に対する外部周辺デバイスからの割込みは、一旦FPGA206に入力されて統合された後、FPGA206からMPU201に出力されるようになっている。

## [0034]

ノースバス 2 1 0 及びサウスバス 2 0 6 は共にローカルバスであり、ゲート 2 0 5 によって接続されている。ノースバス 2 1 0 のバス権制御はM P U 2 0 1 によって行われ、サウスバス 2 1 1 のバス権制御は F P G A 2 0 6 によって行われる。

## [0035]

ゲート 2 0 5 は、ノースバス 2 1 0 とサウスバス 2 1 1 との間に介在し、MPU 2 0 1 又はFPGA 2 0 6 の指示により、ノースバス 2 1 0 とサウスバス 2 1 1 の接続 / 非接続を行うものである。つまり、ゲートが「接続」の状態であれば、ノースバス 2 1 0 とサウスバス 2 1 1 との間のデータ伝送が可能であり、ゲート 2 0 5 が「非接続」の状態であれば、ノースバス 2 1 0 とサウスバス 2 1 1 との間のデータ伝送は不可能である。

# [0036]

FPGA(Field Programmable Gate Alley) 206は、外部周辺デバイスの一種であり、請求項に記載した「外部制御デバイス」に相当するものである。そして、FPGA206は、サウスバス211にデータを流す権利であるサウスバス権を管理し、サウスバス権の要求があると、要求元のデバイスにサウスバス権を付与する制御を行うものである。

## [0037]

また、FPGA206は、ノースバス210とサウスバス211を接続するゲート205の開閉(接続/非接続)を制御するものであり、通常は非接続の状態にしておき、MPU201と、FPGA206やLAN(1)203及びLAN(2)204等の外部周辺デバイスとの間でデータの送受が行われる際にゲート205を接続の状態にする。例えば、FPGA206からMPU201に対して割込みを送出する場合にはゲート205を接続状態にし、MPU201からサウスバス権開放の要求があった場合には、ゲート205を非接続状態にする制御を行うものである。

## [0038]

また、FPGA206は、LAN(1)203及びLAN(2)204からの割込みを 統括して、MPU201に出力する割込み制御を行うものである。FPGA206の内部 10

20

30

40

には、外部周辺デバイスからの割込みを受け付けて統括し、MPU201に出力する割り 込みコントローラ210が設けられている。割込みコントローラ210の処理については 後で説明する。

[0039]

LAN(1)203及び LAN(2)204 は、 LANを介してデータの送受信を行う LANコントローラであり、内部に送受信データを一時蓄積する <math>FIFO メモリを備えている。また、受信時に、FIFO に蓄積されたデータを、サウスバス 211 を介してメモリ(2)207 に転送する DMAC (Dynamic Memory Access Controller)を備えている。これにより、 LAN(1)203 及び LAN(2)204 が受信したデータは、 MPU201 が管理する J-Z バス Z10 を占有することなく、メモリ(2)207 に転送可能としているものである。

10

[0040]

HOST-cPCIブリッジ208は、ローカルバスであるサウスバス211と、システム内の情報処理ボード間に設けられたC-PCIバス209とを接続し、信号変換を行うブリッジである。

[0041]

図7に示した一般的な情報処理ボードでは、MPU201と外部周辺デバイスとの間を接続するのにPCIバス及びHOST-PCIブリッジを用いているが、このように、本装置では、PCIバス及びHOST-PCIブリッジの代わりに安価なローカルバスと簡易な構成のゲート205を用いたことにより、情報処理ボードのコストを低減することができるものである。

20

[0042]

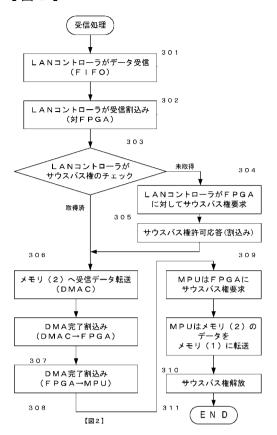

次に、本装置における受信時の動作について図2を用いて説明する。図2は本装置におけるLANを介してデータを受信する際の動作を示すフローチャート図である。

図 2 に示すように、LANの送受信を制御するLANコントローラであるLAN(1) 2 0 3 又はLAN(2) 2 0 4 がLANを介してデータを受信すると、LANコントローラは、受信データを内部のFIFOに格納する(301)。FIFOにデータが一定値以上蓄積されると、LANコントローラは、FPGA206に対して受信割込みを通知する(302)。

[0043]

30

そして、LANコントローラが、サウスバス権を取得しているかどうかを判断し(303)、取得していれば処理306に移行する。

処理303で、LANコントローラがサウスバス権を取得していない場合には、LANコントローラがFPGA206に対してサウスバス権を要求し(304)、FPGA206からサウスバス権許可応答を受信することにより、サウスバス権を取得する(305)

0

[0044]

そして、LANコントローラがサウスバス権を取得すると、DMAC (Dynamic Memory Access Controller) により、FIFOに蓄積されたデータをサウスバス 2 1 1 を介してメモリ( 2 ) 2 0 7 に転送する( 3 0 6 )。

40

[0045]

メモリ(2)207への転送が完了すると、DMACは、FPGA206に対してDMA完了を割込みで通知する(307)。その際、LANコントローラは、サウスバス権を開放する。これを受けて、FPGA206は、ゲート205を接続状態にして、MPU201に対してDMA完了割込みを通知する(308)。

[0046]

MPU201は、FPGA206にサウスバス権を要求し(309)、FPGA206からサウスバス権許可応答を受信してサウスバス権を取得した後、メモリ(2)207のデータをメモリ(1)202に転送し(310)、ユーザアプリケーションへ引き渡す。そして、MPU201は、サウスバス権を開放する(311)。FPGA206は、サウ

スバス権の開放を受けて、ゲート205を非接続状態にする。又は、MPU201からのサウスバス権開放要求にゲート205を非接続状態とする指示を含むようにしてもよい。このようにして本装置における受信処理が行われるものである。

#### [0047]

このように、本装置では、LANコントローラからMPU201に対する割込み要求が、MPU201ではなくFPGA206に出力される点が従来とは異なっている。つまり、受信動作に伴う割込み要求は全て一旦FPGA206に出力され、FPGA206で優先度に応じて統合されて順次MPU201に出力される。MPU201に入力された割込みは、優先度に応じて順次MPU201で処理されるようになっている。

#### [0048]

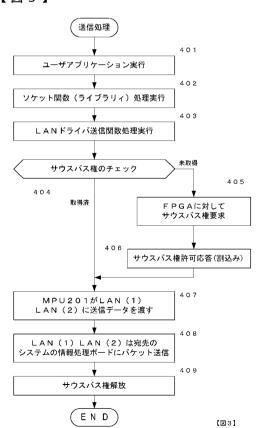

次に、本装置における送信時の動作について図3を用いて説明する。図3は、本装置におけるLANを介してデータを送信する際の動作を示すフローチャート図である。

図3に示すように、MPU201上で起動されているユーザアプリケーションが、送信指示の入力を受けると(401)、ユーザアプリケーションがソケット関数(ライブラリ)を呼び出して起動し、データを渡す(402)。

#### [0049]

次に、MPU201は、ソケット関数の処理で、渡されたデータをソケット構造体に入れ、ソケットバッファとして管理し、LANドライバの送信関数を起動して、ソケットバッファを渡す(403)。

## [0050]

MPU201上のLANドライバの送信関数の処理では、サウスバス権を取得しているかどうかを判断し(404)、取得していれば処理407に移行する。

#### [0051]

処理 4 0 4 でサウスバス権を取得していなければ、MPU2 0 1 はLANドライバの送信関数の処理で、FPGA2 0 6 に対してサウスバス権を要求する(4 0 5 )。ここで、サウスバス権要求の中にゲート2 0 5 を接続状態とする指示を含むようにすれば、ゲート2 0 5 が通常は非接続状態となっていてもFPGA2 0 6 にサウスバス権の要求を出力することができるものである。

## [0052]

MPU201は、サウスバス権許可応答を割込みで受信することによりサウスバス権を取得すると(406)、LANドライバの送信関数の処理においてLANコントローラLAN(1)203又はLAN(2)204にデータを渡す(407)。

#### [0053]

そして、LAN(1)203又はLAN(2)204は宛先のシステムの情報処理ボードにパケット送信する(408)。このとき、送信に関連して発生する割り込み「送信EMPTY割込み」又は「送信エラー割込み」の要求は、受信の際と同様に、全てFPGA206に出力され、優先度に応じて統合された後、MPU201に出力されるようになっている。

## [0054]

そして、MPU201は、サウスバス権を開放し(409)、ユーザアプリケーションからの次の送信要求を待ち受ける。これを受けてFPGA206は、ゲート205を「非接続」とする。又はMPU201からのサウスバス権開放要求にゲート205を非接続状態とする指示を含むようにしてもよい。このようにして、本装置における送信時の処理が行われるものである。

#### [0055]

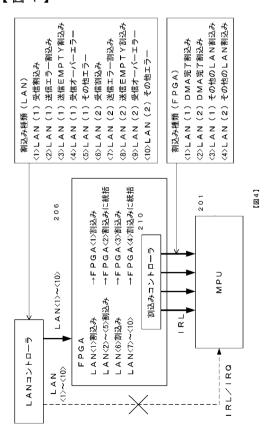

次に、本装置におけるLANコントローラからの割込み制御について図4を用いて説明する。図4は、本装置における割込み制御を示す模式説明図である。

図4に示すように、LANコントローラ(LAN(1)203又はLAN(2)204 )からMPU201に対する割込み要求には 1 ~ 10 の10種類の要因がある。 具体的には、 1 LAN(1)受信割込み、 2 LAN(1)送信エラー割込み、 10

20

30

40

3 LAN(1)送信EMPTY割込み、 4 LAN(1)受信オーバーランエラー、 5 LAN(1)その他エラー、 6 LAN(2)受信割込み、 7 LAN(2)送信エラー割込み、 8 LAN(2)送信EMPTY割込み、 9 LAN(2)受信オーバーランエラー、 10 LAN(2)その他エラー、の10種類である。

そして、従来は、これらの10種類が独立してそれぞれMPU201に入力されていた

#### [0056]

本装置では、FPGA206の割込みコントローラ210が、これらの10種類の割込み要求を優先度に応じて4種類に分類してまとめて、MPU201に出力するようにしている。

分類の仕方は、チャンネル毎に「受信割込み」とそれ以外の割込みとしており、上述した「 1 LAN(1)受信割込み」を「FPGA割込み 1 」とし、「 2 ~ 5 の割込み」を「FPGA割込み 2 」とし、「 6 LAN(2)受信割込み」を「FPGA割込み 3 」とし、「 7 ~ 10 の割込み」を「FPGA割込み 4 」としてMPU201に出力するようにしている。つまり、本装置では、優先度の高い各チャンネルの「受信割込み」と優先度のあまり高くない「受信割込み以外の割込み」に分けている。

#### [0057]

FPGA206の割り込みコントローラ210からMPU201に対する割込みは、優先順位に応じたレベル割込み(IRL)であり、FPGA割込み 1 ~ 4 に応じた優先順位は予め設定されているものである。そして、統合されたFPGA割込み 1 ~ 4 の内の複数が同時にMPU201に出力された場合には、MPU201において優先順位に応じて順次割込み処理を行うものである。

#### [0058]

このように、本装置では、FPGA206がサウスバス権の制御と外部周辺デバイスからの割込み制御を行うようにしているので、LANを頻繁に利用する状況であっても、MPU201のバス権制御処理と割込み処理の負荷を軽減することができるものである。

#### [0059]

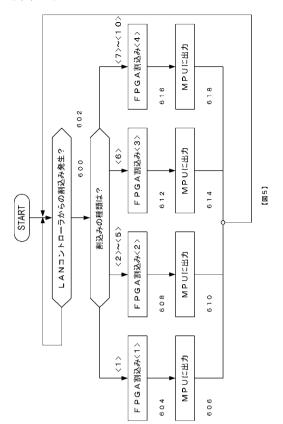

ここで、 F P G A 2 0 6 の割込みコントローラ 2 1 2 の処理について図 5 を用いて説明する。図 5 は、割込みコントローラ 2 1 2 の処理を示すフローチャート図である。

図 5 に示すように、 F P G A 2 0 6 の割込みコントローラ 2 1 2 は、 L A N コントローラの L A N (1) 2 0 3 又は L A N (2) 2 0 4 から割込み発生を受けると(6 0 0)、 L A N割込みの種類が何であるかを判断し(6 0 2)、 1 であれば「F P G A 割込み 1 」として(6 0 4) M P U 2 0 1 に出力し(6 0 6)、 2 ~ 5 であれば「F P G A 割込み 2 」に統合して(6 0 8) M P U 2 0 1 に出力し(6 1 0)、 6 であれば「F P G A 割込み 3 」として(6 1 2) M P U 2 0 1 に出力し(6 1 4)、 7 ~ 1 0 であれば「F P G A 割込み 4 」に統合して(6 1 6) M P U 2 0 1 に出力する(6 1 8)。このようにして割込みコントローラ 2 1 2 の処理が行われるものである。

## [0060]

本発明の実施の形態に係る情報処理ボードによれば、MPU201が接続された第1のローカルバスであるノースバス210と、LAN(1)203、LAN(2)204等の外部周辺デバイスが接続された第2のローカルバスであるサウスバス211とを備え、ノースバス210とサウスバス211との間に、データ伝送路の開閉(ノースバス210とサウスバス211に接続)を行うゲート205を設け、サウスバス211に接続された外部制御デバイスであるFPGA206がゲート205の接続/非接続の制御及びサウスバス権を付与する制御を行う情報処理ボードとしているので、外部周辺デバイスをPCIバスで接続して、更にMPUにHOST-PCIブリッジで接続する回路に比べて、構成を簡素にして回路コストを低減することができ、また、MPU201におけるバス権制御の処理による負荷を低減することができる効果がある。

10

20

30

40

#### [0061]

また、本装置によれば、FPGA206の割り込みコントローラ212が、LAN(1 ) 2 0 3 、 L A N ( 2 ) 2 0 4 からの 1 0 種類の割込み要因を優先順位に応じて 4 種類に 分類して統合して、MPU201に出力する情報処理ボードとしているので、MPU20 1における割込み処理の負荷を軽減することができる効果がある。

#### 【産業上の利用可能性】

#### [0062]

本発明は、外部周辺デバイスとのデータのやり取りに伴うバス権の制御や外部割り込み に伴うMPUの負荷を低減することができる情報処理ボードに適している。

## 【図面の簡単な説明】

[0063]

- 【図1】本発明の実施の形態に係る情報処理ボード(本装置)の構成ブロック図である。

- 【図2】本装置におけるLANを介してデータを受信する際の動作を示すフローチャート 図である。

- 【図3】本装置におけるLANを介してデータを送信する際の動作を示すフローチャート 図である。

- 【図4】本装置における割込み制御を示す模式説明図である。

- 【図5】割込みコントローラ212の処理を示すフローチャート図である。

- 【図6】一般的な分散情報処理システムの概略構成図である。

- 【図7】一般的な情報処理ボードの構成を示す構成ブロック図である。

### 【符号の説明】

## [0064]

101…システム A、 102…システム B、 103~106…情報処理ボード、 09、110…通信バス(C-PCI)、 201…MPU、 202…メモリ(1)、 203... LAN(1)...、204... LAN(2)、205... ゲート、206... F PGA、 207...メモリ(2)、 208...HOST-cPCIブリッジ、 209... C-PCIバス、 2 1 0 ... ノースバス、 2 1 1 ... サウスバス、 2 1 2 ... 割り込みコ ントローラ、 7 0 1 ... M P U 、 7 0 2 ... メモリ(1)、 7 0 3 ... L A N ( 1 ) 、 7 0 4 ... L A N ( 2 ) 、 7 0 5 ... H O S T - P C I ブリッジ、 7 0 6 ... メモリ ( 2 ) 7 0 7 ... P C I - c P C I ブリッジ、 7 0 8 ... C - P C I バス

30

10

【図1】

【図2】

【図3】

【図4】

# 【図5】

【図6】

【図7】

[図7]

# フロントページの続き

(56)参考文献 特開昭 6 3 - 2 8 6 9 4 9 (JP, A)

特開平01-177664(JP,A)

特開平08-095900(JP,A)

特開昭57-178524(JP,A)

特開平02-230356(JP,A)

(58)調査した分野(Int.CI., DB名)

G06F 3/00

G06F 13/20-13/378