Office de la Propriété Intellectuelle du Canada

CA 3108151 C 2024/02/20

(11)(21) 3 108 151

# (12) BREVET CANADIEN CANADIAN PATENT

(13) **C**

(22) Date de dépôt/Filing Date: 2018/02/23

(41) Mise à la disp. pub./Open to Public Insp.: 2018/08/30

(45) Date de délivrance/Issue Date: 2024/02/20

(62) Demande originale/Original Application: 3 051 990

(30) Priorités/Priorities: 2017/02/23 (US62/462,640); 2017/04/17 (US62/486,372); 2017/06/11 (US62/517,949); 2017/06/15 (US62/520,433); 2017/06/19 (US62/522,065); 2017/06/19 (US62/522,081); 2017/08/08 (US62/542,645); 2017/08/08 (US62/542,657); 2017/11/01 (US62/580,207);

2018/02/09 (US62/628,784); 2018/02/09 (US62/628,773)

(51) Cl.Int./Int.Cl. G06N 3/08 (2023.01), G06N 3/045 (2023.01), G06N 3/048 (2023.01), G06N 3/063 (2023.01)

(72) Inventeurs/Inventors:

LIE, SEAN, US; MORRISON, MICHAEL, US; JAMES, MICHAEL EDWIN, US; LAUTERBACH, GARY R., US; AREKAPUDI, SRIKANTH, US

(73) Propriétaire/Owner:

CEREBRAS SYSTEMS INC., US

(74) Agent: OYEN WIGGS GREEN & MUTALA LLP

(54) Titre: APPRENTISSAGE PROFOND ACCELERE (54) Title: ACCELERATED DEEP LEARNING

### (57) Abrégé/Abstract:

Techniques in advanced deep learning provide improvements in one or more of accuracy, performance, and energy efficiency, such as accuracy of learning, accuracy of prediction, speed of learning, performance of learning, and energy efficiency of learning. An array of processing elements performs flow-based computations on wavelets of data. Each processing element has a respective compute element and a respective routing element. Each compute element has processing resources and memory resources. Each router enables communication via wavelets with at least nearest neighbors in a 2D mesh. Stochastic gradient descent, mini-batch gradient descent, and continuous propagation gradient descent are techniques usable to train weights of a neural network modeled by the processing elements. Reverse checkpoint is usable to reduce memory usage during the training.

### Abstract

Techniques in advanced deep learning provide improvements in one or more of accuracy, performance, and energy efficiency, such as accuracy of learning, accuracy of prediction, speed of learning, performance of learning, and energy efficiency of learning. An array of processing elements performs flow-based computations on wavelets of data. Each processing element has a respective compute element and a respective routing element. Each compute element has processing resources and memory resources. Each router enables communication via wavelets with at least nearest neighbors in a 2D mesh. Stochastic gradient descent, mini-batch gradient descent, and continuous propagation gradient descent are techniques usable to train weights of a neural network modeled by the processing elements. Reverse checkpoint is usable to reduce memory usage during the training.

| 1  |                                                                                                          | ACCELERATED DEEP LEARNING                                                                 |  |

|----|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| 2  |                                                                                                          |                                                                                           |  |

| 3  |                                                                                                          |                                                                                           |  |

| 4  |                                                                                                          |                                                                                           |  |

| 5  | <b>[00</b> 01]                                                                                           | [Intentionally blank]                                                                     |  |

| 6  |                                                                                                          |                                                                                           |  |

| 7  |                                                                                                          | BACKGROUND                                                                                |  |

| 8  |                                                                                                          |                                                                                           |  |

| 9  | [0002]                                                                                                   | Field: Advancements in accelerated deep learning are needed to provide                    |  |

| 10 | improvemen                                                                                               | nts in one or more of accuracy, performance, and energy efficiency.                       |  |

| 11 |                                                                                                          |                                                                                           |  |

| 12 | [0003]                                                                                                   | Related Art: Unless expressly identified as being publicly or well known, mention         |  |

| 13 | herein of te                                                                                             | chniques and concepts, including for context, definitions, or comparison purposes, should |  |

| 14 | not be const                                                                                             | trued as an admission that such techniques and concepts are previously publicly known or  |  |

| 15 | otherwise p                                                                                              | art of the prior art.                                                                     |  |

| 16 |                                                                                                          |                                                                                           |  |

| 17 |                                                                                                          |                                                                                           |  |

| 18 |                                                                                                          |                                                                                           |  |

| 19 |                                                                                                          |                                                                                           |  |

| 20 |                                                                                                          | SYNOPSIS                                                                                  |  |

| 21 |                                                                                                          |                                                                                           |  |

| 22 | [0004]                                                                                                   | The invention may be implemented in numerous ways, e.g., as a process, an article of      |  |

| 23 | manufactur                                                                                               | e, an apparatus, a system, a composition of matter, and a computer readable medium such   |  |

| 24 | as a computer readable storage medium (e.g., media in an optical and/or magnetic mass storage device     |                                                                                           |  |

| 25 | such as a disk, an integrated circuit having non-volatile storage such as flash storage), or a computer  |                                                                                           |  |

| 26 | network wherein program instructions are sent over optical or electronic communication links. The        |                                                                                           |  |

| 27 | Detailed Description provides an exposition of one or more embodiments of the invention that enable      |                                                                                           |  |

| 28 | improvements in cost, profitability, performance, efficiency, and utility of use in the field identified |                                                                                           |  |

| 29 | above. The Detailed Description includes an Introduction to facilitate understanding of the remainder    |                                                                                           |  |

| 30 | of the Detailed Description. The Introduction includes Example Embodiments of one or more of             |                                                                                           |  |

| 31 | systems, methods, articles of manufacture, and computer readable media in accordance with concepts       |                                                                                           |  |

| 32 | described h                                                                                              | erein. As is discussed in more detail in the Conclusions, the invention encompasses all   |  |

| 33 | possible mo                                                                                              | difications and variations within the scope of the issued claims.                         |  |

| 1  |               | Brief Description of Drawings                                                          |

|----|---------------|----------------------------------------------------------------------------------------|

| 2  |               |                                                                                        |

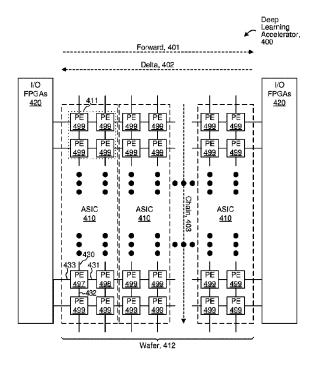

| 3  | [0005]        | Fig. 1 illustrates selected details of an embodiment of a system for neural network    |

| 4  | training and  | inference, using a deep learning accelerator.                                          |

| 5  |               |                                                                                        |

| 6  | [0006]        | Fig. 2 illustrates selected details of an embodiment of software elements associated   |

| 7  | with neural   | network training and inference, using a deep learning accelerator.                     |

| 8  |               |                                                                                        |

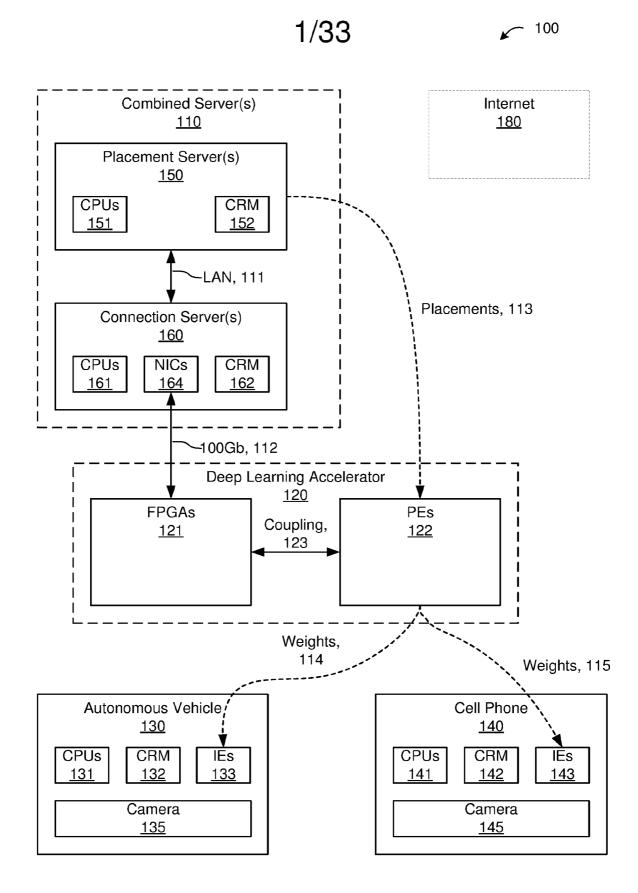

| 9  | [0007]        | Fig. 3 illustrates selected details of an embodiment of processing associated with     |

| 10 | training a ne | eural network and performing inference using the trained neural network, using a deep  |

| 11 | learning acc  | elerator.                                                                              |

| 12 |               |                                                                                        |

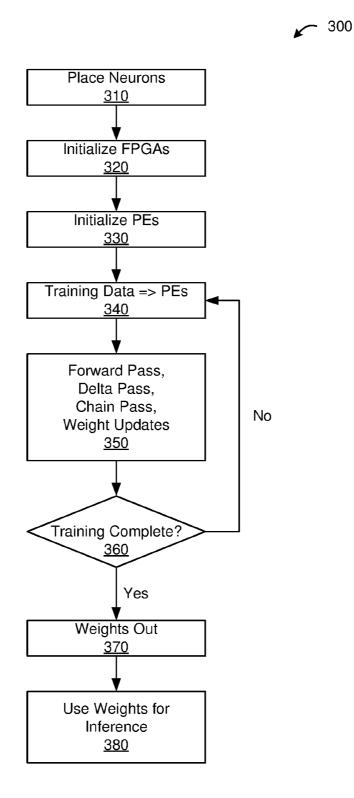

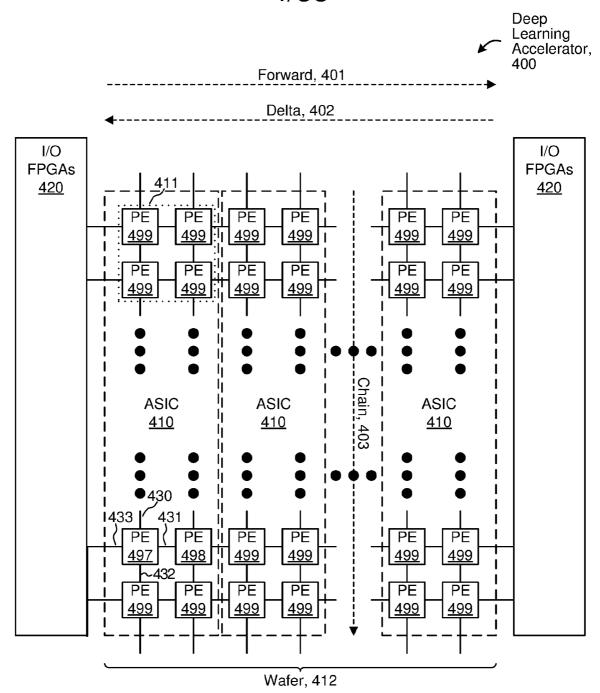

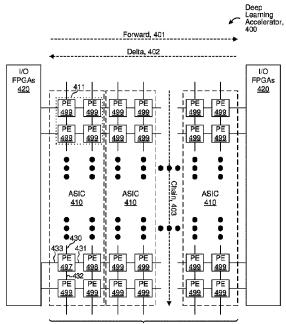

| 13 | [0008]        | Fig. 4 illustrates selected details of an embodiment of a deep learning accelerator.   |

| 14 |               |                                                                                        |

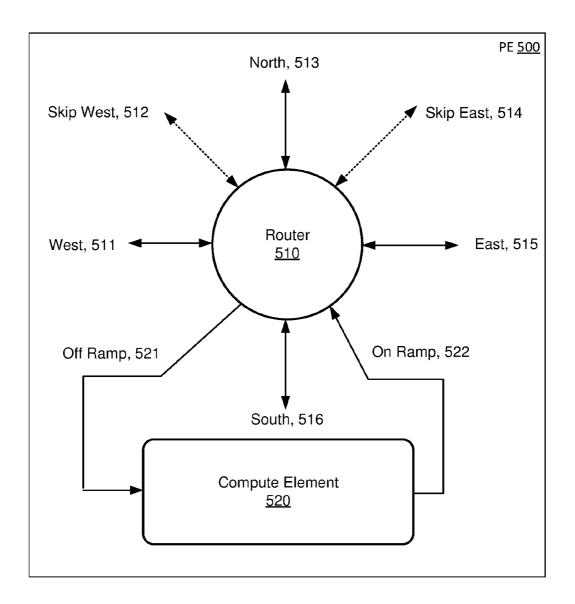

| 15 | [0009]        | Fig. 5 illustrates selected details of an embodiment of a processing element of a deep |

| 16 | learning acc  | elerator.                                                                              |

| 17 |               |                                                                                        |

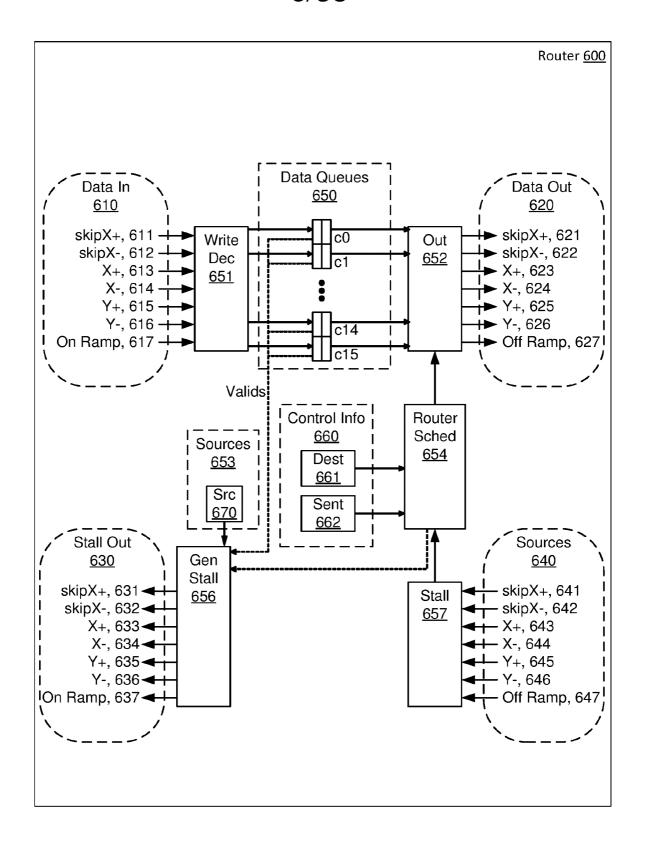

| 18 | [0010]        | Fig. 6 illustrates selected details of an embodiment of a router of a processing       |

| 19 | element.      |                                                                                        |

| 20 |               |                                                                                        |

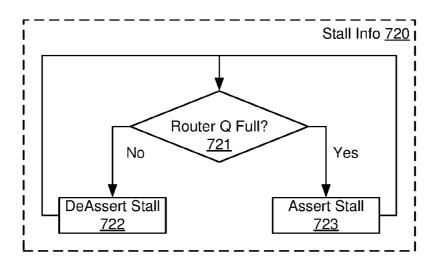

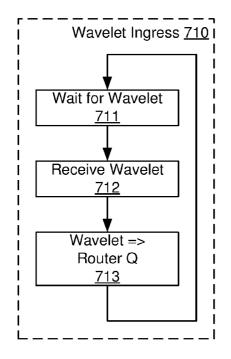

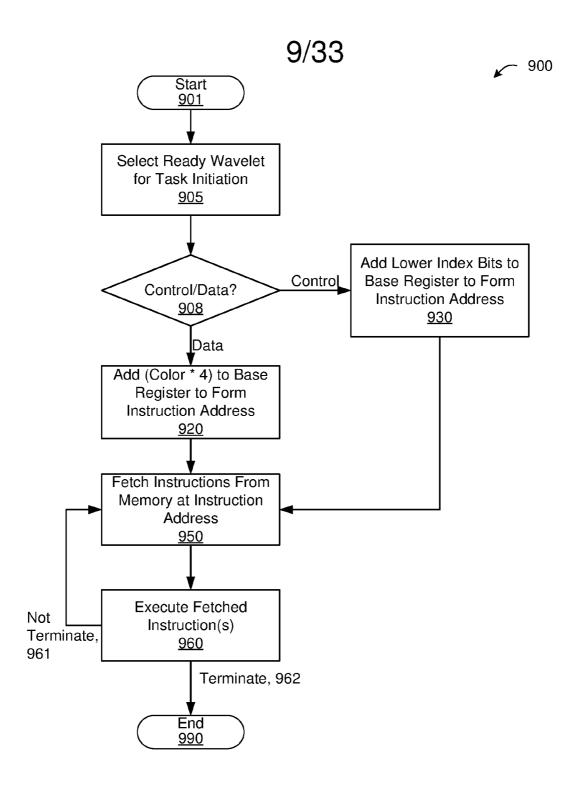

| 21 | [0011]        | Fig. 7 illustrates selected details of an embodiment of processing associated with a   |

| 22 | router of a p | rocessing element.                                                                     |

| 23 |               |                                                                                        |

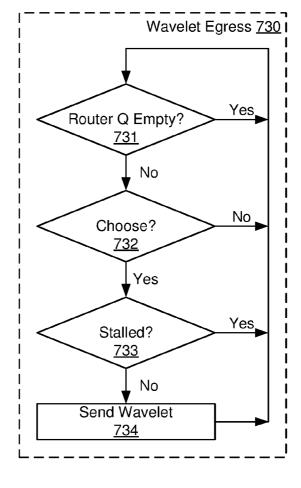

| 24 | [0012]        | Fig. 8 illustrates selected details of an embodiment of a compute element of a         |

| 25 | processing e  | element.                                                                               |

| 26 |               |                                                                                        |

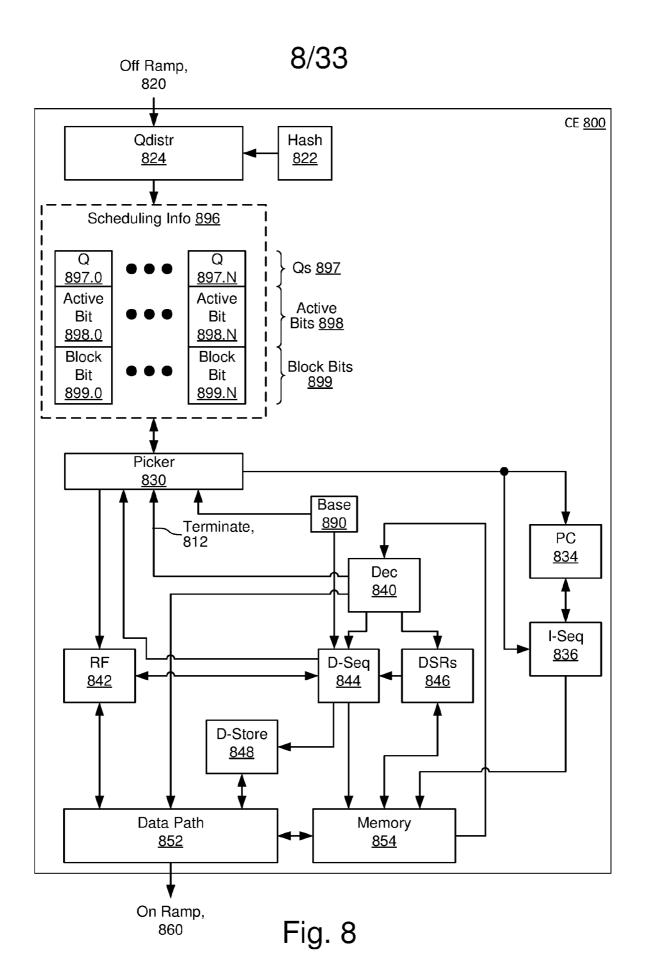

| 27 | [0013]        | Fig. 9 illustrates selected details of an embodiment of processing a wavelet for task  |

| 28 | initiation.   |                                                                                        |

| 29 |               |                                                                                        |

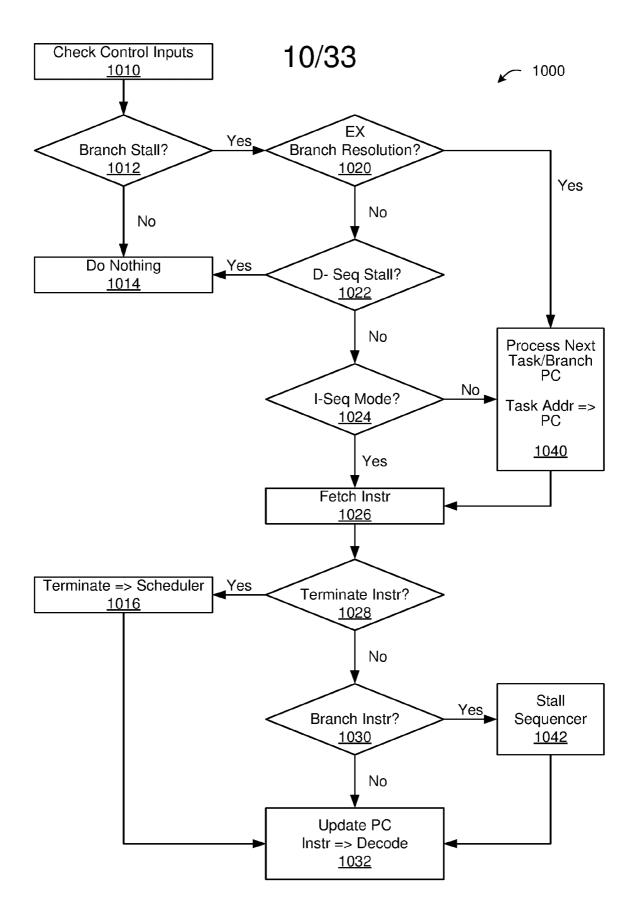

| 30 | [0014]        | Fig. 10 illustrates selected details of an embodiment of instruction processing        |

| 31 | associated w  | rith a compute element of a processing element.                                        |

| 32 | F004F-        |                                                                                        |

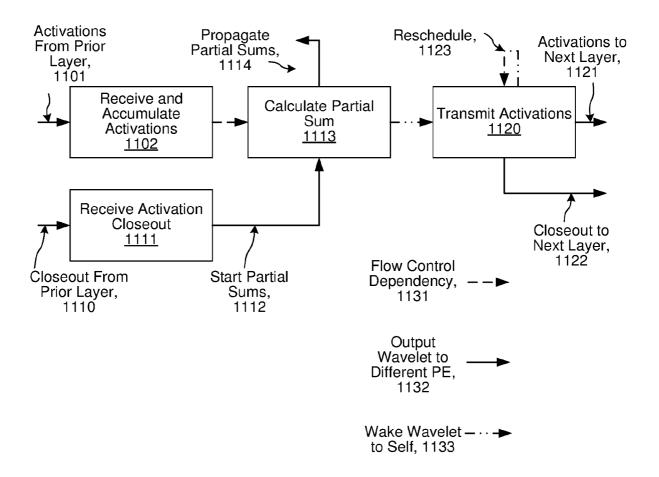

| 33 | [0015]        | Fig. 11 illustrates selected details of an embodiment of flow associated with          |

| 34 | dependency    | management via closeouts.                                                              |

| Ţ        |                 |                                                                                          |

|----------|-----------------|------------------------------------------------------------------------------------------|

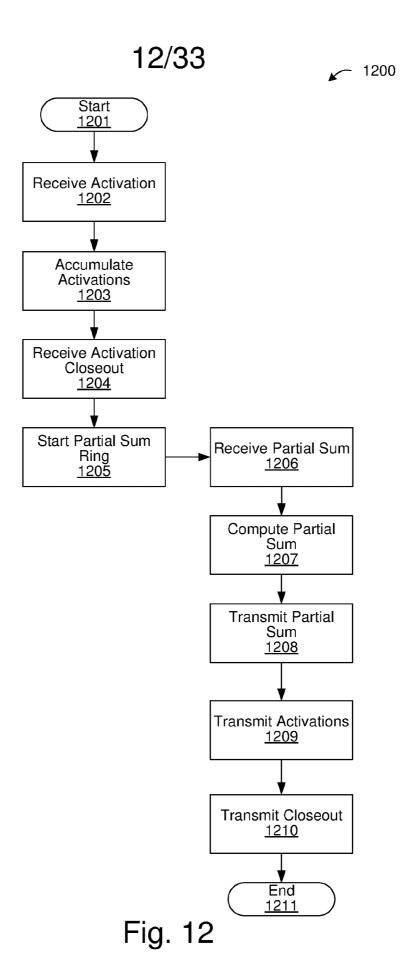

| 2        | [0016]          | Fig. 12 illustrates selected details of an embodiment of flow associated with activation |

| 3        | accumulation    | and closeout, followed by partial sum computation and closeout.                          |

| 4        |                 |                                                                                          |

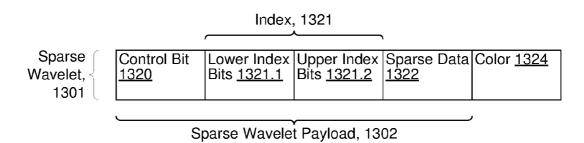

| 5        | [0017]          | Fig. 13A illustrates selected details of an embodiment of a sparse wavelet.              |

| 6        |                 |                                                                                          |

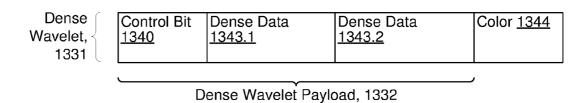

| 7        | [0018]          | Fig. 13B illustrates selected details of an embodiment of a dense wavelet.               |

| 8        |                 |                                                                                          |

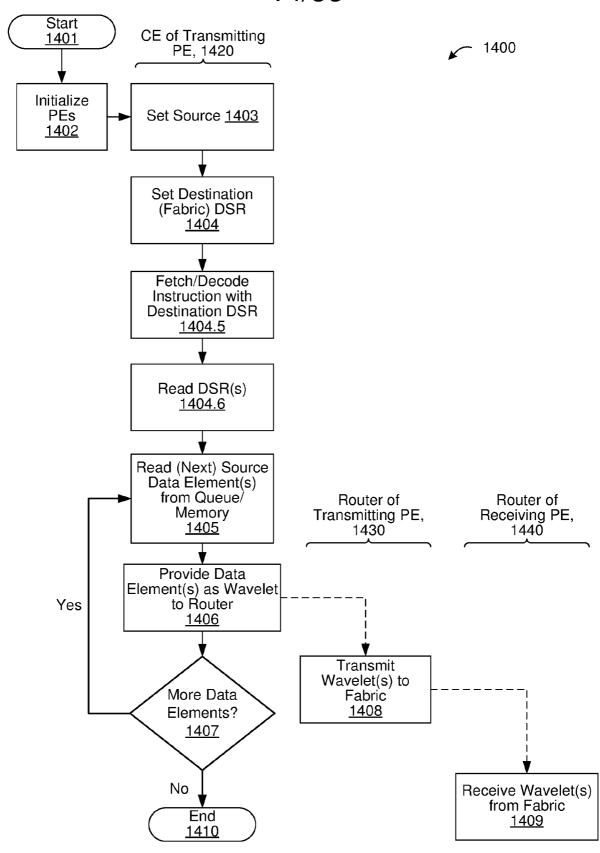

| 9        | [0019]          | Fig. 14 illustrates selected details of an embodiment of creating and transmitting a     |

| 10       | wavelet.        |                                                                                          |

| 11       |                 |                                                                                          |

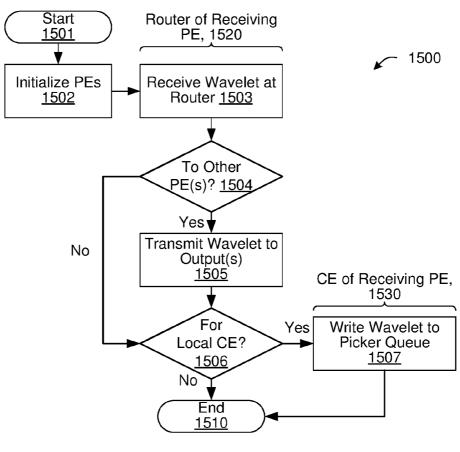

| 12       | [0020]          | Fig. 15A illustrates selected details of an embodiment of receiving a wavelet.           |

| 13       |                 |                                                                                          |

| 14       | [0021]          | Fig. 15B illustrates selected details of an embodiment of consuming a wavelet.           |

| 15       |                 |                                                                                          |

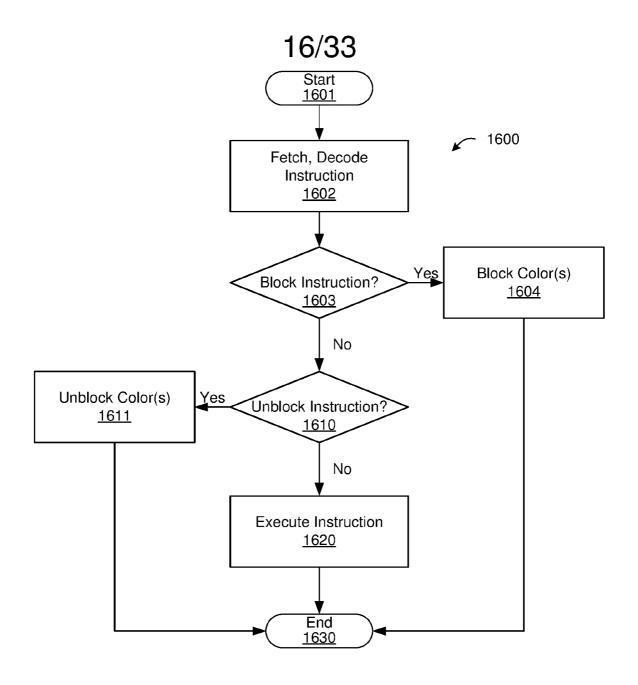

| 16       | [0022]          | Fig. 16 illustrates selected details of an embodiment of block instruction and unblock   |

| 17       | instruction exe | ecution.                                                                                 |

| 18       | 100001          |                                                                                          |

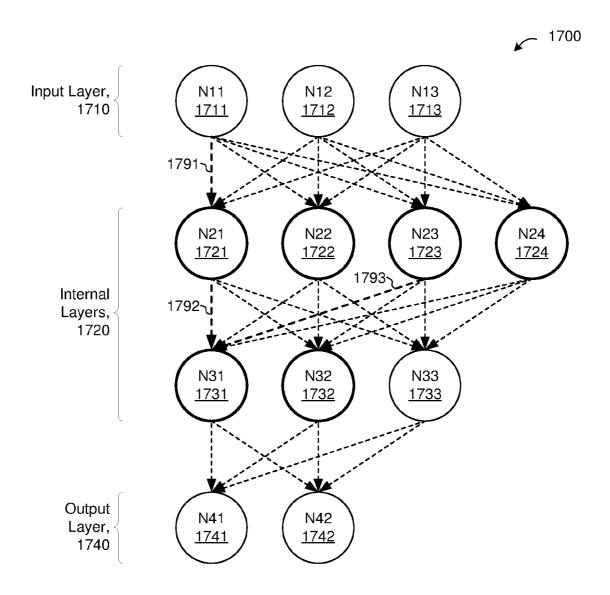

| 19       | [0023]          | Fig. 17 illustrates selected details of an embodiment of a neural network.               |

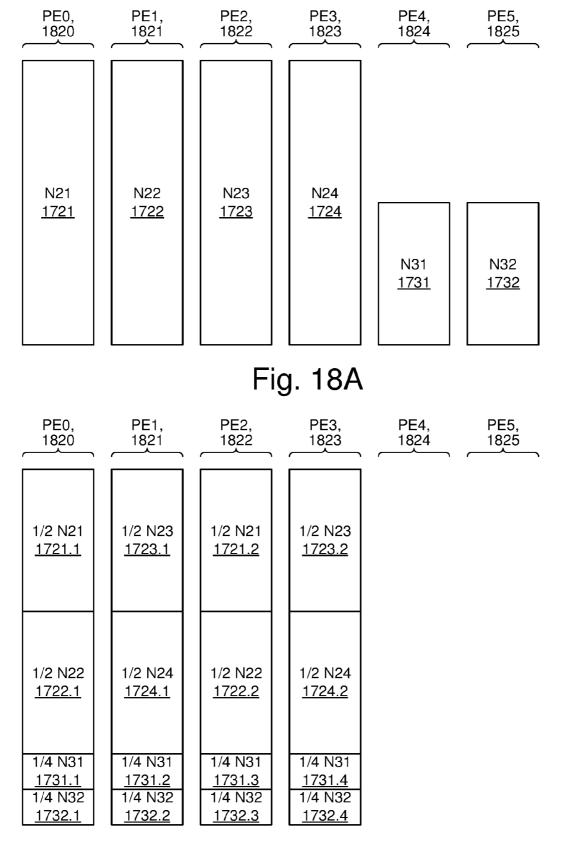

| 20       | [0024]          | Fig. 10A illustration of the first of a Control of the state of the state of             |

| 21       | [0024]          | Fig. 18A illustrates selected details of a first embodiment of an allocation of          |

| 22       | processing ele  | ements to neurons.                                                                       |

| 23<br>24 | [0025]          | Fig. 18B illustrates selected details of a second embodiment of an allocation of         |

| 25       |                 | ements to neurons.                                                                       |

| 25<br>26 | processing ere  | ments to neurons.                                                                        |

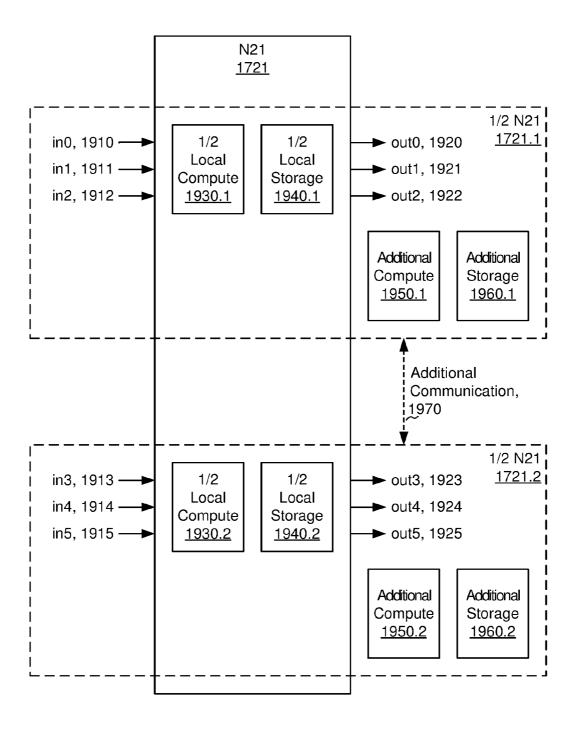

| 27       | [0026]          | Fig. 19 illustrates selected details of an embodiment of smearing a neuron across a      |

| 28       | • •             | ocessing elements.                                                                       |

| 29       | r               |                                                                                          |

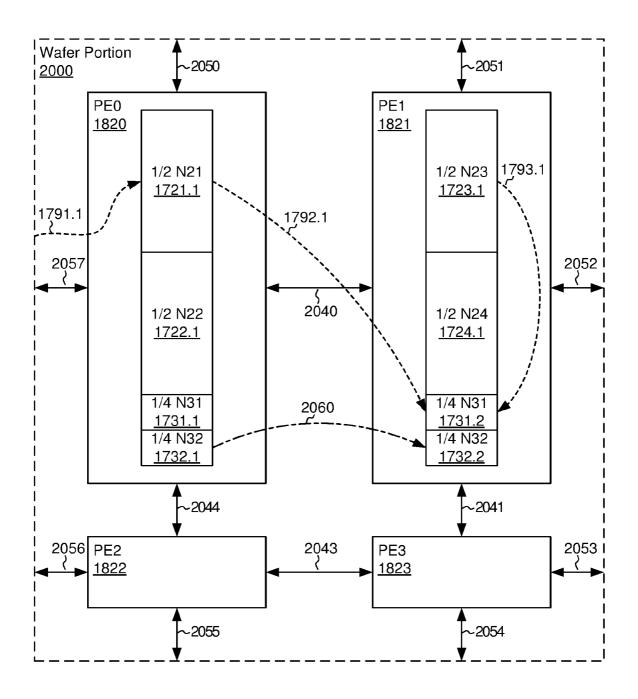

| 30       | [0027]          | Fig. 20 illustrates selected details of an embodiment of communication between           |

| 31       | portions of spi | lit neurons.                                                                             |

| 32       |                 |                                                                                          |

| 33       | [0028]          | Fig. 21A illustrates selected details of an embodiment of a Fabric Input Data Structure  |

| 34       | Descriptor.     |                                                                                          |

| 1  |                |                                                                                        |

|----|----------------|----------------------------------------------------------------------------------------|

| 2  | [0029]         | Fig. 21B illustrates selected details of an embodiment of a Fabric Output Data         |

| 3  | Structure Des  | criptor.                                                                               |

| 4  |                |                                                                                        |

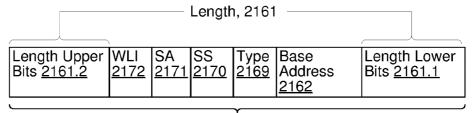

| 5  | [0030]         | Fig. 21C illustrates selected details of an embodiment of a 1D Memory Vector Data      |

| 6  | Structure Des  | criptor.                                                                               |

| 7  |                |                                                                                        |

| 8  | [0031]         | Fig. 21D illustrates selected details of an embodiment of a 4D Memory Vector Data      |

| 9  | Structure Des  | criptor.                                                                               |

| 10 |                |                                                                                        |

| 11 | [0032]         | Fig. 21E illustrates selected details of an embodiment of a Circular Memory Buffer     |

| 12 | Data Structure | e Descriptor.                                                                          |

| 13 |                |                                                                                        |

| 14 | [0033]         | Fig. 22A illustrates selected details of an embodiment of a Circular Memory Buffer     |

| 15 | Extended Dat   | a Structure Descriptor.                                                                |

| 16 |                |                                                                                        |

| 17 | [0034]         | Fig. 22B illustrates selected details of an embodiment of a 4D Memory Vector           |

| 18 | Extended Date  | a Structure Descriptor.                                                                |

| 19 |                |                                                                                        |

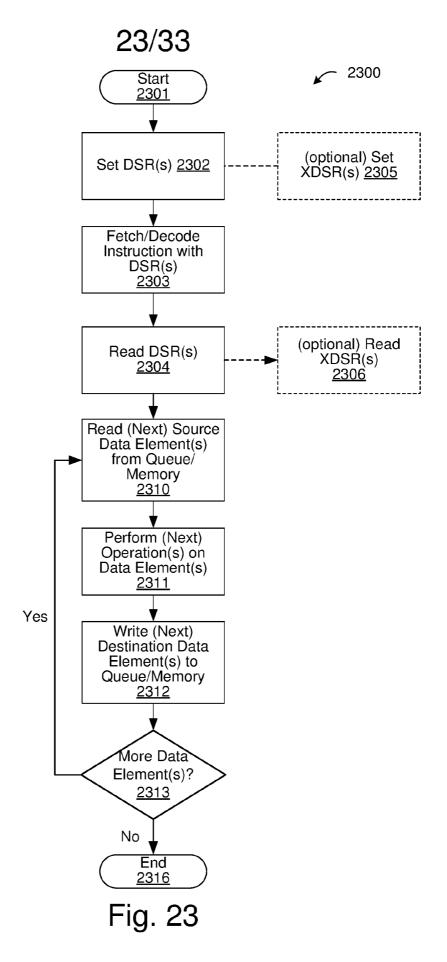

| 20 | [0035]         | Fig. 23 illustrates selected details of accessing operands in accordance with data     |

| 21 | structure desc | riptors.                                                                               |

| 22 |                |                                                                                        |

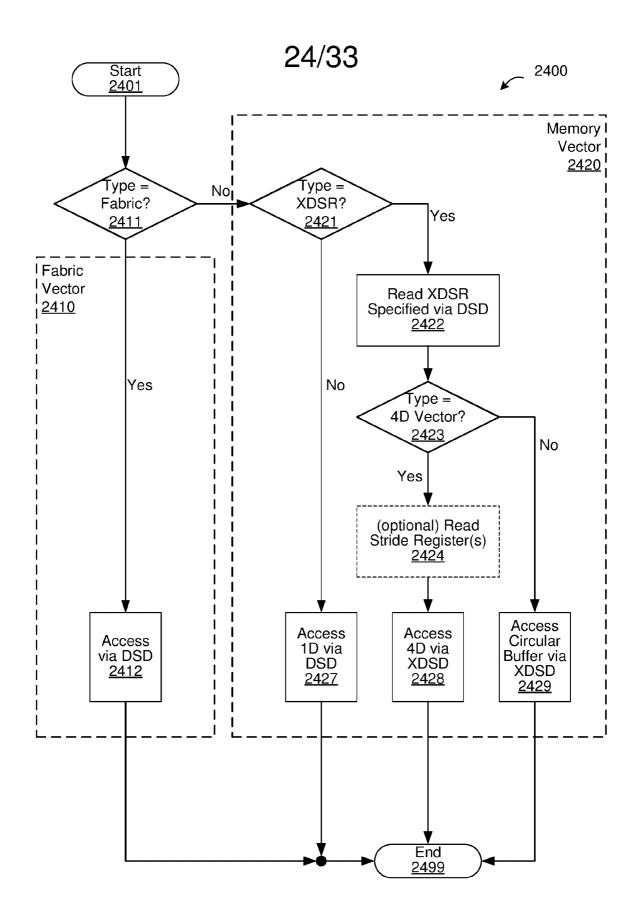

| 23 | [0036]         | Fig. 24 illustrates selected details of an embodiment of decoding a data structure     |

| 24 | descriptor.    |                                                                                        |

| 25 |                |                                                                                        |

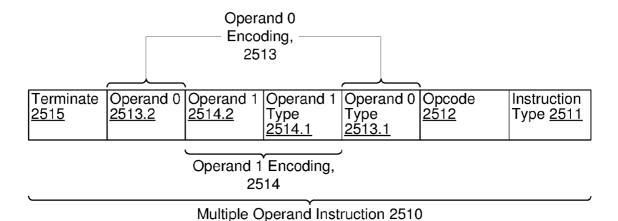

| 26 | [0037]         | Fig. 25A illustrates selected details of an embodiment of a multiple operand           |

| 27 | instruction.   |                                                                                        |

| 28 |                |                                                                                        |

| 29 | [0038]         | Fig. 25B illustrates selected details of an embodiment of a one source, no destination |

| 30 | operand instru | action.                                                                                |

| 31 |                |                                                                                        |

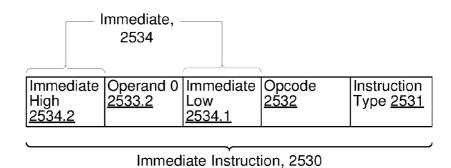

| 32 | [0039]         | Fig. 25C illustrates selected details of an embodiment of an immediate instruction.    |

| 33 |                |                                                                                        |

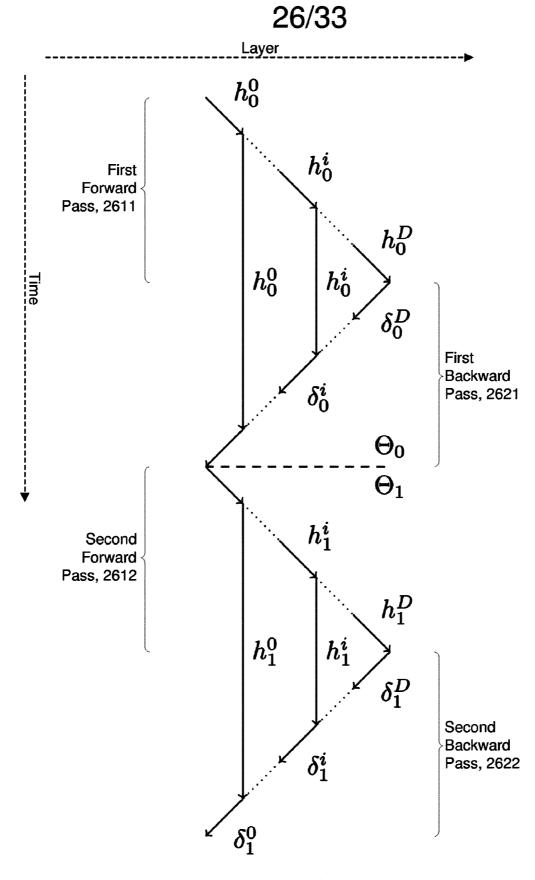

| 1  | [0040]                                                              | Fig. 26A illustrates an embodiment of a pipeline flow for Stochastic Gradient Descent     |  |

|----|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| 2  | (SGD).                                                              |                                                                                           |  |

| 3  |                                                                     |                                                                                           |  |

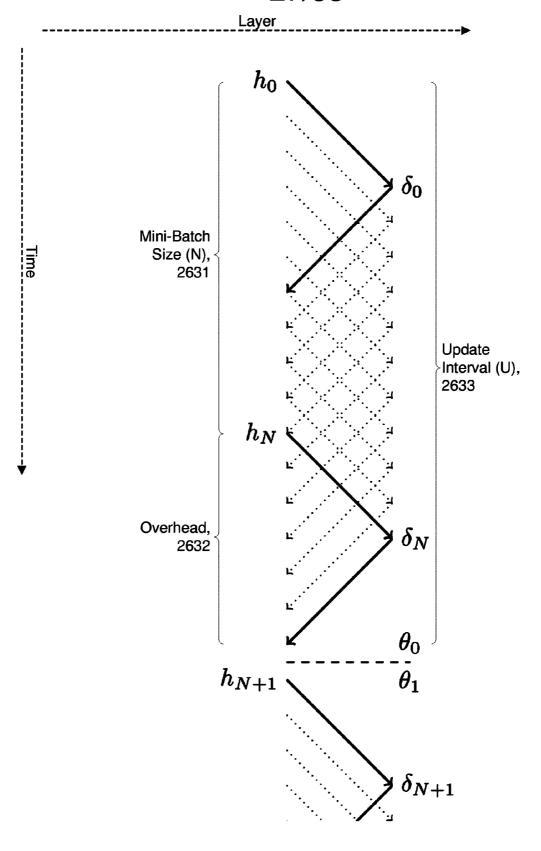

| 4  | [0041]                                                              | Fig. 26B illustrates an embodiment of a pipeline flow for Mini-Batch Gradient             |  |

| 5  | Descent (MBGD).                                                     |                                                                                           |  |

| 6  |                                                                     |                                                                                           |  |

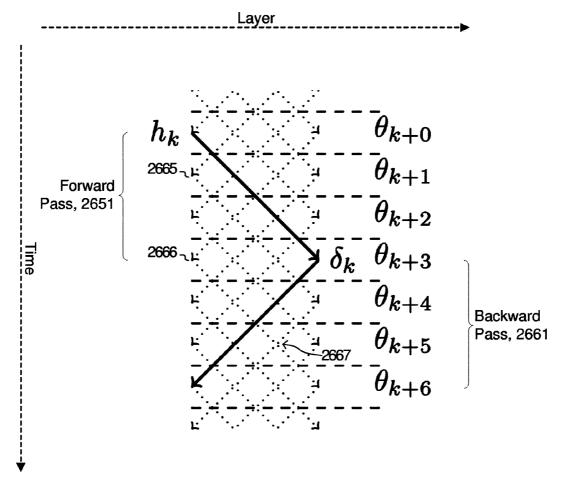

| 7  | [0042]                                                              | Fig. 26C illustrates an embodiment of a pipeline flow for Continuous Propagation          |  |

| 8  | Gradient D                                                          | escent (CPGD).                                                                            |  |

| 9  |                                                                     |                                                                                           |  |

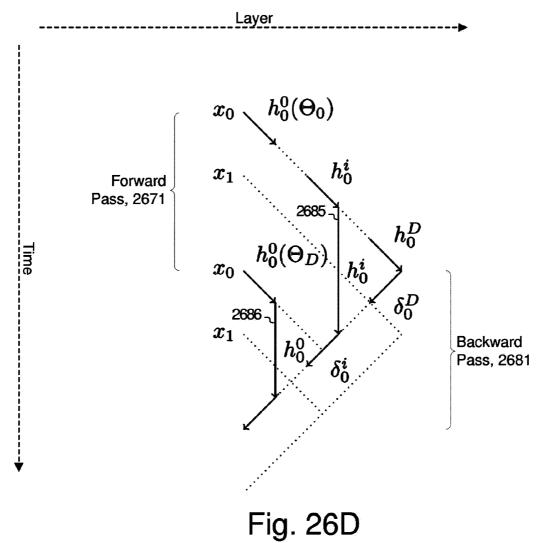

| 10 | [0043]                                                              | Fig. 26D illustrates an embodiment of a pipeline flow for Continuous Propagation          |  |

| 11 | Gradient Descent (CPGD) with Reverse CheckPoint (RCP).              |                                                                                           |  |

| 12 |                                                                     |                                                                                           |  |

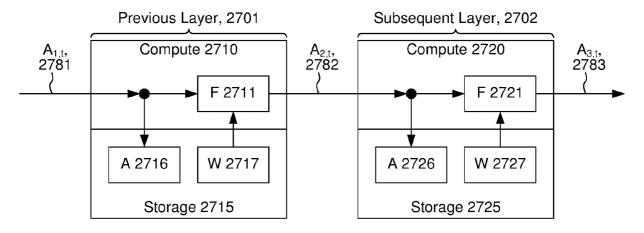

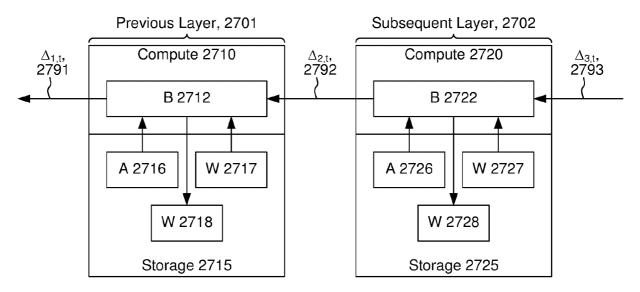

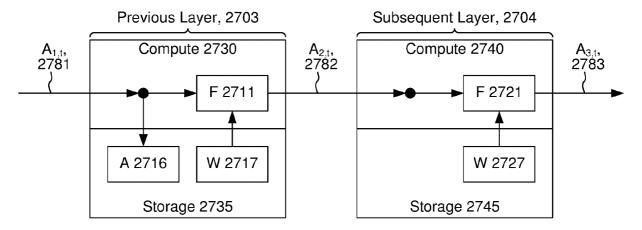

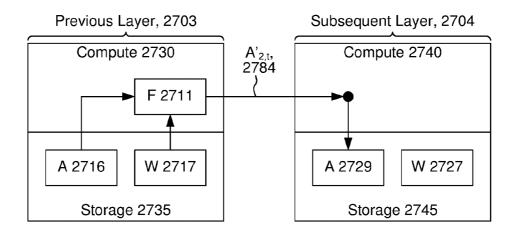

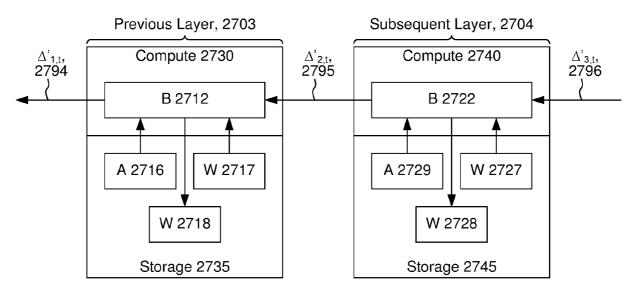

| 13 | [0044]                                                              | Figs. 27A-27E illustrate various aspects of forward pass and backward pass                |  |

| 14 | embodiments in accordance with SGD, MBGD, CPGD, and RCP processing. |                                                                                           |  |

| 15 |                                                                     |                                                                                           |  |

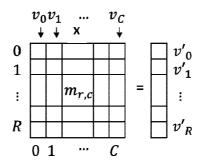

| 16 | [0045]                                                              | Fig. 28A illustrates a generic operation of a matrix $(m)$ multiplied by a vector $(v)$ . |  |

| 17 |                                                                     |                                                                                           |  |

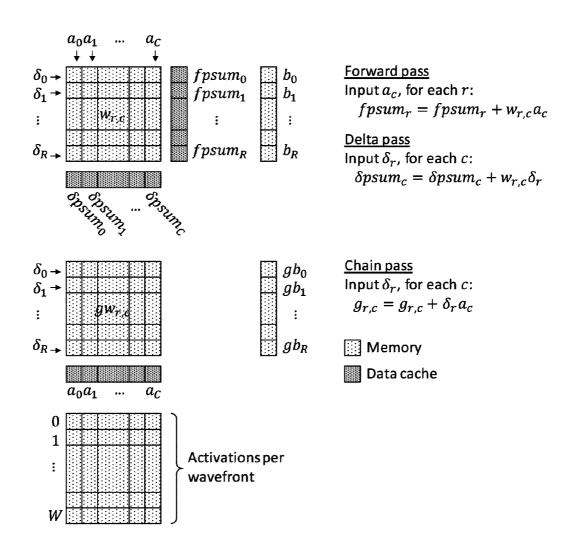

| 18 | [0046]                                                              | Fig. 28B illustrates various representations of memory structures used in a forward       |  |

| 19 | pass, a delta                                                       | a pass, and a chain pass.                                                                 |  |

| 20 |                                                                     |                                                                                           |  |

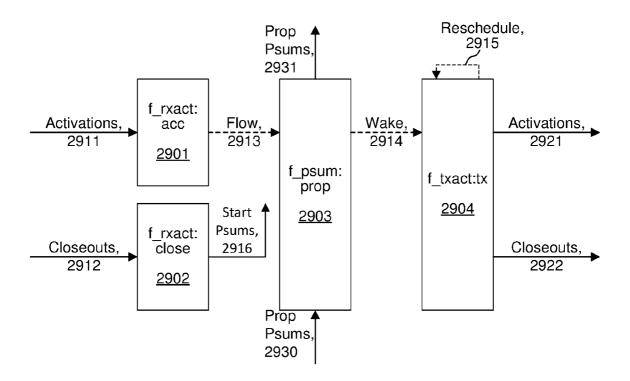

| 21 | [0047]                                                              | Fig. 29 illustrates an embodiment of tasks as used in a forward pass state machine.       |  |

| 22 |                                                                     |                                                                                           |  |

## [0048]

| Ref. Symbol | Element Name              |

|-------------|---------------------------|

| 100         | Neural Network System     |

| 110         | Combined Server(s)        |

|             | LAN                       |

| 112         | 100 <b>G</b> b            |

| 113         | Placements                |

| 114         | Weights                   |

| 115         | Weights                   |

|             | Deep Learning Accelerator |

|             | FPGAs                     |

| 122         | PEs                       |

| 123         | Coupling                  |

| 130         | Autonomous Vehicle        |

|             | CPUs                      |

|             | CRM                       |

|             |                           |

|             | Camera                    |

| 140         | Cell Phone                |

| 141         | CPUs                      |

| 142         | CRM                       |

| 143         | IEs                       |

| 145         |                           |

| 150         | Placement Server(s)       |

| 151         |                           |

|             |                           |

|             | Connection Server(s)      |

| 161         | CPUs                      |

|             |                           |

|             | NICs                      |

|             | Internet                  |

|             | Neural Network Software   |

|             | Placement Server(s) SW    |

| 212         | Neuron to PE Mapping SW   |

| 220         | Connection Server(s) SW   |

|             | 100Gb NIC Driver          |

|             | Training Info Provider SW |

| 226         | Weight Receiver SW        |

| 230         | Autonomous Vehicle SW     |

| 232         | Video Camera SW           |

| 233         | Inference Engine(s) SW    |

| 234         | Navigating SW             |

| 240         | Cell Phone SW             |

| 242         | Still Camera SW           |

| 243         | Inference Engine(s) SW    |

| 244         | Posting SW                |

| Ref. Symbol | Element Name                                         |

|-------------|------------------------------------------------------|

| 250         | Misc SW on FPGAs                                     |

| 260         | Task SW on PEs                                       |

| 300         |                                                      |

|             | Place Neurons                                        |

| 320         |                                                      |

| 330         |                                                      |

| 340         |                                                      |

| 350         | Forward Pass, Delta Pass, Chain Pass, Update Weights |

|             | Training Complete?                                   |

| 370         |                                                      |

|             | Use Weights for Inference                            |

| 400         |                                                      |

| 401         | Forward                                              |

| 402         | Delta                                                |

| 403         | Chain                                                |

| 410         | ASIC                                                 |

| 411         | ASIC                                                 |

| 412         | Wafer                                                |

| 420         | I/O FPGAs                                            |

| 430         | North coupling                                       |

| 431         | East coupling                                        |

| 432         | South coupling                                       |

| 433         |                                                      |

| 497         | Particular PE                                        |

| 498         | Particular PE                                        |

| 499         | PE                                                   |

| 500         | PE                                                   |

| 510         | Router                                               |

| 511         | West                                                 |

| 512         | 1                                                    |

|             | North                                                |

| 514         |                                                      |

|             | East                                                 |

|             | South                                                |

|             | Compute Element                                      |

| 521         | Off Ramp                                             |

| 522         | On Ramp                                              |

| 600         | Router                                               |

| 610         | Data In                                              |

| 611         | skipX+                                               |

| 612         | skipX-                                               |

| 613         | X+                                                   |

| 614         |                                                      |

| 615         |                                                      |

| 616         |                                                      |

|             | On Ramp                                              |

|             | Data Out                                             |

| 621         | ski <b>pX</b> +                                      |

| Ref. Symbol | Element Name                  |

|-------------|-------------------------------|

| 622         | ski <b>pX</b> -               |

| 623         |                               |

| 624         |                               |

| 625         |                               |

| 626         |                               |

|             | Off Ramp                      |

|             | Stall Out                     |

|             | skipX+                        |

|             | skipX-                        |

| 633         | X+                            |

| 634         |                               |

| 635         |                               |

| 636         |                               |

|             | On Ramp                       |

| 640         | Sources                       |

|             | skipX+                        |

| 642         | skipX-                        |

| 643         | X+                            |

| 644         | X-                            |

| 645         |                               |

| 646         | Y-                            |

| 647         | Off Ramp                      |

| 650         | Data Queues                   |

| 651         | Write Dec                     |

| 652         | Out                           |

| 653         | Sources                       |

| 654         |                               |

| 656         |                               |

| 657         | Stall                         |

| 660         | Control Info                  |

| 661         | Dest                          |

| 662         | Sent                          |

| 670         |                               |

| 710         | Wavelet Ingress               |

|             | Wait for Wavelet              |

|             | Receive Wavelet               |

| 713         |                               |

| 720         | Stall Info                    |

| 721<br>722  | Router Q Full? DeAssert Stall |

| 723         | Assert Stall                  |

| 730         | Wavelet Egress                |

| 731         | Q Empty?                      |

| 732         | Choose?                       |

| 733         |                               |

| 734         |                               |

| 800         | CE                            |

| 812         | Terminate                     |

| 812         | 1 Criminaec                   |

| Ref. Symbol | Element Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 820         | Off Ramp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 822         | Hash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 824         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 830         | Picker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 834         | PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 836         | I-Seq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 840         | Dec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 842         | RF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | D-Seq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | DSRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             | D-Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 852         | Data Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 854         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 860         | On Ramp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 890         | Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 896         | Scheduling Info                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 897         | Qs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 897.0       | Q0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 897.N       | QN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |