# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 29 December 2004 (29.12.2004)

**PCT**

# (10) International Publication Number WO 2004/114421 A1

(51) International Patent Classification<sup>7</sup>:

H01L 33/00

(21) International Application Number:

PCT/KR2004/001480

(22) International Filing Date: 21 June 2004 (21.06.2004)

(25) Filing Language:

Korean

(26) Publication Language:

English

(30) Priority Data:

10-2003-0041409

25 June 2003 (25.06.2003) KR

- (71) Applicant (for all designated States except US): LG IN-NOTEK CO.,LTD [KR/KR]; 14th Fl. Hansol Bldg., 736-1 Yoksam-dong, Kangnam-gu, Seoul 135-083 (KR).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): LEE, Suk-Hun [KR/KR]; 706-502 Chumdan Line7th Apt., Wolgae-dong, Gwangsan-gu, Gwangju 506-302 (KR).

- (74) Agent: HAW, Yong-Noke; 8th Fl. Songchon Bldg., 642-15,, Yoksam-dong, Kangnam-gu, Seoul 135-080 (KR).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: A LIGHT EMITTING DEVICE USING NITRIDE SEMICONDUCTOR AND FABRICATION METHOD OF THE SAME

| lnxGa <sub>1-x</sub> N/lnyGa <sub>1-y</sub> N Super Lattice | 120               |

|-------------------------------------------------------------|-------------------|

| P-GaN                                                       | 118               |

| ln₂Ga <sub>1-z</sub> N Barrier                              | 114 )             |

| InyGa <sub>1-y</sub> N Well                                 | 114<br>112<br>110 |

| Low mole In <sub>x</sub> Ga <sub>1-x</sub> N                | 110               |

| Si-In co-doped GaN                                          | 108               |

| In-doped GaN                                                | 106               |

| Buffer Layer                                                | 104               |

| Substrate                                                   | 102               |

|                                                             |                   |

(57) Abstract: A nitride based 3-5 group compound semiconductor light emitting device comprising: a substrate; a buffer layer formed above the substrate; a first In-doped GaN layer formed above the buffer layer; in  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer formed above the first In-doped GaN layer; a first electrode contact layer formed above the  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer; an active layer formed above the first electrode contact layer and functioning to emit light; a second In-doped GaN layer; a GaN layer formed above the second In-doped GaN layer; and a second electrode layer formed above the GaN layer. The present invention can reduce crystal defects of the nitride based 3-5 group compound semiconductor light emitting device and ensure the reliability thereof.

# A LIGHT EMITTING DEVICE USING NITRIDE SEMICONDUCTOR AND FABRICATION METHOD OF THE SAME

### Technical Field

5

10

15

20

25

30

35

The present invention relates to a nitride based 3-5 group compound semiconductor. More particularly, the present invention relates to a nitride based 3-5 group compound semiconductor light emitting device and a fabrication method thereof capable of reducing crystal defects originated from the mismatch of thermal expansion coefficient and lattice constant between a substrate and a GaN based single crystal layer grown thereon as well as improving the crystallinity of the GaN based single crystal layer in order to improve the performance of the light emitting device and ensure the reliability thereof.

## Background Art

GaN-based semiconductors are generally applied to optical devices such as a blue/green LED and high-speed switching and high-power electronic devices such as a Metal Semiconductor Field Effect Transistor (MESFET) and a High Electron Mobility Transistor (HEMT). In particular, blue/green LEDs have been mass produced lately, and their worldwide demand is rising sharply.

A GaN-based semiconductor light emitting device is typically grown on a substrate of sapphire or SiC. Then, a polycrystalline layer of  $\mathrm{Al_yGa_{1-y}N}$  is grown as a buffer layer on the sapphire or SiC substrate at a low growth temperature. At a higher temperature, an undoped GaN layer and a Si-doped n-type GaN layer or a mixed structure thereof are grown on the buffer layer to provide the n-type GaN layer as a first electrode contact layer. Then, a Mg-doped p-type layer is-formed as a second electrode contact layer thereon to produce a nitride based 3-5 group compound semiconductor light emitting device. In addition, an active layer (of a multiple quantum well structure) is interposed between the n-type

first electrode contact layer and the p-type second electrode contact layer.

In the nitride based 3-5 group compound semiconductor light emitting device of this structure, crystal defects found in the interface between the substrate and the buffer layer have a very high value of about  $10^8 \, / \, \mathrm{cm}^3$ . As a result, this degrades electrical characteristics of the nitride based 3-5 group compound semiconductor light emitting device, and more particularly, increases leakage current under reverse bias conditions, thereby causing a fatal effect to the reliability of the light emitting device.

In addition, the crystal defects created in the interface between the substrate and the buffer layer degrades the crystallinity of the active layer, and therefore disadvantageously lowers the luminous efficiency of the nitride based 3-5 group compound semiconductor light emitting device.

In the meantime, in order to improve the performance and reliability of the GaN-based semiconductor light emitting device, researches have been made for new buffer layers and various fabrication methods of GaN-based semiconductors have been studied.

## Disclosure of the Invention

5

10 .

15

20

35

The present invention has been made to solve the foregoing problems of the prior art and it is therefore an object of the present invention to provide a nitride based 3-5 group compound semiconductor light emitting device and a fabrication method thereof capable of reducing crystal defects of a GaN based single crystal layer as well as improving its crystallinity in order to improve the performance and reliability thereof.

It is another object of the present invention to provide a nitride based 3-5 group compound semiconductor light emitting device and a fabrication method thereof capable of practically realizing high brightness performance

from an active layer of only a single quantum well structure.

According to an aspect of the invention for realizing the above objects, there is provided A nitride based 3-5group compound semiconductor Light emitting comprising: a substrate; a buffer layer formed above the substrate; a first In-doped GaN layer formed above the buffer layer; an  $In_xGa_1-_xN/In_yGa_1-_yN$  super lattice structure layer formed above the first In-doped GaN layer; a first electrode layer formed above the contact  $In_xGa_1-_xN/In_yGa_{1-y}N$  super lattice structure layer; an active layer formed above the first electrode contact layer and functioning to emit light; a second In-doped GaN layer; a GaN layer formed above the second In-doped GaN layer; and a second electrode contact layer formed above the GaN layer.

5

10

15

20

25

30

35

According to another aspect of the invention for realizing the above objects, there is provided A nitride based 3-5 group compound semiconductor light emitting device comprising: a substrate; a buffer layer formed above the substrate; a first In-doped GaN layer formed above the buffer layer; a first electrode contact layer formed above the first In-doped GaN layer; an active layer formed above the first electrode contact layer and functioning to emit light; a GaN layer formed above the active layer; and a second electrode contact layer formed above the GaN layer.

According to further an aspect of the invention for realizing the above objects, there is provided A nitride based 3-5 group compound semiconductor light emitting device comprising: a substrate; a buffer layer formed above the substrate; a first electrode contact layer formed above the GaN buffer layer; an active layer formed above the first electrode contact layer, and including a low mole In-doped  $In_xGa_{1-x}N$  layer, an  $In_yGa_{1-y}N$  well layer and an  $In_zGa_{1-z}N$  barrier layer; a GaN layer formed above the active layer; and a second electrode contact layer formed above the GaN layer.

According to still another aspect of the invention for realizing the above objects, there is provided A fabrication

method of a nitride based 3-5 group compound semiconductor light emitting device, comprising: forming a buffer layer above a substrate; forming a first In-doped GaN layer above the buffer layer; forming a first electrode contact layer above the first In-doped GaN layer; forming an active layer for emitting light above the first electrode contact layer; forming a GaN layer above the active layer; and forming a second electrode contact layer above the GaN layer.

The advantage of the present invention is to reduce crystal defects of a GaN based single crystal layer as well as improve its crystallinity, thereby improving the performance and reliability thereof.

As another advantage, the present invention can practically realize high brightness performance from an active layer of only a single quantum well structure.

## Brief Description of the Drawings

5

10

15 ·

20

25

30

35

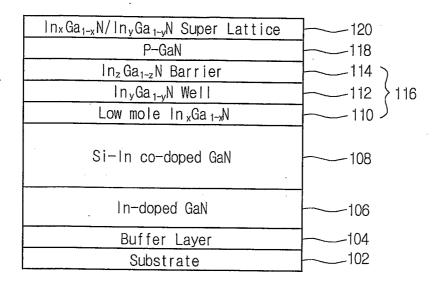

FIG. 1 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a first embodiment of the present invention;

FIG. 2 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a second embodiment of the present invention;

FIG. 3 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a third embodiment of the present invention; and

FIG. 4 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a fourth embodiment of the present invention.

## Best Mode for Carrying Out the Invention

Hereinafter, preferred embodiments of the present invention will be described in detail with reference to accompanying drawings.

While preferred embodiments of the present invention will be described in reference with the accompanying

drawings, it is apparent to those skilled in the art that the principle of the present invention is not limited by the disclosed embodiments thereof, but can be readily modified into various alternatives through the addition, variation and omission of components.

## First Embodiment

5

10

15

20

.25

30

35

FIG. 1 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a first embodiment of the present invention.

As shown in FIG. 1, a nitride based 3-5 group compound semiconductor light emitting device has a cross-sectional structure including a buffer layer 104 grown on a substrate 102, a first electrode contact layer 108 made of an n-type GaN layer (codoped with Si and In) and a second electrode contact layer 120 of an  $\rm In_x Ga_{1-x}N/In_y Ga_{1-y}N$  super lattice structure. Herein, the first and second electrode contact layers 108 and 120 are provided with electrodes (not shown), respectively, in following process steps so that external voltage can be applied thereto via the electrodes.

The nitride based 3-5 group compound semiconductor light emitting device of the present invention also has an active layer 116 of a quantum well structure which is interposed between the first electrode contact layer 108 and the second electrode contact layer 120 to form a heterostructure. The active layer 116 includes a low mole In-doped GaN layer 110, an  $\rm In_x Ga_{1-y} N$  well layer 112 and an  $\rm In_x Ga_{1-x} N$  barrier layer 114.

In addition, the nitride based 3-5 group compound semiconductor light emitting device also has an In-doped GaN layer 106 formed between the buffer layer 104 and the first electrode contact layer 108 and a p-type GaN layer 118 formed between the  $\rm In_xGa_{1-x}N$  barrier layer 114 and the second electrode contact layer 120.

A fabrication method of the nitride-based 3-5 group compound semiconductor light emitting device of the present

invention will be described as follows:

5

10

15

20

25

30

35

First, a GaN buffer layer 104 is formed on a sapphire substrate 102 at a low growth temperature. Then, the buffer layer 104 of the GaN-based semiconductor may be grown into an InGaN/GaN super lattice structure and a structure of  $In_xGa_{1-x}N/GaN$  and  $Al_xIn_yGa_{1-x}N/In_xGa_{1-x}N/GaN$  at the low growth temperature.

The buffer layer 104 formed on the substrate 102 as above can efficiently restrain crystal defects induced from the mismatch of thermal expansion coefficient and lattice constant between the substrate 102 and a GaN-based single crystal layer grown on the substrate 102, thereby producing a high quality GaN-based semiconductor.

More particularly, in the process step of growing the GaN buffer layer 104,  $H_2$  and  $N_2$  carrier gases, TMGa, TMIn and TMAl sources and  $NH_3$  gas are fed at a temperature of about 500 to  $700\,^{\circ}$ C to grow the GaN buffer layer 104.

Then, an In-doped GaN layer 106 and a GaN layer 108 containing Si and In codoped therein are grown on the buffer layer 104 at a high growth temperature. Herein the Si/Incodoped GaN layer 108 is used as a first electrode contact layer.

More particularly, in the process step of growing a GaN based single crystal layer of the GaN-based semiconductor, the GaN based single crystal layer is grown by feeding TMGa, TMIn and TMAl sources at a temperature of about 900 to  $1100\,^{\circ}$ C with an MOCVD apparatus, in which SiH4 gas may be used as a Si doping source, and TMIn may be used as an In doping source.

The active layer 116 for emitting light in a desired wavelength range includes a single quantum well. More particularly, the low mole In-doped GaN layer 110 of the active layer 116 is grown in the range of 10 to  $500\,\text{Å}$ . More preferably, the low mole In-doped GaN layer 110 is grown to a thickness in the range of 50 to  $300\,\text{Å}$ . The content of the low mole In-doped GaN layer may be expressed as  $\text{In}_x\text{Ga}_{1-x}\text{N}$  (0 <

$x \leq 0.2$ ). Then, a quantum well layer of an  $In_yGa_{1-y}N$  well layer 112 and an  $In_zGa_{1-z}N$  barrier layer 114 of different In content is grown on the low mole In-doped  $In_xGa_{1-x}N$  layer 110 to form the active layer.

5

10

15

20

25

30

35

In the process step of growing a single quantum well structure of the active layer 116, the low mole In-doped  $In_xGa_{1-x}N$  layer 110, the  $In_yGa_{1-y}N$  well layer 112 (0 < y  $\leq$ 0.35) and the  $In_zGa_{1-z}N$  barrier layer 114 (0 < z  $\leq$ 0.2) are grown by flowing TMGa, TMIn and TMAl sources on  $N_2$  or  $H_2+N_2$  carrier gas in  $NH_3$  atmosphere. In this case, the low mole In-doped  $In_xGa_{1-x}N$  layer 110 has a thickness of about 10 to 500Å, and its surface is uniformly grown in a spiral mode. Further, at a surface growth temperature of about 700 to 800°C, the InGaN well layer 112 for emitting light is grown to a thickness of 5 to 30Å and the InGaN barrier layer 114 is grown to a thickness of 50 to 500Å.

In addition, in order to realize high brightness light emitting device performance, it is necessary to maintain the uniform spiral mode from the surface of the low mole In-doped  ${\rm In_xGa_{1-x}N}$  layer 110 to the InGaN barrier layer 114. If above growth conditions are satisfied, a practical high brightness light emitting device can be fabricated through the formation of an active layer having a single quantum well structure as well as having a multiple quantum well structure. Of course, the multiple quantum well structure can be adopted in cases that other parts are the same.

In the meantime, the content distribution of dopant in the low mole In-doped  $\rm In_xGa_{1-x}N$  layer 110, the  $\rm In_yGa_{1-y}N$  well layer 112 and the  $\rm In_zGa_{1-z}N$  barrier layer 114 can be adjusted as follows: The In content of the low mole In-doped  $\rm In_xGa_{1-x}N$  layer 110 is adjusted to be lower than that of the  $\rm In_zGa_{1-z}N$  barrier layer 114. The doped In contents x, y and z may be expressed as 0 < x < 0.05, 0 < y < 0.3, and 0 < z < 0.1.

After the active layer for emitting light is grown according to the above-described process steps, temperature is elevated to grow the Mg-doped p-type GaN based single

crystal layer 118 in  $H_2$ ,  $N_2$  and  $H_2+N_2$  gases and under  $NH_3$  atmosphere. The p-type GaN layer 118 is grown to a thickness of about 500 to 5000Å at a growth temperature of about 900 to  $1020\,\mathrm{C}$ .

5

10

15

20

25

30

35

Upon the growth of the p-type GaN layer 118, the second electrode contact layer 120 of an  $\rm In_x Ga_{1-x}N/\rm In_y Ga_{1-y}N$  super lattice structure(0 < x  $\leq$ 0.2, and 0 < y  $\leq$ 0.2) is grown on the p-type GaN layer 118. The  $\rm In_x Ga_{1-x}N/\rm In_y Ga_{1-y}N$  super lattice structure imparts efficient current spreading to the second electrode contact layer 120. The electrode of the second electrode contact layer can be advantageously obtained from electrode metal the same as that of the first electrode contact layer 108.

According to the nitride based 3-5 group compound semiconductor light emitting device of this embodiment, the first electrode contact layer 108 is formed of an n-type electrode contact layer and the second electrode contact layer 120 is formed of a n-type electrode contact layer. Since high contact resistance is originated from the low Mg doping efficiency of a p-type GaN layer used as a second electrode contact layer in a conventional nitride based 3-5 group compound semiconductor light emitting device having first and second electrode contact layers in the form of n-type and p-type electrode contact layers, this embodiment can overcome the high contact resistance and remove a resultant current spreading layer.

Regarding the relation with the p-type GaN layer 118, it can be expressed that the first electrode contact layer 108, the p-type GaN layer 118 and the second electrode contact layer 120 have an n-p-n junction.

Here, the second electrode contact layer 120 alternate with each other at a thickness of 2 to  $50\,\text{Å}$ , and the second electrode contact layer 120 has the maximum thickness under  $200\,\text{Å}$ . Also, the growing step can be performed by feeding  $N_2$ ,  $N_2+H_2$  and  $NH_3$  gases and TMGa and TMIn sources in a growth temperature range from 700 to  $850\,\text{°C}$  in order to grow a high

brightness light emitting device having a hetero-structure which is excellent in internal quantum efficiency and operating voltage characteristics.

## Second Embodiment

5

10

15

20

25

30

35

FIG. 2 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a second embodiment of the present invention.

The structure of the nitride based 3-5 group compound semiconductor light emitting device of this embodiment shown in FIG. 2 is basically similar to that of the first embodiment except that an  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 210 is additionally placed underlying a first electrode contact layer 212 forming a heterostructure in order to minimize crystal defects originated from the mismatch of lattice constant and thermal expansion coefficient between a substrate 202 and a Si/In-doped GaN based single crystal layer 212.

This structure can reduce dislocation density propagated from the substrate 202 and a low temperature buffer layer 204 to improve the reverse breakdown voltage Vbr of the light emitting device thereby improving the reliability thereof.

The structure of the nitride based 3-5 group compound semiconductor light emitting device according to the second embodiment of the present invention will be described in brief as follows.

The buffer layer 204 is grown on the substrate 202, and a first electrode contact layer 212 is made of n-type GaN (codoped with Si and In) and a second electrode contact layer 224 is grown to have an  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure. The first and second electrode contact layers 212 and 224 are provided with electrodes (not shown), respectively, in following process steps so that external voltage can be applied thereto via the electrodes.

The nitride based 3-5 group compound semiconductor

light emitting device of the present invention also has an active layer 220 of a single quantum well structure which is interposed between the first electrode contact layer 212 and the second electrode contact layer 224 to form a heterostructure. The active layer 220 includes a low mole  $In\text{-}doped\ In_xGa_{1-x}N$  layer 214, an  $In_xGa_{1-y}N$  well layer 216 and an  $In_xGa_{1-x}N$  barrier layer 218.

In addition, the nitride based 3-5 group compound semiconductor light emitting device also has an In-doped GaN layer 206 and an undoped GaN layer 208 between the buffer layer 204 and the first electrode contact layer 212. A ptype GaN layer 222 is also formed between the  $\rm In_x Ga_{1-x} N$  barrier layer 218 and the second electrode contact layer 224.

A fabrication method of the nitride based 3-5 group compound semiconductor light emitting device having the above-described structure is similar to that of the first embodiment, and therefore will not be described further.

The second embodiment of this structure can reduce dislocation density propagated from the substrate 202 and the buffer layer 204 to improve the reverse breakdown voltage Vbr of the light emitting device and therefore to improve the reliability thereof.

## Third Embodiment

5

10

15

20

25

30

35

FIG. 3 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a third embodiment of the present invention.

Referring to FIG. 3, this embodiment is generally similar to the first embodiment except that an In-doped GaN layer 318 is additionally interposed between a p-type GaN layer 320 and an  $\rm In_z Ga_{1-z} N$  barrier layer 314 to form a heterostructure.

The additional In-doped GaN layer 318 can restrain the in-diffusion of Mg atoms used as dopant in the p-type GaN layer 320 thereby improving characteristics. The In-doped GaN layer 318 is grown to a thickness of 100Å or less.

Hereinafter a fabrication method of the semiconductor light emitting device of the third embodiment will be described. A buffer layer 304 is grown on a substrate 302, a first electrode contact layer 308 is made of an n-type GaN (codoped with Si and In), and a second electrode contact layer 322 is formed of an  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure. Herein, the first and second electrode contact layers 308 and 322 are provided with electrodes (not shown), respectively, in following process steps so that external voltage can be applied thereto via the electrodes.

The nitride based 3-5 group compound semiconductor light emitting device of the present invention also has an active layer 316 of a single quantum well structure which is interposed between the first electrode contact layer 308 and the second electrode contact layer 322 to form a heterostructure. The active layer 316 includes a low mole  $In\text{-doped }In_xGa_{1-x}N$  layer 310, an  $In_xGa_{1-y}N$  well layer 312 and an  $In_xGa_{1-x}N$  barrier layer 314.

In addition, the nitride based 3-5 group compound semiconductor light emitting device also has an In-doped GaN layer 306 between the buffer layer 304 and the first electrode contact layer 308, and the p-type GaN layer 320 and the In-doped GaN layer 318 are placed between the  $\rm In_z Ga_{1-z} N$  barrier layer 314 and the second electrode contact layer 322.

As described above, the additional GaN layer 318 of this embodiment can restrain the in-diffusion of Mg atoms used as dopant in the p-type GaN layer 320. This embodiment can improve characteristics of the light emitting device.

## Fourth Embodiment

5

10

15

20

25

30

35

FIG. 4 illustrates a structure of a nitride based 3-5 group compound semiconductor light emitting device according to a fourth embodiment of the present invention.

Many parts of the fourth embodiment are the same as those of the third embodiment except that an In-doped GaN layer 406, an  $\rm In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer

408, an In-doped GaN layer 412 and an  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 414 are additionally provided. The  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 408, the Indoped GaN layer 412 and the  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 414 function to minimize crystal defects originated from the mismatch of lattice constant and thermal expansion coefficient from a substrate 402. Further, the  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 408 can reduce dislocation density propagated from the substrate 402 and a low temperature buffer layer 404 to improve the reverse breakdown voltage Vbr of the light emitting device.

5

10

15

20

25

30

35

Hereinafter a fabrication method of the semiconductor light emitting device of this embodiment will be described in detail with reference to FIG. 4.

The GaN-based semiconductor buffer layer 404 is grown on the sapphire substrate 402 at a low growth temperature. At the low growth temperature, the buffer layer 404 of the GaN-based semiconductor can be formed of an InGaN/GaN super lattice structure and a structure of  $In_xGa_{1-x}N/GaN$  and  $Al_xIn_yGa_{1-x},yN/In_xGa_{1-x}N/GaN$ .

The buffer layer 404 formed on the substrate 402 as above can efficiently restrict crystal defects induced from the mismatch of thermal expansion coefficient and lattice constant between the substrate 402 and a GaN based single crystal layer grown on the substrate 402, thereby producing a high quality GaN-based semiconductor.

Then, the In-doped GaN layer 406 is grown on the buffer layer 404 at a high growth temperature, and the  $\rm In_x Ga_{1-x}N/\rm In_y Ga_{1-y}N$  super lattice structure layer 408 is additionally formed on the In-doped GaN layer 408 in order to minimize crystal defects originated from the mismatch of lattice constant and thermal expansion coefficient from the substrate 402.

This structure can reduce dislocation density propagated from the substrate 402 and the low temperature buffer layer 404 to improve the reverse breakdown voltage Vbr

of the light emitting device thereby improving the reliability thereof.

Also, the In-doped GaN layer 412 and the  $\rm In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 414 are additionally formed on the  $\rm In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer 408 in order to further reduce crystal defects.

5

10

15

20

25

30

35

Then, a Si/In-codoped GaN layer 416 is grown on the  ${\rm In_xGa_{1-x}N/In_yGa_{1-y}N}$  super lattice structure layer 414. The Si/In-codoped GaN layer 416 is used as a first electrode contact layer.

After that, a single quantum well layer is formed in an active layer 424 for emitting a desired wavelength range of light. More particularly, a low mode In-doped  $\rm In_x Ga_{1-x} N$  layer 418 (0 < x  $\leq$  0.2) is first grown in the active layer 424 in order to improve the internal quantum efficiency of the active layer 424. A quantum well structure including an  $\rm In_y Ga_{1-y} N$  well layer 420 and an  $\rm In_z Ga_{1-z} N$  barrier layer 422 of different In content are grown on the low mole In-doped  $\rm In_x Ga_{1-x} N$  layer 418 to complete the active layer.

In the growing step, the active layer 424 of the single quantum well structure including the low mole In-doped  $In_xGa_{1-x}N$  layer 418, the  $In_yGa_{1-y}N$  well layer 420 (0 < y  $\leq$ 0.35) and the  $In_zGa_{1-z}N$  barrier layer 422(0 < z  $\leq$  0.2) are grown by feeding  $N_2$  and  $H_2+N_2$  gases and TMGa, TMIn and TMAl sources under  $NH_3$  atmosphere. The low mole  $In_xGa_{1-x}N$  layer 418 has a thickness of about 10 to 500Å, and its surface is uniformly grown in a spiral mode.

The InGaN well layer 420 for emitting light is grown to a thickness of 10 to 40Å and the InGaN barrier layer 422 is grown to a thickness of 50 to 500Å at a growth temperature of about 700 to  $800^{\circ}$ C. In addition, in order to realize high brightness light emitting device performance, it is necessary to maintain the uniform spiral mode from the surface of the low mole In-doped  $In_xGa_{1-x}N$  layer 418 to the  $In_zGa_{1-z}N$  barrier layer 422. If the above growth conditions are satisfied, a

practical high brightness light emitting device can be fabricated through the formation of an active layer having a single quantum well structure as well as that having a multiple quantum well structure.

After the growth of the light-emitting active layer, the In-doped GaN layer 426 and a Mg-doped p-type GaN GaN based single crystal layer 428 are grown. The p-type GaN layer 428 is grown to a thickness of about 500 to 5000 Å at a growth temperature of about 900 to  $1020^{\circ}$ C.

5

10

15

20

25

30

35

Then, after the p-type GaN layer 428 is grown, a second electrode contact layer 430 of an  $\rm In_x Ga_{1-x}N/\rm In_y Ga_{1-y}N$  super lattice structure (0 < y  $\leq$  0.2, and 0 < x  $\leq$ 0.2) is grown on the p-type GaN layer 428. Advantageously, the  $\rm In_x Ga_{1-x}N/\rm In_y Ga_{1-y}N$  super lattice structure can effectuate the current spreading of the second electrode contact layer 430, The electrode of the second electrode contact layer can be advantageously obtained from electrode metal the same as that of the first electrode contact layer 416.

According to the nitride based 3-5 group compound semiconductor light emitting device of this embodiment, the first electrode contact layer 416 is formed of an n-type electrode contact layer and the second electrode contact layer 430 is formed of a n-type electrode contact layer. Since high contact resistance is originated from the low Mg doping efficiency of a p-type GaN layer used as a second electrode contact layer in a conventional nitride based 3-5 group compound semiconductor light emitting device having first and second electrode contact layers in the form of n-type and p-type electrode contact layers, this embodiment can overcome the high contact resistance and remove a resultant current spreading layer.

Regarding the relation with the p-type GaN layer 428, it can be expressed that the first electrode contact layer 416, the p-type GaN layer 428 and the second electrode contact layer 430 have an n-p-n junction. The super lattice structure layers of the second electrode contact layer 430

alternate with each other at a thickness of 2 to 50Å, and the second electrode contact layer 430 has the maximum thickness under 200Å. Also, the growing step can be performed by feeding  $N_2$ ,  $N_2+H_2$  and  $NH_3$  gases and TMGa and TMIn sources in a growth temperature range from 700 to 850°C in order to grow a high brightness light emitting device having a hetero-structure excellent in internal quantum efficiency and operating voltage characteristics.

## Industrial Applicability

According to the nitride based 3-5 group compound semiconductor light emitting device and its fabrication method of the present invention as set forth above, it is possible to effectively restrain crystal defects originated from the mismatch of thermal expansion coefficient and lattice constant between a substrate of for example sapphire and a GaN GaN based single crystal layer grown thereon thereby to grow high quality GaN-based semiconductors. In particular, an  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure is placed underlying a Si/In-codoped GaN layer used as a first electrode contact layer thereby to further restrain crystal defects.

Also, a low mole In-doped  $\rm In_x Ga_{1-x} N$  is added in order to raise the internal quantum efficiency of an active layer thereby uniformly controlling the growth mode of a quantum well. Since the  $\rm In_x Ga_{1-x} N/In_y Ga_{1-y} N$  super lattice structure is used as a second electrode contact layer, operating voltage can be reduced. As a consequence, the present invention can advantageously reduce crystal defects of a nitride based 3-5 group compound semiconductor light emitting device as well as improve the crystallinity of a GaN GaN based single crystal layer, thereby improving the performance and reliability of the nitride based 3-5 group compound semiconductor light emitting device.

### Claims

5

10

20

1. A nitride based 3-5 group compound semiconductor light emitting device comprising:

- a substrate;

- a buffer layer formed above the substrate;

- a first In-doped GaN layer formed above the buffer layer;

- an  $In_xGa_1-_xN/In_yGa_1-_yN$  super lattice structure layer formed above the first In-doped GaN layer;

- a first electrode contact layer formed above the  ${\rm In_xGa_{1-x}N/In_yGa_{1-y}N}$  super lattice structure layer;

- an active layer formed above the first electrode contact layer and functioning to emit light;

- 15 a second In-doped GaN layer;

- a GaN layer formed above the second In-doped GaN layer; and

- a second electrode contact layer formed above the  ${\tt GaN}$  layer.

- 2. The device according to claim 1, wherein the second electrode contact layer is an n-type electrode contact layer.

- 3. The device according to claim 1, wherein the buffer layer comprises one selected from the group consisting of an InGaN/GaN super lattice structure, an  $In_xGa_1-xN/GaN$  structure and an  $Al_xIn_yGa_1-x,yN/In_xGa_1-xN/GaN$  structure.

- 4. The device according to claim 1, wherein the first electrode contact layer comprises a Si/In-codoped GaN layer.

- 5. The device according to claim 1, wherein the active layer comprises a single or multiple quantum well structure.

- 6. The device according to claim 1, wherein the active layer comprises a single or multiple quantum well structure,

including a low mole In-doped  ${\rm In}_x{\rm Ga}_{1-x}{\rm N}$  layer, an  ${\rm In}_y{\rm Ga}_{1-y}{\rm N}$  well layer and an  ${\rm In}_z{\rm Ga}_{1-z}{\rm N}$  barrier layer.

- 7. The device according to claim 6, wherein the low mole In-doped  $In_xGa_{1-x}N$  layer has an In content smaller than that of the  $In_zGa_{1-z}N$  barrier layer.

- 8. The device according to claim 6, wherein the low mole In-doped  $In_xGa_{1-x}N$  layer, the  $In_yGa_{1-y}N$  well layer and the  $In_zGa_{1-z}N$  barrier layer have an In content expressed as 0 < x < 0.05, 0 < y < 0.3 and 0 < z < 0.1, respectively.

- 9. The device according to claim 6, wherein the low mole In-doped  $\rm In_x Ga_{1-x}N$  layer has a surface configuration that is grown in a spiral mode.

- 10. The device according to claim 6, wherein the low mole In-doped  $In_xGa_{1-x}N$  layer has a surface configuration that is grown in a spiral mode, and wherein the spiral mode is extended to the surface of the  $In_zGa_{1-z}N$  barrier layer.

- 11. The device according to claim 1, wherein the second electrode contact layer comprises an  $\rm In_x Ga_{1-x}N/In_y Ga_{1-y}N$  super lattice structure.

- 12. The device according to claim 1, wherein the low mole In-doped  $\rm In_x Ga_{1-x} N$  layer and the  $\rm In_x Ga_{1-x} N/\rm In_y Ga_{1-y} N$  super lattice structure layer formed thereon are repeatedly layered in plurality.

- 13. A nitride based 3-5 group compound semiconductor light emitting device comprising:

- a substrate;

20

25

30

- a buffer layer formed above the substrate;

- a first In-doped GaN layer formed above the buffer layer;

a first electrode contact layer formed above the first In-doped GaN layer;

- an active layer formed above the first electrode contact layer and functioning to emit light;

- a GaN layer formed above the active layer; and

5

15

20

25

30

35

- a second electrode contact layer formed above the GaN layer.

- 14. The device according to claim 13, wherein the second electrode contact layer is an n-type electrode contact layer.

- 15. The device according to claim 13, further comprising a second In-doped GaN layer formed between the active layer and the p-type GaN layer.

- 16. The device according to claim 13, further comprising an  $In_xGa_{1-x}N/In_yGa_{1-y}N$  super lattice structure layer formed between the first In-doped GaN layer and the first electrode contact layer.

- 17. The device according to claim 13, further comprising an  ${\rm In_xGa_{1-x}N/In_yGa_{1-y}N}$  super lattice structure and an undoped GaN layer between the first In-doped GaN layer and the first electrode contact layer.

- 18. The device according to claim 13, wherein the buffer layer comprises one selected from the group consisting of an InGaN/GaN super lattice structure,  $In_xGa_1-_xN/GaN$  structure and an  $Al_xIn_yGa_1-_x,_yN/In_xGa_1-_xN/GaN$  structure.

- 19. The device according to claim 13, wherein the first electrode contact layer comprises a Si/In-codoped GaN layer.

- 20. The device according to claim 13, wherein the

active layer comprises a single or multiple quantum well structure.

21. The device according to claim 13, wherein the active layer comprises a single or multiple quantum well structure, including a low mole  $In-doped\ In_xGa_{1-x}N$  layer, an  $In_yGa_{1-y}N$  well layer and an  $In_zGa_{1-z}N$  barrier layer.

5

25

30

35

- 22. The device according to claim 21, wherein the low mole In-doped  $In_xGa_{1-x}N$  layer has an In content smaller than that of the  $In_zGa_{1-z}N$  barrier layer.

- 23. The device according to claim 21, wherein the low mole In-doped  $In_xGa_{1-x}N$  layer, the  $In_yGa_{1-y}N$  well layer and the  $In_zGa_{1-z}N$  barrier layer have an In content expressed as 0 < x < 0.05, 0 < y < 0.3 and 0 < z < 0.1, respectively.

- 24. The device according to claim 21, wherein the low mole In-doped  ${\rm In}_x{\rm Ga}_{1-x}{\rm N}$  layer has a surface configuration that 20 is grown in a spiral mode.

- 25. The device according to claim 21, wherein the low mole In-doped  $\rm In_x Ga_{1-x} N$  layer has a surface configuration that is grown in a spiral mode, and wherein the spiral mode is extended to the surface of the  $\rm In_z Ga_{1-z} N$  barrier layer.

- 26. The device according to claim 13, wherein the second electrode contact layer comprises an  $\rm In_x Ga_{1-x}N/In_y Ga_{1-y}N$  super lattice structure.

- 27. A fabrication method of a nitride based 3-5 group compound semiconductor light emitting device, comprising:

forming a buffer layer above a substrate;

forming a first In-doped GaN layer above the buffer layer;

forming a first electrode contact layer above the first

In-doped GaN layer;

5

10

15

25

35

forming an active layer for emitting light above the first electrode contact layer;

forming a GaN layer above the active layer; and forming a second electrode contact layer above the GaN layer.

- 28. The fabrication method according to claim 27, wherein the second electrode contact layer is an n-type electrode contact layer.

- 29. The fabrication method according to claim 27, wherein the first electrode contact layer comprises a Si/Incodoped GaN layer.

30. The fabrication method according to claim 27, wherein the second electrode contact layer comprises an  ${\rm In_xGa_{1-x}N/In_yGa_{1-y}N}$  super lattice structure layer.

- 31. The fabrication method according to claim 27, wherein the active layer comprises a single or multiple quantum well structure, including a low mole In-doped  ${\rm In_xGa_{1-xN}}$  layer, an  ${\rm In_yGa_{1-yN}}$  well layer and an  ${\rm In_zGa_{1-zN}}$  barrier layer.

- 32. The fabrication method according to claim 31, wherein the low mole In-doped  $\rm In_x Ga_{1-x} N$  layer is grown to have a surface configuration in a spiral mode.

- 33. The fabrication method according to claim 31, wherein the low mole  $In\text{-}doped\ In_xGa_{1-x}N$  layer is grown into a surface configuration of a spiral mode, wherein the spiral mode is extended to the surface of the  $In_zGa_{1-z}N$  barrier layer.

- 34. A nitride based 3-5 group compound semiconductor

light emitting device comprising:

a substrate;

5

20

25

- a buffer layer formed above the substrate;

- a first electrode contact layer formed above the GaN buffer layer;

- an active layer formed above the first electrode contact layer, and including a low mole  $In-doped\ In_xGa_{1-x}N$  layer, an  $In_yGa_{1-y}N$  well layer and an  $In_zGa_{1-z}N$  barrier layer;

- a GaN layer formed above the active layer; and

- 10 a second electrode contact layer formed above the GaN layer.

- 35. The device according to claim 34, wherein the second electrode contact layer is an n-type electrode contact layer.

- 36. The device according to claim 34, wherein the low mole In-doped  $\rm In_x Ga_{1-x}N$  layer has an In content smaller than that of the  $\rm In_z Ga_{1-z}N$  barrier layer.

- 37. The device according to claim 34, wherein the low mole In-doped  $\rm In_x Ga_{1-x}N$  layer, the  $\rm In_y Ga_{1-y}N$  well layer and the  $\rm In_z Ga_{1-z}N$  barrier layer have an In content expressed as 0 < x < 0.05, 0 < y < 0.3 and 0 < z < 0.1, respectively.

- 38. The device according to claim 34, wherein the low mole In-doped  $\rm In_xGa_{1-x}N$  layer has a surface configuration that is grown in a spiral mode.

- 39. The device according to claim 34, wherein the low mole  $In\text{-}doped\ In_xGa_{1-x}N$  layer has a surface configuration that is grown in a spiral mode, wherein the spiral mode is extended to the surface of the  $In_zGa_{1-z}N$  barrier layer.

FIG. 1

FIG. 2

| 7        |

|----------|

| 224      |

| 222      |

| 218 )    |

| 216 }220 |

| 214      |

| 212      |

| 210      |

| 208      |

| 206      |

| 204      |

| 202      |

|          |

FIG. 3

|                                                             | •       |

|-------------------------------------------------------------|---------|

| InxGa <sub>1-x</sub> N/InyGa <sub>1-y</sub> N Super Lattice | 322     |

| P-GaN                                                       | 320     |

| In-doped GaN                                                | 318     |

| ln <sub>z</sub> Ga <sub>1-z</sub> N Barrier                 | 314 )   |

| InyGa <sub>1-y</sub> N Well                                 | 312 316 |

| Low mole In <sub>x</sub> Ga <sub>1-x</sub> N                | 310     |

| Si-In co-doped GaN                                          | 308     |

| In-doped GaN                                                | 306     |

| Buffer Layer                                                | 304     |

| Substrate                                                   | 302     |

FIG. 4

| InxGa <sub>1-x</sub> N/InyGa <sub>1-y</sub> N Super Lattice                           | 430      |

|---------------------------------------------------------------------------------------|----------|

| P-GaN                                                                                 | 428      |

| In-doped GaN                                                                          | 426      |

| ln₂Ga₁-₂N Barrier                                                                     | 422 )    |

| InyGa <sub>1-y</sub> N Well                                                           | 420 \424 |

| Low mole In xGa 1-xN                                                                  | 418      |

| Si-In co-doped GaN                                                                    | 416      |

| In <sub>x</sub> Ga <sub>1-x</sub> N/In <sub>y</sub> Ga <sub>1-y</sub> N Super Lattice | 414      |

| In-doped GaN                                                                          | 412      |

| In <sub>x</sub> Ga <sub>1-x</sub> N/In <sub>y</sub> Ga <sub>1-y</sub> N Super Lattice | 408      |

| In-doped GaN                                                                          | 406      |

| Buffer Layer                                                                          | 404      |

| Substrate                                                                             | 402      |

International application No. PCT/KR2004/001480

## A. CLASSIFICATION OF SUBJECT MATTER

# IPC7 H01L 33/00

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L H01S

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Korean Patents and application for inventions, since 1973

Electronic data base consulted during the intertnational search (name of data base and, where practicable, search terms used)

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                          | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 6274399 B1 (LUMILEDS LIGHTING, U.S. LLS) 14 AUGUST 2001 see figure 3, column 3 line 53 - column4 line 19 | 1-39                  |

| A         | JP 10-214999 A (TOYODA GOSEI CO., LTD.) 11 AUGUST 1998 see figure 1                                         | 1-39                  |

| A         | JP 10-303458 A (TOYODA GOSEI CO., LTD.) 13 NOVEMBER 1998 see the whole documents                            | 1-39                  |

| A         | JP 10-4210 A (TOYODA GOSEI CO., LTD.) 06 JANUARY 1998 see the whole documents                               | 1-39                  |

| E, A      | WO 03/073484 A1 (NIKKO MATERIALS CO., LTD.) 04 SEPTEMBER 2003 see the whole documents                       | 1-39                  |

|           |                                                                                                             |                       |

Further documents are listed in the continuation of Box C.

X See patent family annex.

- Special categories of cited documents:

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

Date of mailing of the international search report

Date of the actual completion of the international search

23 SEPTEMBER 2004 (23.09.2004)

,

23 SEPTEMBER 2004 (23.09.2004)

Name and mailing address of the ISA/KR

Korean Intellectual Property Office 920 Dunsan-dong, Seo-gu, Daejeon 302-701, Republic of Korea

Facsimile No. 82-42-472-7140

Authorized officer

KIM, Dong Yup

Telephone No. 82-42-481-5749

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No. PCT/KR2004/001480

| Patent document cited in search report | Publication date | Patent family member(s) | Publication<br>date |

|----------------------------------------|------------------|-------------------------|---------------------|

| US 6274399 B1                          | 14.08.2001       | NONE                    |                     |

| JP 10-214999 A                         | 11.08.1998       | NONE                    |                     |

| JP 10-303458 A                         | 13.11.1998       | NONE                    |                     |

| JP 10-4210 A                           | 06.01.1998       | NONE                    |                     |

| WO 03/073484 A1                        | 04.09.2003       | NONE                    |                     |

|                                        |                  | <del></del>             |                     |