(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4858820号 (P4858820)

(45) 発行日 平成24年1月18日(2012.1.18)

(24) 登録日 平成23年11月11日(2011.11.11)

(51) Int. Cl. F. L

**GO2F** 1/1368 (2006.01) GO2F 1/1368 **GO2F** 1/1343 (2006.01) GO2F 1/1343

請求項の数 11 (全 12 頁)

(21) 出願番号 特願2006-75954 (P2006-75954) (22) 出願日 平成18年3月20日 (2006.3.20)

(65) 公開番号 特開2007-249100 (P2007-249100A) (43) 公開日 平成19年9月27日 (2007.9.27)

審査請求日 平成21年2月17日 (2007. 5. 27)

(73) 特許権者 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

|(74)代理人 100114672

弁理士 宮本 恵司

[(72) 発明者 川崎 拓

神奈川県川崎市中原区下沼部1753番地 NEC液晶テクノロジー株式会社内

(72)発明者 西田 真一

神奈川県川崎市中原区下沼部1753番地 NEC液晶テクノロジー株式会社内

(72) 発明者 今野 隆之

神奈川県川崎市中原区下沼部1753番地 NEC液晶テクノロジー株式会社内

最終頁に続く

(54) 【発明の名称】アクティブマトリクス基板及び液晶表示装置並びにその製造方法

### (57)【特許請求の範囲】

### 【請求項1】

複数の走査線及び複数の共通配線と信号線とが交差し、前記走査線と前記信号線とで囲まれる各々の画素にスイッチング素子を備えるアクティブマトリクス基板において、

第1の絶縁膜を介して前記信号線の下層、かつ、前記基板の法線方向から見て前記信号線の両側に、前記共通配線に接続される共通電位線が形成され、

第2の絶縁膜を介して前記信号線の上層、かつ、前記基板の法線方向から見て前記信号線と該信号線両側の前記共通電位線の少なくとも一部とに相重なるように、フローティング膜が形成されることを特徴とするアクティブマトリクス基板。

### 【請求項2】

基板側から、複数の走査線及び複数の共通配線と、第1の絶縁膜と、スイッチング素子と、前記走査線に交差し、前記スイッチング素子の一方の電極に接続される複数の信号線と、第2の絶縁膜と、を備え、

前記走査線と前記信号線とで囲まれる各々の画素に、前記スイッチング素子の他方の電極に接続される画素電極と前記共通配線に接続される共通電極とが交互に配設されてなるアクティブマトリクス基板において、

前記信号線の下層、かつ、前記基板の法線方向から見て前記信号線の両側に、前記共通配線に接続される共通電位線が形成され、

前記第2の絶縁膜の上層、かつ、前記基板の法線方向から見て前記信号線と該信号線両側の前記共通電位線の少なくとも一部とに相重なるように、フローティング膜が形成され

ることを特徴とするアクティブマトリクス基板。

### 【請求項3】

前記第2の絶縁膜上に、前記信号線に沿って、該信号線よりも広い幅で有機膜が形成され、前記フローティング膜は、前記有機膜に沿って、該有機膜よりも広い幅で形成されることを特徴とする請求項1又は2に記載のアクティブマトリクス基板。

### 【請求項4】

前記フローティング膜は、前記基板の法線方向から見て、幅方向の端部が前記信号線両側の前記共通電位線の両外側と略一致するように形成されることを特徴とする請求項1乃至3のいずれか一に記載のアクティブマトリクス基板。

### 【請求項5】

前記フローティング膜は、前記画素毎に分離して形成されることを特徴とする請求項 1 乃至 4 のいずれかーに記載のアクティブマトリクス基板。

### 【請求項6】

請求項1乃至5のいずれか一に記載のアクティブマトリクス基板と、該アクティブマトリクス基板に対向する基板との間に液晶が挟持され、前記画素電極と前記共通電極との間の電界により前記液晶が駆動される横電界方式の液晶表示装置。

### 【請求項7】

基板上に、複数の走査線と複数の共通配線とを形成すると共に、画素が形成される領域内に前記共通配線に接続される共通電極を形成する第1の工程と、

第1の絶縁膜を形成する第2の工程と、

スイッチング素子となる半導体層を形成する第3の工程と、

前記走査線に交差し、前記スイッチング素子の一方の電極に接続される複数の信号線を 形成すると共に、前記画素内に前記スイッチング素子の他方の電極に接続される画素電極 を形成する第4の工程と、

第2の絶縁膜を形成する第5の工程と、を少なくとも備えるアクティブマトリクス基板の製造方法において、

前記第4の工程の前に、前記基板の法線方向から見て前記信号線の両側に、前記共通配線に接続される共通電位線を形成し、

前記第5の工程の後に、前記基板の法線方向から見て前記信号線と該信号線両側の前記 共通電位線の少なくとも一部とに相重なるように、フローティング膜を形成する第6の工程を備えることを特徴とするアクティブマトリクス基板の製造方法。

# 【請求項8】

前記第5の工程と前記第6の工程との間に、前記第2の絶縁膜上に、前記信号線に沿って、該信号線よりも広い幅の有機膜を形成する工程を含み、

前記第6の工程では、前記有機膜に沿って、該有機膜よりも広い幅の前記フローティング膜を形成することを特徴とする請求項7記載のアクティブマトリクス基板の製造方法。

# 【請求項9】

前記第6の工程では、前記フローティング膜を、前記基板の法線方向から見て、幅方向の端部が前記信号線両側の前記共通電位線の両外側と略一致するように形成することを特徴とする請求項7又は8に記載のアクティブマトリクス基板の製造方法。

# 【請求項10】

前記第6の工程では、前記フローティング膜を、前記画素毎に分離して形成することを 特徴とする請求項7乃至9のいずれかーに記載のアクティブマトリクス基板の製造方法。

# 【請求項11】

請求項7乃至10のいずれか一に記載の製造方法を用いて前記アクティブマトリクス基板を製造し、前記アクティブマトリクス基板と対向基板との間に液晶を挟持する液晶表示装置の製造方法。

【発明の詳細な説明】

# 【技術分野】

[0001]

10

20

30

40

本発明は、アクティブマトリクス基板及び液晶表示装置並びにその製造方法に関し、特に、横電界方式の液晶表示装置を構成するアクティブマトリクス基板及び横電界方式の液晶表示装置並びにその製造方法に関する。

### 【背景技術】

# [0002]

近年、高解像度のディスプレイとして、薄膜トランジスタ(以下、TFT:Thin Film Transistorと略記する。)を画素のスイッチング素子として用いるアクティブマトリクス型液晶表示装置が広く用いられている。この液晶表示装置は、配向した液晶分子のダイレクタの方向をTFT基板に対して垂直な方向に回転させる縦電界方式(例えば、TN:Twisted Nematic方式)と、TFT基板に対して平行な方向に回転させる横電界方式(例えば、IPS:In Plane Switching方式)とに分類される。

### [0003]

横電界方式の液晶表示装置は、TFT基板上に互いに平行な画素電極と共通電極とを交互に形成し、これらの間に電圧を印加して基板面に平行な電界を形成することにより液晶のダイレクタの向きを変化させ、これによって透過光量を制御するものであり、この表示方式ではダイレクタが基板面内で回転するため、縦電界方式の場合のようにダイレクタの方向から見たときと基板法線方向から見込んだときとで透過光量と印加電圧の関係が大きく異なってしまうといった問題は発生せず、非常に広い視角から見て、良好な画像を得ることができる。

# [0004]

このように、各々の画素の内部では、上記画素電極と共通電極とで生じる電界によって液晶が駆動されるが、画素周縁部、特に信号線近傍では、信号線から漏洩する電界が液晶に作用するため、液晶の配向に乱れが生じ、これに伴って光漏れが生じるなどによって表示品位が低下してしまう。そこで、TFT基板に対向する対向基板の画素周縁部に対向する領域にブラックマトリクスを設けて遮光する方法が用いられている。

### [0005]

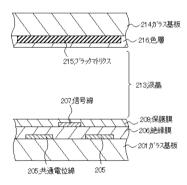

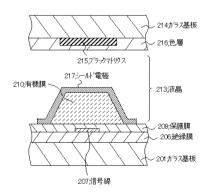

しかしながら、信号線から漏洩する電界の影響が大きい場合にブラックマトリクスの幅を広くすると、その分、表示に利用される領域(画素開口部)の面積が小さくなってしまうことから、信号線から漏洩する電界を抑制するための様々な構造が提案されている(例えば、下記特許文献 1~3)。この従来構造について、図6及び図7を参照して説明する。図6及び図7は、横電界方式の液晶表示装置の信号線近傍の構造を示す断面図である。

# [0006]

図6は下記特許文献1、2に開示されている構造(以下、第1の従来構造と呼ぶ。)を示しており、信号線207からの漏れ電界を抑制するために、信号線207の下層かつ両脇に共通配線に接続される共通電位線205を配置している。また、図7は下記特許文献3に開示されている構造(以下、第2の従来構造と呼ぶ。)を示しており、信号線207上に、共通配線に接続されるシールド電極217を配置している。

### [0007]

【特許文献1】特開2004-213031号公報(第5-9頁、第1図)

【特許文献2】特開2005-99855号公報(第4-6頁、第1図)

【特許文献3】特開2002-258321号公報(第11-19頁、第4図)

### 【発明の開示】

【発明が解決しようとする課題】

# [0008]

しかしながら、図6に示すように、信号線207の両脇に共通電位線205を配置した第1の従来構造では、信号線207の上層(液晶213側)にシールド構造がないため、信号線207からの漏れ電界が広がってしまう。そのため、共通電位線205の配線幅を大きくしなければならず、必然的にブラックマトリクス215の幅も広くなり、画素開口部が狭くなるという欠点があった。

### [0009]

10

20

30

40

また、図7に示すように、信号線207の上層を共通電極に接続されるシールド電極217でシールドした第2の従来構造では、シールド電極217を介して容量結合している信号線207と共通配線との間の寄生容量により共通電位遅延が生じてしまうと共に、シールド電極217と信号線207とがオーバーラップしているため、信号線207とシールド電極217との間にショートが発生した場合に、信号線207に十分に電位が供給できなくなり、線欠陥となって表示に重大な支障を引き起こすという欠点があった。

### [0010]

本発明は、上記問題点に鑑みてなされたものであって、その主たる目的は、開口率を向上させると共に、表示品位を向上させることができるアクティブマトリクス基板及び液晶表示装置並びにその製造方法を提供することにある。

【課題を解決するための手段】

### [0011]

上記目的を達成するため、本発明は、複数の走査線及び複数の共通配線と信号線とが交差し、前記走査線と前記信号線とで囲まれる各々の画素にスイッチング素子を備えるアクティブマトリクス基板において、第1の絶縁膜を介して前記信号線の下層、かつ、前記基板の法線方向から見て前記信号線の両側に、前記共通配線に接続される共通電位線が形成され、第2の絶縁膜を介して前記信号線の上層、かつ、前記基板の法線方向から見て前記信号線と該信号線両側の前記共通電位線の少なくとも一部とに相重なるように、フローティング膜が形成されるものである。

### [0012]

また、本発明は、基板側から、複数の走査線及び複数の共通配線と、第1の絶縁膜と、スイッチング素子と、前記走査線に交差し、前記スイッチング素子の一方の電極に接続される複数の信号線と、第2の絶縁膜と、を備え、前記走査線と前記信号線とで囲まれる各々の画素に、前記スイッチング素子の他方の電極に接続される画素電極と前記共通配線に接続される共通電極とが交互に配設されてなるアクティブマトリクス基板において、前記信号線の下層、かつ、前記基板の法線方向から見て前記信号線の両側に、前記共通配線に接続される共通電位線が形成され、前記第2の絶縁膜の上層、かつ、前記基板の法線方向から見て前記信号線と該信号線両側の前記共通電位線の少なくとも一部とに相重なるように、フローティング膜が形成されるものである。

### [0013]

本発明においては、前記第2の絶縁膜上に、前記信号線に沿って、該信号線よりも広い幅で有機膜が形成され、前記フローティング膜は、前記有機膜に沿って、該有機膜よりも広い幅で形成される構成とすることができる。

### [0014]

また、本発明においては、前記フローティング膜は、前記基板の法線方向から見て、幅方向の端部が前記信号線両側の前記共通電位線の両外側と略一致するように形成される構成とすることができる。

### [0015]

また、本発明においては、前記フローティング膜は、前記画素毎に分離して形成される 構成とすることができる。

# [0016]

また、本発明の横電界方式の液晶表示装置は、上記いずれか一に記載のアクティブマトリクス基板と、該アクティブマトリクス基板に対向する基板との間に液晶が挟持され、前記画素電極と前記共通電極との間の電界により前記液晶が駆動されるものである。

### [0017]

また、本発明の方法は、基板上に、複数の走査線と複数の共通配線とを形成すると共に、画素が形成される領域内に前記共通配線に接続される共通電極を形成する第1の工程と、第1の絶縁膜を形成する第2の工程と、スイッチング素子となる半導体層を形成する第3の工程と、前記走査線に交差し、前記スイッチング素子の一方の電極に接続される複数の信号線を形成すると共に、前記画素内に前記スイッチング素子の他方の電極に接続され

10

20

30

40

る画素電極を形成する第4の工程と、第2の絶縁膜を形成する第5の工程と、を少なくとも備えるアクティブマトリクス基板の製造方法において、前記第4の工程の前に、前記基板の法線方向から見て前記信号線の両側に、前記共通配線に接続される共通電位線を形成し、前記第5の工程の後に、前記基板の法線方向から見て前記信号線と該信号線両側の前記共通電位線の少なくとも一部とに相重なるように、フローティング膜を形成する第6の工程を備えるものである。

### [0018]

本発明においては、前記第5の工程と前記第6の工程との間に、前記第2の絶縁膜上に、前記信号線に沿って、該信号線よりも広い幅の有機膜を形成する工程を含み、前記第6の工程では、前記有機膜に沿って、該有機膜よりも広い幅の前記フローティング膜を形成する構成とすることができる。

[0019]

また、本発明においては、前記第6の工程では、前記フローティング膜を、前記基板の 法線方向から見て、幅方向の端部が前記信号線両側の前記共通電位線の両外側と略一致す るように形成する構成とすることができる。

[0020]

また、本発明においては、前記第6の工程では、前記フローティング膜を、前記画素毎に分離して形成する構成とすることもできる。

[0021]

また、本発明の液晶表示装置の製造方法は、上記いずれかーに記載の製造方法を用いて アクティブマトリクス基板を製造し、前記アクティブマトリクス基板と対向基板との間に 液晶を挟持するものである。

[0022]

このように、本発明は上記構成により、信号線から漏洩する電界を抑制することができるため、共通電位線及び対向基板のブラックマトリクスの幅を狭くすることができ、これにより、画素開口部を広げて開口率を向上させることができる。

[0023]

また、フローティング膜はいずれの配線にも接続されておらず、フローティング状態になっているため、フローティング膜を介して容量結合している信号線と共通配線との間の寄生容量を小さくすることができ、また、信号線とフローティング膜とが短絡しても信号線に十分に電位を供給することができ、かつ、フローティング膜を画素毎に分離することによって短絡の影響を画素単位で抑えることができるため、表示品位の向上を図ることができる。

[0024]

更に、信号線上の第2の絶縁膜を厚くしたり、第2の絶縁膜上に信号線に沿って信号線よりも幅の広い凸状の有機膜を形成することにより、信号線と共通配線との間の寄生容量を更に小さくすることができ、また、フローティング膜を両側の共通電位線を覆うように形成し、フローティング膜の電位を共通電位に近づけることにより、漏れ電界のシールド効果を高めることができるため、表示品位を向上させることができる。

【発明の効果】

[0025]

本発明のアクティブマトリクス基板及び液晶表示装置並びにその製造方法によれば、下記記載の効果を奏する。

[0026]

本発明の第1の効果は、各画素の開口率を向上させることができるということである。

[0027]

その理由は、絶縁膜を介して信号線の下層、かつ、基板の法線方向から見て信号線の両側に共通配線に接続される共通電位線を配置し、保護膜を介して信号線の上層、かつ、基板の法線方向から見て信号線と共通電位線の少なくとも一部とに相重なるようにフローティング膜を配置することにより、信号線近傍の電界漏れを確実に抑制することができるた

10

20

30

40

め、共通電位線及び遮光用ブラックマトリクスの幅を縮小することができるからである。

### [0028]

また、本発明の第2の効果は、表示品位を向上させることができるということである。

### [0029]

その理由は、信号線をシールドするフローティング膜は共通電位等に接続されておらず、信号線と共通電位線との結合容量を小さくすることができるため、共通電位遅延を抑制することができるからである。また、フローティング膜はいずれの配線にも接続されておらず、かつ、画素毎に分離しているため、フローティング膜と信号線とが短絡するような欠陥が生じた場合でも、線欠陥にすることなく、単一画素のみの点欠陥に抑えることができるからである。また、信号線上の保護膜を厚くしたり、保護膜上に信号線に沿って信号線よりも幅の広い凸状の有機膜を形成することにより、信号線とフローティング膜との結合容量を小さくして共通電位遅延を抑制することができるからである。更に、フローティング膜を共通電位線と相重なるように形成することにより、フローティング膜の電位を共通電位に近づけることができ、漏れ電界のシールド効果を高めることができるからである

### 【発明を実施するための最良の形態】

### [0030]

本発明は、その好ましい一実施の形態において、信号線と走査線及び共通配線とが交差して延在し、各々の画素内において、信号線に接続される画素電極と共通配線に接続される共通電極とが信号線に沿って交互に櫛歯状に配置される横電界方式のアクティブマトリクス型液晶表示装置において、絶縁膜を介して信号線の下層、かつ、基板の法線方向から見て信号線の両側に共通配線に接続される共通電位線を配置すると共に、保護膜を介して信号線の上層、かつ、基板の法線方向から見て信号線と両側の共通電位線の少なくとも一部とに相重なるようにフローティング膜を配置する。また、信号線上の保護膜を厚くしたり、保護膜上に有機膜を信号線に沿って凸状にパターニングして、その上にフローティング膜を形成したり、フローティング膜を両側の共通電位線にオーバーラップするように形成する。

### [0031]

これにより、信号線のシールド効果を高めて共通電位線の配線幅やブラックマトリクスの幅を縮小して開口率を向上させることができる。また、フローティング膜を介して容量結合している信号線と共通電位の間の寄生容量を充分小さくして共通電位の遅延を短縮してクロストークの発生を抑制すると共に、信号線とフローティング膜とが短絡した場合の欠陥を最小限に抑えて表示品位を向上させることができる。

### 【実施例】

# [0032]

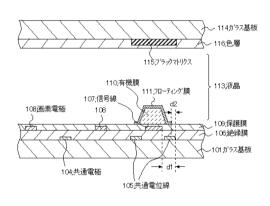

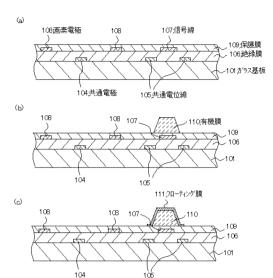

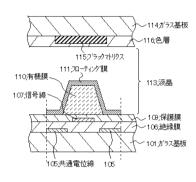

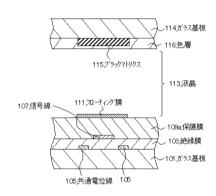

上記した本発明の実施の形態についてさらに詳細に説明すべく、本発明の一実施例に係るアクティブマトリクス基板及び液晶表示装置並びにその製造方法について、図1乃至図5を参照して説明する。図1は、本実施例の液晶表示装置のアクティブマトリクス基板の平面構造を示す図であり、図2は、図1のX-X線における液晶表示装置の断面構造を示す図である。また、図3は、本実施例のアクティブマトリクス基板の製造方法を示す工程断面図であり、図4及び図5は、本実施例の液晶表示装置の断面構造の他の例を示す図である。

# [0033]

本実施例のアクティブマトリクス型液晶表示装置は、TFTなどのスイッチング素子が 形成される一方の基板(ここではTFT基板と呼ぶ。)と、他方の基板(ここでは対向基 板と呼ぶ。)と、その間に狭持される液晶とから構成される。なお、以下では、本実施例 の液晶表示装置を横電界方式とし、TFTの構造を逆スタガ型として説明する。

### [0034]

また、本実施例のTFT基板は、図1及び図2に示すように、ガラス基板101上に、 走査線(ゲート線)102と信号線(データ線)107とが所定の角度で交差するように 10

20

30

40

10

20

30

40

50

配置され、各々の走査線102と略平行に共通配線103が配置されている。また、走査線102と信号線107とで囲まれる各々の画素にTFT112が配置され、ソース/ドレイン電極の一方が信号線107に接続され、ソース/ドレイン電極の他方が、画素内で信号線107に沿って延びる画素電極108に接続されている。また、共通配線103には、画素内で信号線107に沿って延びる共通電極104が接続され、画素電極108と共通電極104とが交互に配置されて櫛歯電極が形成されている。そして、各画素において、TFT112を介して信号線107から供給される画素電位を持つ画素電極108と共通電位を持つ共通電極104との間に働く横電界によって液晶113が駆動される。

[0035]

更に、本実施例のTFT基板は、絶縁膜106を介して信号線107の下層、かつ、基板の法線方向から見て信号線107の両側に、共通配線103に接続される共通電位線105が配置されると共に、保護膜109及び有機膜110を介して信号線107の上層、かつ、基板の法線方向から見て信号線107と両側の共通電位線105の少なくとも一部とに相重なるようにフローティング膜111が配置され、このフローティング膜111は画素毎に分離して形成されている。

[0036]

また、図2に示すように、対向基板には、ガラス基板114上に、RGB各色のカラー表示を行うための色層116と、不要な光を遮断するためのブラックマトリクス115などが形成されている。このブラックマトリクス115、信号線107の延在方向に関しては、基板の法線方向から見て、信号線107及びその両側の共通電位線105を覆う幅で形成されている。

[0037]

また、TFT基板及び対向基板の内側には、配向膜(図示せず)が形成されており、これをラビング処理することにより、液晶113を走査線101の長手方向に直交する向きに配向させている。また、TFT基板及び対向基板の外側には、偏光板(図示せず)がクロスニコルとなるように配置され、片側の偏光軸が液晶113の初期配向方位と一致するように構成されている。

[0038]

なお、図1及び図2は例示であり、信号線107と共通電位線105とフローティング膜111との関係が満たされる限りにおいて、他の部材の構成、配置、形状等は適宜変更することができる。例えば、図1では、画素電極108と共通電極104とが画素内で屈曲している構造を示しているが、画素電極108と共通電極104とを直線状としてもよい。また、図1では、1本の共通電極104と2本の画素電極108とで櫛歯電極を構成しているが、画素電極108及び共通電極104の本数を増減させてもよい。また、図1では、フローティング膜111が画素毎に分離して形成されている構成を示したが、信号線107とフローティング膜111との短絡が起こりにくい構造(例えば、保護膜109が厚い場合など)では、例えば、複数画素毎に分離したり、連続して形成してもよい。

[0039]

次に、上記構成のTFT基板の製造方法について、図3の工程断面図を参照して説明する。

[0040]

まず、図3(a)に示すように、ガラスやプラスチックなどの透明な絶縁基板(ここではガラス基板101とする。)上に、Cr等の金属を堆積し、公知のフォトリソグラフィ技術及びエッチング技術を用いて走査線102、共通配線103、画素内の共通電極104を形成する。その際、絶縁膜106を挟んで上層に形成される信号線107の両側となる位置に、共通配線103に接続される共通電位線105を形成する。なお、この共通電位線105は、共通配線103に上頭配線103に接続してもよい。

[0041]

ここで、第1の従来構造(図6の構造)では、信号線207からの漏れ電界が広がるた

めに共通電位線 2 0 5 の配線幅を大きくしなければならず、必然的にブラックマトリクス 2 1 5 の幅が広くなり、開口率が低下するという問題があったが、本実施例では、信号線 1 0 7 の上層にフローティング膜 1 1 1 を形成するため、共通電位線 1 0 5 の配線幅を小さくしても信号線 1 0 7 からの漏れ電界を抑制することができ、必然的にブラックマトリクス 1 0 5 の幅も狭くすることができるため、開口率を高めることができる。この共通電位線 1 0 5 の配線幅は、液晶表示装置に求められる性能、絶縁膜 1 0 6 の膜厚、信号線 1 0 7 の幅などに応じて適宜変更可能であるが、本実施例では、図 2 に示すように信号線 1 0 7 のエッジから共通電位線 1 0 5 のエッジまでの距離(d 1)が 8  $\mu$ m程度になるようにしている。

### [0042]

次に、SiOx、SiNx等をプラズマCVD法などにより堆積して絶縁膜106を形成し、a-Si等の半導体層を堆積し島状にパターニングした後、Cr等の金属を堆積、パターニングして、信号線107と画素電極108を形成する。その後、SiNx膜等をプラズマCVD法などにより堆積し、TFT112を保護する保護膜109を形成する。【0043】

次に、図3(b)に示すように、保護膜109の上にフローティング膜111を形成するための有機膜110を形成する。例えば、感光性のアクリル樹脂等をスピン塗布法により塗布し、アルカリ現像液を用いて現像し、所定の温度でキュアすることにより所望の形状の有機膜110を形成することができる。その際、信号線107とフローティング膜111とが近接すると結合容量が大きくなることから、本実施例では、有機膜110が信号線107とフローティング膜111とが確実に離間するようにしている。

### [0044]

次に、図3(c)に示すように、スパッタ法等を用いて、ITO(Indium Thin Oxide)等を堆積、パターニングして、フローティング膜111を形成する。その際、フローティング膜111と共通電位線105との間隔が大きくなるとフローティング膜111の電位を共通電位に近づけることができないことから、本実施例では、フローティング膜111を有機膜110の上面から側面を通って保護膜109の上面に達するように形成すると共に、基板の法線方向から見てフローティング膜111が両側の共通電位線105の少なくとも一部を覆うようにし、これによりフローティング膜111の電位を共通電位に近づけて、漏れ電界のシールド効果を高めている。

# [0045]

このフローティング膜111の幅は、液晶表示装置に求められる性能、信号線107の幅などに応じて適宜変更可能であるが、本実施例では、図2に示すように、フローティング膜111のエッジから共通電位線105のエッジまでの張り出し距離(d2)を4μm程度にしている。なお、本実施例ではフローティング膜111で光が反射されないようにするためにITOで形成しているが、フローティング膜111がブラックマトリクス115の幅よりも狭ければ金属材料で形成してもよい。また、上記説明では、画素電極108を信号線107と同層に形成したが、例えば、フローティング膜111を形成する際に、画素電極108を形成し、TFT112上に設けたコンタクトホールを介して、ソース/ドレイン電極の一方に接続する構成としてもよい。

### [0046]

上記工程で製造されたTFT基板では、フローティング膜111は有機膜110の外側で共通電位線105と容量結合を持ちつつ、信号線107からの漏れ電界をシールドする。この際、有機膜110の外側部分ではフローティング膜111と共通電位線105とは大きい容量で結合されるが、有機膜110の部分で結合されている信号線107とフローティング膜111間の容量は小さくなるので、結果として信号線107と共通電位線105の間の容量は低く抑えられている。

### [0047]

また、フローティング膜111の電位は、信号線107および共通電位線105との間

10

20

30

40

の容量結合により決定されるので、フローティング膜111と共通電位線105との間の容量がフローティング膜111と信号線107との間の容量に比べて大きくなることにより、フローティング膜111の電位は共通電位に近づくため、フローティング膜111による信号線107のシールド効果はより完全になる。

### [0048]

そして、漏れ電界がシールドされることによって信号線107近傍の漏れ電界による液晶の配向の乱れは軽減し、それに起因した信号線107近傍の光漏れが解消する。そのため、共通電位線105及び遮光のために設けているブラックマトリクス115の幅を縮小して開口率を拡大させることができる。

### [0049]

なお、図 2 では、フローティング膜 1 1 1 のエッジから共通電位線 1 0 5 のエッジまでの張り出し距離(d 2 ) を 4  $\mu$  m程度にしたが、本発明では、共通電位線 1 0 5 との容量結合を介してフローティング膜 1 1 1 に電位を与え、信号線 1 0 7 をシールドしていることから、図 4 に示すように、フローティング膜 1 1 1 と共通電位線 1 0 5 とを完全にオーバーラップさせ、フローティング膜 1 1 1 の電位を共通電位に近づけることにより、漏れ電界のシールド効果を高めることができる。

### [0050]

また、図2では、保護膜109の上層に有機膜110を形成して、信号線107とフローティング膜111との間に間隔を設けたが、図5に示すように、有機膜110を用いずに保護膜109を厚くすることによって、信号線107とフローティング膜1111との容量を減らし、信号遅延を避けることもできる。この場合、有機膜110を使用しないため、信号線107近傍の平坦性を良好にすることができ、ラビングにより容易に液晶配向が保たれること、また、有機膜110の形成が必要ないため、工程数を削減できることなどが利点として挙げられる。

### [0051]

なお、上記実施例では、本発明を横電界方式の液晶表示装置に適用する場合について述べたが、本発明は上記実施例に限定されるものではなく、縦電界方式の液晶表示装置に対しても適用することができる。また、上記実施例では、本発明を逆スタガ型のTFT基板に適用する場合について述べたが、正スタガ型のTFT基板に対しても適用することができる。

【産業上の利用可能性】

# [0052]

本発明は、任意の液晶表示装置及びその製造方法に適用することができる。

【図面の簡単な説明】

[0053]

- 【図1】本発明の一実施例に係るTFT基板の構造を示す平面図である。

- 【図2】本発明の一実施例に係る液晶表示装置の構造を示す断面図である。

- 【図3】本発明の一実施例に係るTFT基板の製造方法を示す工程断面図である。

- 【図4】本発明の一実施例に係る液晶表示装置の他の構造を示す断面図である。

- 【図5】本発明の一実施例に係る液晶表示装置の他の構造を示す断面図である。

- 【図6】従来の液晶表示装置の構造(第1の従来構造)を示す断面図である。

- 【図7】従来の液晶表示装置の構造(第2の従来構造)を示す断面図である。

【符号の説明】

[0054]

- 101、201 ガラス基板

- 102、202 走査線

- 103、203 共通配線

- 104、204 共通電極

- 105、205 共通電位線

- 106、206 絶縁膜

20

10

30

40

107、207 信号線

108、208 画素電極

109、109a、209 保護膜

110、210 有機膜

111 フローティング膜

1 1 2 T F T

113、213 液晶

1 1 4 、 2 1 4 ガラス基板

115、215 ブラックマトリクス

116、216 色層

2 1 7 シールド電極

# 【図1】

# 107.信号線 108.再通配線 104.共通電極 105.共通電位線 105.共通電位線 111.70-元ング膜 111.70-元ング膜 112.TFT

# 【図2】

# 【図3】

# 【図4】

【図5】

# 【図6】

# 【図7】

# フロントページの続き

# 審査官 右田 昌士

(56)参考文献 特開2005-195927(JP,A)

特開平10-020338(JP,A)

特開平04-362923(JP,A)

特開2002-258321(JP,A)

特開2004-213031(JP,A)

特開2005-099855(JP,A)

特開平10-010570(JP,A)

米国特許第06784965(US,B1)

米国特許第07061566(US,B1)

(58)調査した分野(Int.CI., DB名)

G02F 1/1368

G02F 1/1343