심사관 :

이현홍

# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

#### GO1S 5/14 (2006.01)

(21) 출원번호 10-2008-0021605

(22) 출원일자 **2008년03월07일** 심사청구일자 **2009년09월11일**

(65) 공개번호 **10-2009-0096190**

(43) 공개일자 2009년09월10일

(56) 선행기술조사문헌

US5621416 A

US6393046 B1

US20040202235 A1

WO0142973 A1

전체 청구항 수 : 총 15 항

(45) 공고일자 2011년10월17일

(11) 등록번호 10-1073408

(24) 등록일자 2011년10월07일

(73) 특허권자

## 주식회사 코아로직

서울 강남구 삼성동 154-10 융전빌딩

(72) 발명자

#### 부성춘

서울 강동구 천호4동 290-34 건풍 월드 빌라 402 호

(74) 대리인

양문옥

# (54) 위성 신호 추적기의 상관 장치 및 그 방법

#### (57) 요 약

본 발명은, 위성 신호 추적기의 상관 장치 및 그 방법에 관한 것으로, 본 발명에 따른 위성 신호 추적기의 상관 장치는, 위성 식별 코드 신호를 발생하는 코드 발생기; 상기 위성 식별 코드 신호를 지연시켜 복수의 빠른 (Early) 코드 신호와 복수의 느린(Late) 코드 신호를 생성하는 지연기; 상기 지연기에서 생성된 복수의 빠른 코드 신호와 복수의 느린 코드 신호 중 특정 칩 간격으로 지연된 코드 신호와 다른 칩 간격으로 지연된 코드 신호를 번갈아가며 다중화하는 다중화기; 반송파가 제거된 입력 신호와 상기 다중화기에서 다중화되어 출력되는 코드 신호를 혼합하는 혼합기; 및 상기 혼합기에서 출력되는 신호를 적분하는 적분기;를 포함하는 것을 특징으로한다.

# 대 표 도 - 도1

## 특허청구의 범위

#### 청구항 1

위성 신호를 추적하기 위한 상관 장치에 있어서,

PN(Pseudo Noise) 코드의 주파수와 동일한 제 1 기준 주파수 및 상기 PN 코드의 주파수의 N(N은 2 이상의 정수)배에 해당하는 제 2 기준 주파수를 생성하는 수치 제어 발진기;

상기 제 1 기준 주파수에 따라 상기 PN 코드를 생성하는 코드 생성기;

상기 제 2 기준 주파수에 따라 상기 코드 생성기로부터 수신된 상기 PN 코드에 대응하는 Prompt 신호, 상기 Prompt 신호보다 빠른 칩 간격을 갖는 복수의 Early 신호들 및 상기 Prompt 신호보다 느린 칩 간격을 갖는 복수의 Late 신호들을 생성하는 지연기;

상기 복수의 Early 신호들을 정해진 주기마다 하나씩 번갈아 가면서 출력하고, 상기 복수의 Late 신호들을 상기 정해진 주기마다 하나씩 번갈아가면서 출력하는 코드 다중화부;

상기 위성 신호에 상기 코드 다중화부로부터 출력되는 Early 신호와 Late 신호를 각각 믹싱하는 코드 혼합기; 및

상기 코드 혼합기에서 출력되는 신호를 적분하여 상관 신호를 획득하는 적분기를 포함하는 상관 장치.

#### 청구항 2

삭제

# 청구항 3

제 1 항에 있어서,

상기 복수의 Early 신호들은 1/2 Early 신호와 1/4 Early 신호인 것을 특징으로 하는 상관 장치.

# 청구항 4

제 1항에 있어서,

상기 복수의 Late 신호들은 1/2 Late 신호와 1/4 Late 신호인 것을 특징으로 하는 상관 장치.

#### 청구항 5

제 1 항에 있어서,

상기 복수의 Early 신호들의 칩 간격과 상기 복수의 Late 신호들의 칩 간격은 동일한 것을 특징으로 하는 상관 장치.

#### 청구항 6

제 1 항에 있어서,

상기 코드 다중화부에서 출력되는 Early 신호와 Late 신호를 선택하는 제어 신호를 상기 코드 다중화부로 출력 하는 모드 설정부를 더 포함하고,

상기 코드 다중화부는 상기 복수의 Early 신호들 및 상기 복수의 Late 신호들 중 상기 제어 신호에 대응하는 Early 신호 및 Late 신호를 출력하는 것을 특징으로 하는 상관 장치.

#### 청구항 7

제 6 항에 있어서.

상기 복수의 Early 신호들은 1/2 Early 신호와 1/4 Early 신호이고, 상기 복수의 Late 신호들은 1/2 Late 신호 와 1/4 Late 신호이며,

상기 모드 설정부는 상기 코드 다중화부가 상기 1/2 Early 신호 및 상기 1/2 Late 신호를 출력하도록 제어하는

것을 특징으로 하는 상관 장치.

#### 청구항 8

제 6 항에 있어서,

상기 복수의 Early 신호들은 1/2 Early 신호와 1/4 Early 신호이고, 상기 복수의 Late 신호들은 1/2 Late 신호 와 1/4 Late 신호이며,

상기 모드 설정부는 상기 코드 다중화부가 상기 1/4 Early 신호 및 상기 1/4 Late 신호를 출력하도록 제어하는 것을 특징으로 하는 상관 장치.

#### 청구항 9

제 6 항에 있어서,

상기 복수의 Early 신호들은 1/2 Early 신호와 1/4 Early 신호이고, 상기 복수의 Late 신호들은 1/2 Late 신호 와 1/4 Late 신호이며,

상기 모드 설정부는 상기 코드 다중화부가 상기 1/2 Early 신호 및 상기 1/2 Late 신호 또는 상기 1/4 Early 신호 및 상기 1/4 Late 신호를 번갈아 출력하도록 제어하는 것을 특징으로 하는 상관 장치.

#### 청구항 10

삭제

## 청구항 11

제 1 항에 있어서,

상기 N은 4인 것을 특징으로 하는 상관 장치.

#### 청구항 12

삭제

# 청구항 13

제 1 항에 있어서,

상기 정해진 주기는 상기 적분기의 적분 시간인 것을 특징으로 하는 상관 장치.

#### 청구항 14

위성 신호를 추적하기 위한 방법에 있어서,

위성 신호를 획득하는 단계;

위성 식별 코드인 PN 코드의 주파수와 동일한 제 1 기준 주파수 및 상기 PN코드의 주파수의  $N(N^2)$  이상의 정수) 배에 해당하는 제 2 기준 주파수를 생성하는 단계;

상기 제 1 기준 주파수에 따라 상기 PN 코드를 생성하는 단계;

상기 제 2 기준 주파수에 따라 상기 PN 코드에 대응하는 Prompt 신호, 상기 Prompt 신호보다 빠른 칩 간격을 갖는 복수의 Early 신호들 및 상기 Prompt 신호보다 느린 칩 간격을 갖는 복수의 Late 신호들을 생성하는 단계;

상기 복수의 Early 신호들을 정해진 주기마다 하나씩 번갈아 가면서 출력하고 상기 복수의 Late 신호들을 상기 정해진 주기마다 하나씩 번갈아가면서 출력하는 출력 단계; 및

상기 Prompt 신호, 상기 출력 단계에서 출력되는 Early 신호 및 Late 신호를 이용하여 상기 위성 신호로부터 상기 위성 신호를 추적하기 위한 상관 신호를 획득하는 단계를 포함하는 방법.

## 청구항 15

삭제

#### 청구항 16

제 14 항에 있어서,

상기 출력 단계에서 출력되는 Early 신호 및 Late 신호에 대한 상기 Prompt 신호로부터의 칩 간격은 동일한 것을 특징으로 하는 방법.

#### 청구항 17

제 14 항에 있어서,

상기 복수의 Early 신호와 상기 복수의 Late 신호는 상기 Prompt 신호를 기준으로 순차적으로 쉬프트시켜 생성되는 것을 특징으로 하는 방법.

#### 청구항 18

삭제

#### 청구항 19

제 14 항에 있어서,

상기 상관 신호를 획득하는 단계는

상기 위성 신호로부터 반송파를 제거하는 단계;

상기 반송파가 제거된 신호에 상기 Prompt 신호, 상기 출력 단계에서 출력되는 Early 신호 및 Late 신호를 각각 믹싱하는 단계; 및

상기 믹싱된 신호를 적분하여 상기 상관 신호를 획득하는 단계를 포함하는 것을 특징으로 하는 방법.

#### 청구항 20

GPS(Global Positioning System) 위성로부터 수신되는 신호로부터 위성 신호를 생성하는 RF부;

상기 위성 신호를 추적하기 위한 위성 기반 측정 결과를 생성하는 상관기; 및

상기 위성 기반 측정 결과를 기초로 위치 해를 결정하는 위성 프로세서를 포함하되,

상기 상관기는

PN(Pseudo Noise) 코드의 주파수와 동일한 제 1 기준 주파수 및 상기 PN 코드의 주파수의 N(N은 2 이상의 정수)배에 해당하는 제 2 기준 주파수를 생성하는 수치 제어 발진기;

상기 제 1 기준 주파수에 따라 상기 PN 코드를 생성하는 코드 생성기;

상기 제 2 기준 주파수에 따라 상기 코드 생성기로부터 수신된 상기 PN 코드에 대응하는 Prompt 신호, 상기 Prompt 신호보다 빠른 칩 간격을 갖는 복수의 Early 신호들 및 상기 Prompt 신호보다 느린 칩 간격을 갖는 복수의 Late 신호들을 생성하는 지연기;

상기 복수의 Early 신호들을 정해진 주기마다 하나씩 번갈아 가면서 출력하고, 상기 복수의 Late 신호들을 상기 정해진 주기마다 하나씩 번갈아가면서 출력하는 코드 다중화부;

상기 위성 신호에 상기 코드 다중화부로부터 출력되는 Early 신호와 Late 신호를 각각 믹싱하는 코드 혼합기; 및

상기 코드 혼합기에서 출력되는 신호를 적분하여 상관 신호를 획득하는 적분기를 포함하는 GPS 수신기.

## 명세서

# 발명의 상세한 설명

# 기 술 분 야

[0001] 본 발명은 위성 신호 추적기에 관한 것으로, 보다 구체적으로 위성 신호 추적기의 상관 장치 및 그 방법에 관한 것이다.

# 배경기술

- [0002] 위성 항법 시스템(GNSS:Global Navigation Satellite System)은 우주 상공에 띄운 인공 위성의 네트워크를 이용, 지상에 있는 목표물의 위치를 정확히 추적해내는 시스템으로, 미국 국방부에서 운영하는 통상적인 GPS(Global Positioning System) 및 유럽 연합을 위주로 하여 개발중인 갈릴레오 위치 결정 시스템(Galileo Positioning System), 그리고 러시아에서 운영하는 GLONASS(GLObal Navigation Satellite System) 등을 지칭한다. 이러한 위성 항법 시스템은 항공기, 선박의 위치확인 및 텔레매틱스 등 정보통신 분야에 광범위하게 사용되고 있다.

- [0003] 대표적으로, GPS(Global Position System)는 우주 궤도를 돌고 있는 위성을 이용해 위치 정보를 제공하는 위치 측정 시스템으로 초기에는 군사용 목적으로 구축되었지만 2000년 이후 고의 잡음인 SA(Selective Availabilit v)를 제거하면서 다양한 분야에서 널리 사용되고 있다.

- [0004] GPS 위성은 6 개의 궤도에 4 개의 위성이 할당되어 있고, CDMA 방식으로 같은 주파수 대역을 이용해 서로 다른 코드를 사용하여 대역을 공유하고 있다. 즉, GPS는 직접 대역 확산(Direct Sequence Spread Spectrum) 방식을 사용한다. 이러한 변조 방식의 특징은 원래 신호의 주파수 대역보다 훨씬 넓은 신호를 확산시킨다는 점이다. 따라서 이러한 신호를 수신하는 GPS 수신기에서는 정확한 의사 잡음(Pseudo Noise) 코드와 동기를 일치시켜야만 원하는 정보의 분리가 가능하게 된다.

- [0005] 이에 따라 GPS 수신기는 RF 단을 통과한 신호를 기저대역으로 낮춘 후 역확산하여 데이터를 복원하는 상관기를 구비한다. GPS 수신기의 RF 단에 수신된 위성 신호는 상기 RF 단에서 중간 주파수(IF)로 변환된 후 2 비트 양자화되어 상기 상관기로 입력되고, 상기 상관기는 이를 기저대역(base-band)으로 낮춘 후 내부 코드 (C/A(Coarse/Acquisition)) 발생기에서 발생된 코드를 곱한 후 적분하여 데이터 값을 획득하고 추적한다.

- [0006] 이때, 상관기의 코드 발생기는 코드 추적을 위해 대부분 1/2 칩 간격의 세 개의 신호를 생성한다. 즉 Prompt 신호, 상기 Prompt 신호보다 1/2 칩 빠른 신호인 Early 신호, Prompt 신호보다 1/2 칩 느린 신호인 Late 신호를 생성한다. 그 이유는 종래 GPS 수신기의 대부분의 RF 단에서는 위성 신호를 2Mhz 필터링을 하기 때문에 기저대역 처리 과정에서 칩 간격을 줄인다고 하더라도 그 효과가 거의 없기 때문이다.

- [0007] 그러나, 최근 갈릴레오 신호까지 고려함으로써 신호 대역폭이 커지게 되어 4Mhz 이상의 대역폭을 갖는 RF 모듈이 설계되고 있고, 4Mhz 이상의 대역폭을 갖는 RF 모듈에 있어서 상관기의 코드 발생기에서 1/2 칩 간격의 신호만을 생성한다면 다중 경로 오차 발생시 이를 판별하기 어렵게 되기 때문에, 따라서 상관기의 코드 발생기는 코드 추척을 위해 1/4 칩 간격의 네 개의 신호를 생성하도록 구현되고 있다. 즉, Prompt 신호, 상기 Prompt 신호보다 1/4 칩 빠른 신호인 1/4 Early 신호, 상기 Prompt 신호보다 1/2 칩 빠른 신호인 1/2 Early 신호, 상기 Prompt 신호보다 1/2 칩 느린 신호인 1/2 Late 신호를 생성한다.

- [0008] 이에 따라 1/4 칩 간격의 코드 발생기를 사용하는 GPS 수신기의 상관기는 1/2 칩 간격의 코드 발생기를 사용할 때보다 4 개의 적분 회로 구조(I, Q phase 각 2 개)가 더 필요하여 많은 메모리 자원이 요구되는 문제점이 있다.

## 발명의 내용

#### 해결 하고자하는 과제

- [0009] 본 발명은 상기와 같은 문제점을 해결하기 위해 안출된 것으로, 자원 리소스를 절약하며 다중 경로 오차를 완화할 수 있는 위성 신호 추적기의 상관 장치 및 그 방법을 제공하는데 그 목적이 있다.

- [0010] 본 발명의 다른 목적 및 장점들은 하기의 설명에 의해서 이해될 수 있으며, 본 발명의 실시예에 의해 보다 분명하게 알게 될 것이다. 또한, 본 발명의 목적 및 장점들은 특허 청구 범위에 나타낸 수단 및 그 조합에 의해 실현될 수 있음을 쉽게 알 수 있을 것이다.

# 과제 해결수단

- [0011] 상기 목적을 달성하기 위한 본 발명의 제 1 측면에 따른, 위성으로부터 수신된 위성 신호에 자체 생성한 위성 식별 코드 신호를 혼합하여 위성 신호를 추적하는 위성 신호 추적기의 상관 장치는, 복수의 빠른 코드 신호와 복수의 느린 코드 신호 중 특정 칩 간격으로 지연된 코드 신호와 다른 칩 간격으로 지연된 코드 신호를 번갈아 가며 다중화하여 상기 위성 식별 코드 신호로서 출력하는 다중화기;를 포함하는 것을 특징으로 한다.

- [0012] 또한, 상기 목적을 달성하기 위한 본 발명의 제 2 측면에 따른, 위성 신호를 수신하여 추적하는 위성 신호 추적 기의 상관 장치는, 위성 식별 코드 신호를 발생하는 코드 발생기; 상기 위성 식별 코드 신호를 지연시켜 복수의 빠른(Early) 코드 신호와 복수의 느린(Late) 코드 신호를 생성하는 지연기; 상기 지연기에서 생성된 복수의 빠른 코드 신호와 복수의 느린 코드 신호 중 특정 칩 간격으로 지연된 코드 신호와 다른 칩 간격으로 지연된 코드 신호를 번갈아가며 다중화하는 다중화기; 반송파가 제거된 입력 신호와 상기 다중화기에서 다중화되어 출력되는 코드 신호를 혼합하는 혼합기; 및 상기 혼합기에서 출력되는 신호를 적분하는 적분기;를 포함하는 것을 특징으로 한다.

- [0013] 또한, 상기 목적을 달성하기 위한 본 발명의 제 3 측면에 따른 위성 신호 추적기에서 위성 식별 코드를 추적하기 위한 상관 방법은, 내부에서 발생된 위성 식별 코드 신호를 지연시켜 복수의 빠른(Early) 코드 신호와 복수의 느린(Late) 코드 신호를 생성하는 단계; 상기 복수의 빠른 코드 신호와 복수의 느린 코드 신호 중 특정 칩 간격으로 지연된 코드 신호를 다중화하는 단계; 반송파가 제거된 입력 신호와 상기 다중화되어 출력되는 코드 신호를 혼합하고 적분하는 단계; 상기 복수의 빠른 코드 신호와 복수의 느린 코드 신호 중 상기 특정 칩 간격과 다른 칩 간격으로 지연된 코드 신호를 다중화하는 단계; 및 반송파가 제거된 입력 신호와 상기 (d) 단계에서 다중화되어 출력되는 코드 신호를 혼합하고 적분하는 단계;를 포함하는 것을 특징으로 한다.

## 直 과

[0014] 상기와 같은 본 발명에 따르면, 하나의 회로 구조로 1/2 칩 지연의 상관 장치 구성과 1/4 칩 지연의 상관 장치 구성을 모두 구현함으로써, 회로 규모를 줄일 수 있을 뿐만 아니라 비용도 절감할 수 있다.

#### 발명의 실시를 위한 구체적인 내용

- [0015] 상술한 목적, 특징 및 장점은 첨부된 도면과 관련한 다음의 상세한 설명을 통하여 보다 분명해 질 것이며, 그에 따라 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 것이다. 또한, 본 발명을 설명함에 있어서 본 발명과 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우에 그 상세한 설명을 생략하기로 한다. 이하, 첨부된 도면을 참조하여 본 발명에 따른 바람직한 일 실시예를 상세히 설명하기로 한다.

- [0016] 본 발명의 실시예를 설명하기에 앞서 본 발명에 따른 상관 장치는 인공 위성으로부터 수신된 신호를 이용하여 위치를 결정하는 위치 측정 시스템의 위성 신호 추적기에 적용되는 상관 장치로 이해되어야 함을 분명히 한다. 즉, 미국 국방부에서 운영하는 통상적인 GPS(Global Positioning System) 및 유럽연합을 위주로 하여 개발중인 갈릴레오 위치 결정 시스템(Galileo Positioning System), 그리고 러시아에서 운영하는 GLONASS(GLObal NAvigation Satellite System) 등에서 위성 신호를 추적하여 위치를 결정하는 위성 신호 추적기에 적용되는 상관 장치로 이해되어야 한다. 이하에서는 위치 신호 추적기로서 대표적으로 GPS 수신 장치를 실시예로서 설명한다. 그러나 이제 제한되는 것은 아니며 상술한 GLONASS, 갈릴레오 위성 항법 시스템의 위성 신호 추적기에 적용됨은 자명하다.

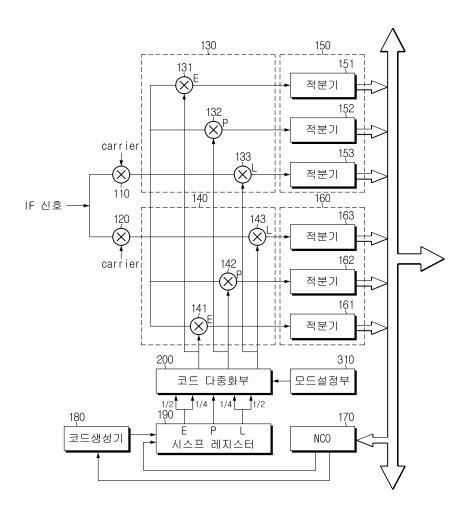

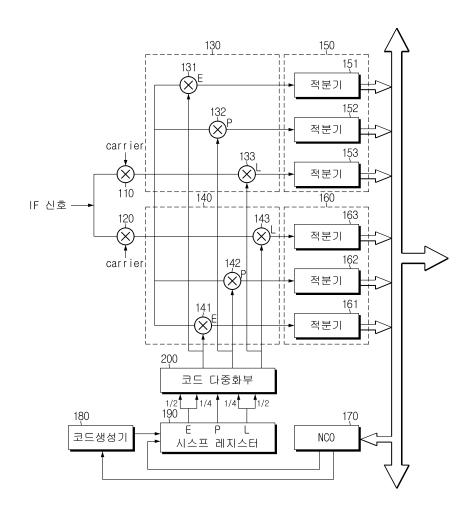

- [0017] 도 1은 본 발명의 일 실시예에 따른 GPS 수신기의 상관 장치의 구성을 나타낸 도면이다.

- [0018] 도 1에 도시된 바와 같이, 본 발명에 따른 상관 장치는, I/Q 반송파 혼합기(110, 120), I/Q 코드 혼합기(130, 140), I/Q 적분기(150, 160), 수치 제어 발진기(NCO)(170), 코드 생성기(180), 지연기(190) 및 코드 다중화부 (200)를 포함한다.

- [0019] GPS 수신기의 RF 단에 수신된 위성 신호는 상기 RF 단에서 중간 주파수(IF)로 변환된 후 이산화(digitalize)되어 I(In-phase) 신호는 I 반송파 혼합기(110)에 입력되고, Q(Quadrature-phase) 신호는 Q 반송파 혼합기(120)에 입력된다.

- [0020] I 반송파 혼합기(110)는 상기 입력된 I 신호에 반송파 클럭 발생기(Carrier Digital Controlled Oscillator)로

부터 제공되는 I(In-phase) 신호를 곱하여 반송파를 제거한 후 I 코드 혼합기(130)로 출력한다.

- [0021] Q 반송파 혼합기(120)는 상기 입력된 Q 신호에 반송파 클럭 발생기(Carrier Digital Controlled Oscillator)로 부터 제공되는 Q(Quadrature-phase) 신호를 곱하여 반송파를 제거한 후 Q 코드 혼합기(140)로 출력한다.

- [0022] I 코드 혼합기(130)는 상기 I 반송파 혼합기(110)로부터 출력된 신호와 Prompt 신호보다 빠른 Early 신호를 곱하여 출력하는 혼합기(131)와, 상기 I 반송파 혼합기(110)로부터 출력된 신호와 Prompt 신호를 곱하여 출력하는 혼합기(132)와, 상기 I 반송파 혼합기(110)로부터 출력된 신호와 Prompt 신호보다 느린 Late 신호를 곱하여 출력하는 혼합기(133)를 포함하여 구성된다. 각 혼합기에 입력되는 Early, Prompt, Late 신호는 코드 다중화부 (200)로부터 제공된다.

- [0023] Q 코드 혼합기(140)는 상기 Q 반송파 혼합기(120)로부터 출력된 신호와 Prompt 신호보다 빠른 Early 신호를 곱하여 출력하는 혼합기(141)와, 상기 Q 반송파 혼합기(120)로부터 출력된 신호와 Prompt 신호를 곱하여 출력하는 혼합기(142)와, 상기 Q 반송파 혼합기(120)로부터 출력된 신호와 상기 Prompt 신호보다 느린 Late 신호를 곱하여 출력하는 혼합기(143)를 포함하여 구성된다. 각 혼합기에 입력되는 Early, Prompt, Late 신호는 코드 다중화 부(200)로부터 제공된다.

- [0024] I 적분기(150)는 상기 I 코드 혼합기(130)로부터 출력되는 신호를 일정한 주기 동안(예컨대, 1ms) 적분하여 출력한다. 즉, 제 1 I 적분기(151)는 제 1 I 코드 혼합기(131)로부터 출력되는 신호를 적분하여 I Prompt 보다 1/2 또는 1/4 칩 빠른 Early 코드에 대한 상관값을 계산하여 출력하고, 제 2 I 적분기(152)는 제 2 I 코드 혼합기(132)로부터 출력되는 신호를 적분하여 I Prompt 코드에 대한 상관값을 계산하여 출력하며, 제 3 I 적분기(153)는 제 3 I 코드 혼합기(133)로부터 출력되는 신호를 적분하여 I Prompt 보다 1/2 또는 1/4 칩 느린 Late 코드에 대한 상관값을 계산하여 출력한다.

- [0025] Q 적분기(160)는 상기 Q 코드 혼합기(140)로부터 출력되는 신호를 C/A 코드 한 주기(예컨대, 1ms)동안 적분하여 출력한다. 즉, 제 1 Q 적분기(161)는 제 1 Q 코드 혼합기(141)로부터 출력되는 신호를 적분하여 Q Prompt 보다 1/2 또는 1/4 칩 빠른 Early 코드에 대한 상관값을 계산하여 출력하고, 제 2 Q 적분기(162)는 제 2 Q 코드 혼합기(142)로부터 출력되는 신호를 적분하여 Q Prompt 코드에 대한 상관값을 계산하여 출력하며, 제 3 Q 적분기(163)는 제 3 Q 코드 혼합기(143)로부터 출력되는 신호를 적분하여 Q Prompt 보다 1/2 또는 1/4 칩 느린 Late 코드에 대한 상관값을 계산하여 출력하다.

- [0026] 수치 제어 발진기(NCO:Numerically Controlled Oscillator)(170)는, C/A 코드의 주파수와 동일한 기준 주파수 및 C/A 코드의 주파수의 4 배에 해당하는 기준 주파수를 생성하여 상기 전자의 기준 주파수는 코드 생성기(18 0)로 출력하고, 상기 후자의 기준 주파수는 지연기(190)에 출력한다.

- [0027] 코드 생성기(180)는, 상기 수치 제어 발진기(170)로부터 수신된 기준 주파수에 따라 C/A 코드를 생성하여 지연 기(190)로 출력한다.

- [0028] 지연기(190)는 상기 수치 제어 발진기(170)로부터 수신된 C/A 코드의 주파수의 4 배에 해당하는 기준 주파수에 따라 상기 코드 생성기(180)로부터 수신된 C/A 코드에 대해 Prompt 코드, 상기 Prompt 코드보다 1/4 칩 빠른 코드인 1/4 Early 코드, 상기 Prompt 코드보다 1/2 칩 빠른 코드인 1/2 Early 코드, 상기 Prompt 코드보다 1/4 칩 느린 코드인 1/4 Late 코드, 상기 Prompt 코드보다 1/2 칩 느린 코드인 1/2 Late 코드를 생성하여 출력한다. 바람직하게, 지연기(190)로서 시프트 레지스터(shift register)를 사용할 수 있다.

- [0029] 코드 다중화부(200)는 상기 지연기(190)에서 출력되어 입력되는 코드에 대해 일정한 주기마다 1/2 칩 지연의 코드와 1/4 칩 지연의 코드를 번갈아 가며 멀티플렉싱하여 I 및 Q 코드 혼합기(130, 140)로 출력한다. 즉, 처음 lms 동안은 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드를 I 및 Q 코드 혼합기(130, 140)로 출력하고, 다음 lms 동안은 Prompt 코드, 1/4 칩 지연의 Early 및 Late 코드를 I 및 Q 코드 혼합기(130, 140)로 출력한다. 따라서 32ms 동안 16 개의 1/2 칩 지연에 대한 상관값, 16 개의 1/4 칩 지연에 대한 상관값, 32 개의 Prompt에 대한 상관값을 얻을 수 있게 된다.

- [0030] 이상과 같이 본 발명에 따른 GPS 수신기의 상관 장치는 1/2 칩 지연 코드에 대한 상관값과 1/4 칩 지연 코드에 대한 상관값을 동시에 획득할 수 있게 되어, 위성 신호를 추적하는데 있어 다중 경로 오차를 완화시킬 수 있다. 종래에는 1/2 칩 지연 코드 및 1/4 칩 지연 코드에 대한 상관값을 획득하기 위해서는 1/2 칩 지연 구성의 상관 장치에 1/4 칩 지연 코드에 대한 코드 혼합기 및 적분기를 추가해야 하므로, 1/2 칩 지연 구성의 상관 장치보다 I 및 Q 쪽에 각각 2 개씩 총 4 개씩의 코드 혼합기 및 적분기가 더 소요되는 문제점이 있다. 그러나 상술한 바와 같은 본 발명에 따른 상관 장치는, 종래 1/2 칩 지연 구성의 상관 장치의 구성을 그대로 유지하며 다중화부

만 추가로 구성하면 되어 자원 리소스를 줄이면서 동일한 효과를 얻을 수 있다.

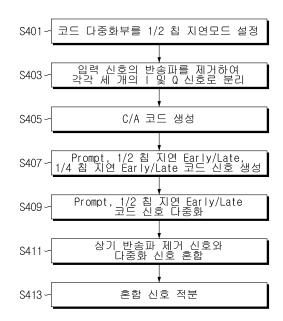

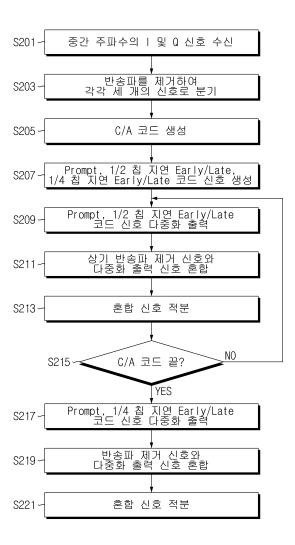

- [0031] 도 2는 본 발명의 일 실시예에 따른 GPS 수신기의 상관 방법을 설명하는 흐름도이다.

- [0032] 도 2에 도시된 바와 같이, GPS 수신기의 RF 단에 수신된 위성 신호는 상기 RF 단에서 중간 주파수(IF)로 변환된 후 이산화(digitalize)되어 I(In-phase) 신호 및 Q(Quadrature-phase) 신호가 상관 장치에 입력된다(S201).

- [0033] 상관 장치의 I 및 Q 반송파 혼합기(110, 120)는 상기 입력된 I 및 Q 신호에 반송파 클럭 발생기(Carrier Digital Controlled Oscillator)로부터 제공되는 I 및 Q 신호를 곱하여 반송파를 제거하여 각각 세 개의 신호로 분기한다(S203).

- [0034] 한편, 상관 장치의 코드 생성기(180)는 C/A 코드 신호를 생성하고(S205), 이어서 지연기(190)는 상기 코드 생성기(180)에서 생성된 C/A 코드에 대해 Prompt 코드 신호, 상기 Prompt 코드 신호보다 1/4 칩 빠른 코드 신호인 1/4 Early 코드 신호, 상기 Prompt 코드 신호보다 1/2 칩 빠른 코드 신호인 1/2 Early 코드 신호, 상기 Prompt 코드 신호보다 1/4 칩 느린 코드 신호인 1/4 Late 코드 신호, 상기 Prompt 코드 신호보다 1/2 칩 느린 코드 신호인 1/2 Late 코드 신호를 생성한다(S207). 여기서, 코드 생성기(180)와 지연기(190)는 각각 수치 제어 발진기(170)로부터 출력된 기준 주파수에 기초하여 C/A 코드 신호를 생성하고 그 C/A 코드 신호에 대한 Prompt 코드 신호, Early 코드 신호 및 Late 코드 신호를 생성한다.

- [0035] 다음으로, 상관 장치의 코드 다중화부(200)는 상기 지연기(190)에서 출력되는 코드 중 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드만을 멀티플렉싱하여 출력한다(S209).

- [0036] 이때, 도 2에서 상기 S205, S207, S209 단계가 상기 S201 및 S203 단계 이후에 실행되는 것으로 도시되어 있으나, 상기 S205 내지 S209 단계는 상기 S201 및 S203 단계가 실행되는 동안 병렬적으로 실행되는 것으로 이해되어야 한다.

- [0037] 이와 같이, 외부로부터 입력된 I 및 Q 신호에서 반송파가 제거되고 동시에 코드 다중화부(200)에서 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드가 출력되면, 상관 장치의 코드 혼합기(131, 132, 133, 141, 142, 143)는 상기 반송파가 제거된 세 개의 I 및 세 개의 Q 신호에 각각 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드를 곱한다(S211).

- [0038] 다음으로, 상관 장치의 적분기(151, 152, 153, 161, 162, 163)는 상기 코드 혼합기(131, 132, 133, 141, 142, 143)로부터 출력되는 각각의 신호를 적분하여 출력한다(S213).

- [0039] 이와 같이 과정을 C/A 코드의 한 주기(즉, 1ms)동안 반복한 후 다음 C/A 코드 주기에서(S215), 상관 장치의 코드 다중화부(200)는 상기 지연기(190)에서 출력되는 코드 중 Prompt 코드, 1/4 칩 지연의 Early 및 Late 코드만을 멀티플렉싱하여 출력한다(S217).

- [0040] 이어서, 상관 장치의 코드 혼합기(131, 132, 133, 141, 142, 143)는 반송파가 제거된 세 개의 입력 I 및 세 개의 입력 Q 신호에 각각 Prompt 코드, 1/4 칩 지연의 Early 및 Late 코드를 곱하여 출력하고(S219), 상관 장치의 적분기(151, 152, 153, 161, 162, 163)는 상기 코드 혼합기(131, 132, 133, 141, 142, 143)로부터 출력되는 각 각의 신호를 적분하여 출력한다(S221).

- [0041] 이상과 같이 본 발명에 따른 GPS 수신기의 상관 장치는 1/2 칩 지연 코드에 대한 상관값과 1/4 칩 지연 코드에 대한 상관값을 동시에 획득할 수 있게 되어, 위성 신호를 추적하는데 있어 다중 경로 오차를 완화시킬 수 있다.

- [0042] 도 3은 본 발명의 다른 실시예에 따른 GPS 수신기의 상관 장치의 구성을 나타낸 도면이다. 도 1과 동일한 참조 부호를 갖는 구성요소는 동일한 기능을 수행하는 것으로 이하에서는 도 1과 다른 부분에 대해서만 설명한다.

- [0043] 도 1과 달리 도 3에 도시된 본 발명에 따른 GPS 수신기의 상관 장치는, 모드 설정부(310)를 더 포함한다. 도 1에 도시된 GPS 수신기의 상관 장치에서 코드 다중화부(200)는 1/2 칩 지연의 코드 및 1/4 칩 지연의 코드를 C/A 코드 주기로 번갈아가며 교차로 발생한다. 그런데 경우에 따라 GPS 수신기의 상관 장치는 1/2 칩 지연의 C/A 코드만을 이용할 필요가 있다. 따라서 도 3의 모드 설정부(310)는 코드 다중화부(200)로 제어 신호를 전송하여, 코드 다중화부(200)로 하여금 1/2 칩 지연의 코드만을 멀티플랙싱하거나 도 1과 같이 1/2 칩 지연의 코드와 1/4 칩 지연의 코드를 번갈아가며 교차 발생하도록 제어한다.

- [0044] 종래에 1/4 칩 지연의 구성과 1/2 칩 지연의 구성을 모두 구현하기 위해서는, 1/4 칩 지연의 상관 장치 회로와 1/2 칩 지연의 상관 장치 회로를 모두 구현해야하므로 리소스가 많이 소요되어 비용이 증가하고 회로 규모가 증대해지는 문제점이 있었으나, 본 발명에 따른 GPS 수신기의 상관 장치는 하나의 회로 구조로 1/2 칩 지연의 상

관 장치 구성과 1/4 칩 지연의 상관 장치 구성을 모두 구현하기 때문에, 회로 규모를 줄일 수 있을 뿐만 아니라 비용도 절감할 수 있다.

- [0045] 도 4는 본 발명의 일 실시예에 따른 GPS 수신기의 상관 방법을 설명하는 흐름도이다.

- [0046] 도 4에 도시된 바와 같이, 먼저 본 발명에 따른 상관 장치의 모드 설정부(310)는 코드 다중화부(200)로 제어 신호를 전송하여 코드 다중화부(200)가 1/2 칩 지연 코드를 출력할 수 있도록 한다(S401). 즉 코드 다중화부(200)를 1/2 칩 지연 모드로 설정한다.

- [0047] 다음으로, GPS 수신기의 RF 단에 수신된 위성 신호는 상기 RF 단에서 중간 주파수(IF)로 변환된 후 이산화 (digitalize)되어 I(In-phase) 신호 및 Q(Quadrature-phase) 신호가 상관 장치에 입력되고, 상관 장치의 I 및 Q 반송파 혼합기(110, 120)는 상기 입력된 I 및 Q 신호에 반송파 클럭 발생기(Carrier Digital Controlled Oscillator)로부터 제공되는 I 및 Q 신호를 곱하여 반송파를 제거하여 각각 세 개의 신호로 분기한다(S403).

- [0048] 한편, 상관 장치의 코드 생성기(180)는 C/A 코드를 생성하고(S405), 이어서 지연기(190)는 상기 코드 생성기 (180)에서 생성된 C/A 코드에 대해 Prompt 코드, 상기 Prompt 코드보다 1/4 칩 빠른 코드인 1/4 Early 코드, 상기 Prompt 코드보다 1/2 칩 빠른 코드인 1/2 Early 코드, 상기 Prompt 코드보다 1/4 칩 느린 코드인 1/4 Late 코드, 상기 Prompt 코드보다 1/2 칩 느린 코드인 1/2 Late 코드를 생성한다(S407). 여기서, 코드 생성기 (180)와 지연기(190)는 각각 수치 제어 발진기(170)로부터 출력된 기준 주파수에 기초하여 C/A 코드를 생성하고 그 C/A 코드에 대한 Prompt 코드, Early 코드 및 Late 코드를 생성한다.

- [0049] 다음으로, 상관 장치의 코드 다중화부(200)는 상기 지연기(190)에서 출력되는 코드 중 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드만을 멀티플렉싱하여 출력한다(S409).

- [0050] 이때, 도 2에서 상기 S405, S407, S409 단계가 상기 S403 단계 이후에 실행되는 것으로 도시되어 있으나, 상기 S405 내지 S409 단계는 상기 S403 단계가 실행되는 동안 병렬적으로 실행되는 것으로 이해되어야 한다.

- [0051] 이와 같이, 외부로부터 입력된 I 및 Q 신호에서 반송파가 제거되고 동시에 코드 다중화부(200)에서 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드가 출력되면, 상관 장치의 코드 혼합기(131, 132, 133, 141, 142, 143)는 상기 반송파가 제거된 세 개의 I 및 세 개의 Q 신호에 각각 Prompt 코드, 1/2 칩 지연의 Early 및 Late 코드를 곱한다(S411).

- [0052] 다음으로, 상관 장치의 적분기(151, 152, 153, 161, 162, 163)는 상기 코드 혼합기(131, 132, 133, 141, 142, 143)로부터 출력되는 각각의 신호를 적분하여 출력한다(S413). 이상의 상기 S403 내지 S413 단계는 C/A 코드의 추적이 완료되는 순간까지 반복 수행된다.

- [0053] 이상과 같은 본 발명에 따르면, 하나의 상관 장치에서 1/4 칩 지연 및 1/2 칩 지연을 선택적으로 적용시킴으로 써 종래 상관 장치에 비해 회로 규모를 줄일 수 있을 뿐만 아니라 비용도 절감할 수 있다. 또한, 1/2 칩 지연의 상관 장치에 비해 1/4 칩 지연도 함게 적용함으로써 다중 경로 오차를 완화할 수 있다.

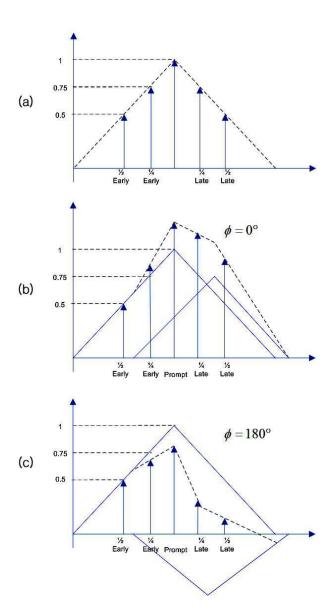

- [0054] 도 5는 1/2 칩 지연을 이용한 상관값 및 1/4 칩 지연을 이용한 상관값을 비교한 그래프이다.

- [0055] 도 5의 (a)는 1/2 칩 지연을 이용한 상관값을 나타낸 그래프로서, 도 5의 (a)에 도시된 바와 같이 1/2 칩 지연의 고정된 칩 지연만을 이용하는 경우 3 개의 상관값만을 측정값으로 얻게 된다. 그러나 이러한 3 개의 상관값만으로는 GPS 수신기에 다중 경로 신호가 수신되었는지 판단하기가 매우 어렵다.

- [0056] 도 5의 (b) 및 (c)는 1/4 칩 지연을 이용한 상관값을 나타낸 그래프로서, 도 5의 (b)는 동일 위상의 다중 경로 신호가 수신된 경우이고 도 5의 (c)는 180° 위상차의 다중 경로 신호가 수신된 경우이다. 도 5의 (b) 및 (c)에 도시된 바와 같이 1/4 칩 지연의 칩 지연을 이용하는 경우 5 개의 상관값을 측정값으로 획득할 수 있게 되어, 다중 경로 신호 판단과 동시에 다중 경로에 대한 보상이 가능하다.

- [0057] 본 발명에 있어서는 상술한 바와 같이 1/2 칩 지연 및 1/4 칩 지연을 선택적으로 적용함으로써 회로 규모를 줄이며 동시에 다중 경로 오차를 완화할 수 있도록 한다.

- [0058] 이러한 본 발명에 따른 방법을 기록매체(씨디롬, 램, 롬, 플로피 디스크, 하드 디스크, 광자기 디스크 등)에 저 장하는 과정은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있으므로 더 이상 상세히 설명하지 않기로 한다.

- [0059] 이상에서 설명한 본 발명은, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 있어 본 발명의 기술적

사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하므로 전술한 실시예 및 첨부된 도면 에 의해 한정되는 것이 아니다.

# 도면의 간단한 설명

- [0060] 도 1은 본 발명의 일 실시예에 따른 GPS 수신기의 상관 장치의 구성을 나타낸 도면이다.

- [0061] 도 2는 본 발명의 일 실시예에 따른 GPS 수신기의 상관 방법을 설명하는 흐름도이다.

- [0062] 도 3은 본 발명의 다른 실시예에 따른 GPS 수신기의 상관 장치의 구성을 나타낸 도면이다.

- 도 4는 본 발명의 일 실시예에 따른 GPS 수신기의 상관 방법을 설명하는 흐름도이다.

- [0064] 도 5는 1/2 칩 지연을 이용한 상관값 및 1/4 칩 지연을 이용한 상관값을 비교한 그래프이다.

# 도면

[0063]

# 도면3