### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3651944号 (P3651944)

(45) 発行日 平成17年5月25日(2005.5.25)

(24) 登録日 平成17年3月4日(2005.3.4)

| (51) Int.C1. <sup>7</sup> |         | FI   |        |         |                        |                      |

|---------------------------|---------|------|--------|---------|------------------------|----------------------|

| нозк                      | 19/173  | нозк | 19/173 |         |                        |                      |

| H <b>O</b> 1L             | 27/118  | нозк | 19/21  |         |                        |                      |

| нозк                      | 19/0175 | HO1L | 21/82  | M       |                        |                      |

| нозк                      | 19/0948 | нозк | 19/00  | 1 O 1 F |                        |                      |

| нозк                      | 19/21   | нозк | 19/094 | В       |                        |                      |

|                           |         |      |        |         | 544 - 15 - T - 345 - 4 | ( * .a <del></del> ) |

請求項の数 1 (全 13 頁)

(21) 出願番号 特願平7-2233

(22) 出願日 平成7年1月10日(1995.1.10)

(65) 公開番号 特開平8-37458

(43) 公開日 平成8年2月6日 (1996.2.6) 審査請求日 平成14年1月9日 (2002.1.9)

(31) 優先権主張番号 178712

(32) 優先日 平成6年1月10日 (1994.1.10)

(33) 優先権主張国 米国(US)

|(73)特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテツド

アメリカ合衆国テキサス州ダラス, ノース セントラルエクスプレスウエイ 135

00

||(74)代理人 100066692

弁理士 浅村 皓

(74)代理人 100072040

弁理士 浅村 肇

(74)代理人 100091339

弁理士 清水 邦明

(74)代理人 100094673

弁理士 林 鉐三

最終頁に続く

(54) 【発明の名称】 CMOSセル

### (57)【特許請求の範囲】

## 【請求項1】

ゲートアレイ中に使用するためのCMOSセルであって、

第1の長方形領域に配置された複数のnチャンネルトランジスタであって、前記第1の 長方形領域の長手方向軸は回路設計に前記nチャンネルトランジスタの幅が一致するよう に調整される対称軸を構成する、複数のnチャンネルトランジスタと、

第2の長方形領域に配置された複数のpチャンネルトランジスタであって、前記第2の 長方形領域の長手方向軸は回路設計に前記pチャンネルトランジスタの幅が一致するよう に調整される対称軸を構成する、複数のpチャンネルトランジスタと、

第3の長方形領域に配置された少なくとも1つの付加的なpチャンネルトランジスタと 少なくとも1つの付加的なnチャンネルトランジスタであって、当該付加的なトランジス タは前記nチャンネルトランジスタよりも大きさが大きい前記付加的なトランジスタと、

前記トランジスタの各々はゲート、ソース及びドレインを有し、

前記複数の n チャンネルトランジスタの内の 2 つのトランジスタのゲートを前記複数の p チャンネルトランジスタの内の 2 つのトランジスタのゲートと電気的に接続する手段と

前記複数のnチャンネルトランジスタの内の一つのトランジスタのゲートと前記複数のpチャンネルトランジスタの内の一つのトランジスタのゲートを電気的に接続する手段と、及び

前記付加的なnチャンネルトランジスタのゲートと前記付加的なpチャンネルトランジ

スタのゲートを電気的に接続する手段と、

を備えたCMOSセル。

【発明の詳細な説明】

[0001]

【産業上の利用分野】

本発明は一般的に、ゲートアレイの分野に関するものであり、更に詳細には、主要な構築 ブロックとして予め部分的に配線された複数個の回路を有し、その回路によって、マルチ プレクサー機能を含む単純な論理回路と複雑な論理回路の両方を生成することのできるセ ルを利用することに基づくアーキテクチャを有するゲートアレイに関する。本セルはライン駆動のための複数個のトランジスタを別途有する。

[0002]

【従来の技術】

従来のゲートアレイ基本セルはトランジスタアレイの効率的なレイアウトをめぐって発展してきた。これは部分的にはアレイ中に形成できるゲート数によるものであり、また部分的にはアレイが有する入力/出力ピンの数によるためでもある。回路が小型になって単一のチップ中に配置できるゲート数が増大するにつれて、プログラム可能な金属層を用いた機能の進展のほうに重点がおかれるようになっている。そのような方向で、メモリ回路、デジタル信号処理回路、加算器等の論理機能、およびその他の開発が行われてきたし、また、そのやり方は利用可能なトランジスタを用いてNANDゲート、AOIセル、インバーター、メモリセル、等を構成することに基づいている。

[00003]

プログラム可能な金属を用いて所望の機能を構成するためには利用可能な空間のかなりの部分を消費してしまい、その結果、非常に高密度に集積されたチップにおいては特に、形成できる機能密度が減少するということが生ずる。この結果、与えられたアレイに対して典型的な配線による非効率化は、そのチップ上の基本セルのうちの40%もが最終的な回路構成において利用されないという現象をもたらす。単一のゲートアレイ中で所望の機能を配線することができないということは、与えられた機能を実現するために必要な面積を増大させ、配線できなかった部品を無駄にすることによって、この技術を利用することのコストを増大させることにつながる。

[0004]

ゲートアレイセルを配線する場合の効率低下に寄与する別の因子は、これまで全く柔軟であると考えられてきた、セルそれ自身がしばしば 2 入力 N A N D 回路を構成するために利用可能なトランジスタを有することに基づいているという事実である。しかし、逐次的論理機能とデータ信号処理機能とを調べた結果、そのような論理回路中にマルチプレクサーが高頻度に存在することと、そのマルチプレクサーが、チャンネルを巡る配線がすぐに利用され尽くすために、設計者が考えていたとおりの数だけ実現することがかなり困難であるということが明らかになった。

[0005]

[0006]

【発明の概要】

本発明はCMOSアレイ基本セルであって、それは従来技術の基本セルに付随する上述の問題点およびその他の問題点を克服するように設計されており、N形トランジスタおよびP形トランジスタを複数個使用している。少なくともP形トランジスタ 2 個がそれらのゲートを少なくとも 2 個のN形トランジスタのゲートへ電気的に接続されている。更に、少なくとも 1 個のその他のN形トランジスタがそれのゲートを少なくとも 1 個のP形トランジスタのゲートへ電気的に接続されている。これら相互に接続されたトランジスタは、このアレイセルを使用して実現できる論理機能のための基本的な構築ブロックを構成する。

相互接続されたトランジスタに加えて、このセル中には一対の駆動トランジスタが設けられている。駆動トランジスタはそれらのゲートを互いに接続されて配置されている。駆動トランジスタの物理的な寸法は基本セル中のその他のトランジスタの寸法よりも大きく、

10

20

30

50

好ましくは、そのセル中のその他のトランジスタの寸法の2ないし5倍の範囲にある。この大きな寸法によって、駆動トランジスタはそのアレイ中の他のトランジスタを駆動するのに適したものとなる。更には、セル中の他のトランジスタが、その他のアレイせる中で典型的に用いられている場合に比べて寸法的に小さくでき、その結果、アレイ中のゲート数が増大し、それらのゲートの動作速度が増大する。

#### [0007]

本発明の上述の長所および特徴は、以下において本開示の一部を構成する図面に関連付けながらより詳細に説明する。

#### [00008]

#### 【実施例】

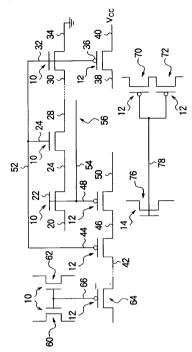

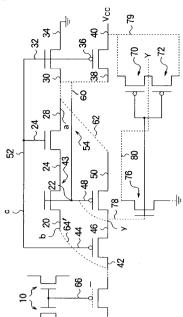

まず図1を参照すると、本発明の基本セルの回路図が示されている。図1の回路は、物理的に1つの行に配置された複数個のNチャンネルトランジスタ10を含み、また別の行に配置された複数個のPチャンネルトランジスタ12を含む。更に別のNチャンネルトランジスタ14が含まれているが、このNチャンネルデバイスはトランジスタ10とは異なる行に配置されている。更に別のPチャンネルトランジスタ13も含まれているが、それらは他のPチャンネルトランジスタ12と同じ行には配置されていない。

#### [0009]

第 1 の複数個の N チャンネルトランジスタ 1 0 は、ソース 2 4、ゲート 2 2、およびドレイン 2 0 を有する第 1 のトランジスタを含み、ゲート 2 6、およびドレイン 2 8 を有する第 2 のトランジスタのソース 2 4 に電気的に接するように作製されている。ソース 3 4、ゲート 3 2、およびドレイン 3 0 を備えた第 3 の N チャンネルトランジスタが設けられている。ソース 3 4 はアースへの接続のためのコンタクトパッドへつながれている。

#### [0010]

第1の複数個の P チャンネルトランジスタ 1 2 は、多結晶シリコン配線によって、トランジスタレベルで前記第1の複数個の N チャンネルトランジスタ 1 0 へ相互接続されている。詳細には、ソース 4 6、ゲート 4 4、およびドレイン 4 2を備えた第1の P チャンネルトランジスタが設けられている。このトランジスタは、ソース 4 6、ゲート 4 8、およびドレイン 5 0を有する第 2 の P チャンネルトランジスタつながれる。ソース 3 8、ゲート 3 6、およびドレイン 4 0を有する第 3 の P チャンネルトランジスタがあって、それは電圧源  $V_{cc}$  への接続のためのコンタクトパッドへつながれている。

#### [0011]

上述の3個のNチャンネルトランジスタおよび3個のPチャンネルトランジスタは多結晶シリコンリード線によって相互接続されて、予め部分的に配線された回路を構成する。特に、ゲート44、ゲート26、ゲート32、およびゲート36は多結晶シリコン導電性リード線52によって互いにつながれている。ゲート22と48とは第2の多結晶シリコン導電性リード線54によって互いにつながれている。このリード線54は後に図面に関する詳細な説明でより明らかになるように、一般に56として示したタブ部分を有し、それはゲート48とゲート22の間の直接接続箇所から延びている。このタブ部分56は、マルチプレクサー回路を構成するための、図1の回路を接続する第1レベル配線が容易になるように設けられている。

### [0012]

図1の回路は更に、2個のNチャンネルトランジスタ60と62を含み、それらはソースとドレインが未接続になっている。Pチャンネルトランジスタ64もソースおよびドレインを未接続として設けられている。しかし、トランジスタ60、62、および64のゲートは多結晶シリコンリード線66によって電気的につながれている。トランジスタ60、62、および64のこの構成は、図1に示した基本セルで以てメモリセルを構成するために特に適したものである。

### [0013]

図1の基本セルはまた、2個の別のPチャンネルトランジスタ70と72とを含んでおり、それらはソースを互いにつながれているが、それらのドレインは未接続のままに残され

10

20

30

40

ている。更に別のNチャンネルトランジスタ76が設けられており、それのソースとドレインも未接続である。しかし、トランジスタ76のゲートは多結晶シリコンリード線78によってトランジスタ70および72のゲートへつながれている。

#### [0014]

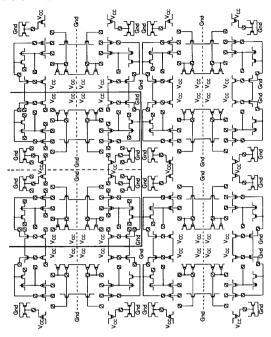

図1に示された基本セルの形状の特徴のために、このセルは各種反転および鏡像操作によって模写することができ、そのため、図1の基本セルを利用して複数の基本セルを互いに集団化して、複雑な関数を生成する設計者の能力を強化することが可能となる。例えば、図2は4個の基本セルをどのように配置すれば"四重(quad)"構成が実現するのかを示している。100で示した2個の斜線部のような四角は、システム設計者が所望の構成に基本セルを配置するためのコンタクト地点として利用することのできるコンタクトパッドを含む。

#### [0015]

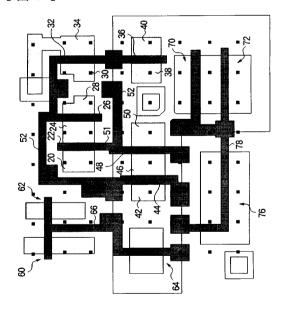

次に図3を参照すると、図1の基本セルの物理的な形状が示されている。図1の要素の各 々が、それらの位置が容易に識別できるように、図3中に示されている。トランジスタ7 0、72、および76は図3中でそれらの上に設けられた本質的に同じ寸法のNチャンネ ルトランジスタおよびPチャンネルトランジスタよりも大きな物理的面積を有するように 示されている。このことは、トランジスタ70、72、および76が、図3に示された基 本セルの外部にある他の回路を駆動するために用いられるためには有利なことである。こ れらのトランジスタを他のトランジスタよりも大きく作ることによって、駆動トランジス タ70、72、および76は図3中のその他のトランジスタよりも、長距離にあるより多 い回路を駆動する能力を有するようになる。事実、トランジスタ70、72、および76 のチャンネル幅は基本セル中のその他のトランジスタと比べて2ないし5倍の範囲にある べきことが分かった。トランジスタ70、72、および76の寸法が図3の基本セル中の その他のトランジスタの寸法を凌賀する正確な程度は、それによって駆動することを意図 する回路の数とトランジスタ間の配線距離とに依存する。設計におけるこの柔軟性は、設 計者がファンアウトと電力との間のトレードオフを好ましいものに選ぶことを可能とする ように基本セルの物理的レイアウトを変更できるようにする点で重要である。従って、本 発明の基本セル設計は変動する市場の需要に応えるように、迅速かつ容易に修正できる。

### [0016]

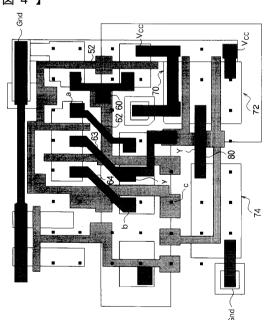

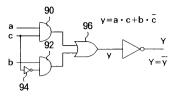

さて、図5を参照すると、図1の基本セルをマルチプレクサー回路へ変換するために必要な第1レベル配線が示されている。図4にもこれに対応する第1レベル配線が示されており、それもマルチプレクサーとして構成される基本セルの物理的トポロジーを含んでいる。特に、タブ56、ドレイン30、およびソース38の間に第1レベル配線60′が設けられている。ドレイン50とドレイン28との間には第2レベル配線62′が設けられている。ソース24とソース46との間には第3レベル配線63′が設けられている。ドレイン20とソース42との間には第4レベル配線64′が設けられている。この構成は、ANDゲート90、ANDゲート92、インバーター94、およびORゲート96を含む図6に示した論理回路図の一部分に対応している。図5には入力a、b、およびcが示され、またマルチプレクサーの出力がYで示されている。

#### [0017]

マルチプレクサー機能を生み出すために用いられるトランジスタの物理的寸法はトランジスタ70、72、および76の寸法よりも小さいので、既に述べたように、マルチプレクサーが他の回路を駆動する能力は小さい。従って、トランジスタ70、72、および76は出力yを反転して、反転信号をYに生成し、それを用いて数多くの他の入力を駆動できるように構成されている。インバーターは出力Yとトランジスタ76のゲートとをつなぐ第1レベル配線78を用いて構成される。トランジスタ76はそれのドレインをアースへつながれ、それのソースをトランジスタ70と72との接続点へつながれている。トランジスタ70および72のソースは第1レベル配線79によって電圧源V。こへつながれている。

### [0018]

40

10

20

上述の説明では、本発明の基本セルをどのように構成すれば複数の回路を駆動することの できる出力駆動器を備えるマルチプレクサーが形成できるかについて述べてきた。本基本 セルは、別の配線パターン状に非常に多数配置することによって異なる論理機能を実現す ることもできることを指摘しておく。事実、図1の構成が、その他の機能を得るために必 要とされる関数であるAND、あるいは排他的OR、および反転関数を作成することがで きることを示すことができる。当業者はこれら4つの関数を組み合わせれば任意の関数を 生成できること、従って、図1の基本セルは異なるやり方で配線されたその他の基本セル と組み合わせることによって実際的にシステム設計者によって望まれる任意の関数を生成 できることを理解するであろう。

#### [0019]

以上の説明は図面に示した本発明の実施例について特に重点的に行われてきたが、本発明 は本発明の精神と視野から外れることなしに、数多くのやり方で修正できることを当業者 は理解するであろう。例えば、もしNチャンネルトランジスタをより大きく作製する必要 があれば、Nチャンネルトランジスタによって占められる長方形領域を、この長方形領域 の長手方向の対称軸に関して単に基本セルのトポロジーを変更することによって広げるこ とができる。この軸はすべてのトランジスタ10、62、および60を貫通している。同 様なやり方で、上述の長方形領域の下にある第2の長方形領域中に位置するPチャンネル トランジスタもまた、第2の長方形領域内にあるPチャンネルトランジスタすべてを貫通 する第2の長手方向の対称軸に関して拡張することができる。

[0020]

これらおよびその他の形状的な変更は、本発明の特許請求の範囲によって定義される精神 と視野から外れることなしに行われ得る。

[0021]

以上の説明に関して更に以下の項を開示する。

(1)ゲートアレイ中に使用するためのCMOSセルであって、

すべて本質的に同じ物理的寸法の第 1 の複数個の n チャンネルトランジスタ、すべて前記 nチャンネルトランジスタと本質的に同じ物理的寸法の第1の複数個のpチャンネルトラ ンジスタであって、前記 p チャンネルトランジスタの 1 個以上が前記 n チャンネルトラン ジスタの1個以上と電気的に相互接続されて部分的に予め配線された回路を形成しており 、プログラム可能な金属層を用いて設計要求に応えるようにそれらを最終的な構成に後に 配置接続できるようになった第1の複数個のpチャンネルトランジスタ、および 少なくとも1個の付加的なnチャンネルトランジスタおよび少なくとも1個の付加的なp チャンネルトランジスタであって、前記付加的なトランジスタの各々が前記第1の複数個

の n チャンネルトランジスタの任意のものよりも大きな物理的寸法である、少なくとも 1 個の付加的なnチャンネルトランジスタおよび少なくとも1個の付加的なpチャンネルト ランジスタ、

を組み合わせて含むСMOSセル。

[0022]

(2)第1項記載のCMOSセルであって、前記付加的なトランジスタの各々が前記第1 の複数個のnチャンネルトランジスタの任意のものよりも約2ないし5倍大きい物理的寸 法であるCMOSセル。

[0023]

(3) 第1項記載のCMOSセルであって、前記寸法がチャンネル幅に対応しているCM OSセル。

[0024]

(4) 第2項記載のCMOSセルであって、前記寸法がチャンネル幅に対応しているCM OSセル。

[0025]

( 5 ) 第 1 項記載の C M O S セルであって、前記トランジスタの各々がソース、ドレイン 、およびゲートを有し、前記複数個のnチャンネルトランジスタのうちのいくつかのトラ 10

20

30

40

(6)

ンジスタのゲートと、前記複数個の p チャンネルトランジスタのうちのいくつかのトランジスタのゲートとが互いに接続されている C M O S セル。

[0026]

(6)第5項記載のCMOSセルであって、前記複数個のnチャンネルトランジスタおよび前記複数個のpチャンネルトランジスタの残りのトランジスタすべてのゲートが互いに接続されているCMOSセル。

[0027]

(7)第1項記載のCMOSセルであって、更に、各々がゲートを有する、2個の追加のnチャンネルトランジスタと1個の追加のpチャンネルトランジスタとを含み、前記追加のトランジスタのゲートが互いに接続されているCMOSセル。

[0028]

(8) 第1項記載のCMOSセルであって、前記付加的なnチャンネルトランジスタの各々と前記付加的なpチャンネルトランジスタの各々とが、互いに接続された1つのゲートを有しているCMOSセル。

[0029]

(9) 第5項記載のCMOSセルであって、前記付加的なnチャンネルトランジスタの各々と前記付加的なpチャンネルトランジスタの各々とが、互いに接続された1つのゲートを有しているCMOSセル。

[0030]

(10)ゲートアレイに使用するためのCMOSセルであって、

第1の対称軸に沿って配置された第1の複数個の n チャンネルトランジスタ、第2の対称軸に沿って配置された第1の複数個の p チャンネルトランジスタ、および

少なくとも1個のnチャンネル出力トランジスタおよび少なくとも1個のpチャンネル出力トランジスタであって、前記第1および第2の複数個のトランジスタのいずれよりも大きい物理的寸法を有する出力トランジスタ、

を組み合わせて含み、

前記複数個のnチャンネルトランジスタのチャンネル幅と前記複数個のpチャンネルトランジスタのチャンネル幅とが互いに独立的に選択できて、所望の電力消費およびファンアウト能力を実現できるようになっており、前記pチャンネルトランジスタの1個以上が前記nチャンネルトランジスタの1個以上と電気的に相互接続されて部分的に予め配線された回路を形成しており、プログラム可能な金属層を用いて設計要求に応えるようにそれらを最終的な構成に後に配置接続できるようになった、

CMOSセル。

[0031]

(11)第10項記載のCMOSセルであって、前記寸法がチャンネル幅に対応している CMOSセル。

[0032]

(12) 第10項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記付加的なトランジスタのうちの別の1個のトランジスタのゲートへ接続されたゲートを有しているCMOSセル。

[0033]

(13)第10項記載のCMOSセルであって、前記トランジスタがそれぞれソース、ドレイン、およびゲートを有し、前記複数個のnチャンネルトランジスタのうちのいくつかのトランジスタのゲートと、前記複数個のpチャンネルトランジスタのうちのいくつかのトランジスタのゲートとが互いに接続されているCMOSセル。

[0034]

(14)第13項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記付加的なトランジスタの別の1個のトランジスタのゲートへ接続されたゲートを有しているCMOSセル。

[0035]

10

20

30

40

(15)第10項記載のCMOSセルであって、更に、各々がゲートを有する、少なくとも2個の付加的なnチャンネルトランジスタと少なくとも1個の付加的なpチャンネルトランジスタとを含み、前記付加的なトランジスタすべてのゲートが互いに電気的に接続されているCMOSセル。

#### [0036]

(16)第13項記載のCMOSセルであって、更に、各々がゲートを有する、少なくとも2個の付加的なnチャンネルトランジスタと少なくとも1個の付加的なpチャンネルトランジスタとを含み、前記付加的なトランジスタすべてのゲートが互いに電気的に接続されているCMOSセル。

#### [0037]

(17)ゲートアレイに使用するためのCMOSセルであって、

各々がゲート、ソース、およびドレインを有する、第 1 、第 2 、および第 3 の n チャンネルトランジスタ、

各々がゲート、ソース、およびドレインを有する、第 1 、第 2 、および第 3 の p チャンネルトランジスタ、

前記第 1 、 第 2 、 および第 3 の n チャンネルトランジスタのドレインを電気的に相互接続するための手段、

前記第 1 、 第 2 、 および第 3 の p チャンネルトランジスタのドレインを電気的に相互接続するための手段、

前記第1のnチャンネルトランジスタのゲートと前記第2のpチャンネルトランジスタのゲートとを電気的に相互接続するための手段、および

前記第1のpチャンネルトランジスタのゲート、前記第2のnチャンネルトランジスタのゲート、前記第3のnチャンネルトランジスタのゲート、および前記第3のpチャンネルトランジスタのゲートを電気的に相互接続するための手段、を組み合わせて含むCMOSセル。

### [0038]

(18)第17項記載のCMOSセルであって、更に、

各々がゲートを有する、少なくとも 1 個の付加的な n チャンネルトランジスタと少なくとも 1 個の付加的な p チャンネルトランジスタ、および

前記付加的な p チャンネルトランジスタのゲートと前記付加的な n チャンネルトランジス 30 タのゲートとを相互接続する相互接続手段、

を含むCMOSセル。

#### [0039]

(19)第17項記載のCMOSセルであって、更に、各々がゲートを有する、2個の追加のnチャンネルトランジスタと1個の追加のpチャンネルトランジスタとを含み、前記追加のトランジスタのゲートが互いに接続されているCMOSセル。

### [0040]

(20)第18項記載のCMOSセルであって、更に、各々がゲートを有する、少なくとも2個の追加のnチャンネルトランジスタと少なくとも1個の追加のpチャンネルトランジスタのゲートが互いに接続されているCMOSセル

### [0041]

(21)第18項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記複数個のnチャンネルトランジスタの任意のものよりも約2ないし5倍大きい物理的寸法を有し、前記複数個のpチャンネルトランジスタの各々が前記複数個のnチャンネルトランジスタの各々と本質的に同じ寸法であるCMOSセル。

#### [0042]

(22)第18項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記複数個のnチャンネルトランジスタの任意のものよりも約2ないし5倍大きい物理的寸法を有し、前記複数個のpチャンネルトランジスタの各々が前記複数個のnチャンネルト

10

20

50

ランジスタの各々と本質的に同じ寸法であるCMOSセル。

[0043]

(23)第19項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記複数個のnチャンネルトランジスタの任意のものよりも約2ないし5倍大きい物理的寸法を有し、前記複数個のpチャンネルトランジスタの各々が前記複数個のnチャンネルトランジスタの各々と本質的に同じ寸法であるCMOSセル。

[0044]

(24)第20項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記複数個のnチャンネルトランジスタの任意のものよりも約2ないし5倍大きい物理的寸法を有し、前記複数個のpチャンネルトランジスタの各々が前記複数個のnチャンネルトランジスタの各々と本質的に同じ寸法であるCMOSセル。

10

[0045]

(25)第17項記載のCMOSセルであって、前記電気的に相互接続するための手段がそれぞれ、導電性金属と多結晶シリコンを含むグループのうちから選ばれた導電性材料を含んでいるCMOSセル。

[0046]

(26)ゲートアレイに使用するためのСМОSセルであって、

第1の一般に長方形の領域に設けられた複数個のnチャンネルトランジスタであって、前記第1の長方形領域の長手方向の軸が対称軸を提供しており、その軸に関して前記nチャンネルトランジスタの幅を回路設計基準に適合するように変更できるようになった複数個のnチャンネルトランジスタ、

20

第2の一般に長方形の領域に設けられた複数個の p チャンネルトランジスタであって、前記第2の長方形領域の長手方向の軸が対称軸を提供しており、その軸に関して前記 p チャンネルトランジスタの幅を回路設計基準に適合するように変更できるようになった複数個の p チャンネルトランジスタ、

第3の一般に長方形の領域に設けられた少なくとも1個の付加的なpチャンネルトランジスタと少なくとも1個の付加的なnチャンネルトランジスタとであって、前記nチャンネルトランジスタよりも大きい寸法を有する付加的なトランジスタ、

前記複数個のnチャンネルトランジスタのうちの2個のトランジスタのゲートと前記複数個のpチャンネルトランジスタのうちの2個のトランジスタのゲートとを電気的に接続する手段、

30

前記複数個のnチャンネルトランジスタのうちの1個のトランジスタのゲートと前記pチャンネルトランジスタのうちの1個のトランジスタのゲートとを電気的に接続する手段、および

前記付加的なnチャンネルトランジスタのゲートと前記付加的なpチャンネルトランジスタのゲートとを電気的に接続するための手段、

を組み合わせて含み、

前記トランジスタの各々がゲート、ソース、およびドレインを有している、CMOSセル

[0047]

40

(27)第26項記載のCMOSセルであって、更に、

前記複数個の n チャンネルトランジスタのうちの 2 個のトランジスタのゲートと前記複数個の p チャンネルトランジスタのうちの 1 個のトランジスタのゲートとを電気的に接続するための手段、

を含むCMOSセル。

[0048]

(28) 第26項記載のCMOSセルであって、前記付加的な各トランジスタの幅が、前記複数個のnチャンネルトランジスタの1個のトランジスタの幅の2ないし5倍であるCMOSセル。

[0049]

(29)第26項記載のCMOSセルであって、更に、第26項において定義された型のCMOSセルであって、第26項記載のセルに隣接して設けられた鏡像形状を有する追加のCMOSセルを含むCMOSセル。

[0050]

(30)第1項記載のCMOSセルであって、前記トランジスタの各々がソース、ドレイン、およびゲートを有し、前記複数個のnチャンネルトランジスタのうちのいくつかのトランジスタのゲートと前記複数個のpチャンネルトランジスタのうちのいくつかのトランジスタのゲートとが多結晶シリコンによって互いに電気的に接続されているCMOSセル

[0051]

(31)第30項記載のCMOSセルであって、前記複数個のnチャンネルトランジスタおよび前記複数個のpチャンネルトランジスタの残っているすべてのトランジスタのゲートが多結晶シリコンによって互いに接続されているCMOSセル。

[0052]

(32)第1項記載のCMOSセルであって、前記トランジスタの各々がソース、ドレイン、およびゲートを有し、前記複数個のnチャンネルトランジスタのうちのいくつかのトランジスタのゲートと前記複数個のpチャンネルトランジスタのうちのいくつかのトランジスタのゲートとがデバイスレベルにおいて互いに電気的に接続されているCMOSセル

[0053]

(33)第18項記載のCMOSセルであって、前記付加的なトランジスタの各々が、前記複数個のnチャンネルトランジスタの任意のものよりも大きい物理的寸法を有し、前記複数個のpチャンネルトランジスタの各々が前記複数個のnチャンネルトランジスタの各々と本質的に同じ寸法であるCMOSセル。

[0054]

(34)複数個のNチャンネルトランジスタ10と複数個のPチャンネルトランジスタ12とを備えたCMOSゲートアレイ用の基本セルが提供される。これらのトランジスタは、トランジスタレベルにおいて相互接続されて部分的に予め配線された回路を構成する。本基本セルには付加的なNチャンネルトランジスタ(14)およびPチャンネルトランジスタ(70、72)が含まれ、それらの少なくともいくつかのトランジスタは複数個のNチャンネルトランジスタ10または複数個のPチャンネルトランジスタ12よりも大きい寸法を有している。これらの大きい寸法のトランジスタは、セルの論理出力信号を他のセルへ送出するための出力駆動器として使用される。

【図面の簡単な説明】

【図1】本発明の基本セルの模式図。

【図2】2本の異なる対称軸に沿って4個の基本セルをどのように接続するかを示す図。

【図3】本発明の基本セルを含む要素の物理的配置。

【図4】図5のマルチプレクサー機能を実現するように図3の基本セルを配置するために必要な第1レベル配線。

【図5】図1に示された基本セルの要素をどのように接続してマルチプレクサー回路を形 40 成するかを示す回路図。

【図6】図4および図5に示すように配線された時の、図1の基本セルの論理回路図。

【符号の説明】

- 10 複数個のnチャンネルトランジスタ

- 12 複数個のpチャンネルトランジスタ

- 13 付加的な p チャンネルトランジスタ

- 14 付加的な n チャンネルトランジスタ

- 20 ドレイン

- 22 ゲート

24 ソース

50

10

20

10

20

30

```

26 ゲート

28 ドレイン

30 ドレイン

32 ゲート

3 4 ソース

3 6

ゲート

38 ソース

4 0

ドレイン

42 ドレイン

44 ゲート

46 ソース

48 ゲート

5 0

ドレイン

52 導電性リード線

5 4 リード線

56 タブ

60 nチャンネルトランジスタ

62 nチャンネルトランジスタ

60 第1レベル配線

62 第2レベル配線

63 第3レベル配線

64 第4レベル配線

64 pチャンネルトランジスタ

66 リード線

70 付加的 p チャンネルトランジスタ

7 2 付加的 p チャンネルトランジスタ

7 6 付加的 n チャンネルトランジスタ

78 リード線

9 0 A N D ゲート

```

9 2 A N D ゲート

9 4 インバーター 9 6 O R ゲート

100 コンタクトパッド

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

### フロントページの続き

(72)発明者 シバリング マハント - シェッティ

アメリカ合衆国テキサス州リチャードソン, スコッツボロ レーン 1405

(72)発明者 ロバート ランダーズ

アメリカ合衆国テキサス州プラノ,クロス ベンド 3228

### 審査官 彦田 克文

(56)参考文献 特開平04-212438(JP,A)

特開平02-003279(JP,A)

特開昭59-163836(JP,A)

特表平06-508480(JP,A)

欧州特許出願公開第00453279(EP,A1)

欧州特許出願公開第00119059(EP,A1)

国際公開第92/022924(WO,A1)

# (58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H03K 19/173

H01L 27/118

H03K 19/0175

H03K 19/0948

H03K 19/21