# (19) **日本国特許庁(JP)**

審査請求日

# (12) 特許公報(B2)

(11)特許番号

特許第3970211号 (P3970211)

(45) 発行日 平成19年9月5日(2007.9.5)

(24) 登録日 平成19年6月15日 (2007.6.15)

(51) Int.C1. FI

HO1L 23/12 (2006, 01) HO1L 23/12 501P HO1L 21/3205 (2006.01) HO1L 21/88 J  $\mathbf{T}$ HO1L 23/52 (2006, 01) HO1L 21/88

> 請求項の数 15 (全 12 頁)

(21) 出願番号 特願2003-179484 (P2003-179484) (22) 出願日 平成15年6月24日 (2003.6.24) (65) 公開番号 特開2005-19522 (P2005-19522A) (43) 公開日

平成17年1月20日 (2005.1.20)

平成18年6月20日 (2006.6.20)

(73)特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

||(74)代理人 100107906

弁理士 須藤 克彦

(74)代理人 100091605

弁理士 岡田 敬

|(72)発明者 高尾 幸弘

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

審査官 菅野 智子

最終頁に続く

### (54) 【発明の名称】半導体装置及びその製造方法

## (57)【特許請求の範囲】

### 【請求項1】

半導体チップの第1の主面に設けられたパッド電極と、

前記半導体チップの第1の主面に接着された支持基板と、

前記半導体チップに形成され順テーパー形状を有したビアホールと、

前記ビアホールを通して、前記パッド電極と電気的に接続され、かつ前記ビアホールから 前記半導体チップの第2の主面上を延在する配線層と、

前記配線層と電気的に接続された導電端子と、を有することを特徴とする半導体装置。

### 【請求項2】

前記半導体チップの第2の主面に半導体凸部が設けられ、前記配線層が前記半導体凸部を 覆うと共に、該半導体凸部上に前記導電端子が配置されたことを特徴とする請求項1記載 の半導体装置。

# 【請求項3】

前記ビアホールの側壁に形成され、前記配線層と前記半導体チップとを電気的に絶縁する 側壁絶縁膜を有することを特徴とする請求項1記載の半導体装置。

### 【請求項4】

前記配線層が前記ビアホールに完全に埋め込まれていることを特徴とする請求項1記載の 半導体装置。

### 【請求項5】

前記配線層が前記ビアホールに不完全に埋め込まれていることを特徴とする請求項1記載

10

の半導体装置。

### 【請求項6】

半導体基板の第1の主面に形成されたパッド電極を含む当該第1の主面に支持基板を接着

前記半導体基板の第2の主面の所定領域にホトレジスト層を形成する工程と、

前記ホトレジスト層をマスクとして前記半導体基板に順テーパー形状を有するビアホール を形成する工程と、

前記ビアホールを通して、前記パッド電極と電気的に接続され、かつ前記ビアホールから 前記半導体チップの第2の主面上を延在する配線層を形成する工程と、前記配線層上に導 電端子を形成する工程と、

前記半導体基板を複数の半導体チップに分割する工程と、を具備することを特徴とする半 導体装置の製造方法。

#### 【請求項7】

前記ビアホール形成後に、このビアホールの側壁に、前記配線層と前記半導体基板とを電 気的に絶縁する側壁絶縁膜を形成する工程を有することを特徴とする請求項6記載の半導 体装置の製造方法。

### 【請求項8】

前記配線層を形成する工程は、前記側壁絶縁膜が形成された前記ビアホール内を含む全面 にシード層をスパッタ法により形成し、その後電解メッキ法により配線層を形成する工程 を含むことを特徴とする請求項7記載の半導体装置の製造方法の製造方法。

### 【請求項9】

前記配線層を形成する工程で、この配線層が前記ビアホールに完全に埋め込まれることを 特徴とする請求項6又は請求項8記載の半導体装置の製造方法。

### 【請求項10】

前記配線層を形成する工程で、この配線層が前記ビアホールに不完全に埋め込まれること を特徴とする請求項6又は請求項8記載の半導体装置の製造方法。

### 【請求項11】

半導体基板の第1の主面に形成されたパッド電極を含む当該第1の主面に支持基板を接着 する工程と、

前記半導体基板の第2の主面の所定領域に第1のホトレジスト層を形成する工程と、

前記第1のホトレジスト層をマスクとして前記半導体基板をエッチングすることにより半 導体凸部を形成する工程と、

前記第1のホトレジスト層を除去する工程と、

前記半導体基板の第2の主面の所定領域に第2のホトレジスト層を形成する工程と、

前記第2のホトレジスト層をマスクとして前記半導体基板に順テーパー形状を有するビア ホールを形成する工程と、

前記第2のホトレジスト層を除去する工程と、

前記ビアホールの側壁に側壁絶縁膜を形成する工程と、

前記ビアホール内を含む全面にスパッタ法によりシード層を形成する工程と、

電解メッキにより、前記ビアホールを通して、前記パッド電極と電気的に接続され、かつ 40 前記ビアホールから前記半導体基板の第2の主面上を延在して前記半導体凸部を覆う配線 層を形成する工程と、

前記配線層上に導電端子を形成する工程と、

前記半導体基板を複数の半導体チップに分割する工程と、を具備することを特徴とする半 導体装置の製造方法。

### 【請求項12】

前記配線層を形成する工程で、この配線層が前記ビアホールに完全に埋め込まれることを 特徴とする請求項11記載の半導体装置の製造方法。

#### 【請求項13】

前記配線層を形成する工程で、この配線層が前記ビアホールに不完全に埋め込まれること

10

20

30

50

20

30

40

50

を特徴とする請求項11記載の半導体装置の製造方法。

### 【請求項14】

前記半導体凸部を形成した後に、この半導体凸部の角を丸める工程を有することを特徴とする請求項11記載の半導体装置の製造方法。

#### 【請求項15】

前記ビアホールを形成した後に、前記ビアホールの上縁の角部を丸める工程を有することを特徴とする請求項6又は請求項11記載の半導体装置の製造方法。

### 【発明の詳細な説明】

### [0001]

### 【発明の属する技術分野】

本発明は、複数のボール状の導電端子が配列されたBGA(Ball Grid Array)型の半導体装置及びその製造方法に関するものである。

#### [00002]

### 【従来の技術】

近年、三次元実装技術として、また新たなパッケージ技術として、CSP(Chip Size Package)が注目されている。CSPとは、半導体チップの外形寸法と略同サイズの外形寸法を有する小型パッケージをいう。

### [0003]

従来より、CSPの一種として、BGA型の半導体装置が知られている。このBGA型の半導体装置は、半田等の金属部材からなるボール状の導電端子をパッケージの一主面上に格子状に複数配列し、パッケージの他の面上に搭載される半導体チップと電気的に接続したものである。

### [0004]

そして、この B G A 型の半導体装置を電子機器に組み込む際には、各導電端子をプリント基板上の配線パターンに圧着することで、半導体チップとプリント基板上に搭載される外部回路とを電気的に接続している。

### [0005]

このようなBGA型の半導体装置は、側部に突出したリードピンを有するSOP(Small Outline Package)やQFP(Quad Flat Package)等の他のCSP型の半導体装置に比べて、多数の導電端子を設けることが出来、しかも小型化できるという長所を有する。このBGA型の半導体装置は、例えば携帯電話機に搭載されるデジタルカメラのイメージセンサチップとしての用途がある。

#### [0006]

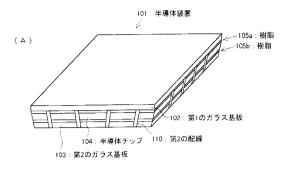

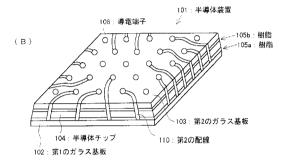

図14は従来のBGA型の半導体装置の概略構成を成すものであり、図14(A)はこのBGA型の半導体装置の表面側の斜視図である。また、図14(B)はこのBGA型の半導体装置の裏面側の斜視図である。

# [0007]

このBGA型の半導体装置101は、第1及び第2のガラス基板102、103の間に半導体チップ104がエポキシ樹脂105a、105bを介して封止されている。第2のガラス基板103の一主面上、即5BGA型の半導体装置101の裏面上には、ボール状の導電端子106が格子状に複数配置されている。この導電端子106は、第2の配線110を介して半導体チップ104へと接続される。複数の第2の配線110には、それぞれ半導体チップ104の内部から引き出されたアルミニウム配線が接続されており、各ボール状の導電端子106と半導体チップ104との電気的接続がなされている。

### [00008]

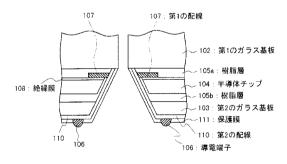

この B G A 型の半導体装置 1 0 1 の断面構造について図 1 5 を参照して更に詳しく説明する。図 1 5 はダイシングラインに沿って、個々のチップに分割された B G A 型の半導体装置 1 0 1 の断面図を示している。

### [0009]

半導体チップ104の表面に配置された絶縁膜108上に第1の配線107が設けられて

いる。この半導体チップ 1 0 4 は樹脂層 1 0 5 a によって第 1 のガラス基板 1 0 2 と接着されている。また、この半導体チップ 1 0 4 の裏面は、樹脂層 1 0 5 b によって第 2 のガラス基板 1 0 3 と接着されている。

### [0010]

そして、第1の配線107の一端は第2の配線110と接続されている。この第2の配線110は、第1の配線107の一端から第2のガラス基板103の表面に延在している。そして、第2のガラス基板103上に延在した第2の配線上には、ボール状の導電端子106が形成されている。

### [0011]

上述した技術は、例えば以下の特許文献1に記載されている。

10

# [0012]

### 【特許文献1】

特表2002-512436号公報

### [0013]

### 【発明が解決しようとする課題】

しかしながら、上述したBGA型の半導体装置101において、第1の配線107と第2の配線110との接触面積が非常に小さいので、この接触部分で断線するおそれがあった。また、第2の配線110のステップカバレージにも問題があった。

#### [0014]

### 【課題を解決するための手段】

20

そこで本発明の半導体装置は、半導体チップの第1の主面にパッド電極が設けられ、半導体チップの第1の主面には支持基板が接着されている。また、半導体チップには順テーパー形状を有するビアホールが形成され、このビアホールを通して、パッド電極と電気的に接続され、かつビアホールから半導体チップの第2の主面上を延在する配線層が設けられている。さらに、配線層と電気的に接続された導電端子とを有することを特徴とするものである。

### [0015]

これにより、半導体チップのパッド電極から、その導電端子に至るまでの配線の断線やステップカバレージの劣化を防止し、信頼性の高い B G A 型の半導体装置を得ることができる。

30

### [0016]

# 【発明の実施の形態】

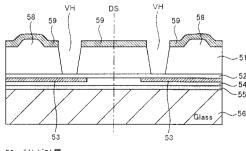

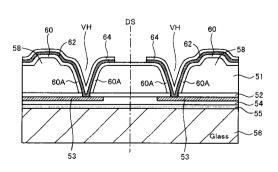

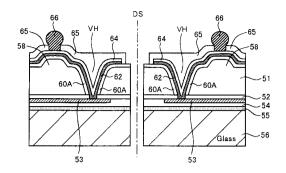

次に、本発明の実施形態について図面を参照しながら詳細に説明する。まず、この半導体装置の構造について説明する。図13はこの半導体装置の断面図であり、後述する工程を経たシリコンウエハーをダイシングライン領域に沿って個々のチップに分割したものを示している。また、図13においてDSはダイシングライン中心である。

### [0017]

シリコンチップ 5 1 A は、例えば C C D イメージセンサ・チップであり、その第 1 の主面である表面には、 B P S G 等の層間絶縁膜 5 2 を介してパッド電極 5 3 が形成されている。このパッド電極 5 3 は、通常のワイヤボンディングに用いられるパッド電極をダイシングライン領域にまで拡張したものであり、拡張パッド電極とも呼ばれる。

40

#### [0018]

このパッド電極 5 3 は、シリコン室化膜等のパッシベーション膜 5 4 で被覆されている。このパッド電極 5 3 が形成されたシリコンチップ 5 1 A の表面には、例えばエポキシ樹脂から成る樹脂層 5 5 を介して、ガラス基板 5 6 が接着されている。ガラス基板 5 6 はシリコンチップ 5 1 A を支持する支持基板として用いられる。シリコンチップ 5 1 A が C C D イメージセンサ・チップの場合には、外部からの光をシリコンチップ 5 1 A の表面の C C D デバイスで受光する必要があるため、ガラス基板 5 6 のような透明基板、もしくは半透明基板を用いる必要がある。シリコンチップ 5 1 A が受光や発光するものでない場合には不透明基板であってもよい。

20

30

40

50

### [0019]

### [0020]

これによって、ガラス基板 5 6 とシリコンチップ 5 1 A の熱膨張係数の差によるガラス基板 5 6 の反りが防止される。シリコンチップ 5 1 A が他の材料の半導体チップである場合にも同様のことが言える。

### [0021]

そして、シリコンチップ51Aの第2の主面である裏面から、パッド電極53に臨むようにこれを貫通するビアホールVHが形成されている。ビアホールVHは順テーパー形状、すなわち、ビアホールVHは底から上方に向けて広がった形状を呈している。

#### [0022]

ビアホール V H の側壁には側壁絶縁膜 6 0 A が形成されている。側壁絶縁膜 6 0 A は後述する配線層 6 4 とシリコンチップ 5 1 A とを電気的に絶縁するものである。

#### [0023]

また、シリコンチップ 5 1 A の裏面には、ビアホールVHと隣接した領域に、シリコン凸部 5 8 が形成されている。シリコン凸部 5 8 は、後述するようにシリコン基板を選択的にエッチングすることで形成され、その高さ h は、シリコンチップ 5 1 A の裏面を基準にして 3 5  $\mu$  m 程度であるが、高いほどプリント基板への実装時に生じる熱応力を緩和するのに有効である。また、シリコン凸部 5 8 の底部の幅 W 1 は 4 0 0  $\mu$  m 程度であり、ハンダボールの径に応じて決められる。シリコン凸部 5 8 の上部の幅 W 2 は 3 4 0  $\mu$  m 程度である。シリコンチップ 5 1 A の厚さは 1 3 5  $\mu$  m 程度である。

### [0024]

そして、シリコンチップ 5 1 A の裏面及びシリコン凸部 5 8 は第 1 の絶縁膜 5 9 によって 覆われている。この第 1 の絶縁膜 5 9 は配線層 6 4 とシリコンチップ 5 1 A とを電気的に 絶縁するものである。

### [0025]

そして、このビアホールVHを通してパッド電極 5 3 に電気的に接続し、かつビアホールVHからシリコンチップ 5 1 A の裏面上を延在する配線層 6 4 が形成されている。配線層 6 4 は、再配線層とも呼ばれるもので、例えば銅(Cu)上に、Ni/Au等のバリアメタルを積層した構造である。配線層 6 4 の下層にはシード層 6 2 が設けられているが、これは配線層 6 4 を電解メッキによって形成する際に用いられるメッキ電極となる金属層である。

### [0026]

なお、 C u 配線のようにシリコンへの拡散傾向の強い金属を使用する場合には C u 拡散によるデバイス特性劣化を防止するため、シード層 6 2 の下にバリア層 ( 例えば、 T i N 層 、 T i W 層 ) を形成する必要がある。配線層 6 4 は、シリコン凸部 5 8 を覆うように、シリコンチップ 5 1 A の裏面上に延びている。

# [0027]

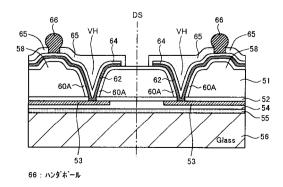

そして、配線層64は保護膜であるソルダーマスク65によって覆われているが、ソルダーマスク65には、シリコン凸部58上の部分に開口部Kが形成されている。このソルダーマスク65の開口部Kを通して、導電端子であるハンダボール66が搭載されている。これにより、ハンダボール66と配線層64とが電気的に接続されている。このようなハンダボール66を複数形成することでBGA構造を得ることができる。

#### [0028]

こうして、シリコンチップ51Aのパッド電極53から、その裏面に形成されたハンダボ

30

40

50

ール66に至るまでの配線が可能となる。また、順テーパー形状を有したビアホールVHを通して配線しているので、配線層64、その下層のシード層62、さらにその下層の側壁絶縁膜60Aのステップカバレージも優れている。特に、ビアホールVHがテーパー形状を有しているので、側壁絶縁膜60A上にシード層62を、スパッタ法を用いて形成できるという利点がある。

#### [0029]

さらに、ハンダボール66は、シリコン凸部58上に配置されているので、その形成位置がシリコンチップ51Aの裏面よりもその分高くなる。これにより、この半導体装置をプリント基板に実装する際に、プリント基板とハンダボール66との熱膨張率の差によって生じる応力によって、ハンダボール66やシリコンチップ51Aが損傷することが防止される。

### [0030]

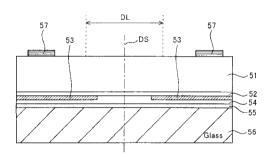

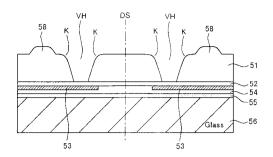

次にこの半導体装置の製造方法について説明する。図1に示すように、シリコンウエハー51の表面には、図示しない半導体集積回路(例えば、CCDイメージセンサ)が形成されているものとする。なお、図1は、後述するダイシング工程で分割される予定の隣接チップの境界の断面を示している。

### [0031]

そのシリコンウエハー51の表面に、BPSG等の層間絶縁膜52を介して、一対のパッド電極53を形成する。この一対のパッド電極53は例えばアルミニウム、アルミニウム合金、銅などの金属層から成り、その厚さは1µm程度である。また、一対のパッド電極53はダイシングライン領域DLに拡張され、その拡張された端部をダイシングライン中心DSの手前に配置している。

### [0032]

そして、一対のパッド電極 5 3 を覆うシリコン窒化膜等のパッシベーション膜 5 4 を形成し、さらにこのパッシベーション膜 5 4 上に、例えばエポキシ樹脂から成る樹脂層 5 5 を塗布する。そして、この樹脂層 5 5 を介して、シリコンウエハー 5 1 の表面にガラス基板 5 6 を接着する。このガラス基板 5 6 はシリコンウエハー 5 1 の保護基板や支持基板として機能する。そして、このガラス基板 5 6 が接着された状態で、必要に応じてシリコンウエハー 5 1 の裏面エッチング、いわゆるバックグラインドを行い、その厚さを 1 5 0  $\mu$  m 程度に加工する。

### [0033]

その後、酸(例えば、HFと硝酸等との混合液)をエッチャントとして用いて20μm程度、シリコンウエハー51をエッチングする。これにより、バックグランドによって生じたシリコンウエハー51の機械的なダメージ層を除去し、シリコンウエハー51の表面に形成されたデバイスの特性を改善するのに有効である。本実施形態では、シリコンウエハー51の最終仕上がりの厚さは130μm程度であるが、これはデバイスの種類に応じて適宜選択することができる。

### [0034]

そして、裏面が削られたシリコンウエハー51の裏面の全面にホトレジストを塗布し、これを露光及び現像することにより、ホトレジスト層57を選択的に形成する。

# [0035]

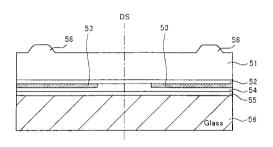

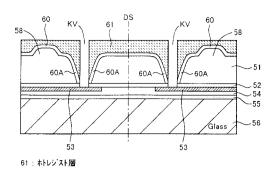

そして、図 2 に示すように、このシリコン凸部 5 8 をマスクにしてシリコンウエハー 5 1 の裏面をエッチングすることにより、シリコン凸部 5 8 を形成する。このエッチングにはスピンエッチャー等を用いたウエットエッチングや、ドライエッチングを用いることができる。シリコン凸部 5 8 の高さ h は、3 5  $\mu$  m程度であるが、これはエッチング量を調整することで任意に変更可能である。

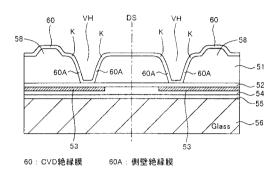

### [0036]

次に、図3に示すように、レジスト剥離液を用いてホトレジスト層57を除去した後に、シリコンウエハー51の裏面を、スピンエッチャー等を用いて、5µm程度ウエットエッチングする。これにより、シリコン凸部58の上縁の角部が丸められ、後述するCVD絶

20

30

40

50

縁膜60の段差被覆性を良好にすることができる。

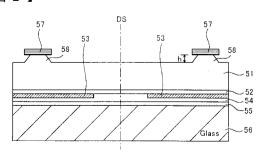

#### [0037]

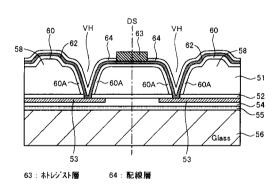

次に、図 4 に示すように、シリコンウエハー 5 1 の裏面上にホトレジスト層 5 9 を選択的に形成し、このホトレジスト層 5 9 をマスクとして、シリコンウエハー 5 1 のエッチングを行い、シリコンウエハー 5 1 を貫通するビアホール V H を形成する。ビアホール V H の幅は、40  $\mu$  m 程度、その長さは 200  $\mu$  m 程度である。

### [0038]

ビアホールVHを形成するには、レーザービームを用いてエッチングする方法やドライエッチングを使用する方法がある。このビアホールVHは、後述するシード層62の被覆性を良くするために、レーザービーム条件やエッチング条件の制御により順テーパー形状に加工される。すなわち、ビアホールVHはその底から上方(シリコンウエハー51の裏面側)に向けて広がった形状を呈している。

## [0039]

次に、図5に示すように、ホトレジスト層59をアッシングやレジスト剥離液を用いて除去した後に、ウエットエッチング(例えば、スピンエッチャーを用いたウエットエッチング)により、シリコンウエハー51の裏面を5µm程度エッチングすることにより、ビアホールVHの上縁の角部Kを丸める処理を施す。

#### [0040]

図6に示すように、ビアホールVHが形成されたシリコンウエハー51の裏面全体にCVD絶縁膜60を形成する。CVD絶縁膜60は、例えばプラズマCVD膜であり、PE-SiO2膜やPE-SiN膜が適している。CVD絶縁膜60はビアホールVHの底部、側壁及びシリコンウエハー51の裏面の全面を被覆するように形成される。CVD絶縁膜60がビアホールVHの側壁を覆う部分が側壁絶縁膜60Aとなる。

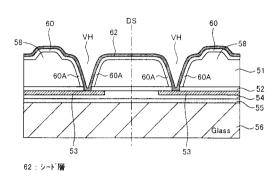

#### [0041]

次に、図7に示すように、ビアホールVHの底部の層間絶縁膜52を露出する開口部 K V が設けられたホトレジスト層61を、ホトリソグラフィ技術を用いて形成し、このホトレジスト層61をマスクとして、ビアホールVHの底部の層間絶縁膜52をウエットエッチングまたはドライエッチングによりエッチングし、その下層にあるパッド電極53を露出させる。なお、テーパー角度が浅ければ、レジストマスク無しでの全面エッチングでパッド電極53を露出させても良い。

# [0042]

次に、配線層64を形成する工程を説明する。図8に示すように、ホトレジスト層61を除去し、その後、バリア層(例えばTiN層)をスパッタ法で形成した後に、更に銅(Cu)から成るシード層62をスパッタ法によって形成する。ビアホールVHは順テーパー形状に加工されているので、バリア層やシード層62はスパッタ法を用いて形成することができる。

### [0043]

このシード層 6 2 は後述する電解メッキ時のメッキ膜成長のためのメッキ電極となる。その厚さは数 1 0 0 n m程度でよい。バリア層は前述と同様に、 C u のシリコンへの拡散を防止するために形成され、その厚さは数 1 0 n mである。

#### [0044]

そして、銅(Cu)の電解メッキを行うが、図9に示すように、その前にメッキを形成しない領域に選択的にホトレジスト層63を形成する。この領域は配線層64及びハンダボール形成領域を除く領域である。そして、銅(Cu)の電解メッキを行い、その銅の表面にニッケル(Ni),金(Au)の無電解メッキを行うことで、ビアホールVH内を不完全又は完全に埋め込む配線層64を形成する。

### [0045]

上記のNi, Auはバリアメタルであり、スパッタ法で形成してもよい。配線層64はビアホールVHからシリコンウエハーの裏面に取り出され、この裏面上を延びて、シリコン

凸部58を覆う。これにより配線層64は、パッド電極53とシード層62を介して電気的に接続される。

### [0046]

この方法は工程削減には良いが、配線層64のメッキの厚さとビアホールVHに成長するメッキ厚さを独立に制御できないので、両者を最適化できないという欠点がある。そこで、ビアホールVH内の配線層64(柱状端子ともいう)については電解メッキで形成し、それ以外の部分の配線層64についてはA1スパッタ法又は電解メッキ法で形成するようにしてもよい。

#### [0047]

次に、図10に示すようにホトレジスト層63を除去する。さらに、配線層64をマスクとして、ホトレジスト層63の下に残存しているシード層62及びバリア層をエッチングにより除去する。このとき、配線層64もエッチングされるが、配線層64はシード層62より厚いので問題はない。なお、ホトレジスト層63をメッキ前に形成して、選択メッキを行う代わりに、全面メッキした後に再配線として残したい領域をホトレジスト層で被覆し、その後、シード層62及びバリア層をエッチング除去しても良い。

#### [0048]

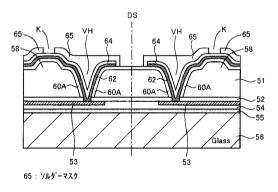

次に、図11に示すように、配線層64上にソルダーマスク65を被着する。ソルダーマスク65のシリコン凸部58上の部分については除去され、開口部Kが設けられている。

#### [0049]

そして、図12に示すように、スクリーン印刷法を用いて、配線層64の所定領域上にハンダを印刷し、このハンダを熱処理でリフローさせることで、ハンダボール66を形成する。なお、配線層64はシリコンウエハー51の裏面の所望領域に、所望の本数を形成することができ、ハンダボール66の数や形成領域も自由に選択できる。

### [0050]

そして、図13に示すように、ダイシングライン中心DSに沿ってダイシング工程を行い、シリコンウエハー51を複数のシリコンチップ51Aに分割する。このダイシング工程では、レーザービームを用いることができる。また、レーザービームを用いたダイシング工程において、ガラス基板56の切断面がテーパー形状となるように加工することにより、ガラス基板56の割れを防止することができる。

### [0051]

なお、上述した実施形態では、通常のワイヤボンディングに用いられるパッド電極をダイシングライン領域 D L まで拡張して成るパッド電極 5 3 を形成しているが、これには限定されず、パッド電極 5 3 の代わりに、ダイシングライン領域 D L まで拡張されない通常のワイヤボンディングに用いられるパッド電極をそのまま利用しても良い。この場合は、ビアホール V H の形成位置をこのパッド電極を合わせれば良く、他の工程は全く同じである

# [0052]

### 【発明の効果】

本発明によれば、半導体チップのパッド電極から、その裏面の導電端子に至るまでの配線の断線やステップカバレージの劣化を防止し、信頼性の高い BGAを有する半導体装置を得ることができる。

### [0053]

また、導電端子は半導体チップの裏面に設けられた半導体凸部上に形成されるので、半導体チップの裏面から高い位置に形成される。これにより、この半導体装置がプリント基板へ実装された時に生じる応力が吸収されやすくなり、導電端子の損傷を極力防止することができる。

### 【図面の簡単な説明】

- 【図1】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図2】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図3】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

40

20

30

50

- 【図4】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図5】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図6】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図7】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図8】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図9】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図10】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図11】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図12】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図13】本発明の実施形態に係る半導体装置の製造方法を説明する断面図である。

- 【図14】従来に係る半導体装置を説明する図である。

- 【図15】従来に係る半導体装置を説明する図である。

# 【図1】

51:シリコンウエハー 52:層間絶縁膜 53:パッド電極 54:パッシベーション膜 55:樹脂層 56:ガラス基板 57:ホトレジスト層

### 【図3】

【図4】

# 【図2】

58:シリコン凸部

59:ホトレジスト層

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

# 【図13】

# 【図14】

# 【図15】

# フロントページの続き

# (56)参考文献 特開2001-060654(JP,A)

特開平03-278539(JP,A) 特開2002-280490(JP,A) 特開平08-213427(JP,A)

特開平10-335337(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 23/12 H01L 21/3205 H01L 23/52