(19) **日本国特許庁(JP)**

## (12)特 許 公 報(B2)

(11)特許番号

特許第5498751号 (P5498751)

(45) 発行日 平成26年5月21日 (2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

(51) Int. Cl.

F I

HO1L 21/768 (2006.01)

HO 1 L 21/90 A HO 1 L 21/90 C

請求項の数 12 (全 32 頁)

(21) 出願番号 特願2009-231131 (P2009-231131)

(22) 出願日 平成21年10月5日 (2009.10.5) (65) 公開番号 特開2011-82231 (P2011-82231A)

(43) 公開日 平成23年4月21日 (2011. 4. 21) 審査請求日 平成24年8月8日 (2012. 8. 8) ||(73)特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

||(74)代理人 100110928

弁理士 速水 進治

(74)代理人 100118544

弁理士 野本 可奈

(74)代理人 100127236

弁理士 天城 聡

(72) 発明者 古谷 晃

神奈川県川崎市中原区下沼部1753番地 NECエレクトロニクス株式会社内

審査官 正山 旭

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程と、 前記凹部内に、前記シード膜よりもめっき成長しにくい導電性膜を形成する工程と、 前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程と

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程と、

前記めっき膜を化学機械研磨して、前記凹部内にのみ前記めっき膜を残す工程と、 前記導電性膜に含まれる金属元素が、前記めっき膜の表面近傍に偏析するように、第二

<u>の熱処理を施す工程と</u>、

を含むことを特徴とする半導体装置の製造方法。

### 【請求項2】

凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程と、 前記凹部内に、前記シード膜よりもめっき成長しにくい導電性膜を形成する工程と、 前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程と

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程と、

を含み、

20

前記凹部内に、前記シード膜よりもめっき成長しにくい導電性膜を形成する工程におい て、

前記凹部内に形成された前記導電性膜は、前記凹部の底部を含む第1領域と、前記凹部 の開口部を含む第2領域とを有し、

前記第1領域における前記導電性膜と、前記第2領域における前記導電性膜とは異なる 材料から形成されることを特徴とする半導体装置の製造方法。

請求項2に記載の半導体装置の製造方法において、

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっ き膜を成長させる工程の後に、

前記めっき膜を化学機械研磨して、前記凹部内にのみ前記めっき膜を残す工程と、

前記導電性膜に含まれる金属元素が、前記めっき膜の表面近傍に偏析するように、第二 の熱処理を施す工程と、

をさらに含むことを特徴とする半導体装置の製造方法。

## 【請求項4】

請求項1乃至3いずれかに記載の半導体装置の製造方法において、

前記凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程は、

前記基板に、前記凹部を形成する工程と、

前記凹部内に前記シード膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

### 【請求項5】

請求項1乃至4いずれかに記載の半導体装置の製造方法において、

前記凹部は、デュアルダマシン法により形成されるデュアルダマシン構造のビアホール および配線溝であって、

前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程は 、前記ビアホールおよび/または前記配線溝の底部の前記シード膜を露出させる工程であ ることを特徴とする半導体装置の製造方法。

#### 【請求項6】

請求項1乃至3いずれかに記載の半導体装置の製造方法において、

前記凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程は、

前記基板上に第一の絶縁層を形成する工程と、

前記第一の絶縁層中にシード膜を埋め込む工程と、

前記第一の絶縁層上に第二の絶縁層を形成する工程と、

前記第二の絶縁層を選択的に除去して前記凹部を形成し、前記凹部の底部に前記シー ド膜を露出させる工程と、

を含むことを特徴とする半導体装置の製造方法。

### 【請求項7】

請求項1乃至5いずれかに記載の半導体装置の製造方法において、

前記凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程は、

前記基板に、前記凹部を形成する工程と、

前記凹部内に絶縁膜を形成する工程と、

前記凹部内の前記絶縁膜上に前記シード膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

## 【請求項8】

請求項1乃至7いずれかに記載の半導体装置の製造方法において、

前記シード膜は、Cuを含むことを特徴とする半導体装置の製造方法。

### 【請求項9】

請求項1乃至8いずれかに記載の半導体装置の製造方法において、

前記導電性膜は、Ta、Ti、Al、Sn、Mn、Ru、またはIrのうち少なくとも 一つを含むことを特徴とする半導体装置の製造方法。

10

20

30

40

## 【請求項10】

請求項1乃至9いずれかに記載の半導体装置の製造方法において、

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程の後に、

前記導電性膜に含まれる金属元素が、前記めっき膜内に拡散するように、第一の熱処理を施す工程、

をさらに含むことを特徴とする半導体装置の製造方法。

## 【請求項11】

請求項1乃至10いずれかに記載の半導体装置の製造方法において、

前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程は、RFバイアス印加を利用して前記導電性膜を除去することを特徴とする半導体装置の製造方法。

### 【請求項12】

請求項1乃至11いずれかに記載の半導体装置の製造方法において、

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程は、

前記めっき膜が前記凹部の開口部上に凸部を形成し、前記凸部の高さが1nm以上100nm以下であることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

#### 【技術分野】

[00001]

本発明は、半導体装置及び半導体装置の製造方法に関する。特に、半導体素子間をつなぐ配線構造およびその製造方法に関する。

#### 【背景技術】

#### [0002]

近年の半導体装置においては配線での信号伝搬の遅延が素子動作を律速している。配線での遅延定数は配線抵抗と配線間容量の積で表される。そこで、配線抵抗を下げて素子動作を高速化するために、配線材料として比抵抗値の小さいCuが用いられている。

#### [0003]

Cu多層配線はダマシン(damascene)法で形成される。ダマシン法は、層間絶縁膜等の絶縁膜の堆積工程、絶縁膜を加工して凹部を形成する工程、バリアメタル堆積工程、Cu 薄膜を電解めっきのカソード電極とした Cu めっき堆積による凹部内部の埋め込み工程、凹部を除く部分に堆積したバリアメタル及び Cu の化学機械研磨(Chemical Mechanical Polishing)による除去工程、およびバリア絶縁膜堆積工程を有する。

## [0004]

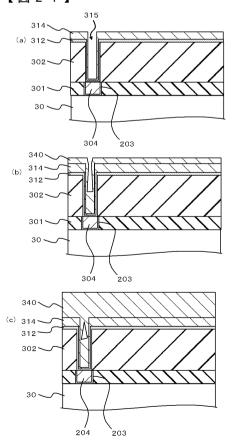

図21は、従来のCu堆積による凹部内部の埋め込み工程を説明する断面図である。図21(a)に示すように、半導体基板30上に、絶縁膜301、絶縁膜302が順に成膜されている。記載は省略しているが、半導体基板30の上面には、トランジスタなどの半導体素子、それらを被覆する層間絶縁膜、半導体素子と配線層をつなぐためのコンタクト、および場合によっては配線層などが形成されている。絶縁膜301の溝内には、バリアメタル膜203とCu配線304が埋設されている。このCu配線304上の絶縁膜302には凹部315が形成されており、凹部315の底面と側面、及び絶縁膜302の表面には、バリアメタル膜312、Cuシード膜314が順に堆積されている。その後、図21(b)に示すように、Cuシード膜314をカソード電極として、Cuシード膜314の表面に、めっき法によってCuの電解めっき膜340を堆積する。図21(b)は、Cuの電解めっき工程の途中状態を表した断面図である。

#### [0005]

Cu多層配線においては、Cu配線中にボイドと呼ばれる空洞が存在すると抵抗上昇や信頼性劣化が生じて半導体装置(チップ)の歩留りが低下する問題が生じてしまう。そこ

10

20

30

40

で、上記のような電解めっきの際に絶縁膜302に形成されている凹部315内部にボイドの無いCu堆積(埋め込み)をすることが重要である。図21(c)は、Cuの電解めっき後、Cu配線中にボイドと呼ばれる空洞が発生した様子を示している。電界めっき成膜は電界強度に影響され、電界強度が強い凹部315の開口部の成膜速度は凹部315の側面に比べて速くなるため、凹部315の底面での成長が十分に速くないとめっき膜が高面から開口部に到達する前に開口部が塞がってしまう。開口部が閉塞されると、凹部315内へのめっき液中の金属イオンの供給がとまり、電界も遮断されるので、底面から成膜されたCuめっき膜の成長は開口部に到着する前に停止し、凹部315内でめっき成膜されなかった部分はボイドとなって残ることとなる。そこで、このボイドの発生を抑制するため、電解めっき液に成膜促進剤及び成膜抑制剤を添加して、凹部315の底面での成度速度を凹部315の開口部及び側面部よりも速くしてCuを埋設する工夫がされている。このめっき方法はボトムアップ埋設、またはスーパーコンフォーマル埋設と呼ばれている

[0006]

ここで、成膜抑制剤には、高分子ポリマーで、例えば、ポリエチレングリコールやポリプロピレングリコールの共重合体が用いられている。また、成膜促進剤には、スルフォン酸ナトリウム塩が用いられている。

[0007]

ボトムアップ埋設の詳細メカニズムは、現在も不明であるが、次のように推定されている。

通常、電解めっき液中には成膜抑制剤と成膜促進剤が含まれている。この電解めっき液中に、凹部の内部と外部にシードが形成された基板を浸漬すると、電解めっき液中の濃度に応じた割合で、成膜抑制剤と成膜促進剤とがシード表面に吸着する。めっき成膜初期においては、凹部内部と外部とで、成膜促進剤の作用に大きな違いは生じない。しかし、めっき成長に伴い、凹部内部の、特にその底部付近では凹部の側面部からのめっき成長もあるため、凹部内部のシードの表面積が小さくなる。一方、シード表面に吸着した成膜促進剤は離脱しないため、凹部内部のシードの表面積の縮小に従い、同部のシード表面における成膜促進剤の密度は大きくなる。この結果、凹部内部での成膜促進効果は相対的に大きくなり、シード上へのめっき成膜速度は凹部内部の方が凹部外部より速くなる。

この現象を利用したのがボトムアップ成長であり、凹部の底部でのめっき成膜速度が凹部開口部及び側面部に比べて十分に速ければ、開口部が閉塞される前に底部から成長しためっき膜が開口部に到着でき、凹部内部のボイド発生を抑制して埋め込むことができる。

[00008]

しかしながら、半導体装置の微細化が進み凹部の開口寸法が小さくなると、従来の電解めっき液では、ボトムアップ成長しにくくなる。これは、開口寸法が小さいために成膜促進剤が凹部の底面で十分に高濃度化しないためである。そのため、凹部の底面から成膜するめっき膜が開口部に到着する前に、開口部で成長しためっき膜により開口部が閉塞されてボイドが形成されてしまうためである。

[0009]

このような問題を解決するため、例えば非特許文献 1 では、めっき液中の C u 、硫酸の高濃度化、めっき抑制剤、平滑化剤の高分子化の手法が開示されている。硫酸の高濃度化により促進剤が活性化され、 C u 高濃度化により析出確率が高くなり、ボトムアップ性が改善されることが開示されている。また、抑制剤、平滑化剤は高分子化することでめっき液中での拡散速度が低下して、めっき成膜初期の凹部内への吸着量が少なくなり、凹部内の促進剤の割合が高くなり、より微細な寸法でもボトムアップ可能となることが開示されている。

[0010]

しかしながら、本発明者の検討によれば以下の問題があることが分かった。

Cu、硫酸の高濃度化は硫酸銅析出によるパーティクルの発生やそれに伴う装置故障のリスクを増大させる。また、めっき抑制剤、平滑化剤は使用中に分解するため長期間使用

10

20

30

40

すると効果が得られなくなる。それを防止するには、頻繁にめっき液を交換せねばならず、コスト増加を招く。更に、凹部内の促進剤の効果を高めただけであり、ボトムアップのメカニズムは同じであるから、より微細な寸法ではボトムアップ成長しなくなる。すなわち、めっき液を改善したとしても、半導体装置の微細化が進むとボトムアップ成長が困難となり、Cuめっき膜中にボイドが形成されるという問題があった。

### [0011]

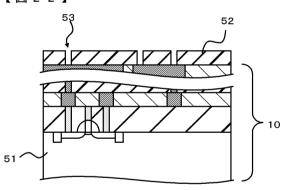

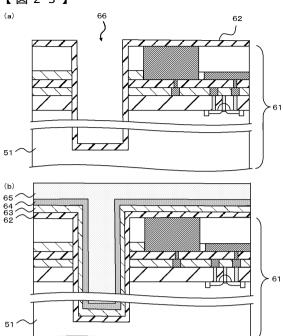

ここで、図22,23を用いて、TSV(Through Silicon Via)構造を用いた半導体装置の問題点について説明する。図22は、従来のダマシン構造による微細パターンを有する半導体装置であって、半導体基板51の素子形成面上にトランジスタ及び多層配線などが形成された基板10の上に、絶縁膜52が形成されている。絶縁膜52は、基板10とは反対側の面に開口した凹部53を有している。図23は、TSV構造を用いた半導体装置であって、半導体基板51の素子形成面上にトランジスタ、多層配線層、及び電極パッドなどが形成された基板61を有している。基板61は、多層配線層を貫通し半導体基板51の内部に達する凹部66を有している。凹部66及び基板61上には、絶縁膜62が形成されている。

#### [0012]

図23に示すようなTSV構造は、従来のダマシン構造による微細パターンに比べて、 大きなパターンであるため、半導体装置の製造工程において、以下のような問題があった

## [0013]

まず図 2 3 ( a ) に示すように、基板 6 1 上に、径が数十 $\mu$  m、高さが数十 $\alpha$  1 0 0  $\mu$  m程度の凹部 6 6 を形成する。つづけて図 2 3 ( b ) に示すように、基板 6 1 上及び凹部 6 6 内に、バリアメタル 6 3、シードとなる C u 膜 6 4 を順に成膜する。その後、 C u 膜 6 4 を電解めっきのカソード電極とした C u めっき成膜によって、凹部 6 6 の内部に C u めっき膜 6 5 を埋め込む。次に、基板 6 1 のフィールド上に形成された、バリアメタル 6 3、 C u 膜 6 4 及び C u めっき膜 6 5 を、 C M P により除去し、凹部 6 6 内だけに C u めっき膜が残った構造にする。また、基板 6 1 の裏面から、凹部 6 6 内の C u めっき膜が露出するまで、 C M P を行う。これにより、基板 6 1 に貫通電極を形成する。

## [0014]

上記 C u めっき成長による C u めっき膜埋込工程では、微細パターンと同様にボトムアップ成長を利用して C u めっき膜 6 5 の埋設を行うが、パターンが大きいためめっき成膜量が多く、高電流による高速成膜が生産能力の確保に必要である点が微細パターンを対象としためっきと異なる。めっき成長を高速化しようとすると、パターン開口での電界強度が強くなって、開口付近での成長がボトムアップの高速化よりも速くなって、開口部で成膜した C u めっき膜 6 5 により開口部が閉塞されてしまうことがあった。そのため、凹部内へのめっき液中の金属イオンの供給がとまるので、底面から成膜された C u めっき膜 6 5 が開口部に到着する前にめっき成長が停止し、凹部 6 6 内でめっき成膜されなかった部分はボイドとなって残り、 C u めっき膜 6 5 埋設不良が発生しやすいという問題があった

## [0015]

このようなボイドの発生といった問題を解決するために、凹部に形成されたシード層を 凹部の底部にのみ残留させてボトムアップさせる技術として特許文献 1 、 2 記載のものが ある。

## [0016]

特許文献1には、基板の上面からシード層を選択的に除去し、フィーチャ(特許文献1に記載された表現であり、溝を意味する)の少なくとも底面にだけシード層を残し、シード層の部分を使用して金属を電気めっきし、金属がフィーチャを埋める技術が開示されている。また特許文献2には、配線溝の底面に残留する導電層の上に金属膜を形成する技術が開示されている。

## [0017]

10

20

30

なお、従来のダマシン構造を有する半導体装置の電解めっきに関連する技術としては、 特許文献3~6記載のものがある。

### 【先行技術文献】

## 【特許文献】

## [0018]

【特許文献1】特開2002-020891号公報

【特許文献2】特開2004-214508号公報

【特許文献3】特開2007-149824号公報

【特許文献4】特開2005-333153号公報

【特許文献 5 】特開 2 0 0 1 - 1 4 4 1 8 1 号公報

【特許文献 6 】特開 2 0 0 2 - 1 1 8 1 0 9 号公報

#### 【非特許文献】

#### [0019]

【非特許文献1】Jon Reid and Jian Zhou, "Electro fill Challenges and Directions for Future Device Generations", Advanced Metallization Conference 2007:17/Asia Session

#### 【発明の概要】

【発明が解決しようとする課題】

## [0020]

しかしながら、発明者の検討によれば上記特許文献1、2に開示された技術を適用した 場合、以下のような問題が存在することが分かった。

## [0021]

特許文献1,2に開示された技術では、シード層を凹部の底面にのみ形成するために、凹部の側面に形成したシード膜を電解研磨やCMP法により除去している。そのため、シード層のCu表面がCMP等に含まれる防食材で汚染される場合がある。また、凹部の側面のシード層の除去が十分でなかったり、均一に除去できない場合があった。そのため、ボイドの発生を十分に抑制できない場合があった。

### [0022]

したがって、いずれの特許文献に記載された技術によっても、めっき埋め込みの際に発生するボイドを充分抑制することはできなかった。

【課題を解決するための手段】

### [0023]

本発明によれば、

凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程と、 前記凹部内に、前記シード膜よりもめっき成長しにくい導電性膜を形成する工程と、 前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程と

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程と、

を含むことを特徴とする半導体装置の製造方法が提供される。

#### [0024]

また、本発明によれば、

基板と、

前記基板に埋設された導電体と、

## を備え、

前記導電体は、前記導電体の側面部から中心部に向かって1 n m 以上2 0 n m 以下の領域で、前記導電体の構成元素以外の金属元素濃度の値が最大となることを特徴とする半導体装置が提供される。

## [0025]

10

20

30

40

本発明は、基板の凹部をめっき成長により埋め込む際に、凹部の内部にボイドが発生す るのを抑制することができるものである。そこで、本発明は、まず凹部の底部にシード膜 が露出した基板を用い、次に凹部内の底部及び側面部に、シード膜よりめっき成長しにく い導電性膜を形成し、その後に、底部の導電性膜を除去することによって底部にシード膜 を露出させている。このように凹部の底部にシード膜、側面部にシード膜よりめっき成長 しにくい導電性膜とした状態で電解めっきすると、側面部よりも底部のシード膜が優先し てめっき成長するため、底部からめっき膜を成長させて凹部内を埋め込むことができる。 これにより、めっき膜成長時に凹部の内部にボイドが発生することを抑制できる。

## 【発明の効果】

[0026]

10

本発明によれば、ボイド発生が低減された半導体装置および半導体装置の製造方法が実 現できる。

#### 【図面の簡単な説明】

[0027]

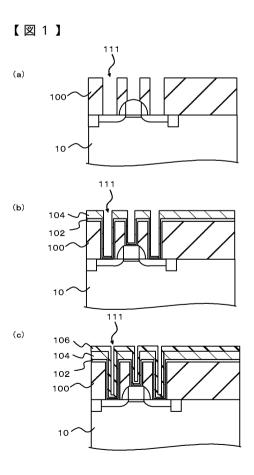

- 【図1】第1の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

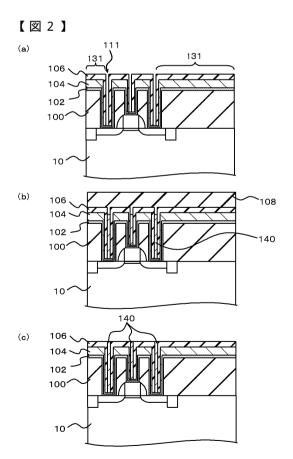

- 【図2】第1の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図3】第1の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図4】(a)は、本実施形態に係る半導体装置の製造工程の一例を示す断面図、(b) は、本実施形態に係る半導体装置の製造工程の効果を説明するための断面図である。

- 【図5】第2の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図6】第2の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図7】第2の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図8】第3の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図9】第4の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図10】第4の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図11】第4の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図12】第5の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図13】第5の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図14】第5の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図15】第6の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図16】第6の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図17】第6の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図18】第7の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図19】第7の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

- 【図20】本実施形態に係る半導体装置の変形例を示す断面図である。

- 【図21】従来のCu堆積による凹部内部の埋め込み工程を説明する断面図である。

- 【図22】従来の半導体装置の一例を示す断面図である。

- 【図23】従来の半導体装置の一例を示す断面図である。

## 【発明を実施するための形態】

## [0028]

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面におい て、同様な構成要素には同様の符号を付し、適宜説明を省略する。なお、本実施の形態で は図示するように前後左右上下の方向を規定して説明する。しかし、これは構成要素の相 対関係を簡単に説明するために便宜的に規定するものである。従って、本発明を実施する 製品の製造時や使用時の方向を限定するものではない。なお、以下特に断らない限り絶縁 膜、バリアメタル膜、シード膜、カバーメタル膜、キャップ膜、めっき膜は単層膜に限ら ず多層膜であってもよい。

## [0029]

(第1の実施形態)

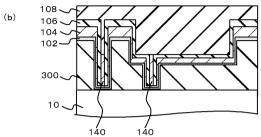

図1~3は、第1の実施形態に係る半導体装置の製造工程の一例を示す断面図である。

20

30

40

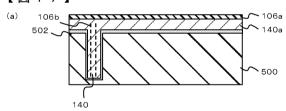

図4の(a)は、本実施形態に係る半導体装置の製造工程の一例を示す断面図、(b)は、本実施形態に係る半導体装置の製造工程の効果を説明するための断面図である。

### [0030]

図1~図4を参照しつつ、第1の実施形態に係る半導体装置の製造工程の一例について 説明する。

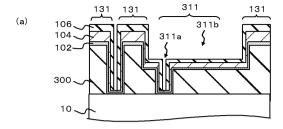

まず、半導体装置の製造方法は、表面にトランジスタ等の素子が形成された半導体基板10の上に形成されている絶縁膜100に凹部111を形成する工程と、凹部111内にバリアメタル膜102とシード膜104を形成する工程と、凹部111内に、カバーメタル膜106を形成する工程と、カバーメタル膜106を選択的に除去して、凹部111の底部にシード膜104を露出させる工程と、凹部111の底部に露出されたシード膜104をシードとして、凹部111内を埋め込むめっき膜140を成長させる工程と、を含む。以下、詳細に説明する。

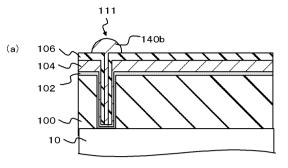

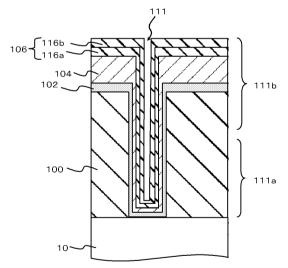

### [0031]

図1(a)に示すように、半導体基板10上に、絶縁膜100を形成し、絶縁膜100 上に凹部111を形成する。半導体基板10上には、例えばソース・ドレイン領域として 機能する拡散層とゲート電極とを有する電界効果トランジスタ(FET)が形成されている。

## [0032]

図1(b)に示すように、絶縁膜100及び凹部111上に、バリアメタル膜102とシード膜104を順に形成する。バリアメタル膜102、シード膜104の形成には、例えば、スパッタ成膜法のような物理気相成長法、CVD(Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法のような化学気相成長法、液相成長法、超臨界流体成長法を用いてもよい。但し、凹部111の開口部でなるべく厚膜化しない条件での成膜が好ましい。

#### [0033]

図1(c)に示すように、シード膜104上に、カバーメタル膜106を形成する。カバーメタル膜106は、例えば、イオン化スパッタ成膜法を用いて、凹部111の底部及び側面部、及び絶縁膜100上に形成される。このとき、凹部111の底部に形成されるカバーメタル膜106よりも薄くなっている。

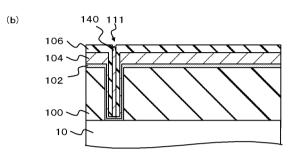

## [0034]

図2(a)に示すように、選択的エッチングをおこなうことにより、凹部111の底部 のカバーメタル膜106を除去して、底部にシード膜104を露出する。選択的エッチン グの手法としては、例えばRFバイアスを印加する等の手法を用いて、プラズマから凹部 111の底部へ向かうイオンを加速させる等して、凹部111の底部のカバーメタル膜1 06を除去し、凹部111の側面部と、絶縁膜100上の凹部111以外の領域(フィー ルド部131)に形成されたシード膜104の上面に、カバーメタル膜106を残留させ る。フィールド上に較べて溝内部の膜厚は薄くなるので、エッチング時間の制御によって 、このような構造は容易に作ることができる。溝フィールド上になお、カバーメタル膜1 0 6 の除去は、底部の少なくとも一部にシード膜104を露出させればよく、凹部111 の底部にあるカバーメタル膜106を完全に除去しなくてもよい。また、凹部111の底 部に限らず、底部近傍、例えば底面から最大でアスペクト比1の領域のカバーメタル膜1 06を除去してもよい。これにより、凹部111を有し、凹部111の底部にシード膜1 04が露出した構造が得られる。なお、最適な形状のカバーメタル膜106を得るために カバーメタル膜106の成膜と選択的エッチングを繰り返してもよい。また選択的エッ チングには溶液を用いたウェットエッチングも可能である。エッチング溶液は、Cuシー ド膜とバリアメタル膜とのエッチングの選択比や電池効果の影響を考慮して選択され、例 えばTiの場合、弗化水素酸やアンモニア過酸化水素溶液を用いることができる。このよ うなウェットエッチングは、以下に説明する他の実施形態においても同様にして適用でき る。

10

20

30

#### [0035]

本実施形態において、バリアメタル膜102には、例えばTaN上にTaを積層した材料を用いる。また、バリアメタル膜102は、1~20nmの厚さに成膜される。

## [0036]

本実施形態において、シード膜104には、例えばCuを材料として用いる。また、シード膜104は、10~100nmの厚さに成膜される。

#### [0037]

本実施形態において、カバーメタル膜106は、シード膜104よりもめっき成長しに くい導電性膜である。

## [0038]

本実施形態において、カバーメタル膜106の材料として、Tiが用いられている。また、カバーメタル膜106は、絶縁膜100上のフィールド部131に0.5~10nmの厚さ、凹部111の側面部に0.5~5nmの厚さに成膜される。カバーメタル膜106の厚さは、凹部111の側面部及びシード膜104上面のフィールド部131のいずれにおいても、0.5~1原子層程度またはそれ以上が好ましい。これにより、後述するめっき成長工程において、凹部111の側面部及びシード膜104上面のフィールド部131におけるめっき成長を抑制でき、ボイドの発生を低減できる。

### [0039]

次に、電解めっき液108を用いて、めっきを行う。図2(b)、(c)に示すように、凹部111の底部に露出されたシード膜104をシードとして、めっき膜140を成長させて、凹部111内を埋め込む。

#### [0040]

めっきの電流密度は、例えば、0.1 A / d m <sup>2</sup> ~ 1 0 A / d m <sup>2</sup> 程度が好ましい。但し、カバーメタル膜 1 0 6 の材料によっては、電流密度を高くするとカバーメタル膜 1 0 6 上にもめっき成長が生じることになる。しかしこの場合であっても、当業者が適宜最適化できる。また電流値は、電流密度と、ウエハ面積に対する凹部 1 1 1 の開口率との積で表される。

## [0041]

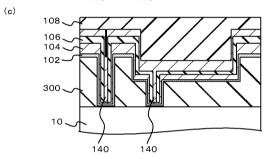

凹部111の底部に露出されたシード膜104をシードとして、めっき膜140を成長させて、凹部111内を埋め込むめっき膜140を成長させる工程は、めっき膜140が凹部111の開口部上に凸部を形成し、凸部の高さが1nm以上100nm以下であるめっき膜140 b としてもよい(図4(a)参照)。これにより、後に行う第一の熱処理によって、凹部111内にめっき成長しためっき膜140が熱収縮して、凹部111内に空間が生じるのを防止できる(図4(b)参照)。

## [0042]

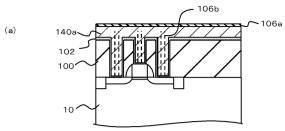

次に、カバーメタル膜106に含まれる金属元素が、めっき膜140内に拡散するように、第一の熱処理を施す。そこで、シード膜104とめっき膜140は再結晶化により一体化し、めっき膜140aとなる。また、カバーメタル膜106に含まれるTiが、めっき膜140a中に拡散し、めっき膜140aの表面に、キャップ膜106aが形成される(図3(a)参照)。さらに、カバーメタル膜106を構成する元素濃度が周辺の元素よりも高い領域106bが形成される。本実施形態において、領域106bはTi濃度が周辺のTi濃度よりも高い。

## [0043]

第一の熱処理は、例えば、100 ~400 に加熱して行われる。また、熱処理中にシード膜104の表面にアンモニアまたは窒素の雰囲気のプラズマを照射してもよい。これにより、Tiをより均一に拡散できる。

### [0044]

図3(b)に示すように、キャップ膜106a、めっき膜140a、及びバリアメタル膜102を、CMP法により選択的に除去して表面を平坦化し、凹部111内のみにめっき膜140aを残す。これにより、絶縁膜100中に、Cu配線105が形成される。

10

20

30

40

10

20

30

40

50

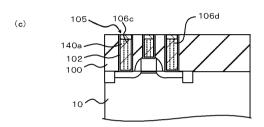

#### [0045]

次に、カバーメタル膜106に含まれる金属元素が、凹部111内のみに残されためっき膜140a(Cu配線105)の表面近傍に偏析するように、第二の熱処理を施す。これにより、Cu配線105中に微量に残留したカバーメタル膜106のTiなどの原子は、Cu配線105の表面に偏析し、キャップ膜106cが形成される(図3(c))。キャップ膜106cは、Cu配線105よりもCu濃度が低く、またCu配線105の上面を覆っている。

## [0046]

また、カバーメタル膜106のTiはより均一に拡散する。図3(c)に示すように、 領域106bのカバーメタル膜106を構成する元素濃度はさらに低くなり領域106d となる。なお、領域106dは、カバーメタル膜106を構成する元素濃度が周辺の元素 よりも高い領域である。

#### [0047]

半導体基板 1 0 上にトランジスタ等の素子と配線構造を形成し図 3 (b)のような構造を形成した後に行う第二の熱処理は、例えば、1 0 0 ~ 4 0 0 で行われる。

#### [0048]

キャップ膜106cは、シード膜104よりもCuが少なく、Ti、A1、Sn、またはMnのうち少なくとも一つを含むものであればよい。

#### [0049]

第一、及び第二の熱処理雰囲気は、酸素や水分を含む雰囲気で行ってもよい。これにより、めっき膜140aの表面に酸化物を形成し、カバーメタル膜106に含まれる金属元素のめっき膜140a中への拡散を促進できる。また、カバーメタル膜106に含まれる金属がTiである場合、アンモニアや窒素を含む雰囲気で行うと、上記の効果が得られるだけでなくさらに、めっき膜140aの表面にTiNが偏析され易くなり、信頼性が向上できる。さらに、熱処理中にめっき膜140aの表面に、これらの雰囲気のプラズマを照射してもよい。

## [0050]

このようにして、トランジスタなどが形成された半導体基板10と、その上に形成された絶縁膜100中に埋設されたCu配線105と、を備え、Cu配線105は、Cu配線105の側面部から中心部に向かって1nm以上20nm以下の領域で、Cu以外の金属元素濃度の値が最大となり、また、半導体基板10と、Cu配線105の側面部との間にバリアメタル膜102を有する半導体装置が得られる(図3(c))。

## [0051]

Cu配線105においては、Cu配線105の側面部から中心部に向かって1nm以上20nm以下の領域で、Cu以外の金属元素濃度の値が最大となる。

### [0052]

次に、本実施形態の作用及び効果を説明する。

## [0053]

本実施形態において、まずトランジスタなどが形成された半導体基板10上に絶縁膜100を形成し、その絶縁膜100に凹部111を形成し、凹部111内にシード膜104、カバーメタル膜106(シード膜よりめっき成長しにくい導電性膜)を順に形成したあと、凹部111底部のカバーメタル膜106を除去することによって、凹部111の底部にシード膜104を露出させている。このように凹部111の底部にシード膜104、側面部にカバーメタル膜106とした状態で電解めっきすると、側面部よりも底部のシード膜104が優先してめっき成長するため、底部からめっき膜140を成長させて凹部111内を埋め込むことができる。これにより、めっき膜140成長時に凹部111の内部にボイドが発生するのを抑制できる。

### [0054]

カバーメタル膜 1 0 6 が、シード膜 1 0 4 よりもめっき成長しにくい理由としては、以下のように考えられる。

10

20

30

40

50

#### [0055]

第一に、カバーメタル膜106がシード膜104よりも抵抗が高い金属を含むことにより、凹部111の側面部のカバーメタル膜106に対して、シード膜104へ優先的に電流が流れ優先的にめっき成長できるためである。

## [0056]

第二に、カバーメタル膜106としてTiを用いた場合、カバーメタル膜106の表面が酸化されるため還元反応が進行しにくくなり、シード膜104が優先的にめっき成長できるためである。

## [0057]

したがって、電解めっきによってめっき膜140をめっき成長させる際、凹部111の側面部よりも底部に露出したシード膜104から優先的にめっき成長されるようになり、凹部111の内部でのボイドの発生が抑制できる。このため、凹部111の開口部が微細であっても、ボトムアップ成膜をすることができる。

## [0058]

また本実施形態においてカバーメタル膜106は、Tiを主成分としている。そのため、上記第二の理由により、カバーメタル膜106上でのめっき成長がより抑制できる。

#### [0059]

また従来技術では、基板上の凹部の底部にのみシード膜を残すために、凹部を有する基板上にシード膜を形成した後電解めっき工程前に、凹部内の側面に形成されたシード膜だけでなく、基板の上面に形成されたシード膜もCMP法などにより取り除く工程を要した。そのため、工程数が追加することとなりコスト増加や生産性の劣化を招いた。これに対し、本実施形態では、電解めっき工程前に、シード膜104を除去する工程を必要としない。

#### [0060]

さらに、本実施形態では、シード膜104上のフィールド部131にも、カバーメタル膜106が形成される。そのため、フィールド部131上はめっき成長による成膜が殆どない。これにより、凹部111でめっき成長させることができ、電解めっき後のCMP工程で、フィールド部131に成長しためっき膜140を除去する時間が短縮できる。従来技術では、このようなCMP工程は半導体装置の製造工程において特に時間を費やすが、本実施形態ではフィールド部131上に成膜されるめっき膜140を制限できるため、CMP工程に費やす時間を短縮し、半導体装置の製造時間を短縮することにより生産性を向上させると同時に、CMP研磨剤の使用量を削減してコストも削減できる。

#### [0061]

なお、フィールド部 1 3 1 上に形成されたカバーメタル膜 1 0 6 にはばらつきがあるため、部分的にめっき膜 1 4 0 が形成される場合もあるが、この場合でも本実施形態ではフィールド部 1 3 1 上に成膜されるめっき膜 1 4 0 を制限できるため、半導体装置の製造時間を短縮して生産性を向上させることができる。

## [0062]

また、非特許文献に示されるように従来の手法では、分子量の大きな Cu めっき添加剤を要し、その分解消耗による性能劣化を防ぐためにめっき液を頻繁に交換する必要があるため、コストが増加していた。これに対し、本実施形態では特別な添加剤を用いる必要がないため、低コスト化が実現できる。

## [0063]

また、半導体装置は、凹部111内のCu配線105の表面にキャップ膜106cを有する。これにより、Cu配線105の信頼性を向上させることができる。

## [0064]

さらに、本実施形態の他の効果について、図4を用いて説明する。

#### [0065]

図4(a)に示すように、本実施形態では、凹部111上にめっき成長して半球状の凸部を有するめっき膜140bが形成されてもよい。この理由としては、基板上に複数の凹

部111が形成される場合、凹部111の基板面内での位置や、互いの位置関係が異なるため、めっき成長による埋込が速い凹部111と、遅い凹部111とが存在する。そのため、遅い凹部111の埋込が完了したときには、埋込が速い凹部111では凹部111内部以外の領域にもめっき成長し、凹部111上に凸部を有するめっき膜140bが形成され、その一部がフィールド部131上にも形成されることとなる。一方、凹部111内部にのみめっき膜140の埋込をおこなうと、その後熱処理によって、図4(b)に示すように、凹部111の開口部周辺でめっき膜140が収縮する場合がある。

## [0066]

そこで、凹部111上に半球状の凸部を有するめっき膜140bが形成されることにより、凹部111開口部周辺において熱処理によるめっき膜140の収縮を抑制することができる。

[0067]

上記実施形態では、バリアメタル膜102としてTaN上にTaを積層した材料を用いた場合について説明したが、Ti、Ru、Ir、W、これらを含む金属、及びこれらのうち少なくとも2種以上からなる積層物であってもよい。

[0068]

(第2の実施形態)

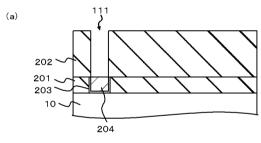

第1の実施形態は、凹部111を有し、凹部111の底部にシード膜104が露出した基板を準備する工程が、凹部111を形成し、凹部111内にシード膜104を堆積した例であるのに対し、第2の実施形態は、凹部111形成前にシード膜204を形成し、凹部111内にシード膜を堆積する工程を含まない例である。

[0069]

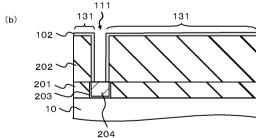

図5~7を参照して、第2の実施形態に係る半導体装置の製造工程の一例について説明する。

本実施形態では、半導体装置の製造方法は、半導体基板10上に絶縁膜201(第一の絶縁膜)を形成する工程と、絶縁膜201(第一の絶縁膜)に形成した溝中にシード膜204を埋め込む工程と、絶縁膜201(第一の絶縁膜)上に絶縁膜202(第二の絶縁膜)を選択的に除去して凹部111を形成し、凹部111の底部にシード膜204を露出する工程と、凹部111内に、カバーメタル膜106を形成する工程と、カバーメタル膜106を選択的に除去して、凹部111の底部にシード膜204を露出させる工程と、凹部111の底部に露出されたシード膜204をシードとして、めっき膜240を成長させて、凹部111内を埋め込むめっき膜240を成長させる工程と、を含む。以下、詳細に説明する。

[0070]

図5(a)に示すように、半導体基板10上に絶縁膜201を形成する。記載は省略しているが、半導体基板10の上面には、トランジスタなどの半導体素子、それらを被覆する層間絶縁膜、半導体素子と配線層をつなぐためのコンタクト、および場合によっては配線層などが形成されている。つづけて、絶縁膜201に配線溝を形成しその中にバリアメタル膜203、シード膜204を順に埋め込む。つづけて、絶縁膜201上に絶縁膜202を形成する。次に、絶縁膜202を選択的に除去して凹部111を形成し、凹部111の底部にシード膜204を露出させる。これにより、凹部111を有し、凹部111の底部にシード膜204が露出した構造が得られる。

[0071]

本実施形態においてシード膜204は、下層の配線層のCu配線、またはビア層のCu ビア等であってもよい。

[0072]

次に、図5(b)に示すように、絶縁膜202及びシード膜204上に、バリアメタル膜102を形成する。バリアメタル膜102の形成には、例えば、スパッタ成膜法のような物理気相成長法、CVD法やALD法のような化学気相成長法、液相成長法、超臨界流体成長法を用いてもよい。但し、凹部111の開口部でなるべく厚膜化しない条件での成

10

20

30

40

膜が好ましい。

## [0073]

つづけて、選択的エッチングをおこなうことにより、凹部111の底部のバリアメタル膜102を除去して、シード膜204を露出する(図5(b))。このとき、例えばRFバイアスを印加する等の手法を用いて、プラズマから凹部111の底部へ向かうイオンを加速させる等して、凹部111の底部のバリアメタル膜102を除去し、凹部111の側面部と、絶縁膜202上の凹部111以外の領域(フィールド部131)にバリアメタル膜102を残留させる。

## [0074]

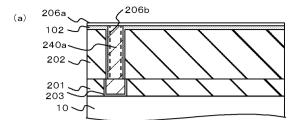

図5 (c)に示すように、バリアメタル膜102上に、カバーメタル膜206を形成する。カバーメタル膜206は、例えば、イオン化スパッタ成膜法を用いて、凹部111の底部及び側面部、及びバリアメタル膜102の上面に形成される。

#### [0075]

図6(a)に示すように、選択的エッチングをおこなうことにより、凹部111の底部のカバーメタル膜206を除去して、シード膜204を露出する。このとき、例えばRFバイアスを印加する等の手法を用いて、プラズマから凹部111の底部へ向かうイオンを加速させる等して、凹部111の底部のカバーメタル膜206を除去し、凹部111の側面部と、絶縁膜202の凹部111以外の領域(フィールド部131)にカバーメタル膜206を残留させる。

## [0076]

本実施形態において、バリアメタル膜 1 0 2 には、例えばルテニウム(Ru)を主に含む材料が用いられる。また、バリアメタル膜 1 0 2 は、例えば絶縁膜 2 0 2 上のフィールド部 1 3 1 に 1 ~ 1 0 n m の厚さ、凹部 1 1 1 の側面部に 0 . 5 ~ 1 n m の厚さに成膜される。

## [0077]

本実施形態において、カバーメタル膜 2 0 6 は、シード膜 2 0 4 よりもめっき成長しにくい導電性膜である。カバーメタル膜 2 0 6 としては、例えばアルミニウム(A 1 )を材料として用いられる。カバーメタル膜 2 0 6 は、例えば絶縁膜 2 2 1 上のフィールド部 1 3 1 に 1 ~ 1 0 n m の厚さ、凹部 1 1 1 の側面部に 0 . 5 ~ 1 n m の厚さに成膜される。

## [0078]

次に上記実施形態で図 2 ( b )、( c )を用いて説明したのと同様にして、まず凹部 1 1 0 底部に露出したシード膜 2 0 4 をシードとして、電解めっき液 1 0 8 を用いて、めっきを行い、めっき膜 2 4 0 を成長させる(図 6 ( b ) )。これにより、凹部 1 1 1 0 底部から、シード膜 2 0 4 上にめっき膜 2 4 0 を選択成長させ、凹部 1 1 1 内にめっき膜 2 4 0 を埋め込むことができる(図 6 ( c ) )。

## [0079]

その後の工程は、上記実施形態と同様である。

まず、第一の熱処理を行う。そこで、シード膜204とめっき膜240は再結晶化により一体化し、めっき膜240aとなる。また、カバーメタル膜206に含まれるA1などの構成元素がめっき膜240a中に拡散し、キャップ膜206aが形成される(図7(a)参照)。さらに、カバーメタル膜106を構成する元素濃度が周辺の元素よりも高い領域206bが形成される。その後、キャップ膜206a、バリアメタル膜102およびめっき膜240aを、CMP法により選択的に除去して表面を平坦化し、Cu配線205を形成する(図7(b))。

## [080]

さらに第二の熱処理を行ってCu配線205の表面への偏析を行い、キャップ膜206 cを形成する(図7(c))。また、カバーメタル膜206を構成する元素濃度はより均一に拡散する。図7(c)に示すように、領域206bのカバーメタル膜206を構成する元素濃度はさらに低くなり、領域206dとなる。なお、領域206bは、カバーメタル膜206を構成する元素濃度が周辺の元素よりも高い領域である。 10

20

30

40

#### [0081]

本実施形態における効果を説明する。

本実施形態では、絶縁膜200はシード膜204を有しており、この絶縁膜200上に絶縁膜202を形成し、絶縁膜202に凹部111を形成する際にその底部にシード膜204を露出させている。そこで、露出させたシード膜204をシードとして利用して、めっき膜240を成長させるため、凹部111形成後にシード膜を形成する工程を要さない。また、シード膜204として、下層の配線層のCu配線、またはビア層のCuビア等を用いることができるため、あえてシード膜204を形成しなくてもよい。したがって、第2の実施形態では、シード膜204形成による工程増加がなく、凹部111形成後のシード膜形成工程が省略されるため、工程数が第1の実施形態よりも削減される。

[0082]

また、従来の技術では、A1をシードとして用いた場合その後のCuめっきでフィールド上のA1にもCuめっき膜が成膜されるため、フィールド上に形成されたCuめっき膜を除去しなければならないのに対し、本実施形態ではフィールド部131上にはカバーメタル膜206が形成されているためめっき膜240がめっき成長しにくい。そのため、本実施形態では、フィールド部131上にめっき成長しためっき膜240を除去する工程を省略または簡略化できる。

[0083]

また、本発明者によれば、A1をシードとして用いた場合、めっき成長核形成のために従来のCuめっき埋め込みで使用していない特別な添加剤を要する。しかし、本実施形態では特別な添加剤を用いることなくめっきすることができ、低コスト化が可能となる。

その他の効果は、上記第1の実施形態と同様である。

[0084]

なお、本発明は上記実施形態に限定されるものではなく、様々な変形が可能である。例えば本実施形態では、凹部111の底部に形成されたバリアメタル膜102を除去した後に、カバーメタル膜206を形成し、凹部111の底部に形成されたカバーメタル膜206を除去する例について説明したが、凹部111底部に形成されたバリアメタル膜102を除去せずにカバーメタル膜206を形成した後、凹部111の底部においてバリアメタル膜102およびカバーメタル膜206を同時に除去してもよい。

[0085]

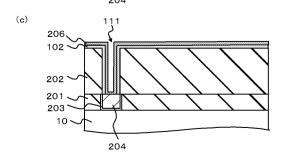

(第3の実施形態)

第2の実施形態は、シード膜204よりもめっき成長しにくい導電性膜としてカバーメタル膜206、およびバリアメタル膜102を用いた例について説明したのに対し、第3の実施形態は、バリアメタル膜兼カバーメタル膜107を用いた例である。

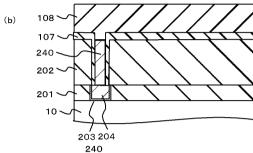

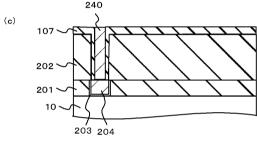

[0086]

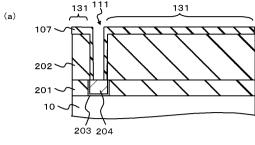

図8を参照して、第3の実施形態に係る半導体装置の製造工程の一例について説明する

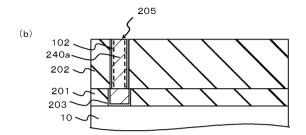

半導体基板10上の絶縁膜201(第一の絶縁膜)には、バリアメタル膜203、シード膜204が順に埋め込まれている。記載は省略しているが、半導体基板10の上面には、トランジスタなどの半導体素子、それらを被覆する層間絶縁膜、半導体素子と配線層をつなぐためのコンタクト、および場合によっては配線層などが形成されている。絶縁膜201上に絶縁膜202(第二の絶縁膜)を形成し、絶縁膜202上に凹部111を形成する。

[0087]

次に、図8(a)に示すように、絶縁膜202及びシード膜204上に、バリアメタル膜兼カバーメタル膜107を形成する。バリアメタル膜兼カバーメタル膜107の形成には、例えば、スパッタ成膜法のような物理気相成長法、CVD法やALD法のような化学気相成長法、液相成長法、超臨界流体成長法を用いてもよい。但し、凹部111の開口部でなるべく厚膜化しない条件での成膜が好ましい。

[0088]

10

20

30

つづけて、選択的エッチングをおこなうことにより、凹部111の底部のバリアメタル膜兼カバーメタル膜107を除去して、シード膜204を露出する。このとき、例えばRFバイアスを印加する等の手法を用いて、プラズマから凹部111の底部へ向かうイオンを加速させる等して、凹部111の底部のバリアメタル膜兼カバーメタル膜107を除去し、凹部111の側面部と、絶縁膜202上の凹部111以外の領域(フィールド部131)にバリアメタル膜兼カバーメタル膜107を残留させる。

#### [0089]

本実施形態において、バリアメタル膜兼カバーメタル膜107は、シード膜204よりもめっき成長しにくい導電性膜であり、かつバリアメタル膜としての機能を有しつつ、Cuとの密着性を良好にする。これにより半導体装置の信頼性を向上できる。またさらに、バリアメタル膜兼カバーメタル膜107により電解めっきの際に凹部111内に電流を流すことができる。

### [0090]

本実施形態において、バリアメタル膜兼カバーメタル膜107の材料としては、100~400 程度の温度でCu中に拡散しない材料が好ましく、例えば、ルテニウム(Ru)を主に含む材料が用いられる。また、バリアメタル膜兼カバーメタル膜107は、絶縁膜202上のフィールド部131に0.5~10nmの厚さ、凹部111の側面部に0.5~5nmの厚さに成膜される。

## [0091]

次に、上記実施形態で図2(b)、(c)を用いて説明したのと同様にして、まず凹部111の底部に露出したシード膜204をシードとして、電解めっき液108を用いて、めっきを行いめっき膜240を成長させる(図8(b))。これにより、凹部111の底部から、シード膜204上にめっき膜240を選択成長させ、凹部111内にめっき膜240を埋め込むことができる(図8(c))。

#### [0092]

その後の工程は、通常のダマシン配線と同様である。まず熱処理を行い、シード膜204とめっき膜240を再結晶化して一体化させる。その後、バリアメタル膜兼カバーメタル膜107、めっき膜240をCMP法により選択的に除去して表面を平坦化してCu配線を形成し、半導体装置を得る。

## [0093]

本実施形態における効果を説明する。

本実施形態では、バリアメタル膜兼カバーメタル膜107を用いているため、バリアメタル膜、カバーメタル膜を別々の工程で形成する場合に比べ、成膜工程が簡略化できる。 その他の効果は、上記第1、第2の実施形態と同様である。

## [0094]

上記実施形態では、バリアメタル膜兼カバーメタル膜107の材料として、Ruを用いた場合について説明したが、これに限られない。例えば、Ru以外でも、TaN上にTaが積層したものやTiN、WN等が挙げられる。なお、バリアメタル膜兼カバーメタル膜107として、Cu中に拡散しない材料を用いた場合、熱処理によっても、バリアメタル膜兼カバーメタル膜107の構成元素は、シード膜204およびめっき膜240中に拡散しない。

#### [0095]

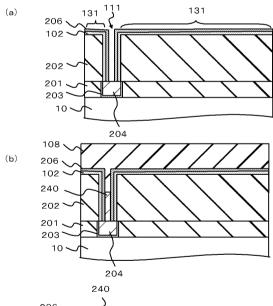

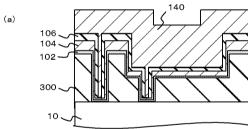

(第4の実施形態)

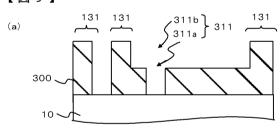

第4の実施形態における半導体装置はデュアルダマシン構造を有する例である。

#### [0096]

図9~11を参照して、第4の実施形態に係る半導体装置の製造工程の一例について説明する。

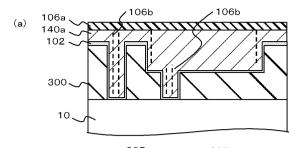

図 9 ( a ) に示すように、半導体基板 1 0 上に、絶縁膜 3 0 0 を形成し、絶縁膜 3 0 0 に凹部 3 1 1 を形成する。凹部 3 1 1 は、デュアルダマシン構造におけるビア孔 3 1 1 a と配線溝 3 1 1 b からなる。

10

20

30

40

#### [0097]

ビア孔311aのアスペクト比は、1.5以下が好ましく、より好ましくは1以下である。通常、めっき成長はほぼ等方的におこなわれるため、電解めっき液への添加剤、または電解めっき条件などを調整することにより最適化される。これに対し、ビア孔311aのアスペクト比を1.5以下、より好ましくは1以下とすることにより、配線溝311bの底部からのめっき成長がほぼ等方的におこなわれた場合であっても、ビア孔311aの底部からのめっき成長がビア孔311aの開口部に到達する前に配線溝311bの底部からのめっき成長によってビア孔311aの開口部が塞がれるのを抑制できる。また、ビア孔311aのアスペクト比が1以下であることにより、カバーメタル膜106がビア孔311aの内壁の一部にのみ形成された場合であっても、ボイド抑制効果を得つつ、めっき成長時間の短縮が可能となる。

[0098]

半導体基板 1 0 上の絶縁膜 3 0 0 に形成されたビア孔 3 1 1 a の底面に相当する位置に C u を含む構造体がある場合には上記第 2 の実施形態及び第 3 の実施形態で説明したのと 同様に、ビア孔 3 1 1 a の底部に C u を含む構造体を露出させ、それをシードとしてめっき成長させてもよい。

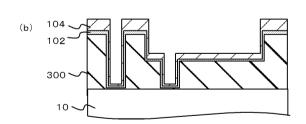

[0099]

図9(b)に示すように、絶縁膜300及び凹部311上に、バリアメタル膜102、シード膜104を順に形成する。バリアメタル膜102、シード膜104の形成には、例えば、スパッタ成膜法のような物理気相成長法、CVD法やALD法のような化学気相成長法、液相成長法、超臨界流体成長法を用いてもよい。但し、凹部311の開口部でなるべく厚膜化しない条件での成膜が好ましい。

[0100]

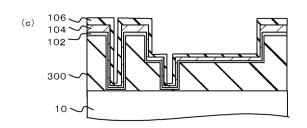

図9(c)に示すように、シード膜104上に、カバーメタル膜106を形成する。カバーメタル膜106は、例えば、イオン化スパッタ成膜法を用いて、凹部311の底部及び側面部に形成される。

[0101]

図10(a)に示すように、選択的エッチングをおこなうことにより、ビア孔311aの底部のカバーメタル膜106、及び配線溝311bの底部のカバーメタル膜106をそれぞれ除去して、それぞれの底部にシード膜104を露出する。このとき、例えばRFバイアスを印加する等の手法を用いて、プラズマから凹部311の底部へ向かうイオンを加速させる等して、凹部311の底部のカバーメタル膜106を除去し、凹部311の側面部と、絶縁膜300上の凹部311以外の領域(フィールド部131)に形成されたシード膜104の上面には、カバーメタル膜106を残留させる。

[0102]

本実施形態において、バリアメタル膜102には、例えばTaN上にTaが積層した材料を用いる。また、バリアメタル膜102は、1~20nmの厚さに成膜される。

[0103]

本実施形態において、シード膜 1 0 4 には、例えば C u を材料として用いる。また、シード膜 1 0 4 は、 1 0 ~ 1 0 0 n m の厚さに成膜される。

[0104]

本実施形態において、カバーメタル膜106には、例えばTiを材料として用いる。また、カバーメタル膜106は、絶縁膜300上のフィールド部131(ビア孔311a、配線溝311bそれぞれの側面部と、絶縁膜300上の凹部311以外の領域)に0.5~10nmの厚さ、凹部311の側面部に0.5~5nmの厚さに成膜される。

[0105]

図10(b)に示すように、ビア孔311a、配線溝311bのそれぞれの底部に露出したシード膜104をシードとして、電解めっき液108を用いて、めっきを行い、めっき膜140を成長させる。これにより、図10(c)に示すように、ビア孔311a、配線溝311bのそれぞれの底部からシード膜104上にめっき膜140を選択成長させ、

10

20

30

40

凹部 3 1 1 内にめっき膜 1 4 0 を埋め込む。

## [0106]

次に、上記第1の実施形態で説明した第一の熱処理、CMP処理、第二の熱処理と同様の処理を行う。以下簡単に説明する。

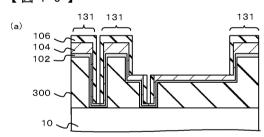

## [0107]

まず、第一の熱処理を施す。そこで、シード膜104とめっき膜140は再結晶化により一体化し、めっき膜140aとなる。また、カバーメタル膜106に含まれるTiが、めっき膜140a中に拡散し、めっき膜140a表面に、キャップ膜106aが形成される(図11(a)参照)。さらに、カバーメタル膜106を構成する元素濃度が周辺の元素よりも高い領域106bが形成される。本実施形態において、領域106bはTi濃度が周辺のTi濃度よりも高い。

[0108]

[0109]

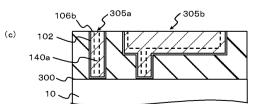

図11(b)に示すように、キャップ膜106a、めっき膜140a、及びバリアメタル膜102を、CMP法により選択的に除去して表面を平坦化し、凹部111内のみにめっき膜140aを残す。これにより、ビア305a、Cu配線305bが形成される。

次に、第二の熱処理を施す。 Cu 配線 105 中に微量に残留したカバーメタル膜 106 の T i などの原子は、ビア 305 a、 Cu 配線 305 b の表面にそれぞれに偏析し、キャップ膜 106 c を形成する(図 11 ( c ) )。また、カバーメタル膜 106 の T i はより均一に拡散する。図 11 ( c ) に示すように、領域 106 b のカバーメタル膜 106 を構成する元素濃度はさらに低くなり、領域 106 d となる。なお、領域 106 d は、カバーメタル膜 106 を構成する元素濃度が周辺の元素よりも高い領域である。

[0110]

本実施形態において、ビア305aおよびCu配線305bの底面部から上面部に向かって1nm以上20nm以下の領域で、Cu以外の金属元素濃度の値が最大となる。

[0111]

本実施形態における効果を説明する。

本実施形態では、半導体装置はデュアルダマシン構造であるため、シングルダマシン構造と比較して工程が簡略化できる。その他の効果は、上記第1の実施形態と同様である。

[0112]

(第5の実施形態)

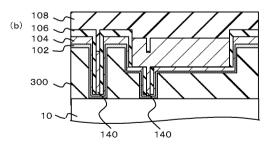

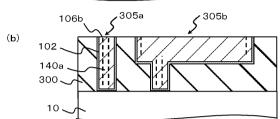

第5の実施形態における半導体装置はデュアルダマシン構造を有する例である。図12~14を参照して、説明する。第4の実施形態では、ビア孔311a及び配線溝311b底部にシード膜104を露出させてめっきを行っていたが、本実施形態では、配線溝31b底部のビア孔311a開口部を除く領域のカバーメタル膜106は除去されず、ビア孔311a底部のシード膜104を露出させてめっきが行なわれる。

[0113]

図12~14を参照して、第5の実施形態に係る半導体装置の製造工程の一例について 説明する。

まず上述したように図9(a)~図10(a)と同様にして、絶縁膜300に凹部311を形成し、バリアメタル膜102、シード膜104、カバーメタル膜106を順に形成し、ビア孔311aの底部にシード膜104を露出させる。なお、配線溝311b底部のビア孔311a開口部を除く領域には、バリアメタル膜102、シード膜104及びカバーメタル膜106が順に堆積している。

[0114]

本実施形態において、バリアメタル膜 1 0 2 には、例えば T a N 上に T a N 積層した材料を用いる。また、バリアメタル膜 1 0 2 は、 1 ~ 2 0 n m の厚さに成膜される。

[0115]

本実施形態において、シード膜 1 0 4 には、例えば C u を材料として用いる。また、シード膜 1 0 4 は、 1 0 ~ 1 0 0 n m の厚さに成膜される。

10

20

30

40

### [0116]

本実施形態において、カバーメタル膜 1 0 6 には、例えば R u を材料として用いる。また、カバーメタル膜 1 0 6 は、絶縁膜 3 0 0 上のフィールド部 1 3 1 (ビア孔 3 1 1 a 、配線溝 3 1 1 b それぞれの側面部と、絶縁膜 3 0 0 上の凹部 3 1 1 以外の領域)に 0 . 5 ~ 1 0 n m の厚さ、凹部 3 1 1 の側面部に 0 . 5 ~ 5 n m の厚さに成膜される(図 1 2 (a))。

### [0117]

図12(b)に示すように、ビア孔311aの底部に露出したシード膜104をシードとして、電解めっき液108を用いて、めっきを行い、めっき膜140を成長させる。これにより、図12(b)、(c)に示すように、ビア孔311aの底部から、シード膜104上にめっき膜140を選択成長させ、凹部311内にめっき膜140を埋め込む。

#### [0118]

このとき、図12(b)のようにビア孔311aが埋まるまでは0.1A/dm²~1A/dm²程度のめっき電流値とし、ビア孔311aが埋まった以降は1A/dm²~10A/dm²程度のめっき電流値とする。通常、Ti(カバーメタル膜106)のめっき成膜はCu(シード膜104)に比べて高電圧が必要である。そのため、0.1A/dm²~1A/dm²~1A/dm²~10A/dm²程度のめっき電流値として低電圧とすると、ビア孔311aの底部のみ成膜することができる。その後、電圧を高くし1A/dm²~10A/dm²程度の高電圧とすると、Ti上にもめっき成長が生じる。

## [0119]

次に、上記第1の実施形態で説明した第一の熱処理、CMP処理、第二の熱処理と同様の処理を行う。以下簡単に説明する。

## [0120]

まず、第一の熱処理を施す。そこで、シード膜104とめっき膜140は再結晶化により一体化し、めっき膜140aとなる。また、カバーメタル膜106に含まれるTiが、めっき膜140a中に拡散し、めっき膜140a表面に、キャップ膜106aが形成される(図13(b)参照)。さらに、カバーメタル膜106を構成する元素濃度が周辺の元素よりも高い領域106bが形成される。本実施形態において、領域106bはTi濃度が周辺のTi濃度よりも高い。

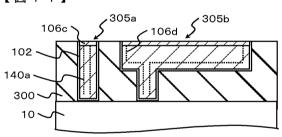

## [0121]

図 1 3 ( c ) に示すように、キャップ膜 1 0 6 a 、めっき膜 1 4 0 a 、及びバリアメタル膜 1 0 2 を、 C M P 法により選択的に除去して表面を平坦化し、凹部 1 1 1 内のみにめっき膜 1 4 0 a を残す。これにより、ビア 3 0 5 a 、 C u 配線 3 0 5 b が形成される。

## [0122]

次に、第二の熱処理を施す。これにより、Cu 配線 105 中に微量に残留したカバーメタル膜 106 の Ti などの原子は、ビア 305 a、Cu 配線 305 b の表面にそれぞれに偏析し、キャップ膜 106 c を形成する(図 14)。また、カバーメタル膜 106 の Ti はより均一に拡散する。図 14 に示すように、領域 106 b のカバーメタル膜 106 を構成する元素濃度はさらに低くなり、領域 106 d となる。なお、領域 106 d は、カバーメタル膜 106 を構成する元素濃度が周辺の元素よりも高い領域である。

## [0123]

本実施形態における効果を説明する。

本実施形態では、ビア孔311a内でのめっき成長が、配線溝311bよりも優先的におこなわれるため、ビア孔311aの開口部でのボイドの発生がより抑制できる。また、ビア孔311aが埋設されてアスペクト比が低くなるため、微細パターンでボトムアップ性が低くてもボイドの発生を抑制できる。その他の効果は、上記第1の実施形態と同様である。

### [0124]

本発明による半導体装置は、上記実施形態に限定されるものではなく、様々な変形が可能である。

10

20

30

40

上記実施形態では、半導体基板10上の絶縁膜に凹部を形成する場合について説明したが、絶縁膜を形成せず、基板の一面に凹部を形成し、その一面の表面及び凹部の側面に、絶縁材料を塗布するなどして絶縁膜を形成してもよい。この場合も、上記実施形態で説明したのと同様にして、凹部内をめっき膜で埋め込むことができる。

## [0125]

### (第6の実施形態)

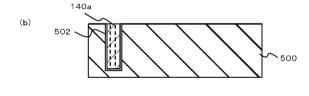

第1の実施形態は、ダマシン配線構造を有する半導体装置について説明したのに対し、 第6の実施形態は、TSV構造を有する半導体装置を用いた例である。

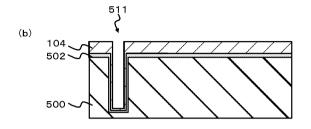

## [0126]

本実施形態において半導体装置は、基板500と、基板500に埋設された貫通シリコンビア505と、を備え貫通シリコンビア505は、貫通シリコンビア505の側面部から中心部に向かって1nm以上20nm以下の領域で、Cu以外の金属元素濃度の値が最大となり、また、基板500と、貫通シリコンビア505の側面部との間に絶縁膜502を有する。

### [0127]

本実施形態において、記載は省略しているが、基板 5 0 0 は、半導体基板やトランジスタ等の半導体素子や層間膜を含む多層配線層を含むものとする。

#### [0128]

図15~図17を参照しつつ、第6の実施形態に係る半導体装置の製造工程の一例について説明する。

## [0129]

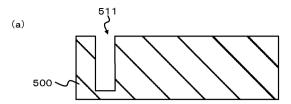

本実施形態の半導体装置の製造方法において、凹部511を有し、凹部511の底部にシード膜104が露出した基板500を準備する工程は、基板500に、凹部511を形成する工程と、凹部511内に絶縁膜502を形成する工程と、凹部511内の絶縁膜502上にシード膜104を形成する工程と、を含む。以下、詳細に説明する。

## [0130]

図 1 5 ( a ) に示すように、基板 5 0 0 の片側の面に凹部 5 1 1 を形成する。つづけて、凹部 5 1 1 内に絶縁膜 5 0 2 を形成する。絶縁膜 5 0 2 は、絶縁材料からなる。

## [0131]

図15(b)に示すように、基板500及び凹部511上の絶縁膜502上に、シード膜104を順に形成する。絶縁膜502及びシード膜104の形成には、例えば、スパッタ成膜法のような物理気相成長法、CVD法やALD法のような化学気相成長法、液相成長法、超臨界流体成長法を用いてもよい。但し、凹部511の開口部でなるべく厚膜化しない条件での成膜が好ましい。また、絶縁膜502の堆積後、シード膜104の堆積前にバリアメタル膜を堆積してもよい。

### [0132]

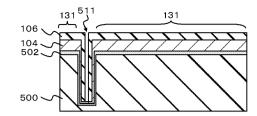

図15(c)に示すように、シード膜104上に、カバーメタル膜106を形成する。カバーメタル膜106は、例えば、イオン化スパッタ成膜法を用いて、凹部511の底部及び側面部、及び絶縁膜502上に形成される。本実施形態において、カバーメタル膜106は、シード膜204よりもめっき成長しにくい導電性膜である。

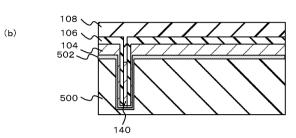

## [0133]

図16(a)に示すように、選択的エッチングをおこなうことにより、凹部511の底部のカバーメタル膜106を除去して、シード膜104を露出する。このとき、例えばRFバイアスを印加する等の手法を用いて、プラズマから凹部511の底部へ向かうイオンを加速させる等して、凹部511の底部のカバーメタル膜106を除去し、凹部511の側面部と、基板500上の凹部511以外の領域(フィールド部131)に形成されたシード膜104の上面には、カバーメタル膜106を残留させる。

### [0134]

次に、図16(b)に示すように、凹部511の底部に露出したシード膜104をシードとして、電解めっき液108を用いて、めっきを行い、めっき膜140を成長させる。

10

20

40

これにより、図16(c)に示すように、凹部511の底部からシード膜104上にめっき膜140を選択成長させ、凹部511内にめっき膜140を埋め込む。

## [0135]

めっき条件は、上記実施形態で説明したのと同様にして行うことができる。

## [0136]

次に、第一の熱処理を施す。そこで、シード膜104とめっき膜140は再結晶化により一体化してめっき膜140aとなる。また、カバーメタル膜106に含まれるTiが、めっき膜140a中に拡散し、めっき膜140a表面に、キャップ膜106aが形成される(図17(a)参照)。さらに、カバーメタル膜106を構成する元素濃度が周辺の元素よりも高い領域106bが形成される。本実施形態において、領域106bはTi濃度が周辺のTi濃度よりも高い。

[0137]

つづけて、図17(b)に示すように、キャップ膜106a、めっき膜140a、及び 絶縁膜502を、CMP法により選択的に除去して表面を平坦化し、凹部111内のみに めっき膜140aを残す。

[0138]

さらに、図17(c)に示すように、基板500の凹部511が形成された面とは反対側の面から、CMP法により基板500を選択的に除去し、貫通シリコンビア505を形成する。これにより、TSV構造を有する半導体装置が得られる。

[0139]

本実施形態における効果も、上記第1の実施形態と同様にして得られる。

[ 0 1 4 0 ]

上記実施形態においては、カバーメタル膜106の材料としてTiを用いた場合について説明したが、Cuを主成分としない材料であればよく、また、100~400 の熱処理により成分がめっき膜中に拡散できる材料がより好ましい。

[0141]

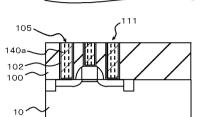

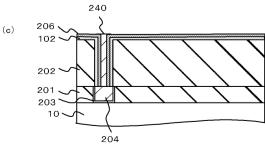

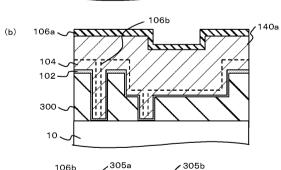

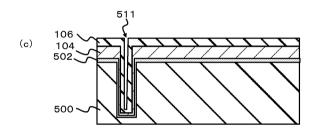

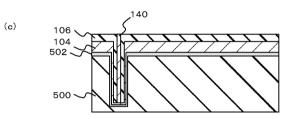

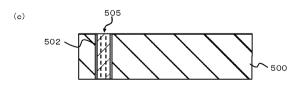

(第7の実施形態)

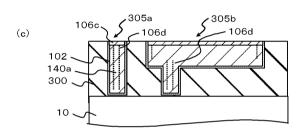

凹部 1 1 1 に形成されるカバーメタル膜 1 0 6 において、上記実施形態では単一層である場合について説明したが、第 7 の実施形態は多層構造となっている。

[0142]

本実施形態における半導体装置の製造方法は、上記第1実施形態で図1(c)~図2(a)を用いて説明したカバーメタル膜106の形成工程以外は同様であるため、以下凹部111内に、カバーメタル膜106を形成する工程について説明し、他の工程は省略する

[0143]

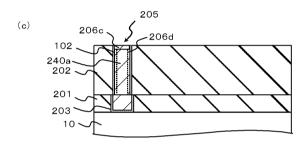

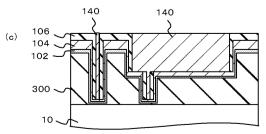

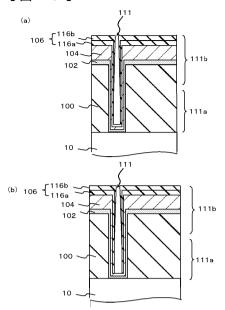

図18、図19は、本実施形態に係る半導体装置の製造工程の一例を示す断面図である。本実施形態において、凹部111内に形成されたカバーメタル膜106は、凹部111 の底部を含む第1領域と、凹部111の開口部を含む第2領域とを有し、第1領域におけるカバーメタル膜106(カバーメタル膜116a)と、第2領域におけるカバーメタル膜106(カバーメタル膜116b)とは異なる材料から形成される。

[0144]

まず、図18に示すように、絶縁膜100及び凹部111上に、例えば、スパッタ成膜法を用いて、カバーメタル膜116aを形成する。つづけて、カバーメタル膜116aとは異なる材料を用いて、カバーメタル膜116a上にカバーメタル膜116bを積層する。カバーメタル膜106は、凹部111の底部を含む第1領域111aと、凹部111の開口部を含む第2領域111bとを有する。

[0145]

次に、図19(a)に示すように、凹部111の側面のカバーメタル膜116bのうち 底面側を選択的に除去して、凹部111の底部側にカバーメタル膜116aを露出する。 これにより、第1領域111aにカバーメタル膜116a、第2領域111bにカバーメ 10

20

30

40

タル膜 1 1 6 b が露出したカバーメタル膜 1 0 6 が得られる。このようなカバーメタル膜 1 0 6 の構造は、カバーメタル膜 1 0 6 の成膜条件や、用いられる金属材料を最適化することで、適宜調整される。

### [0146]

つづけて、凹部111の底部のカバーメタル膜116a及びカバーメタル膜116bを除去して、凹部111の底部にシード膜104を露出する(図19(b))。その後、上記実施形態と同様にして、シード膜104を用いてめっきを行い、所望の半導体装置を得る。

## [0147]

本実施形態において、カバーメタル膜116bは選択性に優れた金属膜、カバーメタル膜116aは密着性に優れた金属膜となっている。これにより、カバーメタル膜106と、めっき成長しためっき膜との密着性が改善し、またCuめっきの選択性が向上できる。

#### [0148]

ここで、密着性に優れる金属膜で凹部の内部、すなわち凹部の底部、側面、及び開口部付近を被覆した場合、凹部の底部から選択的にめっき成長することができるが、凹部の開口部付近で選択破れが生じてボイドが発生することがあった。これに対し、本実施形態のカバーメタル膜106は、凹部111の底部近傍と開口部近傍とで異なる材料から形成されている。本実施形態において、開口部近傍には選択性に優れた金属膜116bが形成されているため、上記のような選択破れによるボイドの発生を抑制できる。他の効果は、上記第1の実施形態と同様にして得られる。

### [0149]

なお、カバーメタル膜106は、図18、19に示された形態に限定されるものではなく、様々な変形が可能である。例えば、第1領域111aが少なくとも凹部111の底部を含み、第2領域111bが少なくとも凹部111の開口部を含むものであってもよい。

#### [0150]

また、カバーメタル膜106は、二層構造に限定されず、さらに異なる材料から形成される多層構造であってもよい。この場合、カバーメタル膜106の除去領域が各層で異なっていてもよい。また、少なくとも一つの層で凹部111の側壁が底面近傍まで被覆されていればよい。この場合も、上記と同様の効果が得られる。

## [0151]

本発明による半導体装置は、上記実施形態に限定されるものではなく、様々な変形が可能である。

#### [0152]

上記実施形態においては、カバーメタル膜106は凹部111内壁のほぼ全面を被覆する場合について説明したが、連続的な被覆に限られず、断続的な被覆であってもよく、また凹部内壁の一部のみの被覆でもよい。ただし、この場合、凹部のアスペクト比は1以下であることが好ましい。これにより、ボイド抑制効果を得つつ、めっき成長の時間短縮が可能となる。一方、カバーメタル膜106が凹部内壁のほぼ全面を被覆する場合は、めっき成長の時間が相対的に長くなるが、より高いボイド抑制効果が得られる。

### [0153]

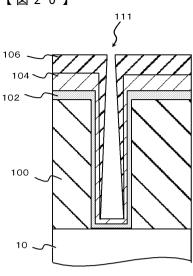

上記実施形態では、図2(a)に示すように、凹部111の底部のカバーメタル膜106を除去して、シード膜104を露出し、凹部111側面のカバーメタル膜106が除去されていない場合について説明したが、これに限られない。例えば、図20に示すように、凹部111の底部だけでなく、底部側の側面に形成されたカバーメタル膜106が除去され、シード膜104が露出してもよい。すなわち、カバーメタル膜106が凹部111内において凹部111の底部側が薄く、開口部側が厚くなっていてもよい。

### [0154]

上記実施形態においては、カバーメタル膜106の材料としてTiを用いた場合について説明したが、Cuを主成分としない材料であればよい。また、100~400 に熱処理することで成分がめっき膜中に拡散できる材料がより好ましい。

10

20

30

40

#### [0155]

カバーメタル膜106の材料としては、例えば、Cu、Ta、Al、Sn、Mn、Ru 、またはIrのうち少なくとも一つを含むものが挙げられる。

## [0156]

上記実施形態においては、第一、及び第二の熱処理雰囲気は、酸素や水分を含む雰囲気で行う場合について説明したが、カバーメタル膜106が、Ta、Cu、Ti、Al、Sn、またはMnのうち少なくとも一つを含む場合は、第一の熱処理を施す工程は、窒素、酸素、水またはアンモニアのうち少なくとも一つを含む雰囲気下でおこなってもよい。これにより、カバーメタル膜106に含まれる金属成分がめっき膜中により拡散できる。以下、参考形態の例を付記する。

1. 凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程と、 前記凹部内に、前記シード膜よりもめっき成長しにくい導電性膜を形成する工程と、 前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程と

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程と、

を含むことを特徴とする半導体装置の製造方法。

2. 1に記載の半導体装置の製造方法において、

前記凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程は、

前記基板に、前記凹部を形成する工程と、

前記凹部内に前記シード膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

3. 1に記載の半導体装置の製造方法において、

前記凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程は、

前記基板上に第一の絶縁層を形成する工程と、

前記第一の絶縁層中にシード膜を埋め込む工程と、

前記第一の絶縁層上に第二の絶縁層を形成する工程と、

前記第二の絶縁層を選択的に除去して前記凹部を形成し、前記凹部の底部に前記シー ド膜を露出させる工程と、

を含むことを特徴とする半導体装置の製造方法。

4. 1または2に記載の半導体装置の製造方法において、

前記凹部を有し、前記凹部の底部にシード膜が露出した基板を準備する工程は、

前記基板に、前記凹部を形成する工程と、

前記凹部内に絶縁膜を形成する工程と、

前記凹部内の前記絶縁膜上に前記シード膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

5. 1乃至4いずれかに記載の半導体装置の製造方法において、

前記シード膜は、Cuを含むことを特徴とする半導体装置の製造方法。

6. 1乃至5いずれかに記載の半導体装置の製造方法において、

<u>前記導電性膜は、Ta、Ti、Al、Sn、Mn、Ru、またはIrのうち少なくとも</u> 一つを含むことを特徴とする半導体装置の製造方法。

7. 1 乃至 6 いずれかに記載の半導体装置の製造方法において、

<u>前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっ</u>き膜を成長させる工程の後に、

\_\_前記導電性膜に含まれる金属元素が、前記めっき膜内に拡散するように、第一の熱処理 を施す工程、

をさらに含むことを特徴とする半導体装置の製造方法。

8. 1乃至7いずれかに記載の半導体装置の製造方法において、

前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっき膜を成長させる工程の後に、

10

20

30

40

前記めっき膜を化学機械研磨して、前記凹部内にのみ前記めっき膜を残す工程と、

\_\_\_前記導電性膜に含まれる金属元素が、前記めっき膜の表面近傍に偏析するように、第二 の熱処理を施す工程と、

をさらに含むことを特徴とする半導体装置の製造方法。

9. 1乃至8いずれかに記載の半導体装置の製造方法において、

前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程は 、RFバイアス印加を利用して前記導電性膜を除去することを特徴とする半導体装置の製 造方法。

10. 1乃至9いずれかに記載の半導体装置の製造方法において、

<u>前記凹部の底部に露出された前記シード膜をシードとして、前記凹部内を埋め込むめっ</u>き膜を成長させる工程は、

前記めっき膜が前記凹部の開口部上に凸部を形成し、前記凸部の高さが1 n m 以上1 0 0 n m 以下であることを特徴とする半導体装置の製造方法。

11. 1乃至10いずれかに記載の半導体装置の製造方法において、

前記凹部内に、前記シード膜よりもめっき成長しにくい導電性膜を形成する工程において、

前記凹部内に形成された前記導電性膜は、前記凹部の底部を含む第1領域と、前記凹部の開口部を含む第2領域とを有し、

前記第1領域における前記導電性膜と、前記第2領域における前記導電性膜とは異なる 材料から形成されることを特徴とする半導体装置の製造方法。

<u>12. 1又は2、あるいは4乃至11いずれかに記載の半導体装置の製造方法において</u>、

<u>前記凹部は、デュアルダマシン法により形成されるデュアルダマシン構造のビアホール</u>および配線溝であって、

前記導電性膜を選択的に除去して、前記凹部の底部に前記シード膜を露出させる工程は 、前記ビアホールおよび / または前記配線溝の底部の前記シード膜を露出させる工程であ ることを特徴とする半導体装置の製造方法。

13. 基板と、

前記基板に埋設された導電体と、

#### を備え、

前記導電体は、前記導電体の側面部から中心部に向かって1 n m 以上2 0 n m 以下の領域で、前記導電体の構成元素以外の金属元素濃度の値が最大となることを特徴とする半導体装置。

14. 13に記載の半導体装置は、

前記基板と、前記導電体の側面部との間に導電性膜または絶縁膜を有することを特徴と する半導体装置。

15. 13または14に記載された半導体装置において、

前記導電体はCu配線であって、前記Cu配線の上面は、前記Cu配線よりもCu濃度が低い膜で覆われていることを特徴とする半導体装置。

16. 15に記載された半導体装置において、

前記 C u 配線よりも C u 濃度が低い膜は、 T i 、 A 1 、 S n 、または M n のうち少なくとも一つを含むことを特徴とする半導体装置。

17. 13乃至16いずれかに記載の半導体装置において、

前記半導体装置がデュアルダマシン構造であることを特徴とする半導体装置。

#### 【符号の説明】

## [0157]

- 10 半導体基板

- 30 半導体基板

- 5 1 半導体基板

- 5 2 絶縁膜

30

10

20

40

```

5 3

凹部

6 1

基板

6 2

絶縁膜

6 3

バリアメタル

6 4

Cu膜

6 5

Cuめっき膜

6 6

凹部

1 0 0

絶縁膜

1 0 2

バリアメタル膜

シード膜

10

1 0 4

1 0 5

Cu配線

カバーメタル膜

1 0 6

1 0 6 a

キャップ膜

1 0 6 b

領域

1 0 6 c

キャップ膜

106d

領域

1 0 7

バリアメタル膜兼カバーメタル膜

1 0 8

電解めっき液

1 1 1

凹部

20

1 1 1 a

領域

領域

1 1 1 b

1 1 6 a

カバーメタル膜

1 1 6 b

カバーメタル膜

1 3 1

フィールド部

1 4 0

めっき膜

1 4 0 a

めっき膜

1 4 0 b

めっき膜

2 0 0

絶縁膜

2 0 1

絶縁膜

30

2 0 2

絶縁膜

2 0 3

バリアメタル膜

2 0 4

シード膜

2 0 5

Cu配線

2 0 6

カバーメタル膜

2 0 6 a

キャップ膜

2 0 6 b

領域

2 0 6 c

キャップ膜

2 0 6 d

領域

2 2 1

絶縁膜

40

2 4 0

めっき膜

2 4 0 a

めっき膜

3 0 0

絶縁膜

3 0 1

絶縁膜

3 0 2

絶縁膜

3 0 4

Cu配線

3 0 5 a

ビア

3 0 5 b

Cu配線

3 1 1

凹部

3 1 1 a

ビア孔

50

3 1 1 b

配線溝

```

| 3 1 | 2 | バリアメタル膜  |

|-----|---|----------|

| 3 1 | 4 | Cuシード膜   |

| 3 4 | 0 | 電解めっき膜   |

| 5 0 | 0 | 基板       |

| 5 0 | 2 | 絶縁膜      |

| 5 0 | 5 | 貫通シリコンビア |

5 1 1 凹部

## 【図3】

(b)

## 【図4】

## 【図5】

## 【図6】

## 【図7】

## 【図8】

## 【図9】

## 【図10】

## 【図11】

## 【図12】

## 【図13】

## 【図14】

(a)

## 【図15】

## 【図16】

## 【図17】

【図19】

【図20】

【図21】

【図22】

# 【図23】

## フロントページの続き

## (56)参考文献 特開2001-023925(JP,A)

特開平07-201988(JP,A)

特開2004-356315(JP,A)

特開2006-269860(JP,A)

特開2000-340593(JP,A)

特開2010-080525(JP,A)

特開2001-319930(JP,A)

特開平05-029315(JP,A)

国際公開第98/040910(WO,A1)

## (58)調査した分野(Int.CI., DB名)

H01L 21/768