### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6770516号 (P6770516)

(45) 発行日 令和2年10月14日(2020, 10, 14)

(24) 登録日 令和2年9月29日(2020.9.29)

| (51) Int.Cl. |        |           | FΙ   |        |   |

|--------------|--------|-----------|------|--------|---|

| HO1L         | 33/12  | (2010.01) | HO1L | 33/12  |   |

| HO1L         | 21/338 | (2006.01) | HO1L | 29/80  | Н |

| HO1L         | 29/778 | (2006.01) | HO1L | 21/205 |   |

| HO1L         | 29/812 | (2006.01) | HO1L | 21/20  |   |

| HO1L         | 21/205 | (2006.01) |      |        |   |

請求項の数 12 (全 17 頁) 最終頁に続く

(21) 出願番号 特願2017-526553 (P2017-526553) (86) (22) 出願日 平成27年11月17日 (2015.11.17) (65) 公表番号 特表2018-503968 (P2018-503968A) (43)公表日 平成30年2月8日(2018.2.8) (86) 国際出願番号 PCT/EP2015/076816 (87) 国際公開番号 W02016/079115 平成28年5月26日 (2016.5.26) (87) 国際公開日 審査請求日 平成30年11月13日 (2018.11.13)

(31) 優先権主張番号 1461109

(32)優先日 平成26年11月18日 (2014.11.18)

(33) 優先権主張国・地域又は機関 フランス(FR) ||(73)特許権者 502124444

コミッサリア ア レネルジー アトミー ク エ オ ゼネルジ ザルタナテイヴ フランス国 エフー75015 パリ、 バテイマン 「 ル ポナン デー 」. リュ ルブラン 25

|(74)代理人 110001416

特許業務法人 信栄特許事務所

||(72) 発明者 チャールズ マチユー

フランス国、エフー38000 グルノー

ブル、82 クール ベリア

審査官 村井 友和

前置審查

最終頁に続く

(54) 【発明の名称】六方格子結晶構造を有するIII-V族半導体層を含んだ半導体構造

### (57)【特許請求の範囲】

### 【請求項1】

基板(102)と、

前記基板(102)の上に配置され、格子定数が前記基板(102)の材料の格子定数 と同一でないような、 $A \ 1_X \ G \ a_Y \ I \ n_{(1-X-Y)} \ N$ に対応する半導体の第1の層( 106)と、ここで0 X < 1、0 < Y 1かつ(X + Y) 1であり、

前記半導体を含んだ、互いに交互に配置された複数の第2および第3の層(108、1 10)を含む、第1および第2の積層体(107、109)において、前記第1の積層体 (107)が、前記基板(102)と前記第1の層(106)の間に配置され、前記第2 の積層体(109)が、前記第1の積層体(107)と前記第1の層(106)の間に配 置される、第1および第2の積層体(107、109)と、

前記第1の積層体(107)と前記第2の積層体(109)の間に配置される、前記第 1の層(106)における前記半導体とほぼ同じ組成を有する半導体の第4の層(112 )と、

前記第4の層(112)と前記第2の積層体(109)の間に配置される、A1Nを含 んだ緩和層(114)とを、少なくとも備える半導体構造(100)であって、

前記第1および前記第2の積層体(107、109)のそれぞれで、

前記第2の層(108)のそれぞれは、前記第3の層(110)の少なくとも一つと直 接接触しており、前記第2および第3の層(108、110)は、一組の第2の層(10 8)が少なくとも1つの第3の層(110)を挟むように、および/または一組の第3の

20

50

### 層(110)が少なくとも1つの第2の層(108)を挟むように配置され、

前記第2の層(108)における前記半導体のGaの比率が、前記基板(102)から前記第1の層(106)に向かう方向に沿って、前記第2の層ごとに変化しながら増加し

前記第3の層(110)における前記半導体のGaの比率<u>が、</u>1つの第2の層とそれに隣接する第3の層(108、110)からなる各グループの平均格子定数が、前記第1の積層体内で前記<u>基板(102)から前記第1の層(106)に向かう</u>方向に沿ってひとグループごとに増加するように、前記<u>基板(102)から前記第1の層(106)に向かう</u>方向に沿って前記第3の層ごとに変化しながら減少し、

前記第2および第3の層(108、110)のそれぞれの厚さが約5nmより薄い、半導体構造(100)。

#### 【請求項2】

請求項1に記載の半導体構造(100)であって、

前記第1の積層体(107)と前記第1の層(106)の間に配置される、前記半導体を含み上下に交互に配置された複数の第2および第3の層(108、110)からなる、n個の第2の積層体(109)と、

前記第1の層(106)の半導体の組成に非常に類似した組成を有する半導体の、n個の第4の層(112)において、前記第4の層(112)の1つが前記第1の積層体(107)に接触して配置され、前記第4の層(112)または他の各第4の層(112)が他の第2の積層体(109)のうちの1つに隣接して配置されるような、n個の第4の層(112)と、

前記第4の層(112)の1つと前記第2の積層体(109)の1つの間にそれぞれ配置される、AINを含んだ複数の緩和層(114)とを備え、

ここで n は 2 ~ 1 9 の整数である、半導体構造(100)。

#### 【請求項3】

前記第1の層(106)の半導体がGaNであり、かつ/または前記第2の層(108)の半導体がA $1_X$ Ga $_{(1_1 X)}$ Nであり、かつ/または前記第3の層(110)の半導体がGaNである、請求項1または請求項2に記載の半導体構造(100)。

### 【請求項4】

前記第 1 および第 2 の積層体の 1 つまたは複数の中において、前記第 2 および第 3 の層 ( 1 0 8 、 1 1 0 ) の半導体の組成と異なる組成を有する、 A 1 Nまたは A 1 G a Nを含んだ第 5 の層 ( 1 1 6 ) が、それぞれ第 2 および第 3 の層 ( 1 0 8 、 1 1 0 ) からなる層 グループ同士の間に差し挟まれる、請求項 1 から請求項 3 のいずれか一項に記載の半導体構造 ( 1 0 0 ) 。

### 【請求項5】

前記基板(102)と前記第1の積層体(107)の間に配置される、A1Nを含んだ第1の緩衝層(104)もまた備える、請求項1から請求項4のNずれか一項に記載の半導体構造(100)。

### 【請求項6】

前記第2 および第3 の層(108、110)のそれぞれの厚さが約2 n mより薄い、請 40 求項1 から請求項5 のいずれか一項に記載の半導体構造(100)。

#### 【請求項7】

各前記第2の層(108)の厚さが同様の厚さであり、かつ/または全ての前記第3の層(110)の厚さが同様の厚さである、請求項1から請求項6のいずれか一項に記載の半導体構造(100)。

### 【請求項8】

前記基板(102)が単結晶シリコンを含む、請求項1から請求項7のいずれか一項に記載の半導体構造(100)。

### 【請求項9】

前記第1の積層体(107)の全体の厚さおよび/または1つまたは複数の前記第2の

積層体(109)のそれぞれの全体の厚さが、約5μm以下である、請求項1から請求項8のいずれか一項に記載の半導体構造(100)。

### 【請求項10】

少なくとも前記第1、第2、第3および第4の層(106、108、110、112) と前記緩和層(114)が、分子線エピタキシまたは気相エピタキシによって作製される 、請求項1から請求項9のいずれか一項に記載の半導体構造(100)を作製する方法。

#### 【請求項11】

請求項1~9のいずれか一項に記載の少なくとも1つの半導体構造(100)と活性域とを含んだ半導体デバイス(200、300)であって、前記活性域が、前記半導体構造(110)の前記第1の層(106)を含む、あるいは前記半導体構造(110)の前記第1の層(106)の上に配置される、半導体デバイス(200、300)。

#### 【請求項12】

前記活性域を含んだ少なくとも1つの発光ダイオード(300)および/または少なくとも1つのトランジスタ(200)を含む、請求項11に記載の半導体デバイス(200、300)。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本明細書の説明は、立方または六方格子結晶構造を有するIII・VまたはII・VI族の半導体層を含んだ半導体構造において、この結晶の構造の格子定数すなわち結晶定数が、その層が形成される基板の材料と異なる半導体構造と、かかる構造を作製する方法に適用される。本明細書ではまた、例えば複数の半導体量子井戸のうちの1つを有する高電子移動度トランジスタ(HEMT)等のトランジスタや発光ダイオードなどの、かかる半導体構造から作製された1つまたは複数の半導体デバイスについて述べる。

#### 【背景技術】

### [0002]

様々な既存の半導体の中で、立方晶または六方晶格子構造を有するIII・V族または II・VI族の半導体、特にGaNが、高品質電子デバイスの作製からみて興味深い。妥 当なコストでGaNを得るために、GaNは、ヘテロエピタキシによって、シリコン基板 やサファイア基板など様々な性質を有する基板上に成長されうる。

#### [0003]

しかしながら、こういったシリコンやサファイアなどの基板の材料の格子定数と熱膨張係数(CTE)は、GaNのものと異なる。したがって、シリコンまたはサファイア基板上へ直接GaNをエピタキシャル成長させると、GaN内に、転位などの重大な結晶欠陥が発生する。

#### [0004]

GaNの成長中におけるこれらの欠陥の出現を防止するために、まず必要な段階は、基板上に緩衝層を成長させることであり、その上にGaNが作製される。この緩衝層はGaNのための核形成層として機能し、この層によってGaN内の応力を変えうる。例えば、かかる緩衝層は、GaNと基板材料の格子定数の差を縮めうるA1Nの層にしうる。ただし単一のA1N緩衝層では、優れた品質のGaNが得られうる厚さは非常に限られる。

## [0005]

厚みのある品質の優れたGaNの層がシリコン上に成長するために重要なことは、GaNがシリコンと直接接触すべきではないこと、GaNのエピタキシ後の冷却中に、GaNとシリコンの熱膨張係数の差が原因でGaN層にクラックが生じないように圧縮応力をかけてGaNが形成されることである。こういった層内に転位があると一定の緩和が生じうることを考慮すると、GaN層内の転位密度を低減することで、より長い期間、圧縮の保持が可能になる。同様にして、GaNが圧縮状態になりうるように各層が成長により連続的に作製されれば、その圧縮によって、周囲温度では、GaN内の応力状態がゼロにリセットされ、ウエハの曲率がゼロになる。

10

20

30

40

#### [0006]

特許文献1に、第1のA1N層およびA1GaN層を含んだ緩衝構造を用いてシリコン基板上にGaNが成長されうる方法が記載されている。この緩衝構造では、ガリウムの比率がその厚さと共に連続的または段階的に徐々に大きくなる。このタイプの、ガリウムの組成がその厚さと共に変化するA1GaN緩衝層によって、GaNを圧縮状態にすることが可能になる。しかしながら、かかる緩衝層に形成されるGaN内における転位数の低減も、かかる材料よって得られ保持されうる張力も、十分ではない。

### [0007]

特許文献 1 および特許文献 2 に、ガリウム比が互いに異なるAlGaN層が交互に形成される緩衝構造の使用についても記載されている。かかる緩衝構造は超格子とも呼ばれる

10

#### [00008]

この構造の目的は、格子定数が小さく厚さが数ナノメートルの緩和層(例えばA1N)を成長させ、次いで、格子定数がより大きく厚さが数十ナノメートルの圧縮層を成長させるというものである。

#### [0009]

かかる超格子は、抵抗層に対して優れた引張強度をもたらしうるが、GaNの最終層における転位の含有量を十分に低減できない。

#### [0010]

GaNについて上記に述べた問題は、立方晶または六方晶格子構造を有する他のIII - V族またはII - VI族半導体を、その半導体とは格子定数が異なる基板上へ成長させる時にも生じる。 20

### 【先行技術文献】

#### 【特許文献】

#### [0011]

【 特 許 文 献 1 】 米 国 特 許 出 願 公 開 第 2 0 0 2 / 0 0 7 4 5 5 2 号 明 細 書

【特許文献2】米国特許出願公開第2012/0223328号明細書

#### 【発明の概要】

【発明が解決しようとする課題】

### [0012]

30

本発明の1つの目的は、立方晶または六方晶格子構造を有するIII - V族またはII - VI族半導体の層を、格子定数がこの半導体とは異なる材料を含んだ基板の上に備える半導体構造において、従来技術による半導体構造を用いて得られうるものよりも、品質 / 応力 / 耐電圧性の間における妥協点が優れている半導体構造を開示することである。

### 【課題を解決するための手段】

#### [0013]

一般に、本明細書は以下の半導体構造を述べる。すなわち、 基板と、

上記基板の上に配置される、立方晶または六方晶格子構造を有するIII-VまたはII-VI族半導体の第1の層において、上記基板が、その材料の格子定数と上記半導体の格子定数が異なるような、第1の層と、

40

上記基板と上記第1の層の間に、交互に配置された互いに接触する上記半導体を含んだ 複数の第2および第3の層からなる第1の積層体とを、少なくとも含んだ、半導体構造で あって、

上記第2の層における半導体元素の比率が、上記基板から上記第1の層に向かう方向に沿って、上記第2の層ごとに変化しながら増加し、

上記第3の層における上記半導体元素の比率が、立方晶格子構造の事例では、隣接する第2の層と第3の層からなる各グループの平均格子定数値が第1の積層体内でほぼ一定であるように、上記方向に沿って上記第3の層ごとに変化しながら減少し、あるいは、六方晶格子構造の事例では、隣接する第2の層と第3の層からなる各グループの平均格子定数

(5)

値が上記方向に沿って第1の積層体内でひとグループごとに増加するように、ほぼ一定または上記方向に沿って上記第3の層ごとに減少するように変化し、

上記第2および第3の層のそれぞれの厚さが約5nmより薄い、半導体構造である。

#### [0014]

本発明は、上記で述べた技術的な問題を解決する手段を開示する。すなわちその手段は

基板と.

上記基板の上に配置され、格子定数が上記基板の材料の格子定数と同一でないような、 A  $1_X$  G a  $_Y$  I n  $_{(\ 1_{-X}\ x_{-Y}\ )}$  N に対応する半導体の第 1 の層と、ここで 0 -X<1、0 < Y -1 かつ ( X+Y ) -1 であり、

上記半導体を含んだ、互いに交互に配置された複数の第2および第3の層からなる、第1および第2の積層体において、上記第1の積層体が、上記基板と上記第1の層の間に配置され、上記第2の積層体が、上記第1の積層体と上記第1の層の間に配置される、第1および第2の積層体と、

上記第1の積層体と上記第2の積層体の間に配置される、上記第1の層における上記半 導体とほぼ同じ組成を有する半導体の第4の層と、

上記第4の層と上記第2の積層体の間に配置される、A1Nを含んだ緩和層とを、少なくとも備える半導体構造において、

上記第1および上記第2の積層体のそれぞれで、

上記第2の層における上記半導体のGaの比率が、上記基板から上記第1の層に向かう方向に沿って、上記第2の層ごとに変化しながら増加し、

上記第3の層における上記半導体のGaの比率がほぼ一定、または、1つの第2の層とそれに隣接する第3の層からなる各グループの平均格子定数が、上記第1の積層体内で上記方向に沿ってひとグループごとに増加するように、上記方向に沿って上記第3の層ごとに変化しながら減少し、

上記第2および第3の層のそれぞれの厚さが約5nmより薄い、半導体構造に対応する

## [0015]

従来技術による超格子と同様に、かかる半導体構造の第1および第2の積層体は、各種組成を有する各層の間に多数の界面を含み、それによってその構造の内部に形成される転位の密度を低減できる。さらに、第1および第2の積層体の内部における格子定数の平均値が、六方晶格子構造を有する材料内では圧縮が適切に保たれるように、立方晶格子構造を有する材料内では応力を回避できるように、増加していくまたは一定のままとなっている。

### [0016]

この半導体構造に含まれる第2および第3の層内の第1および第2の積層体によって、この構造の各種層の内部で適切な圧縮応力を保持しながら、同等の厚さに対して、従来技術による構造よりも優れた品質を有する第1の層を得ることが可能になる。同様にして、この構造により、所与の半導体の品質(第1の層における半導体の品質)に対して、第1の半導体層の厚みを、従来技術による構造で可能になるはずのものよりも厚くすることが可能になる。

#### [0017]

さらに、従来技術に従って使用される緩衝層と異なり、そして、得られる最終的な半導体(第1の層における半導体)の品質が同一の場合、基板と第1の層の間にある層の全体の厚さは、同一の電気的性能に対して、従来技術による緩衝層の厚さよりも薄くでき、このことによってサイズ面で改善でき、製造コストが従来技術による構造よりも低くなる。さらに、基板に形成される層の全体の厚さが増すとウエハの脆性が高まることから、この厚さの低減により、製造されるウエハの堅牢性が向上しうる。

#### [0018]

第2の層における半導体元素の比率、つまり本発明の事例では第2の層における半導体

10

20

30

40

のガリウム比は、基板から第1の層に向かう方向に沿って、第2の層ごとに変化しながら増加する。つまり、第1の積層体の内部にある2個の第2の層について見れば、その2個の第2の層のうちの、基板に近い方の上記元素の比率が、その2個の第2の層のうちのもう一方における上記元素の比率よりも小さくなる。

### [0019]

上記半導体の立方晶格子構造の事例では、第3の層における上記半導体元素の比率は第1の層から基板に向かう方向に沿って、第3の層ごとに変化しながら減少する。つまり、第1の積層体の内部にある2個の第3の層について見れば、その2個の第3の層のうちの、第1の層に近い方の上記元素の比率が、その2個の第3の層のうちのもう一方における上記元素の比率よりも大きくなる。

[0020]

上記半導体の六方晶格子構造の事例では、第3の層における上記半導体元素の比率は全ての第3の層においてほぼ一定である。 < 0 0 0 1 > 方向の成長に対して平行な面以外はかかる半導体内にすべり面が存在しないので、この構成によって、転位を発生させずに圧縮応力を追加する手段が可能になる。具体的には、この圧縮応力により、成長後の冷却中における、例えばGaNとシリコンなどの材料間の熱膨張係数の差を補償できる。

[0021]

III - V族半導体とは、周期表すなわちメンデレーエフの表における、IIIA列すなわち13列目に属する1つまたは複数の元素と、VA列すなわち15列目に属する1つまたは複数の元素とを含んだ半導体である。

[0022]

II-VI族半導体とは、周期表における、IIB列すなわち12列目に属する1つまたは複数の元素と、VIA列すなわち16列目に属する1つまたは複数の元素とを含んだ半導体である。

[0023]

第2および第3の層のそれぞれの厚さは、ある臨界厚さよりも厚くなると緩和現象が生じ、その結果転位および界面準位が形成されてしまうが、それらの厚さを、その臨界厚さより薄いものにできる。具体的には、約5 n mより薄い第2 および第3の層を作製する場合にこれが該当する。これらの層におけるかかる緩和を回避することによって、制御された形で連続的に増加する応力に相当する効果が得られる。

[0024]

それぞれ超格子を形成する複数の積層体を第1の層と基板の間に差し挟むことによって、各種材料の多数の界面が第1の層と基板の間に差し挟まれ、そのことにより、半導体構造が脆弱化することなくその半導体構造全体の厚さが増す。この構成では、第4の半導体層の上に配置される第2および第3の半導体層からなる第2の積層体によって、この第4の半導体層に圧縮応力を加えることが可能になり、最終的に、より厚みのある第1の層をその頂上に含んだ、より厚みのある構造を得ることが可能になる。この構造は例えば、それより薄い同じ半導体の層よりも大きな値の電圧に耐えうるトランジスタの作製に適合する。したがって、電気的にみて、非常に多数の界面を含んだこの構成によって、その構造の内部における電流の漏れを低減しながら、かかる半導体構造から作製される電気および/または電子デバイスの耐電圧性を改善できる。

[0025]

さらに、第4の層と第2の積層体の間にA1Nの緩和層が配置されることによって、第4の層と第2の積層体の間の格子定数による応力を緩和することが可能になり、したがって緩和層上の第2の積層体に対応する超格子の成長が容易になり、さらに、各界面の効率が向上することにより、この構造の内部の漏れ電流が低減される。

[0026]

第2の積層体は、第1の積層体と類似していてもいなくてもよい。

[0027]

上記半導体構造は、

20

10

30

上記第1の積層体と上記第1の層の間に配置される、上記半導体を含み上下に交互に配置された複数の第2および第3の層からなる、n個の第2の積層体と、

上記第1の層の半導体の組成に非常に類似した組成を有する半導体の、n個の第4の層において、上記第4の層の1つが上記第1の積層体に接触して配置され、上記第4の層または他の各第4の層が他の第2の積層体のうちの1つに隣接して配置されるような、n個の第4の層と、

上記第4の層の1つと上記第2の積層体の1つの間にそれぞれ配置される、A1Nを含んだ複数の緩和層とを備えるようなものでありうる。

ここで n は 2 ~ 1 9 の整数である。

[0028]

こうして半導体構造の内部にある積層体の数、したがって超格子の数を増加させることによって、半導体構造内の漏れ電流は小さくなり、その結果かかる半導体構造を含んだ電気/電子デバイスの絶縁破壊電圧値が高くなりうる。

[0029]

第2の積層体は互いに類似していてもいなくてもよい。

[0030]

上記半導体は $A \ 1_X \ G \ a_Y \ I \ n_{(1-X-Y)} \ N$ にしうる。ここで $0 \ X < 1$ 、 $0 < Y \ 1$ かつ(X+Y) 1である。このタイプの半導体は、六方晶格子構造を有する $I \ I \ I$  - Vタイプの半導体である。

[0031]

1つまたは複数の上記第4の層のそれぞれの厚さが、その第4の層が接触して配置される上記積層体の厚さの約0.5~1.5倍でありうる。

[0032]

上記第1の層の半導体がGaNでありうる、かつ/または上記第2の層の半導体がA1 $_{\rm X}$ Ga $_{\rm (1-X)}$ N(これはA1 $_{\rm X}$ Ga $_{\rm (1-X-Y)}$ Nに対応し、ここでX+Y=1である)でありうる、かつ/または上記第3の層の半導体がGaNでありうる。

[0033]

[0034]

上記第1および第2の積層体のうちの1つまたは複数の中において、上記第2および第3の層の半導体の組成と異なる組成を有する、A1NまたはA1GaNを含んだ第5の層が、それぞれ第2および第3の層からなる層グループ同士の間に配置されうる。したがって、この1つまたは複数の積層体では、A1NまたはA1GaNのかかる第5の層は、第2および第3の層をそれぞれ含んだ2個の層グループの間に配置されうる。各第5の層は、これらの層グループのうちの一方の第3の層の上に配置されうる。第5の層におけるA1NまたはA1GaNと、例えばGaNなどでできた第3の層における半導体との間のこういった追加の界面によって、積層体内の漏れ電流がさらに低減される。

[0035]

上記半導体構造がまた、上記基板と上記第1の積層体の間に配置される、AlNを含んだ第1の緩衝層を備えうる。

[0036]

有利には、上記第2および第3の層のそれぞれの厚さが約2nmより薄くできる。

[0037]

全ての上記第2の層の厚さが同様の厚さになりうる、かつ/または全ての上記第3の層の厚さが同様の厚さになりうる。

[0038]

上記基板が単結晶シリコンを含みうる。

[0039]

10

20

30

上記第1の積層体の全体の厚さおよび/または1つまたは複数の上記第2の積層体のそれぞれの全体の厚さが、約5μm以下でありうる。

#### [0040]

上記半導体構造はまた、

上記第1の積層体と上記第1の層の間に配置される、上記第1の積層体における第2および第3の層に類似した、それぞれ互いに接触して交互に配置された複数の第2および第3の層からなる第2の積層体と、

上記第1の積層体と上記第2の積層体の間に配置される、上記第1の層の半導体とほぼ同じ組成を有する半導体の第4の層とを、少なくとも含みうる。

[0.041]

本発明はまた、上記で定義した半導体構造を作製する方法に関し、この方法では、少なくとも上記第1、第2、第3および第4の層と上記緩和層が、分子線エピタキシまたは気相エピタキシによって作製される。

[0042]

本発明はまた、上記で定義した少なくとも1つの半導体構造と活性域とを含んだ半導体デバイスに関し、上記活性域は、上記半導体構造の上記第1の層を含む、あるいは上記半導体構造の上記第1の層の上に配置される。

[0043]

上記半導体デバイスが、上記活性域を含んだ少なくとも1つの発光ダイオードおよび/ または少なくとも1つのトランジスタを含みうる。

[0044]

本発明については、例示的実施形態の説明を添付の図面を参照して読むと、よく理解されよう。これらの例示的実施形態は、単に説明のために示すものであって、本発明を限定するものではない。

【図面の簡単な説明】

[0045]

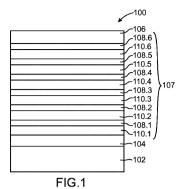

- 【図1】第1の例示的実施形態による半導体構造の図である。

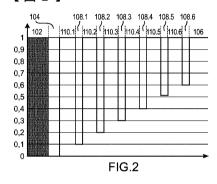

- 【図2】上記半導体構造の第1の例示的実施形態の層の半導体におけるガリウム比の変化の図である。

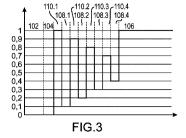

- 【図3】上記半導体構造の第2の例示的実施形態の層の半導体におけるガリウム比の変化の図である。

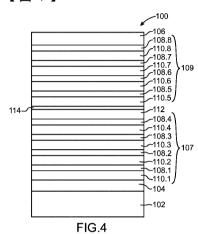

- 【図4】本発明による半導体構造の第1の実施形態の図である。

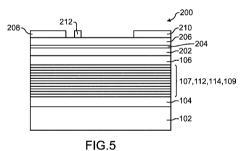

- 【図5】本発明による半導体構造の一実施形態に作製されたパワートランジスタの模式図である。

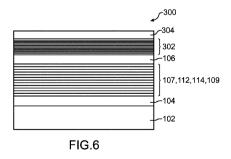

- 【図6】本発明による半導体構造の一実施形態に作製された発光ダイオードの模式図である。

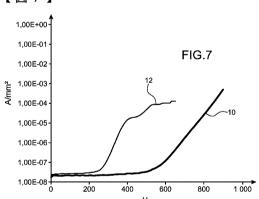

- 【図7】本発明による半導体構造で得られた漏れ電流の図である。

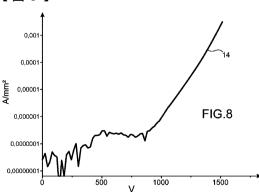

- 【図8】本発明による半導体構造で得られた漏れ電流の図である。

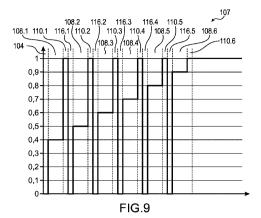

- 【図9】有利な一変形形態での、本発明による半導体構造の積層体の層の半導体における ガリウム比の変化の図である。

【発明を実施するための形態】

[0046]

以下に説明する各図の同一、同様または同等の部品は、各図同士の比較を容易にするために、同じ参照記号を有する。

[0047]

各図に示されている各種部品は、各図を理解し易くするために、必ずしも全てが同じスケールになっているわけではない。

[0048]

様々な可能性(変形形態および実施形態)は、互いに排他的なものではなく、互いに組 み合わせうることを理解されたい。 10

20

30

00

40

20

30

40

50

#### [0049]

まず、半導体構造100の第1の実施形態を示す図1を参照する。

#### [0050]

構造100は基板102を含み、この基板102から開始して構造100の他の半導体層が作製される。この第1の例示的実施形態では、基板102は、厚さが数ミクロンまたは数十もしくは数百ミクロンに等しい(111)タイプの単結晶シリコンを含む。一変形形態として、基板102は、例えばサファイアやSiCなどの他の材料を含みうる。

### [0051]

緩衝層  $1\ 0\ 4$  が基板  $1\ 0\ 2$  上に配置され、構造  $1\ 0\ 0$  の他の半導体層を成長させるための核形成層として機能する。例えば、緩衝層  $1\ 0\ 4$  は A  $1\ N$  を含み、その厚さは約  $5\ n$  m  $\sim 1\ \mu$  m にでき、例えば約  $2\ 0\ 0\ n$  m に等しい。この緩衝層  $1\ 0\ 4$  の別の目的は、構造  $1\ 0\ 0$  の他の半導体層の作製に関わる高温から、基板  $1\ 0\ 2$  を保護することである。

#### [0052]

構造100はまた、その一番上に配置される第1の半導体層106を含む。この第1の層106は、半導体デバイスの活性域の作製に使用される半導体を含む。第1の層106の半導体は、立方晶または六方晶格子構造を有するIII・VまたはII・VI族半導体に対応する。第1の層106の半導体は有利には、六方晶格子構造を有するIII・V半導体であるGaNである。一変形形態として、第1の層106における半導体は、例えばやはり六方晶格子構造を有するIII・V半導体のA1GaNまたはA1GaInNに対応しうる。別の変形形態によると、第1の層106は、例えばGaAsやInPなど、立方晶格子構造を有するIII・V半導体を含みうる。別の変形形態によると、第1の層106は、例えばZnOなどの六方晶格子構造、あるいは例えばZnSやZnSeなどの立方晶格子構造を有するII・VI半導体を含みうる。

#### [0053]

第 1 の層 1 0 6 の厚さは、この層 1 0 6 における半導体の今後の用途に応じて選択される。したがって、第 1 の層 1 0 6 が H E M T タイプのトランジスタの活性域の作製に使用され、数百ボルトの電圧に耐える目的に使用される場合、第 1 の層 1 0 6 の厚さは、例えば約 2  $\mu$  mに等しくできる。一般に、第 1 の層 1 0 6 の厚さは約 1 0 0 n m ~ 5  $\mu$  m に きる。

### [0054]

基板 1 0 2 の材料の格子定数が第 1 の層 1 0 6 の半導体の格子定数と異なるため、そして、品質に優れ、十分に圧縮応力をかけられ、十分に厚みがあり、優れた耐電圧性をもたらしうる半導体を含むような第 1 の層 1 0 6 が作製されうるように、第 2 の半導体層 1 0 8 と第 3 の半導体層 1 1 0 が交互になった積層体が、基板 1 0 2 上に事前に作製される。この層 1 0 8 、 1 1 0 の積層体上に、第 1 の層 1 0 6 が配置される。図 1 では、この積層体に参照記号 1 0 7 が付いている。

## [0055]

この事例における各層 1 0 8 、 1 1 0 の厚さは約 0 . 5 n m (つまり単層 2 枚の厚さ) ~ 5 n mである。好ましくは、各層 1 0 8 、 1 1 0 の厚さは約 2 n m以下、さらには約 1 n m以下である。第 2 の層 1 0 8 の厚さは図 1 の事例のように全て同様の厚さにしうる、あるいは互いに少なくとも部分的に異なりうる。第 3 の層 1 1 0 の厚さは図 1 の事例のように全て同様の厚さにしうる、あるいは互いに少なくとも部分的に異なりうる。最後に、第 2 の層 1 0 8 の厚さは第 3 の層 1 1 0 の厚さと同様であっても、異なっていてもよい(図 1 の事例)。各層 1 0 8 、 1 1 0 の厚さはその臨界厚さよりも薄い。この臨界厚さを超えると緩和が生じ、その緩和は、材料における転位の形成または他の層との界面での界面準位の形成を引き起こしうる。この臨界厚さは上記層の半導体の性質によって決まる。例えば、G a N 上に配置される A 1 N では、G a N は約 2 n m に等しい厚さから緩和し始める。

### [0056]

図1の例では、6個の第2の層108(参照記号108.1~108.6)と、6個の

20

30

40

50

第3の層110(参照記号110.1~110.6)のみが示されている。ただし、構造100は通常例えば約500個、より一般的には約150~2000個という、図1の例よりもはるかに大きな総数の層108、110を含む。積層体107における層108、110の総数は、具体的には、これらの層に対して選択された厚さと、通常は約5μm以下の各層からなるこの積層体107に必要な全体の厚さ(この厚さ自体は第1の層106に必要な厚さによって決まる)に応じて選択される。

#### [0057]

この第1の例示的実施形態では、第3の層110はGaNを含み、第2の層108は、その層ごとにガリウム比(1-X)が変化するA1 $_{\rm X}$  Ga $_{\rm (1-X)}$  Nを含む。ガリウム比は層108ごとに、基板102から第1の層106に向かう方向に変化しながら増加する。したがって、基板102に最も近い第2の層108(図1の例では層108.1)のガリウム比は、例えば0~0.2など、ゼロに近くなりうる。第1の層106に最も近い第2の層108(図1の例では層108.6)のガリウム比は、例えば0.5に等しいなど、約0.6~0.1になりうる。典型的には、2個の最終層(図1の例では層110.6および108.6)の平均組成のガリウム比は、層106が確実に圧縮されるように約0.2を上回るように選択される。一般に、積層体107内部における2個の第2の層108について見ると、その2個の第2の層108のうちの、基板102に近い方におけるガリウム比が、その2個の第2の層108のうちのもう一方におけるガリウム比よりも小さくなっている。

### [0058]

第3の層110の半導体におけるガリウム比は、ほぼ一定である(この事例では1に等 しい)。

### [0059]

### [0060]

図2に、構造100の各種層の半導体におけるガリウム比の変化が示されている。このガリウム比は、基板102および緩衝層104ではゼロであり、第3の層110および第1の層106ではそれぞれ1に等しい。第2の層108におけるガリウム比は、基板102から第1の層106に向かう方向に、層ごとに規則的に増加する(この例では直前の第2の層からの増加量は0.1である)。したがって、互いに隣接する第2の層108の1つと第3の層110の1つからなる各グループの平均格子定数値は、基板102から第1の層106へと増加する。さらに、第2の層108における半導体の組成が層ごとに変化するので、層108、110の積層体107の長手に沿って、応力もやはり変化する。こういった層108、110からなる積層体107の特性の組合せによって、第1の層106では、比較的厚い厚さの層に対して、適切な圧縮応力が保持されると同時に、そこに出現する転位数が低減されうる。この構造によりまた、優れた耐電圧性も得られる。

## [0061]

この第1の例に対する一変形形態として、第3の層110のガリウム比が、基板102から第1の層106に向かう方向に沿って、層ごとに規則的に減少しうる。ただし、この第3の層110ごとのガリウム比の減少は、それと同じ方向に沿った第2の層108におけるガリウム比の増加よりも小さくなっている。これは、互いに隣接する第2の層108の1つと第3の層110の1つからなる各グループの平均格子定数の値が、基板102から第1の層106へと増加するようにするためである。この第3の層110における材料の組成の変化は、層108および110からなる積層体に沿った応力の変化に寄与する。上記と同様に、こういった層108、110からなる積層体107の特性の組合せによって、第1の層106では、比較的厚い厚さの層に対して、適切な圧縮応力が保持されると

20

30

40

50

同時に、そこに出現する転位数が低減されうる。この構造によりまた、優れた耐電圧性も 得られる。

#### [0062]

上述の各事例では、第2の層108の組成の変化および/または第3の層110の組成の変化、したがって、互いに隣接する第2の層108の1つと第3の層110の1つからなる各グループの平均格子定数の変化は、線形であってもなくてもよい。

#### [0063]

第2の例示的実施形態では、層106、108 および110の半導体が、立方晶格子構造を有するIII-V族またはII-VI族半導体に対応しうる。例えば、1つのかかる半導体は $A1_X$ Ga<sub>1-X</sub>Asである。この事例では、緩衝層104は例えばA1As またはGaAsを含み、第1の層106はGaAsを含み、第2 および第3の層108 および110はA1GaAsを含み、このガリウム比は、第2の層108と第3の層110の両方について、層ごとに変化する。層106、108、110の半導体は立方晶格子構造を有しているため、層108と110の積層体の作製は、その積層体の厚さ全体にわたって、層108 および110の中のガリウム比が変化し、第2の層とそれに隣接する第3の層とからなる各グループの平均格子定数値がほぼ一定になるように行われる。

### [0064]

図3に、この第2の実施形態による構造100の各種層における半導体のガリウム比の 変化の例が示されている。この実施形態では、層108、110の積層体は、4個の第2 の層108.1~108.4と4個の第3の層110.1~110.4を含む。この図で 分かるのは、第2の層108のガリウム比が、基板102から第1の層106に向かう方 向に沿って層ごとに規則的に増加し(この例では、第2の層108ごとの、直前の層から の増加量は0.1である)、それと同時に同じ方向に沿って、第3の層110のガリウム 比が、第2の層108のガリウムの増加量に比例して規則的に減少する(この例では、第 3の層110ごとの、直前の層からの減少量は0.1である)ということである。したが って、第2の層108の1つとそれに隣接する第3の層110の1つからなる各グループ の平均格子定数値は、基板102から第1の層106までほぼ一定になる。また、層10 8 および 1 1 0 の作製を、第 3 の層 1 1 0 のガリウム比が、基板 1 0 2 から第 1 の層 1 0 6に向かう方向に沿って層ごとに規則的に増加し、それと同時に同じ方向に沿って、第2 の層108のガリウム比が、第3の層110のガリウム比の増加量に比例して層ごとに規 則的に減少するように行うことによって、層108および110の積層体に沿って応力を 変化させるようにその層108および110の組成に変化をつけながら、基板108と第 1 の層 1 0 6 の間で、第 2 の層 1 0 8 の 1 つとそれに隣接する第 3 の層 1 1 0 とからなる 各グループの、ほぼ一定な平均格子定数値を実現することも可能である。

### [0065]

第1の例示的実施形態と同様に、第2の層108の組成の変化と、第3の層110の組成の変化は、線形であってもなくてもよい。

### [0066]

第1の実施形態によると、構造100は、第1の層106と緩衝層104の間で、上述の積層体と類似した層108、110からなる複数の積層体が上下に配置され、それらの積層体が互いに、第1の層106における半導体の組成と類似した組成を有する半導体の第4の層で分離されるようなものになっている。

### [0067]

図4に、この第1の実施形態による半導体構造100が示されている。したがって、図2を参照して上記に述べたように(考慮したのは層110.1~110.4および108.1~108.4のみ)、上記緩衝層104の上に、ガリウムの組成が変化する第2の層108.1~108.4およびA1GaNの第3の層110.1~110.4からなる第1の積層体107が配置されている。この第1の積層体107の上に、第1の層106のものと類似した組成(この事例ではGaN)を有する第4の層112が配置される。この第4の層112の上に、A1Nを含んだ緩和層114が配置される。緩和層114の厚さ

20

30

40

50

は約5 nm~50 nmなど、例えば約15 nmに等しくしうる。この緩和層114の上に、この事例では第1の積層体107と類似した、第2の層108.5~108.8と第3の層110.5~110.8からなる第2の積層体109が配置される。この第2の積層体109の上に、第1の層106が形成される。

### [0068]

こうして構造100の内部で層108、110の積層体を繰り返すことによって、応力を第4の層112に加えること、したがってより厚みのある半導体構造100を得ることが可能になる。その結果、例えば、この第2の層108と第3の層110の積層体の繰り返しを含まない構造で可能な値よりも高い電圧値に耐えうるトランジスタなどの半導体デバイスの作製などのために、より厚みのある第1の層106が得られうる。

#### [0069]

第4の層112と第2の積層体109の間に緩和層114を挿入することによって、第4の層112と第2の積層体109の間の格子定数による応力を緩和することが可能になり、したがって緩和層上での第2の積層体109の成長が容易になり、さらに構造100内部の漏れ電流が低減される。

#### [0070]

さらに、上記と同様に、層108、110の各積層体107、109は一般に、図4に示されているものよりはるかに大きな数の層を含む。

#### [0071]

図4では、第4の層112および緩和層114によって互いに分離された、層108、110からなる2個の積層体107、109が、基板102と第1の層106の間に配置される。ただし、それより大きな数の層108、110の積層体、つまり第1の積層体107と第1の層106の間に配置される複数の第2の積層体109と、したがってやはり複数の第4の層112と複数の緩和層114(それぞれ2個の第2の積層体109の間に差し挟まれる)が、基板102と第1の層106の間に重ねられて配置されることも可能である。

#### [0072]

全ての事例において、第1の積層体107および第2の積層体109は、特に第2および第3の層108、110の数、全体の厚さ、第2および第3の層108、110におけるGa比などの点で互いに類似していても、していなくてもよい。

### [0073]

各第4の層112の厚さは、その第4の層112が支持される積層体107または10 9の厚さの約0.5~1.5倍にしうる。

### [0074]

有利には、構造100は、1~19個の第2の積層体109を含みうる。

#### [0075]

上記実施形態または変形形態に関係なく、半導体構造100の各種層は、成長によって、特に分子線エピタキシまたは気相エピタキシによって製造される。これらの成長段階は、層108、110については約75mbarなどの低圧で、約1000 に等しい温度、約10mbarに等しいアンモニアの分圧下で実施されうる。例えば、上述の第1の実施形態における層と類似した性質を有する層(GaNを含む)の成長については、圧力約25mbar~1000mbar、温度約900 ~1100 で層が成長されうる。第2の実施形態における層と類似した性質を有する層(GaAsを含む)の成長については、圧力約25mbar~1000mbar、温度約500 ~700 で層が成長されうる。

## [0076]

図7に示されている曲線10は、図4を参照して上記で説明したものと類似した構造100で得られた、最大の絶縁破壊電圧までの漏れ電流を示している。この構造100は、合計340個の第2および第3の層108、110からなる複数の積層体107、109を含み、構造100の全体の厚さは約3.6µmである。比較のために、曲線12が、同

20

30

40

50

様の厚さを有するが積層体107、109を含まない構造で得られた、最終的な絶縁破壊電圧までの漏れ電流を示している。

### [0077]

これらの曲線が示しているのは、第4の層112および緩和層114と結合した積層体107、109を追加することで絶縁破壊電圧値を高めることができ(曲線10と曲線12では250Vの向上)、所与の電圧値に対して漏れ電流が小さくなる(例えば電圧600Vで1000倍の向上)ということである。

### [0078]

図 8 では、曲線 1 4 が、図 4 を参照して上記で説明したものと同様だが 1 個の第 1 の積層体 1 0 7 と 2 個の第 2 の積層体 1 0 9 を含んだ構造 1 0 0 で得られた漏れ電流を示している。これらの積層体の間に 3 個の第 4 の層 1 1 2 と 2 個の緩和層 1 1 4 が配置され、基板 1 0 2 と第 1 の層 1 0 6 の間に差し挟まれた層の全体の厚さは約 6 . 5  $\mu$  mである。かかる構造 1 0 0 の絶縁破壊電圧が 1 5 0 0 V を超え、約 1 2 0 0 V 未満の電圧では漏れ電流が小さいこと(この事例では約 5  $\mu$  A / m m  $^2$  未満)がわかる。

### [0079]

1つの有利な変形形態では、構造100の1つまたは複数の積層体107、109の中において、第2および第3の層108、110に加えて、その第2および第3の層108、110に加えて、その第2および第3の層108、110の半導体の組成と異なる組成を有するA1NまたはA1GaNの第5の層116が、1つの第2の層108と1つの第3の層110からなる各グループの間に挿入されうる。図9に、この有利な変形形態による構造100の積層体の1つ(例えばこの事例では第1の積層体107)の各種層における半導体のガリウム比の変化の例が示されている。緩衝層104の上に形成されたこの第1の積層体107では、その緩衝層104の上に、第2の層108.1と第3の層110.1からなる第1のグループが形成される。その第3の層110.1の上に、この事例ではA1Nを含んだ第5の層116.1が形成される。その第5の層116.1の上に、第2の層108.2と第3の層110.2からなる第2のグループが形成される。その第3の層110.2の上に、A1Nをやはり含んだ第5の層116.2がもう1つ形成される。この第2の層108および第3の層110および第5の層116からなるグループを含んだ構造が複数回繰り返されて、第1の積層体107を形成する。この例では、6個の第2の層108.1~108.6におけるガリウム比が、第2の層ごとに0.4から0.9まで変化する。

#### [0800]

こういったA1NまたはA1GaNを含んだ第5の層116を、1つまたは複数の積層体107、109に挿入することによって、各層の材料の成長がより容易になる。さらに、GaNでできた第3の層110とA1NまたはA1GaNでできた第5の層の間に形成される界面によって、その1つまたは複数の積層体107、109における漏れ電流がさらに低減されうる。

## [0081]

1つまたは複数の積層体107、109の内部に、他の層も差し挟まれうる。例えば、構造100の各種層の成長を容易にし、構造100の耐電圧性を改善し、漏れ電流を低減する目的で、この1つまたは複数の積層体107、109を形成するために繰り返される3個、4個、5個さらには6個の層からなる構造を形成するものなどである。

### [0082]

得られた第1の層106は、構造100によって形成された基板から作製される半導体デバイスの活性層として使用されうる。例えば、HEMTトランジスタ200は、図5に模式的に示されているように、第1のGaN層106から作製されうる。この第1の層106に、炭素などが例えば約10 $^{1.9}$  c m  $^{-.3}$  に等しい濃度でドープされる。その第1の層106の上に、追加の層202が形成される。追加の層202は、第1の層106と類似した半導体を含み、第1の層106より薄く(例えば約100nmに等しい、または約25nm~1μmの厚さ)、ドープ剤としてやはり炭素を例えば約5×10 $^{1.6}$  c m  $^{-.3}$  に等しい濃度で含む。このGaNの追加の層202は、HEMTトランジスタ200のチ

ャネルを形成する。次に、GaNの追加の層202の上に、例えばA1Nを含んだ、約1nmに等しい厚さのスペーサ層204が成膜される。

### [0083]

最後に、このスペーサ層 2 0 4 の上に、例えば約 8 0 %に等しいガリウム比を有する A 1 G a N層 2 0 6 が形成される。この層は、トランジスタ 2 0 0 のチャネルに二次元電子ガスを形成できる。次いでソース領域 2 0 8 およびドレイン領域 2 1 0 、金属接点、ゲート 2 1 2 を形成するなど、従来の各段階によって、H E M T トランジスタ 2 0 0 が完成する。

### [0084]

得られた第1の層106はまた、例えば図6に示されているように、発光ダイオード300のための活性層としても使用されうる。この事例では、第1のGaN層はnドープされうる。次いでこの第1の層106の上に、GaNバリア層およびInGaN発光層を含んだ量子井戸構造302が形成される。最後に、この量子井戸構造302に、pドープされたGaN層304が作製されうる。

### 【符号の説明】

### [0085]

- 100 半導体構造

- 102 基板

- 104 緩衝層

- 106 第1の半導体層

- 107 第1の積層体

- 108 第2の半導体層

- 109 第2の積層体

- 1 1 0 第 3 の 半 導体層

- 112 第4の半導体層

- 1 1 4 緩和層

- 116 第5の層

- 200 HEMTトランジスタ

- 202 追加の層

- 2 0 4 スペーサ層

- 206 AlGaN層

- 208 ソース領域

- 2 1 0 ドレイン領域

- 2 1 2 ゲート

- 300 発光ダイオード

- 302 量子井戸構造

- 3 0 4 pドープされた G a N層

10

20

## 【図1】

## 【図2】

## 【図3】

## 【図4】

## 【図5】

## 【図6】

## 【図7】

## 【図8】

# 【図9】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 21/20 (2006.01)

(56)参考文献 特開2012-243871(JP,A)

特開2014-057020(JP,A)

特開2010-232293(JP,A)

特開2014-036231(JP,A)

米国特許出願公開第2013/0187125(US,A1)

(58)調査した分野(Int.CI., DB名)

H01L 33/00-33/64

H01S 5/00-5/50